Samsung SC32442B54 User Manual

SC32442B54

USER’S MANUAL

Revision 1.0

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-1

1 PRODUCT OVERVIEW

INTRODUCTION

This user’s manual describes SAMSUNG's SC32442B 16/32-bit RISC microprocessor. SAMSUNG’s SC32442B

is designed to provide hand-held devices and general applications with low-power, and high-performance microcontroller solution in small die size. To reduce total system cost, the SC32442B includes the following

components.

The SC32442B is developed with ARM920T core, 0.13um CMOS standard cells and a memory complier. Its lowpower, simple, elegant and fully static design is particularly suitable for cost- and power-sensitive applications. It

adopts a new bus architecture known as Advanced Micro controller Bus Architecture (AMBA).

The SC32442B offers outstanding features with its CPU core, a 16/32-bit ARM920T RISC processor designed by

Advanced RISC Machines, Ltd. The ARM920T implements MMU, AMBA BUS, and Harvard cache architecture

with separate 16KB instruction and 16KB data caches, each with an 8-word line length.

By providing a complete set of common system peripherals, the SC32442B minimizes overall system costs and

eliminates the need to configure additional components. The integrated on-chip functions that are described in

this document include:

• Around 500MHz@1.7V arm and 1.2V internal, 400MHz@1.4V arm and 1.2V internal, 1.8Vmemory, 3.3V

external I/O microprocessor with 16KB I-Cache/16KB D-Cache/MMU

• External memory controller (SDRAM Control and Chip Select logic)

• LCD controller (up to 4K color STN and 256K color TFT) with LCD-dedicated DMA

• 4-ch DMA controllers with external request pins

• 3-ch UARTs (IrDA1.0, 64-Byte Tx FIFO, and 64-Byte Rx FIFO)

• 2-ch SPls

• IIC bus interface (multi-master support)

• IIS Audio CODEC interface

• SD Host interface version 1.0 & MMC Protocol version 2.11 compatible

• 2-ch USB Host controller / 1-ch USB Device controller (ver 1.1)

• 4-ch PWM timers / 1-ch Internal timer / Watch Dog Timer

• 8-ch 10-bit ADC and Touch screen interface

• RTC with calendar function

• Camera interface (Max. 4096 x 4096 pixels input support. 2048 x 2048 pixel input support for scaling)

• 130 General Purpose I/O ports / 24-ch external interrupt source

• Power control: Normal, Slow, Idle, stop and Sleep mode

• On-chip clock generator with PLL

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-2

FEATURES

Architecture

• Integrated system for hand-held devices and

general embedded applications.

• 16/32-Bit RISC architecture and powerful

instruction set with ARM920T CPU core.

• Enhanced ARM architecture MMU to support

WinCE, EPOC 32 and Linux.

• Instruction cache, data cache, write buffer and

Physical address TAG RAM to reduce the effect

of main memory bandwidth and latency on

performance.

• ARM920T CPU core supports the ARM debug

architecture.

• Internal Advanced Microcontroller Bus

Architecture (AMBA) (AMBA2.0, AHB/APB).

System Manager

• Little/Big Endian support.

• Support Fast bus mode and Asynchronous bus

mode.

• Address space: 128M bytes for each bank (total

1G bytes).

• Supports programmable 8/16/32-bit data bus

width for each bank.

• Fixed bank start address from bank 0 to bank 6.

• Programmable bank start address and bank size

for bank 7.

• Eight memory banks:

– Six memory banks for ROM, SRAM, – Two

memory banks for ROM/SRAM/

Synchronous DRAM.

• Complete Programmable access cycles for all

memory banks.

• Supports external wait signals to expand the bus

cycle.

• Supports self-refresh mode in SDRAM for power-

down.

• Supports various types of ROM for booting

(NOR/NAND Flash, EEPROM, and others).

NAND Flash Boot Loader

• Supports booting from NAND flash memory.

• 4KB internal buffer for booting.

• Supports storage memory for NAND flash

memory after booting.

• Supports Advanced NAND flash

Cache Memory

• 64-way set-associative cache with I-Cache

(16KB) and D-Cache (16KB).

• 8words length per line with one valid bit and two

dirty bits per line.

• Pseudo random or round robin replacement

algorithm.

• Write-through or write-back cache operation to

update the main memory.

• The write buffer can hold 16 words of data and

four addresses.

Clock & Power Manager

• On-chip MPLL and UPLL:

UPLL generates the clock to operate USB

Host/Device.

MPLL generates the clock to operate MCU at

maximum 500MHz@1.7V arm and 1.2V interna

400MHz@1.4V arm and 1.2V internal,

• Clock can be fed selectively to each function

block by software.

• Power mode: Normal, Slow, Idle, Deep-stop and

Sleep mode

Normal mode: Normal operating mode

Slow mode: Low frequency clock without PLL

Idle mode: The clock for only CPU is stopped.

Stop mode: All clocks are stopped.

Deep-Stop mode: Arm power off internal clocks

are stopped.

Sleep mode: The Core power including all

peripherals is shut down.

• Woken up by EINT[15:0] or RTC alarm interrupt

from Sleep mode

Stacked Memory

• 512Mbit mSDR x32, VDD=1.8V

• 2Gbit Nand Flash x8, VDD=1.8V

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-3

FEATURES (Continued)

Interrupt Controller

• 59 Interrupt sources

(One Watch dog timer, 5 timers, 9 UARTs, 24

external interrupts, 4 DMA, 2 RTC, 2 ADC, 1 IIC,

2 SPI, 1 SDI, 2 USB, 1 LCD, 1 Battery Fault, 1

NAND and 2 Camera)

• Level/Edge mode on external interrupt source

• Programmable polarity of edge and level

• Supports Fast Interrupt request (FIQ) for very

urgent interrupt request

Timer with Pulse Width Modulation (PWM)

• 4-ch 16-bit Timer with PWM / 1-ch 16-bit internal

timer with DMA-based or interrupt-based

operation

• Programmable duty cycle, frequency, and polarity

• Dead-zone generation

• Supports external clock sources

RTC (Real Time Clock)

• Full clock feature: msec, second, minute, hour,

date, day, month, and year

• 32.768 KHz operation

• Alarm interrupt

• Time tick interrupt

• RTC Low Battery Check

General Purpose Input/Output Ports

• 24 external interrupt ports

• 130 Multiplexed input/output ports

DMA Controller

• 4-ch DMA controller

• Supports memory to memory, IO to memory,

memory to IO, and IO to IO transfers

• Burst transfer mode to enhance the transfer rate

LCD Controller STN LCD Displays Feature

• Supports 3 types of STN LCD panels: 4-bit dual

scan, 4-bit single scan, 8-bit single scan display

type

• Supports monochrome mode, 4 gray levels, 16

gray levels, 256 colors and 4096 colors for STN

LCD

• Supports multiple screen size

– Typical actual screen size: 640x480, 320x240,

160x160, and others.

– Maximum frame buffer size is 4 Mbytes.

– Maximum virtual screen size in 256 color mode:

4096x1024, 2048x2048, 1024x4096 and others

TFT(Thin Film Transistor) Color Displays Feature

• Supports 1, 2, 4 or 8 bpp (bit-per-pixel) palette

color displays for color TFT

• Supports 16, 24 bpp non-palette true-color

displays for color TFT

• Supports maximum 16M color TFT at 24 bpp

mode

• LPC3600 Timing controller embedded for

LTS350Q1-PD1/2(SAMSUNG 3.5” Portrait /

256K-color/ Reflective a-Si TFT LCD)

• LCC3600 Timing controller embedded for

LTS350Q1-PE1/2(SAMSUNG 3.5” Portrait /

256K-color/ Transflective a-Si TFT LCD)

• Supports multiple screen size

– Typical actual screen size: 640x480, 320x240,

160x160, and others.

– Maximum frame buffer size is 4Mbytes.

– Maximum virtual screen size in 64K color mode :

2048x1024, and others

UART

• 3-channel UART with DMA-based or interrupt-

based operation

• Supports 5-bit, 6-bit, 7-bit, or 8-bit serial data

transmit/receive (Tx/Rx)

• Supports external clocks for the UART operation

(UEXTCLK)

• Programmable baud rate

• Supports IrDA 1.0

• Loopback mode for testing

• Each channel has internal 64-byte Tx FIFO and

64-byte Rx FIFO.

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-4

FEATURES (Continued)

A/D Converter & Touch Screen Interface

• 8-ch multiplexed ADC

• Max. 500KSPS and 10-bit Resolution

• Internal FET for direct Touch screen interface

Watchdog Timer

• 16-bit Watchdog Timer

• Interrupt request or system reset at time-out

IIC-Bus Interface

• 1-ch Multi-Master IIC-Bus

• Serial, 8-bit oriented and bi-directional data

transfers can be made at up to 100 Kbit/s in

Standard mode or up to 400 Kbit/s in Fast mode.

IIS-Bus Interface

• 1-ch IIS-bus for audio interface with DMA-based

operation

• Serial, 8-/16-bit per channel data transfers

• 128 Bytes (64-Byte + 64-Byte) FIFO for Tx/Rx

• Supports IIS format and MSB-justified data

format

USB Host

• 2-port USB Host

• Complies with OHCI Rev. 1.0

• Compatible with USB Specification version 1.1

USB Device

• 1-port USB Device

• 5 Endpoints for USB Device

• Compatible with USB Specification version 1.1

SD Host Interface

• Normal, Interrupt and DMA data transfer

mode(byte, halfword, word transfer)

• DMA burst4 access support(only word transfer)

• Compatible with SD Memory Card Protocol

version 1.0

• Compatible with SDIO Card Protocol version 1.0

• 64 Bytes FIFO for Tx/Rx

• Compatible with Multimedia Card Protocol

version 2.11

SPI Interface

• Compatible with 2-ch Serial Peripheral Interface

Protocol version 2.11

• 2x8 bits Shift register for Tx/Rx

• DMA-based or interrupt-based operation

Camera Interface

• ITU-R BT 601/656 8-bit mode support

• DZI (Digital Zoom In) capability

• Programmable polarity of video sync signals

• Max. 4096 x 4096 pixels input support ( 2048 x

2048 pixel input support for scaling)

• Image mirror and rotation (X-axis mirror, Y-axis

mirror, and 180° rotation)

• Camera output format (RGB 16/24-bit and YCbCr

4:2:0/4:2:2 format)

Operating Voltage Range

• Core : 1.7V for 533MHz, 1.4V for 400MHz

• Internal : 1.2V for 400MHz and 1.2V for 300MHz

• Memory:1.8V for 100MHz or 133MHz

• I/O : 3.3V / 2.5V

Operating Frequency

• Fclk Up to 500MHz, 400MHz

• Hclk Up to 133MHz

• Pclk Up to 66MHz or 50MHz

Package

• 332-FBGA

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-5

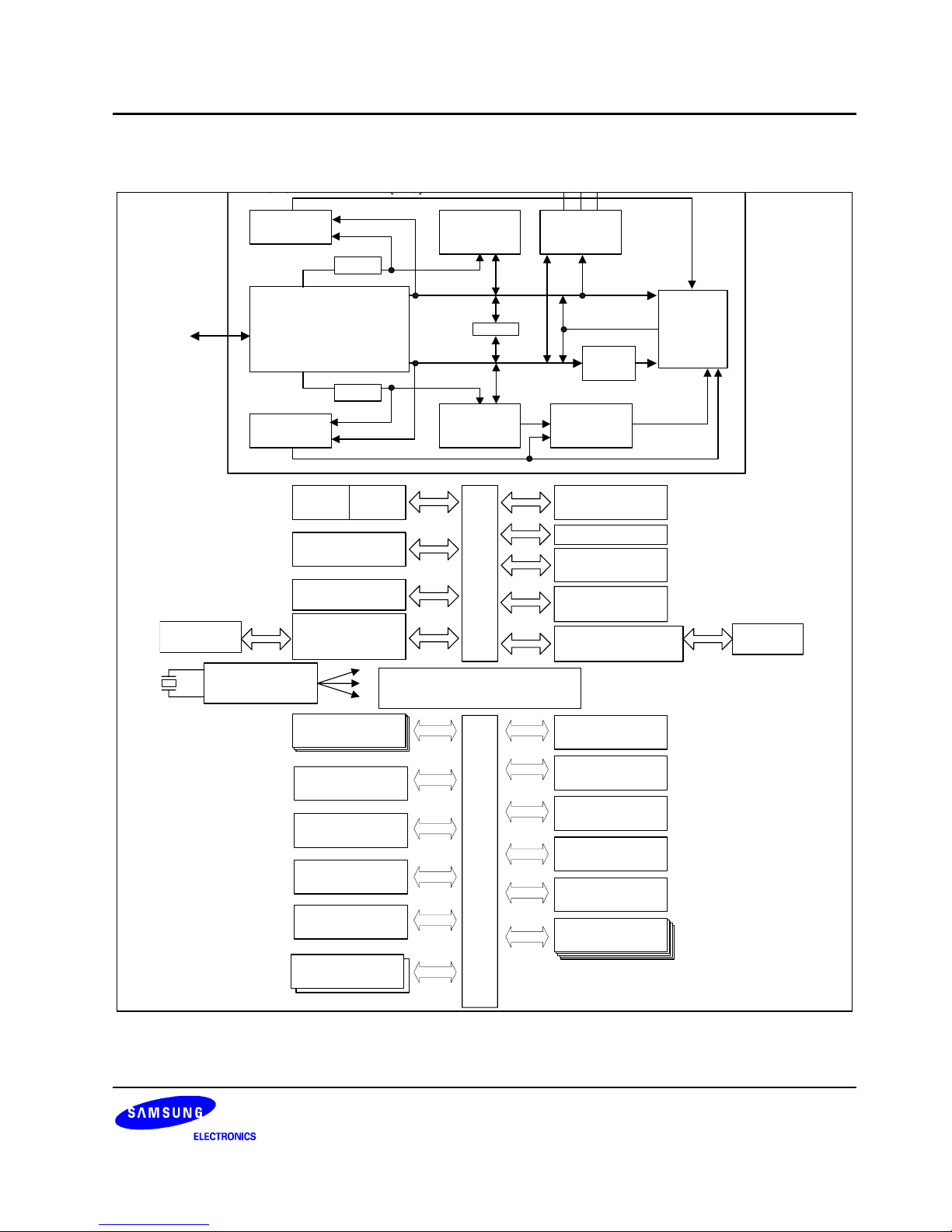

BLOCK DIAGRAM

ARM920T

ARM9TDMI

Processor core

(Internal Embedded ICE)

DD[31:0]

WriteBack

PA Tag

RAM

Data

MMU

C13

DVA[31:0]DVA[31:0]

Instruction

CACHE

(16KB)

Instruction

MMU

External

Coproc

Interface

C13

ID[31:0]

IPA[31:0]

IVA[31:0]

CP15

Write

Buffer

AMBA

Bus

I/F

JTAG

Data

CACHE

(16KB)

WBPA[31:0]

DPA[31:0]

Bridge & DMA (4Ch)

Clock Generator

(MPLL)

A

H

B

B

U

S

Memory CONT.

SRAM/NOR/SDRAM

BUS CONT.

Arbitor/Decode

Power

Management

Interrupt CONT.

USB Host CONT.

ExtMaster

LCD

DMA

LCD

CONT.

A

P

B

B

U

S

I2C

GPIO

I2S

RTC

SPI

ADC

SDI/MMC

USB Device

Watchdog

Timer

BUS CONT.

Arbitor/Decode

Timer/PWM

0 ~ 3, 4(Internal)

SPI 0, 1

UART 0, 1, 2

NAND Ctrl.

NAND Flash Boot

Loader

Camera

Interface

Stacked

Nand Flash

Stacked

mSDR

Figure 1-1. SC32442B Block Diagram

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-6

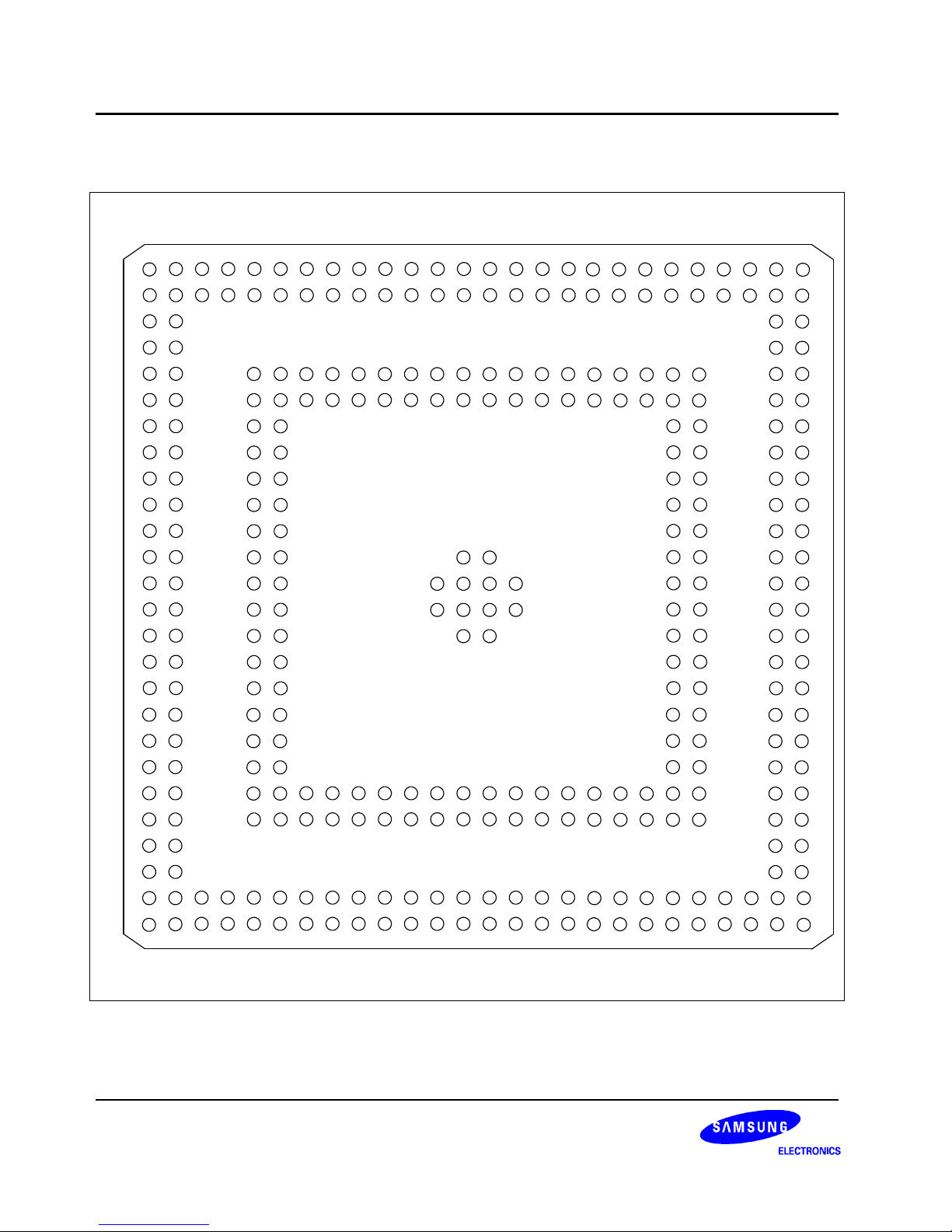

PIN ASSIGNMENTS

TOP VIEW

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17

V

W

Y

AA

AB

AC

AD

AE

AF

18 19 20 21 22 23 24 25 26

14mm(H)x14mm(V)x1.6mm(T)

Figure 1-2. SC32442B Pin Assignments (332-FBGA)

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-7

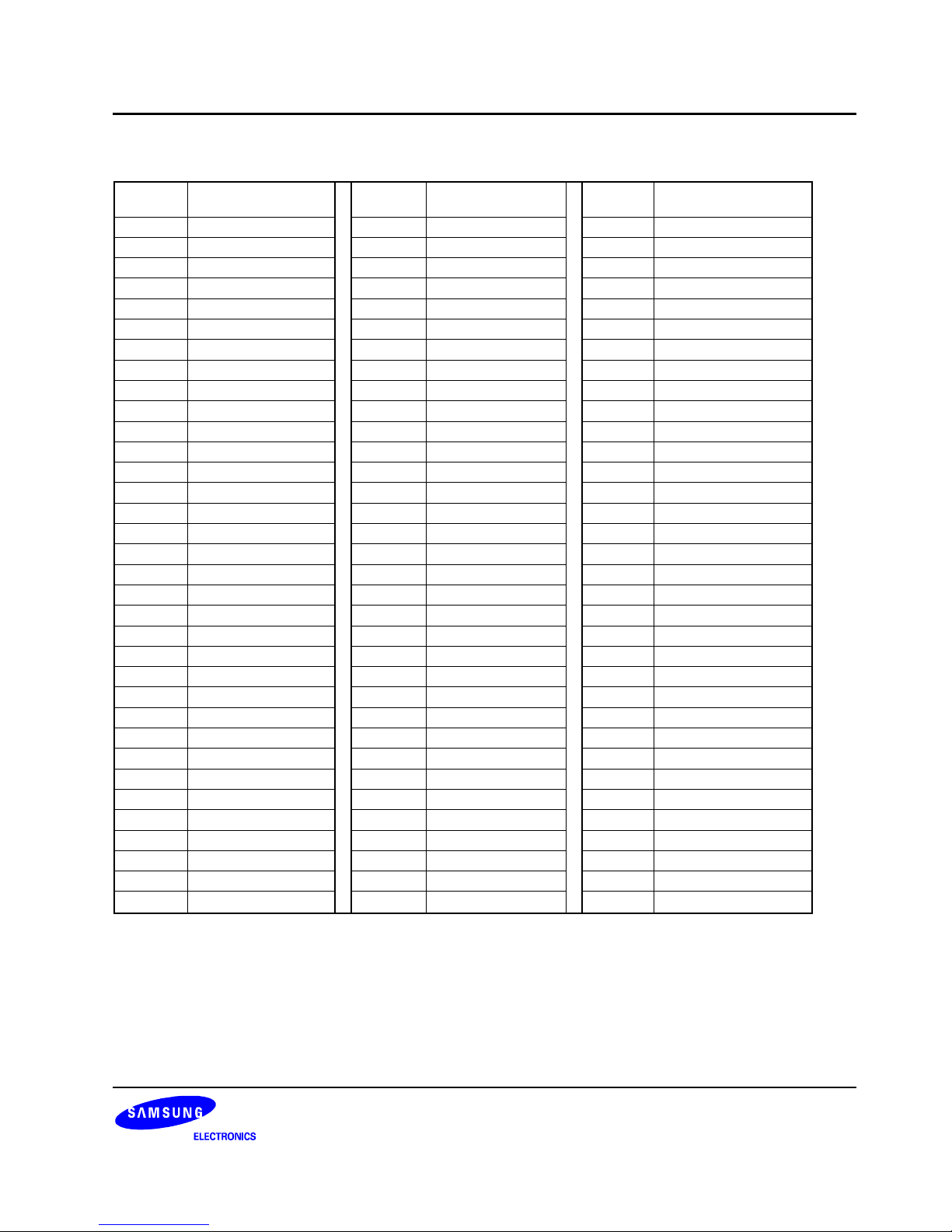

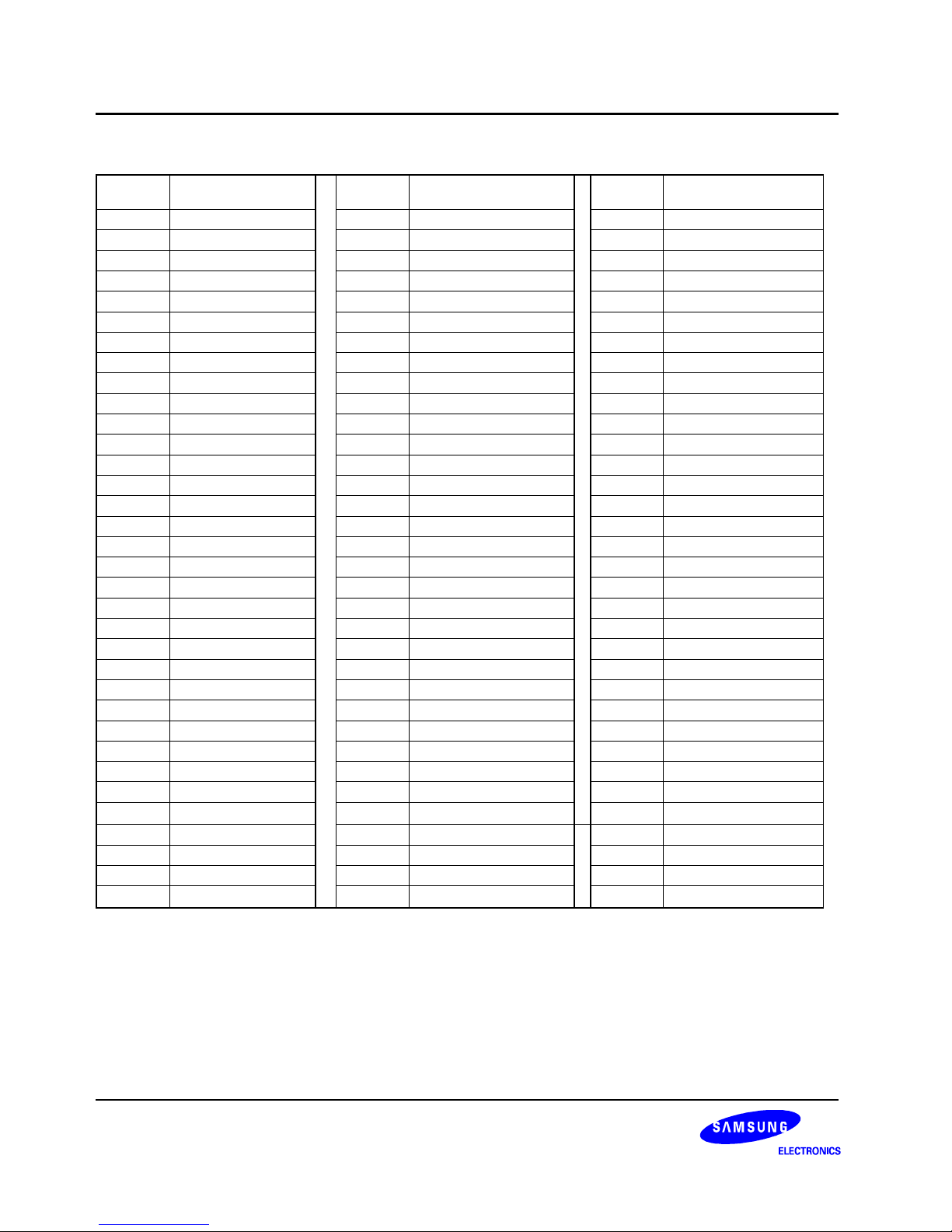

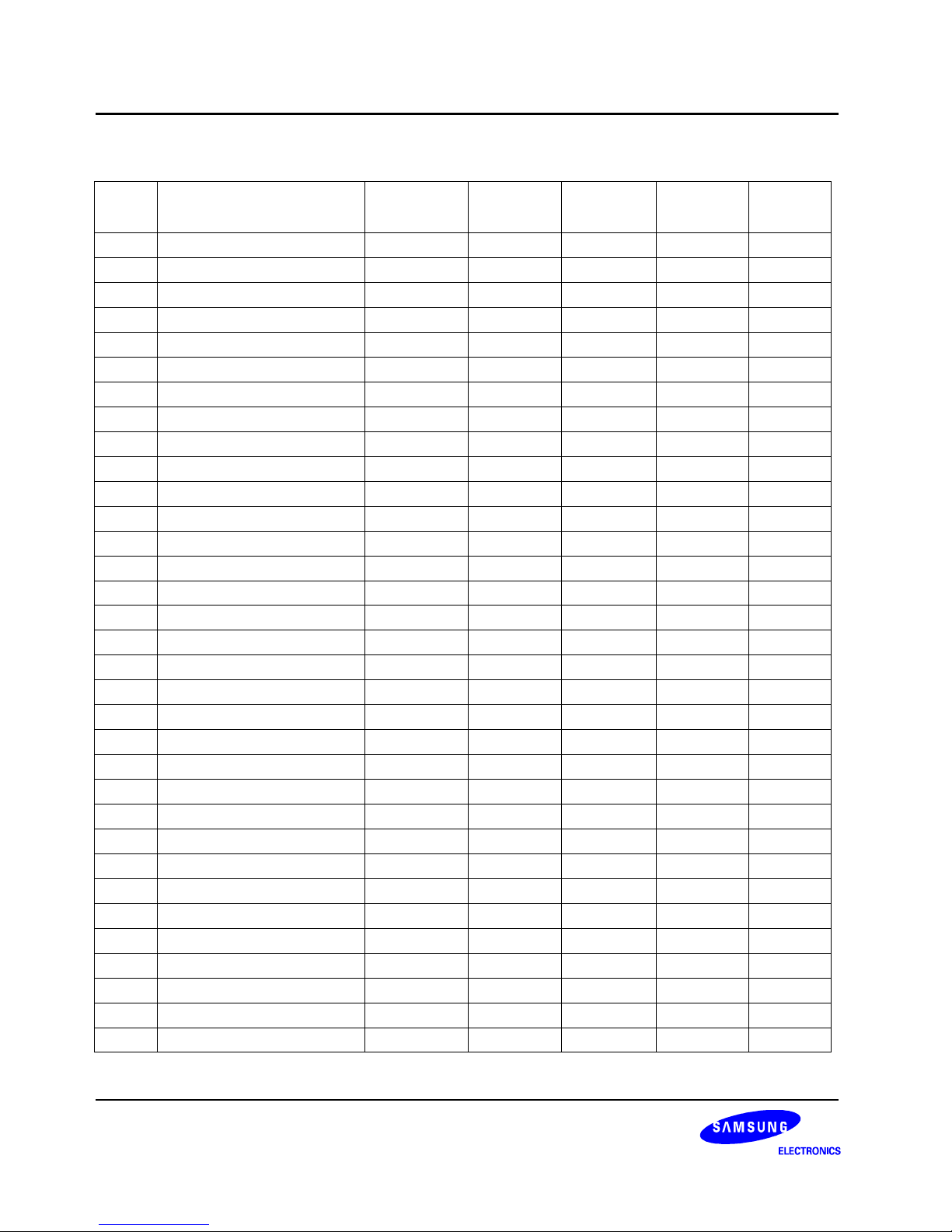

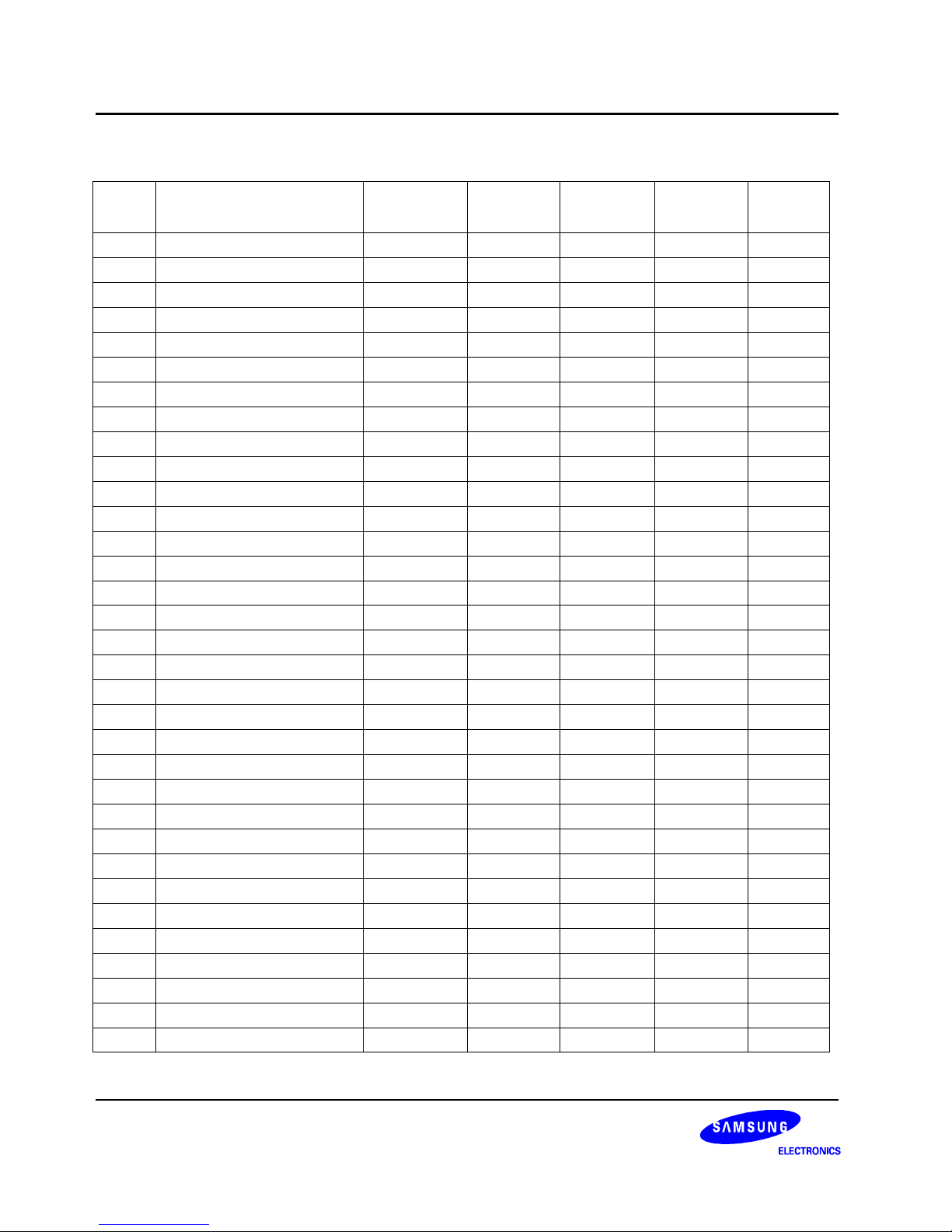

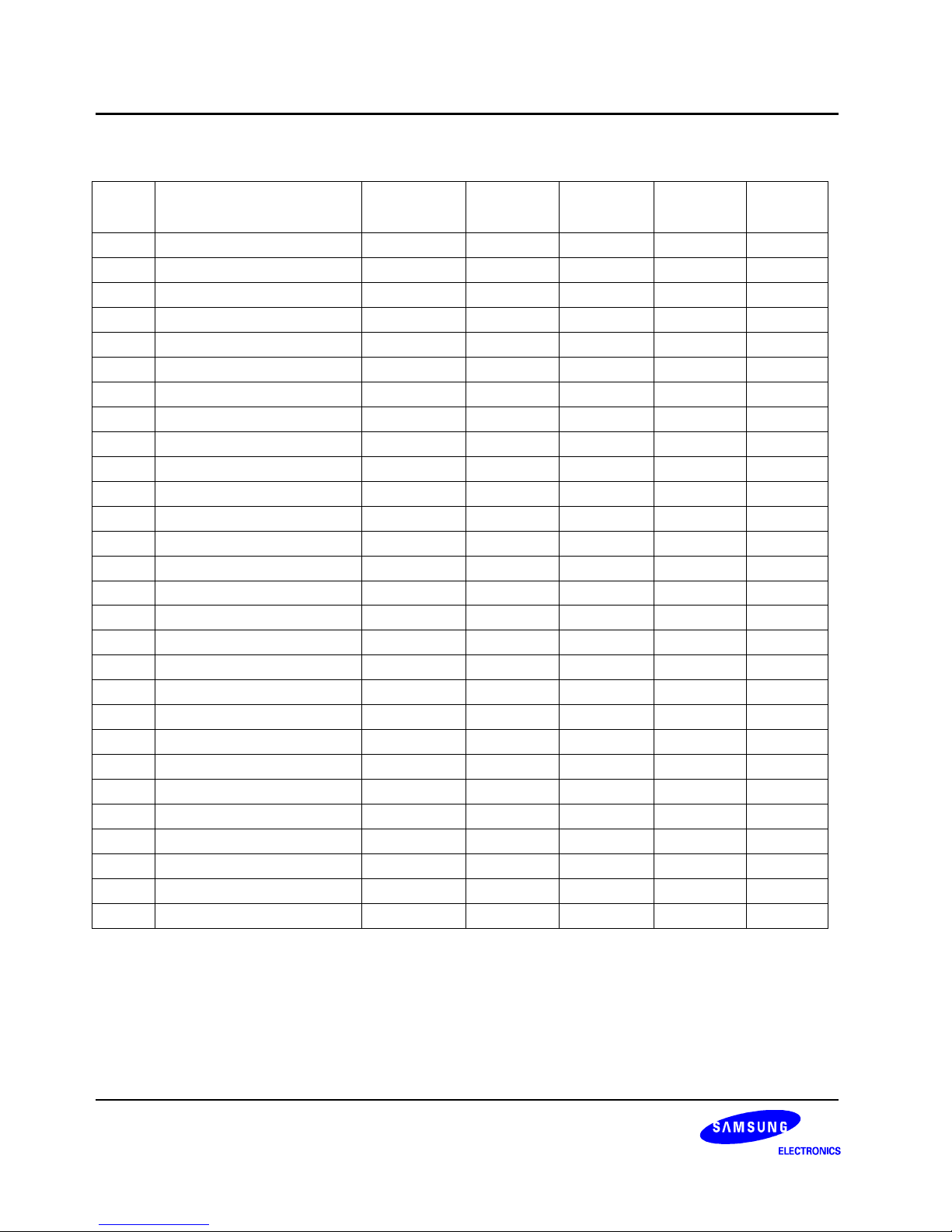

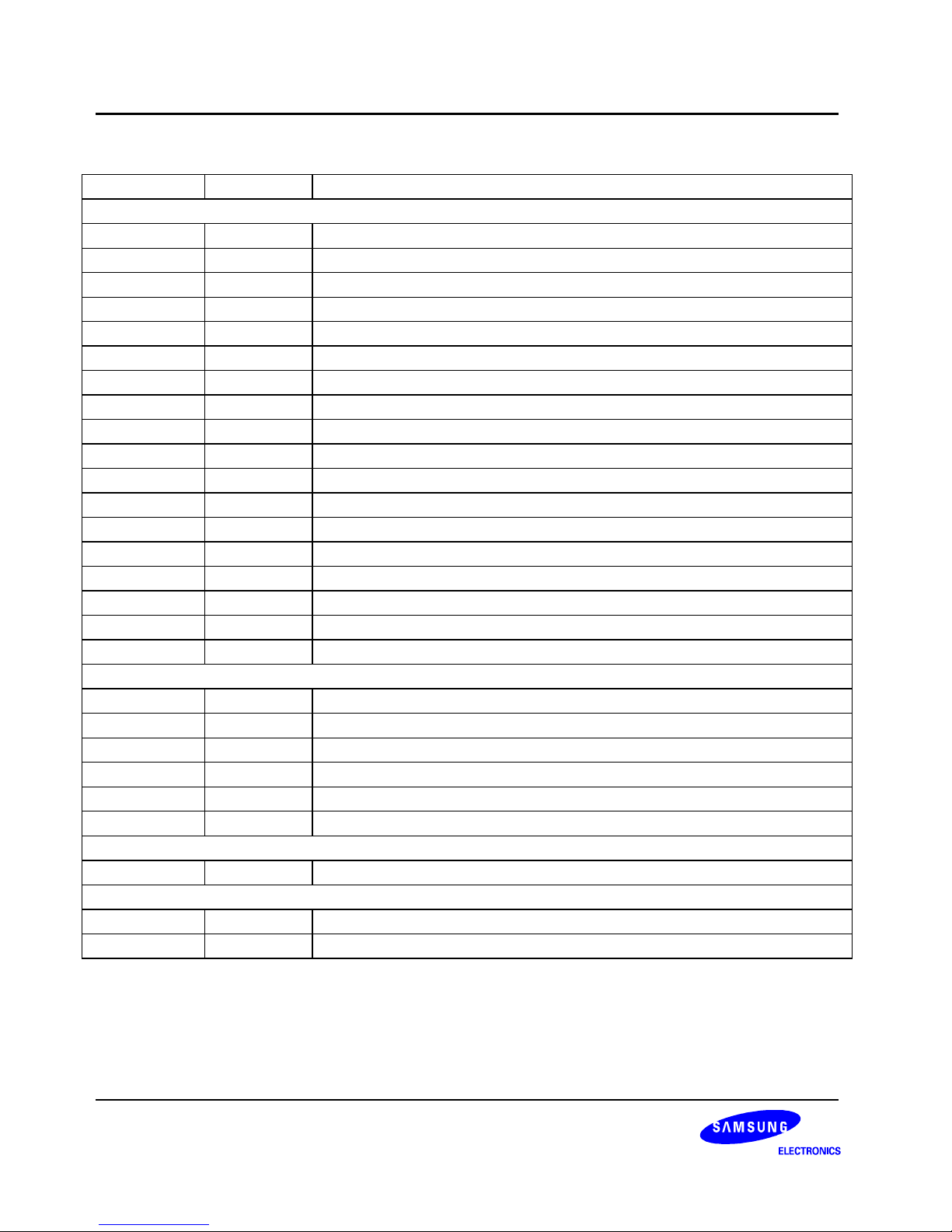

Table 1-1. 332-Pin FBGA Pin Assignments – Pin Number Order (Sheet 1 of 4)

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

A2 ADDR10

B11 ADDR1 E13 VDDI

A3 ADDR13

B12 ADDR12 E14 VSSCOM

A4 NGCS5/GPA16 B13 ADDR15 E15 ADDR16/GPA1

A5 NBE1

B14 ADDR23/GPA8 E16 VDDI

A6 NSRAS

B15 ADDR18/GPA3 E17 VDDMOP

A7 NSCAS

B16 ADDR21/GPA6 E18 ADDR25/GPA10

A8 ADDR2

B17 ADDR26/GPA11 E19 VSSMOP

A9 ADDR7

B18 DATA3 E20 TCK

A10 ADDR9

B19 DATA1 E21 TMS

A11 VSSMOP

B20 DATA8 E22 XTOPLL

A12 ADDR11

B21 VDDI E25 DATA21

A13 ADDR14

B22 VSSOP1 E26 DATA18

A14 ADDR24/GPA9 B23 DATA11 F1 NBE0

A15 DATA2

B24 VDDMOP F2 NGCS7

A16 DATA4

B25 DATA14 F5 VDDI

A17 DATA0

B26 DATA13 F6 NGCS0

A18 DATA5

C1 ADDR5 F7 VDDIARM

A19 DATA6

C2 NWAIT F8 VDDIARM

A20 VDDMOP

C25 DATA19 F9 CAMVSYNC/GPJ9

A21 DATA7

C26 DATA15 F10 VSSMOP

A22 DATA9

D1 ADDR3 F11

CAMCLKOUT/GPJ11

A23 DATA10

D2 NGCS4/GPA15 F12 ADDR20/GPA5

A24 DATA16

D25 VSSMOP F13 ADDR19/GPA4

A25 DATA12

D26 DATA17 F14 ADDR17/GPA2

B1 ADDR6

E1 NBE2 F15 ADDR22/GPA7

B2 ADDR8

E2 VSSMOP F16

CAMDATA0/GPJ0

B3 SCKE

E5 VSSMOP F17 TXD1/GPH4

B4 NGCS6

E6 NGCS3/GPA14 F18

CAMRESET/GPJ12

B5 NGCS2/GPA13 E7 NGCS1/GPA12 F19 TOUT1/GPB1

B6 NBE3

E8 VDDMOP F20 PWREN

B7 VDDI

E9 VDDI F21 VDDALIVE

B8 VSSCOM

E10 SCLK1 F22 TDI

B9 ADDR4

E11 ADDR0/GPA0 F25 VDDI

B10 NOE

E12 VDDMOP F26 DATA20

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-8

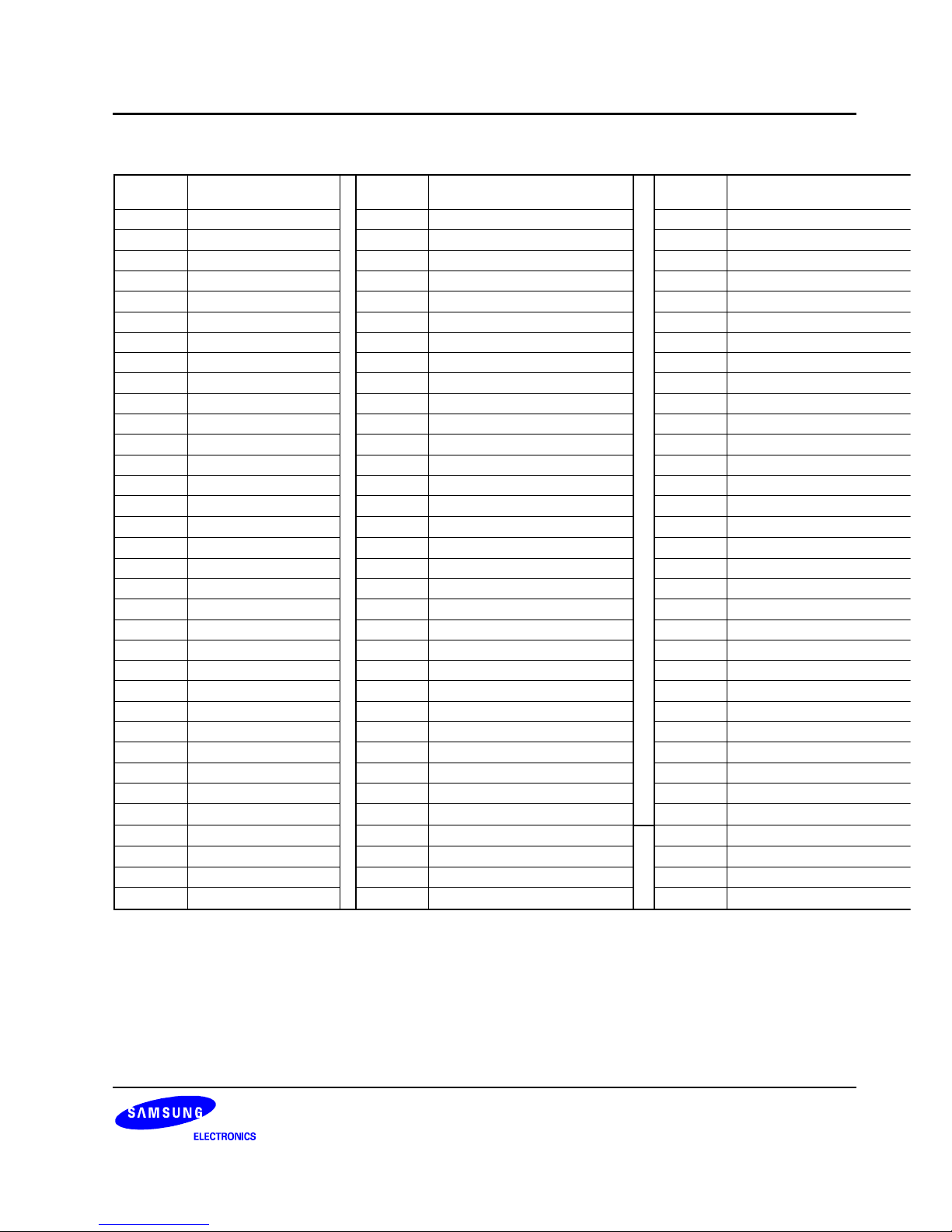

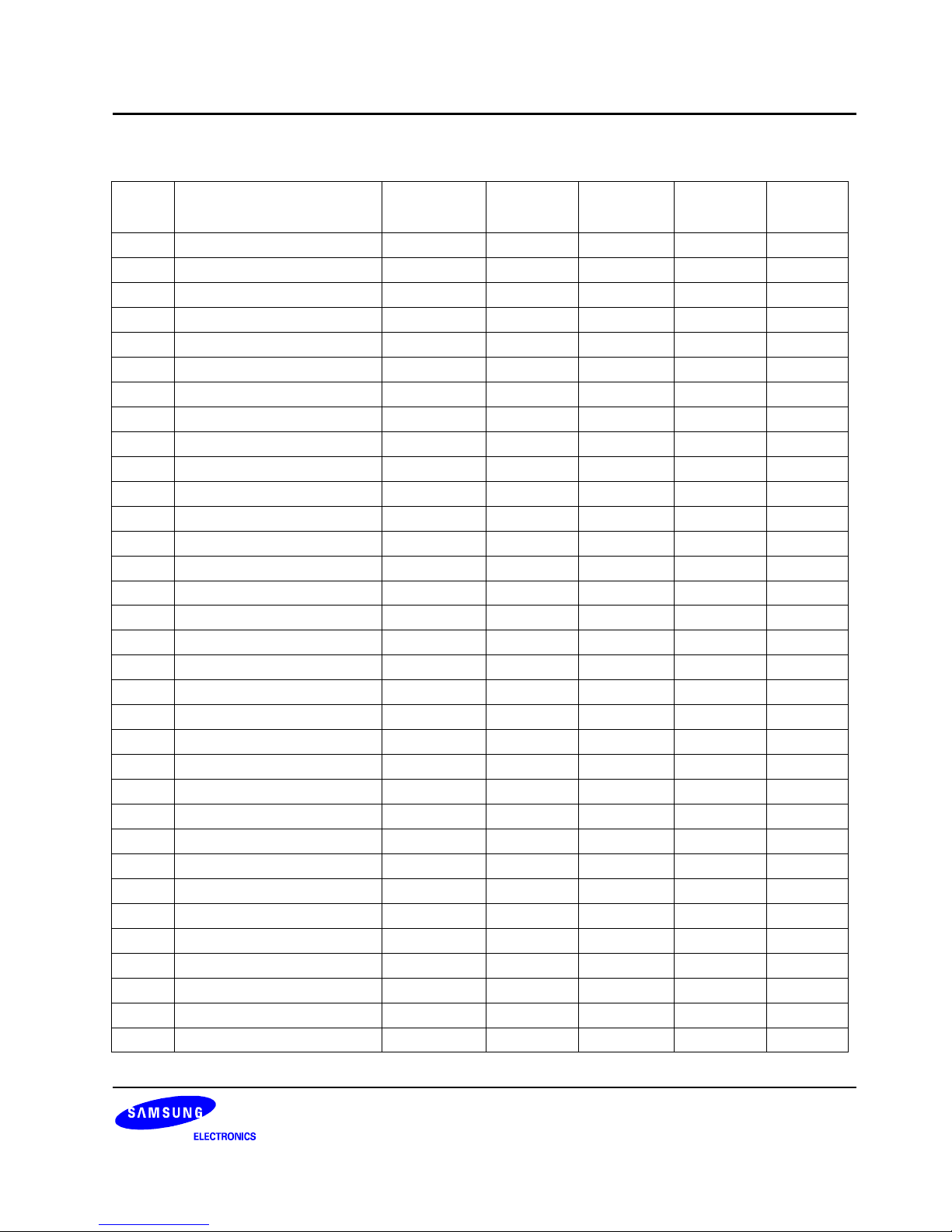

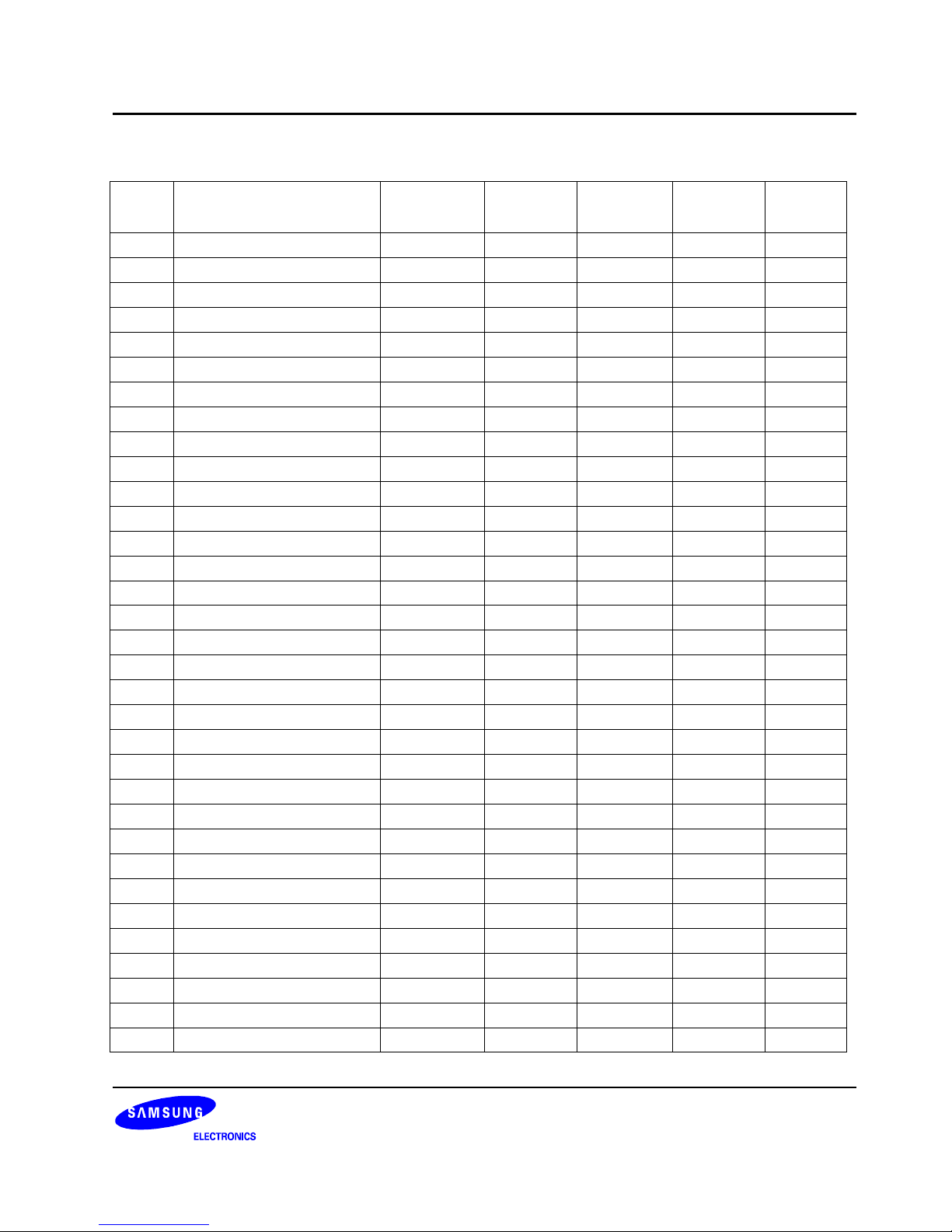

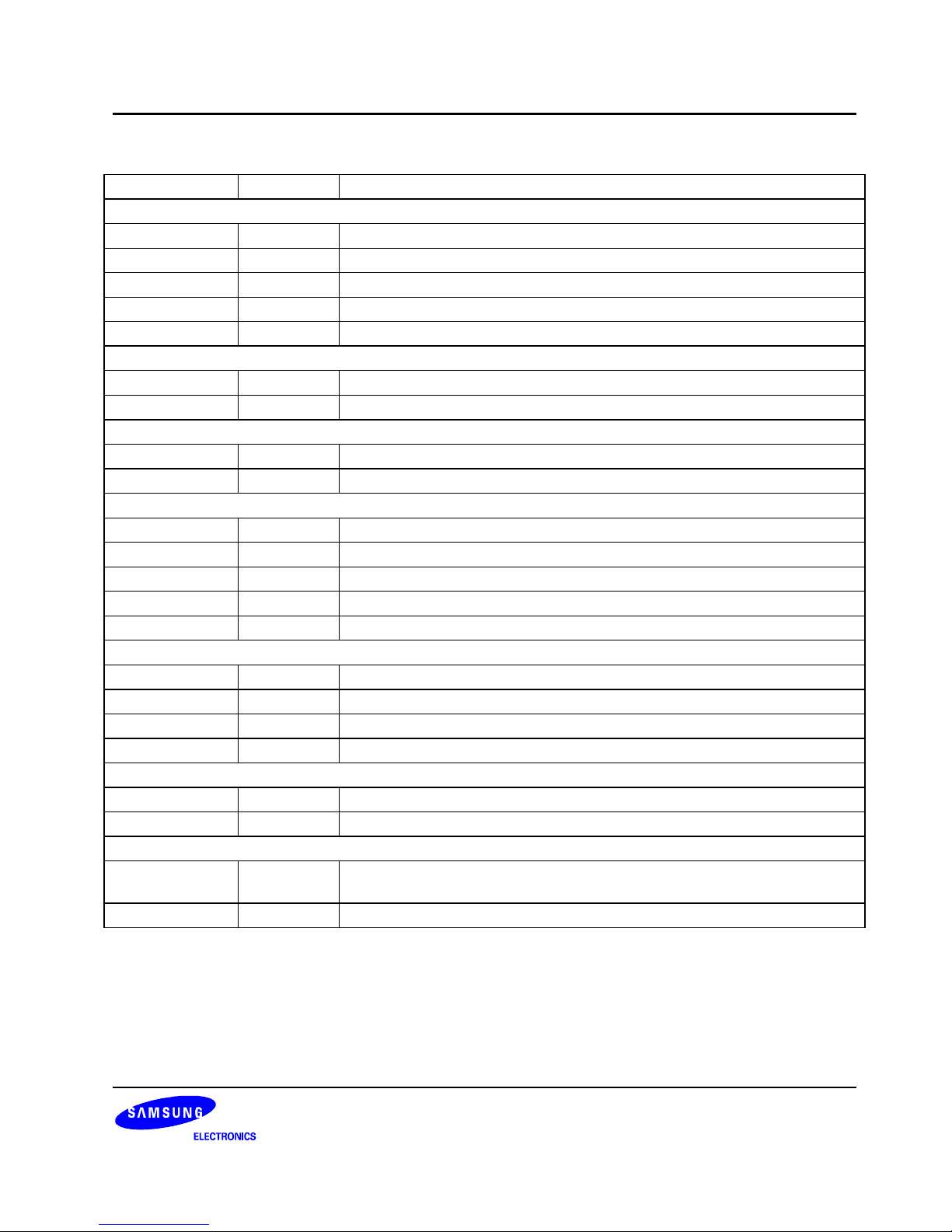

Table 1-1. 332-Pin FBGA Pin Assignments – Pin Number Order (Sheet 2 of 4)

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

G1 SCLK0

L5 TOUT0/GPB0 P14 VSSCOM

G2 VDDMOP

L6 CAMDATA6/GPJ6 P15 VSSCOM

G5 NFCE/GPA22 L21 TXD2/NRTS1/GPH6 P21 VDDOP1

G6

CAMDATA5/GPJ5

L22 TXD0/GPH2 P22 VSSA_UPLL

G21 VSSMOP

L25 XTIPLL P25 RXD1/GPH5

G22 EXTCLK

L26 DATA25 P26 DATA30

G25 VSSMOP

M1 /CE R1 VSSCOM

G26 DATA22

M2 CAMDATA4/GPJ4 R2 NXDACK0/GPB9

H1 ALE/GPA18

M5 VSSCOM R5

LEND/GPC0

H2 CLE/GPA17

M6 NXBACK/GPB5 R6 LCDVF1/GPC6

H5 CAMHREF/GPJ10 M13 VSSCOM R13 VSSCOM

H6 VSSOP2

M14 VSSCOM R14 VSSCOM

H21 VDDMOP

M21 RXD2/NCTS1/GPH7 R21 SDDAT1/GPE8

H22 NRESET

M22 TDO R22 EINT4/GPF4

H25 VSSCOM

M25 BATT_FLT R25 RXD0/GPH3

H26 DATA26

M26 DATA29 R26 NRTS0/GPH1

J1 NFWE/GPA19 N1 NWE T1 VSS_NF

J2 VSSCOM

N2 TOUT3/GPB3 T2 VM/GPC4

J5 CAMPCLK/GPJ8 N5 VDDOP2 T5 VDDIARM

J6 CAMDATA3/GPJ3 N6 NXDACK1/GPB7 T6 NXDREQ0/GPB10

J21 NCTS0/GPH0 N12 VSSCOM T21 VDDA_UPLL

J22 TOUT2/GPB2 N13 VSSCOM T22 EINT0/GPF0

J25 DATA24

N14 VSSCOM T25 EINT7/GPF7

J26 DATA23

N15 VSSCOM T26 EINT3/GPF3

K1 NFRE/GPA20 N21 EINT2/GPF2 U1 /WP

K2 CAMDATA1/GPJ1 N22 UCLK/GPH8 U2 /CS

K5 VDDALIVE

N25 NTRST U5 VDDIARM

K6 CAMDATA2/GPJ2 N26 DATA28 U6 VFRAME/GPC3

K21 EINT6/GPF6

P1 VCC_NF U21 IICSDA/GPE15

K22 VSSCOM

P2 TCLK0/GPB4 U22 VSSOP

K25 DATA31

P5 NXBREQ/GPB6 U25 EINT5/GPF5

K26 DATA27

P6 NXDREQ1/GPB8 U26 EINT1/GPF1

L1 FRNB

P12 VSSCOM V1 LCDVF0/GPC5

L2 CAMDATA7/GPJ7 P13 VSSCOM V2 VD2/GPC10

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-9

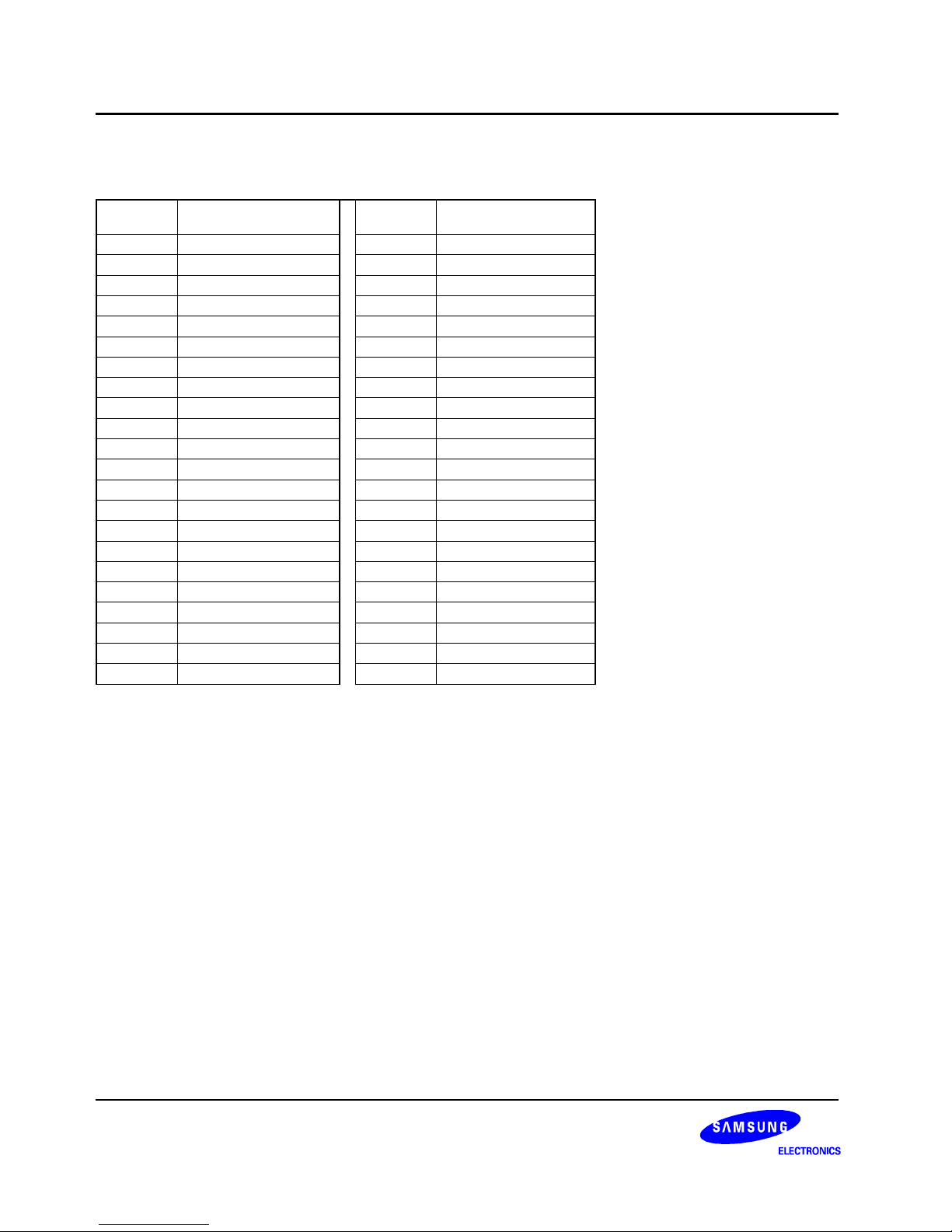

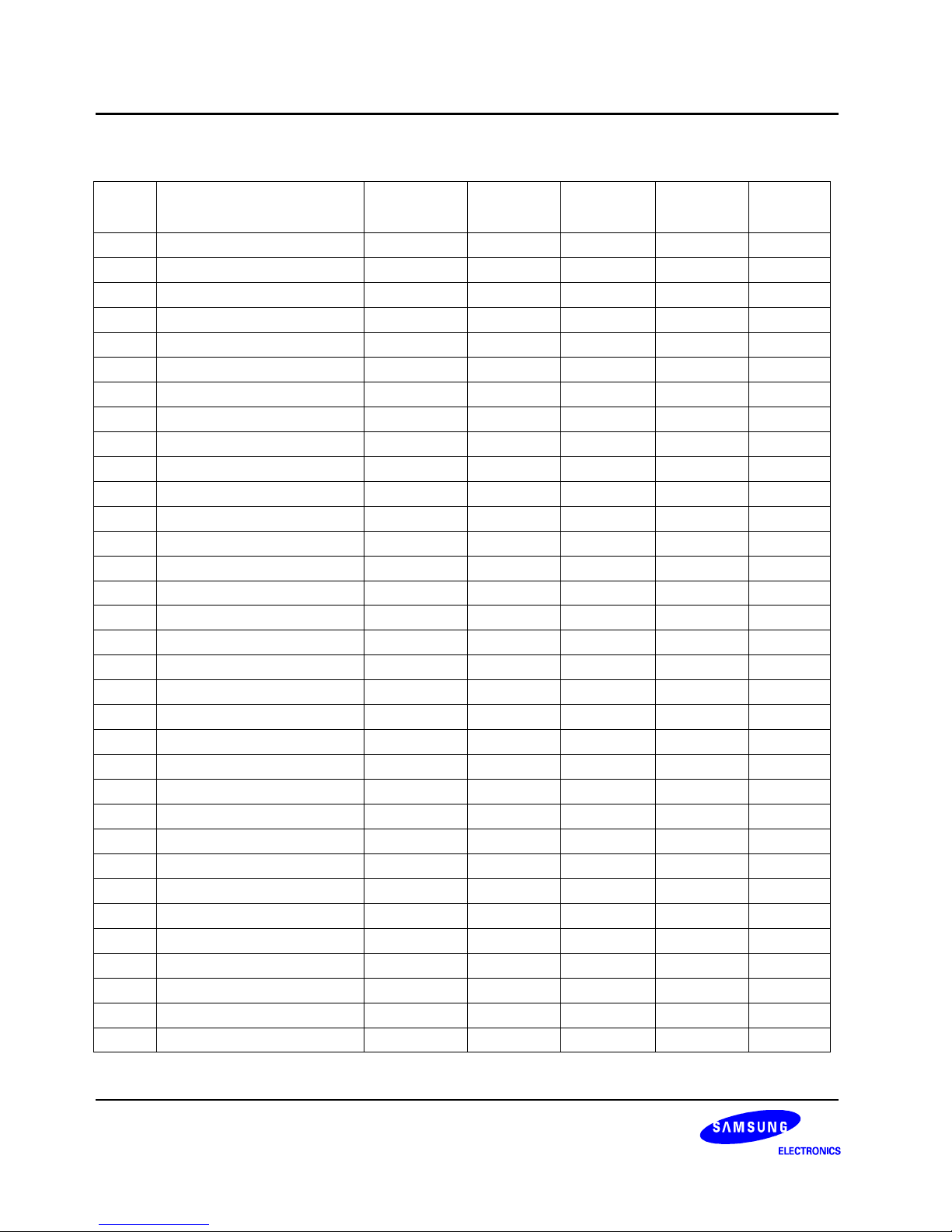

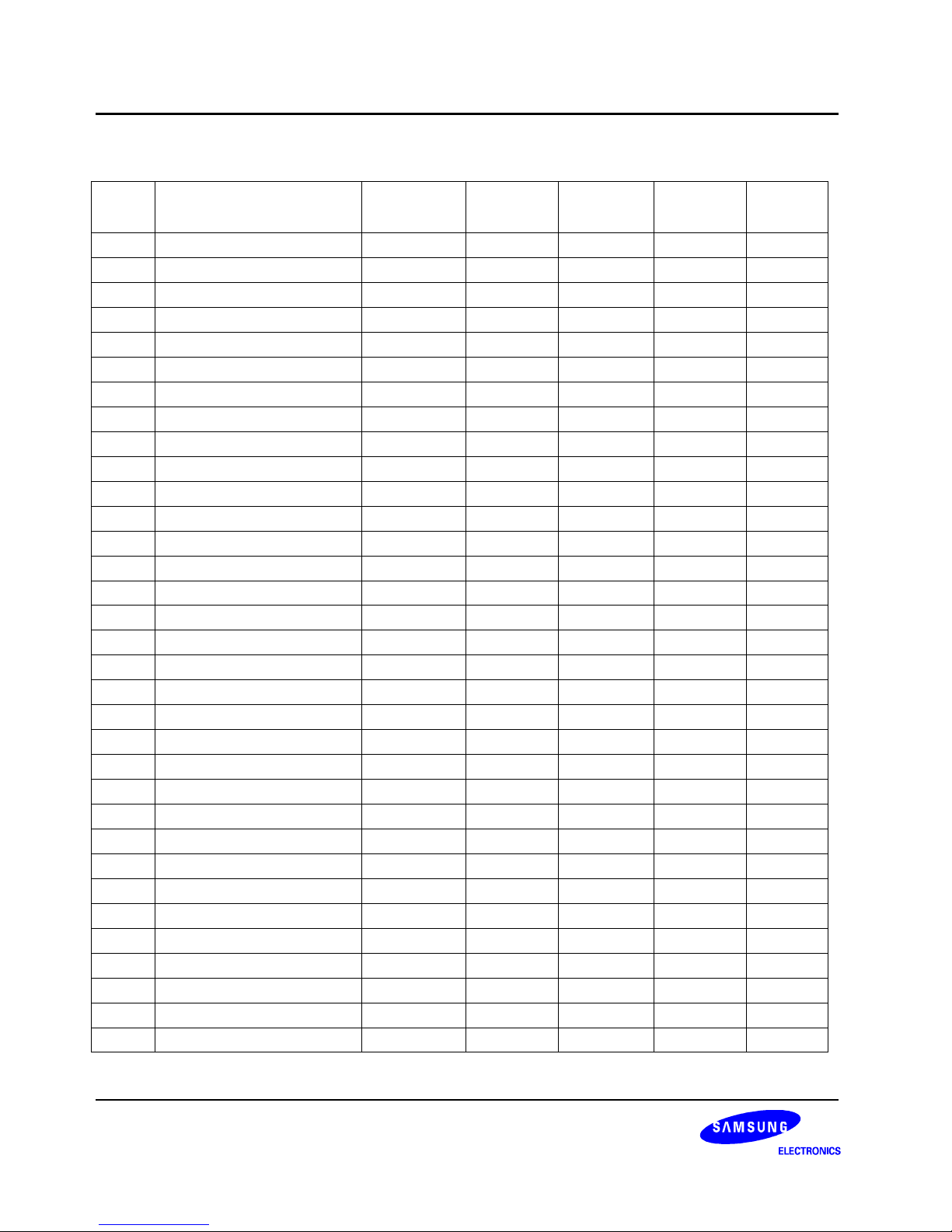

Table 1-1. 332-Pin FBGA Pin Assignments – Pin Number Order (Sheet 3 of 4)

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

V5 VLINE/GPC2 AA15 SPIMISO0/GPE11 AC25 AIN3

V6 VD4/GPC12

AA16 SPICLK0/GPE13 AC26 VCC_NF

V21

EINT15/SPICLK1/GPG7 AA17 DN1/PDN0 AD1 VSS_SDRAM

V22 AIN6

AA18 EINT13/SPIMISO1/GPG5 AD2 VDDIARM

V25 MPLLCAP

AA19

EINT18/GPG10/NCTS1

AD25 AIN2

V26 XTIRTC

AA20 VDDI AD26 VSS_SDRAM

W1 VSSOP3

AA21 VSSOP AE1 VD13/GPD5

W2 VSSCOM

AA22 OM2 AE2 VSS_SDRAM

W5 VD10/GPD2

AA25 AIN5 AE3

VD18/GPD10/SPICLK1

W6 VD6/GPC14

AA26 VSS_NF AE4

VD17/GPD9/SPIMOSI1

W21

EINT20/nSPICS0/GPG12 AB1 VD12/GPD4 AE5 I2SLRCK/GPE0

W22 XTORTC

AB2 VSSCOM AE6 VD15/GPD7/NSS0

W25 UPLLCAP

AB5 VD9/GPD1/SPCLK1 AE7 VD22/NSS1/GPD14

W26 VCC_NF

AB6 VD14/GPD6/NSS1 AE8 VD19/GPD11

Y1 VD5/GPC13

AB7

VD16/GPD8/SPIMOSI1

AE9 VD23/NSS0/GPD15

Y2 VD7/GPC15

AB8 VDDIARM AE10 SDDAT0/GPE7

Y5 VD3/GPC11

AB9 VDDIARM AE11

I2SSDO/GPE4

Y6 VCLK/GPC1 AB10 SDCLK/GPE5 AE12 SDDAT2/GPE9

Y21 NCON0

AB11 SDDAT3/GPE10 AE13 VDDIARM

Y22 VDDA_ADC

AB12 IICSCL/GPE14 AE14 CLKOUT1/GPH10

Y25 VDDA_MPLL

AB13 SPIMOSI0/GPE12 AE15 EINT9/GPG1

Y26 VDD_RTC

AB14

EINT12/LCD_PWREN/GPG4

AE16

EINT14/SPIMOSI1/GPG6

AA1 VD11/GPD3

AB15 EINT10/NSS0/GPG2 AE17 DP1/PDP0

AA2

VD8/GPD0/nSPICS1 AB16 VDDOP AE18 NRSTOUT/GPA21

AA5 VDDIARM_1

AB17 DP0 AE19 OM3

AA6 VD0/GPC8

AB18 DN0 AE20 AIN0

AA7 VSSOP3

AB19 EINT22/YMON/GPG14 AE21 VREF

AA8 LCDVF2/GPC7 AB20 EINT16/GPG8 AE22 AIN1

AA9 VD1/GPC9

AB21 EINT17/GPG9/NRTS1 AE23 OM0

AA10 I2SSCLK/GPE1 AB22 OM1 AE24 EINT21/NXPON/GPG13

AA11

I2SSDI/GPE3

AB25 AIN7 AE25 VDD_SDRAM

AA12 SDCMD/GPE6

AB26 VSSA_MPLL AE26 AIN4

AA13

CLKOUT0/nSPICS0/GPH9 AC1 VDDOP3 AF2 VDD_SDRAM

AA14 EINT8/GPG0

AC2 VDD_SDRAM AF3 VDDQ_SDRAM

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-10

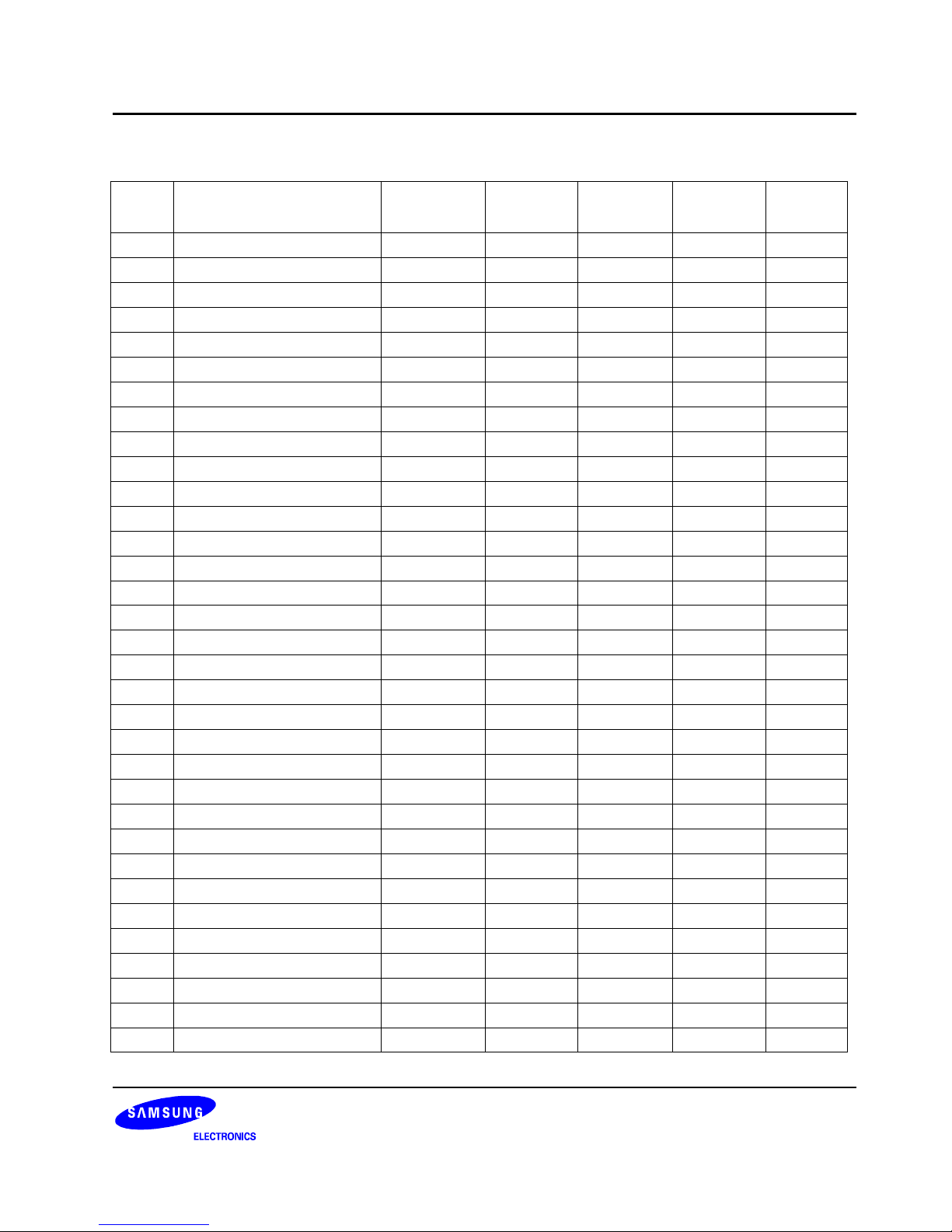

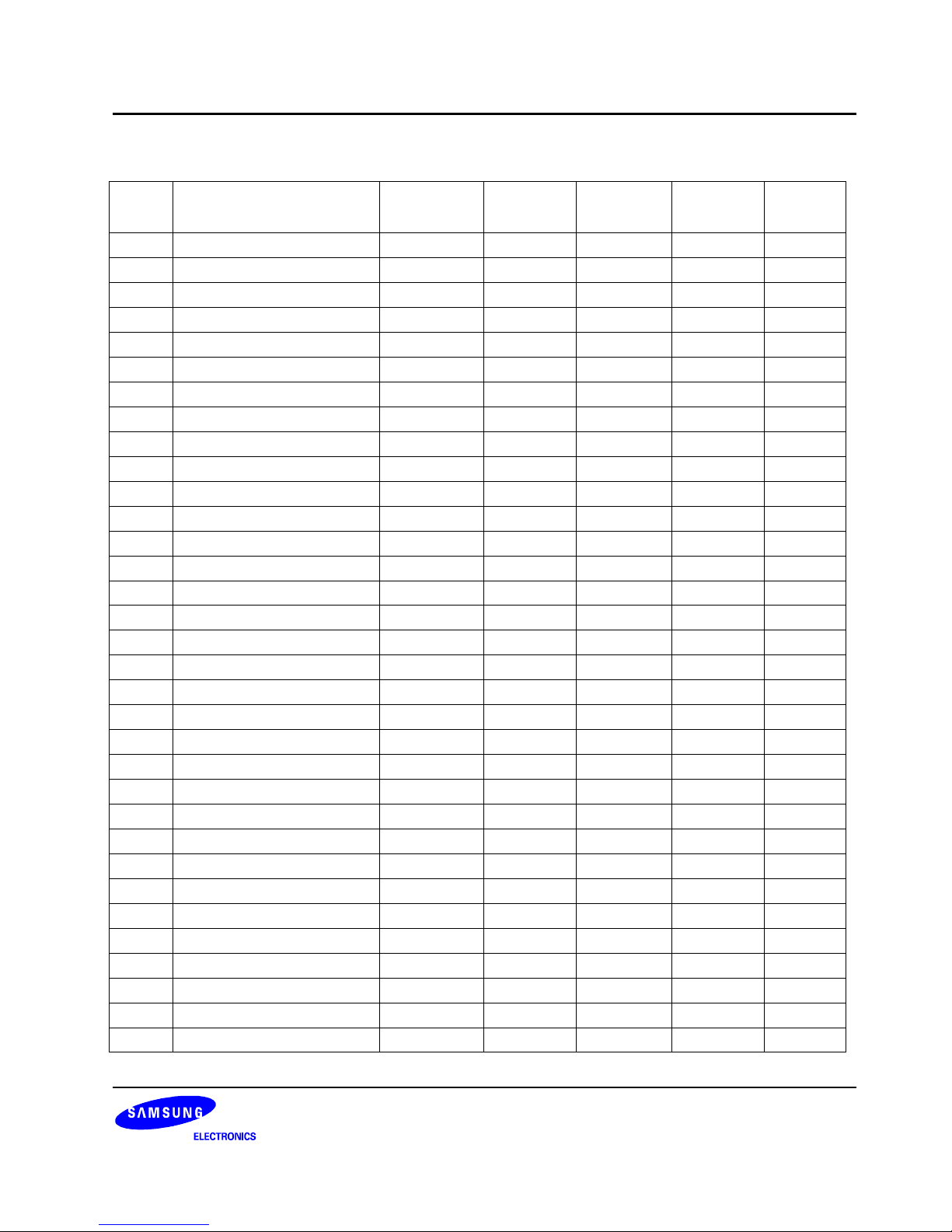

Table 1-1. 332-Pin FBGA Pin Assignments – Pin Number Order (Sheet 4 of 4)

Pin

Number

Pin Name

Pin

Number

Pin Name

AF4 VD20/GPD12

A1 NC

AF5 VD21/GPD13

A26 NC

AF6 VSSQ_SDRAM AF1 NC

AF7 VDDQ_SDRAM AF26 NC

AF8 CDCLK/GPE2

AF9 VSSQ_SDRAM

AF10 VDDQ_SDRAM

AF11 VSS_SDRAM

AF12 VSSQ_SDRAM

AF13 VDD_SDRAM

AF14

EINT11/NSS1/GPG3

AF15 VDDQ_SDRAM

AF16

EINT19/TCLK1/GPG11

AF17 VSSQ_SDRAM

AF18

EINT23/NYPON/GPG15

AF19 VDDQ_SDRAM

AF20 VSSA_ADC

AF21 VSSQ_SDRAM

AF22 VSSQ_SDRAM

AF23 VDDQ_SDRAM

AF24 VDD_SDRAM

AF25 VSS_SDRAM

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-11

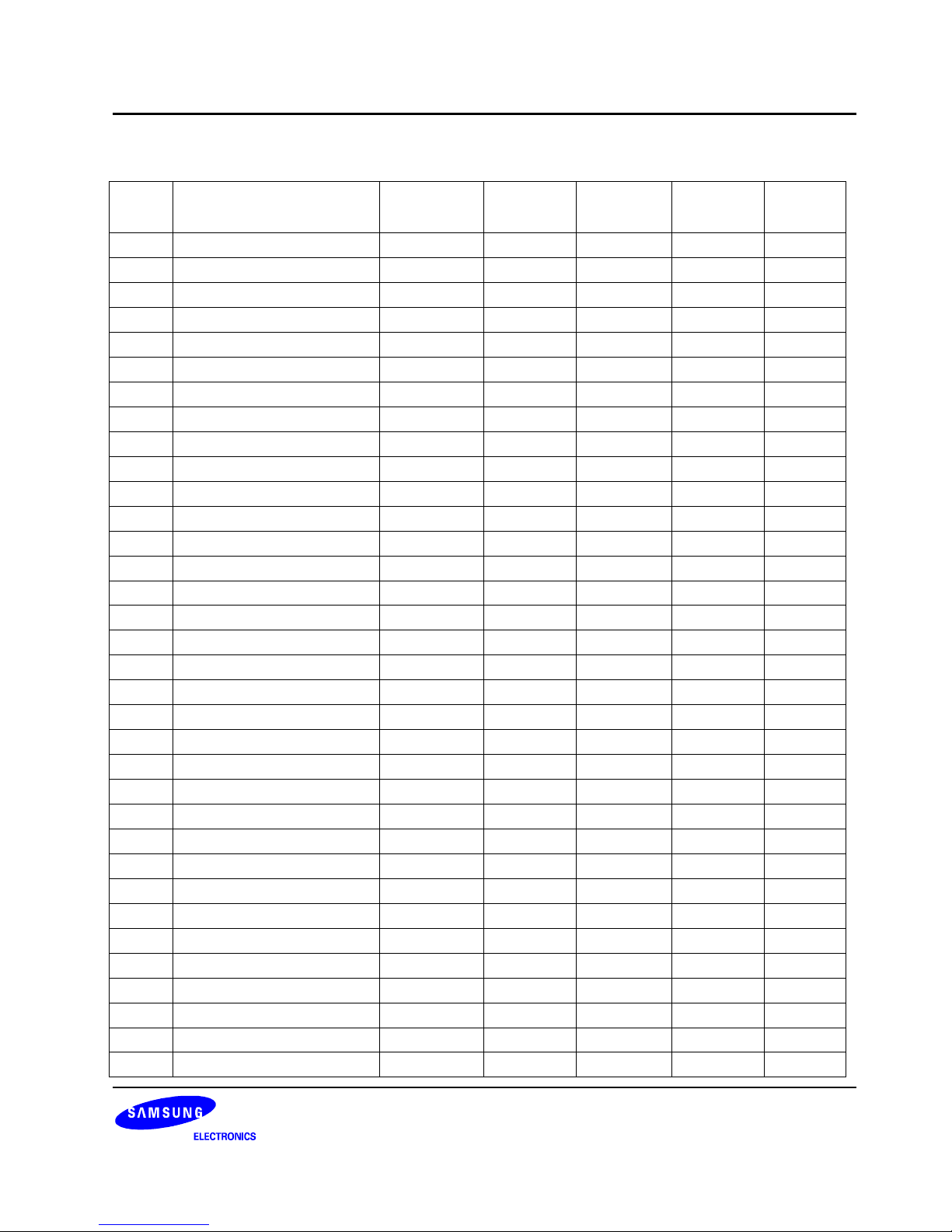

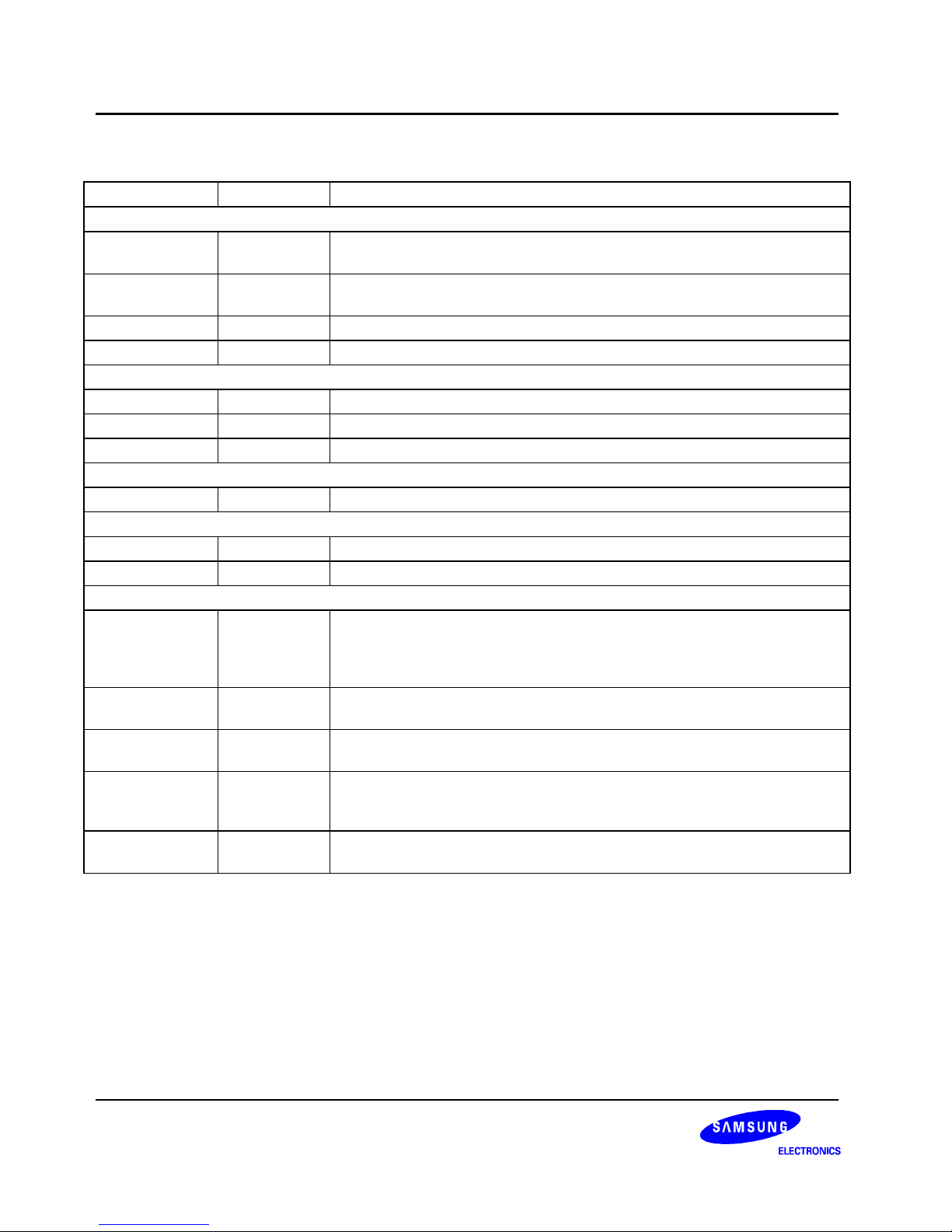

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 1 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

E11

ADDR0/GPA0 ADDR0 Hi-z/– O(L)/– O(L)

t12s

B11

ADDR1 ADDR1 Hi-z O(L) O(L)

t12s

A8

ADDR2 ADDR2 Hi-z O(L) O(L)

t12s

D1

ADDR3 ADDR3 Hi-z O(L) O(L)

t12s

B9

ADDR4 ADDR4 Hi-z O(L) O(L)

t12s

C1

ADDR5 ADDR5 Hi-z O(L) O(L)

t12s

B1

ADDR6 ADDR6 Hi-z O(L) O(L)

t12s

A9

ADDR7 ADDR7 Hi-z O(L) O(L)

t12s

B2

ADDR8 ADDR8 Hi-z O(L) O(L)

t12s

A10

ADDR9 ADDR9 Hi-z O(L) O(L)

t12s

A2

ADDR10 ADDR10 Hi-z O(L) O(L)

t12s

A12

ADDR11 ADDR11 Hi-z O(L) O(L)

t12s

B12

ADDR12 ADDR12 Hi-z O(L) O(L)

t12s

A3

ADDR13 ADDR13 Hi-z O(L) O(L)

t12s

A13

ADDR14 ADDR14 Hi-z O(L) O(L)

t12s

B13

ADDR15 ADDR15 Hi-z O(L) O(L)

t12s

E15

ADDR16/GPA1 ADDR16 Hi-z/– O(L)/– O(L)

t12s

F14

ADDR17/GPA2 ADDR17 Hi-z/– O(L)/– O(L)

t12s

B15

ADDR18/GPA3 ADDR18 Hi-z/– O(L)/– O(L)

t12s

F13

ADDR19/GPA4 ADDR19 Hi-z/– O(L)/– O(L)

t12s

F12

ADDR20/GPA5 ADDR20 Hi-z/– O(L)/– O(L)

t12s

B16

ADDR21/GPA6 ADDR21 Hi-z/– O(L)/– O(L)

t12s

F15

ADDR22/GPA7 ADDR22 Hi-z/– O(L)/– O(L)

t12s

B14

ADDR23/GPA8 ADDR23 Hi-z/– O(L)/– O(L)

t12s

A14

ADDR24/GPA9 ADDR24 Hi-z/– O(L)/– O(L)

t12s

E18

ADDR25/GPA10 ADDR25 Hi-z/– O(L)/– O(L)

t12s

B17

ADDR26/GPA11 ADDR26 Hi-z/– O(L)/– O(L)

t12s

AE20

AIN0 AIN0 – – AI r10

AE22

AIN1 AIN1 – – AI r10

AD25

AIN2 AIN2 – – AI r10

AC25

AIN3 AIN3 – – AI r10

AE26

YM/AIN4 AIN4 –/– –/– AI r10

AA25

YP/AIN5 YP –/– –/– AI r10

V22

XM/AIN6 AIN6 –/– –/– AI r10

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-12

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 2 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

AB25 XP/AIN7 XP –/– –/– AI r10

F16

CAMDATA0/GPJ0 GPJ0 –/– Hi-z/– I t8

K2

CAMDATA1/GPJ1 GPJ1 –/– Hi-z/– I t8

K6

CAMDATA2/GPJ2 GPJ2 –/– Hi-z/– I t8

J6

CAMDATA3/GPJ3 GPJ3 –/– Hi-z/– I t8

M2

CAMDATA4/GPJ4 GPJ4 –/– Hi-z/– I t8

G6

CAMDATA5/GPJ5 GPJ5 –/– Hi-z/– I t8

L6

CAMDATA6/GPJ6 GPJ6 –/– Hi-z/– I t8

L2

CAMDATA7/GPJ7 GPJ7 –/– Hi-z/– I t8

J5 CAMPCLK/GPJ8 GPJ8 –/– Hi-z/– I t8

F9 CAMVSYNC/GPJ9 GPJ9 –/– Hi-z/– I t8

H5 CAMHREF/GPJ10 GPJ10 –/– Hi-z/– I t8

F11 CAMCLKOUT/GPJ11 GPJ11 –/– O(L)/– I t8

F18 CAMRESET/GPJ12 GPJ12 –/– O(L)/– I t8

A17

DATA0 DATA0 Hi-z Hi-z,O(L) I b12s

B19

DATA1 DATA1 Hi-z Hi-z,O(L) I b12s

A15

DATA2 DATA2 Hi-z Hi-z,O(L) I b12s

B18

DATA3 DATA3 Hi-z Hi-z,O(L) I b12s

A16

DATA4 DATA4 Hi-z Hi-z,O(L) I b12s

A18

DATA5 DATA5 Hi-z Hi-z,O(L) I b12s

A19

DATA6 DATA6 Hi-z Hi-z,O(L) I b12s

A21

DATA7 DATA7 Hi-z Hi-z,O(L) I b12s

B20

DATA8 DATA8 Hi-z Hi-z,O(L) I b12s

A22

DATA9 DATA9 Hi-z Hi-z,O(L) I b12s

A23

DATA10 DATA10 Hi-z Hi-z,O(L) I b12s

B23

DATA11 DATA11 Hi-z Hi-z,O(L) I b12s

A25

DATA12 DATA12 Hi-z Hi-z,O(L) I b12s

B26

DATA13 DATA13 Hi-z Hi-z,O(L) I b12s

B25

DATA14 DATA14 Hi-z Hi-z,O(L) I b12s

C26

DATA15 DATA15 Hi-z Hi-z,O(L) I b12s

A24

DATA16 DATA16 Hi-z Hi-z,O(L) I b12s

D26

DATA17 DATA17 Hi-z Hi-z,O(L) I b12s

E26

DATA18 DATA18 Hi-z Hi-z,O(L) I b12s

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-13

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 3 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

C25

DATA19 DATA19 Hi-z Hi-z,O(L) I b12s

F26

DATA20 DATA20 Hi-z Hi-z,O(L) I b12s

E25

DATA21 DATA21 Hi-z Hi-z,O(L) I b12s

G26

DATA22 DATA22 Hi-z Hi-z,O(L) I b12s

J26

DATA23 DATA23 Hi-z Hi-z,O(L) I b12s

J25

DATA24 DATA24 Hi-z Hi-z,O(L) I b12s

L26

DATA25 DATA25 Hi-z Hi-z,O(L) I b12s

H26

DATA26 DATA26 Hi-z Hi-z,O(L) I b12s

K26

DATA27 DATA27 Hi-z Hi-z,O(L) I b12s

N26

DATA28 DATA28 Hi-z Hi-z,O(L) I b12s

M26

DATA29 DATA29 Hi-z Hi-z,O(L) I b12s

P26

DATA30 DATA30 Hi-z Hi-z,O(L) I b12s

K25

DATA31 DATA31 Hi-z Hi-z,O(L) I b12s

AB18 DN0 DN0 – – AI us

AB17 DP0 DP0 – – AI us

AA17 DN1/PDN0 DN1 –/– – AI us

AE17 DP1/PDP0 DP1 –/– – AI us

T22

EINT0/GPF0 GPF0 –/– Hi-z/– I t8

U26

EINT1/GPF1 GPF1 –/– Hi-z/– I t8

N21

EINT2/GPF2 GPF2 –/– Hi-z/– I t8

T26

EINT3/GPF3 GPF3 –/– Hi-z/– I t8

R22

EINT4/GPF4 GPF4 –/– Hi-z/– I t8

U25

EINT5/GPF5 GPF5 –/– Hi-z/– I t8

K21

EINT6/GPF6 GPF6 –/– Hi-z/– I t8

T25

EINT7/GPF7 GPF7 –/– Hi-z/– I t8

AA14

EINT8/GPG0 GPG0 –/– Hi-z/– I t8

AE15

EINT9/GPG1 GPG1 –/– Hi-z/– I t8

AB15

EINT10/nSS0/GPG2 GPG2 –/–/– Hi-z/Hi-z/– I t8

AF14

EINT11/nSS1/GPG3 GPG3 –/–/– Hi-z/Hi-z/– I t8

AB14

EINT12/LCD_PWREN/GPG4 GPG4 –/–/– Hi-z/O(L)/– I t8

AA18

EINT13/SPIMISO1/GPG5 GPG5 –/–/– Hi-z/Hi-z/– I t8

AE16

EINT14/SPIMOSI1/GPG6 GPG6 –/–/– Hi-z/Hi-z/– I t8

V21

EINT15/SPICLK1/GPG7 GPG7 –/–/– Hi-z/Hi-z/– I t8

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-14

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 4 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

AB20

EINT16/GPG8 GPG8 –/– Hi-z/– I t8

AB21

EINT17/nRTS1/GPG9 GPG9 –/–/– Hi-z/O(H)/– I t8

AA19

EINT18/nCTS1/GPG10 GPG10 –/–/– Hi-z/Hi-z/– I t8

AF16

EINT19/TCLK1/GPG11 GPG11 –/–/– Hi-z/Hi-z/– I t12

W21

EINT20/nSPICS0/GPG12 GPG12 –/– Hi-z/– I t12

AE24

EINT21/GPG13 GPG13 –/– Hi-z/– I t12

AB19

EINT22/GPG14 GPG14 –/– Hi-z/– I t12

AF18

EINT23/GPG15 GPG15 –/– Hi-z/– I t12

G22

EXTCLK EXTCLK – – AI is

W25

UPLLCAP UPLLCAP – – AI r50

V25

MPLLCAP MPLLCAP – – AI r50

M25

nBATT_FLT nBATT_FLT – – I is

F1

nBE0 nBE0 Hi-z Hi-z,O(H) O(H) t12s

A5

nBE1 nBE1 Hi-z Hi-z,O(H) O(H) t12s

E1

nBE2 nBE2 Hi-z Hi-z,O(H) O(H) t12s

B6

nBE3 nBE3 Hi-z Hi-z,O(H) O(H) t12s

Y21 NCON NCON – – I is

L1 FRnB FRnB – Hi-z,O(L) I d2s

J1

nFWE/GPA19 nFWE O(H)/– Hi-z,O(H)/– O(H) t12s

K1

nFRE/GPA20 nFRE O(H)/– Hi-z,O(H)/– O(H) t12s

G5

nFCE/GPA22 nFCE O(H)/– Hi-z,O(H)/– O(H) t12s

H2

CLE/GPA17 CLE O(L)/– Hi-z,O(L)/– O(L) t12s

H1

ALE/GPA18 ALE O(L)/– Hi-z,O(L)/– O(L) t12s

AE18

nRSTOUT/GPA21 nRSTOUT –/– O(L)/– O(L) b8

B10

nOE nOE Hi-z Hi-z,O(H) O(H) t12s

H22

nRESET nRESET – – I is

F6

nGCS0 nGCS0 Hi-z Hi-z,O(H) O(H)

t12s

E7

nGCS1/GPA12 nGCS1 Hi-z/– Hi-z,O(H)/– O(H)

t12s

B5

nGCS2/GPA13 nGCS2 Hi-z/– Hi-z,O(H)/– O(H)

t12s

E6

nGCS3/GPA14 nGCS3 Hi-z/– Hi-z,O(H)/– O(H)

t12s

D2

nGCS4/GPA15 nGCS4 Hi-z/– Hi-z,O(H)/– O(H)

t12s

A4

nGCS5/GPA16 nGCS5 Hi-z/– Hi-z,O(H)/– O(H)

t12s

B4

nGCS6 nGCS6 Hi-z Hi-z,O(H) O(H)

t12s

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-15

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 5 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

F2 nGCS7 nGCS7 Hi-z Hi-z,O(H) O(H)

t12s

A7

nSCAS nSCAS Hi-z Hi-z,O(H) O(H)

t12s

A6

nSRAS nSRAS Hi-z Hi-z,O(H) O(H)

t12s

N25

nTRST nTRST I – I is

C2

nWAIT nWAIT – Hi-z,O(L) I d2s

N1

nWE nWE Hi-z Hi-z,O(H) O(H) t12s

L5

TOUT0/GPB0 GPB0 –/– O(L)/– I t8

F19

TOUT1/GPB1 GPB1 –/– O(L)/– I t8

J22

TOUT2/GPB2 GPB2 –/– O(L)/– I t8

N2

TOUT3/GPB3 GPB3 –/– O(L)/– I t8

P2

TCLK0/GPB4 GPB4 –/– –/– I t8

M6

nXBACK/GPB5 GPB5 –/– O(H)/– I t8

P5

nXBREQ/GPB6 GPB6 –/– –/– I t8

N6

nXDACK1/GPB7 GPB7 –/– O(H)/– I t8

P6

nXDREQ1/GPB8 GPB8 –/– –/– I t8

R2

nXDACK0/GPB9 GPB9 –/– O(H)/– I t8

T6

nXDREQ0/GPB10 GPB10 –/– –/– I t8

AE23

OM0 OM0 – – I is

AB22

OM1 OM1 – – I is

AA22

OM2 OM2 – – I is

AE19

OM3 OM3 – – I is

F20 PWREN PWREN O(H) O(L) O(H) b8

J21

nCTS0/GPH0 GPH0 –/– –/– I t8

R26

nRTS0/GPH1 GPH1 –/– O(H)/– I t8

L22

TXD0/GPH2 GPH2 –/– O(H)/– I t8

R25

RXD0/GPH3 GPH3 –/– –/– I t8

F17

TXD1/GPH4 GPH4 –/– O(H)/– I t8

P25

RXD1/GPH5 GPH5 –/– –/– I t8

L21

TXD2/nRTS1/GPH6 GPH6 –/–/– O(H)/O(H)/– I t8

M21

RXD2/nCTS1/GPH7 GPH7 –/–/– Hi-z/Hi-z/– I t8

N22

UEXTCLK/GPH8 GPH8 –/– Hi-z/– I t8

AA13

CLKOUT0/nSPICS0/GPH9 GPH9 –/– O(L)/– I t12

AE14

CLKOUT1/GPH10 GPH10 –/– O(L)/– I t12

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-16

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 6 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

B3

SCKE SCKE Hi-z O(L) O(H) t12s

G1

SCLK0 SCLK0 Hi-z O(L) O(SCLK) t12s

E10

SCLK1 SCLK1 Hi-z O(L) O(SCLK) t12s

AE5

I2SLRCK GPE0 –/– Hi-z/– I t8

AA10

I2SSCLK GPE1 –/– Hi-z/– I t8

AF8

CDCLK GPE2 –/– Hi-z/– I t8

AA11

I2SSDI GPE3 –/–/– Hi-z/Hi-z/– I t8

AE11

I2SSDO GPE4 –/–/– O(L)/Hi-z/– I t8

AB10

SDCLK/GPE5 GPE5 –/– O(L)/– I t8

AA12

SDCMD/GPE6 GPE6 –/– Hi-z/– I t8

AE10

SDDAT0/GPE7 GPE7 –/– Hi-z/– I t8

R21

SDDAT1/GPE8 GPE8 –/– Hi-z/– I t8

AE12

SDDAT2/GPE9 GPE9 –/– Hi-z/– I t8

AB11

SDDAT3/GPE10 GPE10 –/– Hi-z/– I t8

AA15

SPIMISO0/GPE11 GPE11 –/– Hi-z/– I t8

AB13

SPIMOSI0/GPE12 GPE12 –/– Hi-z/– I t8

AA16

SPICLK0/GPE13 GPE13 –/– Hi-z/– I t8

AB12

IICSCL/GPE14 GPE14 –/– Hi-z/– I d8

U21

IICSDA/GPE15 GPE15 –/– Hi-z/– I d8

E20

TCK TCK I – I is

F22

TDI TDI I – I is

M22

TDO TDO O O O ot

E21

TMS TMS I – I is

R5

LEND/GPC0 GPC0 –/– O(L)/– I t8

Y6

VCLK/GPC1 GPC1 –/– O(L)/– I t8

V5

VLINE/GPC2 GPC2 –/– O(L)/– I t8

U6

VFRAME/GPC3 GPC3 –/– O(L)/– I t8

T2

VM/GPC4 GPC4 –/– O(L)/– I t8

V1

LCD_LPCOE/GPC5 GPC5 –/– O(L)/– I t8

R6

LCD_LPCREV/GPC6 GPC6 –/– O(L)/– I t8

AA8

LCD_LPCREVB/GPC7 GPC7 –/– O(L)/– I t8

AA6

VD0/GPC8 GPC8 –/– O(L)/– I t8

AA9

VD1/GPC9 GPC9 –/– O(L)/– I t8

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-17

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 7 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

V2

VD2/GPC10 GPC10 –/– O(L)/– I t8

Y5

VD3/GPC11 GPC11 –/– O(L)/– I t8

V6

VD4/GPC12 GPC12 –/– O(L)/– I t8

Y1

VD5/GPC13 GPC13 –/– O(L)/– I t8

W6

VD6/GPC14 GPC14 –/– O(L)/– I t8

Y2

VD7/GPC15 GPC15 –/– O(L)/– I t8

AA2

VD8/GPD0/nSPICS1 GPD0 –/– O(L)/– I t8

AB5

VD9/GPD1/SPICLK1 GPD1 –/– O(L)/– I t8

W5

VD10/GPD2 GPD2 –/– O(L)/– I t8

AA1

VD11/GPD3 GPD3 –/– O(L)/– I t8

AB1

VD12/GPD4 GPD4 –/– O(L)/– I t8

AE1

VD13/ GPD5 GPD5 –/–/– O(L)/O/– I t8

AB6

VD14/GPD6 GPD6 –/–/– O(L)/O/– I t8

AE6

VD15/GPD7 GPD7 –/–/– O(L)/O/– I t8

AB7

VD16/SPIMISO1/GPD8 GPD8 –/–/– O(L)/Hi-z/– I t8

AE4

VD17/SPIMOSI1/GPD9 GPD9 –/–/– O(L)/Hi-z/– I t8

AE3

VD18/SPICLK1/GPD10 GPD10 –/–/– O(L)/Hi-z/– I t8

AE8

VD19//GPD11 GPD11 –/–/– O(L)/Hi-z/– I t8

AF4

VD20/ GPD12 GPD12 –/–/– O(L)/Hi-z/– I t8

AF5

VD21/ GPD13 GPD13 –/–/– O(L)/Hi-z/– I t8

AE7

VD22/nSS1/GPD14 GPD14 –/–/– O(L)/Hi-z/– I t8

AE9

VD23/nSS0/GPD15 GPD15 –/–/– O(L)/Hi-z/– I t8

AE21

Vref Vref – – AI ia

L25

XTIpll XTIpll – – AI m26

V26

Xtirtc Xtirtc – – AI nc

E22

XTOpll XTOpll – – AO m26

W22

Xtortc Xtortc – – AO nc

Y26

VDD_RTC VDD_RTC P P P drtc

Y22

VDDA_ADC VDDA_ADC P P P d33th

Y25

VDDA_MPLL VDDA_MPLL P P P d12t

T21

VDDA_UPLL VDDA_UPLL P P P d12t

K5

VDDalive VDDalive P P P d12i

F21

VDDalive VDDalive P P P d12i

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-18

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 8 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

AA20

VDDi VDDi P P P d12c

F5

VDDi VDDi P P P d12c

F25

VDDi VDDi P P P d12c

B21

VDDi VDDi P P P d12c

E16

VDDi VDDi P P P d12c

E13

VDDi VDDi P P P d12c

E9

VDDi VDDi P P P d12c

B7

VDDi VDDi P P P d12c

F7

VDDiarm VDDiarm P P P d12c

F8

VDDiarm VDDiarm P P P d12c

T5

VDDiarm VDDiarm P P P d12c

U5

VDDiarm VDDiarm P P P d12c

AD2

VDDiarm VDDiarm P P P d12c

AB8

VDDiarm VDDiarm P P P d12c

AB9

VDDiarm VDDiarm P P P d12c

AE13

VDDiarm VDDiarm P P P d12c

AA5

VDDiarm VDDiarm P P P d12c

G2

VDDMOP VDDMOP P P P d18o

H21

VDDMOP VDDMOP P P P

d18o

B24

VDDMOP VDDMOP P P P

d18o

A20

VDDMOP VDDMOP P P P

d18o

E17

VDDMOP VDDMOP P P P

d18o

E12

VDDMOP VDDMOP P P P

d18o

E8

VDDMOP VDDMOP P P P

d18o

AB16

VDDOP VDDOP P P P

d18o

P21

VDDOP1 VDDOP1 P P P

d18o

N5

VDDOP2 VDDOP2 P P P d33o

AC1

VDDOP3 VDDOP3 P P P d33o

AC2

VDD_SDRAM VDD_SDRAM P P P

AE25

VDD_SDRAM VDD_SDRAM P P P

AF2

VDD_SDRAM VDD_SDRAM P P P

AF13

VDD_SDRAM VDD_SDRAM P P P

AF24

VDD_SDRAM VDD_SDRAM P P P

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-19

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 9 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

AF3 VDDQ_SDRAM

VDDQ_SDRAM

P P P

AF7 VDDQ_SDRAM

VDDQ_SDRAM

P P P

AF10 VDDQ_SDRAM

VDDQ_SDRAM

P P P

AF15 VDDQ_SDRAM

VDDQ_SDRAM

P P P

AF19 VDDQ_SDRAM

VDDQ_SDRAM

P P P

AF23 VDDQ_SDRAM

VDDQ_SDRAM

P P P

AC26

VCC_NF VCC_NF

P P P

P1

VCC_NF VCC_NF

P P P

W26

VCC_NF VCC_NF

P P P

AF20

VSSA_ADC VSSA_ADC P P P Sth

AB26

VSSA_MPLL VSSA_MPLL P P P st

P22

VSSA_UPLL VSSA_UPLL P P P st

J2 VSSCOM VSSCOM

P P P si

M5 VSSCOM VSSCOM

P P P si

R1 VSSCOM VSSCOM

P P P si

W2 VSSCOM VSSCOM

P P P si

AB2 VSSCOM VSSCOM

P P P si

M14 VSSCOM VSSCOM

P P P si

K22 VSSCOM VSSCOM

P P P si

H25 VSSCOM VSSCOM

P P P si

M13 VSSCOM VSSCOM

P P P si

N12 VSSCOM VSSCOM

P P P si

N13 VSSCOM VSSCOM

P P P si

N14 VSSCOM VSSCOM

P P P si

N15 VSSCOM VSSCOM

P P P si

P12 VSSCOM VSSCOM

P P P si

P13 VSSCOM VSSCOM

P P P si

P14 VSSCOM VSSCOM

P P P si

P15 VSSCOM VSSCOM

P P P si

R13 VSSCOM VSSCOM

P P P si

R14 VSSCOM VSSCOM

P P P si

E14 VSSCOM VSSCOM

P P P si

B8 VSSCOM VSSCOM

P P P si

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-20

Table 1-2. SC32442B 332-Pin FBGA Pin Assignments (Sheet 10 of 10)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

E2

VSSMOP VSSMOP P P P s18

E5

VSSMOP VSSMOP P P P

s18

G25

VSSMOP VSSMOP P P P

s18

G25

VSSMOP VSSMOP P P P

s18

D25

VSSMOP VSSMOP P P P

s18

G21

VSSMOP VSSMOP P P P

s18

E19

VSSMOP VSSMOP P P P

s18

A11

VSSMOP VSSMOP P P P

s18

F10

VSSMOP VSSMOP P P P

s18

U22

VSSOP VSSOP P P P so

AA21

VSSOP VSSOP P P P so

B22

VSSOP1 VSSOP1 P P P so

H6

VSSOP2 VSSOP2 P P P so

W1

VSSOP3 VSSOP3 P P P so

AA7

VSSOP3 VSSOP3 P P P so

AD1

VSS_SDRAM VSS_SDRAM

P P P so

AD26

VSS_SDRAM VSS_SDRAM

P P P so

AE2

VSS_SDRAM VSS_SDRAM

P P P so

AF11

VSS_SDRAM VSS_SDRAM

P P P so

AF25

VSS_SDRAM VSS_SDRAM

P P P so

AF6

VSSQ_SDRAM

VSSQ_SDRAM

P P P so

AF9

VSSQ_SDRAM

VSSQ_SDRAM

P P P so

AF12

VSSQ_SDRAM

VSSQ_SDRAM

P P P so

AF17

VSSQ_SDRAM

VSSQ_SDRAM

P P P so

AF21

VSSQ_SDRAM

VSSQ_SDRAM

P P P so

AF22

VSSQ_SDRAM

VSSQ_SDRAM

P P P so

T1 VSS_NF VSS_NF P P P so

AA26 VSS_NF VSS_NF P P P so

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-21

NOTE:

1. The @BUS REQ. shows the pin state at the external bus, which is used by the other bus master.

2. ' – ‘ mark indicates the unchanged pin state at Bus Request mode.

3. Hi-z or Pre means Hi-z or early state and it is determined by the setting of MISCCR register.

4. AI/AO means analog input/analog output.

5. P, I, and O mean power, input and output respectively.

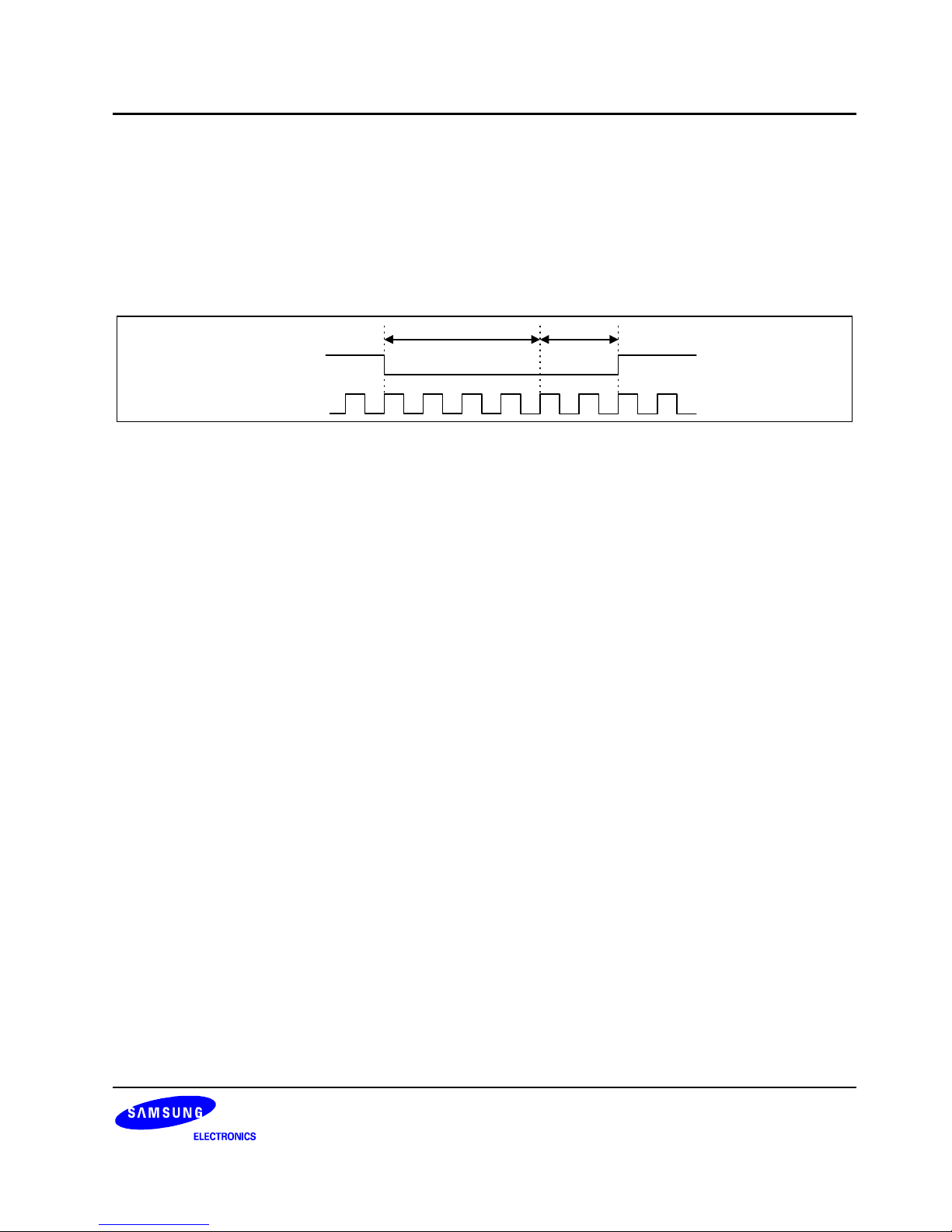

6. The I/O state @nRESET shows the pin status in the @nRESET duration below.

nRESET

FCLK

@nRESET4 OSCin

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-22

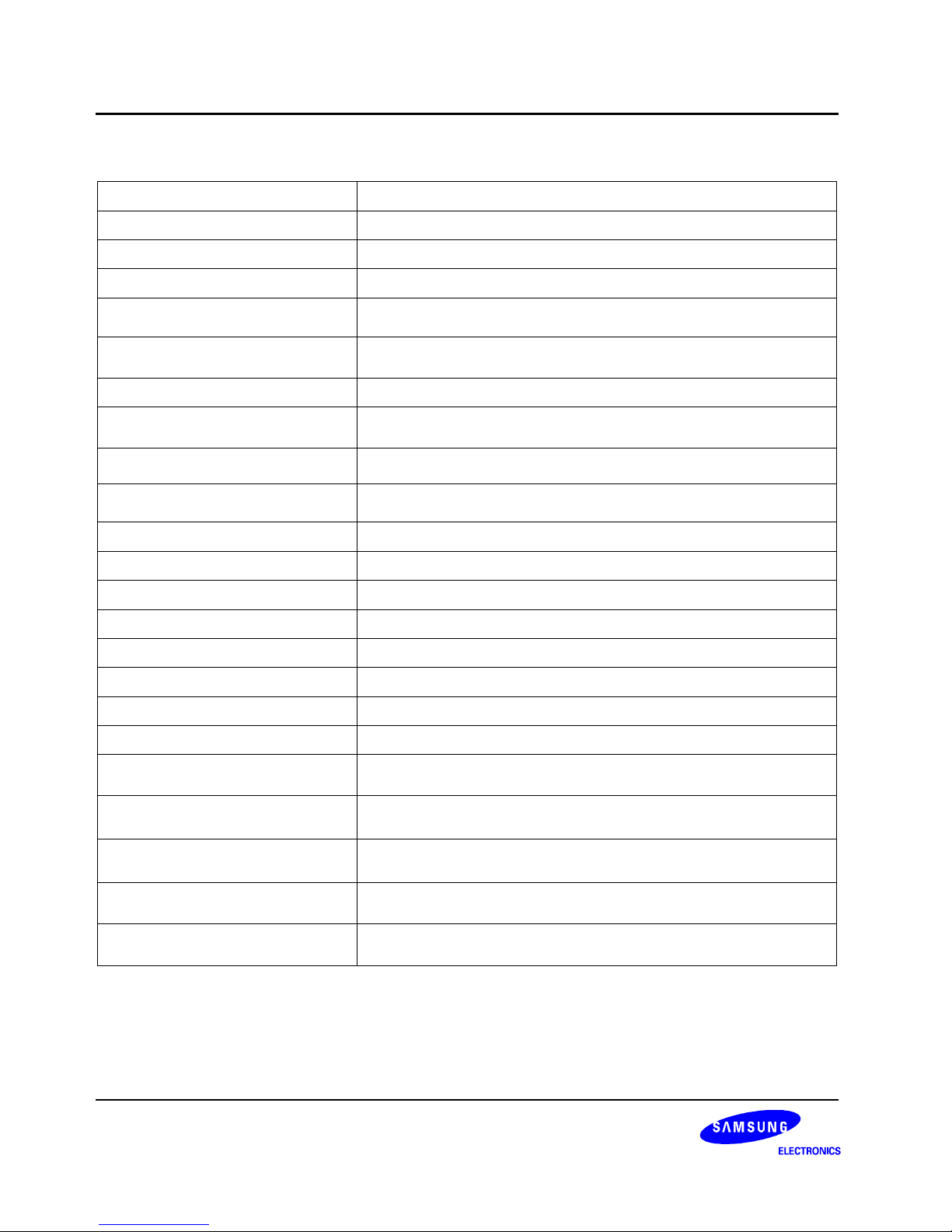

THE TABLE BELOW SHOWS I/O TYPES AND DESCRIPTIONS.

Input (I)/Output (O) Type Descriptions

d12i(vdd12ih_45p) 1.2V Vdd for alive power

d12c(vdd12ih_core_45p), si(vssiph_45p)

1.2V Vdd/Vss for internal logic

d18o(vdd18op_ddr), s18(vsso_ddr) 1.8V Vdd/Vss for external logic

33o(vdd33oph), so(vssoph) 3.3V Vdd/Vss for external logic

d33th(vdd33th_abb),sth(vssbbh_abb) 3.3V Vdd/Vss for analog circuitry

d12t(vdd12t_abb), st(vssbb_abb) 1.2V Vdd/Vss for analog circuitry

drtc(vdd30th_rtc) 3.0V Vdd for RTC power

t8(phbsd100ct8sm)

Bi-directional pad, LVCMOS schmitt-trigger,100Kohm pull-down resisto

r

with control, tri-state, Io=8mA

t12 (phbsd100ct12sm)

Bi-directional pad,LVCMOS schmitt-trigger,100Kohm pull-down resisto

r

with control, tri-state, Io=12mA

is(phis) Input pad, LVCMOS schmitt-trigger level

us(pbusb0) USB pad

ot(phot8) Output pad, tri-state, Io=8mA

b8(phob8) Output pad, Io=8mA

r10(phiar10_abb) Analog input pad with 10-ohm resistor

ia(phia_abb) Analog input pad

m26(phsoscm26) Oscillator cell with enable and feedback resistor

d8(phbsd8sm) Bi-directional pad, LVCMOS schmitt-trigger, Open Drain, Io=8mA

b12s(phnbsud100ct12cd_ddr)

Bi-directional pad, LVCMOS schmitt-trigger, 100Kohm pull-up

resistor with control, tri -state,output drive strenth control,

d2s(phbsd2)

Bi-directional pad, LVCMOS schmitt-trigger, open-drain, output

drive strenth ignore,

r50(poar50_pll_abb) Analog Output pad, 50Kohm resistor, Separated bulk-bias

t12s(phnot12cd_ddr)

output pad, LVCMOS , tri -state, output drive strenth control,

Io=6,8,10,12mA

nc(phnc) No connection pad

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-23

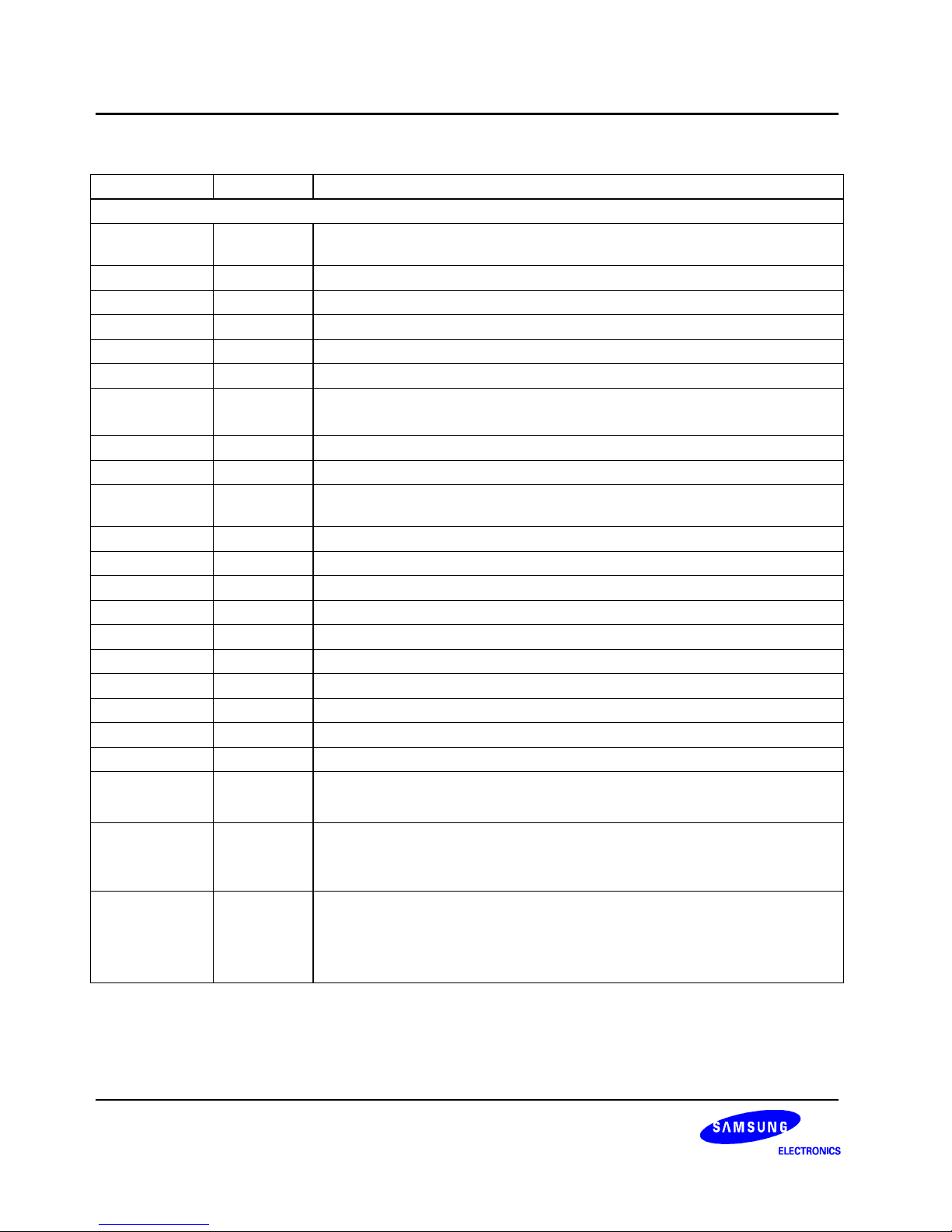

SIGNAL DESCRIPTIONS

Table 1-3. SC32442B Signal Descriptions (Sheet 1 of 6)

Signal Input/Output Descriptions

Bus Controller

OM[1:0] I OM[1:0] sets SC32442B in the TEST mode, which is used only at fabrication.

Also, it determines the bus width of nGCS0. The pull-up/down resistor

determines the logic level during RESET cycle.

00:Nand-boot 01:16-bit 10:32-bit 11:Test mode

ADDR[26:0] O ADDR[26:0] (Address Bus) outputs the memory address of the corresponding

bank .

DATA[31:0] IO DATA[31:0] (Data Bus) inputs data during memory read and outputs data during

memory write. The bus width is programmable among 8/16/32-bit.

nGCS[7:0] O nGCS[7:0] (General Chip Select) are activated when the address of a memory is

within the address region of each bank. The number of access cycles and the

bank size can be programmed.

nWE O nWE (Write Enable) indicates that the current bus cycle is a write cycle.

nOE O nOE (Output Enable) indicates that the current bus cycle is a read cycle.

nXBREQ I nXBREQ (Bus Hold Request) allows another bus master to request control of

the local bus. BACK active indicates that bus control has been granted.

nXBACK O nXBACK (Bus Hold Acknowledge) indicates that the SC32442B has

surrendered control of the local bus to another bus master.

nWAIT I nWAIT requests to prolong a current bus cycle. As long as nWAIT is L, the

current bus cycle cannot be completed.

SDRAM/SRAM

nSRAS O SDRAM Row Address Strobe

nSCAS O SDRAM Column Address Strobe

nSCS[1:0] O SDRAM Chip Select

DQM[3:0] O SDRAM Data Mask

SCLK[1:0] O SDRAM Clock

SCKE O SDRAM Clock Enable

nBE[3:0] O Upper Byte/Lower Byte Enable(In case of 16-bit SRAM)

nWBE[3:0] O Write Byte Enable

NAND Flash

CLE O Command Latch Enable

ALE O Address Latch Enable

nFCE O Nand Flash Chip Enable

nFRE O Nand Flash Read Enable

nFWE O Nand Flash Write Enable

NCON I Nand Flash Configuration

FRnB I Nand Flash Ready/Busy

* If NAND flash controller isn’t used, it has

to be pull-up. (VDDMOP)

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-24

Table 1-3. SC32442B Signal Descriptions (Sheet 2 of 6)

Signal Input/Output Descriptions

LCD Control Unit

VD[23:0] O STN/TFT/SEC TFT: LCD Data Bus

LCD_PWREN O STN/TFT/SEC TFT: LCD panel power enable control signal

VCLK O STN/TFT: LCD clock signal

VFRAME O STN: LCD Frame signal

VLINE O STN: LCD line signal

VM O STN: VM alternates the polarity of the row and column voltage

VSYNC O TFT: Vertical synchronous signal

HSYNC O TFT: Horizontal synchronous signal

VDEN O TFT: Data enable signal

LEND O TFT: Line End signal

STV O SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

CPV O SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

LCD_HCLK O SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

TP O SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

STH O SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

LCD_LPCOE O SEC TFT: Timing control signal for specific TFT LCD

LCD_LPCREV O SEC TFT: Timing control signal for specific TFT LCD

LCD_LPCREVB O SEC TFT: Timing control signal for specific TFT LCD

CAMERA Interface

CAMRESET O Software Reset to the Camera

CAMCLKOUT O Master Clock to the Camera

CAMPCLK I Pixel clock from Camera

CAMHREF I Horizontal sync signal from Camera

CAMVSYNC I Vertical sync signal from Camera

CAMDATA[7:0] I Pixel data for YCbCr

Interrupt Control Unit

EINT[23:0] I External Interrupt request

DMA

nXDREQ[1:0] I External DMA request

nXDACK[1:0] O External DMA acknowledge

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-25

Table 1-3. SC32442B Signal Descriptions (Sheet 3 of 6)

Signal Input/Output Descriptions

UART

RxD[2:0] I UART receives data input

TxD[2:0] O UART transmits data output

nCTS[1:0] I UART clear to send input signal

nRTS[1:0] O UART request to send output signal

UEXTCLK I External clock input for UART

ADC

AIN[7:0] AI ADC input[7:0]. If it isn’t used pin, it has to be Low (Ground).

Vref AI ADC Vref

IIC-Bus

IICSDA IO IIC-bus data

IICSCL IO IIC-bus clock

IIS-Bus

I2SLRCK IO IIS-bus channel select clock

I2SSDO O IIS-bus serial data output

I2SSDI I IIS-bus serial data input

I2SSCLK IO IIS-bus serial clock

CDCLK O CODEC system clock

Touch Screen

nXPON O Plus X-axis on-off control signal

XMON O Minus X-axis on-off control signal

nYPON O Plus Y-axis on-off control signal

YMON O Minus Y-axis on-off control signal

USB Host

DN[1:0] IO DATA(–) from USB host. (Need to 15K ohm pull-down)

DP[1:0] IO DATA(+) from USB host. (Need to 15K ohm pull-down)

USB Device

PDN0 IO DATA(–) for USB peripheral.

(Need to 470K ohm pull-down for power consumption in sleep mode)

PDP0 IO DATA(+) for USB peripheral. (Need to 1.5K ohm pull-up)

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-26

Table 1-3. SC32442B Signal Descriptions (Sheet 4 of 6)

Signal Input/Output Description

SPI

SPIMISO[1:0] IO SPIMISO is the master data input line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role.

SPIMOSI[1:0] IO SPIMOSI is the master data output line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role.

SPICLK[1:0] IO SPI clock

nSS[1:0] I SPI chip select(only for slave mode)

SD

SDDAT[3:0] IO SD receive/transmit data

SDCMD IO SD receive response/ transmit command

SDCLK O SD clock

General Port

GPn[129:0] IO General input/output ports (some ports are output only)

TIMMER/PWM

TOUT[3:0] O Timer output[3:0]

TCLK[1:0] I External timer clock input

JTAG TEST LOGIC

nTRST I nTRST(TAP Controller Reset) resets the TAP controller at start.

If debugger is used, A 10K pull-up resistor has to be connected.

If debugger(black ICE) is not used, nTRST pin must be issued by a low active

pulse(Typically connected to nRESET).

TMS I TMS (TAP Controller Mode Select) controls the sequence of the TAP

controller's states. A 10K pull-up resistor has to be connected to TMS pin.

TCK I TCK (TAP Controller Clock) provides the clock input for the JTAG logic.

A 10K pull-up resistor must be connected to TCK pin.

TDI I TDI (TAP Controller Data Input) is the serial input for test instructions and

data.

A 10K pull-up resistor must be connected to TDI pin.

TDO O TDO (TAP Controller Data Output) is the serial output for test instructions and

data.

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-27

Table 1-3. SC32442B Signal Descriptions (Sheet 5 of 6)

Signal Input/Output Description

Reset, Clock & Power

XTOpll AO Crystal Output for internal osc circuit.

When OM[3:2] = 00b, XTIpll is used for MPLL CLK source and UPLL CLK

source.

When OM[3:2] = 01b, XTIpll is used for MPLL CLK source only.

When OM[3:2] = 10b, XTIpll is used for UPLL CLK source only.

If it isn't used, it has to be a floating pin.

MPLLCAP AI Loop filter capacitor for main clock.

UPLLCAP AI Loop filter capacitor for USB clock.

XTIrtc AI 32 kHz crystal input for RTC. If it isn’t used, it has to be High (VDDRTC).

XTOrtc AO 32 kHz crystal output for RTC. If it isn’t used, it has to be Float.

CLKOUT[1:0] O Clock output signal. The CLKSEL of MISCCR register configures the clock

output mode among the MPLL CLK, UPLL CLK, FCLK, HCLK, PCLK.

nRESET ST nRESET suspends any operation in progress and places SC32442B into a

known reset state. For a reset, nRESET must be held to L level for at least 4

OSCin after the processor power has been stabilized.

nRSTOUT O For external device reset control(nRSTOUT = nRESET & nWDTRST &

SW_RESET)

PWREN O 1.2V/1.3V core power on-off control signal

nBATT_FLT I Probe for battery state(Does not wake up at Sleep mode in case of low battery

state). If it isn’t used, it has to be High (VDDOP).

OM[3:2] I OM[3:2] determines how the clock is made.

OM[3:2] = 00b, Crystal is used for MPLL CLK source and UPLL CLK source.

OM[3:2] = 01b, Crystal is used for MPLL CLK source

and EXTCLK is used for UPLL CLK source.

OM[3:2] = 10b, EXTCLK is used for MPLL CLK source

and Crystal is used for UPLL CLK source.

OM[3:2] = 11b, EXTCLK is used for MPLL CLK source and UPLL CLK source.

EXTCLK I External clock source.

When OM[3:2] = 11b, EXTCLK is used for MPLL CLK source and UPLL CLK

source.

When OM[3:2] = 10b, EXTCLK is used for MPLL CLK source only.

When OM[3:2] = 01b, EXTCLK is used for UPLL CLK source only.

If it isn't used, it has to be High (VDDOP).

XTIpll AI Crystal Input for internal osc circuit.

When OM[3:2] = 00b, XTIpll is used for MPLL CLK source and UPLL CLK

source.

When OM[3:2] = 01b, XTIpll is used for MPLL CLK source only.

When OM[3:2] = 10b, XTIpll is used for UPLL CLK source only.

If it isn't used, XTIpll has to be High (VDDOP).

PRODUCT OVERVIEW SC32442B RISC MICROPROCESSOR

1-28

Table 1-3. SC32442B Signal Descriptions (Sheet 6 of 6)

Signal Input/Output Description

Power

VDDALIVE P SC32442B reset block and port status register VDD.

It should be always supplied whether in normal mode or in Sleep mode.

VDDIARM P SC32442B core logic VDD for ARM core.

VDDI P SC32442B core logic VDD for Internal block.

VSSCOM P SC32442B core logic VSS

VDDA_MPLL P SC32442B MPLL analog and digital VDD.

VSSA_MPLL P SC32442B MPLL analog and digital VSS.

VDDOP,OP1,

OP2, OP3

P SC32442B I/O port VDD 3.3V/2.5V

VDDMOP P SC32442B Memory I/O VDD

VSSOP P SC32442B I/O port VSS

VDDRTC P RTC VDD (3.0V, Input range: 1.8 ~ 3.6V)

This pin must be connected to power properly if RTC isn't used.

VDDA_UPLL P SC32442B UPLL analog and digital VDD

VSSA_UPLL P SC32442B UPLL analog and digital VSS

VDDA_ADC P SC32442B ADC VDD(3.3V)

VSSA_ADC P SC32442B ADC VSS

VCC_NF P NAND VDD in SC32442B

VSS_NF P NAND VSS in SC32442B

VDD_SDRAM P mSDRAM VDD Core in SC32442B

VSS_SDRAM P mSDRAM VSS Core in SC32442B

VDDQ_SDRAM P mSDRAM VDD IO in SC32442B

VSSQ_SDRAM P mSDRAM VSS IO in SC32442B

/CS O

mSDRAM chip select in SC32442B,,This pin should be connected nGCS6,

externally

/WP I

NAND write protect in SC32442B. The WP pin provides inadvertent write/erase

protection during power transitions. The internal high voltage generator is reset

when the WP pin is active low.

/CE O NAND chip select in SC32442B

The CE input is the device selection control. When the device is in the BUSY

state, CE high is ignored, and the device does not return to standby mode. This

pin should be connected nFCE, externally.

NOTE:

1. I/O means Input/Output.

2. AI/AO means analog input/analog output.

3. ST means schmitt-trigger.

4. P means power.

SC32442B RISC MICROPROCESSOR PRODUCT OVERVIEW

1-29

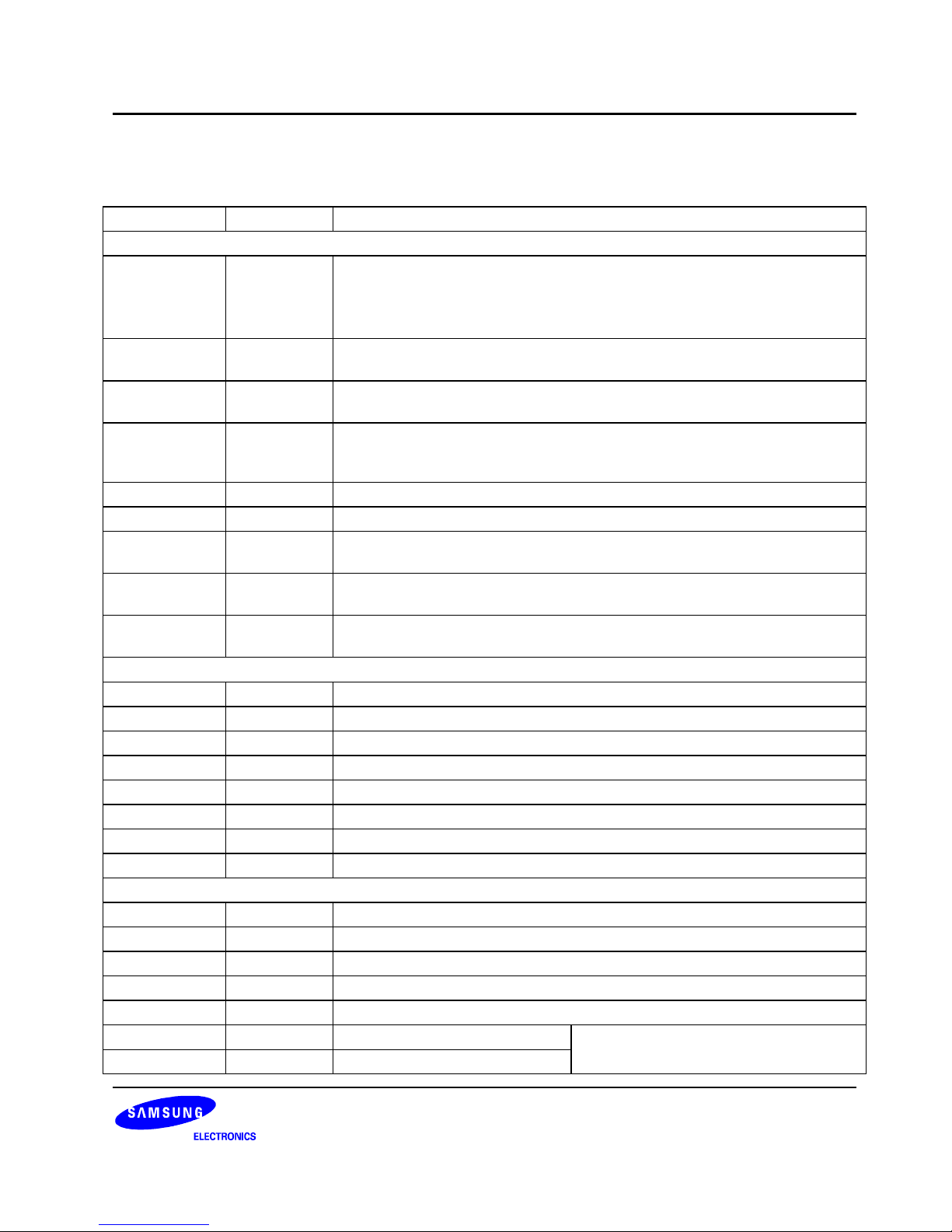

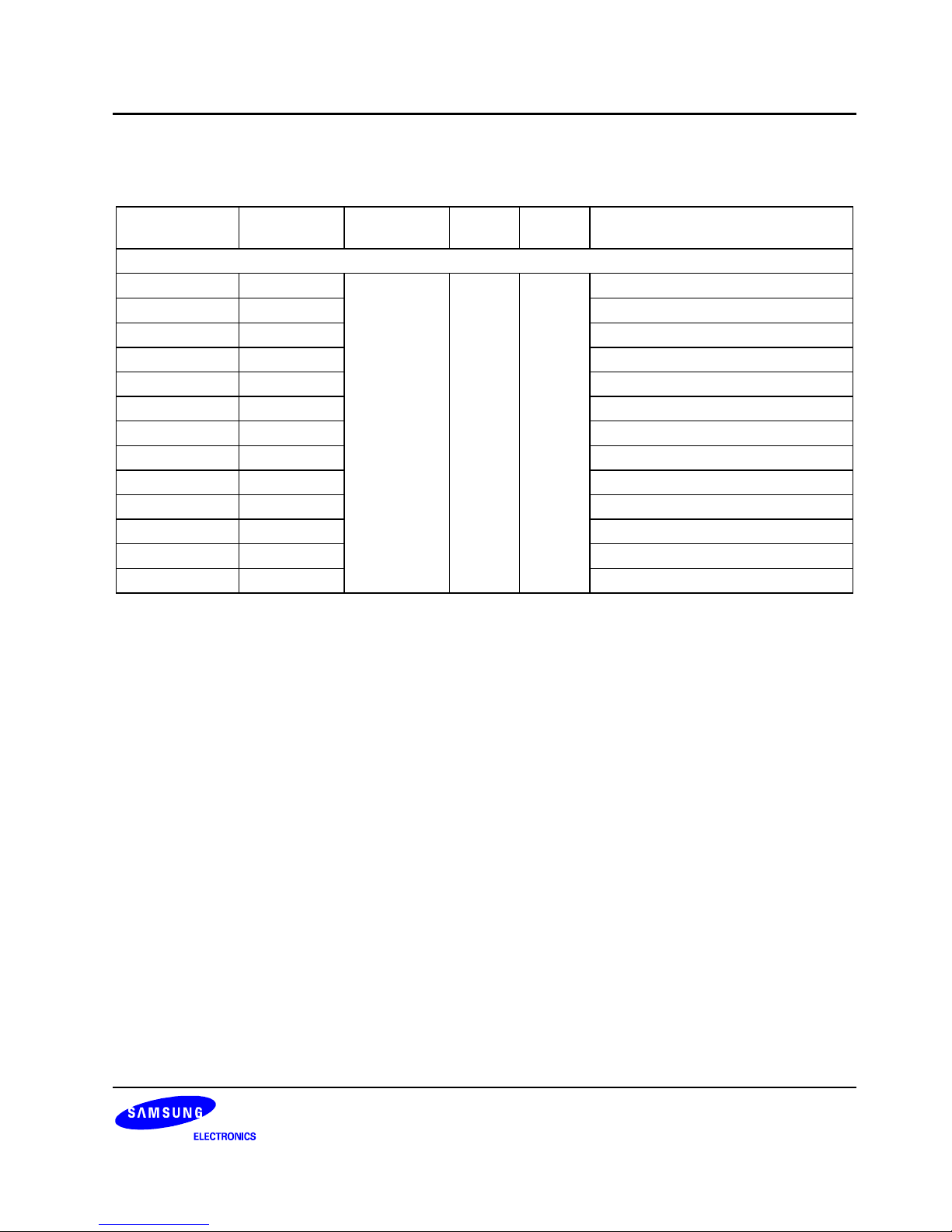

SC32442B SPECIAL REGISTERS

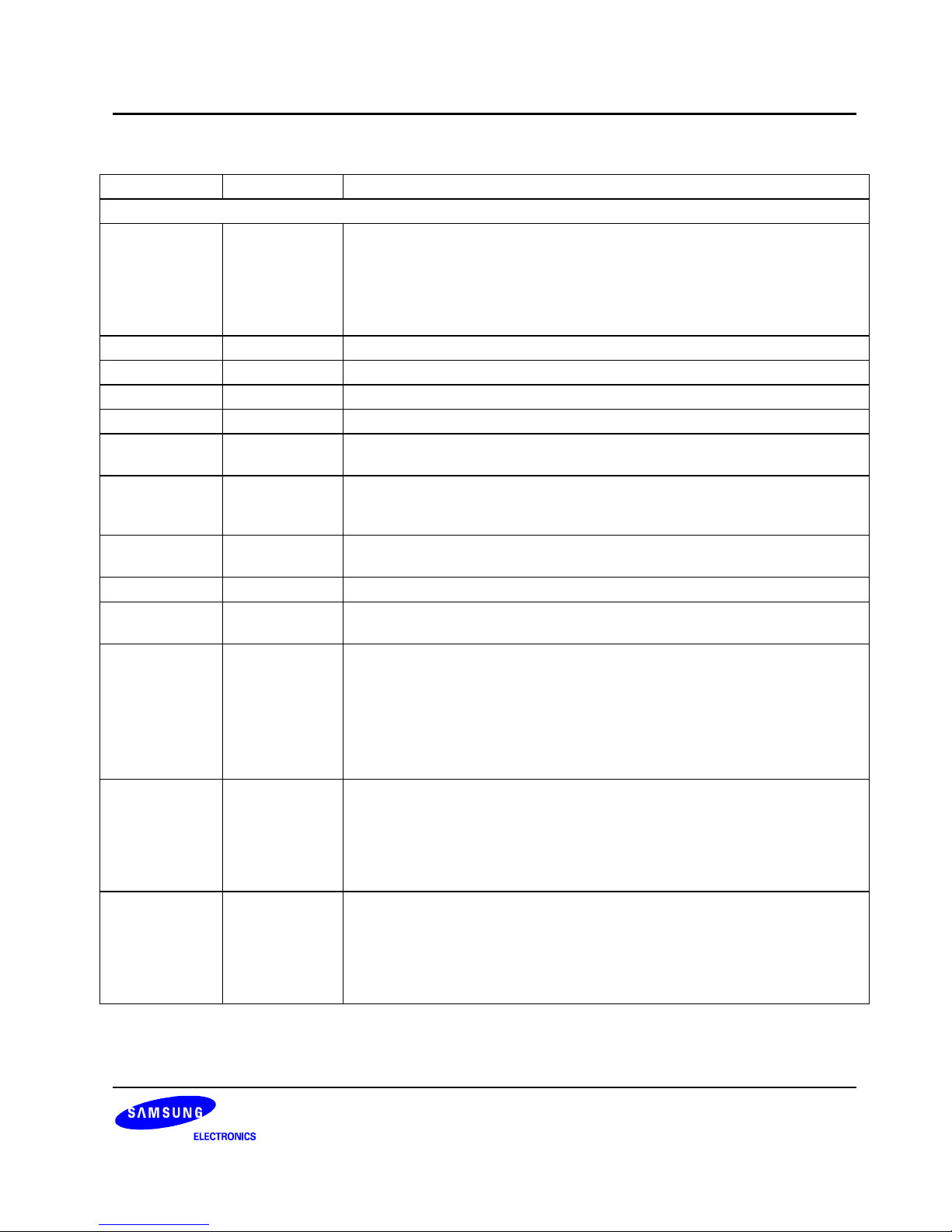

Table 1-4. SC32442B Special Registers (Sheet 1 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

Memory Controller

BWSCON 0x48000000

←

W R/W Bus Width & Wait Status Control

BANKCON0 0x48000004 Boot ROM Control

BANKCON1 0x48000008 BANK1 Control

BANKCON2 0x4800000C BANK2 Control

BANKCON3 0x48000010 BANK3 Control

BANKCON4 0x48000014 BANK4 Control

BANKCON5 0x48000018 BANK5 Control

BANKCON6 0x4800001C BANK6 Control

BANKCON7 0x48000020 BANK7 Control

REFRESH 0x48000024 DRAM/SDRAM Refresh Control

BANKSIZE 0x48000028 Flexible Bank Size

MRSRB6 0x4800002C Mode register set for SDRAM BANK6

MRSRB7 0x48000030 Mode register set for SDRAM BANK7

Loading...

Loading...