Samsung S524AD0XD1, S524AD0XF1 Datasheet

S524AD0XD1/D0XF1

128K/256K-bit

Serial EEPROM

for Low Power

Data Sheet

OVERVIEW

The S524AD0XD1/D0XF1 serial EEPROM has a 128K/256K-bit (16,384/32,768 bytes) capacity, supporting the

standard I2C™-bus serial interface. It is fabricated using Samsung’s most advanced CMOS technology. It has

been developed for low power and low voltage applications (1.8 V to 5.5 V). One of its major feature is a

hardware-based write protection circuit for the entire memory area. Hardware-based write protection is controlled

by the state of the write-protect (WP) pin. Using one-page write mode, you can load up to 64 bytes of data into

the EEPROM in a single write operation. Another significant feature of the S524AD0XD1/D0XF1 is its support for

fast mode and standard mode.

FEATURES

I2C-Bus Interface

• Two-wire serial interface

• Automatic word address increment

EEPROM

• 128K/256K-bit (16,384/32,768 bytes) storage

area

• 64-byte page buffer

• Typical 3 ms write cycle time with

auto-erase function

• Hardware-based write protection for the entire

EEPROM (using the WP pin)

• EEPROM programming voltage generated

on chip

• 500,000 erase/write cycles

• 50 years data retention

Operating Characteristics

• Operating voltage

— 1.8 V to 5.5 V

• Operating current

— Maximum write current: < 3 mA at 5.5 V

— Maximum read current: < 400 µA at 5.5 V

— Maximum stand-by current: < 1 µA at 5.5 V

• Operating temperature range

— – 25°C to + 70°C (commercial)

— – 40°C to + 85°C (industrial)

• Operating clock frequencies

— 400 kHz at standard mode

— 1 MHz at fast mode

• Electrostatic discharge (ESD)

— 5,000 V (HBM)

— 500 V (MM)

Packages

• 8-pin DIP, and TSSOP

8-1

S524AD0XD1/D0XF1 SERIAL EEPROM DATA SHEET

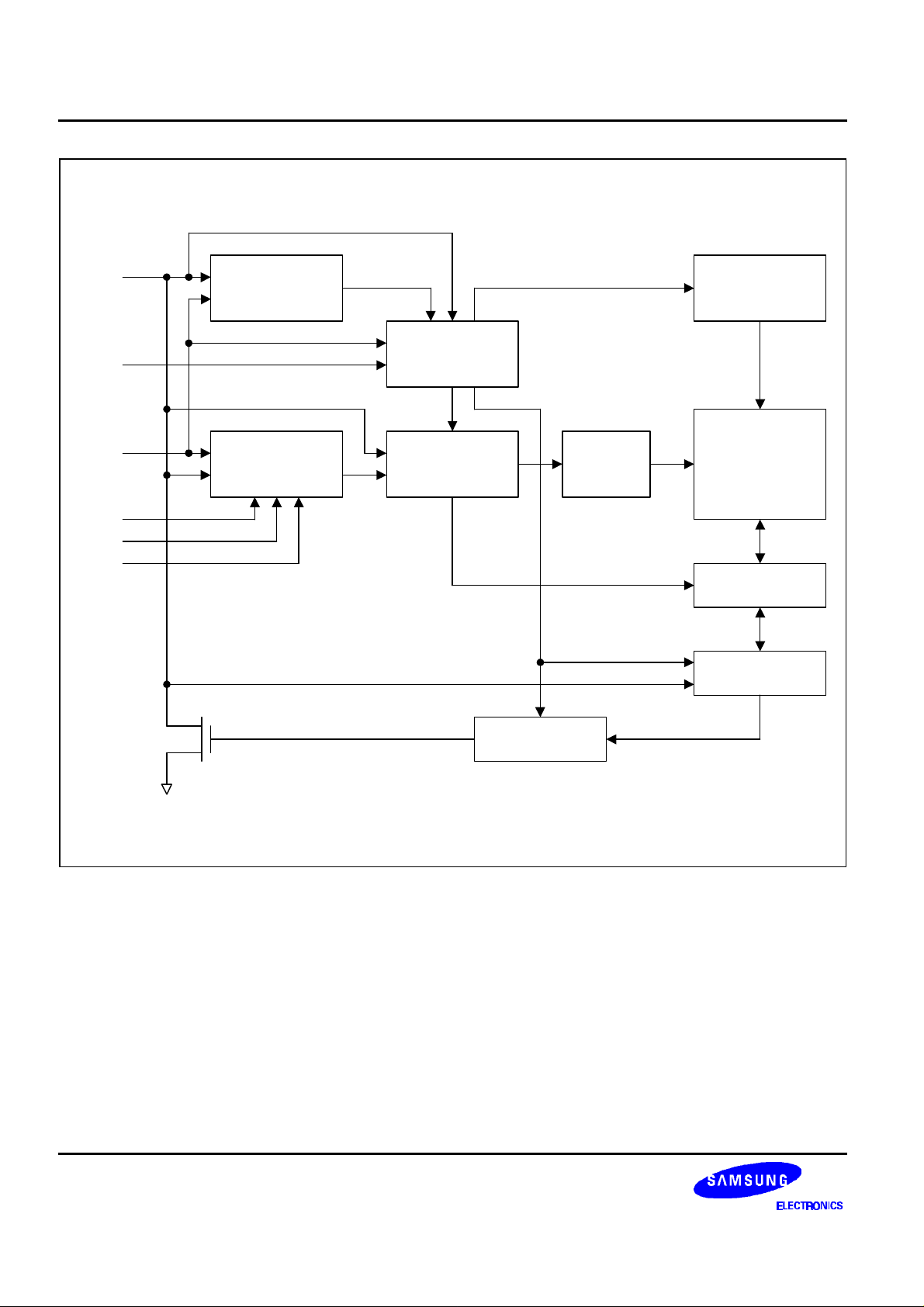

SDA

WP

SCL

A0

A1

A2

Start/Stop

Logic

Slave Address

Comparator

Control Logic

Word Address

Pointer

Row

decoder

HV Generation

Timing Control

EEPROM

Cell Array

16,384 x 8 bits

32,768 x 8 bits

Column Decoder

Data Register

DOUT and ACK

Figure 8-1. S524AD0XD1/D0XF1 Block Diagram

8-2

DATA SHEET S524AD0XD1/D0XF1 SERIAL EEPROM

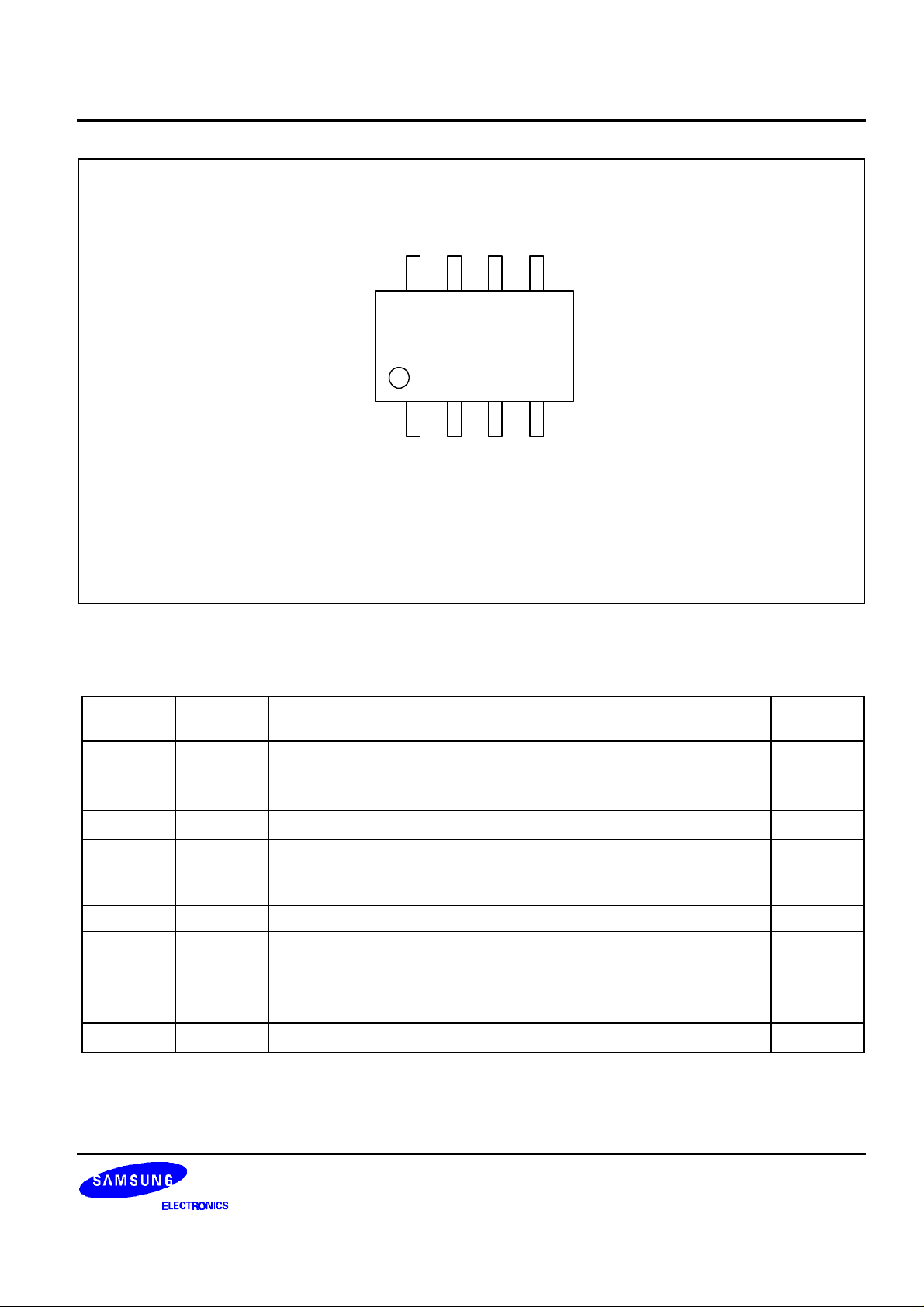

VCC WP SCL SDA

S524AD0XD1/D0XF1

A0 A1 A2 VSS

NOTE: The S524AD0XD1/D0XF1 is available

in 8-pin DIP, and TSSOP package.

Figure 8-2. Pin Assignment Diagram

Table 8-1. S524AD0XD1/D0XF1 Pin Descriptions

Name Type Description Circuit

A0, A1, A2

VSS

Input Input pins for device address selection. To configure a device address,

these pins should be connected to the VCC or V

These pins are internally pulled down to V

SS.

of the device.

SS

– Ground pin. –

SDA I/O Bi-directional data pin for the I2C-bus serial data interface. Schmitt

trigger input and open-drain output. An external pull-up resistor must

be connected to V

DD.

SCL Input Schmitt trigger input pin for serial clock input. 2

WP Input

Input pin for hardware write protection control. If you tie this pin to V

CC,

the write function is disabled to protect previously written data in the

entire memory; if you tie it to VSS, the write function is enabled.

VCC

This pin is internally pulled down to V

– Single power supply. –

SS.

Type

1

3

1

NOTE: See the following page for diagrams of pin circuit types 1, 2, and 3.

8-3

S524AD0XD1/D0XF1 SERIAL EEPROM DATA SHEET

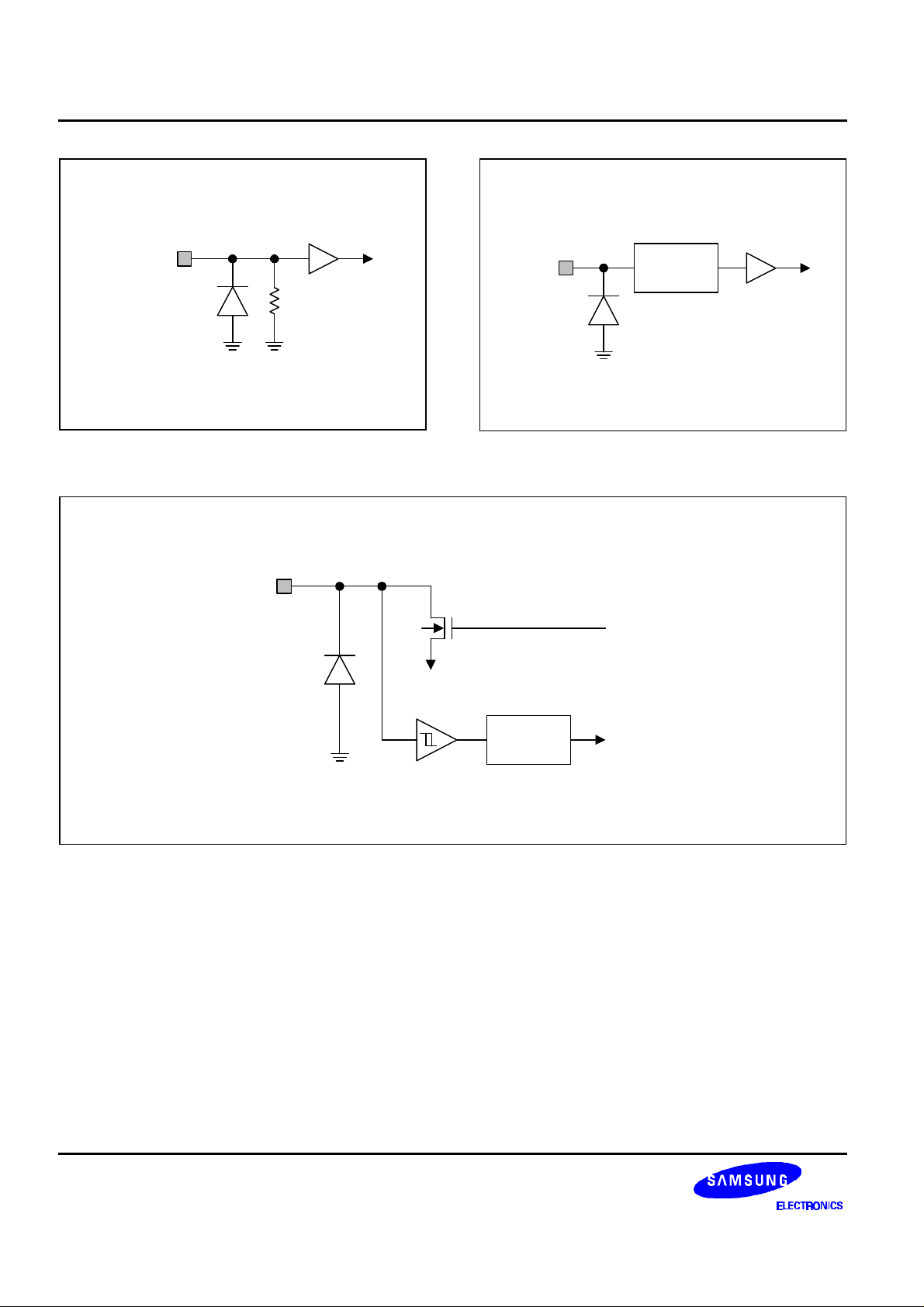

A0, A1,

A2, WP

Figure 8-3. Pin Circuit Type 1

SDA

VSS

SCL

Noise

Filter

Figure 8-4. Pin Circuit Type 2

Data Out

Noise

Filter

Figure 8-5. Pin Circuit Type 3

Data In

8-4

DATA SHEET S524AD0XD1/D0XF1 SERIAL EEPROM

FUNCTION DESCRIPTION

I2C-BUS INTERFACE

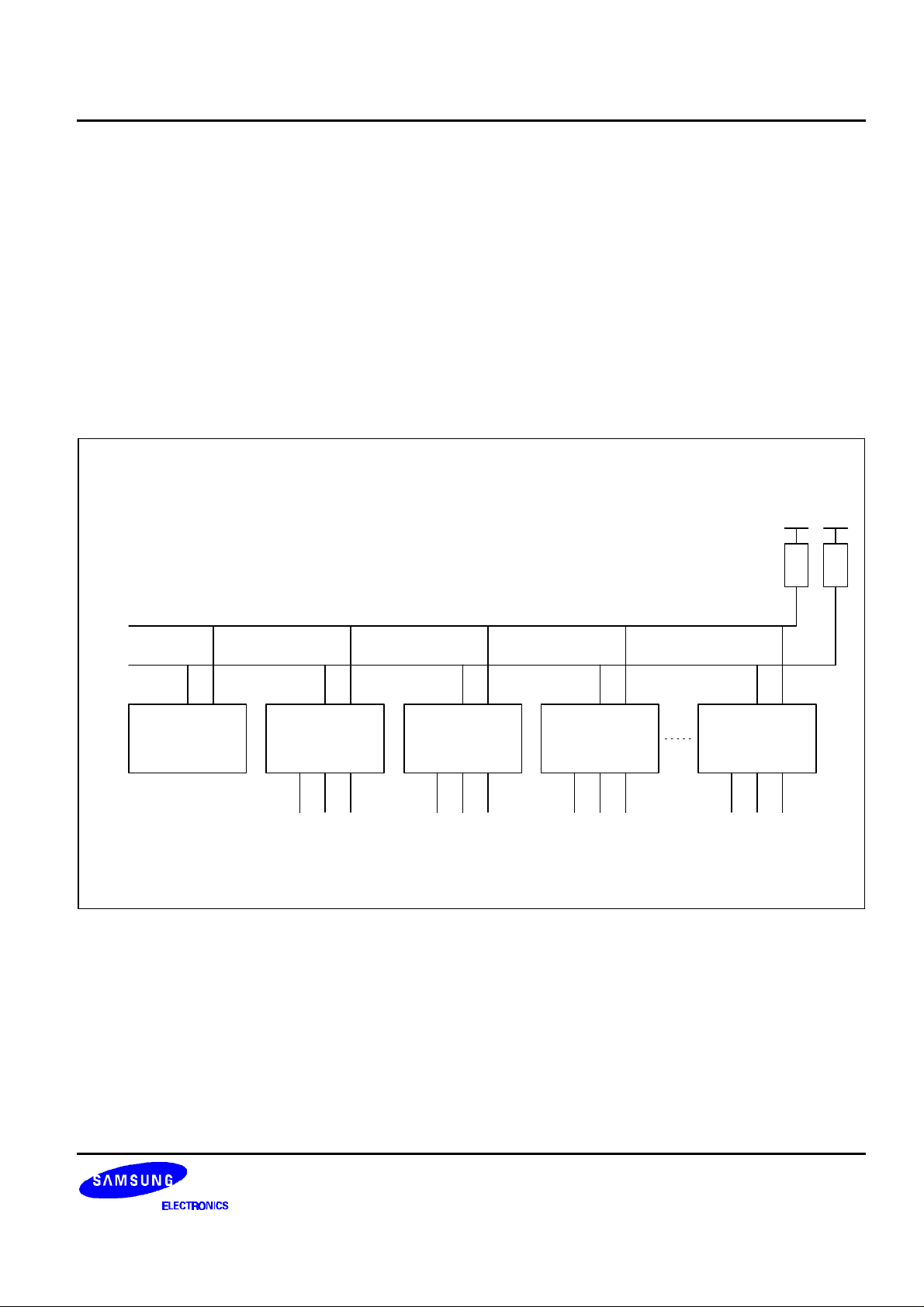

The S524AD0XD1/D0XF1 supports the I2C-bus serial interface data transmission protocol. The two-wire bus

consists of a serial data line (SDA) and a serial clock line (SCL). The SDA and the SCL lines must be connected

to VCC by a pull-up resistor that is located somewhere on the bus.

Any device that puts data onto the bus is defined as a “transmitter” and any device that gets data from the bus is

a “receiver.” The bus is controlled by a master device which generates the serial clock and start/stop conditions,

controlling bus access. Using the A0, A1, and A2 input pins, up to eight S524AD0XD1/D0XF1 devices can be

connected to the same I2C-bus as slaves (see Figure 8-6). Both the master and slaves can operate as a

transmitter or a receiver, but the master device determines which bus operating mode would be active.

V

CC

V

CC

SDA

SCL

Bus Master

(Transmitter/

Receiver)

MCU

Slave 1

S524AD0XD1/

D0XF1

Tx/Rx

A0 A1 A2

To VCC or V

SS

Slave 2

S524AD0XD1/

D0XF1

Tx/Rx

A0 A1 A2

To VCC or V

SS

Slave 3

S524AD0XD1/

D0XF1

Tx/Rx

A0 A1 A2

To VCC or V

Figure 8-6. Typical Configuration

SS

Slave 8

S524AD0XD1/

D0XF1

Tx/Rx

A0 A1 A2

To VCC or V

SS

R

R

8-5

Loading...

Loading...