OSD PART

查询S1D2514X01供应商

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

VIDEO AMP MERGED OSD PROCESSOR

The S1D2514X01 is a very high frequency video amplifier

& wide range OSD processor 1 chip system with I2C Bus

control used in monitors. It contains 3 matched R/G/B video

amplifiers with OSD processor and provides flexible

interfacing to I2C Bus controlled adjustment systems.

FUNCTIONS

ORDERING INFORMATION

• R/G/B video amplifier

• OSD processor

• I2C bus control

• Cut-off brightness control

• R/G/B sub contrast/cut-off control

• Half tone

S1D2514X01-D0B0 32-DIP-600A -20 °C − +75 °C

FEATURES

VIDEO AMP PART

32-DIP-600A

Device Package Operating Temperature

• 3-channel R/G/B video amplifier, 150MHz @f-3dB

• I2C bus control items

— Contrast control: -38dB

- Sub contrast control for each channel: -12dB

- Brightness control

- OSD contrast control: -38dB

- Cut-off brightness control (AC coupling)

- Cut-off control for each channel (AC coupling)

- Switch registers for SBLK and video half tone and

CLP/BLK polarity selection and INT/EXT CLP selection

• Built in ABL (automatic beam limitation)

• Built in video input clamp, BRT clamp

• Built in video half tone (3mode) function on OSD

pictures

• Capable of 8.0Vp-p output swing

• Improvement of rise & fall time (2.2ns)

• Cut-off brightness control

• Built in blank gate with spot killer

• Clamp pulse generator

• OSD intensity

• BLK, CLP polarity selection

• Clamp gate with anti OSD sagging

• Built in 1K-byte SRAM

• 256 ROM fonts (each font consists of 12 × 18

dots.)

• Full screen memory architecture

• Wide range PLL available (15kHz — 90kHz,

Reference 800 X 600)

• Programmable vertical height of character

• Programmable vertical and horizontal

positioning

• Character color selection up to 16 different

colors (in a units of character)

• Programmable background color (up to 16

colors)

• Character blinking and shadowing

• Character scrolling

• 72MHz pixel frequency from on-chip PLL

(Reference 800 ± 600)

• Full white pattern generation function

0

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

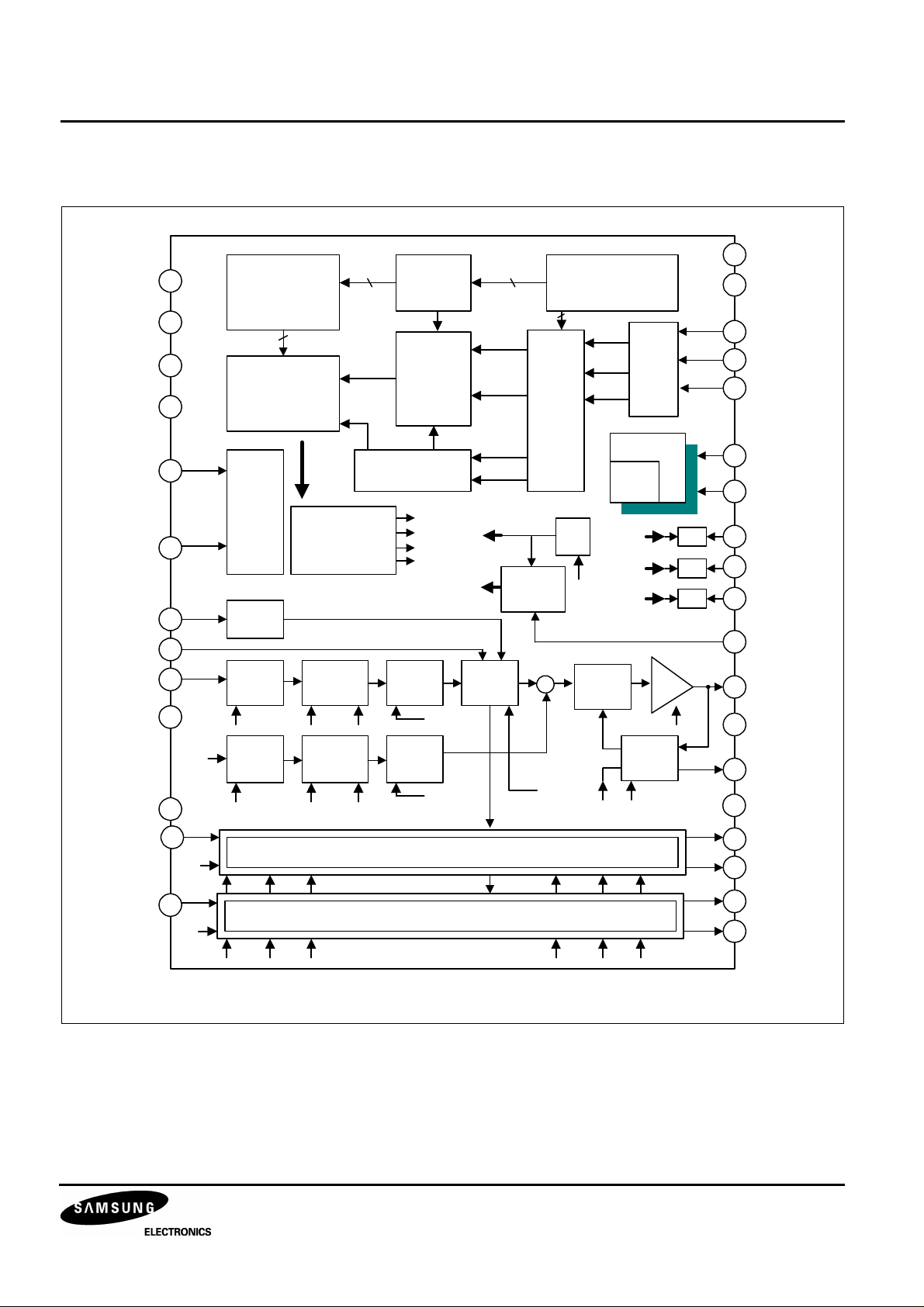

BLOCK DIAGRAM

6

VDDA

9 16

ROM

Address

(480 x 16)

Ctrl Font

Display

Display Ctrl

RAM Data

Frame Ctrl

ROM Ctrl

Control

16Ctrl Data

CLK

H_Pulse

V_Pulse

OSD

2

VSSA

32

HFLB

1

VFLB

3

VCO_IN_P

VSS

VCC3

GND3

31

(448 x 18 x 12)

28

Font Data

11

12

Output Stage

9

VREF1

VREF

ABL

CONT_CAP

RIN

GND1

VCC1

GIN

BIN

4

5

8

7

12

15

13

14

16

R OSD

G OSD

B OSD

H/V/CLK Ctrl

RGB OSD

FBL

INTE

HT DET.

Frame Ctrl

ROM Ctrl

BLK

CLP

Clamp

Pulse

Band

Gap.Ref

R/G/B OSD

FBLK

Intensity

Timing Controller

Multi (3 mode)

Half Tone

H/V/CLK Ctrl

Gen.

ABL

Video

Input

Clamp

CLP

OSD

Input

Cilp.

HT DET.

Video

Half Tone

SW

OSD

Half Tone

SW

FBLK I2C

Sub

Cont.

Control

I2CFBLK

Video

Contrast

I2C

+

OSD

Cont.

Control

I2C

I2C Cont. Cntl

G-CHANNEL

CLP HT DET. FBLK CLP BLKI2C

B-CHANNEL

CLP HT DET. FBLK CLP BLKI2C

BLK

Int

HFLB

R cut off

G cut off

B cut off

Sub

Cont.

Control

Latches

I2C bus

decoder

D/A

Amp

Out

Birght

Control

CLPI2C

V/I

V/I

V/I

BLK

30

29

27

26

25

10

24

22

23

19

20

21

17

18

SDA

SCL

RCT

GCT

BCT

CLP_IN

R OUT

VCC2

R CLP

GND2

G CLP

G OUT

B CLP

B OUT

Figure 1. Functional Block Diagram

1

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

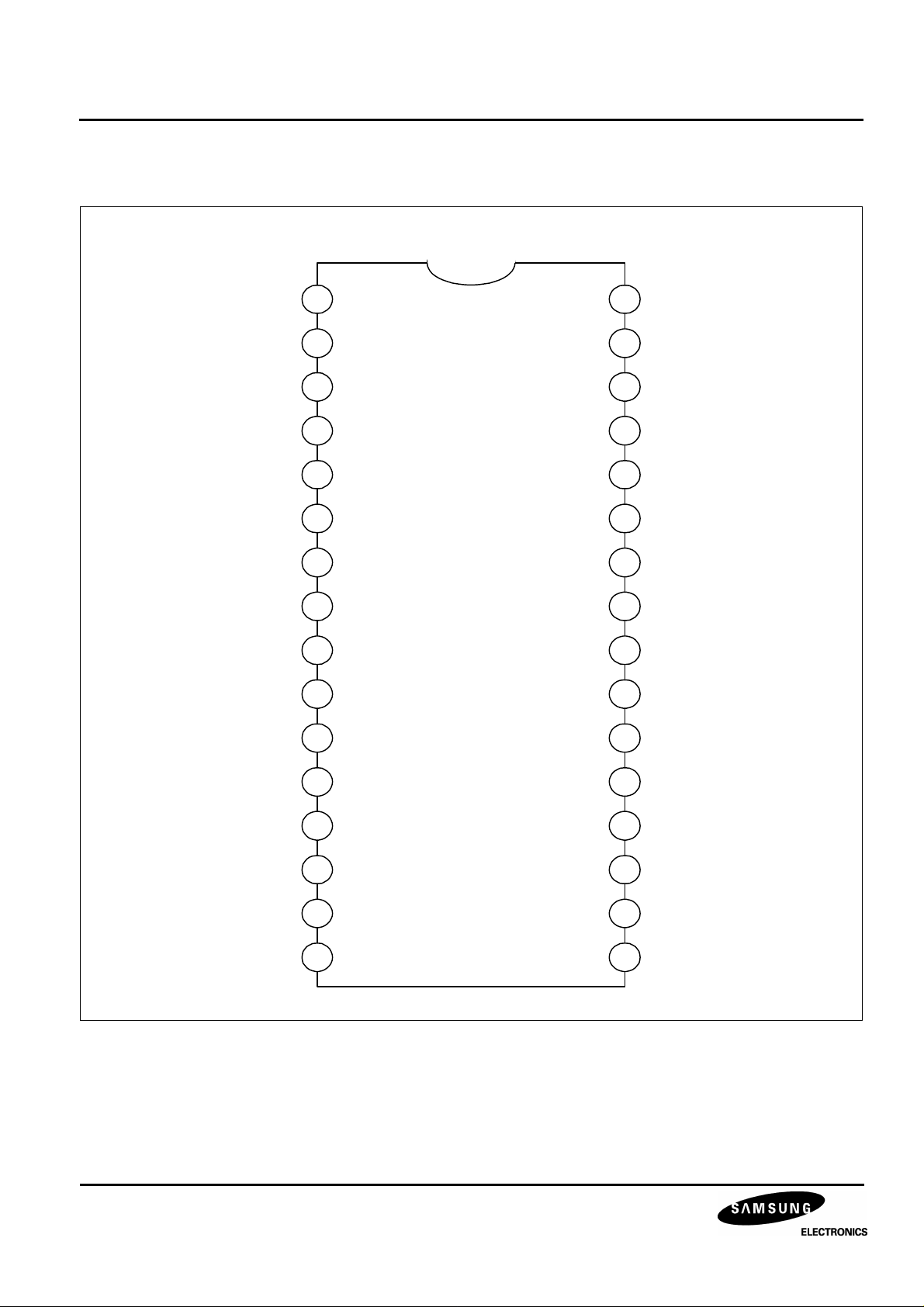

PIN CONFIGURATION

1

VFLB

VSSA

2

VCO_IN_P

3

4

VREF1

5

VREF

6

VDDA

CONT_CAP

7

ABL_IN

8

9

GND3

CLP_IN

10

VCC3

11

HFLB

VDD

SDA

VSS

RCT

GCT

BCT

KB2514

ROUT

S1D2514X01

RCLP

VCC2

SCL

32

31

30

29

28

27

26

25

24

23

22

12

13

14

15

16

RIN

VCC1

GIN

GND1

BIN

GOUT

GCLP

GND2

BOUT

BCLP

21

20

19

18

17

Figure 2. Pin Configuration

2

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

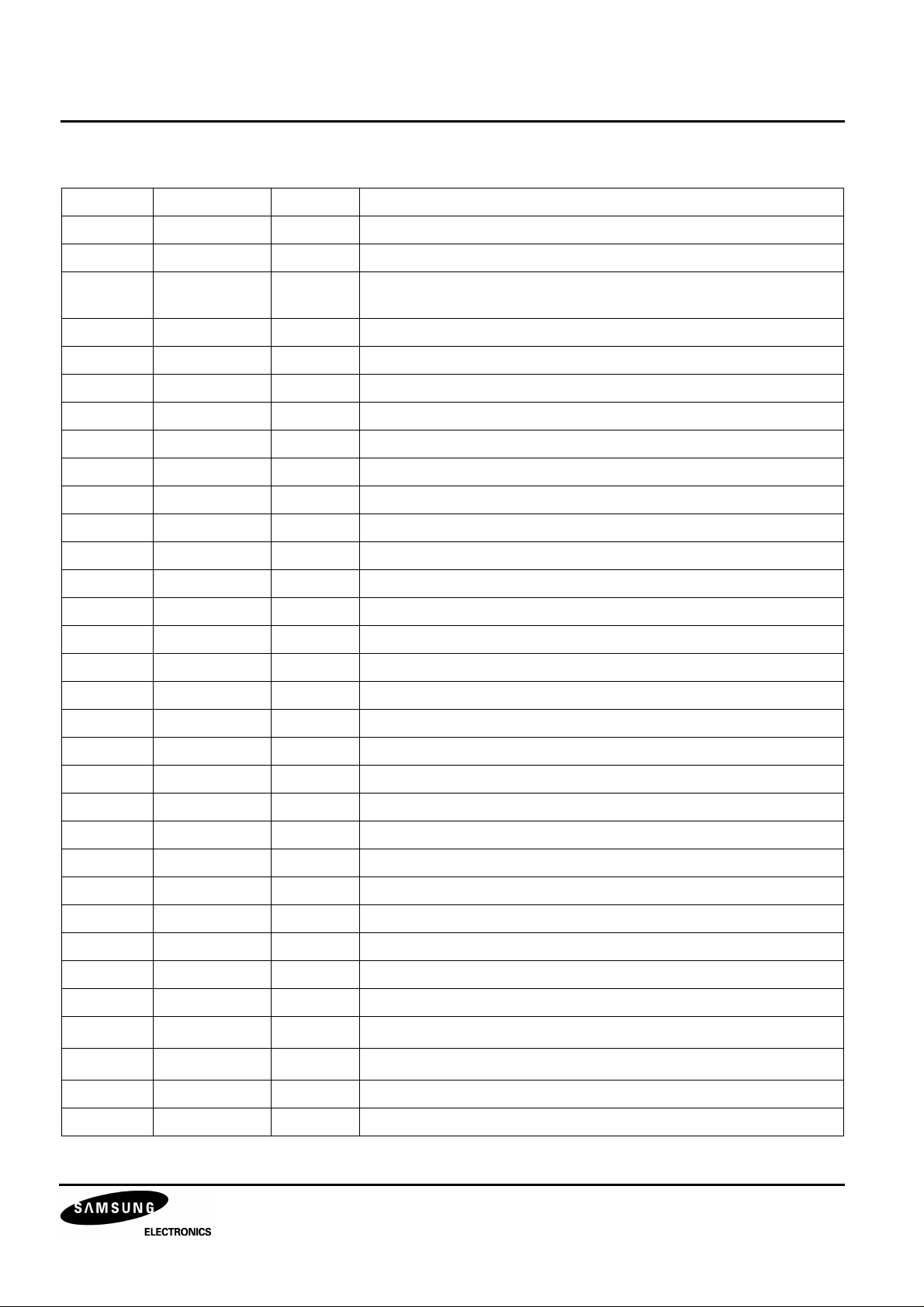

Table 1. Pin Configuration

Pin No. Symbol I/O Configuration

1 VFLB I Vertical flyback signal

2 VSSA - Ground (PLL part)

3 VCO_IN_P I

4 VREF1 O Charge pump output

5 VREF O PLL regulator filter

6 VDDA - +5V supply voltage for PLL part

7 CONT_CAP - Contrast control for AMP part

8 ABL - Auto beam limit.

9 GND3 - Ground for video AMP part(for AMP control)

10 CLP_IN - Video clamp pulse input

11 VCC3 - +12V supply voltage for video AMP part(for AMP control)

12 RIN I Video signal input (red)

13 VCC1 - +12V supply voltage for video AMP(for main video signal process)

14 GIN I Video signal input (green)

15 GND1 - Ground for video AMP part(for main video signal process)

16 BIN I Video signal input (blue)

17 BCLP - B output clamp cap

18 BOUT O Video signal output (blue)

This voltage is generated at the external loop filter and goes into the

input stage of the VCO.

19 GND2 - Ground for video AMP part(for video output drive)

20 GCLP - G output clamp cap

21 GOUT O Video signal output (green)

22 VCC2 - +12V supply voltage for video AMP part(for video output drive)

23 RCLP - R output clamp cap

24 ROUT O Video signal output (red)

25 BCT - B cut-off output

26 GCT - G cut-off output

27 RCT - R cut-off output

28 VSS - Ground for digital part

29 SCL I

30 SDA I/O

31 VDD - +5V supply voltage for digital part

32 HFLB I Horizontal flyback signal

Serial clock (I2C)

Serial data (I2C)

3

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

PIN DESCRIPTION

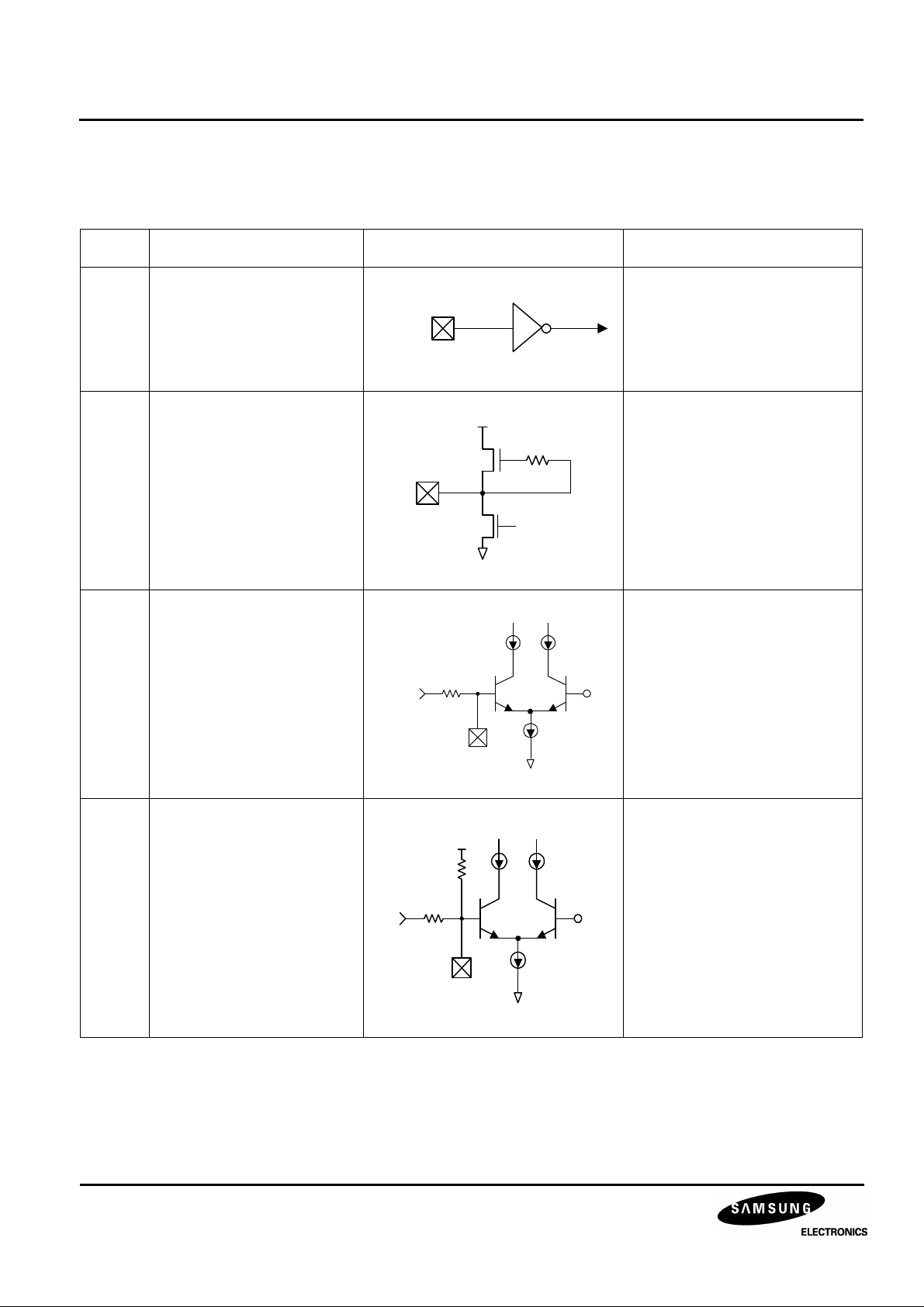

Table 2. Pin Description

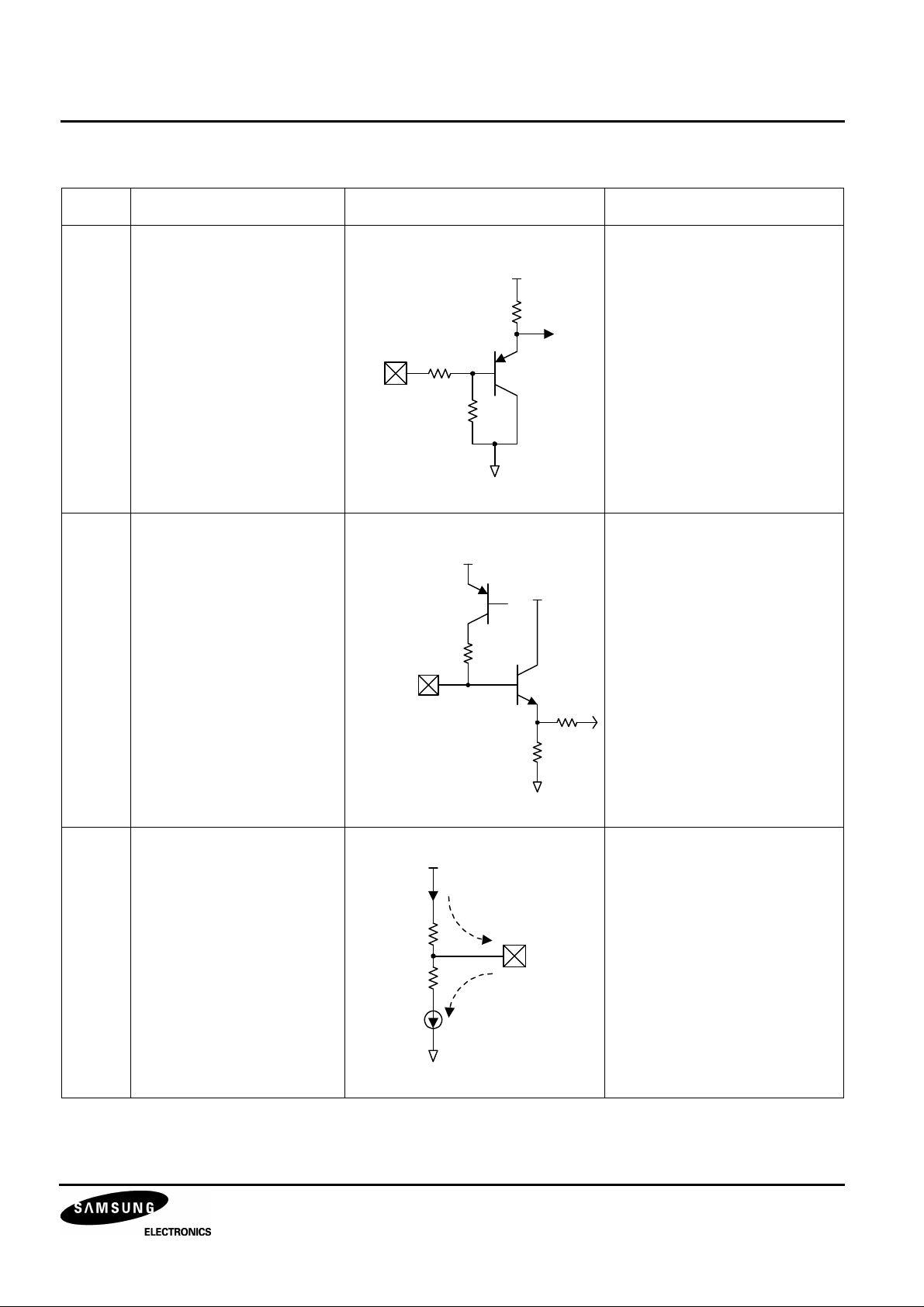

Pin No Pin Name Schematic Description

1

32

3

4

5

VFLB

HFLB

VCO_IN_P

VPEF1

VREF

7 Contrast cap

(CONT_CAP)

VFLB

HFLB

4.0K

FLB signal is in TTL level

Multi polarity input

PLL loop filter output

BandGap ref. output

Contrast cap range

(0.1uF — 5uF)

VrefI2C Data

100µA

8 ABL_IN

4

100K

2K

VCC

ABL input DC range

(1 — 4.5V)

VrefVref

250µA

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Table 2. Pin Description (Continued)

Pin No Pin Name Schematic Description

10 CLP_IN Multi polarity input

VCC

50K

Clamp gate pulse TTL level

input

10K

12

14

Red video input

(RIN)

Green video input

VCC

Max input video signal is 0.7

Vpp

VCC

(GIN)

16

Blue video input

(BIN)

Video_In

0.2K

17

20

23

Blue (B clamp cap)

Green (G clamp cap)

Red (R clamp)

0.2K

0.2K

12K

Brightness controlling actives by

charging and discharging of the

external cap. (0.1µF)

(During clamp gate)

CLP

Iclamp

5

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Table 2. Pin Description (Continued)

Pin No Pin Name Schematic Description

18

21

24

27

26

25

Blue video output

(BOUT)

Green video output

(GOUT)

Red video output

(ROUT)

Red cut-off control

(RCT)

Green cut-off control

(GCT)

Blue cut-off control

(BCT)

VCC

0.05K

0.5K

0.04K

Isink

0-600uA 0-200uA 50uA 100uA

Video_Out

0.2K

Video signal output

Cut-off control output

CTX

29 SCL

30 SDA

SDA

SCL

Serial clock input port of I2C bus

Serial data input port of I2C bus

ACK

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

ABSOLUTE MAXIMUM RATINGS

(see 1)

(Ta = 25 °C)

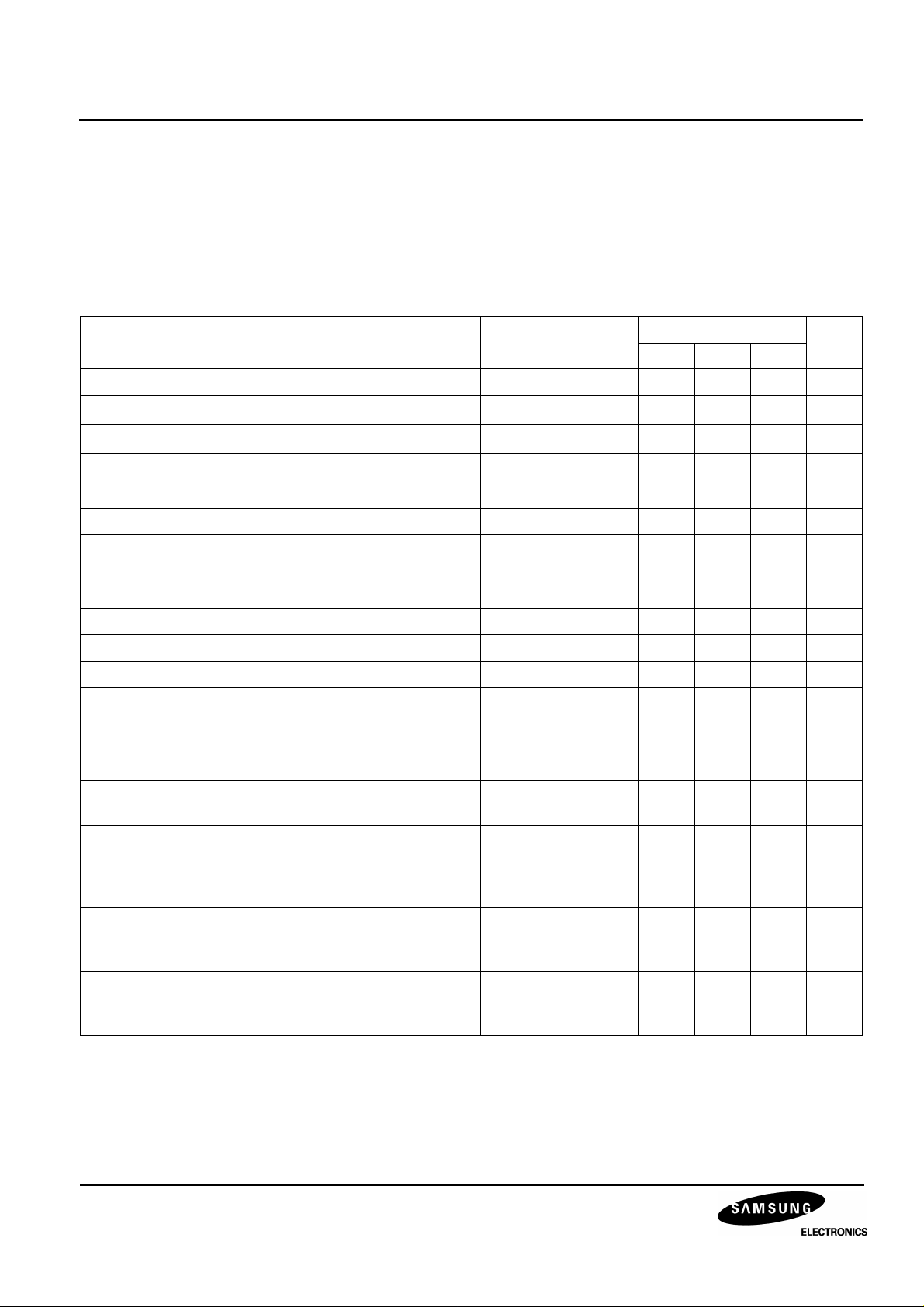

Table 3. Absolute Maximum Ratings

Value

No Item Symbol

Min Typ Max

1 Maximum supply voltage

2

Operating temperature

(see 2)

V

CC

V

DD

Topr -20 - 75 °C

- - 13.2

- - 6.5

3 Storage temperature Tstg -65 150 °C

4 Operating supply voltage

V

V

5 Power dissipation P

CCop

DDop

D

11.4 12.0 12.6

4.75 5.00 5.25

- - W

THERMAL & ESD PARAMETER

Table 4. Thermal & ESD Parameter

Unit

V

V

(see 3)

No Item Symbol

Value

Min Typ Max

Thermal resistance

1

(junction-ambient)

θja - 48 - °C/W

2 Junction temperature Tj - 150 - °C

Human body model

3

(C = 100p, R = 1.5k)

Machine model

4

(C = 200p, R = 0)

HBM 2 - - KV

MM 300 - - V

5 Charge device model CDM 800 - - V

Unit

7

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

ELECTRICAL CHARACTERISTICS

DC ELECTRICAL CHARACTERISTICS

(Tamb = 25 °C, VCC = 12V, VDD = V

= 5V, ABL input voltage = 5V, HFLB input signal = S3, load resistors =

DDA

470Ω, except OSD part current 35mA, unless otherwise stated)

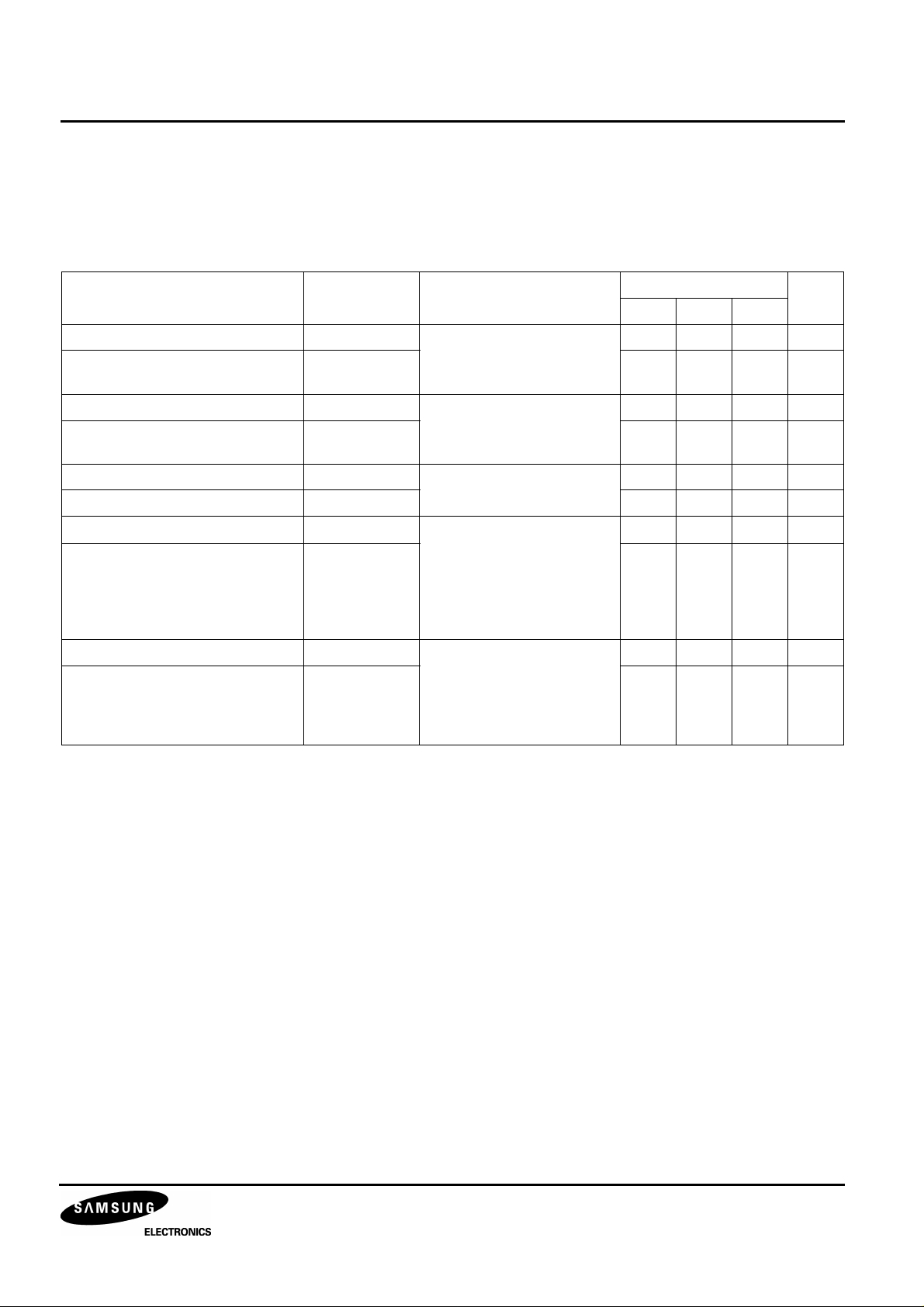

Table 5. DC Electrical Characteristics

Parameter Symbol Conditions

Supply current ICC

Minimum supply current ICC min VCC = 11.4V 95 110 120 mA

Maximum supply current ICC max VCC = 12.6V 105 130 140 mA

ABS supply current ICC abs VCC = 13.2V - - 175 mA

Video input bias voltage V bias 1.8 2.1 2.4 V

Video black level voltage (POR) V blackpor 1.20 1.50 1.80 V

Black level voltage channel difference (POR) ∆ V blackpor

Video black level voltage (FFH) V blackff

Black level voltage channel difference (FFH) ∆ V blackff ∆ 10 - - %

Video black level voltage (00H) V black00 04 = 00H - 0.2 0.5 V

Black level voltage channel difference (00H) ∆ V black00 ∆ 10 - - %

Spot killer voltage Vspot VCC = Var. 9.20 10.4 11.2 V

(see 4)

(see 5)

04 = FFH

(see 13)

Min Typ Max

100 125 130 mA

∆ 10 - - %

2.2 2.7 3.2 V

Value

Unit

Cut-off current (FFH) ICTff Pin25, 26, 27 = 12V

09 — 0B: FFH

0C: 00H

Cut-off current (00H) ICT00 Pin25, 26, 27 = 12V

09 — 0C: 00H

Cut-off brightness current (FFH) ICTBRTff Pin25, 26, 27 = 12V

09 — 0B: 00H

0C: FFH

Cut-off brightness current (80H) ICTBRT80 Pin25, 26, 27 = 12V

09 — 0B: 00H

0C: 80H

Cut-off offset current 1 ICS1 Pin25, 26, 27 = 12V

09 — 0C: 00H

0E: 11H

500 625 750 µA

- 2.0 5.0 µA

100 180 260 µA

50 90 130 µA

25 50 75 µA

8

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Table 5. DC Electrical Characteristics (Continued)

Parameter Symbol Conditions

Value

Min Typ Max

Cut-off offset current 2 ICS2 Pin25, 26, 27 = 12V

50 100 130 µA

09 — 0C: 00H

0E: 12H

Soft BLK output voltage Vsblk 0D: 80H

- 0.2 0.5 V

0E: 14H

Clamp cap voltage (POR) Vcap 6.0 7.0 8.0 V

Total external cut-off current range

Red

cut-off

Creen

cut-off

Blue

cut-off

600uA

Unit

Cut-Off Brightness

Cut-Off Offset

Switch

CS2

CS1

200uA

100uA

50uA

150uA

9

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

AC ELECTRICAL CHARACTERISTICS

(Tamb = 25 °C, VCC = 12V, VDD = V

470Ω, Vin = 0.7Vpp manually adjust video output pins 18, 21 and 24 to 4V DC for the AC test

otherwise stated

(see 12)

)

= 5V, ABL input voltage = 5V, HFLB input signal = S3, load resistors =

DDA

(see 11)

unless

Table 6. AC Electrical Characteristics

Parameter Symbol Conditions

Min Typ Max

Contrast max. output voltage Vcff 03, 05, 06, 07 = FFH

Contrast max. output channel difference ∆ Vcff ∆ 10 - - %

04, 08 — 0C = 80H

RGB input = S1

Contrast center output voltage Vc80 03, 04, 08 — 0C = 80H

Contrast center output channel difference ∆ Vc80 ∆ 10 - - %

05, 06, 07 = FFH

RGB input = S1

5.0 5.7 6.4 Vpp

2.5 2.85 3.2 Vpp

Contrast max. - Center attenuation C C = 20log (Vc80/Vcff) -8 -6 -4 dB

Sub contrast center output voltage Vd80 03 = FFH

Sub contrast center output channel

difference

∆ Vd80 ∆ 10 - - %

04 — 0C = 80H

RGB input = S1

Sub contrast min. output voltage Vd00 03 = FFH, 05—07: 00H

Sub contrast min. output channel difference ∆ Vd00 ∆ 10 - - %

04, 08 — 0C = 80H

RGB input = S1

2.3 2.6 2.9 Vpp

1.3 1.6 1.9 Vpp

Sub contrast max. - min. attenuation D D = 20log (Vd00/Vcff) -14 -12 -10 dB

ABL control range ABL

R/G/B video rising time

R/G/B video falling time

(see 7)

(see 7)

R/G/B blank output rising time

R/G/B blank output falling time

R/G/B video band width

(see 7, 8)

(see 7)

(see 7)

tr (video) 03, 05 — 07: FFH

tf (video) - 2.2 2.8 ns

tr (blank) POR

tf (blank) - 8.0 15.0 ns

f (-3dB)

Video AMP 50MHz cross talk CT_50M

(see7, 9)

(see 15)

04, 08 — 0C: 80H

RGB input = S2

HFLB: S4

(see 16)

(see 17)

-12 -10 -8 dB

150 - - MHz

Value

- 2.2 2.8 ns

- 6.0 12.0 ns

- -25 -20 dB

Unit

Video AMP 130MHz cross talk CT_130M

(see7, 9)

Absolute gain match Avmatch

Gain change between amplifier Avtrack

(see 7)

10

(see 6)

(see 18)

- -15 -10 dB

-1 - 1 dB

-1 - 1 dB

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

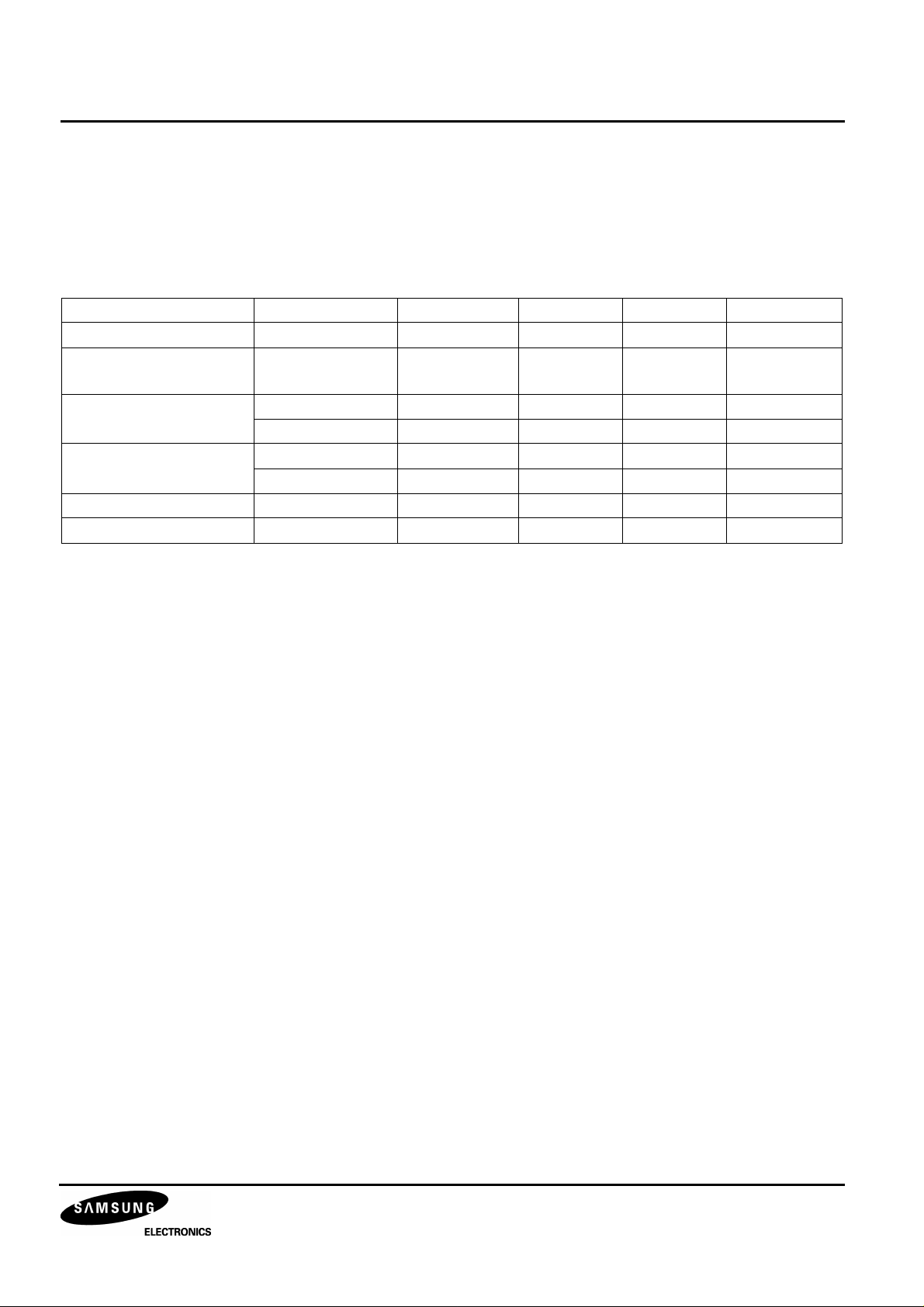

OSD ELECTRICAL CHARCTERISTICS

(Tamb = 25 °C, VCC = 12V, VDD = V

= 5V, HFLB input voltage = S3, load rosistors = 470Ω, V-AMP test

DDA

registor’s FBLK, OSD input conditions unless otherwise stated)

Table 7. OSD Electrical Chaacteristics

Parameter Symbol Conditions

OSD contrast max. output voltage Vocff 08 = FFH

OSD contrast max. output channel

difference

OSD contrast center output voltage Voc80 08 = 80H

OSD contrast center output channel

difference

R/G/B OSD rising time tr (OSD) 08: FFH - 4.0 5.0 ns

R/G/B OSD falling time tf (OSD) - 4.0 5.0 ns

HT video level HTvideo ABL = 6V

HT video output channel difference ∆ HTvideo ∆ 15 - - %

HT OSD level HTosd ABL = 6V

HT OSD output channel difference ∆ HTosd ∆ 15 - - %

∆ Vocff ∆ 10 - - %

∆ Voc80 ∆ 10 - - %

OSD RGB output conditions

OSD RGB output conditions

RGB input = S1

03, 05 — 08: FFH

0D: 01H

OSD black conditions input

HTvideo = 20log(V

05 — 08: FFH

0D: 0FH

OSD white condition input

HTosd = 20log (V

htvideo/Vcff

htosd/Vocff

Min Typ Max

-6.0 -4.5 -3.0 dB

)

-7.0 -5.5 -4.0 dB

)

Value

5.4 6.4 7.4 Vpp

2.7 3.2 3.7 Vpp

Unit

11

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

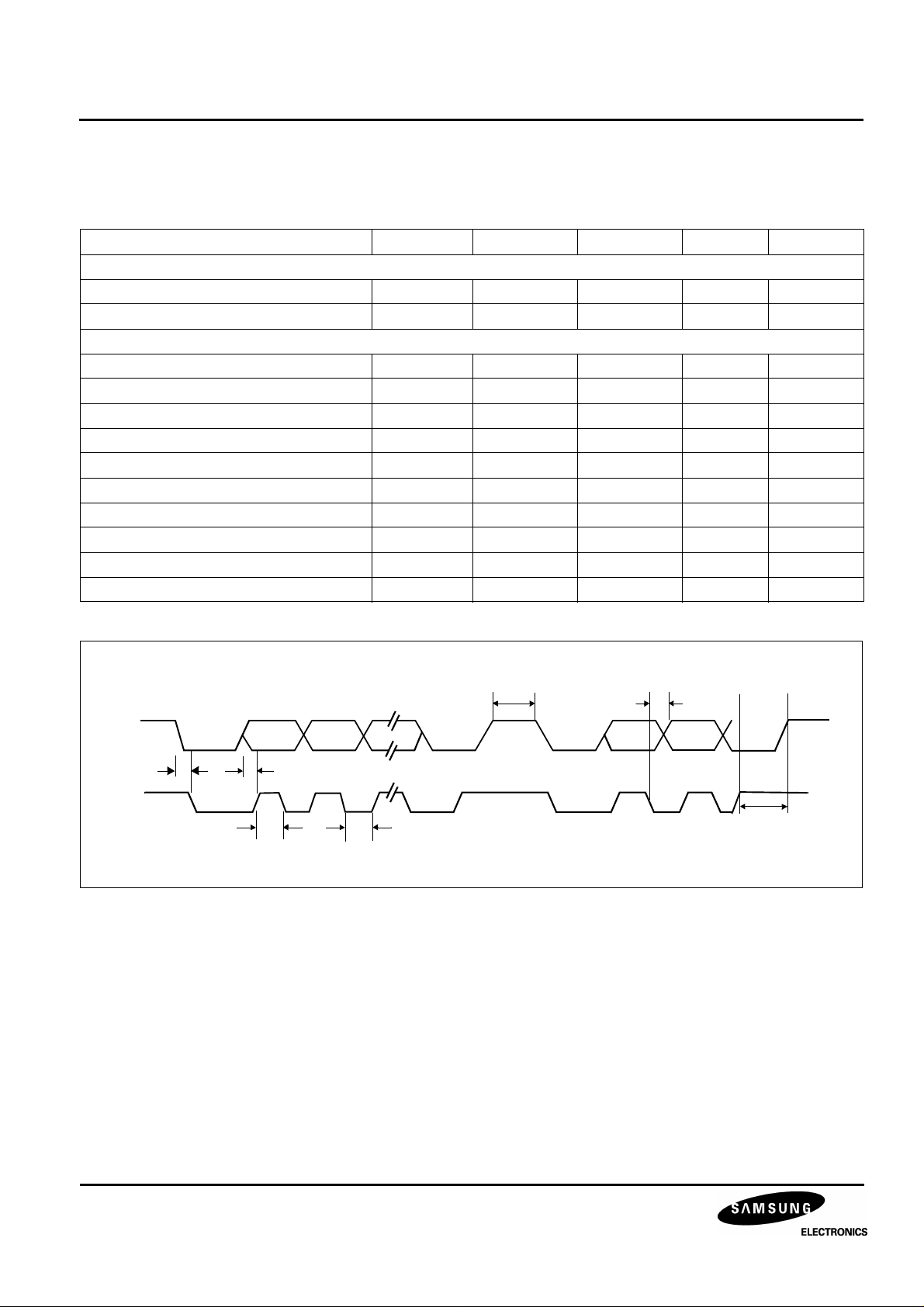

OPERATION TIMINGS

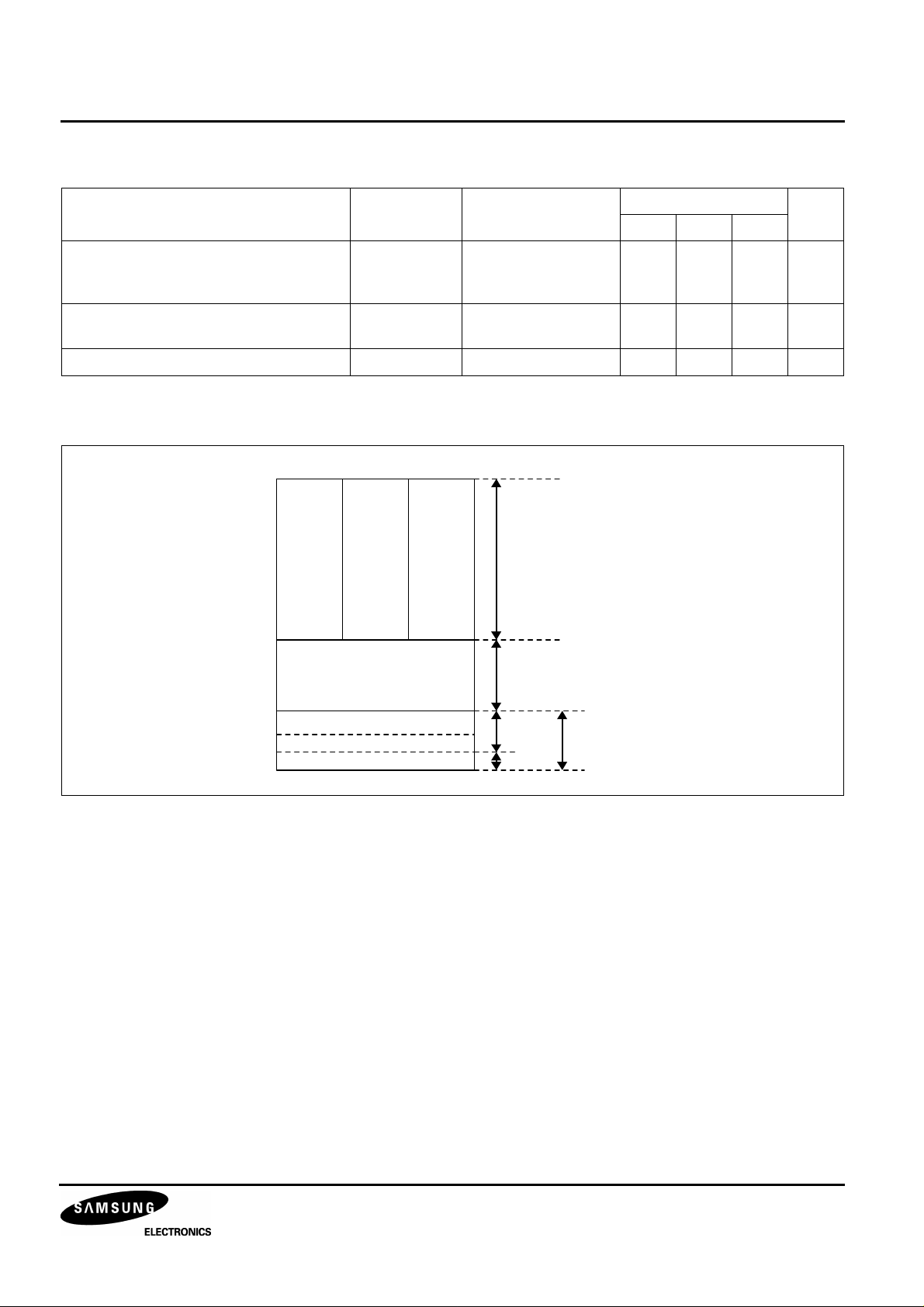

Table 8. Operation Timings

Parameter Symbol Min Typ Max Unit

Input Signal HFLB, VFLB

Horizontal flyback signal frequency f

Vertical flyback signal frequency f

I2C Interface SDA, SCL (Refer to Figure 3)

SCL clock frequency f

Hold time for start condition t

Set up time for stop condition t

Low duration of clock t

High duration of clock t

Hold time for data t

Set up time for data t

Time between 2 access t

Fall time of SDA t

Rise time of both SCL and SDA t

HFLB

VFLB

SCL

hs

sus

low

high

hd

sud

ss

fSDA

rSDA

- - 120 kHz

- - 200 Hz

- - 300 kHz

500 - - ns

500 - - ns

400 - - ns

400 - - ns

0 - - ns

500 - - ns

500 - - ns

- - 20 ns

- - - ns

SDA

SCL

ths

tsud

thigh

tss

tlow

Figure 3. I2C Bus Timing Diagram

thd

tsus

12

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

OSD PART DC ELECTRICAL CHARACTERISTICS

(Ta = 25 C, V

DDA DD

= 5V)

Parameter Symbol Typ Max

Supply voltage V 4.75 5.00 V

Supply current I

DD

Input voltage V 0.8V

IL

Output voltage

±1mA)

VCO input voltage

V

I

VCO

OH

OL

IL

0.8V - -

DD

- V

- 25

- V

SS

- V + 0.4 V

- 10 A

2.5

V

13

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

NOTES:

1. Absolute maximum rating indicates the limit beyond which damage to the device may occur.

2. Operating ratings indicate conditions for which the device is functional but do not guarantee specific performance limits.

For guaranteed specifications and test conditions, see the electrical characteristics. The guaranteed specifications apply

only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under

the listed test conditions.

3. VCC supply pins 11, 13, and 22 must be externally wired together to prevent internal damage during VCC power on/off

cycles.

4. The supply current specified is the quiescent current for VCC1/VCC2 and VCC3 with RL = ∞, The supply current

for VCC2 (pin 22) also depends on the output load.

5. Output voltage is dependent on load resistor. Test circuit uses RL = 470Ω

6. Measure gain difference between any two amplifiers Vin = 700mVpp.

7. When measuring video amplifier bandwidth or pulse rise and fall times, a double sided full ground plane printed circuit

board without socket is recommended. Video amplifier 50MHz cross talk test also requires this printed circuit board. The

reason for a double sided full ground plane PCB is that large measurement variations occur in single sided PCBs.

8. Adjust input frequency from 10MHz (AV max reference level) to the -3dB frequency (f -3dB).

9. Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation.

Terminate the undriven amplifier inputs to simulate generator loading. Repeat test at fin = 50MHz for cross talk 50MHz.

10. A minimum pulse width of 200 ns is guaranteed for a horizontal line of 15kHz. This limit is guaranteed by design. if a lower

line rate is used a longer clamp pulse may be required.

11. During the AC test the 4V DC level is the center voltage of the AC output signal. For example. If the output is 4Vpp the

signal will swing between 2V DC and 6V DC.

12. These parameters are not tested on each product which is controlled by an internal qualification procedure.

13. The conditions block’s 03, 04, 05... etc. signify sub address’ 0F03, 0F04, 0F05... etc.

14. Sub address 0F03, 0F05 — 0F07: FFH

0F04, 0F08 — 0F0C: 80H

RGB input = S1,

When the ABL input voltage is 0V, the R/G/B’s output voltage is VR/VG/VB and uses the formula ABLR = 20log (VR/V

15. OSD TST mode = High, CLP operation off,

RGB input = S5 (frequency sweep),

RGB input clamp cap = 2.1V DC,

RGB clamp cap (pin 23/20/17) = Vcap voltage (7.0V),

S5’s frequency 1MHz → 130MHz sweep, -3dB point = 20log (V

130MHz/V1MHz

)

03, 05 — 07: FFH

04, 08 — 0C: 80H

0F: 80H

16. OSD TST mode = High, CLP operation off,

RGB input clamp cap = 2.1V DC,

RGB clamp cap (pin 23/20/17) = Vcap voltage (7.0V),

03, 05 — 07: FFH

04, 08 — 0C: 80H

0F: 80H

R input = S5 (50MHz)

CT_50M = 20log (V

outG/VoutR

) or 20log (V

outB/VoutR

)

17. OSD TST mode = High, CLP operation off,

RGB input clamp cap = 2.1V DC,

RGB clamp cap (pin 23/20/17) = Vcap voltage (7.0V),

03, 05 — 07: FFH

04, 08 — 0C: 80H

0F: 80H

R input = S5 (130MHz)

CT_150M = 20log (V

outG/VoutR

) or 20log (V

outB/VoutR

)

cffR

)

14

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

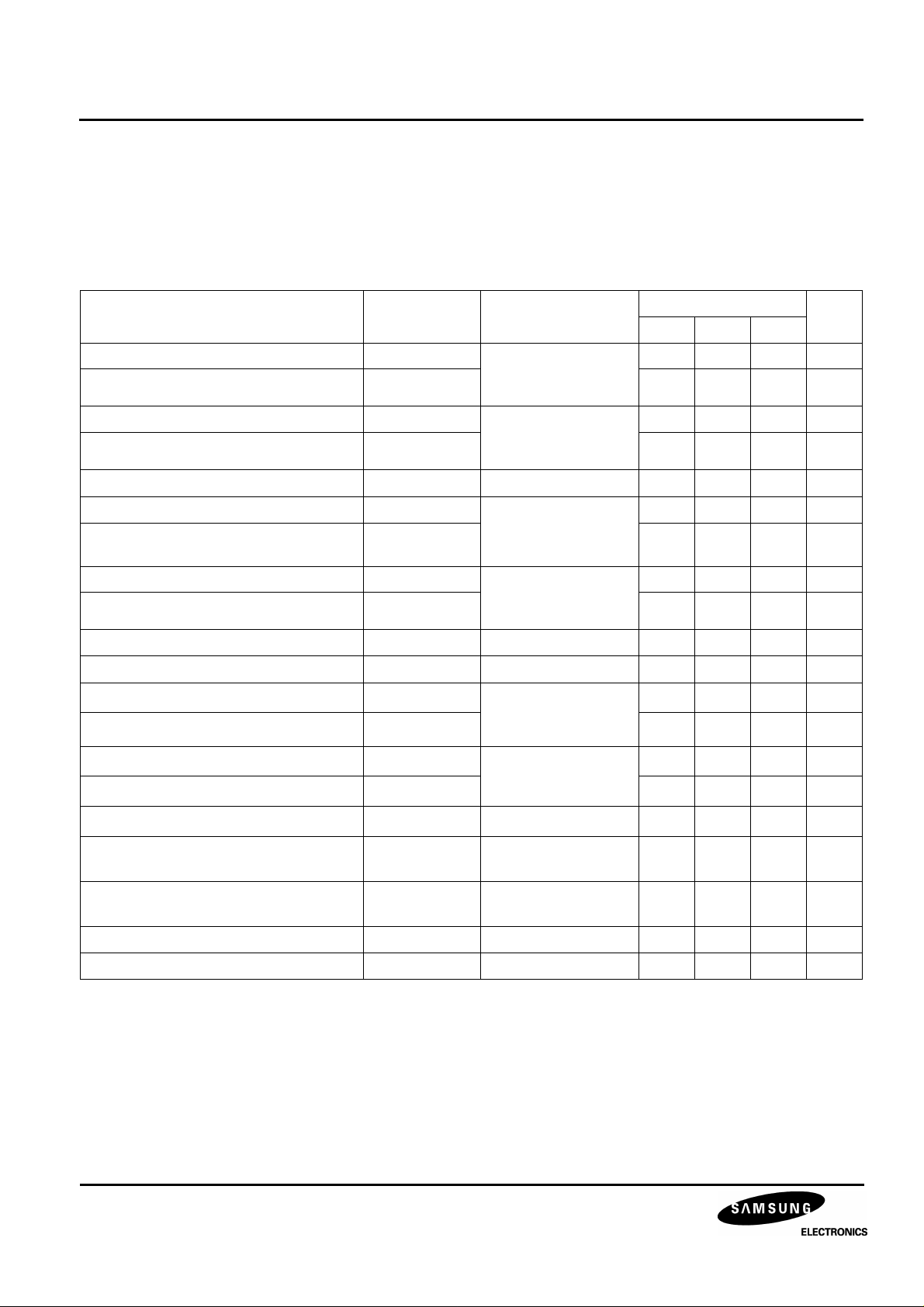

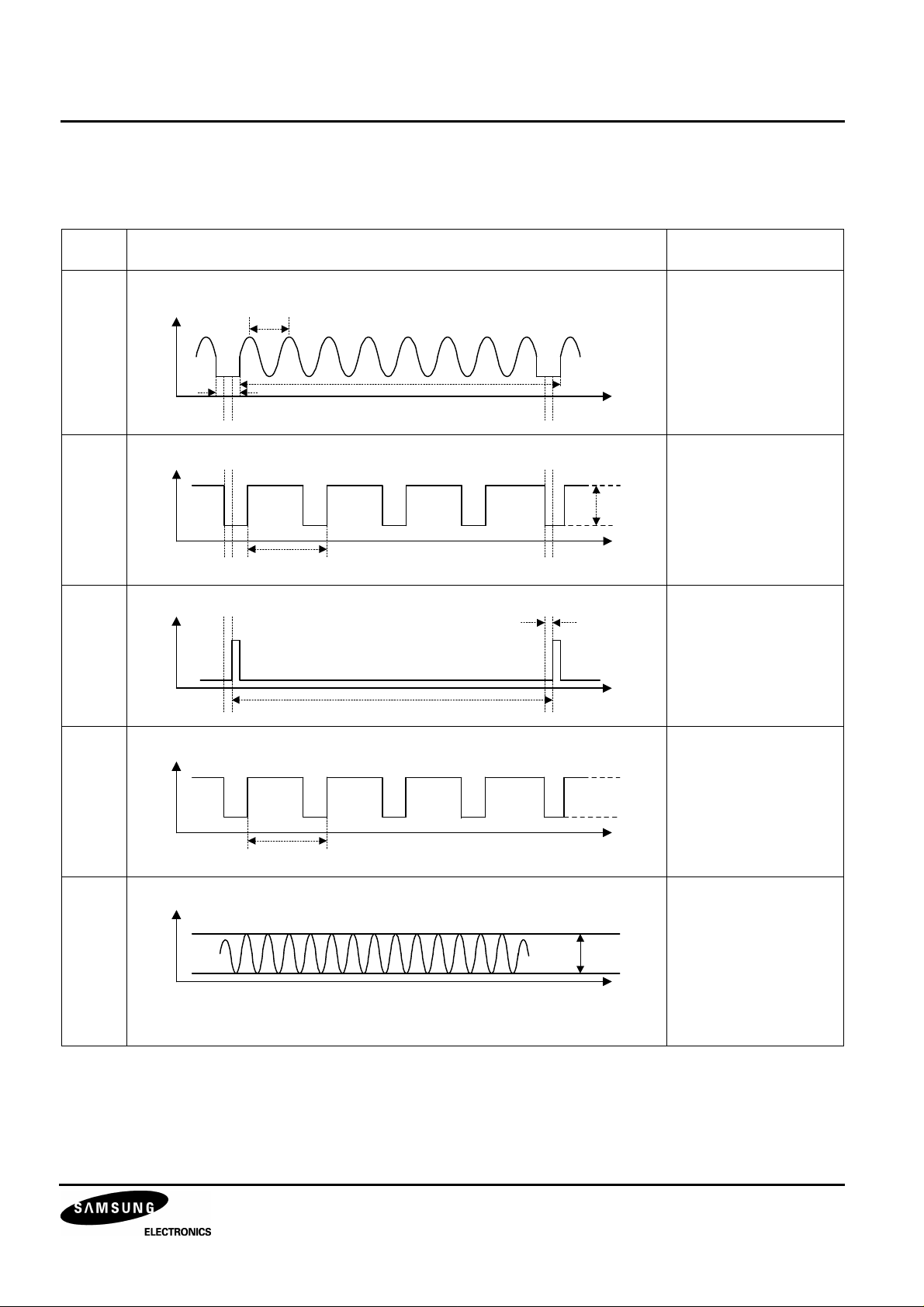

TEST SIGNAL FORMAT

Table 10. Test Signal Format

Signal

Name

S1 Video gain measurement

[V]

S2 Video Tr/Tf measurement

[V]

S3 HFLB (posi & nega.) input

[V]

Video

4uS

f = 200kHz

Input Signal Formal Signal Description

Video = 1MHz/0.7Vpp

Sync = 50kHz

Sync

[t]

f = 200kHz

V = 0.7Vpp

Duty = 50%

Duty = 50%

t = 2uS

0.7

Vpp

[t]

f = 50kHz

t = 2uS

V = 0V/5V

f = 50kHz

S4 OSD level measurement

[V]

[V]

f = 200kHz

S5 Crosstalk test

[V]

Duty = 50%

[t]

5V

0V

[t]

Vi

[t]

Blank Tr/Tf measurement

f = 50kHz

V = 0V/5V

Bandwidth measurement

1MHz/10MHz/50MHz/

Vref

130MHz

Vref = input clamp voltage

Vi = 0.7Vpp

• S1, S2 signal’s low level must be synchronized with the S3 signal’s sync. term.

• The input signal level uses the IC pin as reference.

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

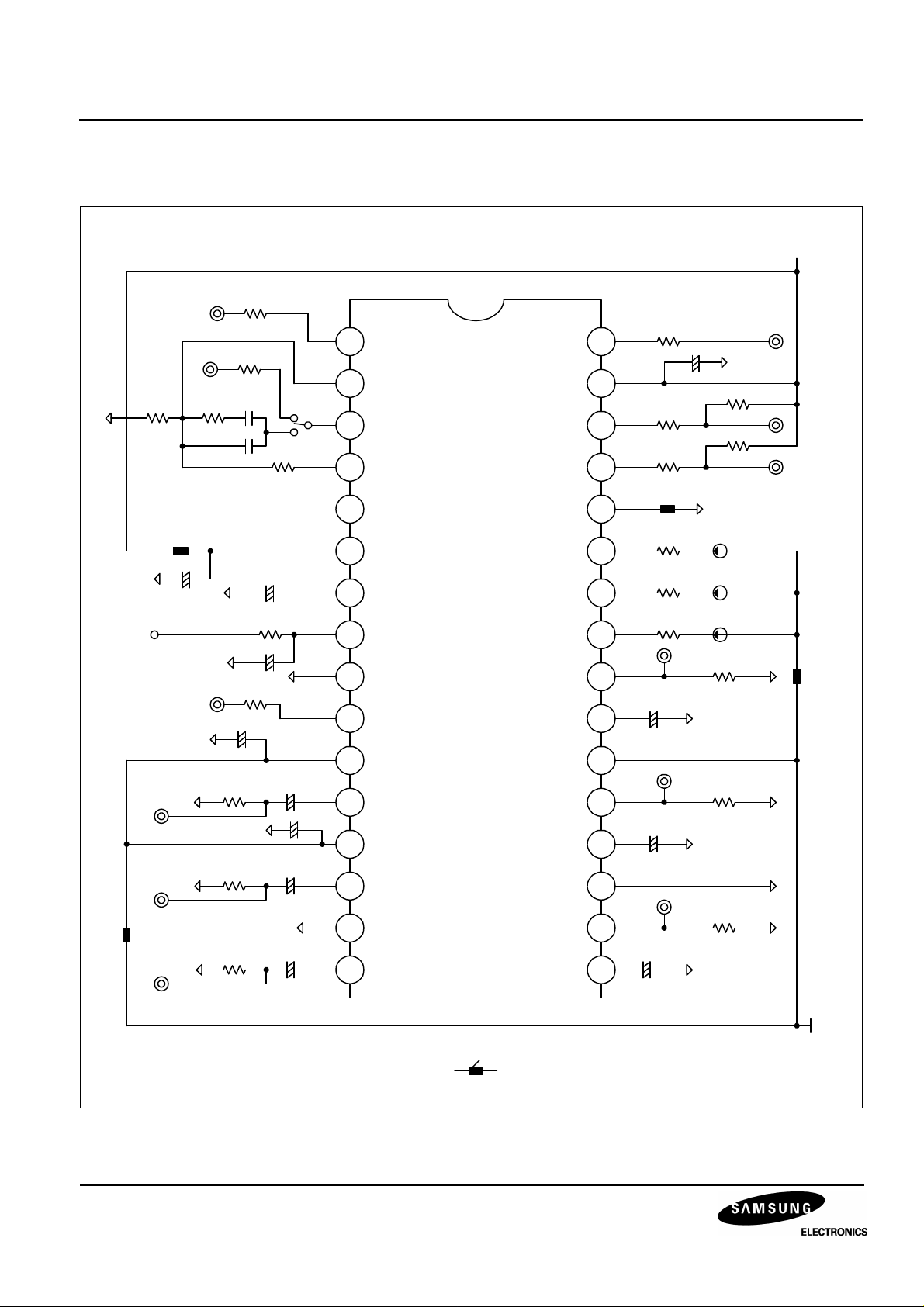

TEST CIRCUIT

VDD = 5.0V

ABL

1M

BNC1

Ω

100u

BNC6

BNC2

33pF

33

10uF5.6K

1u

100u

33

33

27K

1u

100

1

2

SW1

1

VFLB

2

VSSA

3

VCO_IN_P

4

VREF1

5

VREF

6

VDDA

7

CONT_CAP

8

ABL_IN

9

GND3

10

CLP_IN

S1D2514X01

KB2514

HFLB

VDD

SDA

SCL

VSS

RCT

GCT

BCT

ROUT

RCLP

32

31

30

29

28

27

26

25

24

23

0.1u

33

33

33

2K

2K

2K

100u

BNC3

4.7K

BNC5

4.7K

BNC5

470

BNC7

BNC8

BNC9

75

75

75

0.1u

0.1u

0.1u

100u

11

12

13

14

15

16

VCC3

RIN

VCC1

GIN

GND1

BIN

Magnetic core

Figure 4. Test Circuit

VCC2

GOUT

GCLP

GND2

BOUT

BCLP

22

470

21

0.1u

20

19

470

18

0.1u

17

VSS = 12.0V

16

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

FUNCTIONAL DESCRIPTIONS

DATA TRANSMISSION

The interface between S1D2514X01 and MCU follows the I2C protocol. After the starting pulse, the transmission

takes place in the following order: Slave address with R/W bit, 2-byte register address, 2-byte data, and stop

condition. an acknowledge signal is received for each byte, excluding only the start/stop condition. The 2-byte

register address is composed of an 8-bit row address, and an 8-bit column address. The order of transmission for

a 2-byte register address is 'Row address → Column address'. The 2 bytes of data is because S1D2514X01 has a

16-bit base register configuration. S1D2514X01's slave address is BAh. It is BBh in read mode, and BAh in write

mode.

• Address Bit Pattern for Display Registers Data

(a) row address bit pattern

R3 - R0: Valid data for row address

A15 A14 A13 A12 A11 A10 A9 A8

X X X X R3 R2 R1 R0

(b) Column address bit pattern

C4 - C0: Valid data for column address

A7 A6 A5 A4 A3 A2 A1 A0

X X X C4 C3 C2 C1 C0

X:Don't care bit

• Data Transmission Format

Start → Slave address → ACK → Row address → ACK → Column address → ACK

Data byte N → ACK → Data byte N+1 → ACK → Stop

Figure 5. Data Transmission Format at Writing Operation

Start → Slave address → ACK → Row address → ACK → Column address → ACK → Stop

Start → Slave address → ACK → Data byte N → ACK → Data byte N+1 → ACK → Stop

Figure 6. Data Transmission Format at Reading Operation

17

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

• SDA / SCL Signal At Communication

SCL

SDA

START IIC SLAVE ADDRESS ACK MSB ADDRESS ACK LSB ADDRESS ACK

R/W

A5 A4 A3 A2 A1 A0A6A7A9 A8A10A11A12A13A14A15

SCL

SDA

DATA BYTE N(MSB DATA)

D1 D0D2D3D4D5D6D7

D1 D0D2D3D4D5D6D7

ACK DATA BYTE N(MSB DATA) ACK STOPACK DATA BYTE N(LSB DATA)

D1 D0D2D3D4D5D6D7

Figure 7. SDA line and SCL line (Write Operation)

SCL

R/W

R/W

D15

D9

D8D10D11D12D13D14

ACK DATA BYTE N(LSB) ACK STOPACK DATA BYTE N(MSB)

SDA

START IIC SLAVE ADDRESS ACK MSB ADDRESS ACK LSB ADDRESS ACK

SCL

SDA

START IIC SLAVE ADDRESS

A5 A4 A3 A2 A1 A0A6A7A9 A8A10A11A12A13A14A15

D5D6D7

Figure 8. SDA line and SCL line (Read Operation)

...

...

STOP

D1 D0D2D3D4

18

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

MEMORY MAP

27 2829

Row

Row

Row

Row

Row

Row

Row 16

00 01

00

01

12

13

14

15

00 01 02 03

00 01 02 03 04 05

02

Character & Attribute Registers [Display RAM]

(30 x15 Character Display)

Frame Control Registers

Video-AMP Control Registers

Figure 9. Memory Map of Display Registers

The display RAM's address of the row and column number are assigned in order. The display RAM is composed of

3 register groups (character & attribute register, frame control register and V-AMP control register).

The display area in the monitor screen is 30 column × 15 row, so the related character & attribute registers are also

30 column × 15 row. Each register has a character address and characteristics corresponding to the display

location on the screen, and one register is composed of 16 bits. The lower 8 bits select the font from the 256 ROM

fonts, and the upper 8 bits give font characteristics to the selected font.

The frame control registers are in the 16th row. It controls OSD's display location, character height and scroll in

units of frame.

The V-AMP control registers are also located in the 17th row.

19

Preliminary

Character & Attribute Register: Row00 ~ 14, Column00 ~ 29

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

REGISTER DESCRIPTION

F E D C B A 9 8 7 6 5 4 3 2 1 0

Blink SHA RB RG RR CB CG CR C7 C6 C5 C4 C3 C2 C1 C0

CTL1 CTL0

Character AttributeExtended Code

Character Code (256 fonts)

Frame Control Register 0: Row15, Column00

F E D C B A 9 8 7 6 5 4 3 2 1 0

- - - - - - -

FullW EX-EN BGEN ScrEN ScrT BliEN BliT Erase EN

Frame Control Register 1: Row15, Column01

F E D C B A 9 8 7 6 5 4 3 2 1 0

CP1 CP0 Fpll HF2 HF1 HF0 dot1 dot0 HPOL VPOL CH5 CH4 CH3 CH2 CH1 CH0

Character Height ControlPolarityPLL Control

Frame Control Register 2: Row15, Column02

F E D C B A 9 8 7 6 5 4 3 2 1 0

HP7 HP6 HP5 HP4 HP3 HP2 HP1 HP0 VP7 VP6 VP5 VP4 VP3 VP2 VP1 VP0

Vertical Start PosiotionHorizontal Start Posiotion

Frame Control Register 3: Row15, Column03

F E D C B A 9 8 7 6 5 4 3 2 1 0

Blink SHA RINT CINT

Blink SHA RINT CINT Blink SHA RINT CINT Blink SHA RINT CINT

CTL11

20

CTL10 CTL01 CTL00

Preliminary

Video AMP Control Register: Row 16, Column 00 - 05

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Column 00

F E D C B A 9 8 7 6 5 4 3 2 1 0

BRT7 BRT6 BRT5 BRT4 BRT3 BRT2 BRT1 BRT0 VC7 VC6 VC5 VC4 VC3 VC2 VC1 VC0

Contrast ControlBrightness Control

Column 01

F E D C B A 9 8 7 6 5 4 3 2 1 0

GSB7 GSB6 GSB5 GSB4 GSB3 GSB2 GSB1 GSB0 RSB7 RSB6 RSB5 RSB4 RSB3 RSB2 RSB1 RSB0

R SUB Contrast ControlG SUB Contrast Control

Column 02

F E D C B A 9 8 7 6 5 4 3 2 1 0

OSD7 OSD6 OSD5 OSD4 OSD3 OSD2 OSD1 OSD0 BSB7 BSB6 BSB5 BSB4 BSB3 BSB2 BSB1 BSB0

B SUB Contrast ControlOSD Contrast Control

Column 03

F E D C B A 9 8 7 6 5 4 3 2 1 0

GWB7 GWB6 GWB5 GWB4 GWB3 GWB2 GWB1 GWB0 RWB7 RWB6 RWB5 RWB4 RWB3 RWB2 RWB1 RWB0

R Cut-off ControlG Cut-off Control

Column 04

F E D C B A 9 8 7 6 5 4 3 2 1 0

CUT7 CUT6 CUT5 CUT4 CUT3 CUT2 CUT1 CUT0 BWB7 BWB6 BWB5 BWB4 BWB3 BWB2 BWB1 BWB0

B Cut-off Control Cut-off Brightness Control

Column 05

F E D C B A 9 8 7 6 5 4 3 2 1 0

CLPS CLPP BLKP CS2 CS1 HG3 HR3 HB3 SB HG2 HR2 HB2 HG1 HR1 HB1 HT

’ - ’ ; Don’t care bit

Figure 10. Register Description

21

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Table 11. Register Description

Registers Bits Description

Character &

Attribute Registers

(Row 00 ~ 14,

Column 00 ~ 29)

C7 — C0

(Bit 7 — 0)

CB, CG, CR

(Bit A — 8)

RB, RG, RR

(Bit D — B)

SHA / CTL0

(Bit E)

Blink / CTL1

(BIt F)

Character code address

This is the address of 256 ROM fonts.

Character color

The character color is chosen from 16 colors using these 3 bits and the

frame control register 3’s CINT bit.

Raster color is determined by these bits.

The raster color is chosen from out of 16 colors using these 3 bits and the

frame control register 3’s RINT bit.

Character shadowing / CTL0(Extended Code)

If you set the frame control register 0’s EX-EN bit to '0', this bit carries out

character shadowing feature.( If SHA bit is '1', the character shadowing is

shown)

If you set the frame control register 0’s EX-EN bit to '1', this bit is used for

extended code.

Character blinking / CTL1(Extended Code)

If you set the frame control register 0’s EX-EN bit to '0', this bit carries out

character blinking feature.( If Blink bit is '1', the character blinking feature is

shown)

If you set the frame control register 0’s EX-EN bit to '1', this bit is used for

extended code.

If you set the Frame Control Register 0’s 'EX-EN' bit as '1', the Character & Attribute Register’s 'SHA' and 'Blink'

bits are used to call the Extended Code.

In other words, the combination of SHA and Blink bits can call four kind Extended Code 'CTL00', 'CTL01',

'CTL10' and 'CTL11', the CINT, RINT, SHA and Blink features can be carried out in a unit of character fonts.

22

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Table 11. Register Description (Continued)

Registers Bits Description

Frame Control

Registers - 0

(Row15,

Column00)

EN

(Bit 0)

Erase

(Bit 1)

OSD enable

OSD is enabled when this bit is '1'. In other words, if this bit isn't '1'OSD is

not output inspite of writing control data. We recommend that you enable

the OSD after setting the control registers (such as the character & attribute

register) because of video and OSD output timing.

RAM erasing

If this bit is '1', the RAM data (character & attribute registers) is erased. The

time spent in carrying out this operation is called erasing time, which can be

calculated as follows.

Erasing time = RAM clock × 480 (RAM cell no.)

RAM clock = 12 dot clock

Dot clock = 1/(dot frequency)

Dot frequency = Horizontal frequency × resolution (mode)

Therefore, the maximum erasing time value is:

BliT

(Bit 2)

BliEN

(Bit 3)

ScrT

(Bit 4)

ScrEN

(Bit 5)

BGEN

(Bit 6)

EX-EN

(Bit 7)

FullW

(Bit 8)

(Erasing Time)

= (12 × 480) / (15k × 320) = 1.2ms

MAX

Blink time control

If this bit is '1', blink time is 0.5sec, and if not, 1sec.

Blinking enable

Blinking effect is controlled by this bit.

If this bit is ’1’, blinking effect is enabled.

If this bit is '0', a full OSD screen blinking effect is disabled.

Scroll time control

If this bit is '1', scroll time is 0.5sec, and if not, 1sec.

Scroll enable

Scrolling effect is controlled by this bit. If this bit is '1', scrolling effect is

enabled. You must remember that scrolling can be turned on/off only when

OSD is enabled/disabled.

Back ground enable

If the BGEN bit is '1' and the raster color is black, the raster is transparent.

That is, the video back ground is shown. If not, the OSD raster covers the

video’s back ground. Refer to other color effect.

Extended code enable

If the EX-EN bit is '1', the Character & Attribute register’s Blink, SHA bits

carry out Extended Code features instead of Blink and SHA features.

Full white pattern enable

If the FullW bit is '1', the full white pattern is displayed in the screen.

23

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Table 11. Register Description

Registers Bits

Frame Control

Registers - 1

CH5 — CH0 Character height control

While the purpose of VZ[1:0] (vertical character height) is to control the

Column01)

to output OSD of a uniform size even if the resolution changes. If you adjust

the value in the range of CH = 18 ~ CH = 63, each line's repeating number

line is repeated. For more information on repeating number selection, refer

to character height.

Polarity of vertical fly back signal

(Bit 6)

words, this bit is set to '1' if active high, and '0' if active low.

HPOL Polarity of horizontal fly back signal

If this bit is '1', HFLB's polarity is positive, and if '0', it is negative. In other

dot1, dot0

(Bit 9, 8)

Dot1 Dot0

0 0

0 1

1 0

1 1

As shown above, the number of dots per horizontal line is decided by a

combination of these two bits.

Horizontal frequency

(Bit C — A)

This is related to the selection of DOT[1:0], so you can't numerically

express the frequency range with only the HF[2:0] selection. For more

FPLL

(Bit D) If this bit is '1', the OSD_PLL block's VCO operates at full range (4.8MHz -

96MHz). If it is '0', it operates within the region decided by the HF bit [C:A]

the high region, you may set the FPLL bit to '1'.

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Table 11. Register Description (Continued)

Registers Bits Description

Frame Control

Registers - 1

(Row15,

Column01)

The purpose of bits 'HPOL', and 'VPOL' is to provide flexibility when using the S1D2514X01 IC. No matter which

polarity you choose for the input signal, the IC will handle them identically, so you can select active high or active

low according to your convenience.

CP1, CP0

(Bit F, E)

Charge pump output current control

This is the PLL block's internal phase detector output status, converted into

current. Refer to PLL control.

CP1 CP0 Charge Pump Current

0 0 0.50 mA

0 1 0.75 mA

1 0 1.00 mA

1 1 1.25 mA

The output is decided by the combination of these two bits.

25

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Tabel 4. Register Description (Continued)

Registers Bits Description

Frame Control

Registers - 2

(Row 15,

Column 02)

Frame Control

Registers - 3

(Row 15,

Column 03)

VP7 — VP0

(Bit 7 — 0)

HP7 — HP0

(Bit F — 8)

CTL 00

(Bit 3 — 0)

CTL 01

(Bit 7 — 4)

CTL 10

(Bit B — 8)

Vertical start position control ( = VP[7:0] × 4)

Signifies top margin height from the V-Sync reference edge.

Horizontal start position control ( = HP[7:0] × 6)

Signifies delay of the horizontal display from the H-Sync reference edge to

the character's 1st pixel location.

Extended code

In case the EX-EN bit is '1' and the Character & Attribute register’s E and F

bits are '0', these bits have meanings.

If you set the CINT(character color intensity) bit '1', the character color

intensity feature is carried out.

If you set the RINT(raster color intensity) bit '1', the raster color intensity

feature is carried out.

If you set the SHA(character shadowing) bit '1', the character shadowing

feature is carried out.

If you set the Blink(character blinking) bit '1', the character blinking feature

is carried out.

Extended code

In case the EX-EN bit is ’1’ and the Character & Attribute register’s E bit is

'1' and F bit is '0', these bits have meanings.

If you set the CINT(character color intensity) bit '1', the character color

intensity feature is carried out.

If you set the RINT(raster color intensity) bit '1', the raster color intensity

feature is carried out.

If you set the SHA(character shadowing) bit '1', the character shadowing

feature is carried out.

If you set the Blink(character blinking) bit '1', the character blinking feature

is carried out.

Extended code

In case the EX-EN bit is '1' and the Character & Attribute register’s E bit is

'0' and F bit is '1', these bits have meanings.

If you set the CINT(character color intensity) bit '1', the character color

intensity feature is carried out.

If you set the RINT(raster color intensity) bit '1', the raster color intensity

feature is carried out.

If you set the SHA(character shadowing) bit '1', the character shadowing

feature is carried out.

If you set the Blink(character blinking) bit '1', the character blinking feature

is carried out.

26

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Tabel 4. Register Description (Continued)

Registers Bits Description

Frame Control

Registers - 3

(Row 15,

Column 03)

CTL 11

(Bit F — C)

Extended code

In case the EX-EN bit is '1' and the Character & Attribute register’s E and F

bits are '1', these bits have meanings.

If you set the CINT(character color intensity) bit '1', the character color

intensity feature is carried out.

If you set the RINT(raster color intensity) bit '1', the raster color intensity

feature is carried out.

If you set the SHA(character shadowing) bit '1', the character shadowing

feature is carried out.

If you set the Blink(character blinking) bit '1', the character blinking feature

is carried out.

27

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Tabel 4. Register Description (Continued)

Registers Bits Description

V-AMP Control

Registers - 0

(Row 16,

Column 00)

V-AMP Control

Registers - 1

(Row 16,

Column 01)

V-AMP Control

Registers - 2

(Row 16,

Column 02)

V-AMP Control

Registers - 3

(Row 16,

Column 03)

V-AMP Control

Registers - 4

(Row 16,

Column 04)

VC7 — VC0

(Bit7 — 0)

BRT7 — BRT0

(BitF — 8)

RSB7 — RSB0

(Bit7 — 0)

GSB7 — GSB0

(BitF — 8)

BSB7 — BSB0

(Bit7 — 0)

OSD7 — OSD0

(BitF — 8)

RWB7 — RWB0

(Bit7 — 0)

GWB7 — GWB0

(BitF — 8)

BWB7 — BWB0

(Bit7 — 0)

CUT7 — CUT0

(BitF — 8)

The contrast adjustment is made by contrdling simultaneously the gain

of three internal variable gain amplifiers.

The contrast adjustment allows to cover a typical range of 38dB.

The brightness adjustment controls to add the same black level

(pedestal) to the 3-channel R/G/B signals after contrast amplifier.

R channel SUB contrast control.

The SUB contrast adjustment is used to adjust the white balance, and

the gain of each channel is controlled.

The SUB contrast adjustment allows you to cover a typical tange of

12dB.

G channel SUB contrast control.

The SUB contrast adjustment is used to adjust the white balance, and

the gain of each channel is controlled.

The SUB contrast adjustment allows you to cover a typical tange of

12dB.

B channel SUB contrast control.

The SUB contrast adjustment is used to adjust the white balance, and

the gain of each channel is controlled.

The SUB contrast adjustment allows you to cover a typical tange of

12dB.

The OSD contrast adjustment is made by contrdling simultaneously the

gain of three internal variable gain amplifiers.

The OSD contrast adjustment allows to cover a typical range of 38dB.

R channel cut-off control.

The cut-off adjustment is used to adjust the raster white balance.

G channel cut-off control.

The cut-off adjustment is used to adjust the raster white balance.

B channel cut-off control.

The cut-off adjustment B used to adjust the raster white balance.

The cut-off brightness adjustment is made by simultaneously controlling

the external cut-off current.

28

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Tabel 4. Register Description (Continued)

Registers Bits Description

V-AMP Control

Registers - 5

(Row 16,

Column 05)

HT

(Bit 0)

HG1 — HB1

(Bit3 — 1)

Video & OSD half tone enable.

If you set this bit to '1', the half tone function is on.

Then you can see the video signal & OSD raster.

HG1 — HB1 bits select OSD raster color 1 to be half tone.

To carry out half tone function, set the HT bit to '1'.

HG2 — HB2

(Bit6 — 4)

HG1 HR1 HB1

0 0 0 0 0 0 Black O

0 0 1 0 0 1 Blue

0 1 0 0 1 0 Red

0 1 1 0 1 1 Magenta

1 0 0 1 0 0 Green

1 0 1 1 0 1 Cyan

1 1 0 1 1 0 Yellow

1 1 1 1 1 1 White

HG2 ~ HB2 bits select OSD raster color 2 to be half tone.

To carry out half tone function, set the HT bit to '1'.

HG2 HR2 HB2

0 0 0 0 0 0 Black O

0 0 1 0 0 1 Blue

0 1 0 0 1 0 Red

0 1 1 0 1 1 Magenta

1 0 0 1 0 0 Green

1 0 1 1 0 1 Cyan

1 1 0 1 1 0 Yellow

1 1 1 1 1 1 White

OSD

G R B

OSD

G R B

Raster

Color 1

Raster

Color 2

POR

POR

SB

(Bit 7)

Soft blanking enable

If you set this bit '1', the R/G/B outputs go to GND.

29

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Tabel 4. Register Description (Continued)

Bits Description

HG3 — HB3

Registers - 5

(Row 16,

(BitA — 8) To carry out half tone function, set the HT bit to '1'.

HR3 HB3

G R

1 0 0 0 Black

1 1 0 1 Blue

1 0 1 0

1 1 0 1 Magenta

0 0 1 0 Green

0 0 1 0 Cyan

0 0 1 0 Yellow

1 1 1 1

Raster

Color 3

CS2 — CS1 Cut-off offset current control

CS2 CS1 POR

0 100µ

0 1 µA

0 0 A O

1 50 A

BLKP Polarity of horizontral fly back signal

If this bit is '0', HFLB’s polarity is negative, and if '1', it is positive.

Polarity of clamp pulse signal

(Bit E)

This bit has meaning only if the CLPS bit is set to '1'.

CLPS Clamp pulse generation enable

If this bit is '0', clamp signal is made using the HFLB signal, so there is

and if '1' you must supply external clamp signal.

30

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

VIDEO AMP PART ADDRESS MAP

Register sub address

Table 12. Video AMP Part Address Map

SUB

Address

F E D C B A 9 8 7 6 5 4 3 2 1 0

Function POR

[Hex]

1000 Brightness control Contrast control

1001 SUB contrast control (G) SUB contrast control (R)

1002 OSD contrast control SUB contrast control (B)

1003 Cut-off control (G) Cut-off control (R)

1004 Cut-off brightness control Cut-off control (B)

1005

CLPS CLPP BLKP CS2 CS1 HG3 HR3 HB3 SB HG2 HR2 HB2 HG1 HR1 HB1 HT

Contrast Register (SUB ADRS: 00H) (Vin = 0.7Vpp, bright: 80H, subcont: FFH)

Hex

B7 B6 B5 B4 B3 B2 B1 B0

Contrast (Vpp) Gain (dB) int. Value (Hex)

00 0 0 0 0 0 0 0 0 0 80 1 0 0 0 0 0 0 0 2.85 - O

FF 1 1 1 1 1 1 1 1 5.2 -

Increment/bit 0.0223

Value

[Hex]

8080

8080

8080

8080

8080

1800

Brightness Register (3-ch) (SUB ADRS: 00H) (cont: 80H, subcont: 80H)

Hex B7 B6 B5 B4 B3 B2 B1 B0 Brightness (Vpp) Int. Value (Hex)

00 0 0 0 0 0 0 0 0 0.2

80 1 0 0 0 0 0 0 0 1.5 O

FF 1 1 1 1 1 1 1 1 2.7

Increment/bit 0.01055

SUB Contrast Register (R/G/B-ch) (SUB ADRS: 01/02H)

(Vin = 0.7Vpp, bright: 40H, cont: FFH)

Hex B7 B6 B5 B4 B3 B2 B1 B0 SUB Contrast

(Vpp)

Gain

(dB)

Int. Value

(Hex)

00 0 0 0 0 0 0 0 0 80 1 0 0 0 0 0 0 0 - O

FF 1 1 1 1 1 1 1 1 -

Increment/bit

31

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

OSD Contrast Register (SUB ADRS: 02H) (VOSD = TTL, bright: 80H, subcont: 80H)

Hex B7 B6 B5 B4 B3 B2 B1 B0 OSD Contrast

(Vpp)

00 0 0 0 0 0 0 0 0 0 80 1 0 0 0 0 0 0 0 3.2 - O

FF 1 1 1 1 1 1 1 1 6.4 -

Increment/bit 0.025

Cut-Off Brightness Register (3-ch) (SUB ADRS: 04H)

Hex B7 B6 B5 B4 B3 B2 B1 B0 Cut-Off Brightness (µA) Int. Value (Hex)

00 0 0 0 0 0 0 0 0 0

80 1 0 0 0 0 0 0 0 100 O

FF 1 1 1 1 1 1 1 1 200

Increment/bit 0.781

Cut-Off Register (R/G/B-ch) (SUB ADRS: 03/04H)

(cont = 80H, subcont: 80H)

Hex B7 B6 B5 B4 B3 B2 B1 B0 Cut-Off EXT (µA) Int. Value (Hex)

00 0 0 0 0 0 0 0 0 0

80 1 0 0 0 0 0 0 0 300 O

FF 1 1 1 1 1 1 1 1 600

Increment/bit 2.344

Gain

(dB)

Int. Value

(Hex)

32

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

ADDRESSING

• ROM Fonts

S1D2514X01 provides 256 Rom fonts for displaying OSD Icons, which allows the use of multi-language OSD

Icons. Font $000 is reserved for blank data.

0 1 E F

$000 $001 $00E $00F

00

$010 $011 $01E $01F

01

Fonts

$0E0 $0E1 $0EE $0EF

0E

$0F0 $0F1 $0FE $0FF

0F

Figure 11. Composition of the ROM Fonts

33

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

COLORING

If you have an Intensity feature, the number of possible colors you can express becomes doubled. In other words,

the number of colors you can represent with three colors blue, green, and red is 8 ( = 23), but with the intensity

feature, it is 16 ( = 24).

• Character Color

Character color is assinged for each font, and the 4 components for expressing a color are listed below.

Blue Character & attribute register's CB bit[A]

Green Character & attribute register's CG bit[9]

Red Character & attribute register's CR bit[8]

Intensity If the EX-EN bit is '1' and the Frame Control Register 3 CTL’s CINT bit called by Character &

Attribute register’s Blink, SHA bits is '1', the character intensity feature is enabled.

• Raster Color

Blue Character & Attribute register's RB bit[D]

Green Character & Attribute register's RG bit[C]

Red Character & Attribute register's RR bit[B]

Intensity

According to the 'EX-EN', 'RINT' and 'CINT' bits setting, raster and character color intensity can be assigned in

units of character.

Address 000h is appointed as blank data. RAM's initial values are all 0, and all bits are written as 0 when you

erase the RAM, so blank data means the initial value. In other words, blank data means 'do nothing'. You don't

need to write any data for the space font, except for 000h. It just needs to be an undotted area.

If the EX-EN bit is '1' and the Frame Control Register 3 CTL’s RINT bit called by Character &

Attribute register’s Blink, SHA bits is '1', the RASTER intensity feature is enabled.

Notes for When Making S1D2514X01 Fonts

34

Preliminary

• Other Color Effet

The Frame Control Register 0 'BGEN' bit's function is shown in the Figure below. If you set the 'BGEN' bit as '0'

after selecting A's raster color as black, the raster color black will be displayed. But if you set the 'BGEN' bit as

'1', after selecting B's raster color as black, the raster color black becomes invisible, so the video back ground

color (gray) is displayed as if it is the raster color.

BGEN bit = 0 & Rastor Color = Black

Black

A

Gray

Light Blue

Gray

BGEN bit = 1 & Rastor Color = Black

B

BGEN bit = 1 & Rastor Color = Light Blue

C

Figure 12. Color Effect by BGEN Bit

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

HEIGHT/POSITIONING

• Character Height

The purpose of CH[5:0] (Character Height) is to output a uniformly sized OSD even if the resolution changes.

To express a Character Height of CH = 18 ~ CH = 63 after receiving CH[5:0]'s input from the frame control

register-1, decide on each line's repeating number (Standard Height CH = 18) and repeat the lines.

The following Figure shows two examples of a height-controlled character. height control is carried out by

repeating some of the lines.

1

2

3

4

5

6

Standard Font(12*18)

7

8

9

10

11

12

13

14

15

16

17

18

Standard font

in high vertical resolution

Height-controlled font

: added

line

Standard Font(12*18)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

Standard font

in more higher vertical resolution

Figure 13. Character Height

: added

line

Height-controlled font

36

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

Repeating line-number can be found by the following formula.

[# of the repeating lines = 2 + N × M],

where N = 1, 2, 3, ... and M = round{14 ÷ (CH[5:0]-18)}.

1. If CH[5:0] is greater than 32 and less than or equal to 46 (32 < CH[5:0] ≤ 46), all lines are repeated once or

twice. The lines that are repeated twice are chosen by the following formula.

[# of the repeating lines = 2 + N × M],

where N = 1, 2, 3, ... and M = round {14 ≤ (CH[5:0]-32)}.

2. If CH[5:0] is greater than 46 and less than or equal to 60 (46 < CH[5:0] ≤ 60), all lines are repeated two or three

times. The lines that are repeated three times are chosen by the following formula.

[# of the repeating lines = 2 + N × M],

where N = 1, 2, 3, ... and M = round {14 ≤ (CH[5:0]-46)}.

3. If CH[5:0] is greater than 60 and less than or equal to 64 (60 < CH[5:0] ≤ 64), all Lines are repeated three or four

times. The lines that are repeated four times are chosen by the following formula.

[# of the repeating lines = 2 + N x M],

where N = 1, 2, 3, ... and M = round {14 ≤ (CH[5:0]-60)}.

CH's reference value is 18, and even if you input 0, it operates in the same way as when CH = 18. The repeating

line-number is limited to 16. If the M value is less than or equal to 1, all lines of the standard font are repeated more

than once.

Table 13. Repeating Line as Controlling by CH bits

Character Height Repeating Line

CH = 18 CH = 19 9

CH = 20, 21 6, 13

CH = 22 5, 11, 17

CH = 23 4, 9, 14, 19

CH = 24 3, 7, 11, 15, 19, 21

CH = 25, 26, 27 3, 7, 11, 13, 15, 19, 22

CH = 28 3, 6, 9, 12, 14, 18, 20, 23, 25

CH = 29 3, 6, 9, 11, 13, 15, 18, 21, 23, 25, 26

CH = 30 3, 6, 8, 10, 12, 14, 16, 18, 20, 22, 25, 27

CH = 31 2, 5, 7, 9, 11, 13, 15, 17, 21, 23, 25, 27, 28

CH = 32, 33, 34, 35 2, 5, 7, 9, 11, 13, 15, 18, 21, 23, 25, 27, 28, 29

CH = 36 CH = 37 18

37

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Table 13. Repeating Line as Controlling by CH bits

Character Height Repeating Line (Continued)

CH = 38, 39 12, 25

CH = 40 10, 20, 30

CH = 41 8, 16, 24, 32

CH = 42 6, 12, 18, 24, 30, 36

CH = 43, 44, 45 6, 12, 18, 24, 30, 36, 41

CH = 46 4, 8, 12, 17, 21, 25, 29, 33, 37, 41

CH = 47 4, 8, 12, 16, 20, 24, 28, 32, 36, 40, 44

CH = 48 4, 8, 12, 16, 20, 23, 26, 29, 33, 37, 41, 45

CH = 49 4, 8, 12, 16, 19, 22, 25, 28, 31, 35, 39, 43, 47

CH = 50, 51, 52, 53 4, 8, 12, 15, 18, 21, 24, 27, 30, 33, 36, 40, 44, 48

CH = 54 CH = 55 27

CH = 56, 57 18, 36

CH = 58 14, 28, 42

CH = 59 12, 23, 34, 45

CH = 60 9, 18, 26, 34, 43, 52

CH = 61, 62, 63 8, 16, 23, 30, 37, 44, 51

38

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

• Positioning

The frame control register-2's HP Bit [F:8] signifies delay of the horizontal display from the H-Sync reference

edge to the character's 1st pixel location, and is controlled by multiplying HP [F:8]'s range value by 6. Also, VP

bit[7:0] signifies the top margin height from the V-Sync reference edge, and is controlled by multiplying 4 to the

VP [7:0]'s range value. Refer to the Figure shown below.

(HFLB)

HP[7:0]

VP[7:0]

(VFLB)

OSD characters

30 columns (= 30 x 12 dots)

15 rows

(=15 x 18 lines)

Background Screen

Figure 14. Frame Composition with the OSD Characters

39

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

VISUAL EFFECTS

• Shadowing

The character shadow can only be black. Character shadow is making 1 pixel to the right and below the

character.

Shadowing

Figure 15. Character Shadowing

• Scrolling

Scrolling is slowly displaying or erasing a character from the top line to the bottom. This effect makes it look as

if 1 character line is scrolling up or down. asharacter line is scrolling up or down.

40

Figure 16. Scrolling

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

PLL CONTROL

• Introduction

PLL (Phase Lock Loop) is feedback controlled circuit that maintains a constant phase difference between a

reference signal and an oscillator output signal.

Generally, PLL is composed as follow Figure.

Reference Signal

PFD

(Phase Frequency Detector)

(Frequency Detector)

LF

(Loop Filter)

FD

VCO (Voltage

Controlled Oscillator)

Figure 17. Block Diagram of General PLL

- PFD (Phase Frequency Detector)

PFD compares the phase of the VCO output frequency, with the phase of a reference signal frequency output

pulse is generated in proportion to that phase difference.

- LF (Loop Filter)

LF smooths the output pulse of the phase detector and the resulting DC component is the VCO input.

- VCO (Voltage Controlled Oscillator)

VCO is controlled by loop filter output. The output of the VCO is fed back to the phase frequency detector

input for comparison which in turn controls the VCO oscillating frequency to minimize the phase difference.

- FD (Frequency Divider)

FD divides too much different frequency that is oscillated from the VCO to compare it with reference signal

frequency.

41

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

• PLL of the S1D2514X01

PLL is composed of the phase detector, charge pump, VCO, and N-divider as 4 sub-blocks.

HFLB (Pin32)

Detector

Div_out

Phase

Loop

Filter

CP_out

(Pin4)

Charge

Pump

N-Divider

CP0 CP1 DOT0 DOT1 HF0 HF1 HF2

# Composed of External Components

VCO_in

(Pin3)

VCO

Figure 18. Block Diagram of the PLL Built in S1D2514X01

VCO_out

The following is the description of the input/output signals.

- HFLB (Input)

Horizontal flyback signal is refrence signal of the PLL built in S1D2514X01.

The HFLB signal's frequency range is 15 ~ 90kHz, so the PLL block must be a wide range PLL that can cover

HFLB's entire frequency range.

> 4.2V

fHFLB

~2us

< 0.4V

- VCO (Input)

Error signal that passes through an external loop filter is input into VCO.

Operation voltage range is 1-4V. You can raise immunity towards external noise by lowering VCO

sensitivity. You can do this by making it have the maximum operation voltage range possible in the 5V power

voltage.

42

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

- DOT0, 1 (Input)

Mode control signal that controls the number of dots per line in the frame control register. There are 4 modes:

320, 480, 640, and 800 dots/line.

According to your choice of mode, the OSD_PLL block's N-Divider is controlled by one of ÷320, ÷480, ÷640, or

÷800 Divider.

- HF0, 1, 2 (Input)

The horizontal Sync frequency information is received from the micro controller through the frame control

registers-1's bit C-A.

- CP0, 1 (Input)

Charge Pump's output sourcing (or sinking) current control pin.

This control data is received through frame control registers-1's bits E-D.

- VCO_OUT (Output)

VCO output that becomes a system clock. It is the OSD R, G, B output signal's dot frequency, and the standard

signal for OSD's various timings.

Also, it is input into the N-Divider and makes a PLL loop

> 4.2V

< 0.4V

fclk

Rise Time : < 4nS

Fall Time : < 4nS

- CP_OUT (Output)

Charge Pump circuit's output. input into external loop filter. It becomes one of 3 states according to the standard

signal input into the phase detector (HFLB) and the divider output (Div_Out).

- HFLB Div_Out is lead: Current sink

- HFLB Lag: Current source

- HFLB In-Phase: High impedence

43

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

TUNNING FACTORS OF THE S1D2514X01 PLL

• PLL External Circuit

You may follow the recommendations for PCB art work and input/output signal characteristic improvement in

recommendation.

The external circuit that has the most influence on S1D2514X01 PLL block operation is pin 3 (VCO_IN) and pin

4 (CP_OUT)'s surrounding circuit. Refer to OSD PLL block.

3 4

C1

1M

C2

Ω

R1 R2

5

No Connection

(pin open)

Figure 19. PLL External Circuit

Because the PLL circuit is basically a feedback circuit, there are many components that influence the

characteristics. C1, C2, R1, and R2 do not have a localized effect.

As you can see, they are connected to the PLL control bits and influence the characteristics through their

complicated relationships. The main functions of the time canstant and their reference values are as follows.

Table 14. Main Function of Time Constant in PLL External Circuit

Time Canstant Recommended Value Main Function

C1 10uF Influences the damping ratio and controls the PLL

response time

R1 5.6KΩ(7.5KΩ) Same as C1

R2 27KΩ (or 33KΩ) Charge pump current adjustment

C2 33pF Removes ripple caused by R-C circuit

44

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

• PLL Control Bit

After configuring an external circuit using the recommended values, carry out programming using the

recommended values for frequency range and control bits given in the Table below.

Table 15. Recommend Values of PLL Control Bit

Register Set PLL Control Bit

Freq. Range CP1 CP0 FPLL HF2 HF1 HF0 DOT1 DOT0 Hex

Below 40kHz 0 0 0 0 1 0 1 1 0B

40 - 50kHz 1 0 0 1 0 0 1 1 93

50 - 70kHz 1 1 0 1 0 1 1 1 A7

Above 70kHz 1 1 0 1 1 1 1 1 AF

(Ref: 800 × 600, C1: 10uF, R1: 5.6K, R2: 27K, C2: 33pF)

• Locking Range

As you can see the figure below, it is 2.35V that measured voltage at pin-3 to optimize OSD quality. The proper

voltage range is 1.5 — 3.25V.

Locking Range

Ve (min)

1.625V

fmax

4V

3.25V

2.37V

1.5V

f0

0.75V

¥ð

-2

fC

fL

¥ð

2

Ve (max)

1.625V

Figure 20. Locking Range

45

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

• HF Bits Selection

HF bits is not selecting from out of 8 (23) steps uniformly, but selecting the step shown in figure below. In

example, at 800 mode, there are 5 steps that the frequency range is controlled by HF bits.

Table 16. HF Bits Selection

DIV DOT1 DOT0 HF2 HF1 HF0

320 0 0

480 0 1

640 1 0

800 1 1

After fixing time constants of the external circuit and PLL control bits except HF bits, if HF bits are stepped up, the

voltage measured at pin-3 drops. On the contrary, if HF bits are stepped down, the voltage rises.

The voltage measured at pin-3 don't change by changing CP bits.

• External Register at pin-4

The external register at pin-4 is the factor that changes greatly at PLL tunning. The initial value of this external

register value is decided as follows.

At first, the external register is replaced variable-register (about 50KΩ range).

and then, set the lowest PLL control bits at the lowest frequency allowed by set.

and then, change variable-register to be 2.35V that optimum voltage is locking.

and then, measure register value at this time.

also, set the highest PLL control bits at the highest frequency allowed by set.

and then, change variable-register to be 2.35V that optimum voltage is locking.

and then, measure register value at this time.

You may decide the average of these two registers' value to initial value.

46

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

The table below shows that other factors change as changing external register's value.

Fixing Factor Variable Factor Change Voltage Current Lock Range

Time constants of the external circuit

and PLL control bits except

Rext

↑ ↑ ↓ ↓ (shift)

↓ ↓ ↑ ↑ (shift)

47

Preliminary

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

RECOMMENDATION

5V Power Routing

S1D2514X01's OSD part power is composed of analog VDD and digital VDD. To eliminate clock noise influence in

the digital block, you need to separate the analog VDDA and digital VDD.

(BD102 use: Refer to Application Circuit )

12V Power Routing

Because S1D2514X01 is a wideband AMP of above 150MHz, 12V power significantly affects the video

characteristics. The effects from the inductance and capacitance are different for each board, and , therefore,

some tuning is required to obtain the optimum performance. The output power, VCC2, must be separated from

VCC1 and VCC3 using a coil, which is parallel-connected to the damping resistor.The appropriate coil value is

between 20uH - 200uH. Parallel-connected a variable resistor to the coil and control its resistance to obtain the

optimum video waveform.

(Moreover, BD103 can tune using a coil and variable resistor to obtain the optimum video waveform.

L103, R124, BD103: Refer to application circuit)

VCC1, VCC3 12V Power

Use a 104 capacitor and large capacitor greater than 470uH for the power filter capacitor.

12V Output Stage Power VCC2

Do not use the power filter capacitor.

5V Digital Power VDD

Don't use a coil or magnetic core to the VDD input. Make the power filter capacitor, an electric capacitor of greater

than 50uF, single and connect it to VSS, the digital GND.

Output Stage GND2

Care must be taken during routing because it ,as an AMP output stage GND, is an important factor of video

oscillation. R/G/B clamp cap and R/G/B load resistor must be placed as close as possible to the GND2 pin. GND2

must be arranged so that it has the minimum GND loop, which at one point must be connected to the main GND.

Digital GND VSS

When this is to be connected directly to the GND2, it can cause the OSD clock noise, so the loop connection

should be routed as far away as possible. If the OSD clock noise affects the screen, separate VSS GND from all

GND and connect it to the main board using a bead. Again, the bead connection point should be placed as far

away as possible to the GND2.

Analog Block

The PLL built in to S1D2514X01 is sensitive to noise due to the wide range PLL characteristics. Therefore, you

need to isolate the analog block in the following manner. First make a separate land for the analog block (pin2 pin6)'s ground, and connect it to the main ground through a 1MΩ resistor. The analog GND of both sides of a

double faced PCB must be separated from the main ground. (Separate pin 2's 5V analog GND, which is the GND

for OSD PLL, from the main and digital GNDs and connect it to the main GND using about 1MΩ resistor. GND for

pins 2 - 6 is the No. 2 VSSA GND.)

48

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

I2C Control Line (SCL, SDA Line)

I2C communication noise (noise generated in the OSD display pattern when data is transmitted in the I2C line) may

be generated because of an I2C control line that passes near the analog block. The I2C control lines near

S1D2514X01 must be separated from the analog block as much as possible.

Furthermore, the I2C bus interference can be prevented by inserting a series resistor in the line.

Horizontal Flyback Signal

Display jittering can be generated if the horizontal signal (HFLB) input to S1D2514X01 is not a clean signal.

We recommend a short path and shielded cable for obtaining a clean signal.

Generally, the input horizontal signal (HFLB) is generated by using a high voltage horizontal flyback signal. The

effect from the high voltage flyback signal can be reduced by separating the R115 and R117 GND, which

determines the flyback signal slice level, from the transistor GND, which generates the actual S1D2514X01 input

horizontal signal. Furthermore, the flyback signal sharpness must be maintained by minimizing the values of R115,

R116 and R117 resistors, which set the horizontal signal slice level. values.

(R115, R116, R117: Refer to application circuit )

HFLB Input Signal Generator

You can correct the circuit by reducing the resistors that sets the slice level of the horizontal signal in the HFLBgenerating circuit.

49

Preliminary

12_1V

12V

470uF

BD103

S1D2514X01 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

APPLICATION BOARD CIRCUIT

C117

R117

150

D102

R115

2K

1 3

Q102

2N3904

CN2

1N4148

1N4148

1N4148

6

RB01

RG01

75

RB02

75

CB02

104

16

BCLP

BOUT

17

18

CB02

104

RB03

470

RB15

47

RB04

CB08

100

270pF

14

C119

102

5V

SK101

WSP-401M

C126

C116

1nF

C118

330pF

R116

1N4148

1.8nF

1nF

10K

G1

12345678910111213

C123

103

C124

103

L101

100uH

R103

390

R118

R119

DR02

70V

DG02

6.3V

DB02

12V

R107

1K

R101

4.7K

R102

100

560

560

2

CN1

12345

1N4148

DR01

DG01

DB01

RR01

75

75

RG02

RR02

75

75

CR01

CG02

104

104

VCC3

RIN12VCC113GIN14GND115BIN

GOUT

GND2

GCLP

VCC222RCLP

19

20

21

CG02

104

RG03

470

RG15

47

RG04

CG08

100

270pF

12V

C109

1N4148

1N4148

C102

+

1uF

C112

+

1uF

10

11

7

8

ABL_IN

GND9CLP_IN

KB2514

ROUT

BCT25GCT

23

24

26

CR02

104

RR03

470

RR15

47

RR04

CR08

100

270pF

R123

VREF1

VREF5VDDA6CONT_CAP

VSS

SCL29SDA

RCT

27

28

C160

103

1M

C110

+

100uF

BD102

5V

R108

R109

27K

4

+

47uF

L103

5.6K

C113

C114

10uF

33pF

3

VFLB1VSSA2VCO_IN

C152

104

+

C103

HFLB

VDD

30

31

R124

220

27uH

C151

32

104

C128

104

5V

R114

470

CB05

RB12

2.2K

2N5401C-Y

6

7

9

8

BIN

GIN

RIN

LG01

0.15uH

VBB

DRIVER IC

GOUT

ROUT

BOUT

GND

VCC

1

2

5

3

4

RB08

RG08

56

CB07

CG07

56

37pF

37pF

RB14

RG14

75

75

LB01

0.15uH

C121

104

C108

+

47uF

70V

DB03

DG03

1SS244

1SS244

RR09

75K

RG09

75K

G_OUT

DR03

1SS244

+

+

CB04

CG04

1uF

1uF

RB09

75K

RB10

RG10

39

39

B_OUT

C106

C107

70V

DMS-200D

DMS-200D

DMS-200D

220uF

104

+

1SS244

1SS244

1SS244

12V

RR08

CR07

56

37pF

RR14

75

LR01

0.15uH

DB04

DG04

DR04

+

CR04

1uF

RR10

SKB01

39

SKG01

SKR01

R_OUT

CG05

104

RG12

2.2K

QG02

DMS-200D

RG11

100

RG20

4.7K

1 3

QG01

2

2N5551C-Y

CG05

104

2

13

RG13

82K

DG05

1N4148

SK102

C120

CR05

RR12

2.2K

2N5401C-Y

1nF

RR11

100

RR20

4.7K

1 3

QR01

2

2N5551C-Y

CR05

104

104

2

QR02

13

RR13

82K

DR05

1N4148

R104

390

RB11

100

RB20

4.7K

1 3

QB01

2

2N5551C-Y

CB05

104

104

2

QB02

2N5401C-Y

13

RB13

82K

DB05

1N4148

G2G2

Figure 21. Application Board Circuit

50

Preliminary

12_1V

12V

470uF

BD103

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS S1D2514X01

TYPICAL APPLICATION CIRCUIT

C117

R117

150

D102

R115

2K

1 3

Q102

2N3904

GND2

CN1

12345

1N4148

DR01

DG01

DB01

RR01

75

RG02

RR02

75

75

CR01

CG02

104

104

VCC311RIN12VCC113GIN14GND1

GOUT

GCLP

VCC222RCLP

19

20

21

CG02

104

RG03

470

RG15

47

12V

C109

1N4148

1N4148

C102

C112

+

+

1uF

1uF

10

7

8

ABL_IN

GND9CLP_IN

KB2514

ROUT

BCT25GCT

23

24

26

CR02

104

RR03

470

RR15

47

R123

103

1M

C110

+

100uF

BD102

5V

R108

3

VCO_IN

30

R124

5.6K

C113

C114

10uF

33pF

2

VFLB1VSSA

C152

104

+

C103

HFLB

VDD

31

220

27uH

C151

32

104

C128

104

5V

R114

470

R109

27K

4

5

VREF1

VREF

VDDA6CONT_CAP

VSS

SCL29SDA

RCT

27

28

C160

+

47uF

L103

CN2

1N4148

1N4148

1N4148

6

RB01

RG01

75

75

RB02

75

CB02

104

15

16

BIN

BCLP

BOUT

17

18

CB02

104

RB03

470

RB15

47

14

C119

102

5V

SK101

12345678910111213

C123

103

C124

103

L101

100uH

R103

390

DR02

70V

DG02

6.3V

DB02

12V

R107

1K

R101

4.7K

R102

100

WSP-401M

C126

C116

1nF

C118

330pF

R116

1N4148

1.8nF

1nF

G1

10K

R118

560

R119

560

2

CB05

RB12

2.2K

2N5401C-Y

6

7

9

8

BIN

GIN

RIN

G_OUT

VBB

DRIVER IC

GOUT

ROUT

BOUT

GND

VCC

1

2

5

3

4

RB14

RG14

75

75

C121

104

C108

+

47uF

70V

DB03

DG03

1SS244

DR03

1SS244

1SS244

+

+

CB04

CG04

1uF

1uF

RB09

75K

LB01

LG01

0.15uH

0.15uH

RB10

RG10

39

39

RR09

75K

RG09

75K

B_OUT

C106

C107

70V

DMS-200D

DMS-200D

DMS-200D

220uF

104

+

1SS244

1SS244

1SS244

12V

RR14

75

DB04

DG04

DR04

+

CR04

1uF

LR01

0.15uH

RR10

SKB01

39

SKG01

SKR01

R_OUT

CG05

RG12

2.2K

2N5401C-Y

104

QG02

DMS-200D

RG11

100

RG20

4.7K

1 3

QG01

2

2N5551C-Y

CG05

104

2

2N5401C-Y

13

RG13

82K

DG05

1N4148

SK102

C120

RR11

100

RR20

4.7K

1 3

QR01

2

2N5551C-Y

CR05

104

CR05

104

RR12

2.2K

2

QR02

13

RR13

82K

DR05

1N4148

R104

390

1nF

RB11

100

RB20

4.7K

1 3

QB01

2

2N5551C-Y

CB05

104

104

2

QB02

13

RB13

82K

DB05

1N4148

G2G2

Figure 22. Typical Application Circuit

51

Preliminary