Samsung S1D2147A01-A0B0 Datasheet

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS S1D2147A01

DEFLECTION PROCESSOR

42-SDIP-600

The S1D2147A01is a monolithic integrated circuit assembled

in a 42 pins shrunk dual in line plastic package.

The goal of this IC is to control all the functions related to the

horizontal and vertical deflection in multimodes or multisync

monitors.

FUNCTIONS

• Positive or Negative sync polarities

• Auto-sync horizontal processing

• H-PLL lock/unlock identification

• Auto-sync Vertical processing

• East/West signal processing block

• B+ controller

• Safety blanking output

ORDERING INFORMATION

Device Package Operation Temperature

FEATURES

(HORIZONTAL)

• Dual Pll concept

• Self-adaptative (30 to 70kHz)

• X-ray protection input

• DC adjustable duty-cycle

• Internal 1st PLL lock/unlock information

• Wide range DC controlled H-position

• ON/OFF switch (for PWR management)

• Two H-drive polarities

(VERTICAL)

• Vertical ramp generator

• 50 to 120Hz AGC Loop

• DC controlled V-amp, V-pos, S-amp & S-centring

• ON/OFF Switch

(B+ REGULATOR)

S1D2147A01-A0B0 42-SDIP 0 °C — 70 °C

(GENERAL)

• Accept Positive or Negative Horizontal &

Vertical sync polarities

• Separate H & V TTL input

• Safety blanking output

(E

WPCC

)

• Internal PWM generator for B+ current mode

step-up conveter

• DC adjustable B+ voltage

• Output pulse synchronised on horizontal frequency

• Internal MAX current limitation

• Vertical parabola generator with DC

• controlled keystone & amplitude

0

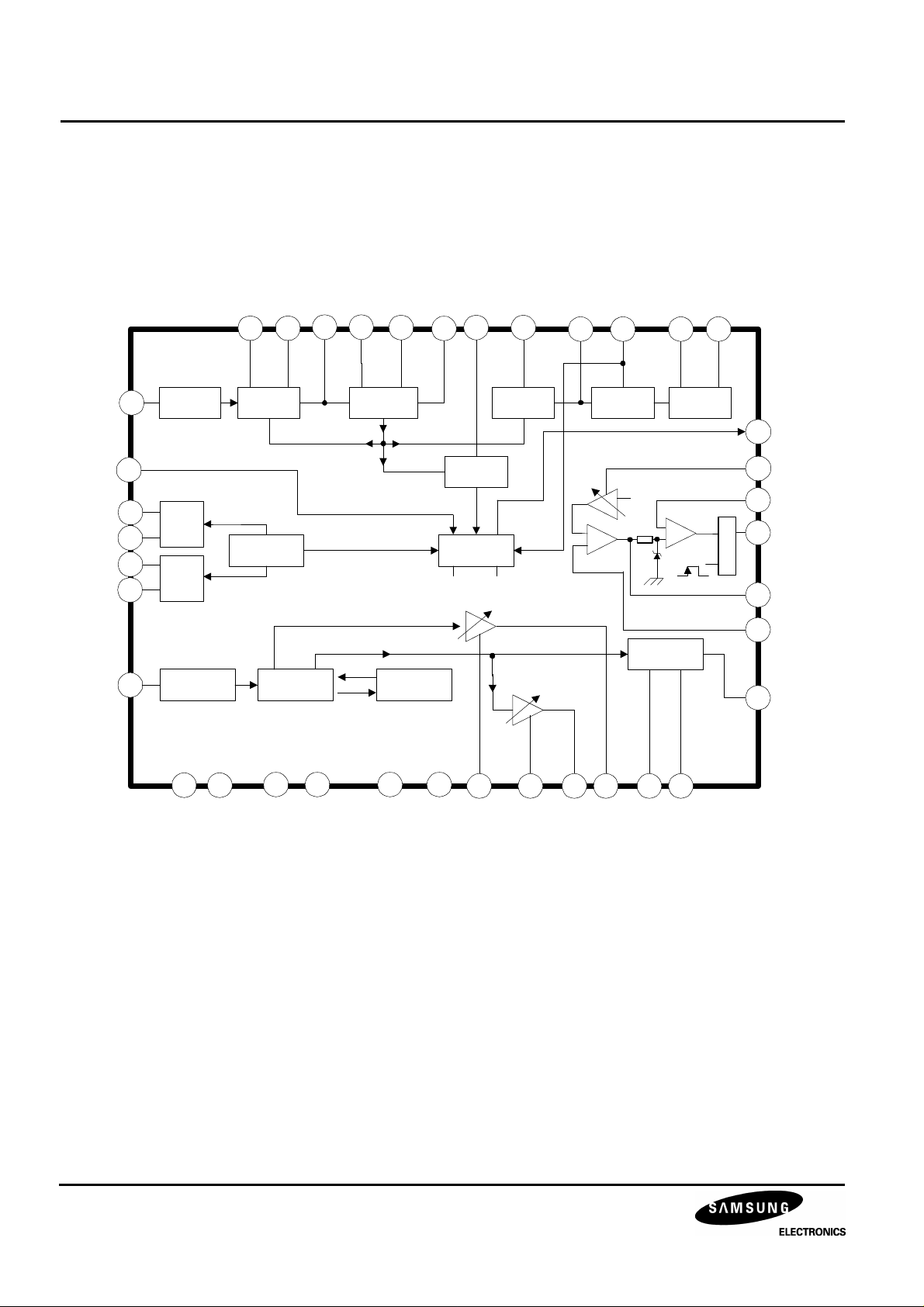

S1D2147A01 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

BLOCK DIAGRAM

R0

PLL1NHIB

35 15

H-POS

PLL1F

12 11

10

C0

FH-MIN

14

HLOCK-CAP

13 3

HFLY

PLL2C

H-DUTY

H-OUTEM

1 2 20 21

H-OUTCOL

HSYNC

XRAY-IN

HREF

HGND

VREF

VGND

VSYNC

16

26

24

34

17

INPUT

INTERFACE

5

H-VREF

4

V-VREF

INPUT

INTERFACE

19

GND

18

VCC

1st PHASE

COMP

BANDGAP

OSCILLATOR

VERTICAL

VCAP

VAGCCAP

VCO

CORRECTION

VS-CENT

S

2nd PHASE

COMP

LOCK

DETECT

+

SAFETY

PROCESSOR

VCC

OUTPUT

INHIBITION

282927 25

33 31 30 32 38 37

V-POS

VS-AMP

V-AMP

EA

-

VOUT

PHASE

SHAPER

DCOUT

V

V

REF

+

PARABOLA

GENERATOR

KEYST

-

OUTPUT

BUTTER

EW-AMP

23

SBLKOUT

39

B+ADJ

42

R

22

S

41

40

36

I

SENSE

B+OUT

COMP

REGIN

E/WOUT

1

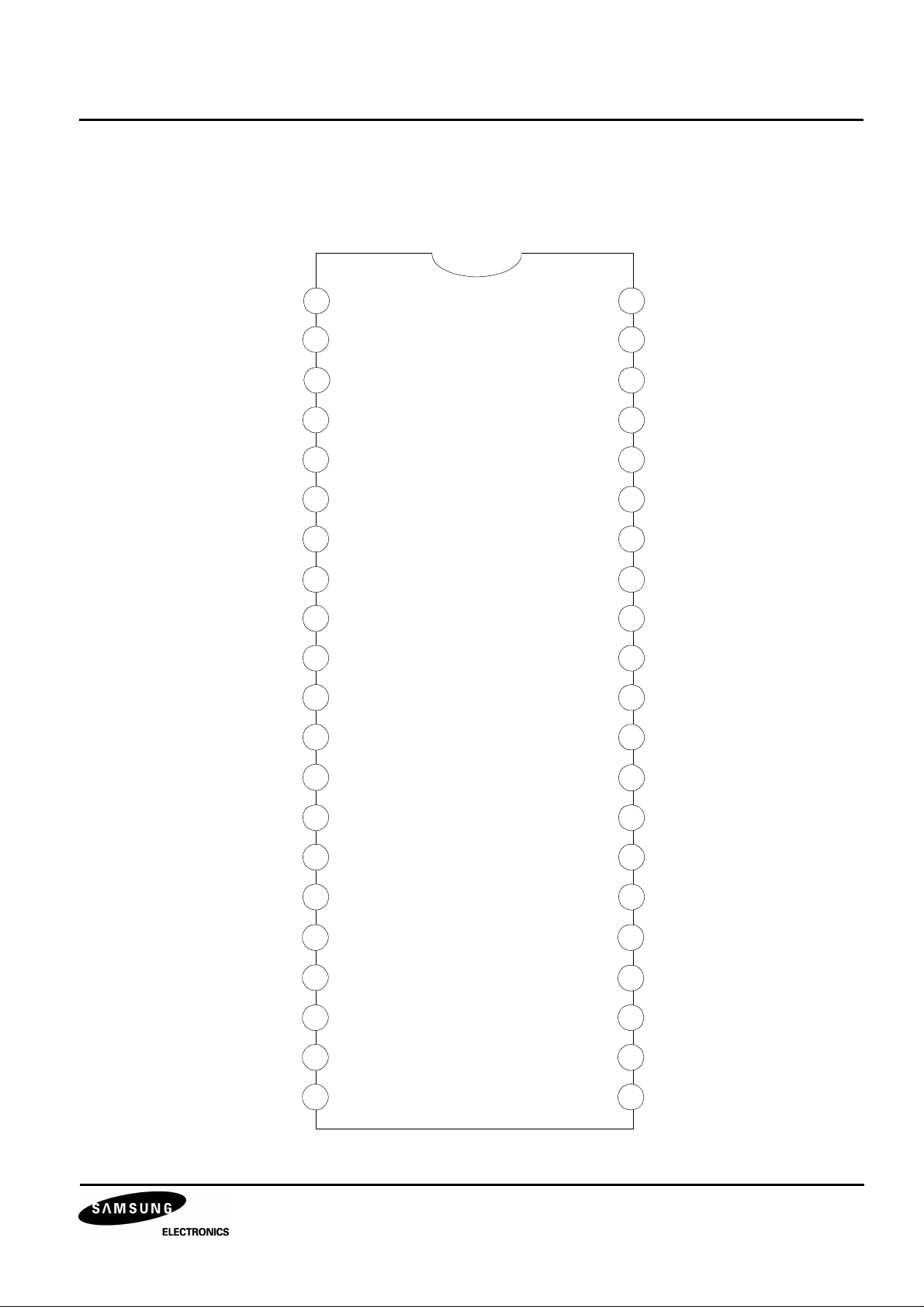

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS S1D2147A01

PIN CONFIGURATIONS

1

2

4

5

6

7

8

9

10

11

12

3

PLL2C

H-DUTY

HFLY

HGND

HREF

NC

NC

NC

NC

C0

R0

PLL1F

I-SENSE

COMP

REGIN

B+ ADJ

KEYST

E/W-AMP

E/WOUT

PLL1-INHIB

VSYNC

V-POS

V-DCOUT

S1D2147

V-AMP

42

41

40

39

38

37

36

35

34

33

32

31

13

HLOCK-CAP

14

FH-MIN

15

H-POS

16

XRAY-IN

17

HSYNC

18

VCC

19

GND

20

H-OUTEM

21

H-OUTCOL

VOUT

VS-CENT

VS-AMP

VCAP

VREF

VAGCCAP

VGND

SBLK-OUT

B+ OUT

30

29

28

27

26

25

24

23

22

2

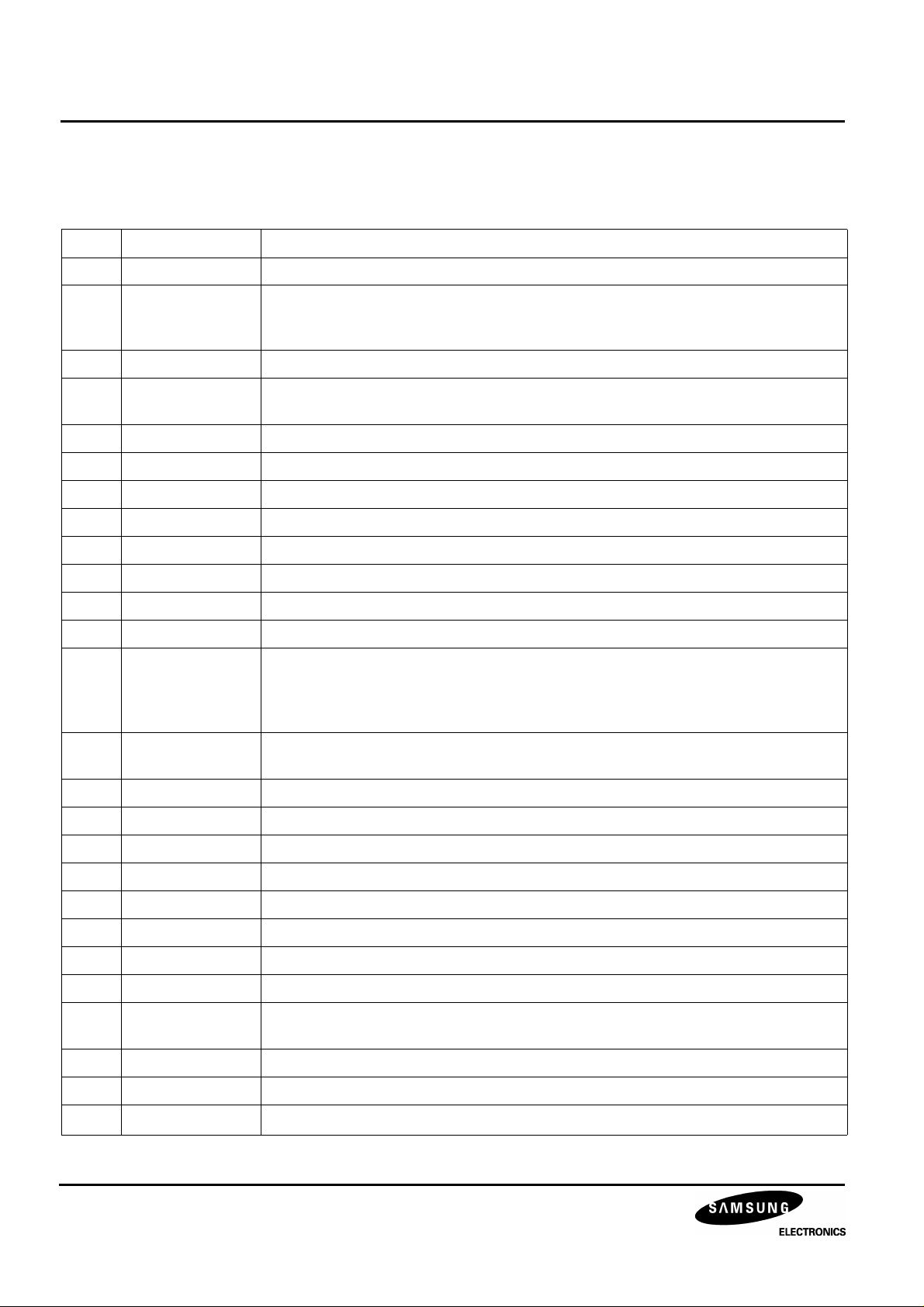

S1D2147A01 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

PIN DESCRIPTION

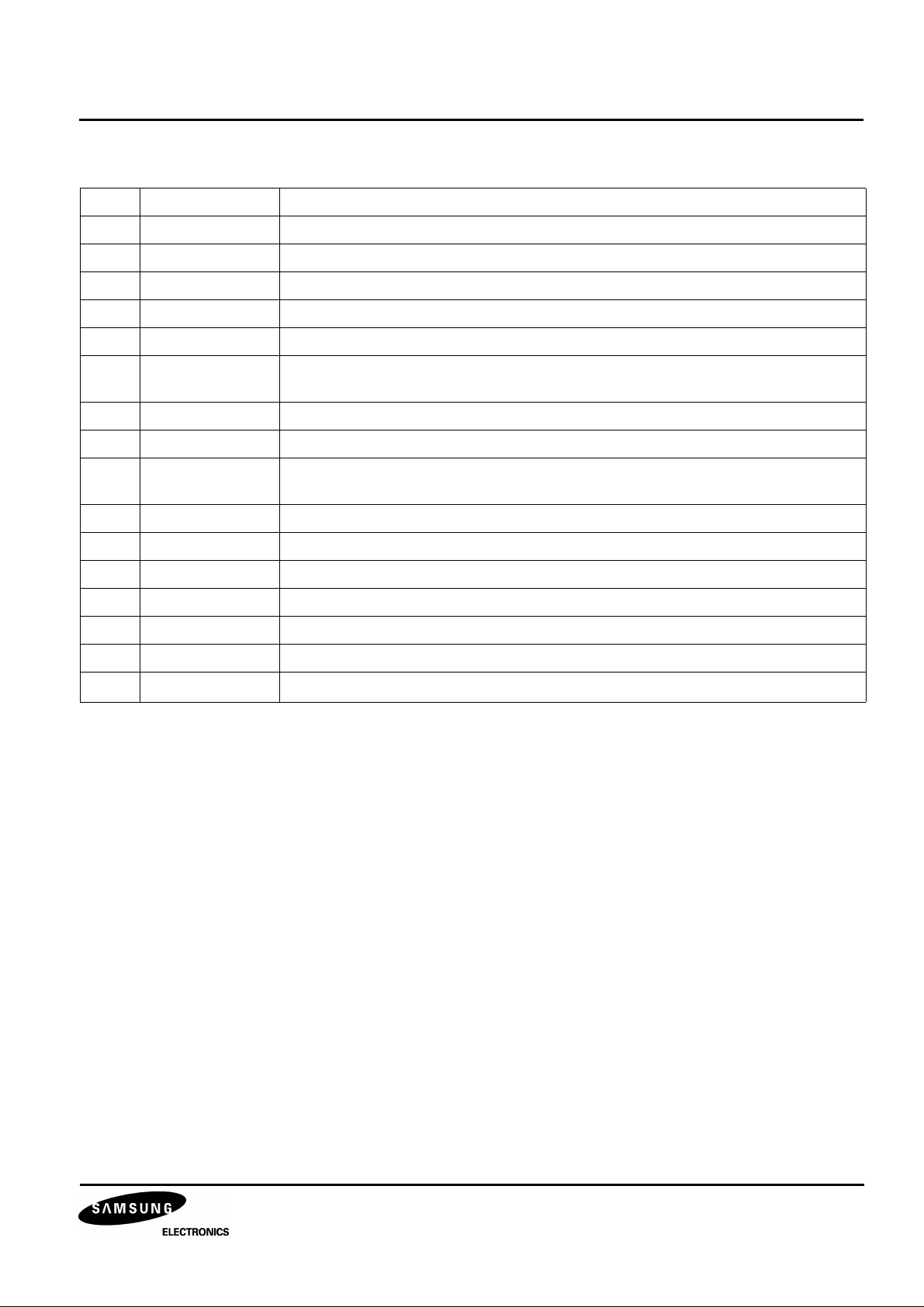

Table 1. Pin Description

Pin No Pin Name Description

1 PLL2C Second PLL Loop Filter

2 H-DUTY DC Control of Horizontal Drive Output Pulse Duty-cycle.

If this pin grounded, the horizontal and vertical outputs are inhibited. By connecting a

capacitor on the this pin a soft-start function may be realized on h-drive output.

3 H-FLY Horizontal Flyback Input (Positive Polarity)

4 H-GND Horizontal section ground. Must be connected only to components related to H

blocks.

5 H-REF Horizontal section reference voltage. Must be filtered by capacitor to pin 4.

6 NC

7 NC

8 NC

9 NC

10 C0 Horizontal Oscillator Capacitor. To be connected to pin 4.

11 R0 Horizontal Oscillator Resistor. To be connected to pin 4.

12 PLL1F First PLL Loop filter. To be connected to pin 4.

13 HLOCK-CAP First PLL Lock/Unlock Time Constant Capacitor. Capacitor filtering the freqency

change detected on pin 13. When frequency is changing, a blanking pulse is

generated on pin 23, the duration of this pulse is proportionnal to the capacitor on

pin 13. To be connected to pin 4.

14 FH-MIN DC Control for free running frequency setting. Comming from DAC output or DC

voltage generated by a resistor bridge connected between pin 5 and 4.

15 H-POS DC Control for Horizontal Centering

16 XRAY-IN X-RAY Protection input (with Internal latch function)

17 H-SYNC TTL Horizontal Sync Input

18 Vcc Supply Voltage (12V Typical)

19 GND Ground

20 H-OUTEM Horizontal Drive Output (emiter of internal transistor)

21 H-OUTCOL Horizontal Drive Output (open collector of internal transistor)

22 B+OUT B+ PWM Regulator output

23 SBLK

OUT

Safety Blanking output. Activated during frequency changes, when X-RAY input is

triggered or when VS is too low.

24 VGND Vertical Section Signal Ground

25 VAGCCAP Memory Capacitor for Automatic Gain Control Loop in Vertical Ramp Generator

26 V

REF

Vertical Section Reference Voltage

3

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS S1D2147A01

Table 1. Pin Description (Continued)

Pin No Pin Name Description

27 VCAP Vertical Sawtooth Generator Capacitor

28 VS-AMP DC Control of Vertical S-Shape Amplitude

29 VS-CENT DC Control of Vertical S-Centering

30 V-OUT Vertical Ramp Output (with frequency independant amplitude and S-Correction)

31 V-AMP DC Control of Vertical Amplitude Adjustment

32 VDCOUT Vertical Position Reference Voltage Output Temperature matched with V-AMP

output

33 V-POS DC Control of Vertical Position Adjustment

34 V-SYNC Vertical TTL Sync Input

35 PLL1INHIB TTL Input for PLL1 Output Current Inhibition (To be used in case of comp sync input

signal)

36 E/WOUT East/West Pincushion Correction Parabola Output

37 E/W-AMP DC Control East/West Pincushion Correction Amplitude

38 KEYST DC Control of Keystone Correction

39 B+ADJ DC Control of B+ Adjustment

40 REGIN Regulation Input of B+ Control Loop

41 COMP B+ Error Amplifier Output for Frequency Compensation and Gain Setting

42 I

SENSE

Sensing of External B+ Switching Transistor Emitter Current

4

Loading...

Loading...