Page 1

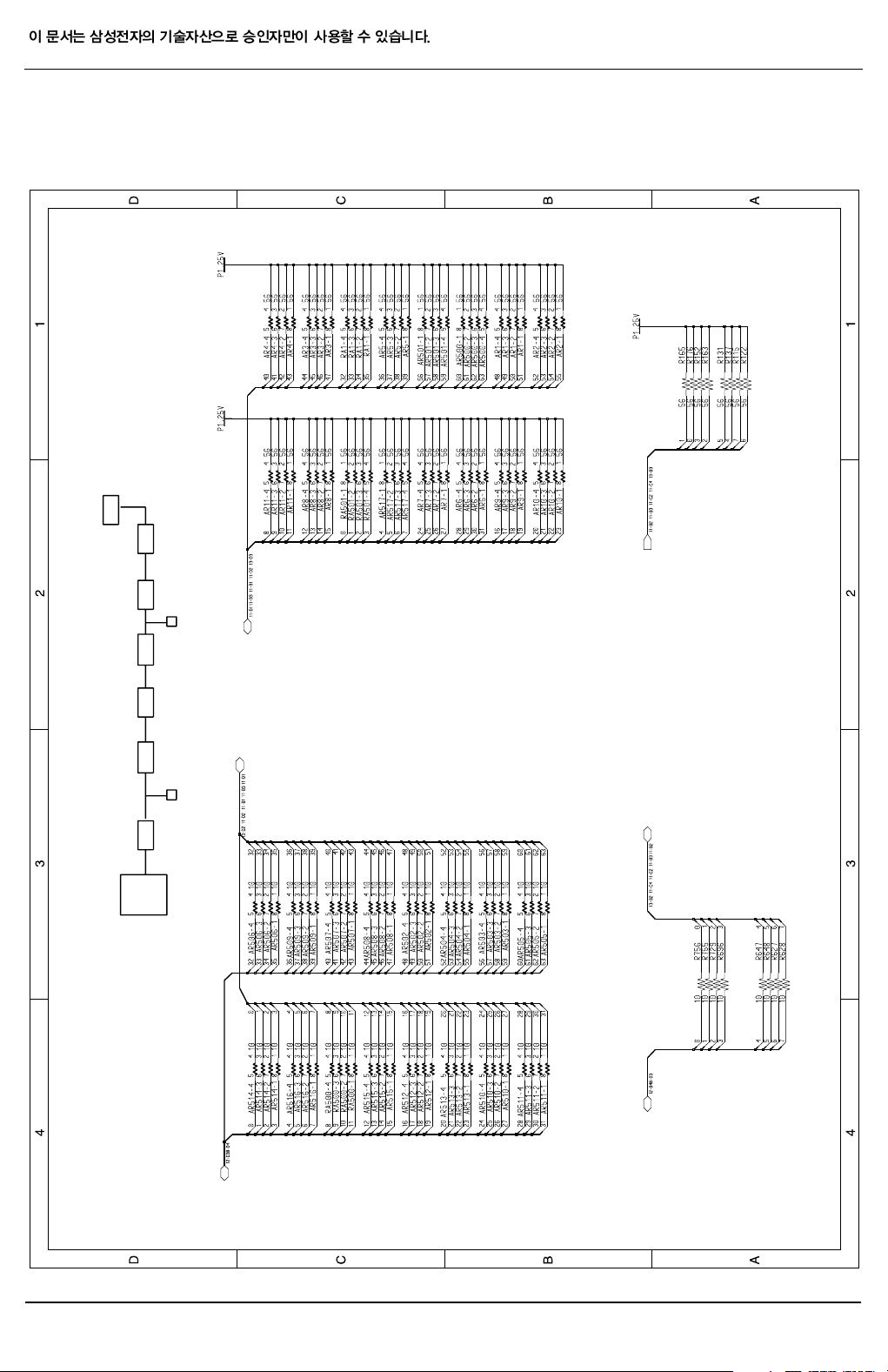

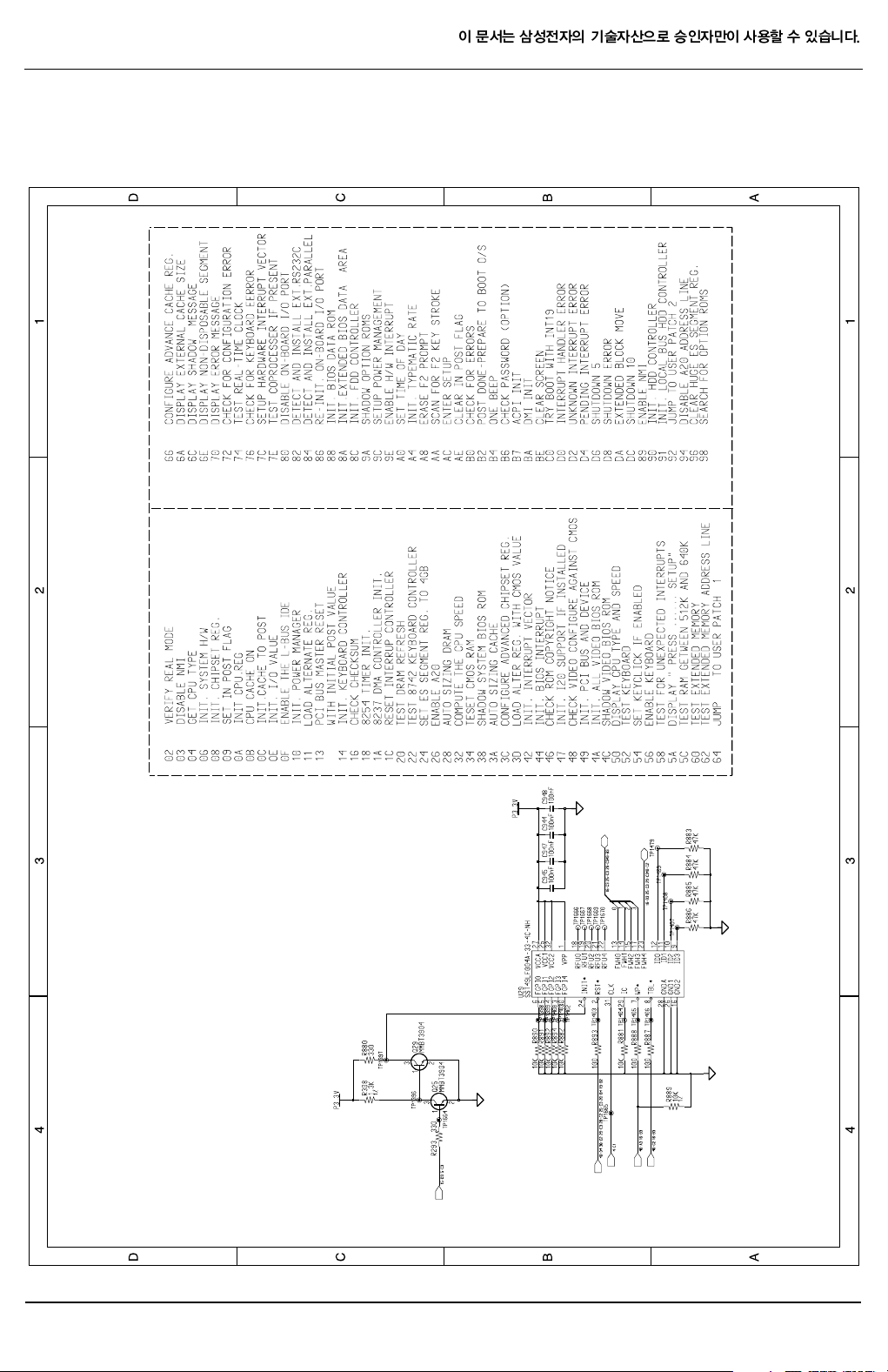

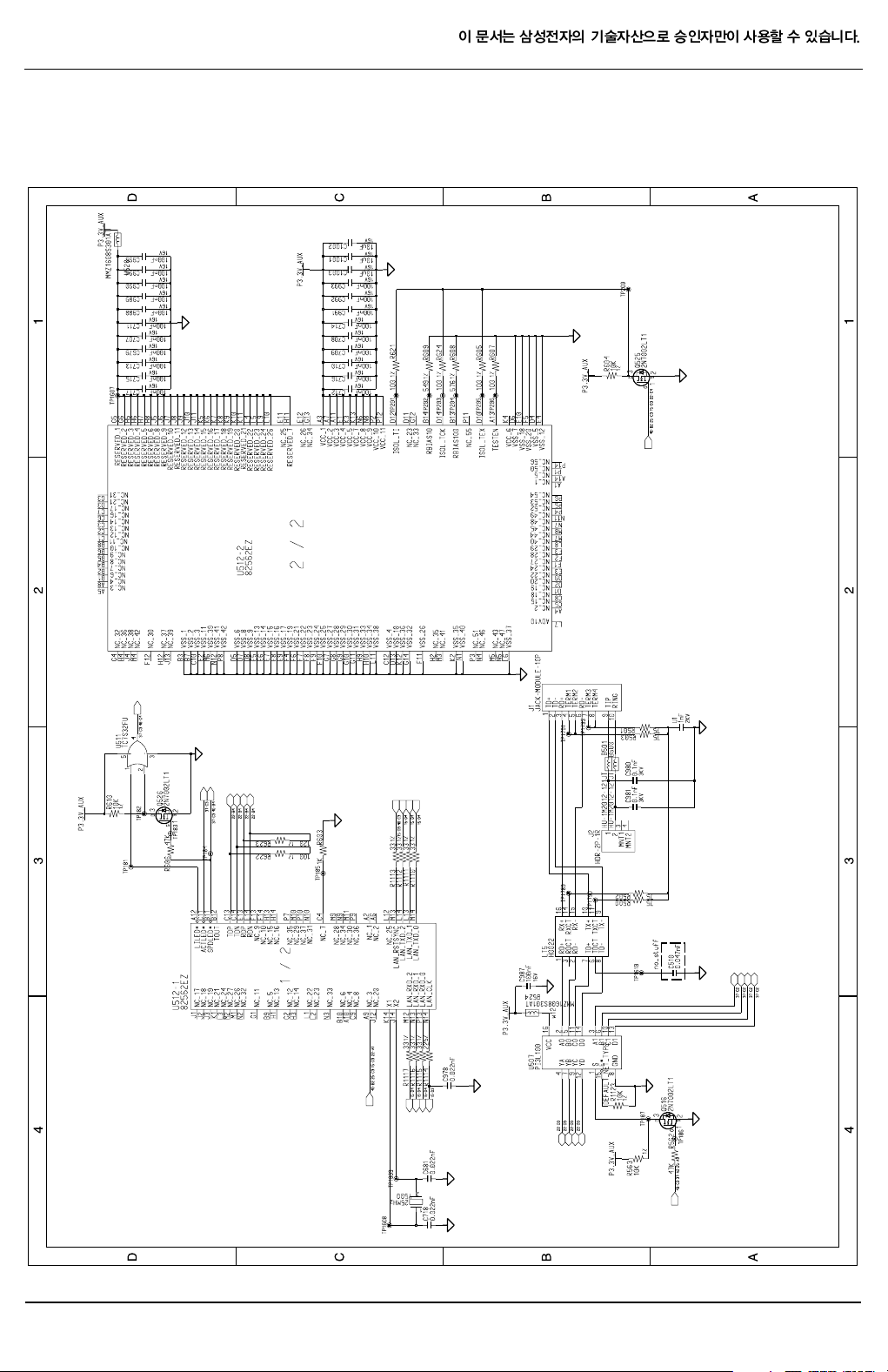

5-1 System Main Board Schematic Diagrams

5-1Sens Q 20

5 System Schematic Diagrams and PCB Silkscreen

15.

3.

13.

Model Name :

1.

31.

12.

T.R. Date :

27.

WS JUNG

BANIAS LV

4.

BA41-00377A

18.

855GM

PCB Code :

CPU :

11.

29.

Remarks :

20.

10.

HJ KIM

Chip Set :

16.

25.

28.

2003. 4. 24

1.0

Kevin

30.

19.

22.

Dev. Step :

CHECK

26.

21.

6.

5.

APPROVAL

2.

8.

MP

14.

7.

24.

9.

17.

CETUS Main

23.

CETUS

Revision :

DRAW

This Document can not be used without Samsung’s authorization.

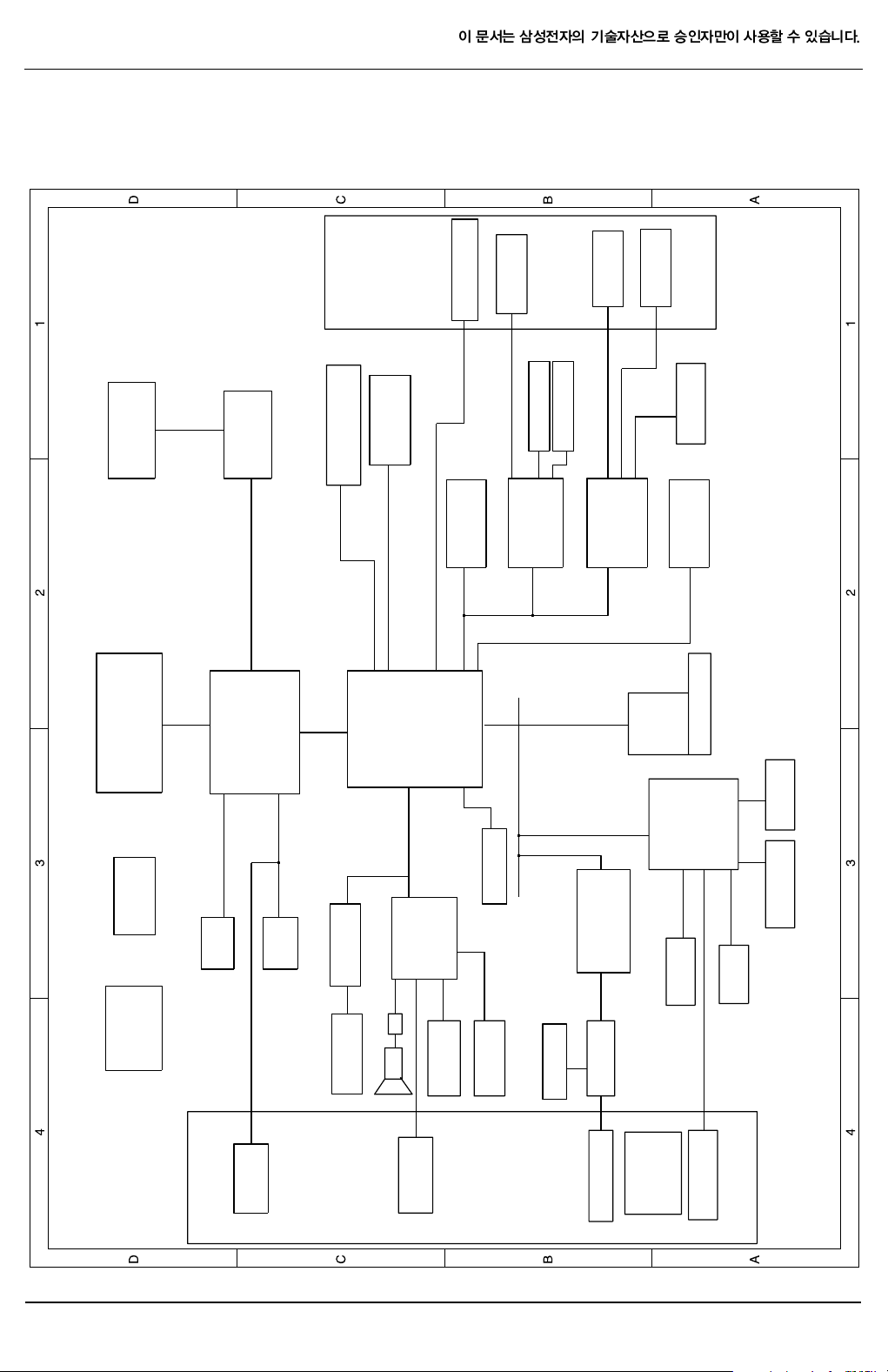

Page 2

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-2

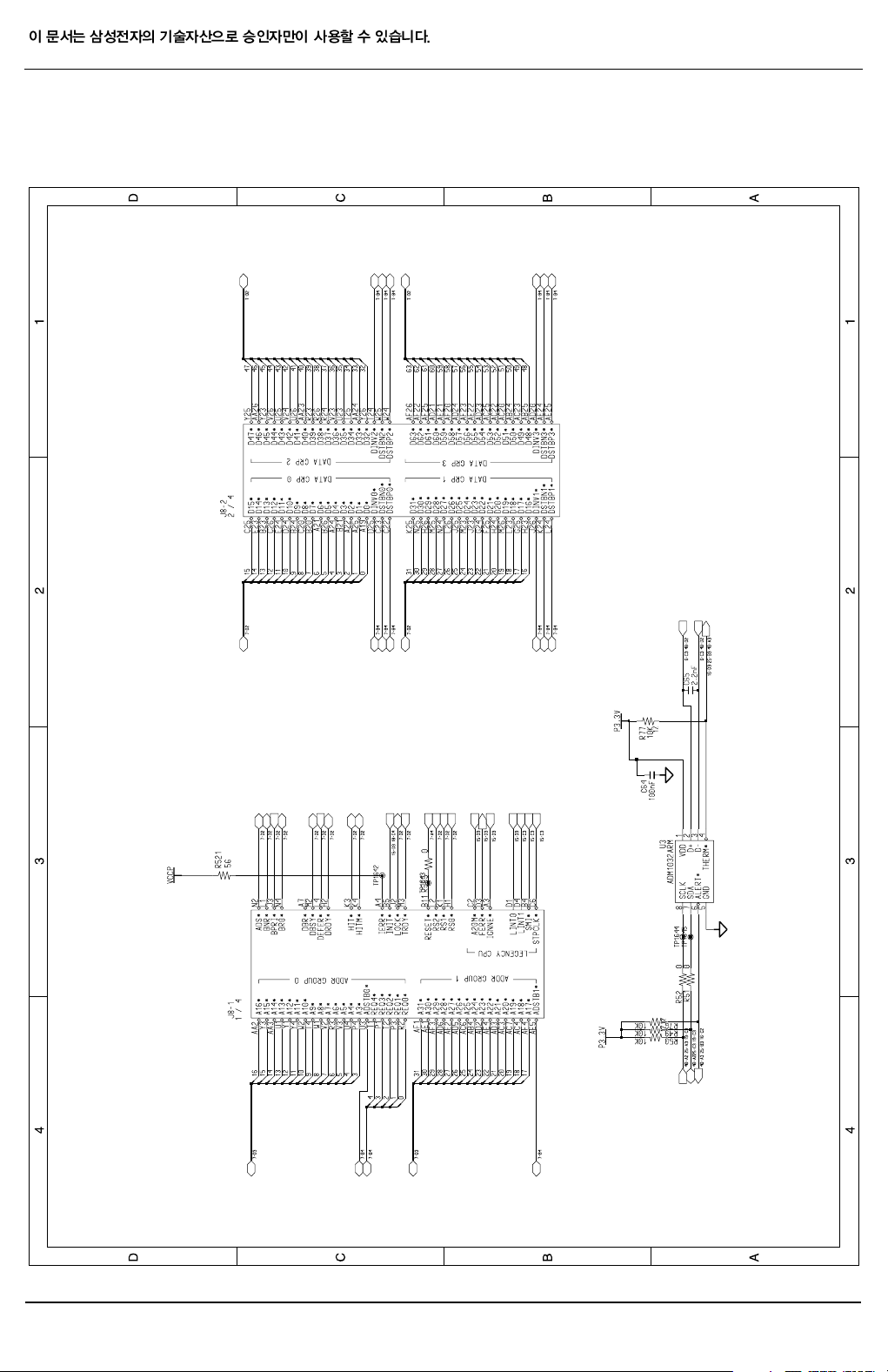

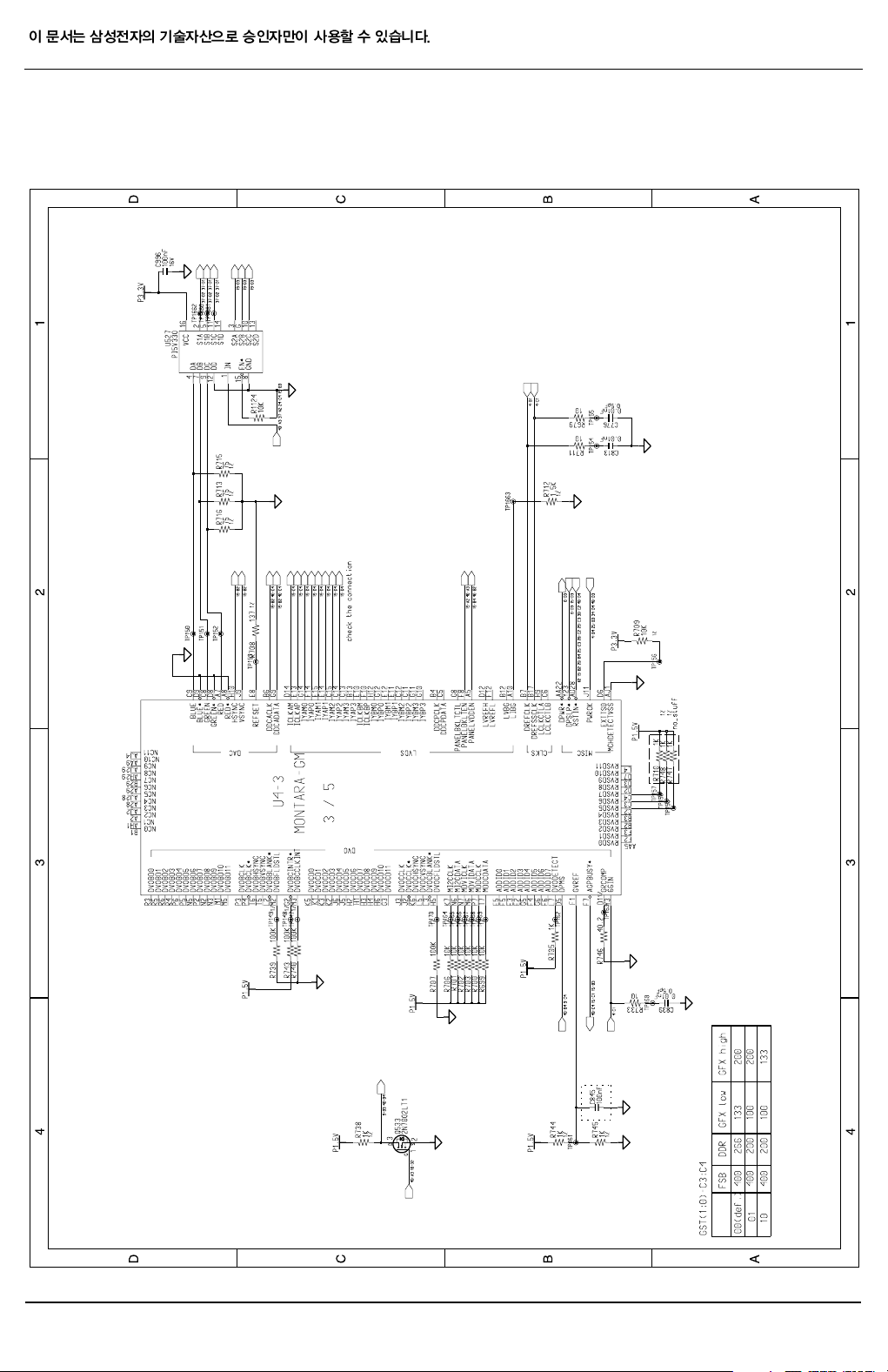

5-1-1(a) System Main Board Schematic Sheet 2 of 40(BLOCK DIAGRAM)

PCI BUS

1394 (port 0)

EEPROM

p24

p23

p23

p22

IDE0

256MB/128MB

SODIMM

Max 1GB

CPU

BaniasLV

USB (port 1)

LAN switch

Clock generator

82801 DBM 1.5V

400MHZ

Docking

SPDIF

RJ-45(10/100)

1394 (port 1)

p28

p30

p18

(FACTORY OPTION)

Clocking

PIO

82562EZ

FIR(Option)

#0

#1

266DDR

On Board

Internal KBD

Touch Pad

87391

p11,p13,p14

p12

USB

BLUETOOTH

p29

p15,p16,p17

p30

p20,p21

p21 p21

port3

LPC

FWH

82802A

MICOM

AC LINK

HDD

RJ-11

MDC

SPKR

HI 1.5

RJ-45(10/100)

EEPROM

p20

GMCH-M

855GM

ICH4 - M

CONN

WLAN/Bluetooth

Docking

CRT

2 USB (port4,5)

CardBus +

1394 Lynx+PHY

R5C591

CARD BUS

Mini PCI

THERMISTER

ADM1032

LCD

CRT

(1.2V)

(100MHZ, 4*)

HP JACK

PS/2

AMP

p4

p25

p29

p28

p19

Hitachi 2160

p24

p24

p24

p24

/2ND HDD

p19

(AC97 2.2)

CS4202

MIC JACK

LOM

KINNERITH+

p20

p22

p5

p5,p6

p7,p8,p9,p10

SIO

p29

p29

SD(MMC) + MS

FDD/ODD

This Document can not be used without Samsung’s authorization.

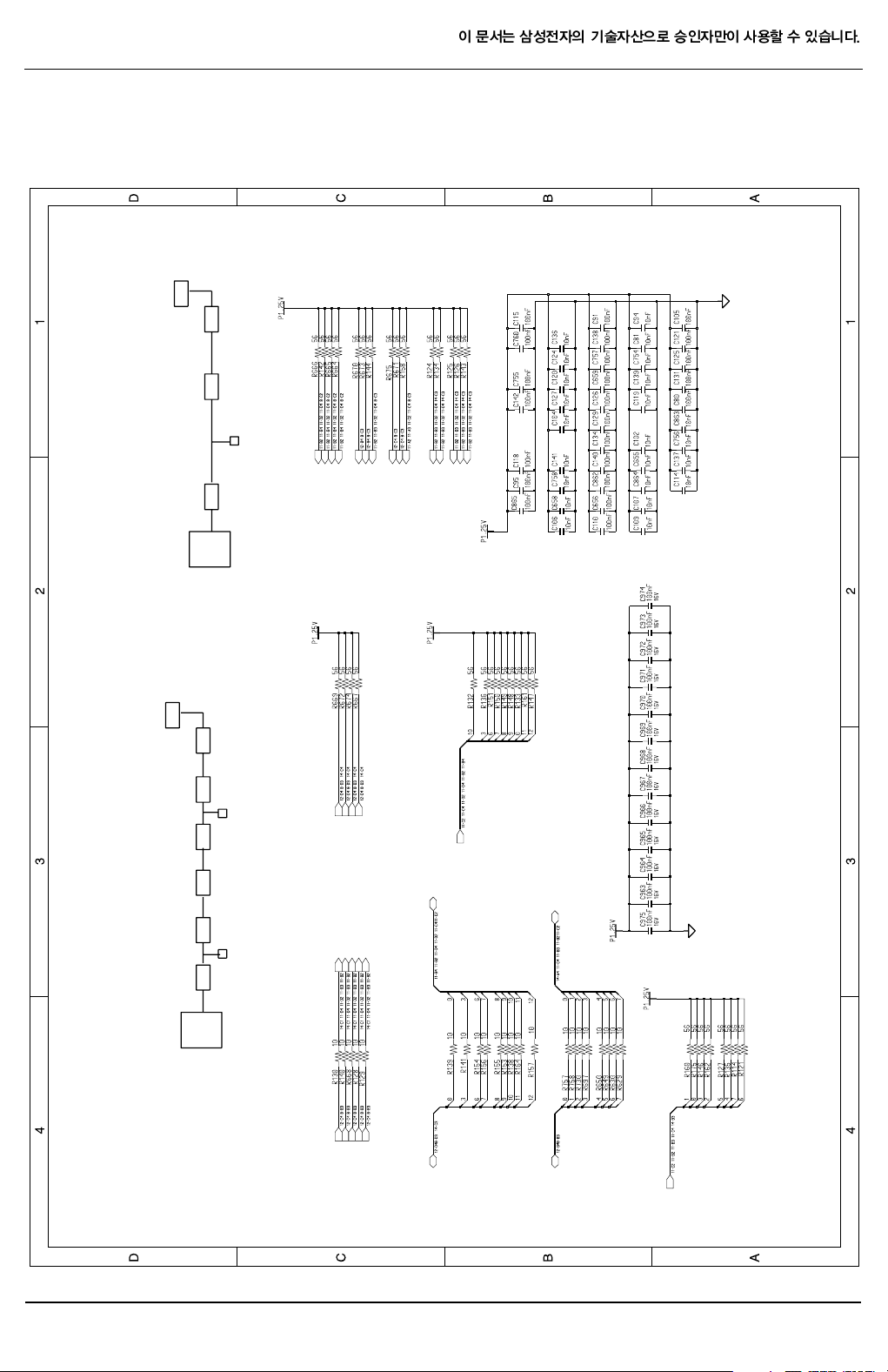

Page 3

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 20

5-1-1(b) System Main Board Schematic Sheet 3 of 40(BOARD INFORMATION)

Devices

ICH4M

SODIMM0

0100 110x

Hex

4Ch

PCI Devices

Devices IDSEL#

Cardbus

USB

Hub to PCI

SYSTEM PORT RIGHT

LPC bridge/IDE/AC97/SMBUS

1

AGP5Internal MAC

3

AD19

AD20

AD29(internal)

E,F

AD30(internal)

AD31(internal)

AD17(internal)

AD24(internal)

REQ/GNT#

0

Interrupts

A,B,C

#0 : A

B

A,B

#1 : D

#2 : C

-

-

E

---

-

I2 C / SMB Address

P1.25V

Address

P2.5V

ADM1032

LAN

Master11010 001x

5.0V power rail ( off in S4-S5)

-

USB2.0 : H

A2h

Bus

SMBUS Master

Thermal Sensor ( CPU )

-

Clock, Unused Clock Output DisableD2hCK-408 (Clock Generator) 1101 001x

Voltage Rails

Primary DC system power supply (9 to 12V)

1.5V switched power rail (off in S3-S5)

1.8V switched power rail (off in S3-S5)

VDC

VCC_CORE

P1.5V

P1.8V

USB PORT Assign

PORT NUMBER ASSIGNED TO

SYSTEM PORT LEFT

0

004

1

Docking

02021

AC Link - B-

MiniPCI SLOT1 BANIAS/MGM Processor System Bus(PSB) Termination (1.05V)VCCP

MCH-M Core Voltage (1.2V)VCC_MCH

Core voltage for BANIAS CPU (1.356 - 0.844V)

3.3V always on power rail for MICOM

3.3V power rail (off in S4-S5)

3.3V switched power rail (off in S3-S5)

5.0V switched power rail (off in S3-S5)

2.5V power rail (off in S4-S5)

P3.3V_AUX

P3.3V

P5V

P2.5V_AUX

MICOM_P3V

1.25V power rail (off in S4-S5)

0

2.5V switched power rail (off in S3-S5)

0

BLUETOOTH

0

AD21

1D1

P5V_AUX

1

Photo snesor72hTSL2550 0111 001x

MICOM Master - SMBUS Master

Battery 0001 011x 16h System Battery

CPU Core Voltage Table

VID4 VoltageVID3 VID2 VID1 VID0

00111001111

1

00111

00010100011

1

111

0

1.612 V

0

VID4

1

VID3

0

VID11011

1

000

1

00000000000

0

000

-

00101

1101000

1

01011

1.708 V

1.692 V

1.676 V

1.516 V

1.660 V

1.596 V

1.580 V

1.564 V

1.548 V

1.500 V

1.484 V

1.468 V

1.644 V

1.628 V01.532 V

0

Voltage

0

VID2

0

VID0

0

0

1.196 V

0

1100101

1

00111

00010100001

010

100

-

0

010011111

1

000

1

01001

1111101

111

1

0

1.180 V

1.164 V

1.004 V

1.148 V

1.084 V

1.068 V

1.052 V

1.036 V

0.988 V

0.972 V

0.956 V

1.132 V

1.116 V

1.100 V

1.020 V

VID500

000001000

10101

0

VID511

111111111

1

11111

0

0

1.452 V01.420 V11.404 V01.324 V01.292 V11.228 V

011

1

00010100011

1

111

0

01000111101

1

000

1

01001101010

1

01011

0

1.436 V

1

1.260 V

1

1.340 V11.308 V11.244 V11.212 V

1.388 V

1.372 V

1.356 V

1.276 V

00101100101

1

001

1

1

010

0.924 V

0

0.748 V

0

0.828 V00.796 V

1

1

11110

00010011111

1

0

00

1

-

1

1111111

111

11111

01001101010

1

010

1

0.940 V10.908 V00.892 V00.812 V00.780 V

0.732 V

0.716 V

0.700 V

0.876 V

0.860 V

0.844 V

0.764 V

00000000000

0

0

VCC (LFM = 600MHz)

0

- 100MHz Geyserville III steps supported

0

- 700MHz point not supported

1

Ultra Low Voltage CPU

1

- GV III points for LV Banias 1.1GHz = 600MHz, 800MHz, 900MHz

1

- TDP = 7W, Iccmax = 9A

11111

11111

11111111111

ICH4

1

MICOM

1

STAC9750

1

CPU

0

P3.3V_AUX0MDC

0000000

000-0

Highest Freq.

Deeper Sleep

Low Voltage Banias

VCC (HFM = 1.1/1.2GHz)

Low Voltage Banias

VCC (LFM = 600MHz)

Ultra Low Voltage Banias

VCC (HFM = 900MHz)

Ultra Low Voltage Banias

5C591

Low Voltage CPU

Docking

- GV III points for LV Banias 1.1/1.2GHz = 600MHz, 800MHz, 900MHz, 1GHz, 1.1/1.2GHz

- TDP = 12W, Iccmax = 12A

- 100MHz Geyserville III steps supported

- 700MHz point not supported

- Vcc (HFM = 1.1/1.2GHz) = 1.180V

- Vcc (LFM = 600MHz) = 0.956V

- Vcc (HFM = 900MHz) = 1.004V

- Vcc (LFM = 600MHz) = 0.844V

MICOM_P3V

POWER

P3.3V P5VP1.8V

MICOM ICH4

P1.5V VCCP

CLOCK

5C591

MINI-PCI

SODIMM

MICOM

S/IO

FWH

HDD HDD

MDC

MINI-PCI

CPUICH4

MINI-PCI

FIR

MGM

THERMISTER

MGM

P5V_AUX

ICH4

P2.5V_AUX

MGM

SODIMM

BLUETOOTH

ICH4

VCC_CORE

CPU

VCC_MCH

CPU

MGM

P1.5V_AUX

ICH4

5C591

5C591

Docking

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

5-3

This Document can not be used without Samsung’s authorization.

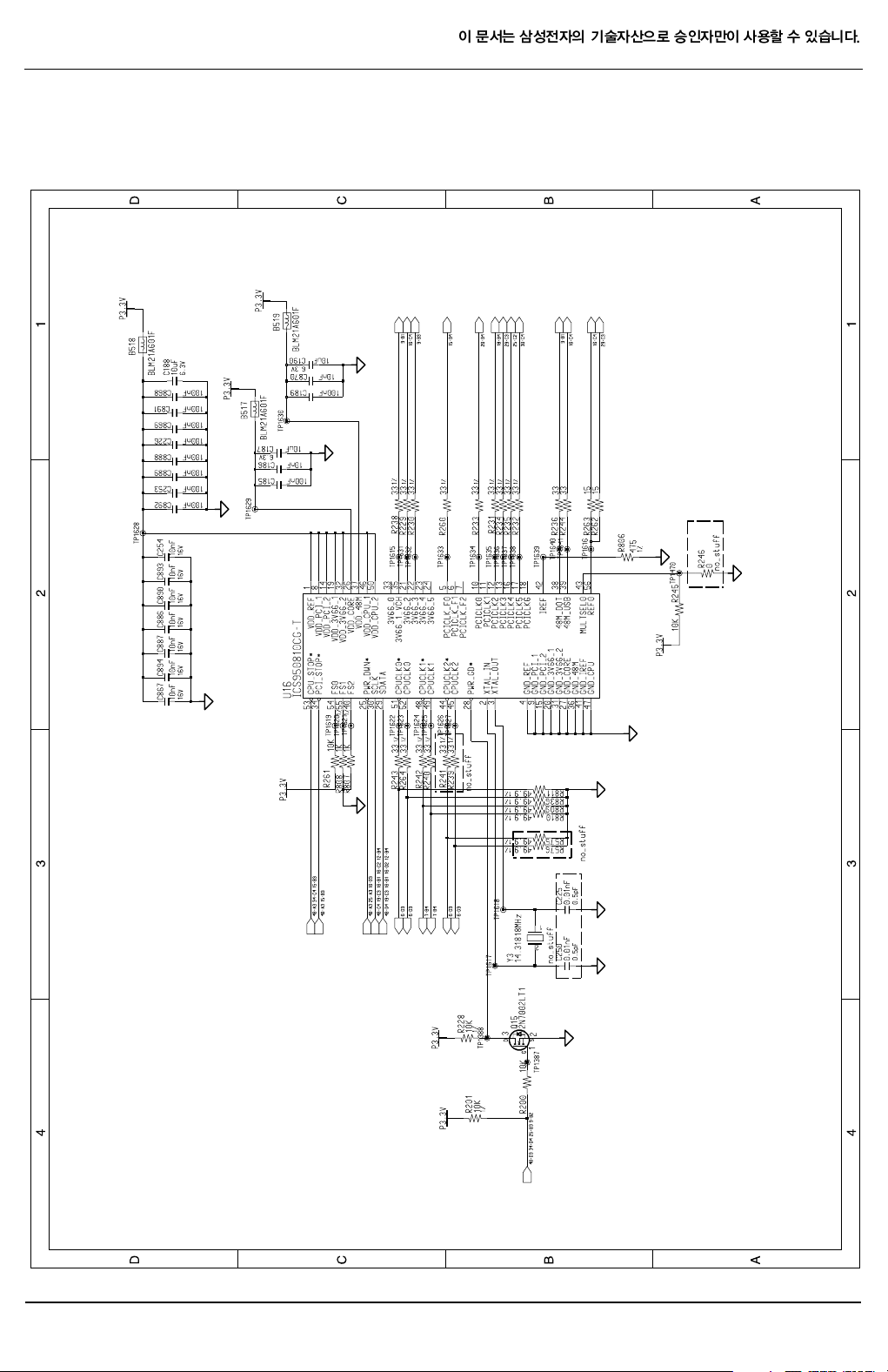

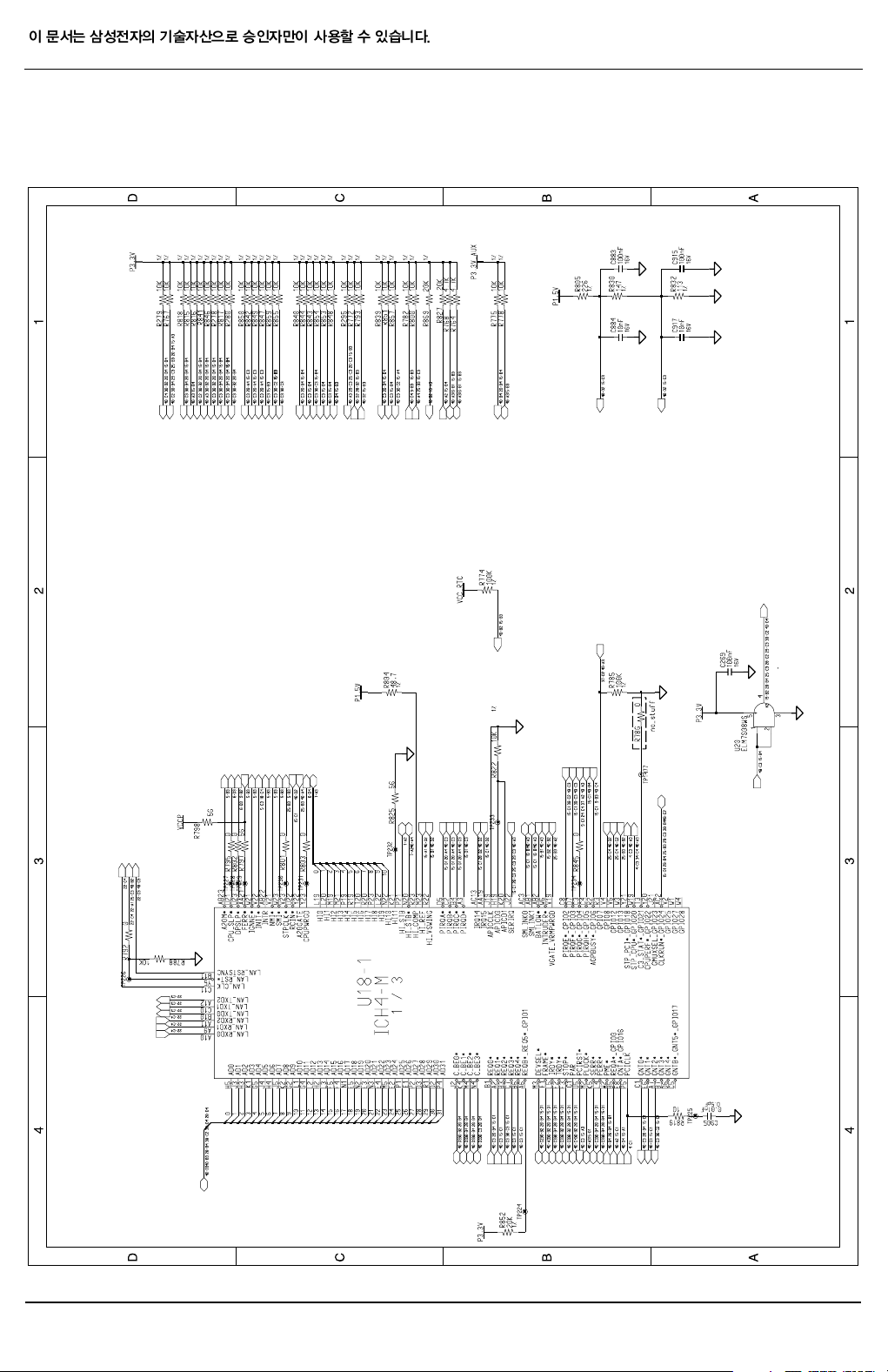

Page 4

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-4

5-1-1(c) System Main Board Schematic Sheet 4 of 40(CLOCK GENERATOR)

Close to chip

HCB3216K-601T20

Be sure to follow A/W guide line!

682088

48Mhz

CLK3_SIO14

CLK3_MCH66

CLK3_PCLKICH

CLK3_PCLKFWH

CLK3_PCLKCB

CLK3_PCLKMICOM

CLK3_DREFSSCLK

CLK_CPU*

CLK_CPUITP

CLK_CPUITP*

CLK3_DREF

CLK3_ICH66

CLK3_ICH14

CLK3_ICH48

CLK3_PCLKSIO

CLK3_PCLKMIN

SMB3_DATA

CLK_MCH

CLK_CPU

CHP3_SLPS1*

IMVP4_PWRGD

CHP3_CPUSTP*

CHP3_PCISTP*

SMB3_CLK

CLK_MCH*

This Document can not be used without Samsung’s authorization.

Page 5

5 System Schematic Diagrams and PCB Silkscreen

5-5Sens Q 20

5-1-1(d) System Main Board Schematic Sheet 5 of 40(BANIAS CPU)

CPU2_THERMDCSMB3_ALERT*

CHP3_OVERT*

KBC3_THERM_SMDATA

KBC3_THERM_SMCLK CPU2_THERMDA

CPU1_A20M*

CPU1_ADSTB1*

CPU1_ADSTB0*

CPU1_ADS*

CPU1_IGNNE*

CPU1_HITM*

CPU1_HIT*

CPU1_FERR*

CPU1_DRDY*

CPU1_DEFER*

CPU1_DBSY*

CPU1_BREQ*

CPU1_BPRI*

CPU1_BNR*

CPU1_RS0*

CPU1_LOCK*

CPU1_NMI

CPU1_INTR

CPU1_INIT* CPU1_DSTBP0*

CPU1_DSTBN0*

CPU1_D*(31:16)

CPU1_D*(15:0)

CPU1_DSTBN3*

CPU1_D*(63:48)

CPU1_D*(47:32)

CPU1_TRDY*

CPU1_STPCLK*

CPU1_SMI*

CPU1_RS2*

CPU1_RS1*

CPU1_A*(16:3)

CPU1_REQ*(4:0)

CPU1_CPURST*

CPU1_DSTBN1*

CPU1_DBI3*

CPU1_DSTBN2*

CPU1_DSTBP2*

CPU1_DSTBP3*

CPU1_DBI2*CPU1_DBI0*

CPU1_DSTBP1*

CPU1_DBI1*

CPU1_A*(31:17)

This Document can not be used without Samsung’s authorization.

Page 6

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-6

5-1-1(e) System Main Board Schematic Sheet 6 of 40(BANIAS CPU)

Placed as close as possible to

COMP 0 , 2 <(COMP 1,3) should be connected

of the First GTLREF0 with Z0= 55 ohm trace

Minimize coupling of any switching signals to this net

Z0=27.4 ohm (55 ohm) trace shorter than

PREQ,PRDY,BPM(0:3),TCK,TDI,TDO,TMS,TRST

PSI*

each of the four VCCA pins.

220uF * 4, 10uF *35

"Mobile Platform Design Checklist rev. 0.94 page19"

STUFFING OPTION

"ALL ITP I/F signals"

220uF = 12mohm(Max/4) 3.5nH/4

must have T.P.

GTLREF : Keep the Voltage divider within 0.5"

1/2 " to their respective Banias Pins

10uF = 5mohm(typ/35) 0.6nH/4

TEST3

CPU1_GTLREF0

VOS-

CPU1_PROCHOT*

CPU1_PSI*

CPU1_DPSLP*

CPU1_PWRGDCPU

CLK_CPU*

CPU3_VID(5:0)

CPU2_THERMDA

CPU2_THERMDC

CPU1_THRMTRIP*

CLK_CPU

CPU1_SLP*

CPU1_DPWR*

CLK_CPUITP

CLK_CPUITP*

This Document can not be used without Samsung’s authorization.

Page 7

5 System Schematic Diagrams and PCB Silkscreen

5-7Sens Q 20

5-1-1(f) System Main Board Schematic Sheet 7 of 40(GMCH-M)

HLZCOMP

Trace should be 10 mil,20mil spacing.

near component

CPURST* Length

near divider

GMCH-CPU : 1.0" ~ 6.0"

800mV +/- 8%

RCOMP reference voltage

GMCH-R-ITP : 12.0" max

Routing : 10 mil trace, 20 mil space

Checklist rev0.94

350mV +/- 8%

Trace should be 10 mil,20mil spacing.

near divider

near component

HUB1_REF_GMCH

GMCH1_PSWING

GMCH1_HDVREF

GMCH1_HCCVREF

GMCH1_HAVREF

GMCH1_HCCVREF

HUB1_REF_GMCH

GMCH1_PSWING

GMCH1_HAVREF

HUB1_STB*

HUB1_STB

CPU1_HITM*

CPU1_LOCK*

CLK_MCH*

CLK_MCH

CPU1_A*(31:3)

CPU1_TRDY*

CPU1_RS0*

CPU1_RS1*

CPU1_RS2*

CPU1_REQ*(4:0)

CPU1_D*(63:0)

GMCH1_HXSWING

GMCH1_HXSWING

CPU1_DSTBP0*

CPU1_DSTBN0*

CPU1_DBI0*

GMCH1_HYSWING

HUB1_HL(0:10)

CPU1_BREQ*

CPU1_DBI1*

CPU1_DBI2*

CPU1_DBI3*

CPU1_ADSTB0*

CPU1_ADSTB1*

CPU1_DSTBN1*

CPU1_DSTBN2*

CPU1_DSTBN3*

CPU1_DSTBP1*

CPU1_DSTBP2*

CPU1_DSTBP3*

GMCH1_HYSWING

GMCH1_HDVREF

CPU1_ADS*

CPU1_BNR*

CPU1_CPURST*

CPU1_BPRI*

CPU1_DBSY*

CPU1_DEFER*

CPU1_DRDY*

CPU1_HIT*

This Document can not be used without Samsung’s authorization.

Page 8

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-8

5-1-1(g) System Main Board Schematic Sheet 8 of 40(GMCH-M)

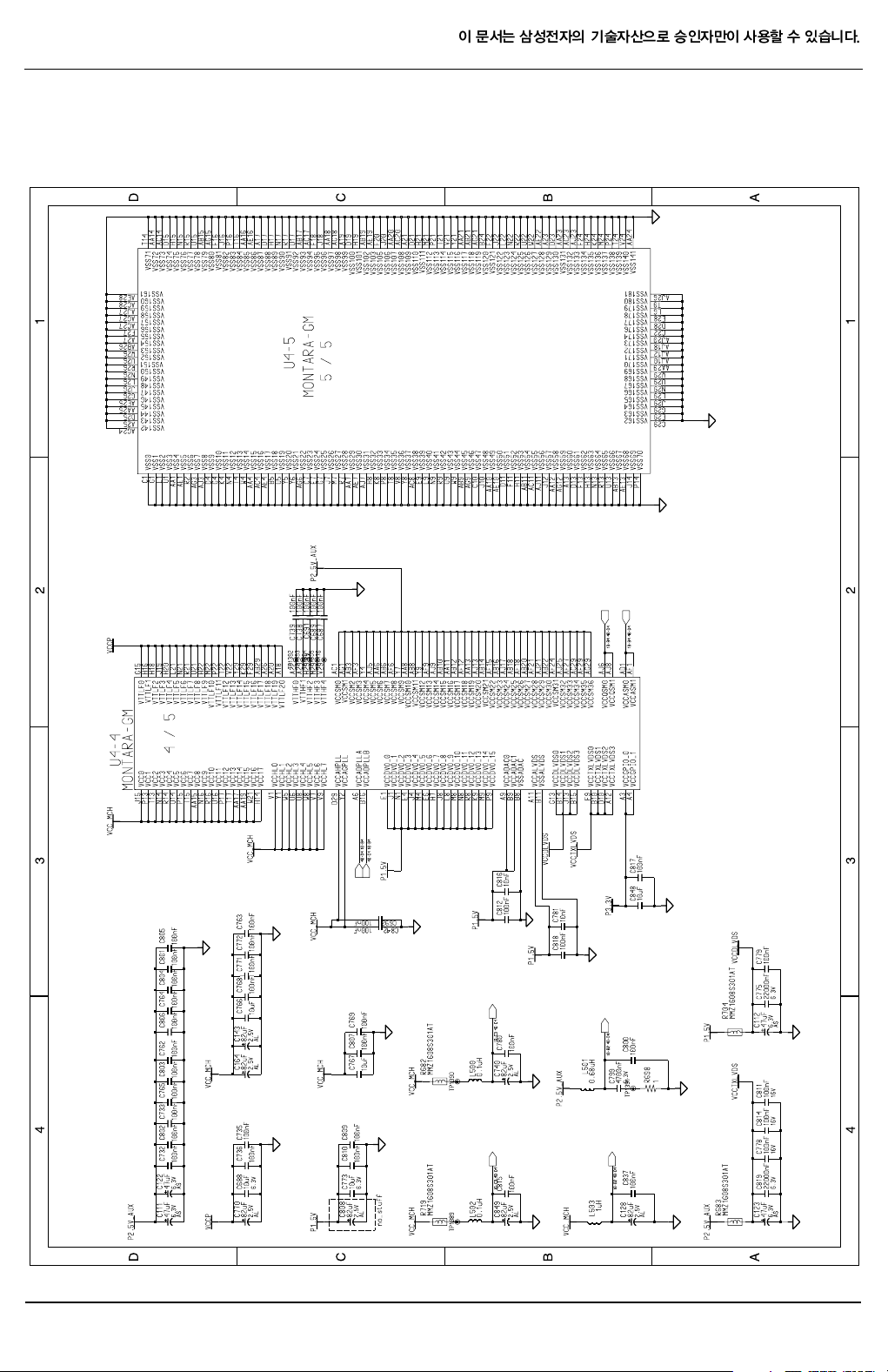

SODIMM 0

On Board : 256MB

On Board : 256MB

Used to measure timing for the read data

SCK2/2*, SCK5/5*, these signal are NC.

SDQ[71:64], SDM8, SDQS8

SODIMM 0

SODIMM0

Both signals should have vias located adjacent to the package

ON BOARD

SODIMM 0

SODIMM 0

If ECC support is not implemented,

GMCH1_SMRCOMP

GMCH1_SMVSWINGH

GMCH1_SMVSWINGL

MEM2_SRASA*

MEM2_SWEA*

CLK2_MCLK1*

CLK2_MCLK3

CLK2_MCLK3*

CLK2_MCLK4

CLK2_MCLK4*

MEM2_CSA0*

MEM2_CSA1*

MEM2_CSA2*

MEM2_SCASA*

MEM2_CKE0

MEM2_CKE1

MEM2_CKE2

CLK2_MCLK0

CLK2_MCLK0*

CLK2_MCLK1

MEM2_MAA(12:0)

MEM2_MD(63:0)

GMCH1_SMRCOMP

MEM2_DQS(7:0)

GMCH1_SMVSWINGH

GMCH1_SMVSWINGL

MEM2_MAB(2:1)

MEM2_MAB(5:4)

MEM2_DM(7:0)

MEM2_BS0

MEM2_BS1

This Document can not be used without Samsung’s authorization.

Page 9

5 System Schematic Diagrams and PCB Silkscreen

5-9Sens Q 20

5-1-1(h) System Main Board Schematic Sheet 9 of 40(GMCH-M)

T-topology

-10mil wide

-20mil spacing

As short as possible

Place near GMCH

GST2

CLK3_DREFSSCLK

CLK3_MCH66

DCK_VGA3_BLUE

DCK_VGA3_GREEN

DCK_VGA3_RED

VGA3_BLUE

VGA3_GREEN

VGA3_RED

CHP3_DCKIN*

VGA3_DDCC

VGA3_DDCD

CPU1_DPSLP*

CPU1_DPWR*

AGP3_BUSY*

DVO1_DPMS

CHP3_SUSCLK

DVO1_DPMS

VGA3_BKLTON

CLK3_DREF

VGA3_CLK-

VGA3_A1-

VGA3_CLK+

VGA3_A1+

VGA3_A0-

VGA3_A2-

VGA3_HSYNC

VGA3_VSYNC

PCI3_RST*

VGA3_A0+

VGA3_A2+

VGA3_LCDVDDON

IMVP4_PWRGD

This Document can not be used without Samsung’s authorization.

Page 10

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-10

5-1-1(i) System Main Board Schematic Sheet 10 of 40(GMCH-M)

Place two caps near MGM ACAP

VCCADPLLA

VCCADPLLB

VCCQSM

VCCASM

VCCQSM

VCCASM

VCCADPLLA VCCADPLLB

This Document can not be used without Samsung’s authorization.

Page 11

5 System Schematic Diagrams and PCB Silkscreen

5-11Sens Q 20

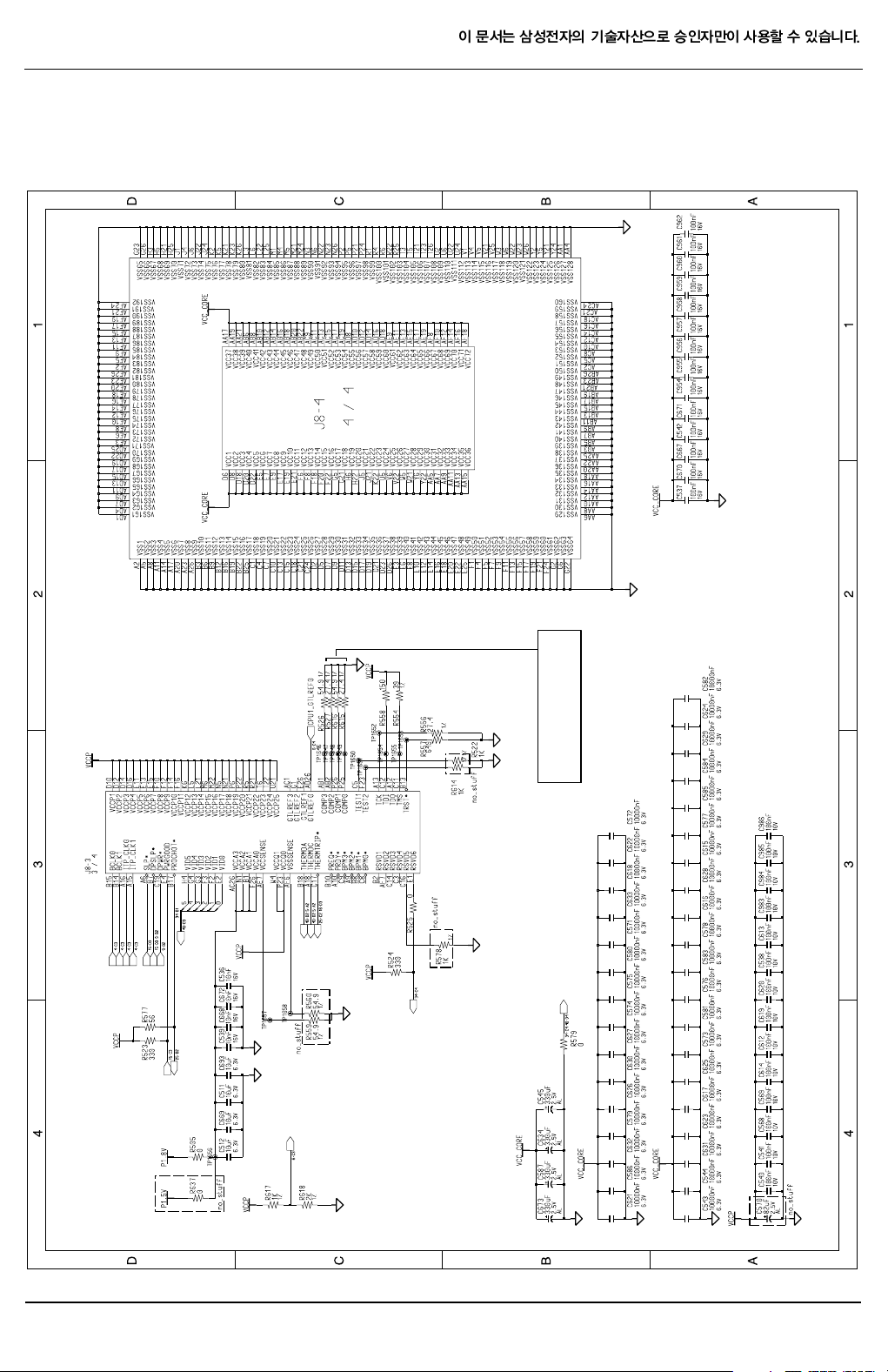

5-1-1(j) System Main Board Schematic Sheet 11 of 40(DDR-ON BOARD)

D3

D2

D1

Close to memory as you can!

Close to memory as you can!

Close to memory as you can!

Close to memory as you can!

D0

MEM2_RMD(63:48)

CLK2_MCLK4*

CLK2_MCLK3

CLK2_MCLK4

MEM2_RDM(7)

MEM2_RDQS(7)

MEM2_RSRASA*

MEM2_RDM(6)

MEM2_RDQS(6)

MEM2_RSWEA*

MEM2_RMAA(12:6)

MEM2_MAB(5:4)

MEM2_MAB(2:1)

MEM2_RBS0

MEM2_RBS1

MEM2_RSCASA*

MEM2_CKE2

MEM2_CSA2*

MEM2_RSRASA*

MEM2_RDM(4)

MEM2_RDQS(4)

MEM2_RSWEA*

MEM2_RMAA(12:6)

MEM2_MAB(5:4)

MEM2_MAB(2:1)

MEM2_RMD(47:32)

MEM2_RMAA(0)

MEM2_RMAA(3)

MEM2_RDM(5)

MEM2_RDQS(5)

MEM2_RSWEA*

MEM2_RMAA(12:6)

MEM2_MAB(5:4)

MEM2_MAB(2:1)

MEM2_RDM(3)

MEM2_RDM(2)

MEM2_RDQS(3)

MEM2_RDQS(2)

MEM2_CSA2*

MEM2_CKE2

MEM2_RMD(31:16)

MEM2_RMAA(0)

MEM2_RMAA(3)

MEM2_RBS0

MEM2_RBS1

MEM2_RSCASA*

MEM2_CKE2

MEM2_CSA2*

MEM2_RSRASA*MEM2_RSRASA*

MEM2_RSWEA*

MEM2_RMAA(12:6)

MEM2_MAB(5:4)

MEM2_MAB(2:1)

MEM2_RDM(1)

MEM2_RDM(0)

MEM2_RDQS(1)

MEM2_RDQS(0)

MEM2_CSA2*

CLK2_MCLK3*

MEM2_CKE2

MEM2_RMD(15:0)

MEM2_RMAA(0)

MEM2_RMAA(3)

MEM2_RBS0

MEM2_RBS1

MEM2_RSCASA*

MEM2_RMAA(0)

MEM2_RMAA(3)

MEM2_RBS0

MEM2_RBS1

MEM2_RSCASA*

This Document can not be used without Samsung’s authorization.

Page 12

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-12

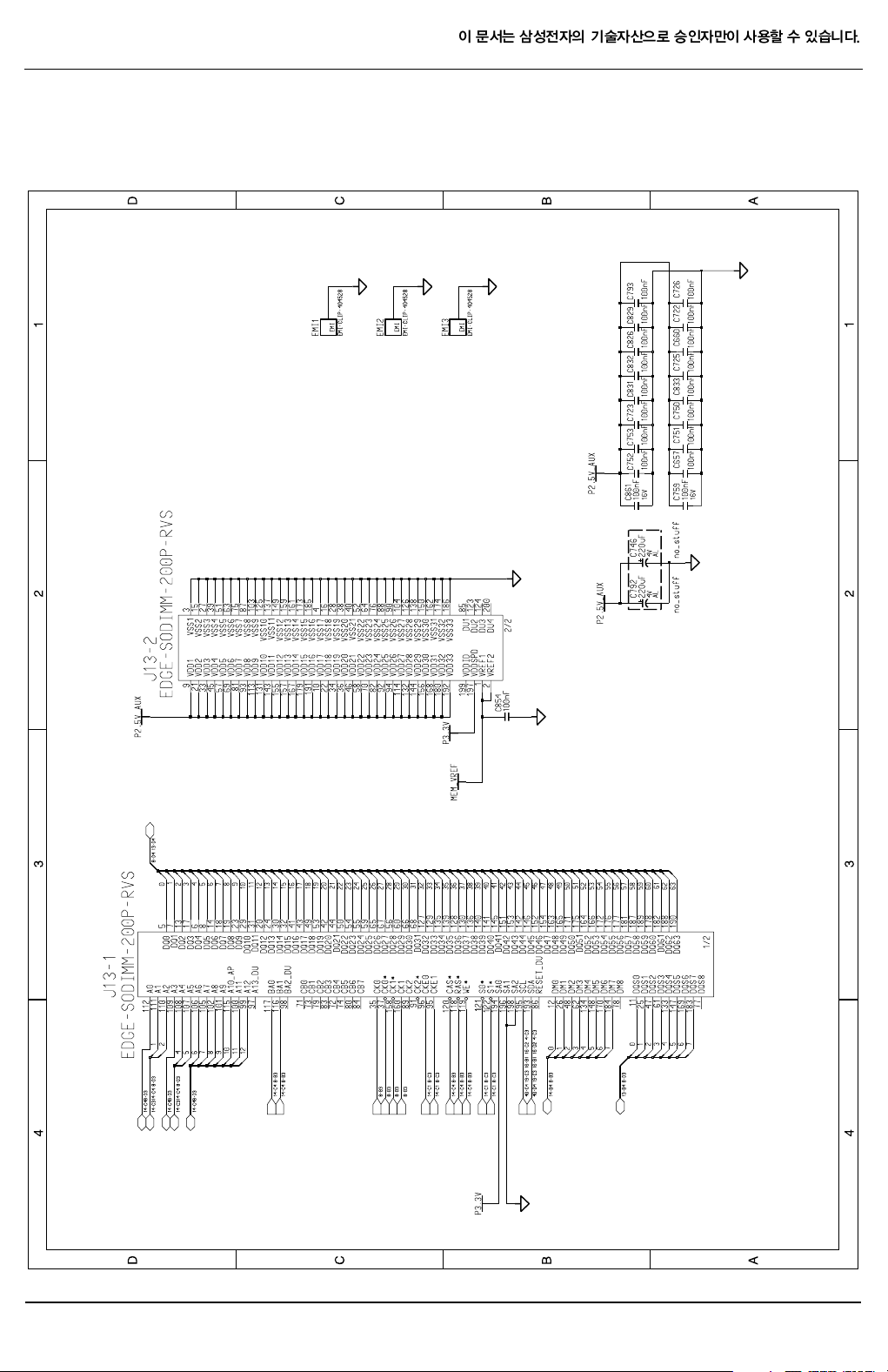

5-1-1(k) System Main Board Schematic Sheet 12 of 40(DDR-SODIMM)

P/N : 3709-001193

SMBUS Addr : 1010000X

MEM2_CSA0*

MEM2_CSA1*

MEM2_BS0

MEM2_BS1

MEM2_SWEA*

MEM2_SCASA*

MEM2_SRASA*

SMB3_CLK

SMB3_DATA

MEM2_MAA(0)

CLK2_MCLK0

CLK2_MCLK0*

CLK2_MCLK1

CLK2_MCLK1*

MEM2_CKE0

MEM2_CKE1

MEM2_MD(63:0)

MEM2_DM(7:0)

MEM2_DQS(7:0)

MEM2_MAA(2:1)

MEM2_MAA(3)

MEM2_MAA(5:4)

MEM2_MAA(12:6)

This Document can not be used without Samsung’s authorization.

Page 13

5 System Schematic Diagrams and PCB Silkscreen

5-13Sens Q 20

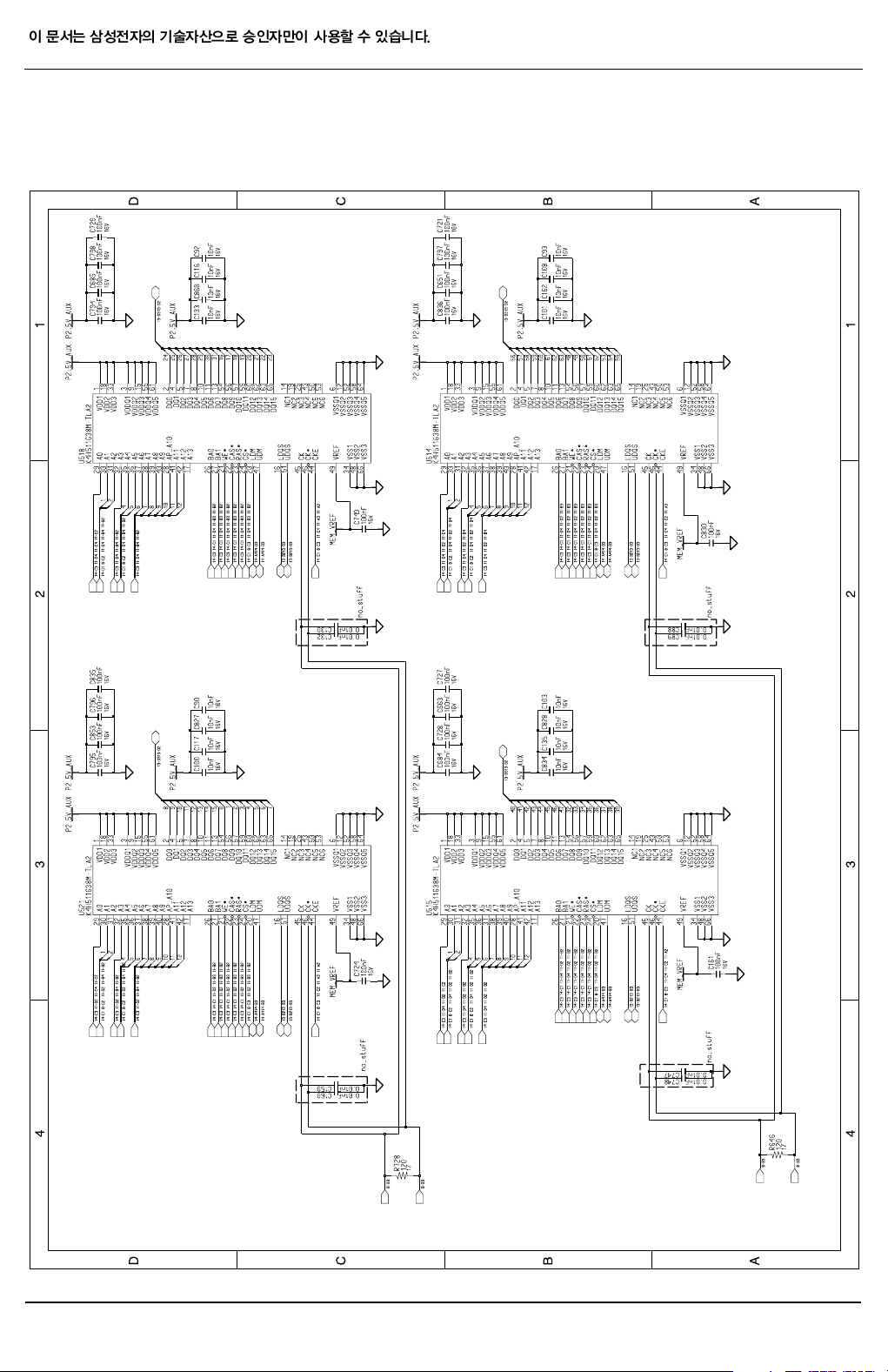

5-1-1(l) System Main Board Schematic Sheet 13 of 40(SERIES & TERMINATION)

SODIMM Pad

Rs

Vtt

L2

: CHECK BITS FOR ECC

SDQS[8:0]

L4 Rt

On Board

GMCH

L3L1

: DATA BUS

SDQ[71:64]

: DATA STROBE

SDM[8:0] : DATA MASK

DATA Signal Routing Topology

SDQ[63:0]

MEM2_RMD(63:0)

MEM2_RDQS(7:0)

MEM2_MD(63:0)

MEM2_RMD(63:0)

MEM2_DQS(7:0) MEM2_RDQS(7:0)

This Document can not be used without Samsung’s authorization.

Page 14

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-14

5-1-1(m) System Main Board Schematic Sheet 14 of 40(SERISE & TERMINATION)

SODIMM 0 Pad / On Board

Control Signal Routing Topology

SMA[12:6,3,0], SBS[1:0], RAS*, CAS*,WE*

L2

CPC signals

Place one 0.1uF cap and one 0.01uF colse to every 4 pull-up resistors terminated to Vcc1_25.

L3 L4

Rt

On Board

L2

Rt

SODIMM 0 Pad

L1

Rs

GMCH

Place 1 Cap close to every 2 pullup resisters terminated to +V1.25

Vtt

GMCH

Command Signals

L1

Command Signal can not be placed within the R-packs as data, strobe or control signals

SCKE[3:0], SCS#[3:0]

SMB[5,4],[2,1]

Vtt

SMA[5,4],[2,1]

MEM2_MAA(1)

MEM2_MAA(2)

MEM2_MAA(4)

MEM2_MAA(5)

MEM2_RMAA(12:0)

MEM2_CSA0*

MEM2_CSA2*

MEM2_CSA1*

MEM2_CKE0

MEM2_CKE1

MEM2_CKE2

MEM2_RBS0

MEM2_RSCASA*

MEM2_RSRASA*

MEM2_RBS1

MEM2_RSWEA*

MEM2_MAA(12:0) MEM2_RMAA(12:0)

MEM2_RBS0

MEM2_RBS1

MEM2_RSWEA*

MEM2_RSCASA*

MEM2_RSRASA*

MEM2_BS0

MEM2_BS1

MEM2_SWEA*

MEM2_SCASA*

MEM2_SRASA*

MEM2_RDM(7:0)MEM2_DM(7:0)

MEM2_MAB(4)

MEM2_MAB(5)

MEM2_MAB(1)

MEM2_MAB(2)

MEM2_RDM(7:0)

This Document can not be used without Samsung’s authorization.

Page 15

5 System Schematic Diagrams and PCB Silkscreen

5-15Sens Q 20

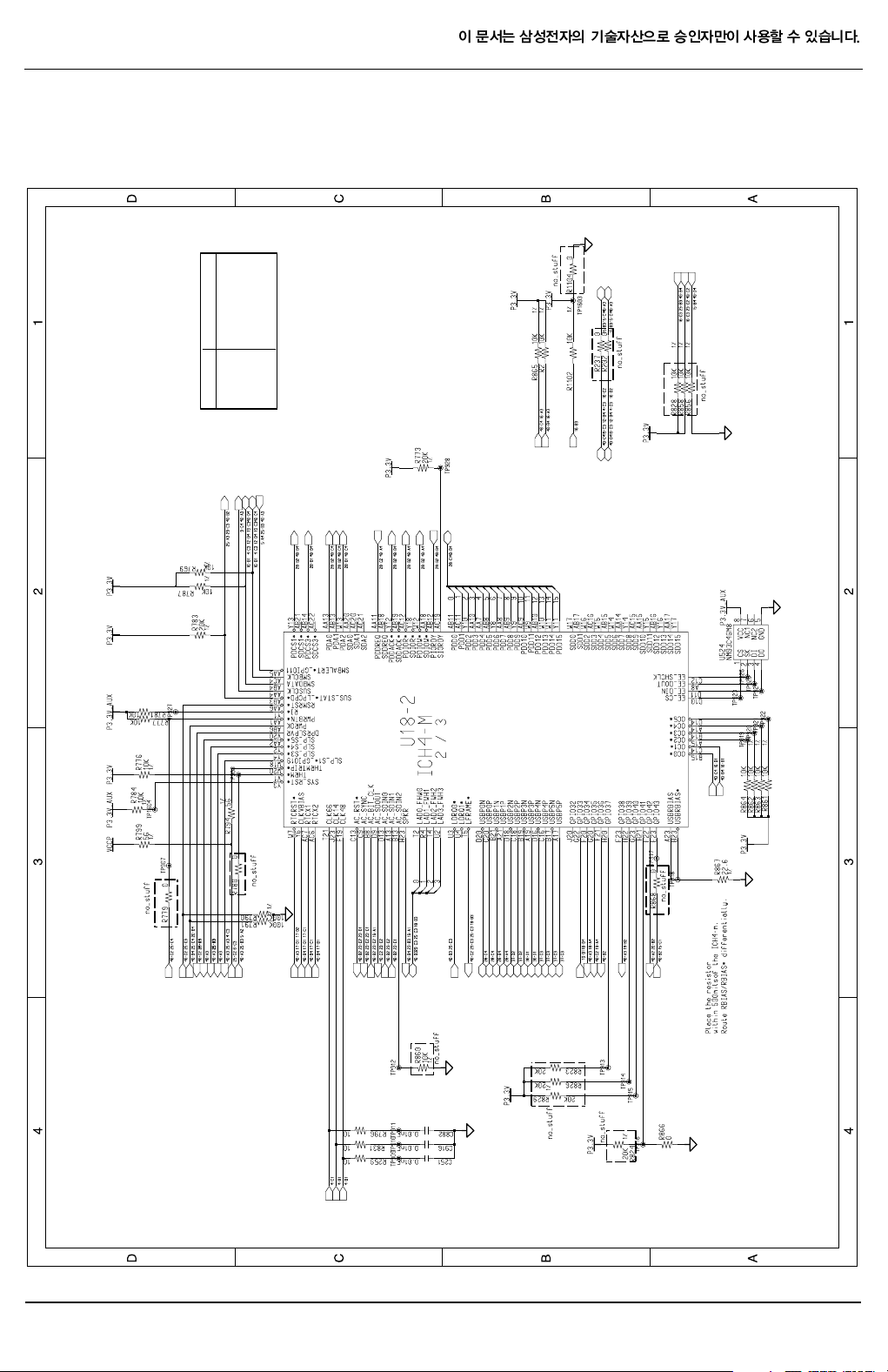

5-1-1(n) System Main Board Schematic Sheet 15 of 40(ICH4-M)

RESUME POWER WELL : GPIO25, GPIO27, GPIO28

350mV +/- 8%

Hub I/F : Route Signal with 5/20 trace/space routing.

PLACE RCOMP Resistor within 0.5" of ICH pad using thick trace

Signals must match +/- 0.1" of Strobe signals.

Place resistor near ICH4-m

near component

Checklist rev 0.91

RESUME POWER WELL : GPI8, GPI12, GPI13

Checklist rev0.94

MAIN POWER WELL : GPO16,GPO17

RCOMP R should be 2/3 board impedance

800mV +/- 8%

SET ALL UNUSED GPIO PINS TO GPO

near divider

near divider

near component

LAN3_TXD1

LAN3_TXD2

LAN3_PHYRST

KBC3_LAN_PWROK

CHP3_SMLINK0

CHP3_SMLINK1

CHP3_PME*

CHP3_DCKIN*

CHP3_IRQH*

PCI3_INTE*

PCI3_INTF*

CHP3_INTRUDER*

AGP3_BUSY*

KBC3_A20G

LCD3_LAMPSTAT

CHP3_DBAY_MODPRES*

HUB1_HVSWING

HUB1_REF_ICH

CLK3_PCLKICH

CHP3_DBAY_MODPRES*

LAN3_PHYCLK

LAN3_RXD0

LAN3_RXD1

LAN3_RXD2

LAN3_TXD0

PCI3_INTF*

PCI3_INTE*

CHP3_IRQH*

PCI3_CLKRUN*

AGP3_BUSY*

PCI3_GNT0*

PCI3_GNT1*

PCI3_GNT2*

HUB1_HVSWING

HUB1_REF_ICH

CHP3_SMLINK0

CHP3_SMLINK1

KBC3_IMVP4_PWRGD

CHP3_BATLOW*

CHP3_INTRUDER*

PCI3_GNT1*

PCI3_GNT2*

PCI3_RSTF*

PCI3_RST*

ISA3_IRQ(14)

ISA3_IRQ(15)

PCI3_PAR

PCI3_CLKRUN*

PCI3_IRDY*

PCI3_TRDY*

PCI3_INTB*

PCI3_INTC*

PCI3_INTD*

PCI3_PERR*

PCI3_PLOCK*

PCI3_REQ0*

PCI3_REQ1*

PCI3_REQ2*

PCI3_REQ3*

PCI3_INTA*

PCI3_FRAME*

PCI3_REQ4*

CHP3_SERIRQ

PCI3_DEVSEL*

KBC3_EXTSMI*

KBC3_RUNSCI*

KBC3_WAKESCI*

CPU1_SMI*

CPU1_STPCLK*

CPU1_DPSLP*

CPU1_PWRGDCPU

HUB1_HL(0:10)

HUB1_STB

HUB1_STB*

PCI3_INTA*

PCI3_INTB*

PCI3_INTC*

PCI3_INTD*

ISA3_IRQ(14)

ISA3_IRQ(15)

CHP3_SERIRQ

PCI3_GNT0*

PCI3_REQ0*

PCI3_REQ1*

PCI3_REQ2*

PCI3_REQ3*

PCI3_REQ4*

CHP3_BATLOW*

CHP3_CPUSTP*

CHP3_PCISTP*

PCI3_STOP*

PCI3_SERR*

PCI3_AD(31:0)

PCI3_CBE0*

PCI3_CBE1*

PCI3_CBE2*

PCI3_CBE3*

PCI3_DEVSEL*

PCI3_FRAME*

PCI3_IRDY*

PCI3_PAR

PCI3_PLOCK*

PCI3_SERR*

PCI3_STOP*

PCI3_TRDY*

GPIO16

PCI3_RSTF*

PCI3_PERR*

CHP3_PME*

KBC3_A20G

CPU1_A20M*

CPU1_FERR*

CPU1_IGNNE*

CPU1_INIT*

CPU1_INTR

CPU1_NMI

KBC3_CPURST*

CPU1_SLP*

CHP3_DCKSTS

This Document can not be used without Samsung’s authorization.

Page 16

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-16

5-1-1(o) System Main Board Schematic Sheet 16 of 40(ICH4-M)

Function

EEP_DOUT

256MB

No Stuff

128MB

On Board Memory Size

ICH4-m Strapping Options

PC/PCI GNTA*

ICH_SPKR

AC97_SDOUT

Default

No Stuff

No Stuff

A16 swap override

Safe Mode

No Stuff

No Reboot

Reserved

SMB3_ALERT*

CLK3_ICH14

USB3_P5+

GPIO16

LCD3_LAMPSTAT

KBC3_SUSPEND

USB_OC0*

SMB3_DATA CHP3_SMLINK1

SMB3_CLK

USB_OC1*

USB_OC0*

USB_OC1*

CLK3_ICH66

CHP3_SMLINK0

CHP3_OVERT*

CHP3_CRISIS*

CHP3_CRISIS*

USB3_P3+

HDD5_D(0:15)

LPC3_LAD(0:3)

CHP3_SPKR

CHP3_AC97_SDO

CHP3_BIOSWP*

CHP3_BIOSTBL*

CHP3_IVTPWRON

CHP3_1394_ROMW*

CHP3_BKLTON

USB3_P4-

USB3_P4+

USB3_P5-

CHP3_SLPS1*

CPU1_THRMTRIP*

CHP3_SLPS3*

SMB3_DATA

CHP3_SUSCLK

SMB3_CLK

CHP3_SUSSTAT*

CHP3_SPKR

KBC3_RSMRST*

USB3_P0-

USB3_P0+

USB3_P1-

USB3_P1+

USB3_P2-

USB3_P2+

USB3_P3-

HDD5_DACK*

HDD5_DREQ

HDD5_IOR*

HDD5_IOW*

HDD5_IORDY

CHP3_SLPS5*

KBC3_PWRGD

CHP3_RTCRST*

CHP3_VBIAS

CHP3_RTCX1

CHP3_RTCX2

CHP3_AC97_SDO

CHP3_AC97_BCLK

CHP3_AC97_SYNC

CHP3_AC97_RST*

CHP3_AC97_SDI1

CHP3_AC97_SDI0

CLK3_ICH48

CHP3_SLPS4*

CHP3_DPRSLPVR

LPC3_LDRQ0*

LPC3_LFRAME*

HDD5_A0

HDD5_A1

HDD5_A2

HDD5_CS1*

HDD5_CS3*

This Document can not be used without Samsung’s authorization.

Page 17

5 System Schematic Diagrams and PCB Silkscreen

5-17Sens Q 20

5-1-1(p) System Main Board Schematic Sheet 17 of 40(ICH4-M)

100nF *4

Vcc 1.5*8, VccPLL, Vcc H1

P1.5V

100nF *5, 4.7uF *1P3.3V_AUX VccSUS 3.3, VccLAN 3.3

100nF *5 10nF*1

VccSus 1.5, VccLAN 1.5

P3.3V

PRTC_BAT:Can drop to 2.0V(min)

RTC_Battery

Vcc 3.3

P1.5V

Mobile Platform Design Checklist rev 0.91

100nF *6

Pins

CHP3_RTCX1CHP3_VBIAS

CHP3_RTCX2

CHP3_RTCRST*

CHP3_VBIAS

CHP3_RTCRST*

This Document can not be used without Samsung’s authorization.

Page 18

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-18

5-1-1(q) System Main Board Schematic Sheet 18 of 40(FWH)

CHP3_BIOSTBL*

CHP3_BIOSWP*

CLK3_PCLKFWH

PCI3_RST*

CPU1_INIT*

LPC3_LAD(0:3)

LPC3_LFRAME*

This Document can not be used without Samsung’s authorization.

Page 19

5 System Schematic Diagrams and PCB Silkscreen

5-19Sens Q 20

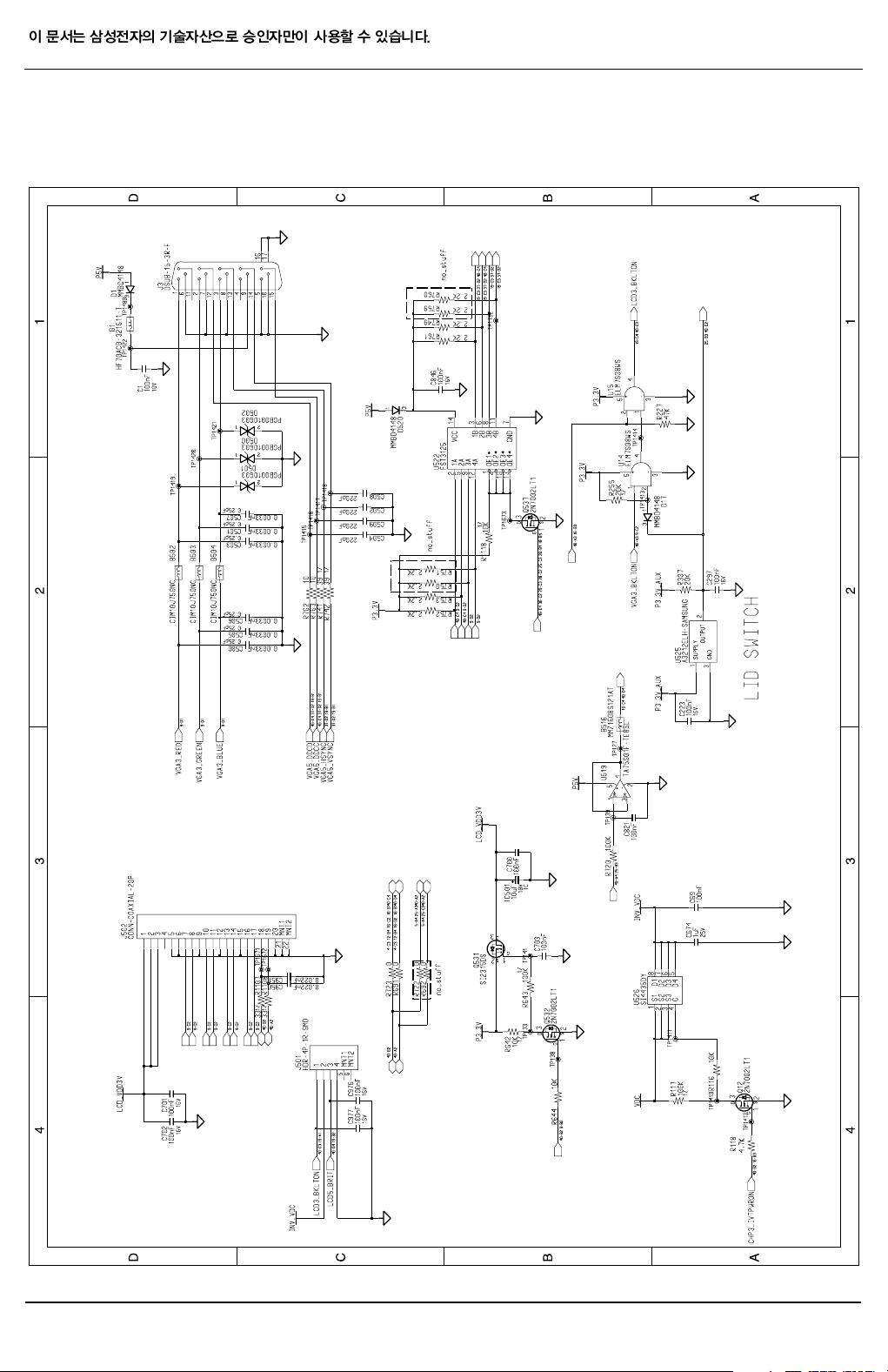

5-1-1(r) System Main Board Schematic Sheet 19 of 40(LCD INTERFACE)

LCD CONNECTOR

CRT CONNECTOR

PHOTO_SMB3_CLK

PHOTO_SMB3_DATA

PCI3_RST*

VGA3_LCDVDDON

LCD5_BRIT

KBC3_BRIT

VGA3_DDCD

VGA3_DDCC

VGA3_HSYNC

VGA3_VSYNC

PHOTO_SMB3_DATA

PHOTO_SMB3_CLK SMB3_CLK

SMB3_DATA

KBC3_THERM_SMCLK

KBC3_THERM_SMDATA

VGA3_A0+

VGA3_A0-

VGA3_CLK+

VGA3_CLK-

VGA3_A2+

VGA3_A2-

VGA3_A1-

VGA3_A1+

CHP3_BKLTON

LID3_SWITCH*

VGA5_DDCD

VGA5_VSYNC

VGA5_HSYNC

VGA5_DDCC

This Document can not be used without Samsung’s authorization.

Page 20

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-20

5-1-1(s) System Main Board Schematic Sheet 20 of 40(CARDBUS & 1394)

-----------GND-----------

-----------GND-----------

---------TPAP0-----------

- It is better no divergence, no-via hole and short wire about IEEE1394 signals.

---------TPAN0-----------

---------TPBN0-----------

- IEEE1394 signals should be designed on outside layers of PCB

---------TPBP0-----------

1.86V

-----------GND-----------

- Place these coil near the connector ACAP.

Implement these ACAP to 5C591

PCI3_INTC*

CLK3_PCLKCB

PCI3_AD(19)

VBUSPWR

VBUSPWR

1394_TPB+

1394_TPA+

CHP3_1394_ROMW*

CB3_SPKR

PCI3_INTA*

CHP3_SERIRQ

PCI3_CBE1*

PCI3_CBE3*

PCI3_INTB*

PCI3_AD(0:31)

1394_TPB-

1394_TPA-

PCI3_CBE0*

KBC3_PWRGD

CHP3_PME*

PCI3_CLKRUN*

PCI3_CBE2*

PCI3_RST*

PCI3_DEVSEL*

PCI3_FRAME*

PCI3_GNT0*

PCI3_IRDY*

PCI3_PAR

PCI3_PERR*

PCI3_REQ0*

PCI3_SERR*

PCI3_STOP*

PCI3_TRDY*

This Document can not be used without Samsung’s authorization.

Page 21

5 System Schematic Diagrams and PCB Silkscreen

5-21Sens Q 20

5-1-1(t) System Main Board Schematic Sheet 21 of 40(CARDBUS & 1394)

1

MemoryStick

1

1

10

0

Memory Card Detect Logic Table

MS_CD*

0

1

0

0

0

1

1

SmartMedia

Socket Frame

Inhibit

Inhibit

SD/MMC

0

0

SM_CD*

1

1

1

Inhibit

SD_CD*

Not Detected

0

1

0

0

Inhibit

1

0

CB3_VCC5EN*

CB3_VPPEN0

CB3_VPPEN1

SD_CD*

MS_INS*

MS_RSVR1

MS_RSVR2

MS_RSVR2

MS_RSVR1

CB3_FUNC1*

CB3_VCC3EN*

CB3_VCC5EN*

CB3_MDVCCEN*

CB3_CCBE1*

CB3_CCBE2*

CB3_CCBE3*

CB3_D14

CB3_D2

CB3_CDEVSEL*

CB3_CFRAME*

CB3_CGNT*

CB3_CINT*

CB3_CIRDY*

CB3_CPAR

CB3_CPERR*

CB3_CREQ*

CB3_CRST*

CB3_CSERR*

CB3_CSTOP*

CB3_CSTSCHG

CB3_CTRDY*

CB3_CVS1

CB3_CVS2

CB3_VCC3EN*

MCCCD*

CB3_FUNC0*

CB3_FUNC1*

CB3_FUNC0*

SD_CD*

CB3_VPPEN1

MCCCD*

CB3_A18

CB3_A19

CB3_CAUDIO

CB3_CCD1*

CB3_CCD2*

CB3_CCLKRUN*

CB3_CCBE0*

CB3_CRST*

CB3_CCD1*

CB3_CCD2*

CB3_VPPEN0

CB3_MDVCCEN*

CB3_CAD(0:31)

MS_INS*

CB3_CSTOP*

CB3_CDEVSEL*

CB3_CTRDY*

CB3_CFRAME*

CB3_CVS2

CB3_CRST*

CB3_CSERR*

CB3_CREQ*

CB3_CCBE3*

CB3_CAUDIO

CB3_CSTSCHG

CB3_CCD2*

CB3_CCLK

CB3_CCBE1*

CB3_CPAR

CB3_CPERR*

CB3_CGNT*

CB3_CINT*

CB3_CCLK

CB3_CIRDY*

CB3_CCBE2*

CB3_D2

CB3_CCLKRUN*

CB3_CCD1*

CB3_CCBE0*

CB3_D14

CB3_CVS1

CB3_A18

CB3_A19

This Document can not be used without Samsung’s authorization.

Page 22

5-1-1(u) System Main Board Schematic Sheet 22 of 40(LOW [BCM5705M])

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-22

Note : All LAN signals should be 5~6mils.

Gemini Name

Aquila Name

LAN3_PHYRST

LAN3_RXD0

LAN3_RXD2

LAN3_PHYCLK

LAN3_RXD1

LAN3_ACT*

LAN3_RDN

LAN3_RDP

100M_LED*

LAN3_TDN

LAN3_TDP

KBC3_LAN_PWROK

LAN3_DCK_TX-

LAN3_DCK_TX+

LAN3_DCK_RX-

LAN3_DCK_RX+

KBC3_DCKIN*

LAN3_TDN

LAN3_TDP

LAN3_RDN

LAN3_RDP

10M_LED*

KBC3_LAN_PWROK

LAN3_TXD0

LAN3_TXD1

LAN3_TXD2

This Document can not be used without Samsung’s authorization.

Page 23

5 System Schematic Diagrams and PCB Silkscreen

5-23Sens Q 20

5-1-1(v) System Main Board Schematic Sheet 23 of 40(LOW [BCM5705M])

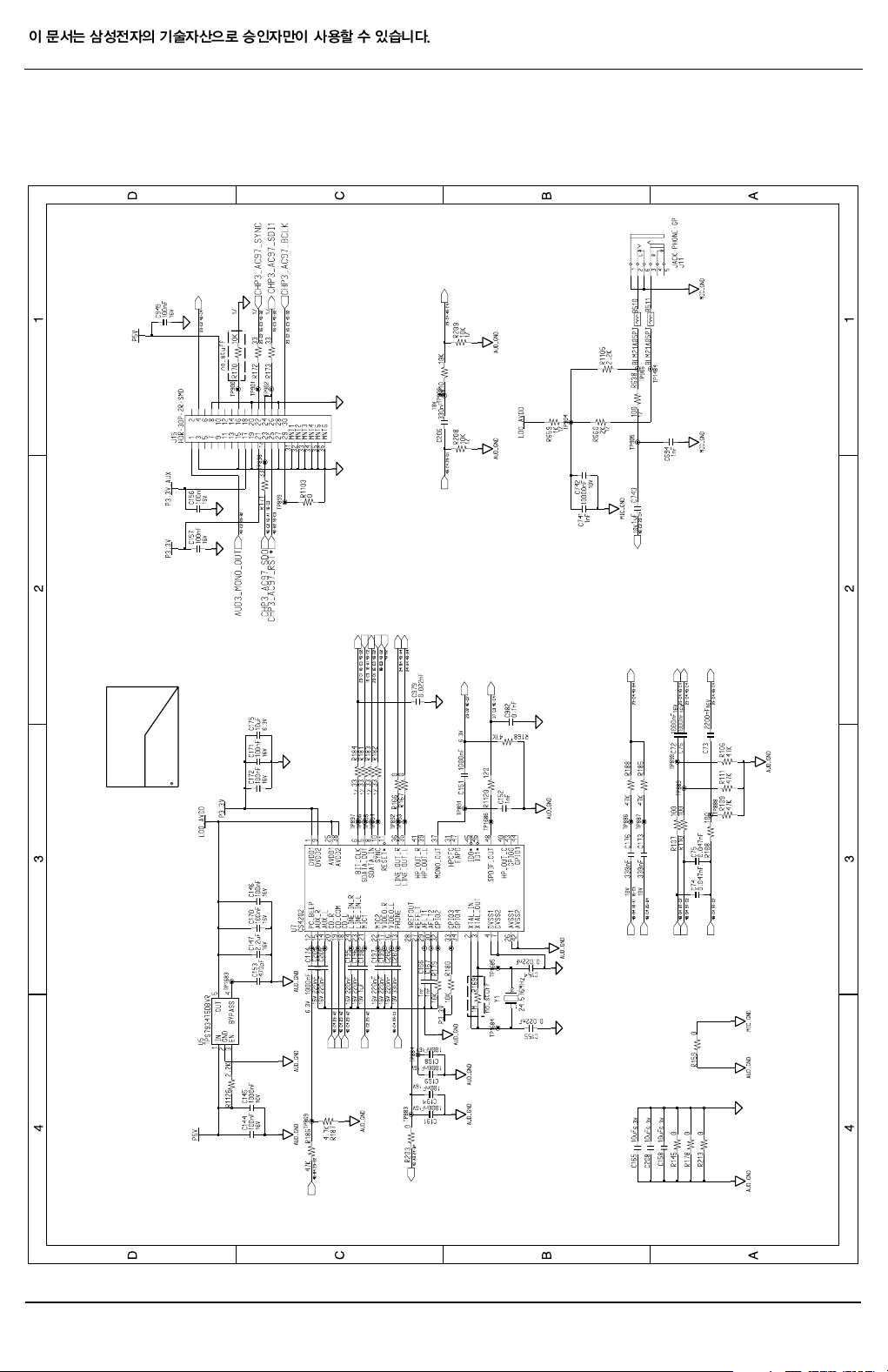

CS4202

1~12, 44~48: Digital GND

Place near HP & MIC conn audio ground partition

13~43 Analog GND

MDC connector

MIC In

CD5_L

CD5_R

CD5_COM

AUD5_CDL

AUD5_CDR

AUD5_CDCOM

AUD5_VREFOUT

LINE_OUT_R

LINE_OUT_L

AUD3_SPDIF

CHP3_AC97_BCLK

CHP3_AC97_SDI0

AUD3_MONO_OUT

AUD3_SPKR

AUD_MIC_CODEC

AUD5_PHONE

AUD5_CDCOM

AUD5_CDL

AUD5_CDR

CHP3_SPKR

CB3_SPKR

AUD3_SPKR

AUD3_PHONE

AUD_MIC_CODEC

AUD3_PHONE AUD5_PHONE

CHP3_AC97_RST*

CHP3_AC97_SDO

CHP3_AC97_SYNC

This Document can not be used without Samsung’s authorization.

Page 24

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-24

5-1-1(w) System Main Board Schematic Sheet 24 of 40(AUDIO)

Min 15mil

HEADPHONE

HP_IN

AUD5_SHUTDOWN

HP_IN

DCK5_LINE_OUT_R

DCK5_LINE_OUT_L

DCK5_SPKR_MUTE

KBC3_SPKMUTE

CHP3_DCKIN*

AUD5_VREFOUT

AUD5_LINE_OUT_R

LINE_OUT_R

AUD5_LINE_OUT_L

LINE_OUT_L

AUD5_SHUTDOWN

HP_IN

AUD5_LINE_OUT_R

AUD5_LINE_OUT_L

AUD5_LINE_OUT_L

AUD5_LINE_OUT_R

This Document can not be used without Samsung’s authorization.

Page 25

5 System Schematic Diagrams and PCB Silkscreen

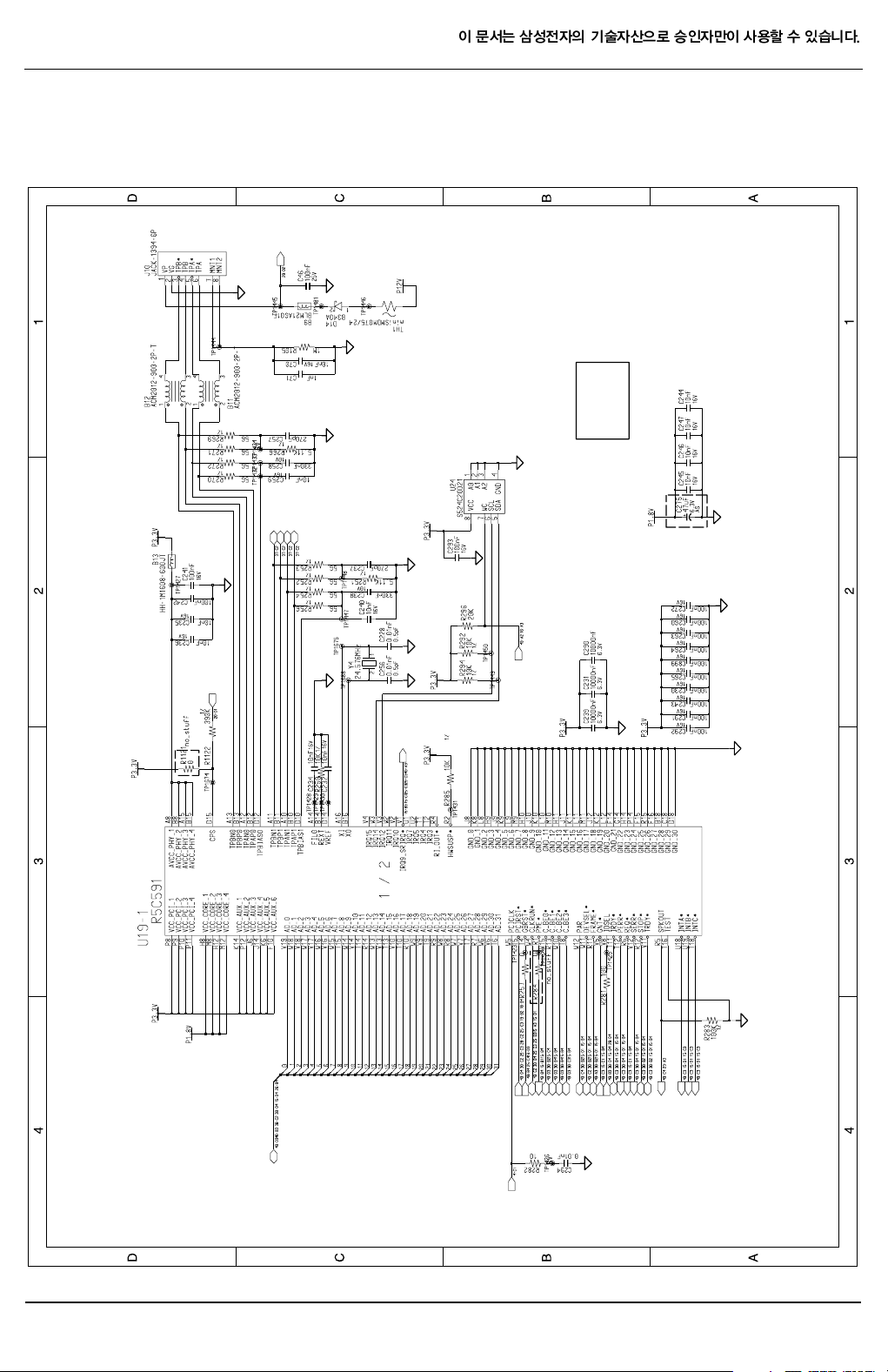

5-25Sens Q 20

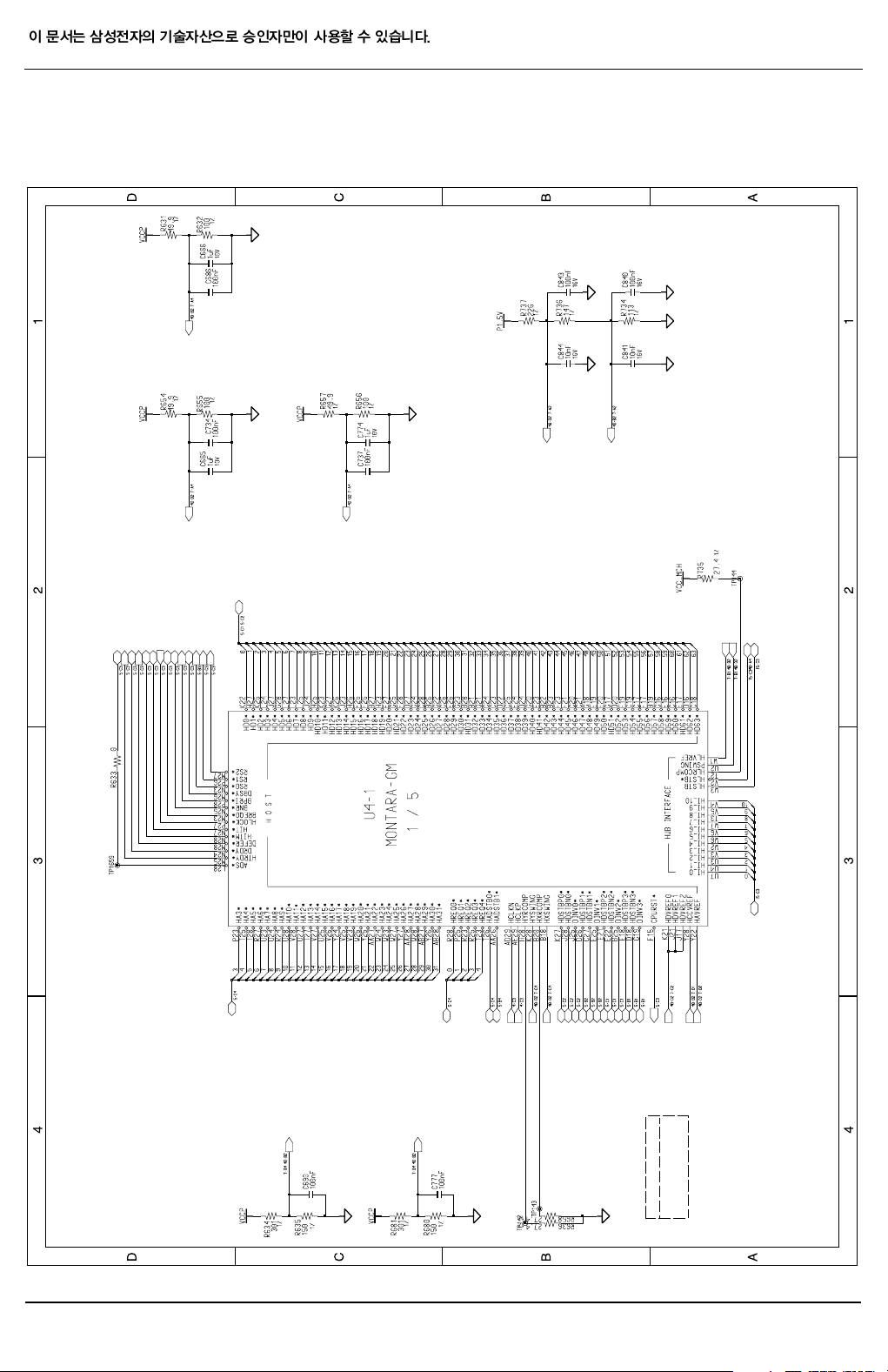

5-1-1(x) System Main Board Schematic Sheet 25 of 40(

MICOM

)

682081

72

A,B,C,D,E,F,G,1,2,3,6

WAKEUP SOURCE

144

RXD

P66 IRQ6

External INT Pin

ON S3

P67 IRQ7

CHP3_SLPS3*

P90 IRQ2

NC

SK : 3704-001155

IC : 0903-001231

P85 IRQ4

109

P92 IRQ0

FAN3_FDBACK*

108 1

P91 IRQ173P84 IRQ3

Port NO. Function

KBC3_THERM_SMCLK

4,5,7,8,9

LAN3_PME*

Internal Pull-up PORTs

TXD

37

Non Internal Pull-up PORTs

ADAPTER_IN*

36

NC

LID3_SWITCH*

P86 IRQ5

Net Name

KBC3_IMVP4_PWRGD

IMVP4_PWRGD

CHP3_THRMTRIP*

CPU1_THRMTRIP*

CPU3_PROCHOT*

CPU1_PROCHOT*

CPU3_PROCHOT*

KBC3_PWRSW*

KBC3_RST*

KBC3_PWRSW*

CLK3_PCLKMICOM

KBC3_LAN_PWROK

CHP3_OVERT*

KBC3_SYSAD

WLAN3_SW_ON*

KBC3_WLAN_ON

KBC5_KSO(0:15)

KBC3_ADID_DCK

KBC5_KSI(0:7)

LID3_SWITCH*

FAN3_FDBACK*

CHP3_SLPS4*

ADAPTOR_IN*

CHP3_SLPS3*

CHP3_SUSSTAT*

CHP3_SLPS1*

CHP3_SLPS5*

KBC3_DCKDCEN

KBC3_PWM

KBC3_THERM_SMDATA

FAN3_ID

KBC3_THERM_SMCLK

SMB3_ALERT*

LAN3_PME*

KBC3_EJECT*

CHP3_THRMTRIP*

LED3_CHARGE

KBC3_RSMRST*

KBC3_DCKPWRON

KBC3_VRON

KBC3_DCKAD

KBC3_SUSPEND

KBC3_SYSCHG

DCK_RST*

KBC3_SPKMUTE

KBC3_CHGEN

LPC3_LAD(0:3)

KBC3_SMDATA

KBC3_CPURST*

BAT3_VOLTA

BAT3_TEMPA

KBC3_DCKIN*

KBC3_A20G

KBC3_SCLED*

KBC3_NUMLED*

KBC3_CAPSLED*

KBC3_PWRGD

KBC3_PWRON

KBC3_SUSPWR

KBC3_BRIT

KBC3_SMCLK

LPC3_LFRAME*

PCI3_RST*

CHP3_SERIRQ

KBC3_WAKESCI*

PCI3_CLKRUN*

KBC5_KCLK

KBC5_KDATA

KBC5_MCLK

KBC5_TCLK

KBC5_MDATA

KBC5_TDATA

KBC3_EXTSMI*

KBC3_RUNSCI*

KBC3_LBLED*

This Document can not be used without Samsung’s authorization.

Page 26

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-26

5-1-1(y) System Main Board Schematic Sheet 26 of 40(

MICOM POWER, POWER SWITCH

)

Switched Power

FOR Function Test

MICOM Power

Power Switch

KBC3_PWRON

KBC3_PWRSW*

KBC3_RST*

SHDN_THER

This Document can not be used without Samsung’s authorization.

Page 27

5 System Schematic Diagrams and PCB Silkscreen

5-27Sens Q 20

5-1-1(z) System Main Board Schematic Sheet 27 of 40(THERMAL SENSOR)

KME FAN : 3WIRE (1,2,4)

Green

Full chargingGreen

Main to LED B D

Power LED S0 : GREEN

FAN

S3 : BLINKING

LED Scheme

Thermal shutdown Sensor

ADAPTERIN/CHARGING LED

Amber

SEPA FAN : 4WIRE(1,2,3,4 : 3 & 4 are shorted)

FDC653N

POWER_ON / LB LED

Charging

Line Width = 20mil

Battery LED

KBC3_LBLED

KBC3_WLAN_ON

ADAPTOR_IN*

AD_SEL

FAN3_ID

FAN3_FDBACK*

KBC3_CAPSLED*

KBC3_NUMLED*

KBC3_SCLED*

HDD3_LED*

LED_AMBER

SHDN_THER

KBC3_PWM

LED_GREEN

KBC3_LBLED

LED_GREEN

LED_AMBER

LED3_CHARGE

PWR_DC

AD_SEL

KBC3_LBLED*

This Document can not be used without Samsung’s authorization.

Page 28

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-28

5-1-1(aa) System Main Board Schematic Sheet 28 of 40(USB, B/T, HDD CONNECTOR)

HDD5_D(0:15)

HDD5_DREQ

HDD5_IOW*

HDD5_IOR*

HDD5_IORDY

HDD5_DACK*

ISA3_IRQ(14)

HDD5_A1

HDD5_A0

HDD5_CS1*

HDD5_LED*

PCI3_RST*

HDD5_LED* HDD3_LED*

HDD5_A2

HDD5_CS3*

This Document can not be used without Samsung’s authorization.

Page 29

5 System Schematic Diagrams and PCB Silkscreen

5-29Sens Q 20

5-1-1(bb) System Main Board Schematic Sheet 29 of 40(SUPER-I/O)

HDD5_D(0:15)

HDD5_DREQ

HDD5_IOW*

HDD5_IOR*

HDD5_IORDY

HDD5_DACK*

ISA3_IRQ(14)

HDD5_A1

HDD5_A0

HDD5_CS1*

HDD5_LED*

PCI3_RST*

HDD5_LED* HDD3_LED*

HDD5_A2

HDD5_CS3*

This Document can not be used without Samsung’s authorization.

Page 30

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-30

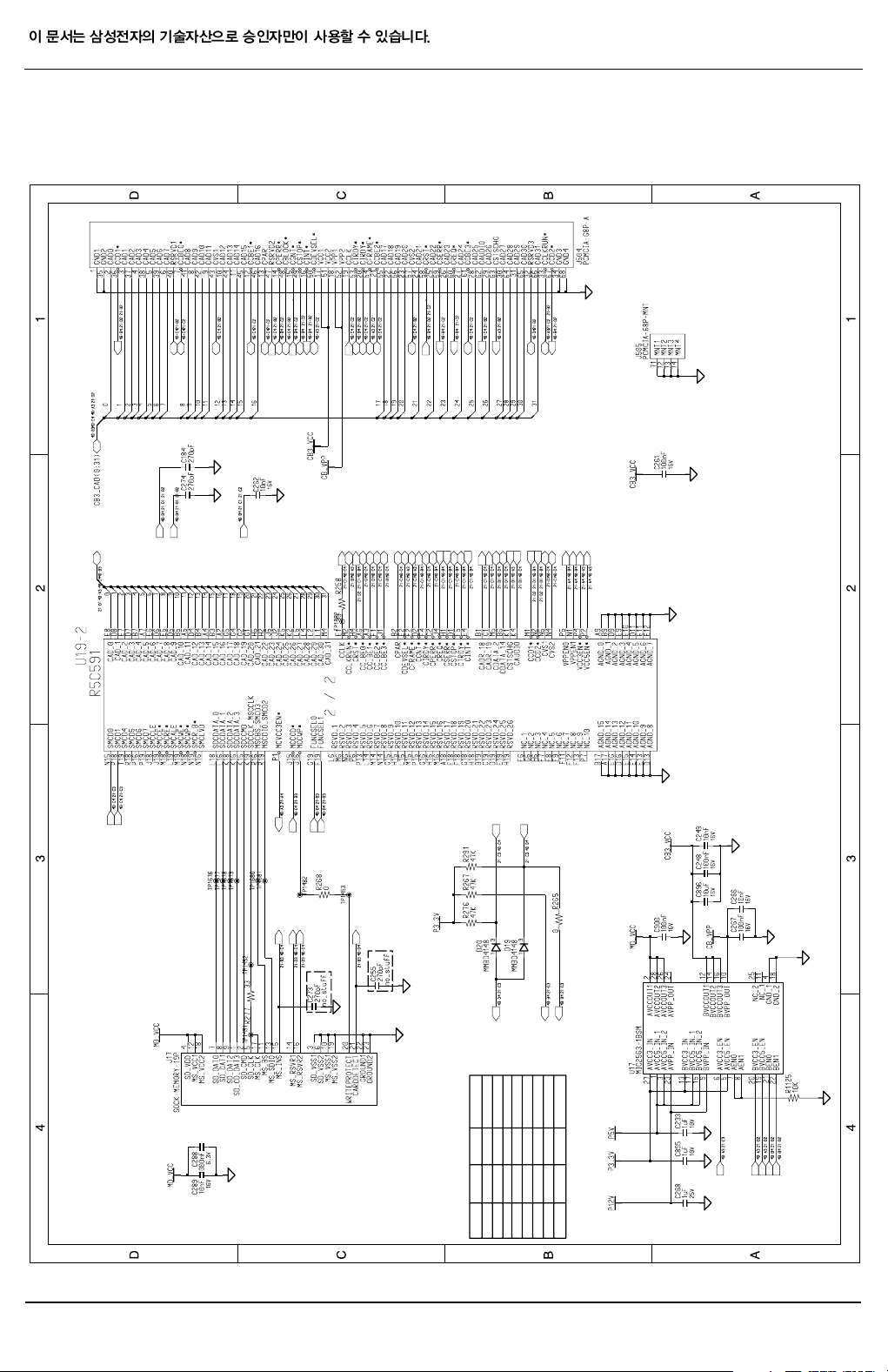

5-1-1(cc) System Main Board Schematic Sheet 30 of 40(MINI-PCI)

Support for Wake On Wireless LAN

5.3mm

MINIPCI

with AC (S3,S4,S5) & BAT (S3) powered status.

Bluetooth

PCI3_AD(0:31)

PCI3_AD(20)

PCI3_CBE2*

PCI3_IRDY*

PCI3_DEVSEL*

PCI3_REQ2* PCI3_GNT2*

LAN3_PME*

PCI3_FRAME*

PCI3_TRDY*

PCI3_STOP*PCI3_SERR*

PCI3_CBE1*

PCI3_CBE0*

PCI3_CBE3*

PCI3_RST*

PCI3_CLKRUN*

PCI3_INTE*

PCI3_INTF*

PCI3_PAR

PCI3_PERR*

CLK3_PCLKMIN

WLAN3_SW_ON*

KBC3_WLAN_ON

USB3_P3-

USB3_P3+

This Document can not be used without Samsung’s authorization.

Page 31

5 System Schematic Diagrams and PCB Silkscreen

5-31Sens Q 20

5-1-1(dd) System Main Board Schematic Sheet 31 of 40(DC/DC, 3.3V_LAN, 5V_AUX)

= 3.307V

919AS-3R7M

Vout =0.8*(1+(470K/150K))

919AS-3R7M

V out=0.8*(1+(270K/51K))

= 5.035V

KBC3_SUSPWR KBC3_SUSPWR

PWR_DC

AD_SEL

KBC3_SYSCHG

SYS_DCIN

KBC3_PWRON

This Document can not be used without Samsung’s authorization.

Page 32

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-32

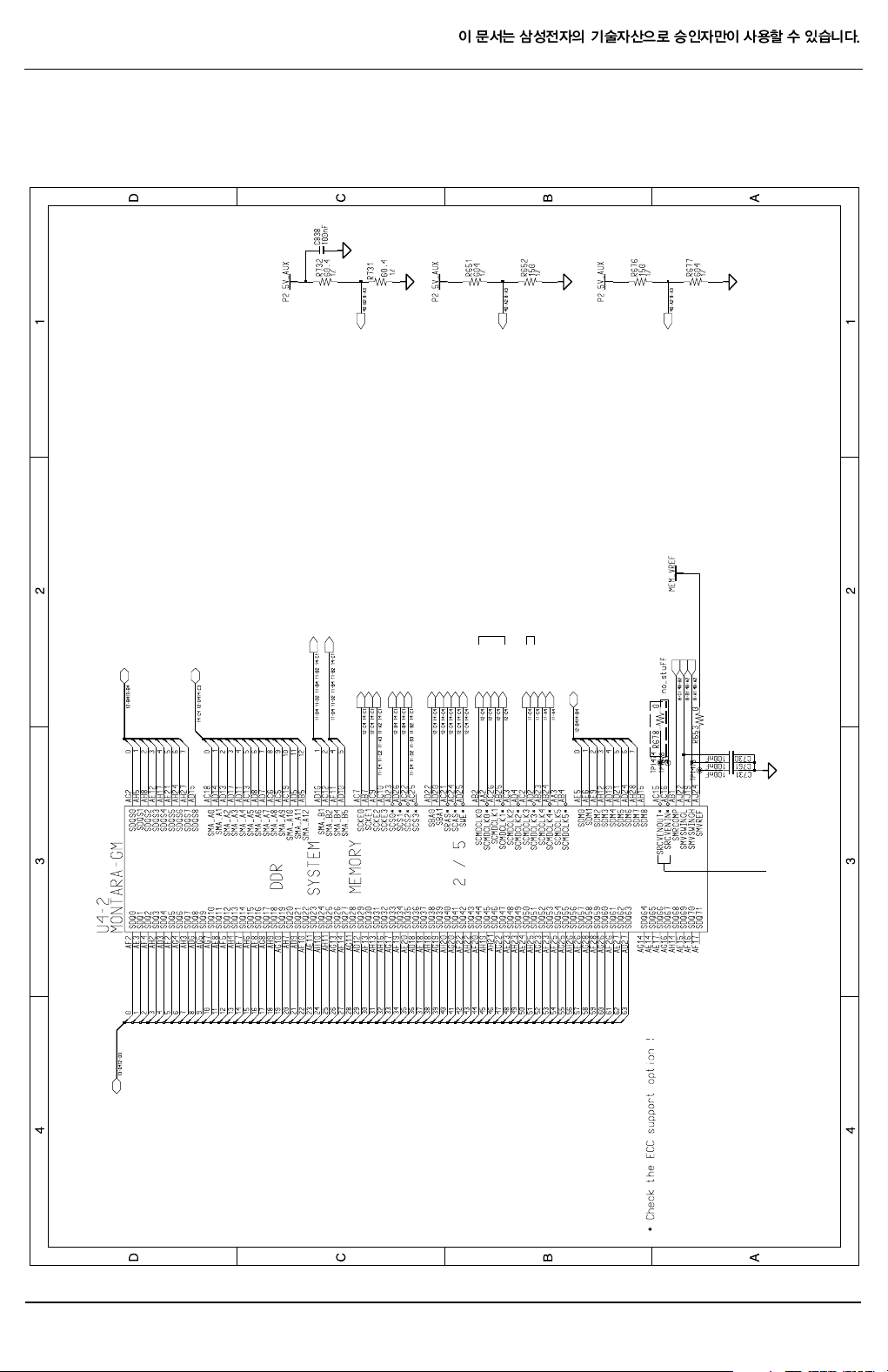

5-1-1(ee) System Main Board Schematic Sheet 32 of 40(DDR 2.5V_AUX, 1.25V)

919AS-4R7M

Main DDR Power

2nd;CDRH104R-5R2;SUMIDA

919AS-4R7M

=2.52V

2nd;RLF7030T-4R7M3R4

Vout =0.9V(1+((43K//30K)/(10K//470K))

KBC3_PWRON*

This Document can not be used without Samsung’s authorization.

Page 33

5 System Schematic Diagrams and PCB Silkscreen

5-33Sens Q 20

5-1-1(ff) System Main Board Schematic Sheet 33 of 40(BATT CHARGER)

919AS-100M

2nd;CDRH104R-100MC;SUMIDA

KBC3_DCKAD

KBC3_SYSAD

DCK_DCIN SYS_DCIN

AD_DCIN

AD_SEL

DCK_DCIN

SYS_DCIN

AD_DCIN

KBC3_CHGEN

This Document can not be used without Samsung’s authorization.

Page 34

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-34

5-1-1(gg) System Main Board Schematic Sheet 34 of 40(VCC_CORE/IMVP4)

1%

1%

VTTPWRGD

S2+

S1+

CHP3_DPRSLPVR

VTTPWRGD

CHP3_CPUSTP*

CPU3_VID(0)

CPU3_VID(1)

CPU3_VID(2)

CPU3_VID(3)

CPU3_VID(5)

S1-

S1+

S2-

S2+

CPU3_VID(4)

S2-

S1-

S1+

S2+

CHP3_THRMTRIP*

CPU1_PSI*

VOS-

IMVP4_PWRGD

This Document can not be used without Samsung’s authorization.

Page 35

5 System Schematic Diagrams and PCB Silkscreen

5-35Sens Q 20

5-1-1(hh) System Main Board Schematic Sheet 35 of 40(VCCP/VCC_MCH)

IHLP-2525-CZ-01

2nd;RLF7030T-6R8M2R8

2nd;RLF7030T-6R8M2R8

This Document can not be used without Samsung’s authorization.

Page 36

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-36

5-1-1(ii) System Main Board Schematic Sheet 36 of 40(1.5V_AUX/1.8V)

Power Sequence Check!

Vo = 0.8(1+20K/(22K+0.649K)) = 1.506V

2nd;SLF7045T-4R7M2R0

A915AY_4R7M

KBC3_PWRON

KBC3_SUSPWR

KBC3_PWRON

KBC3_PWRON

This Document can not be used without Samsung’s authorization.

Page 37

5 System Schematic Diagrams and PCB Silkscreen

5-37Sens Q 20

5-1-1(jj) System Main Board Schematic Sheet 37 of 40(DOCKING CONNECTOR)

CHARGE FROM MEDIABASE

MOUNT101

104

MOUNT102 + MOUNT104

MOUNT103

99

+ 3pin (5,7,9)

DISCHARGE

CHARGE FROM MAIN

101

2

1

100

102

103

LAN3_ACT*

10M_LED*

DCK_VGA3_GREEN

DCK_VGA3_BLUE

DCK_VGA3_RED

LAN3_DCK_RX+

FDD3_TRK0*

FDD3_WDATA*

FDD3_DIR*

FDD3_DSKCHG*

FDD3_INDEX*

FDD3_WGATE*

FDD3_STEP*

FDD3_MTR0*

FDD3_DS0*

FDD3_J3MODE

FDD3_WP*

FDD3_HDSEL*

DCK5_LINE_OUT_R

DCK5_LINE_OUT_L

CD5_COM

CD5_R

CD5_L

DCK5_SPKR_MUTE

DCK_DCIN

100M_LED*

AUD3_SPDIF

KBC3_DCKDCEN

USB3_P4-

USB3_P4+

USB3_P5-

USB3_P5+

VGA5_HSYNC

VGA5_DDCC

VGA5_DDCD

DCK_VGA3_BLUE

DCK_VGA3_GREEN

DCK_VGA3_RED

VGA5_VSYNC

USB3_P2-

USB3_P2+

CHP3_DCKSTS

1394_TPA+

1394_TPA-

1394_TPB+

1394_TPB-

LAN3_DCK_TX-

LAN3_DCK_TX+

DCK3_DOCK_IN1*

LAN3_DCK_RX-

PIO3_ERROR*

PIO3_AUTOFD*

PIO3_SLCT

SIO3_TXD1*

SIO3_DTR1*

KBC5_MDATA

KBC5_MCLK

KBC5_KDATA

KBC5_KCLK

SIO3_DCD1*

SIO3_DSR1*

SIO3_RXD1

SIO3_RI1*

SIO3_CTS1*

KBC3_DCKDCEN

KBC3_EJECT*

KBC3_DCKIN*

DCK_RST*

SIO3_RTS1*

KBC3_DCKPWRON

PIO3_PD(0:7)

FDD3_RDATA*

DCK3_DOCK_IN1*

DCK3_DOCK_IN2*

CHP3_DCKIN*

PIO3_PE

PIO3_BUSY

PIO3_ACK*

PIO3_STROBE*

KBC3_ADID_DCK

DCK3_DOCK_IN2*

PIO3_SLCTIN*

PIO3_INIT*

This Document can not be used without Samsung’s authorization.

Page 38

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-38

5-1-1(kk) System Main Board Schematic Sheet 38 of 40(MOUNT HOLE)

This Document can not be used without Samsung’s authorization.

Page 39

5 System Schematic Diagrams and PCB Silkscreen

5-39Sens Q 20

This Document can not be used without Samsung’s authorization.

5-1-1(ll) System Main Board Schematic Sheet 39 of 40(TOUCHPAD IF BOARD)

Place on Top side

Main to Touchpad IF board

# LED IF BOARD

Touchpad IF board to Touchpad

T_SWR*

T_SWL*

T_TDATA

T_TCLK

T_TCLK

T_SWR*

T_SWL*

T_TDATA

LED3_BTLED_ON*

LED3_NUMLED*

LED3_HDDLED*

LED3_AMBER

LED3_CAPSLED*

LED3_NUMLED*

LED3_SCLED*

LED3_HDDLED*

LED3_GREEN

LED3_AMBER

LED3_LBLED

LED3_BTLED_ON*

LED3_SCLED*

LED3_CAPSLED*

LED3_LBLED

LED3_GREEN

Page 40

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-40

This Document can not be used without Samsung’s authorization.

5-1-1(mm) System Main Board Schematic Sheet 40 of 40(UNDEFINED)

500~ SIDE

1~499 SIDE

Page 41

5 System Schematic Diagrams and PCB Silkscreen

5-41Sens Q 20

5-2 PCB Silkscreen

This Document can not be used without Samsung’s authorization.

Page 42

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-42

This Document can not be used without Samsung’s authorization.

Page 43

5 System Schematic Diagrams and PCB Silkscreen

5-3 System Main Part List

5-43Sens Q 20

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

AJ450 3708-001276 CONNECTOR-FPC/FFC/PIC;12P

AJ451 3708-001276 CONNECTOR-FPC/FFC/PIC;12P

AR1 2011-001402 R-NETWORK;56OHM

AR2 2011-001402 R-NETWORK;56OHM

AR3 2011-001402 R-NETWORK;56OHM

AR4 2011-001402 R-NETWORK;56OHM

AR5 2011-001402 R-NETWORK;56OHM

AR6 2011-001402 R-NETWORK;56OHM

AR7 2011-001402 R-NETWORK;56OHM

AR8 2011-001402 R-NETWORK;56OHM

AR9 2011-001402 R-NETWORK;56OHM

AR10 2011-001402 R-NETWORK;56OHM

AR11 2011-001402 R-NETWORK;56OHM

AR500 2011-001402 R-NETWORK;56OHM

AR501 2011-001402 R-NETWORK;56OHM

AR502 2011-001264 R-NETWORK;10ohm

AR503 2011-001264 R-NETWORK;10ohm

AR504 2011-001264 R-NETWORK;10ohm

AR505 2011-001264 R-NETWORK;10ohm

AR506 2011-001264 R-NETWORK;10ohm

AR507 2011-001264 R-NETWORK;10ohm

AR508 2011-001264 R-NETWORK;10ohm

AR509 2011-001264 R-NETWORK;10ohm

AR510 2011-001264 R-NETWORK;10ohm

AR511 2011-001264 R-NETWORK;10ohm

AR512 2011-001264 R-NETWORK;10ohm

AR513 2011-001264 R-NETWORK;10ohm

AR514 2011-001264 R-NETWORK;10ohm

AR515 2011-001264 R-NETWORK;10ohm

AR516 2011-001264 R-NETWORK;10ohm

AR517 2011-001402 R-NETWORK;56OHM

ASW1100

3404-001052 SWITCH-TACT;12V

ASW1101

3404-001052 SWITCH-TACT;12V

B1 3301-000322 CORE-FERRITE

B2 3301-001162 CORE-FERRITE

B3 3301-001162 CORE-FERRITE

B4 3301-001434 CORE-FERRITE

B5 3301-001434 CORE-FERRITE

B6 3301-000314 CORE-FERRITE

B7 3301-000314 CORE-FERRITE

Ref. PART NO. DESCRIPTION

B8 3301-000314 CORE-FERRITE

B9 3301-001101 CORE-FERRITE

B10 3301-001594 CORE-FERRITE

B11 3301-001594 CORE-FERRITE

B12 3301-001594 CORE-FERRITE

B13 3301-001148 CORE-FERRITE

B500 3301-001272 CORE-FERRITE

B501 3301-001272 CORE-FERRITE

B502 3301-001499 CORE-FERRITE

B503 3301-001499 CORE-FERRITE

B504 3301-001499 CORE-FERRITE

B505 3301-001594 CORE-FERRITE

B506 3301-001434 CORE-FERRITE

B507 3301-001434 CORE-FERRITE

B508 3301-000326 CORE-FERRITE

B509 3301-000326 CORE-FERRITE

B510 3301-000317 CORE-FERRITE

B511 3301-000317 CORE-FERRITE

B512 3301-000314 CORE-FERRITE

B513 3301-000314 CORE-FERRITE

B514 3301-000314 CORE-FERRITE

B515 3301-000314 CORE-FERRITE

B516 3301-000314 CORE-FERRITE

B517 3301-001101 CORE-FERRITE

B518 3301-001101 CORE-FERRITE

B519 3301-001101 CORE-FERRITE

B520 3301-000326 CORE-FERRITE

B522 3301-000314 CORE-FERRITE

B523 3301-000314 CORE-FERRITE

B524 3301-001233 CORE-FERRITE

C1 2203-005482 C-CERAMIC

C2 2203-005061 C-CERAMIC

C3 2203-000438 C-CERAMIC

C4 2203-005061 C-CERAMIC

C5 2203-005061 C-CERAMIC

C6 2203-005664 C-CERAMIC

C7 2203-005198 C-CERAMIC

C8 2203-005261 C-CERAMIC

C9 2203-000254 C-CERAMIC

C10 2203-005198 C-CERAMIC

Page 44

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-44

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C11 2203-005918 C-CERAMIC

C12 2203-000438 C-CERAMIC

C13 2203-005619 C-CERAMIC

C14 2203-000438 C-CERAMIC

C15 2203-000233 C-CERAMIC

C16 2203-000233 C-CERAMIC

C17 2203-000233 C-CERAMIC

C18 2402-001125 C-POLYMER

C26 2203-000206 C-CERAMIC

C27 2203-000206 C-CERAMIC

C28 2402-001170 C-POLYMER

C30 2203-005482 C-CERAMIC

C31 2203-000206 C-CERAMIC

C32 2203-002720 C-CERAMIC

C33 2203-005482 C-CERAMIC

C34 2402-001125 C-POLYMER

C38 2203-000576 C-CERAMIC

C39 2203-005664 C-CERAMIC

C40 2203-005198 C-CERAMIC

C41 2203-005664 C-CERAMIC

C42 2203-005254 C-CERAMIC

C43 2203-005198 C-CERAMIC

C44 2203-000585 C-CERAMIC

C45 2203-005061 C-CERAMIC

C46 2203-000189 C-CERAMIC

C47 2402-001125 C-POLYMER

C48 2402-001170 C-POLYMER

C49 2203-005261 C-CERAMIC

C50 2203-000254 C-CERAMIC

C51 2203-005198 C-CERAMIC

C52 2203-000257 C-CERAMIC

C53 2203-000575 C-CERAMIC

C54 2203-000575 C-CERAMIC

C55 2203-000140 C-CERAMIC

C56 2203-000206 C-CERAMIC

C57 2203-000206 C-CERAMIC

C58 2203-000206 C-CERAMIC

C59 2203-002720 C-CERAMIC

C60 2203-005482 C-CERAMIC

C61 2203-005482 C-CERAMIC

Ref. PART NO. DESCRIPTION

3C62 2203-005482 C-CERAMIC

C63 2402-001168 C-POLYMER

C64 2203-005061 C-CERAMIC

C65 2203-000489 C-CERAMIC

C66 2203-000233 C-CERAMIC

C67 2203-000938 C-CERAMIC

C68 2203-000233 C-CERAMIC

C69 2203-005254 C-CERAMIC

C70 2203-000254 C-CERAMIC

C71 2203-000438 C-CERAMIC

C72 2203-000476 C-CERAMIC

C73 2203-001598 C-CERAMIC

C74 2203-000995 C-CERAMIC

C75 2203-000995 C-CERAMIC

C76 2203-000476 C-CERAMIC

C77 2402-001169 C-POLYMER

C78 2203-005482 C-CERAMIC

C79 2203-000438 C-CERAMIC

C80 2203-005061 C-CERAMIC

C81 2203-000254 C-CERAMIC

C82 2402-001168 C-POLYMER

C84 2402-001168 C-POLYMER

C85 2203-000206 C-CERAMIC

C86 2203-000206 C-CERAMIC

C87 2402-001169 C-POLYMER

C88 2203-000278 C-CERAMIC

C89 2203-000278 C-CERAMIC

C90 2203-000254 C-CERAMIC

C91 2203-005061 C-CERAMIC

C92 2203-000254 C-CERAMIC

C93 2203-000254 C-CERAMIC

C94 2203-000254 C-CERAMIC

C95 2203-005061 C-CERAMIC

C96 2203-005061 C-CERAMIC

C97 2203-005061 C-CERAMIC

C98 2203-005061 C-CERAMIC

C99 2203-005061 C-CERAMIC

C100 2203-000254 C-CERAMIC

C101 2203-000254 C-CERAMIC

C102 2203-000254 C-CERAMIC

Page 45

5 System Schematic Diagrams and PCB Silkscreen

5-45Sens Q 20

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C103 2203-000254 C-CERAMIC

C104 2203-000254 C-CERAMIC

C105 2203-005061 C-CERAMIC

C106 2203-000254 C-CERAMIC

C107 2203-000254 C-CERAMIC

C108 2203-000254 C-CERAMIC

C109 2203-000254 C-CERAMIC

C110 2203-005061 C-CERAMIC

C111 2402-001045 C-AL

C112 2402-001045 C-AL

C113 2203-005061 C-CERAMIC

C114 2203-000254 C-CERAMIC

C115 2203-005061 C-CERAMIC

C116 2203-000254 C-CERAMIC

C117 2203-000254 C-CERAMIC

C118 2203-005061 C-CERAMIC

C119 2203-000254 C-CERAMIC

C120 2203-000254 C-CERAMIC

C121 2203-005061 C-CERAMIC

C122 2402-001045 C-AL

C123 2402-001045 C-AL

C124 2203-000254 C-CERAMIC

C125 2203-005061 C-CERAMIC

C126 2203-005061 C-CERAMIC

C127 2203-000254 C-CERAMIC

C128 2402-001167 C-POLYMER

C129 2203-005061 C-CERAMIC

C130 2203-000278 C-CERAMIC

C131 2203-005061 C-CERAMIC

C132 2203-000278 C-CERAMIC

C133 2203-000254 C-CERAMIC

C134 2203-005061 C-CERAMIC

C135 2203-000254 C-CERAMIC

C136 2203-000254 C-CERAMIC

C137 2203-000254 C-CERAMIC

C138 2203-005061 C-CERAMIC

C139 2203-000254 C-CERAMIC

C140 2203-005061 C-CERAMIC

C141 2203-000254 C-CERAMIC

C142 2203-005061 C-CERAMIC

Ref. PART NO. DESCRIPTION

C143 2402-001167 C-POLYMER

C144 2203-005061 C-CERAMIC

C145 2203-005065 C-CERAMIC

C146 2203-005061 C-CERAMIC

C147 2203-000513 C-CERAMIC

C149 2203-000438 C-CERAMIC

C151 2203-006093 C-CERAMIC

C152 2203-000438 C-CERAMIC

C153 2203-000940 C-CERAMIC

C154 2203-000628 C-CERAMIC

C155 2203-000628 C-CERAMIC

C156 2203-005061 C-CERAMIC

C157 2203-005061 C-CERAMIC

C158 2203-005571 C-CERAMIC

C159 2203-000278 C-CERAMIC

C160 2203-000278 C-CERAMIC

C161 2203-005061 C-CERAMIC

C162 2203-000254 C-CERAMIC

C164 2402-001167 C-POLYMER

C165 2203-005571 C-CERAMIC

C166 2203-000438 C-CERAMIC

C167 2203-000438 C-CERAMIC

C168 2203-005061 C-CERAMIC

C169 2203-000476 C-CERAMIC

C170 2203-005061 C-CERAMIC

C171 2203-005061 C-CERAMIC

C172 2203-005061 C-CERAMIC

C173 2203-005509 C-CERAMIC

C174 2203-006093 C-CERAMIC

C175 2203-005571 C-CERAMIC

C176 2203-005509 C-CERAMIC

C177 2203-005198 C-CERAMIC

C178 2203-005061 C-CERAMIC

C179 2203-005061 C-CERAMIC

C180 2203-005061 C-CERAMIC

C181 2203-002720 C-CERAMIC

C182 2203-005061 C-CERAMIC

C183 2203-005061 C-CERAMIC

C184 2203-000654 C-CERAMIC

C185 2203-005061 C-CERAMIC

Page 46

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-46

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C186 2203-000254 C-CERAMIC

C187 2203-005571 C-CERAMIC

C188 2203-005571 C-CERAMIC

C189 2203-005061 C-CERAMIC

C190 2203-005571 C-CERAMIC

C191 2203-000476 C-CERAMIC

C192 2203-005918 C-CERAMIC

C193 2203-000628 C-CERAMIC

C194 2203-005061 C-CERAMIC

C195 2203-005493 C-CERAMIC

C196 2203-005493 C-CERAMIC

C197 2203-005493 C-CERAMIC

C198 2203-005198 C-CERAMIC

C199 2203-005493 C-CERAMIC

C200 2203-000628 C-CERAMIC

C201 2203-000438 C-CERAMIC

C202 2203-005493 C-CERAMIC

C203 2203-005918 C-CERAMIC

C204 2203-005493 C-CERAMIC

C205 2203-005493 C-CERAMIC

C206 2203-005509 C-CERAMIC

C207 2203-005509 C-CERAMIC

C208 2203-005571 C-CERAMIC

C209 2203-005065 C-CERAMIC

C210 2203-000330 C-CERAMIC

C211 2203-005509 C-CERAMIC

C212 2203-005061 C-CERAMIC

C213 2203-005437 C-CERAMIC

C214 2203-000330 C-CERAMIC

C215 2203-005061 C-CERAMIC

C216 2203-005065 C-CERAMIC

C217 2203-000628 C-CERAMIC

C218 2203-006093 C-CERAMIC

C219 2203-005061 C-CERAMIC

C220 2203-005061 C-CERAMIC

C221 2203-005061 C-CERAMIC

C222 2203-005061 C-CERAMIC

C223 2203-005148 C-CERAMIC

C224 2203-000298 C-CERAMIC

C225 2203-000278 C-CERAMIC

Ref. PART NO. DESCRIPTION

C226 2203-005061 C-CERAMIC

C227 2203-000628 C-CERAMIC

C228 2203-000278 C-CERAMIC

C229 2203-000278 C-CERAMIC

C230 2203-005061 C-CERAMIC

C231 2203-006090 C-CERAMIC

C232 2203-000254 C-CERAMIC

C233 2203-005198 C-CERAMIC

C234 2203-000254 C-CERAMIC

C235 2203-000254 C-CERAMIC

C236 2203-000254 C-CERAMIC

C237 2203-000654 C-CERAMIC

C238 2203-005509 C-CERAMIC

C239 2203-006090 C-CERAMIC

C240 2203-000254 C-CERAMIC

C241 2203-005061 C-CERAMIC

C242 2203-005061 C-CERAMIC

C243 2203-005061 C-CERAMIC

C244 2203-000254 C-CERAMIC

C245 2203-000254 C-CERAMIC

C246 2203-000254 C-CERAMIC

C247 2203-000254 C-CERAMIC

C248 2203-005061 C-CERAMIC

C249 2203-000254 C-CERAMIC

C250 2203-000278 C-CERAMIC

C251 2203-000278 C-CERAMIC

C252 2402-001170 C-POLYMER

C253 2203-005061 C-CERAMIC

C254 2203-000254 C-CERAMIC

C255 2203-000654 C-CERAMIC

C256 2203-000278 C-CERAMIC

C257 2203-000654 C-CERAMIC

C258 2203-005509 C-CERAMIC

C259 2203-000254 C-CERAMIC

C260 2203-005061 C-CERAMIC

C261 2203-005061 C-CERAMIC

C262 2203-000254 C-CERAMIC

C263 2203-005061 C-CERAMIC

C264 2203-005061 C-CERAMIC

C265 2203-005061 C-CERAMIC

Page 47

5 System Schematic Diagrams and PCB Silkscreen

5-47Sens Q 20

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C266 2203-000254 C-CERAMIC

C267 2203-005061 C-CERAMIC

C268 2203-000483 C-CERAMIC

C269 2203-005061 C-CERAMIC

C270 2203-006143 C-CERAMIC

C271 2203-005061 C-CERAMIC

C272 2203-005061 C-CERAMIC

C273 2203-000654 C-CERAMIC

C274 2203-000654 C-CERAMIC

C275 2402-001045 C-AL

C276 2203-000476 C-CERAMIC

C277 2203-000476 C-CERAMIC

C278 2203-005198 C-CERAMIC

C279 2203-005061 C-CERAMIC

C280 2203-005061 C-CERAMIC

C281 2203-000062 C-CERAMIC

C282 2402-001169 C-POLYMER

C283 2203-000476 C-CERAMIC

C284 2203-000233 C-CERAMIC

C285 2203-000438 C-CERAMIC

C286 2203-005655 C-CERAMIC

C287 2203-005061 C-CERAMIC

C288 2203-005655 C-CERAMIC

C289 2203-000254 C-CERAMIC

C290 2203-006090 C-CERAMIC

C291 2203-005061 C-CERAMIC

C292 2203-005061 C-CERAMIC

C293 2203-005061 C-CERAMIC

C294 2203-000278 C-CERAMIC

C295 2203-005061 C-CERAMIC

C296 2203-000438 C-CERAMIC

C297 2203-005148 C-CERAMIC

C500 2203-005052 C-CERAMIC

C501 2203-005052 C-CERAMIC

C502 2203-000585 C-CERAMIC

C503 2203-005052 C-CERAMIC

C504 2203-000585 C-CERAMIC

C505 2203-005052 C-CERAMIC

C506 2203-005052 C-CERAMIC

C507 2203-005052 C-CERAMIC

Ref. PART NO. DESCRIPTION

C508 2203-000585 C-CERAMIC

C509 2203-000585 C-CERAMIC

C510 2203-000995 C-CERAMIC

C511 2203-005571 C-CERAMIC

C512 2203-005571 C-CERAMIC

C513 2203-005571 C-CERAMIC

C514 2203-005061 C-CERAMIC

C515 2203-000257 C-CERAMIC

C516 2203-000206 C-CERAMIC

C517 2203-000233 C-CERAMIC

C518 2203-000438 C-CERAMIC

C519 2203-000438 C-CERAMIC

C520 2203-000585 C-CERAMIC

C521 2203-000585 C-CERAMIC

C522 2203-000438 C-CERAMIC

C523 2203-002720 C-CERAMIC

C524 2203-000995 C-CERAMIC

C525 2203-000438 C-CERAMIC

C526 2203-000604 C-CERAMIC

C527 2203-000206 C-CERAMIC

C528 2402-001125 C-POLYMER

C530 2203-000206 C-CERAMIC

C531 2402-001125 C-POLYMER

C532 2402-001125 C-POLYMER

C533 2203-001103 C-CERAMIC

C534 2203-000206 C-CERAMIC

C535 2203-005261 C-CERAMIC

C536 2203-000254 C-CERAMIC

C537 2203-005061 C-CERAMIC

C538 2203-005482 C-CERAMIC

C539 2203-000254 C-CERAMIC

C540 2203-005482 C-CERAMIC

C541 2203-005482 C-CERAMIC

C542 2203-005061 C-CERAMIC

C543 2203-006090 C-CERAMIC

C544 2203-006090 C-CERAMIC

C545 2402-001168 C-POLYMER

C546 2203-005061 C-CERAMIC

C547 2203-000995 C-CERAMIC

C548 2203-000178 C-CERAMIC

Page 48

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-48

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C549 2203-000206 C-CERAMIC

C550 2203-000206 C-CERAMIC

C551 2203-000189 C-CERAMIC

C552 2203-000233 C-CERAMIC

C553 2203-005482 C-CERAMIC

C554 2203-005254 C-CERAMIC

C555 2203-005254 C-CERAMIC

C556 2203-002720 C-CERAMIC

C557 2203-002720 C-CERAMIC

C558 2203-000260 C-CERAMIC

C559 2203-002720 C-CERAMIC

C560 2203-001397 C-CERAMIC

C561 2203-001662 C-CERAMIC

C562 2203-000438 C-CERAMIC

C563 2203-000575 C-CERAMIC

C564 2203-005261 C-CERAMIC

C565 2203-000206 C-CERAMIC

C566 2203-001103 C-CERAMIC

C567 2203-000438 C-CERAMIC

C568 2203-005482 C-CERAMIC

C569 2203-005482 C-CERAMIC

C570 2402-001167 C-POLYMER

C571 2203-006090 C-CERAMIC

C572 2203-006090 C-CERAMIC

C573 2203-006090 C-CERAMIC

C574 2203-006090 C-CERAMIC

C575 2203-006090 C-CERAMIC

C576 2203-006090 C-CERAMIC

C577 2203-006090 C-CERAMIC

C578 2203-006090 C-CERAMIC

C579 2203-006090 C-CERAMIC

C580 2203-006090 C-CERAMIC

C581 2203-006090 C-CERAMIC

C582 2203-006090 C-CERAMIC

C583 2203-006090 C-CERAMIC

C584 2203-006090 C-CERAMIC

C585 2203-006090 C-CERAMIC

C586 2203-006090 C-CERAMIC

C587 2402-001168 C-POLYMER

C588 2203-001103 C-CERAMIC

Ref. PART NO. DESCRIPTION

C589 2203-000206 C-CERAMIC

C590 2203-001103 C-CERAMIC

C591 2203-000206 C-CERAMIC

C592 2203-000576 C-CERAMIC

C593 2203-000995 C-CERAMIC

C594 2203-005614 C-CERAMIC

C595 2203-005061 C-CERAMIC

C596 2203-005619 C-CERAMIC

C597 2203-000257 C-CERAMIC

C598 2203-005664 C-CERAMIC

C599 2203-005148 C-CERAMIC

C600 2203-005619 C-CERAMIC

C601 2203-005261 C-CERAMIC

C602 2203-001103 C-CERAMIC

C603 2203-000206 C-CERAMIC

C604 2402-001125 C-POLYMER

C605 2203-005655 C-CERAMIC

C606 2203-002050 C-CERAMIC

C607 2203-005619 C-CERAMIC

C608 2402-001125 C-POLYMER

C609 2203-001103 C-CERAMIC

C610 2203-000206 C-CERAMIC

C611 2203-005261 C-CERAMIC

C612 2203-005482 C-CERAMIC

C613 2203-005482 C-CERAMIC

C614 2203-005482 C-CERAMIC

C615 2203-006090 C-CERAMIC

C616 2203-006090 C-CERAMIC

C617 2203-006090 C-CERAMIC

C618 2203-006090 C-CERAMIC

C619 2203-005482 C-CERAMIC

C620 2203-005482 C-CERAMIC

C621 2203-006090 C-CERAMIC

C622 2203-006090 C-CERAMIC

C623 2203-006090 C-CERAMIC

C624 2203-006090 C-CERAMIC

C625 2203-006090 C-CERAMIC

C626 2203-006090 C-CERAMIC

C627 2203-006090 C-CERAMIC

C628 2203-006090 C-CERAMIC

Page 49

5 System Schematic Diagrams and PCB Silkscreen

5-49Sens Q 20

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C629 2203-006090 C-CERAMIC

C630 2203-006090 C-CERAMIC

C631 2203-006090 C-CERAMIC

C632 2203-006090 C-CERAMIC

C633 2203-006090 C-CERAMIC

C634 2402-001168 C-POLYMER

C635 2402-001125 C-POLYMER

C636 2402-001125 C-POLYMER

C637 2402-001125 C-POLYMER

C638 2402-001125 C-POLYMER

C639 2203-001686 C-CERAMIC

C640 2203-000438 C-CERAMIC

C641 2203-000438 C-CERAMIC

C642 2203-005437 C-CERAMIC

C643 2203-005664 C-CERAMIC

C644 2203-000254 C-CERAMIC

C645 2203-000940 C-CERAMIC

C646 2203-000438 C-CERAMIC

C647 2203-005061 C-CERAMIC

C648 2203-005061 C-CERAMIC

C649 2203-000438 C-CERAMIC

C650 2402-001125 C-POLYMER

C651 2203-005061 C-CERAMIC

C652 2203-001103 C-CERAMIC

C653 2203-005261 C-CERAMIC

C654 2203-005619 C-CERAMIC

C655 2203-000254 C-CERAMIC

C656 2203-005061 C-CERAMIC

C657 2203-005061 C-CERAMIC

C658 2203-000254 C-CERAMIC

C659 2203-005061 C-CERAMIC

C660 2203-005061 C-CERAMIC

C661 2203-000206 C-CERAMIC

C662 2203-000575 C-CERAMIC

C663 2203-005061 C-CERAMIC

C664 2203-000438 C-CERAMIC

C665 2203-005198 C-CERAMIC

C666 2203-005198 C-CERAMIC

C667 2203-005061 C-CERAMIC

C668 2203-000254 C-CERAMIC

Ref. PART NO. DESCRIPTION

C669 2203-005571 C-CERAMIC

C670 2203-005061 C-CERAMIC

C671 2203-005061 C-CERAMIC

C672 2203-000254 C-CERAMIC

C673 2402-001168 C-POLYMER

C674 2203-000483 C-CERAMIC

C675 2402-001170 C-POLYMER

C676 2402-001170 C-POLYMER

C677 2402-001170 C-POLYMER

C678 2203-005061 C-CERAMIC

C679 2203-005061 C-CERAMIC

C680 2203-005061 C-CERAMIC

C681 2203-000628 C-CERAMIC

C682 2203-005061 C-CERAMIC

C683 2203-000278 C-CERAMIC

C684 2203-005061 C-CERAMIC

C685 2203-005061 C-CERAMIC

C686 2203-005061 C-CERAMIC

C687 2203-005061 C-CERAMIC

C688 2203-005571 C-CERAMIC

C689 2203-005061 C-CERAMIC

C690 2203-005482 C-CERAMIC

C691 2203-005061 C-CERAMIC

C692 2203-005061 C-CERAMIC

C693 2203-005571 C-CERAMIC

C694 2203-000438 C-CERAMIC

C695 2203-005061 C-CERAMIC

C696 2203-005061 C-CERAMIC

C697 2203-000254 C-CERAMIC

C698 2203-005061 C-CERAMIC

C699 2402-001170 C-POLYMER

C700 2203-005061 C-CERAMIC

C701 2203-005061 C-CERAMIC

C702 2203-005061 C-CERAMIC

C703 2203-005061 C-CERAMIC

C704 2203-005437 C-CERAMIC

C705 2203-005061 C-CERAMIC

C706 2203-005061 C-CERAMIC

C707 2203-005061 C-CERAMIC

C708 2203-005061 C-CERAMIC

Page 50

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-50

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C709 2203-005061 C-CERAMIC

C710 2203-005061 C-CERAMIC

C711 2203-005061 C-CERAMIC

C712 2203-005061 C-CERAMIC

C713 2203-005061 C-CERAMIC

C714 2203-005061 C-CERAMIC

C715 2203-005061 C-CERAMIC

C716 2203-005061 C-CERAMIC

C717 2203-005061 C-CERAMIC

C718 2203-000628 C-CERAMIC

C719 2203-005061 C-CERAMIC

C720 2203-000278 C-CERAMIC

C721 2203-005061 C-CERAMIC

C722 2203-005061 C-CERAMIC

C723 2203-005061 C-CERAMIC

C724 2203-005061 C-CERAMIC

C725 2203-005061 C-CERAMIC

C726 2203-005061 C-CERAMIC

C727 2203-005061 C-CERAMIC

C728 2203-005061 C-CERAMIC

C729 2203-005061 C-CERAMIC

C730 2203-005061 C-CERAMIC

C731 2203-005061 C-CERAMIC

C732 2203-005061 C-CERAMIC

C733 2203-005061 C-CERAMIC

C734 2203-005061 C-CERAMIC

C735 2203-005061 C-CERAMIC

C736 2203-005061 C-CERAMIC

C737 2203-005061 C-CERAMIC

C738 2203-005061 C-CERAMIC

C739 2203-005061 C-CERAMIC

C740 2402-001167 C-POLYMER

C741 2203-000438 C-CERAMIC

C742 2203-005437 C-CERAMIC

C743 2203-005198 C-CERAMIC

C744 2203-005061 C-CERAMIC

C745 2203-000206 C-CERAMIC

C746 2402-001169 C-POLYMER

C747 2203-000278 C-CERAMIC

C748 2203-000278 C-CERAMIC

Ref. PART NO. DESCRIPTION

C749 2203-005061 C-CERAMIC

C750 2203-005061 C-CERAMIC

C751 2203-005061 C-CERAMIC

C752 2203-005061 C-CERAMIC

C753 2203-005061 C-CERAMIC

C754 2203-000254 C-CERAMIC

C755 2203-005061 C-CERAMIC

C756 2203-000254 C-CERAMIC

C757 2203-005061 C-CERAMIC

C758 2203-000254 C-CERAMIC

C759 2203-005061 C-CERAMIC

C760 2203-005061 C-CERAMIC

C761 2203-005061 C-CERAMIC

C762 2203-005061 C-CERAMIC

C763 2203-005061 C-CERAMIC

C764 2203-005061 C-CERAMIC

C765 2203-005061 C-CERAMIC

C766 2203-005571 C-CERAMIC

C767 2203-005571 C-CERAMIC

C768 2203-005061 C-CERAMIC

C769 2203-005061 C-CERAMIC

C770 2402-001167 C-POLYMER

C771 2203-005061 C-CERAMIC

C772 2203-005061 C-CERAMIC

C773 2203-005571 C-CERAMIC

C774 2203-005198 C-CERAMIC

C775 2203-006143 C-CERAMIC

C776 2203-000278 C-CERAMIC

C777 2203-005482 C-CERAMIC

C778 2203-005061 C-CERAMIC

C779 2203-005061 C-CERAMIC

C780 2203-005061 C-CERAMIC

C781 2203-000254 C-CERAMIC

C782 2203-000438 C-CERAMIC

C783 2203-000233 C-CERAMIC

C784 2203-005061 C-CERAMIC

C785 2203-005061 C-CERAMIC

C786 2203-005061 C-CERAMIC

C787 2203-005061 C-CERAMIC

C788 2203-005437 C-CERAMIC

Page 51

5 System Schematic Diagrams and PCB Silkscreen

5-51Sens Q 20

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C789 2203-005061 C-CERAMIC

C790 2203-005437 C-CERAMIC

C791 2203-005148 C-CERAMIC

C792 2402-001169 C-POLYMER

C793 2203-005061 C-CERAMIC

C794 2203-005061 C-CERAMIC

C795 2203-005061 C-CERAMIC

C796 2203-005061 C-CERAMIC

C797 2203-005061 C-CERAMIC

C798 2203-005061 C-CERAMIC

C799 2203-005664 C-CERAMIC

C800 2203-005061 C-CERAMIC

C801 2203-005061 C-CERAMIC

C802 2203-005061 C-CERAMIC

C803 2203-005061 C-CERAMIC

C804 2203-005061 C-CERAMIC

C805 2203-005061 C-CERAMIC

C806 2203-005061 C-CERAMIC

C807 2203-005061 C-CERAMIC

C808 2402-001167 C-POLYMER

C809 2203-005061 C-CERAMIC

C810 2203-005061 C-CERAMIC

C811 2203-005061 C-CERAMIC

C812 2203-005061 C-CERAMIC

C813 2203-000278 C-CERAMIC

C814 2203-005061 C-CERAMIC

C815 2203-005061 C-CERAMIC

C816 2203-000254 C-CERAMIC

C817 2203-005061 C-CERAMIC

C818 2203-005061 C-CERAMIC

C819 2203-006143 C-CERAMIC

C820 2203-000233 C-CERAMIC

C821 2203-005061 C-CERAMIC

C822 2203-000278 C-CERAMIC

C823 2203-005061 C-CERAMIC

C824 2203-005061 C-CERAMIC

C825 2203-005437 C-CERAMIC

C826 2203-005061 C-CERAMIC

C827 2203-000254 C-CERAMIC

C828 2203-000254 C-CERAMIC

Ref. PART NO. DESCRIPTION

C829 2203-005061 C-CERAMIC

C830 2203-005061 C-CERAMIC

C831 2203-005061 C-CERAMIC

C832 2203-005061 C-CERAMIC

C833 2203-005061 C-CERAMIC

C834 2203-000254 C-CERAMIC

C835 2203-005061 C-CERAMIC

C836 2203-005061 C-CERAMIC

C837 2203-005061 C-CERAMIC

C838 2203-005061 C-CERAMIC

C839 2203-000278 C-CERAMIC

C840 2203-005061 C-CERAMIC

C841 2203-000254 C-CERAMIC

C842 2203-005061 C-CERAMIC

C843 2203-005061 C-CERAMIC

C844 2203-000254 C-CERAMIC

C845 2203-005061 C-CERAMIC

C846 2203-005061 C-CERAMIC

C847 2203-005061 C-CERAMIC

C848 2203-005571 C-CERAMIC

C849 2402-001167 C-POLYMER

C850 2203-005664 C-CERAMIC

C851 2203-000940 C-CERAMIC

C852 2203-005664 C-CERAMIC

C853 2203-005061 C-CERAMIC

C854 2203-005061 C-CERAMIC

C855 2203-005198 C-CERAMIC

C856 2203-005061 C-CERAMIC

C857 2203-000425 C-CERAMIC

C858 2203-000425 C-CERAMIC

C859 2203-005061 C-CERAMIC

C860 2203-000254 C-CERAMIC

C861 2203-005061 C-CERAMIC

C862 2203-005061 C-CERAMIC

C863 2203-000254 C-CERAMIC

C864 2203-000254 C-CERAMIC

C865 2203-005061 C-CERAMIC

C867 2203-000254 C-CERAMIC

C868 2203-005061 C-CERAMIC

C869 2203-005061 C-CERAMIC

Page 52

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-52

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C870 2203-000254 C-CERAMIC

C871 2203-005061 C-CERAMIC

C872 2203-005061 C-CERAMIC

C873 2203-005061 C-CERAMIC

C874 2203-005061 C-CERAMIC

C875 2203-005061 C-CERAMIC

C876 2203-005061 C-CERAMIC

C877 2203-005061 C-CERAMIC

C878 2203-006143 C-CERAMIC

C879 2402-001167 C-POLYMER

C880 2203-005061 C-CERAMIC

C881 2203-005061 C-CERAMIC

C882 2203-000278 C-CERAMIC

C883 2203-005061 C-CERAMIC

C884 2203-000254 C-CERAMIC

C885 2203-005198 C-CERAMIC

C886 2203-000254 C-CERAMIC

C887 2203-000254 C-CERAMIC

C888 2203-005061 C-CERAMIC

C889 2203-005061 C-CERAMIC

C890 2203-000254 C-CERAMIC

C891 2203-005061 C-CERAMIC

C892 2203-005061 C-CERAMIC

C893 2203-000254 C-CERAMIC

C894 2203-000254 C-CERAMIC

C895 2203-005198 C-CERAMIC

C896 2203-000298 C-CERAMIC

C897 2203-005061 C-CERAMIC

C898 2203-000254 C-CERAMIC

C899 2203-005061 C-CERAMIC

C900 2203-005061 C-CERAMIC

C901 2203-005061 C-CERAMIC

C902 2203-005061 C-CERAMIC

C903 2203-005061 C-CERAMIC

C904 2203-005061 C-CERAMIC

C905 2203-000278 C-CERAMIC

C906 2203-005061 C-CERAMIC

C907 2203-005061 C-CERAMIC

C908 2203-005061 C-CERAMIC

C909 2203-006143 C-CERAMIC

Ref. PART NO. DESCRIPTION

C910 2203-005061 C-CERAMIC

C911 2203-005061 C-CERAMIC

C912 2203-005061 C-CERAMIC

C913 2203-005061 C-CERAMIC

C914 2203-005061 C-CERAMIC

C915 2203-005061 C-CERAMIC

C916 2203-000278 C-CERAMIC

C917 2203-000254 C-CERAMIC

C918 2203-005571 C-CERAMIC

C919 2203-005061 C-CERAMIC

C920 2203-005061 C-CERAMIC

C921 2203-005061 C-CERAMIC

C922 2203-005198 C-CERAMIC

C923 2203-005061 C-CERAMIC

C924 2203-005061 C-CERAMIC

C925 2203-005061 C-CERAMIC

C926 2203-005061 C-CERAMIC

C927 2203-005061 C-CERAMIC

C928 2203-005061 C-CERAMIC

C929 2203-005061 C-CERAMIC

C930 2203-005061 C-CERAMIC

C931 2203-005061 C-CERAMIC

C932 2203-005571 C-CERAMIC

C933 2203-005061 C-CERAMIC

C934 2203-002720 C-CERAMIC

C935 2203-005061 C-CERAMIC

C936 2203-005061 C-CERAMIC

C937 2203-000438 C-CERAMIC

C938 2203-000476 C-CERAMIC

C939 2203-000233 C-CERAMIC

C940 2203-005437 C-CERAMIC

C941 2203-000233 C-CERAMIC

C942 2203-005061 C-CERAMIC

C943 2203-005061 C-CERAMIC

C944 2203-005061 C-CERAMIC

C945 2203-005061 C-CERAMIC

C946 2203-005061 C-CERAMIC

C947 2203-005061 C-CERAMIC

C948 2203-005061 C-CERAMIC

C949 2203-005061 C-CERAMIC

Page 53

5 System Schematic Diagrams and PCB Silkscreen

5-53Sens Q 20

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

C950 2203-000628 C-CERAMIC

C951 2203-000628 C-CERAMIC

C952 2203-005918 C-CERAMIC

C953 2203-005918 C-CERAMIC

C954 2203-005061 C-CERAMIC

C955 2203-005061 C-CERAMIC

C956 2203-005061 C-CERAMIC

C957 2203-005061 C-CERAMIC

C958 2203-005061 C-CERAMIC

C959 2203-005061 C-CERAMIC

C960 2203-005061 C-CERAMIC

C961 2203-005061 C-CERAMIC

C962 2203-005061 C-CERAMIC

C963 2203-005061 C-CERAMIC

C964 2203-005061 C-CERAMIC

C965 2203-005061 C-CERAMIC

C966 2203-005061 C-CERAMIC

C967 2203-005061 C-CERAMIC

C968 2203-005061 C-CERAMIC

C969 2203-005061 C-CERAMIC

C970 2203-005061 C-CERAMIC

C971 2203-005061 C-CERAMIC

C972 2203-005061 C-CERAMIC

C973 2203-005061 C-CERAMIC

C974 2203-005061 C-CERAMIC

C975 2203-005061 C-CERAMIC

C976 2203-005061 C-CERAMIC

C977 2203-005061 C-CERAMIC

C978 2203-000628 C-CERAMIC

C979 2203-000628 C-CERAMIC

C980 2203-006001 C-CERAMIC

C981 2203-006001 C-CERAMIC

C982 2203-000233 C-CERAMIC

C983 2203-005482 C-CERAMIC

C984 2203-005482 C-CERAMIC

C985 2203-005482 C-CERAMIC

C986 2203-005482 C-CERAMIC

C987 2203-005061 C-CERAMIC

C988 2203-005061 C-CERAMIC

C989 2203-005061 C-CERAMIC

Ref. PART NO. DESCRIPTION

C990 2203-005061 C-CERAMIC

C991 2203-005061 C-CERAMIC

C992 2203-005061 C-CERAMIC

C993 2203-005061 C-CERAMIC

C994 2203-005061 C-CERAMIC

C995 2203-005061 C-CERAMIC

C996 2203-005061 C-CERAMIC

C997 2203-000278 C-CERAMIC

C998 2203-000278 C-CERAMIC

C999 2203-000425 C-CERAMIC

C1000 2203-005052 C-CERAMIC

C1001 2203-000298 C-CERAMIC

C1002 2203-000298 C-CERAMIC

C1003 2203-000298 C-CERAMIC

C1004 2203-000628 C-CERAMIC

C1005 2203-000628 C-CERAMIC

C1006 2203-000330 C-CERAMIC

C1007 2203-000233 C-CERAMIC

C1008 2203-000233 C-CERAMIC

C1009 2203-000995 C-CERAMIC

C1010 2203-000995 C-CERAMIC

C1011 2203-000995 C-CERAMIC

C1012 2203-000995 C-CERAMIC

C1013 2203-000995 C-CERAMIC

D1 0401-000191 DIODE-SWITCHING;MMBD4148

D2 0402-001405 DIODE-RECTIFIER;B340A

D3 0402-001405 DIODE-RECTIFIER;B340A

D4 0402-001405 DIODE-RECTIFIER;B340A

D5 0401-000191 DIODE-SWITCHING;MMBD4148

D6 0404-000157 DIODE-SCHOTTKY;CMPSH-3A

D7 0404-000157 DIODE-SCHOTTKY;CMPSH-3A

D8 0406-001141 DIODE-TVS;PGB0010603NR

D9 0406-001141 DIODE-TVS;PGB0010603NR

D10 0404-000157 DIODE-SCHOTTKY;CMPSH-3A

D11 0404-000157 DIODE-SCHOTTKY;CMPSH-3A

D12 0401-000191 DIODE-SWITCHING;MMBD4148

D13 0404-000114 DIODE-SCHOTTKY;MMBD301LT1

D14 0402-001405 DIODE-RECTIFIER;B340A

D15 0401-000191 DIODE-SWITCHING;MMBD4148

D16 0404-000114 DIODE-SCHOTTKY;MMBD301LT1

Page 54

5 System Schematic Diagrams and PCB Silkscreen

Sens Q 205-54

This Document can not be used without Samsung’s authorization.

Ref. PART NO. DESCRIPTION

D17 0401-000191 DIODE-SWITCHING;MMBD4148

D18 0402-001405 DIODE-RECTIFIER;B340A

D19 0401-000191 DIODE-SWITCHING;MMBD4148

D20 0401-000191 DIODE-SWITCHING;MMBD4148

D21 0404-000114 DIODE-SCHOTTKY;MMBD301LT1

D22 0404-000114 DIODE-SCHOTTKY;MMBD301LT1

D500 0406-001141 DIODE-TVS;PGB0010603NR

D501 0406-001141 DIODE-TVS;PGB0010603NR

D502 0406-001141 DIODE-TVS;PGB0010603NR

D503 0401-000191 DIODE-SWITCHING;MMBD4148

D504 0402-001405 DIODE-RECTIFIER;B340A

D505 0402-001405 DIODE-RECTIFIER;B340A

D506 0402-001405 DIODE-RECTIFIER;B340A

D507 0402-001405 DIODE-RECTIFIER;B340A

D508 0402-001405 DIODE-RECTIFIER;B340A

D509 0402-001405 DIODE-RECTIFIER;B340A

D510 0406-001141 DIODE-TVS;PGB0010603NR

D511 0406-001141 DIODE-TVS;PGB0010603NR

D512 0402-001405 DIODE-RECTIFIER;B340A

D513 0402-001405 DIODE-RECTIFIER;B340A

D514 0401-000191 DIODE-SWITCHING;MMBD4148

D515 0401-000191 DIODE-SWITCHING;MMBD4148

D516 0402-001405 DIODE-RECTIFIER;B340A

D517 0402-001405 DIODE-RECTIFIER;B340A

D518 0402-001405 DIODE-RECTIFIER;B340A

D519 0404-001020 DIODE-SCHOTTKY;BAT54C

D520 0401-000191 DIODE-SWITCHING;MMBD4148

D521 0404-000114 DIODE-SCHOTTKY;MMBD301LT1

D522 0404-000114 DIODE-SCHOTTKY;MMBD301LT1

D1100 0401-000191 DIODE-SWITCHING;MMBD4148

D1101 0401-000191 DIODE-SWITCHING;MMBD4148

EC1 2402-001170 C-POLYMER

EC2 2402-001125 C-POLYMER

EC3 2402-001125 C-POLYMER

EC500 2402-001170 C-POLYMER

EC502 2402-001170 C-POLYMER

EC503 2402-001121 C-POLYMER

EC504 2402-001121 C-POLYMER

EMI1 BA61-00150A CLIP

EMI2 BA61-00150A CLIP

Ref. PART NO. DESCRIPTION

EMI3 BA61-00150A CLIP

J1 3722-001692 JACK-MODULAR;12P/10C

J2 3711-003609 CONNECTOR-HEADER;BOX

J3 3701-001260 CONNECTOR-DSUB;15P

J4 3722-001772 JACK-DC

J5 3711-004687 CONNECTOR-HEADER;NOWALL

J6 3722-001619 JACK-USB;4P

J7 3710-001639 CONNECTOR-SOCKET;100P+4P

J8 0902-001601 IC-MICROPROCESSOR;BANIAS

J9 3722-001619 JACK-USB;4P

J10 3722-001649 JACK-IEEE1394;6P

J11 3722-001775 JACK-PHONE;6P

J12 3709-001206 CONNECTOR-CARD

J13 3709-001196 CONNECTOR-CARD

J14 3722-001785 JACK-PHONE;6P

J15 3710-001763 CONNECTOR-SOCKET;30P

J16 3711-004649 CONNECTOR-HEADER;BOX

J17 781290 CONNECTOR-CARD

J18 3711-000541 CONNECTOR-HEADER;BOX

J400 3708-001132 CONNECTOR-FPC/FFC/PI;15P

J500 3711-004649 CONNECTOR-HEADER;BOX