Samsung NP-X06, BA41-00529A Schematic

- This Document can not be used without Samsung's authorization -

www.kythuatvitinh.com

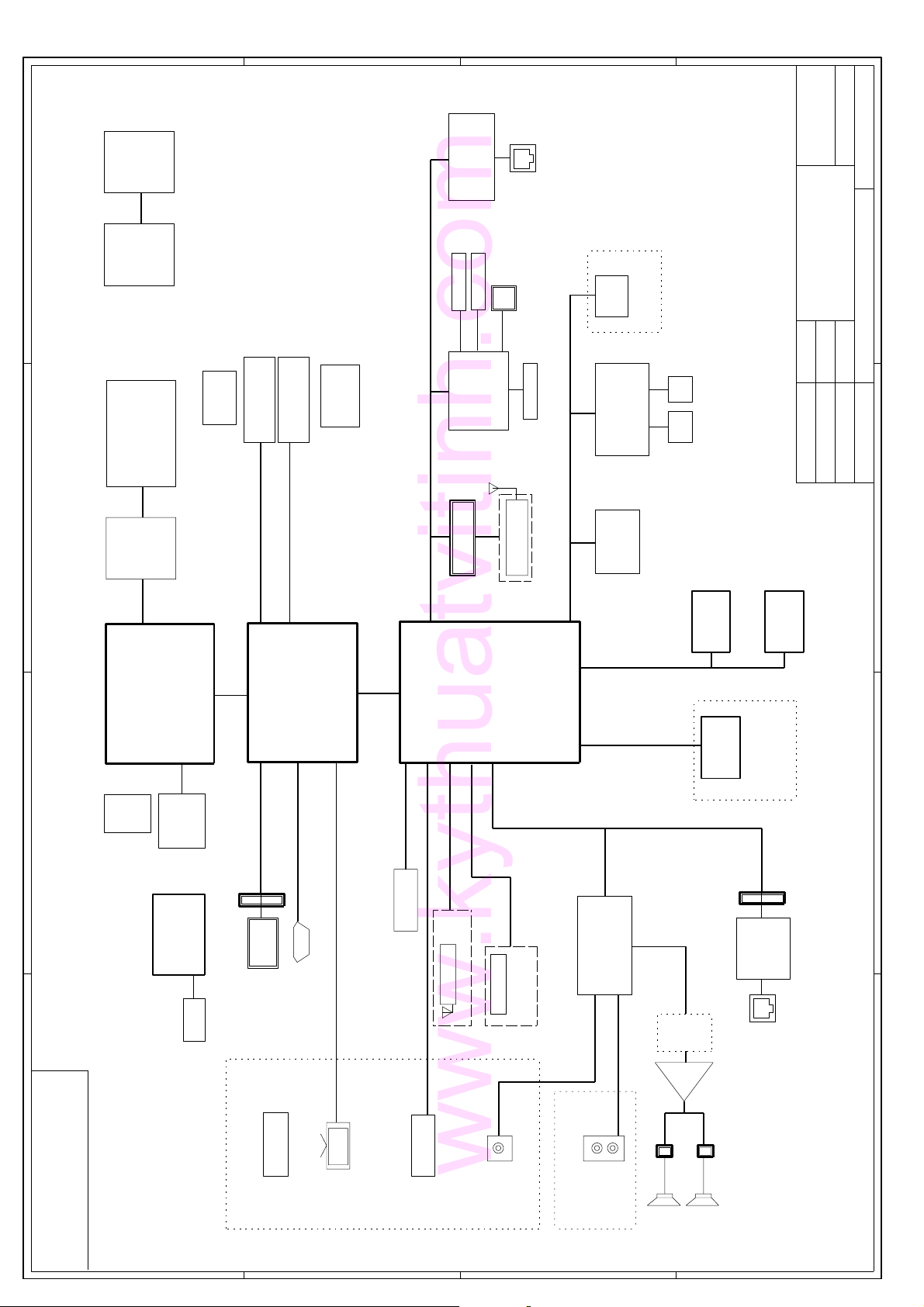

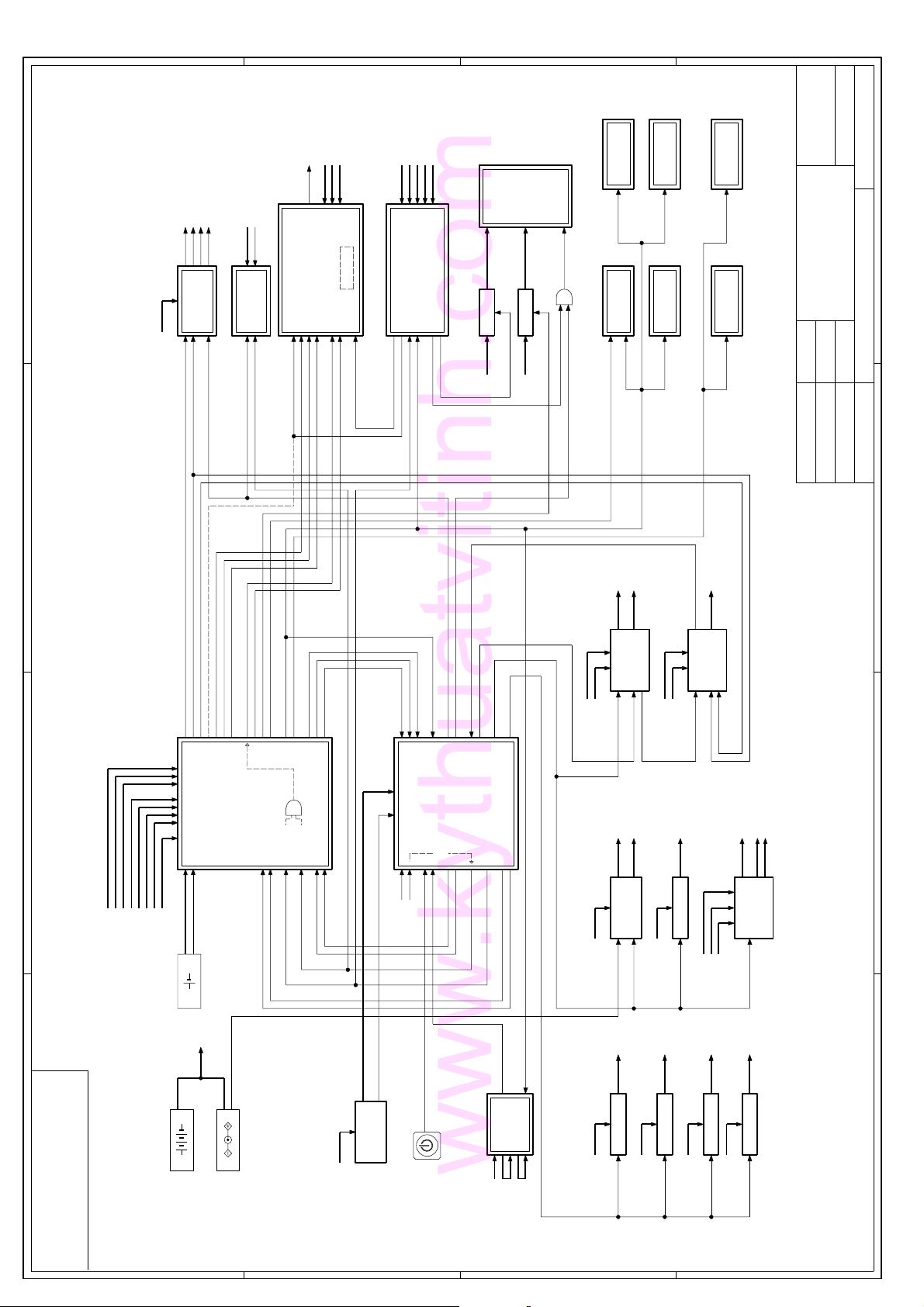

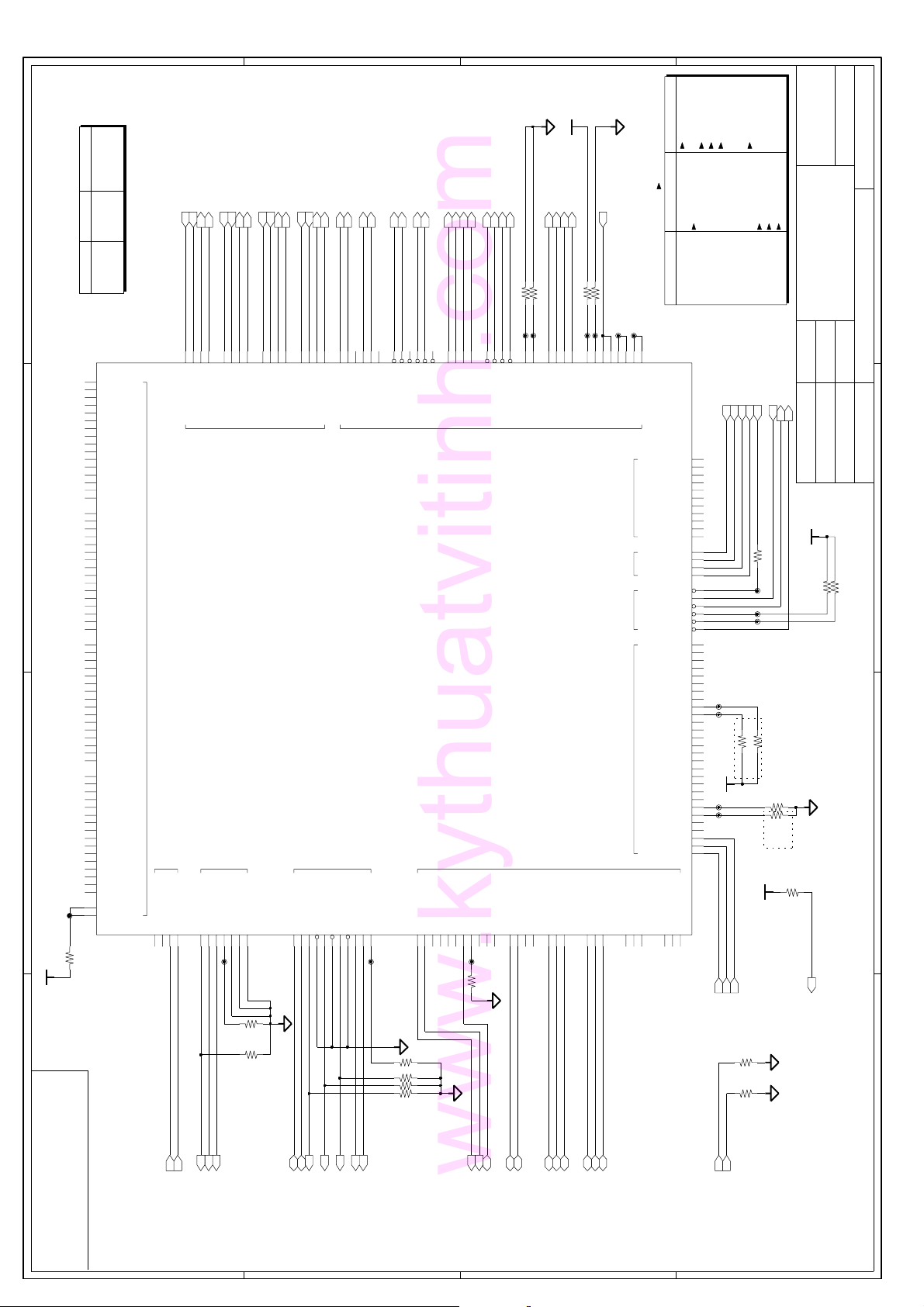

9. Schematic Diagram

9-1 MAIN BOARD

9-1-1 Schematic Diagrams

COVER

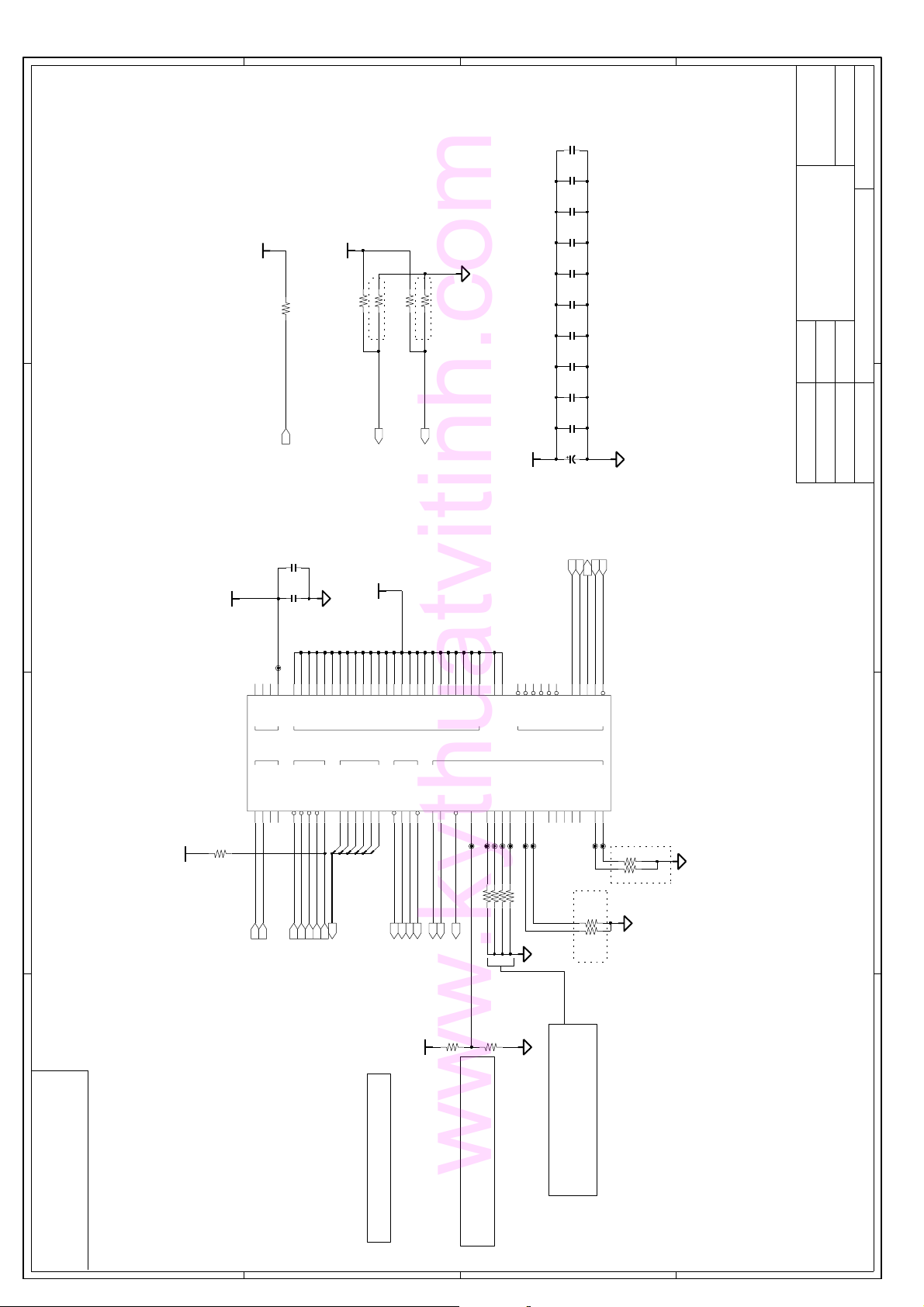

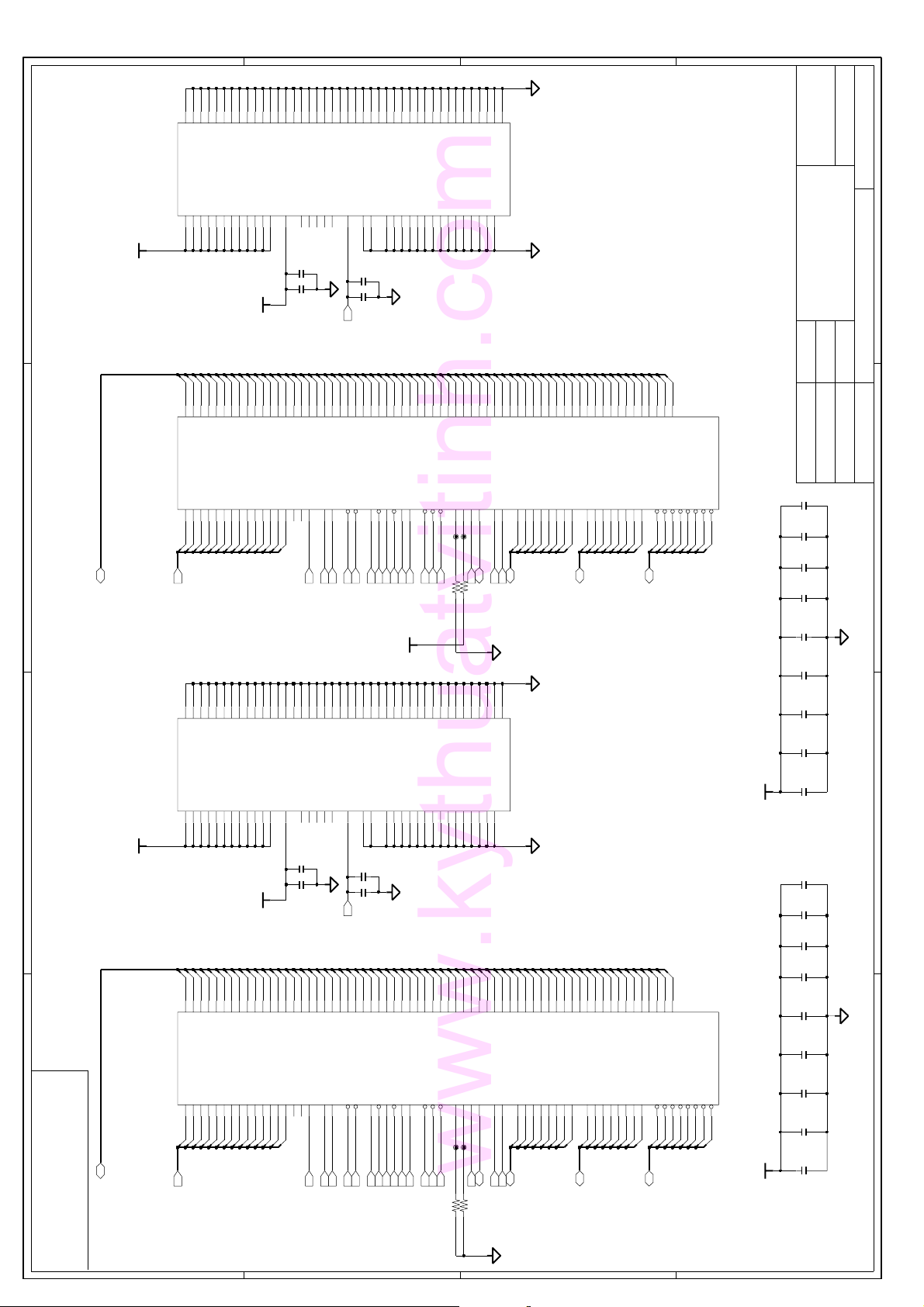

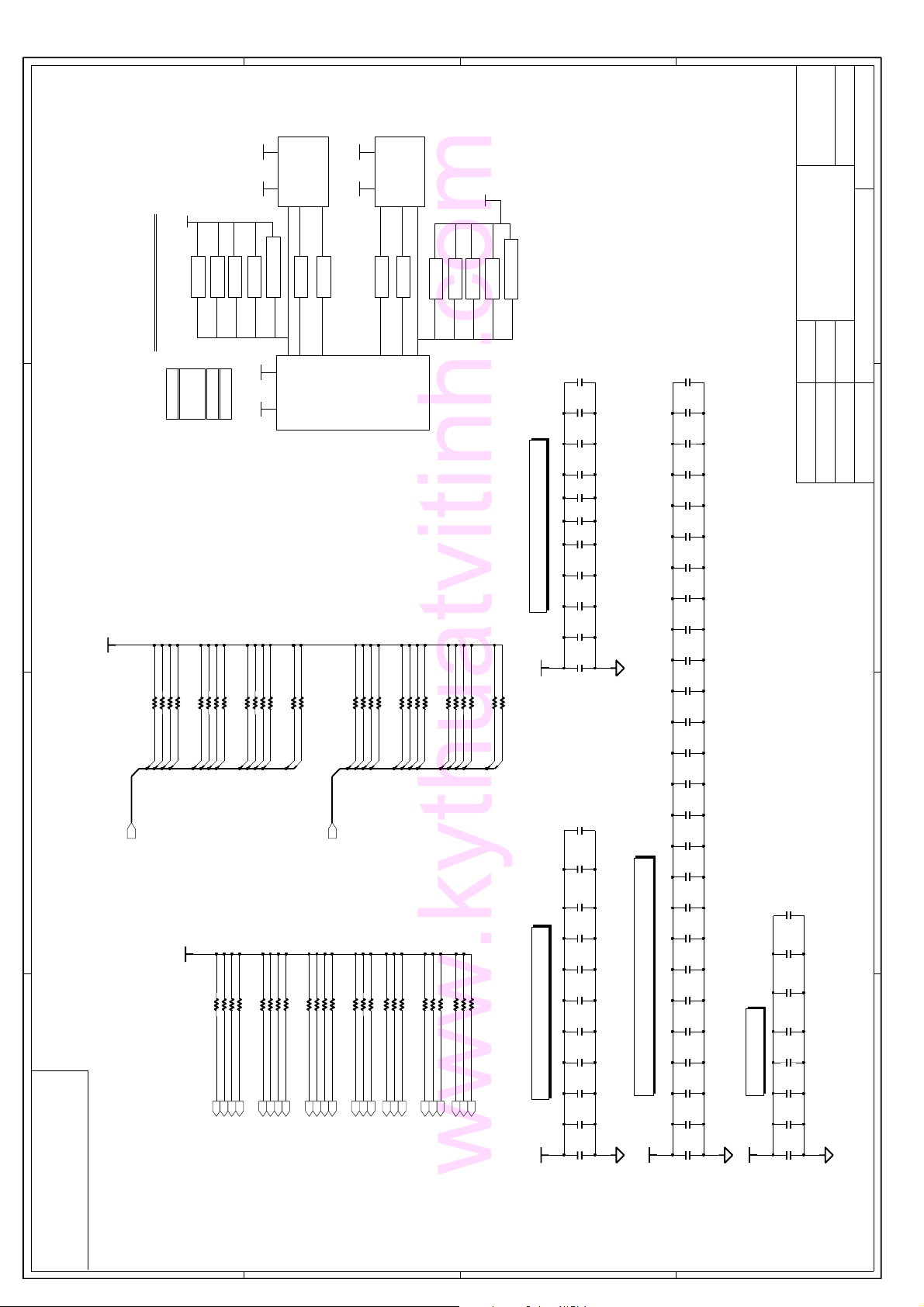

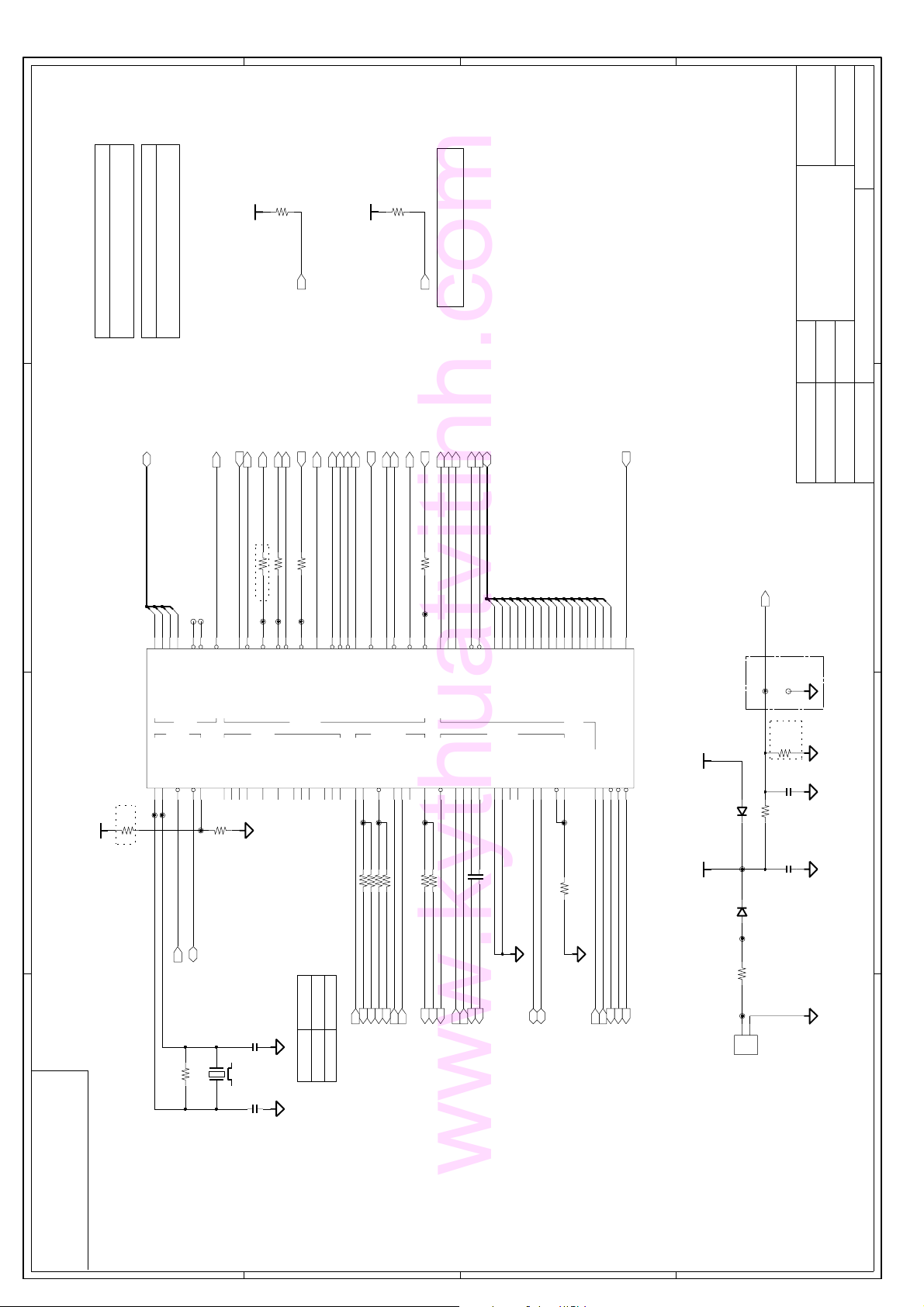

BLOCK DIAGRAM

Sheet2.

Sheet1.

CLOCK GENERATOR

POWER DIAGRAM

POWER ON SEQUENCE

BOARD INFORMATION

Sheet4.

Sheet3.

CPU (2/3)

CPU (1/3)

Sheet6.

Sheet8.

Sheet7.

Sheet9.

CPU (3/3)

Sheet10.

CLOCK DISTRABUTION

Sheet5.

Table of Contents

Dothan

Intel Alviso + ICH6-M

ALVISO (4/5)

DDR II SODIMM

ICH6-M (1/4)

ICH6-M (3/4)

ICH6-M (4/4)

ALVISO (1/5)

ALVISO (3/5)

CPU/DDR THERMAL SENSOR

ALVISO (2/5)

Sheet11.

Sheet12.

Sheet13.

DDR II TERMINATIONS

ALVISO (5/5)

Sheet14.

Sheet15.

Sheet18.

Sheet17.

Sheet16.

Sheet19.

X06

LCD CONN

ICH6-M (2/4)

CRT CONN

Sheet20.

Sheet23.

Sheet21.

Sheet22.

Sheet24.

BA92-03859A

Internal Gfx.

CARDBUS (2/2) & 1394 CONN

MINIPCI

LOM (1/2)

MDC / TPM / FAN / BLUETOOTH / USB

CARDBUS (1/2)

PCMCIA / 3 IN 1 CONN

FWH

Sheet25.

Sheet27.

Sheet26.

BA41-00529A

MP

AUDIO CODEC

LOM (2/2)

Sheet30.

Sheet28.

Sheet32.

Sheet31.

Sheet29.

1.0

2005-6-25

B'D TO B'D CONN

MICOM

AUDIO AMP

IDE CONN

Sheet33.

Sheet34.

Sheet36.

Sheet37.

Sheet35.

SWITCHED POWER

CPU POWER

DDR II POWER

MICOM_P3V / P2.5V

CHARGER

PCB STUFFS

VCCP & GMCH POWER

AUDIO SUB BOARD

Sheet39.

Sheet40.

Sheet44.

Sheet42.

Sheet43.

Sheet38.

APPROVAL

CHECK

Sheet45.

Sheet41.

KEVIN LEE

CHEN TAO

TESTPOINT

Sheet46.

Aquila-So

DRAW

CPU :

Chip Set :

Remarks :

Dev. Step :

Model Name :

PCB Code :

PBA Name :

Revision :

T.R. Date :

SAMSUNG X06 95

GUO LEI

ZHOU JUN

1

4

2

3

D

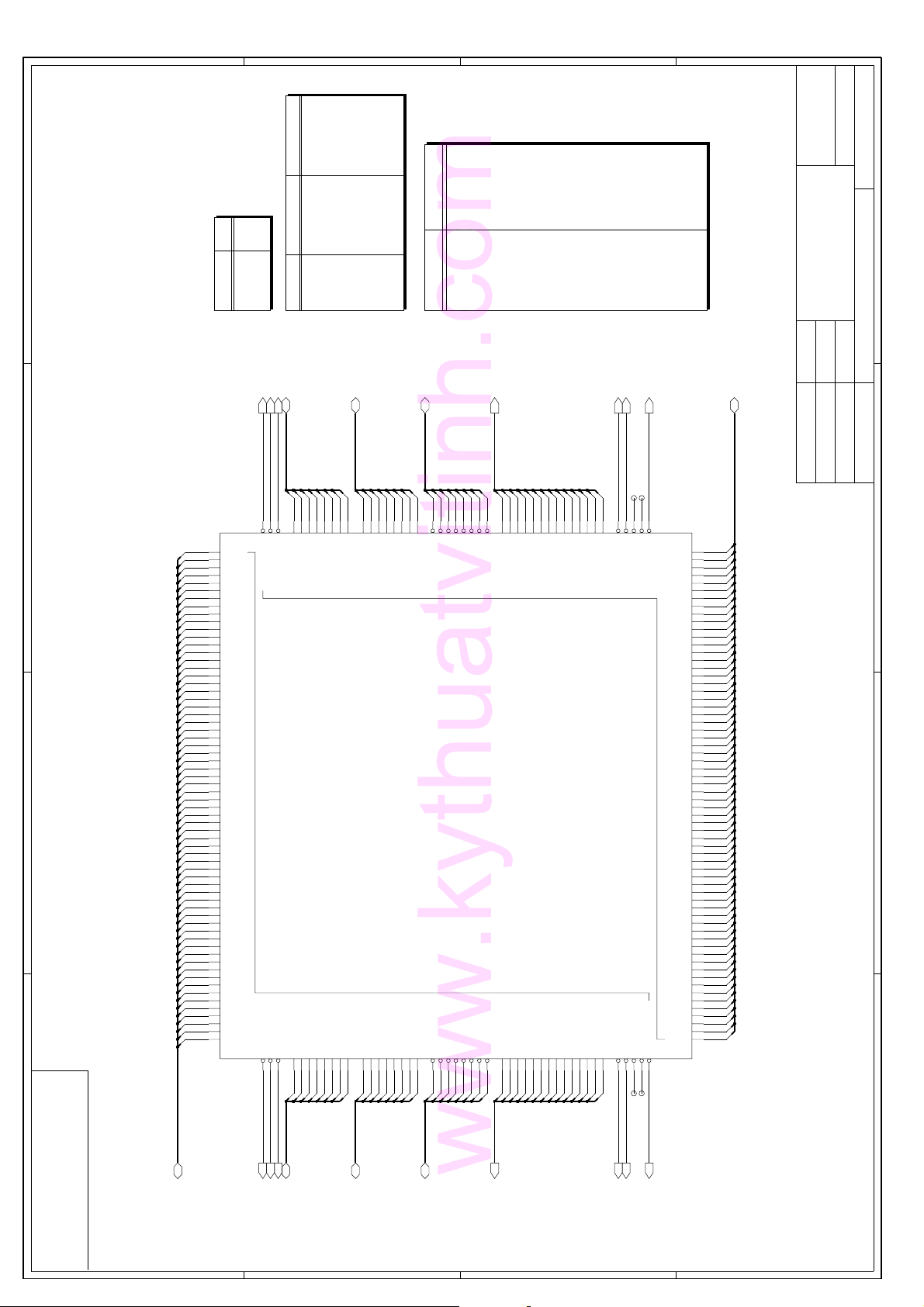

SAMSUNG X06 9-2

www.kythuatvitinh.com

Battery

Smart

Module

C

RJ45

BCM5788M

BROADCOM

B

A

SAMSUNG

OF

BA41-00529A

ELECTRONICS

246

PART NO.

PAGE

1

Circuit

Charging

SD/MS

CardBus

4 pin

DC/DC

DDR II

Thermistor

DDR II

SODIMM 0

DDR II

SODIMM 1

VRM

DDR II

1394

R5C841

R5532V002

CARDBUS

EEPROM

TPM

MICOM

Hitachi H8S

HD64F2169/2160

OPTIONAL

KBD

Scan

PAD

Touch

System

ANT

DDR II 533/400

R 1.3

CPU

IMVP-IV

DC/DC

478pin

L2 Cache : 2 MB

Mobile Processor

FAN

& Yonah

Dothan(w/533MHz)

CPU

EMC6N300

Thermistor

Channel A (Standard)

PSB

533 MT/S

LVDS

Internal Graphics

30P

Dual channel

Channel B (Reverse)

1257 FCBGA

GMCH-M

Alviso-GM

CRT

TV

x4/x2, 1.5V

Direct Media Interface

USB0

USB 0

CONN.

Mini PCI

33MHz, 3.3V PCI, 32bit

609 BGA

ICH6-M

USB1

USB2

USB3

AC’97

Wireless LAN

3.3V LPC, 33MHz

PATA

SATA

FWH

Primary

82802AC

HDD

U-ATA 100

Pri. IDE master

HDD

SATA 150

30P

Sec. IDE slave

CD-ROM

OPTIONAL

Secondary

MAIN

AQUILA-SONOMA

TITLE

MP

6/25/2005

REV

DEV. STEP

DATE

ANTONIO

ZHOU & GUO

DRAW

APPROVAL

CHECK

CD / DVD

June 25, 2005 12:21:39 PM

OPERATION BLOCK DIAGM

1.0

LAST EDIT

KEVIN LEE

MODULE CODE

2

3

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

D

CK-410M

Clocking

SSDC

CRT

LCD

DC/DC

DC/DC Module

Bluetooth

ANT

OPTIONAL

OPTIONAL

Finger Print

ON TOUCHPAD

AUDIO

AD1981B

AC’97 Codec

3D

Sound

MDC

RJ11

Modem

AMP

TV

SVHS

C

USB 1

S/PDIF

MIC-IN

HP

AUDIO BOARD

B

2P

SPKR R

2P

SPKR L

A

4

D

3

2

4

1

B

C

A

D

SAMSUNG X06 9-3

www.kythuatvitinh.com

C

B

A

463

OF

BA41-00529A

ELECTRONICS

PART NO.

PAGE

h

1F

VID Hex

08

h

061.308 V

DEEPER SLEEP

h

h0h

h

02

04

h

01

00

SAMSUNG

LOWEST FREQ.

h

hhh

h

h

h

h

h

h

18

1D

1E

17

15

1B

19

hhhhh

hhh

h

h

h

h

11

13

14

10

0E1.436 V

h

0A

09

0C

0B

Voltage

1.196 V

1.180 V

1.164 V01.148 V

1.132 V

1.116 V

1.100 V

1.068 V

1.052 V

1.036 V

0.988 V

1.004 V

0.972 V

0.956 V

0.940 V

0.924 V

0.892 V

0.908 V

0.860 V

0.876 V

0.828 V350.796 V

0.844 V

1

0

0

1

1

1 1.020 V

1

0

0

0

1

0

011

1

1

1

1

0

0

010

0

1

1

1

1

h

h

h

34131

36

33

1.532 V

1.516 V

1.564 V

0

1

1

0

0

101

1

0

0

0

1

0

111

1

1

0

0

0

0

0

0

0

1

1

0

1

1

1

0

1

1

hhh

h

32

1.500 V

1

0

0

1

1

1

0

0

0

0

1

1

0

1

h

30

2F

1.452 V

1.468 V

0

1

1

0

1

0

1

1

0

0

0

1

0

VID0

VID1

011

0

VID2

0

0

0

VID3

0

VID4

0

0

1

VID5

1

h

h

3F

3E

VID Hex

Voltage

1.708 V1C1.676 V

1.692 V

0

1

VID0

0

0

VID1

0

0

VID2

0

0

VID3

0

0

VID4

0

0

CPU Core Voltage Table

VID5

0

0

0

0

1

h

3D

0-1

1

0

0

0

0

1

0

1

0

0

0

0

0

1

1

h

h

3B

3C

1.660 V

1.644 V

0

1

0

0

1

0

0

0

0

0

0

1

0

1

0

0

1

3A

1.628 V

1

0

1

0

00-

1

0

1

0

1

1

0

1

1

1

1

0

0

0

0

0

1

1

1

1

hhh

h

h

38

39

37

1.612 V

1.580 Vh1.548 Vh1.484 V

1.596 V

1

0

1

0

1

1

1

0

0

1

1

0

0

1

0

0

0

-

0

0

0

1

0

0

0

1

1

0

0

1

0

1

1

1

0

1

0

1

0

1

1

1

0

11

0

0

1

h

1

0

0

0

1

0

01

0

0

0

1

1

1

1

1

101

1

1

1

1

1

1

1

1

h

h

2C

29

2D

2B

2A

28

1.388 V

1.404 V

1.356 V

1.420 V

1.372 V

1.340 V

1

1

0

1

1

0

0

1

1

0

1

1

0

1

1

0

1

1

0

1

0

0

0

0

0

0

1

1

1

1

1

1

1

0

0

0

0

0

-

0

0.748 V

0.812 V

0.780 V

0.764 V

10

0

0

1

0

1

0

1

0

0

0

0

1

0

1

1

1

1

12E0

1

101

1

1

1

1

1

hhhhh

h

h

h

26

23

25

27

24120

1.292 V

1.324 V

1.276 V

1.260 V

1

0

1

0

0

0

0

1

0

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0.732 V

0.716 V

1

0

1

0

1

1

1

1

1

1

1

1

22

21

1.228 V

1.244 V

1

0

1

0

1

1

1

1

1

1

0

0

0.700 V

1

1

1

1

1

h

1.212 V

1

1

12

1

1

0

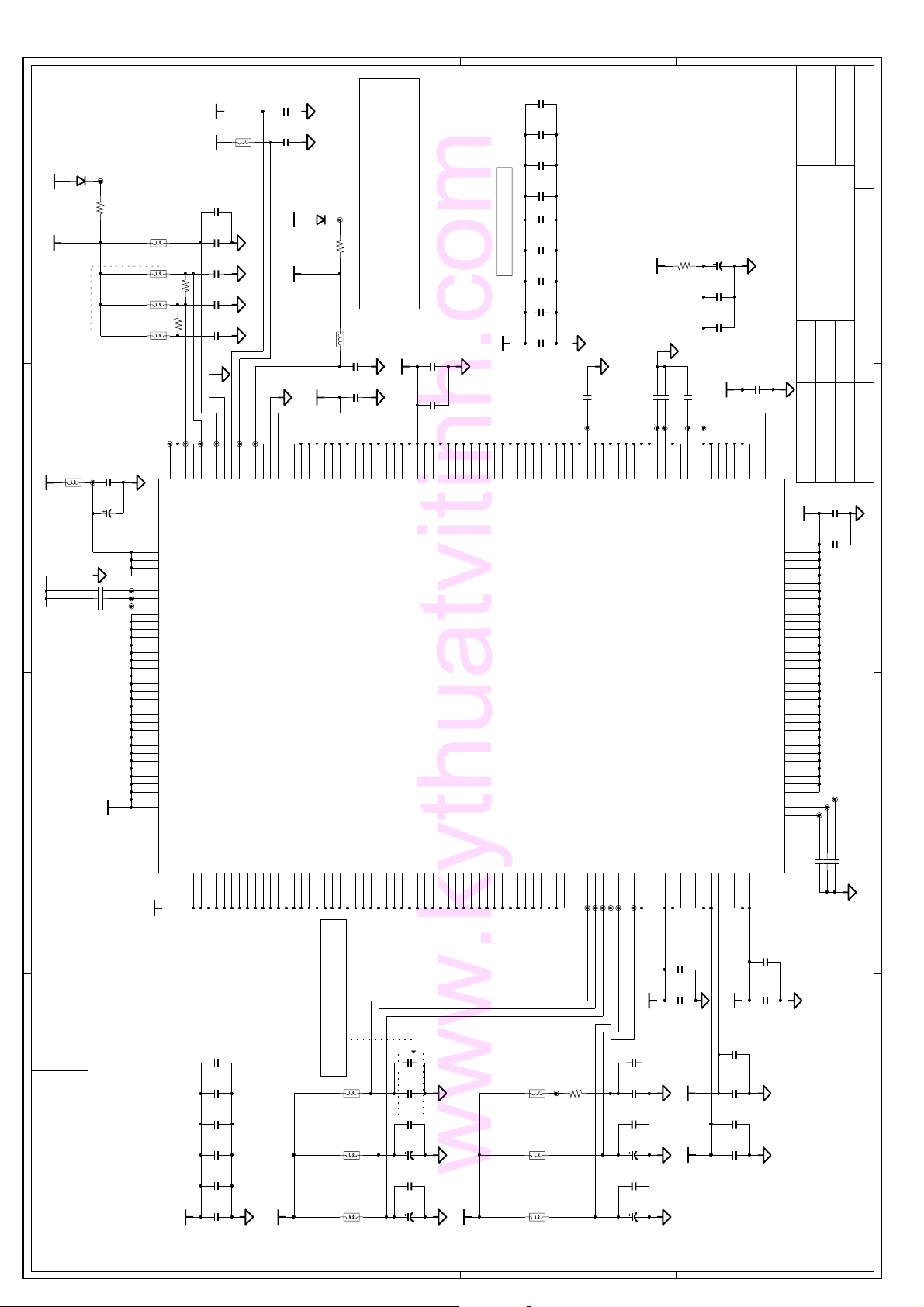

Clocks

ONhOFFhOFF

LOW0OFF

+V*S

ON

OFF

ON

ON03ON

+V*ALW +V*

ON

SLP_S5#

HIGH07HIGH05LOW

SLP_S4#

HIGH

SLP_S3#

HIGH0FLOW1ALOW

Signal

System Power States

S0 (Full On)

OFF

OFF

OFF

ON

OFF

ON

ON2ON

ON

HIGH1HIGH

HIGH0DLOW

HIGH0LOW

LOW

LOW

S3-Hot (STR)16S4 (STD)

S3-Cold (STR)

S5 (Soft Off)

MAIN

AQUILA-SONOMA

TITLE

MP

6/25/2005

DEV. STEP

DATE

ANTONIO

ZHOU & GUO

DRAW

CHECK

1.084 V

1

June 25, 2005 12:21:39 PM

BOARD INFORMATION

1.0

REV

LAST EDIT

KEVIN LEE

APPROVAL

MODULE CODE

HIGHEST FREQ.

3

E,F

Interrupts

A,B,C

0

REQ/GNT#

102

IDSEL#

AD25

AD23

G

AD21

Bus

Clock, Unused Clock Output Disable

-

-

SMBUS Master

BATTERY INFORMATION

-

A4h

A0h

D4h

1101 010x

1010 0000

1010 010X

Thermal Sensor

5Eh

16h

-

0101 111X

Master

0001 011X

SMBUS Master

-

D2h

Hex

Master

Address

1101 001x

(OPTION)

(OPTION)

ASSIGNED TO

SYSTEM PORT B

BLUETOOTH

SYSTEM PORT A

FINGER PRINTER

MCH-M Core Voltage (1.05V)

/

1.5V switched power rail (off in S3-S5)

1.5V power rail (off in S4-S5)

3.3V always on power rail for MICOM

3.3V power rail (Always on@AC-IN mode & off in S4-S5@BATT mode)

Primary DC system power supply (7 to 21V)

0.9V power rail (off in S3-S5)

Processor System Bus(PSB) Termination (1.05V)

Core voltage for DOTHAN CPU (1.356 - 0.844V)

1.8V power rail(off in S4-S5)

3.3V switched power rail (off in S3-S5)

2.5V switched power rail (off in S3-S5)

3.3V power rail (off in S4-S5)

5.0V switched power rail (off in S3-S5)

5V power rail (off in S4-S5)

4

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

(OPTION)

2

MiniPCI SLOT

Devices

LOM

Cardbus

External PCI Devices

ICH6-M

CK-410 (Clock Generator)

CY25823ZC(Spread Spectrum)

Devices

I C / SMBus Address

SODIMM0

EMC6N300(Thermal Sensor)

MICOM

BATTERY

SODIMM1

USB PORT Assign

(OPTION)

1

PORT NUMBER

3

0

P1.5V

P1.5V_AUX

VCC_CORE

VTT

VDC

Voltage Rails

P0.9V

P1.8V_AUX

MICOM_P3V

P3.3V

P3.3V_ALWAYS12P2.5V

P3.3V_AUX

P5V

P5V_AUX

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

See revision notes in the changes file for more information.

REVISION HISTORY

D

B

A

4

3

2

1

SAMSUNG X06 9-4

D

C

www.kythuatvitinh.com

C

B

A

SAMSUNG

464

OF

BA41-00529A

ELECTRONICS

PART NO.REV

PAGE

1

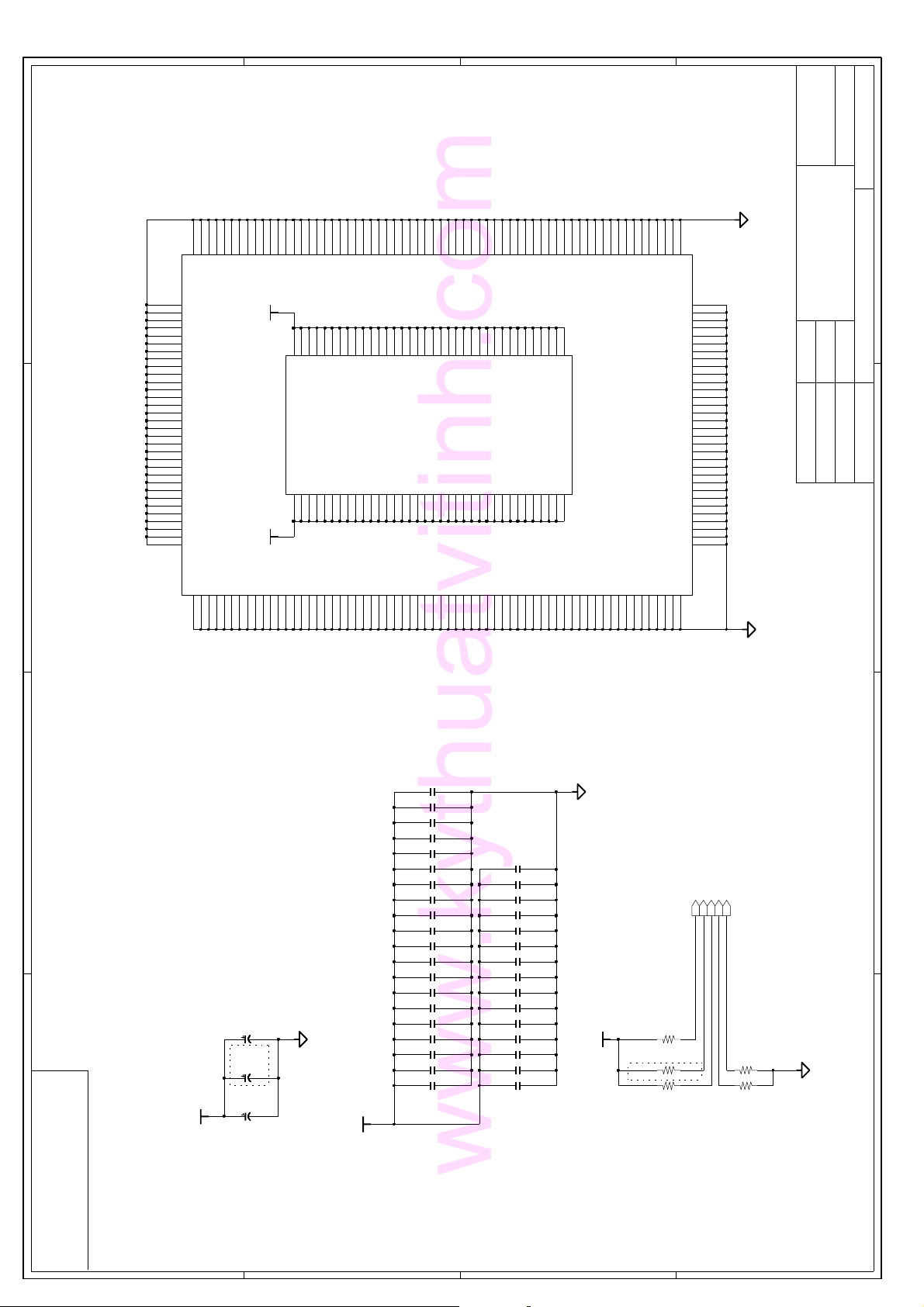

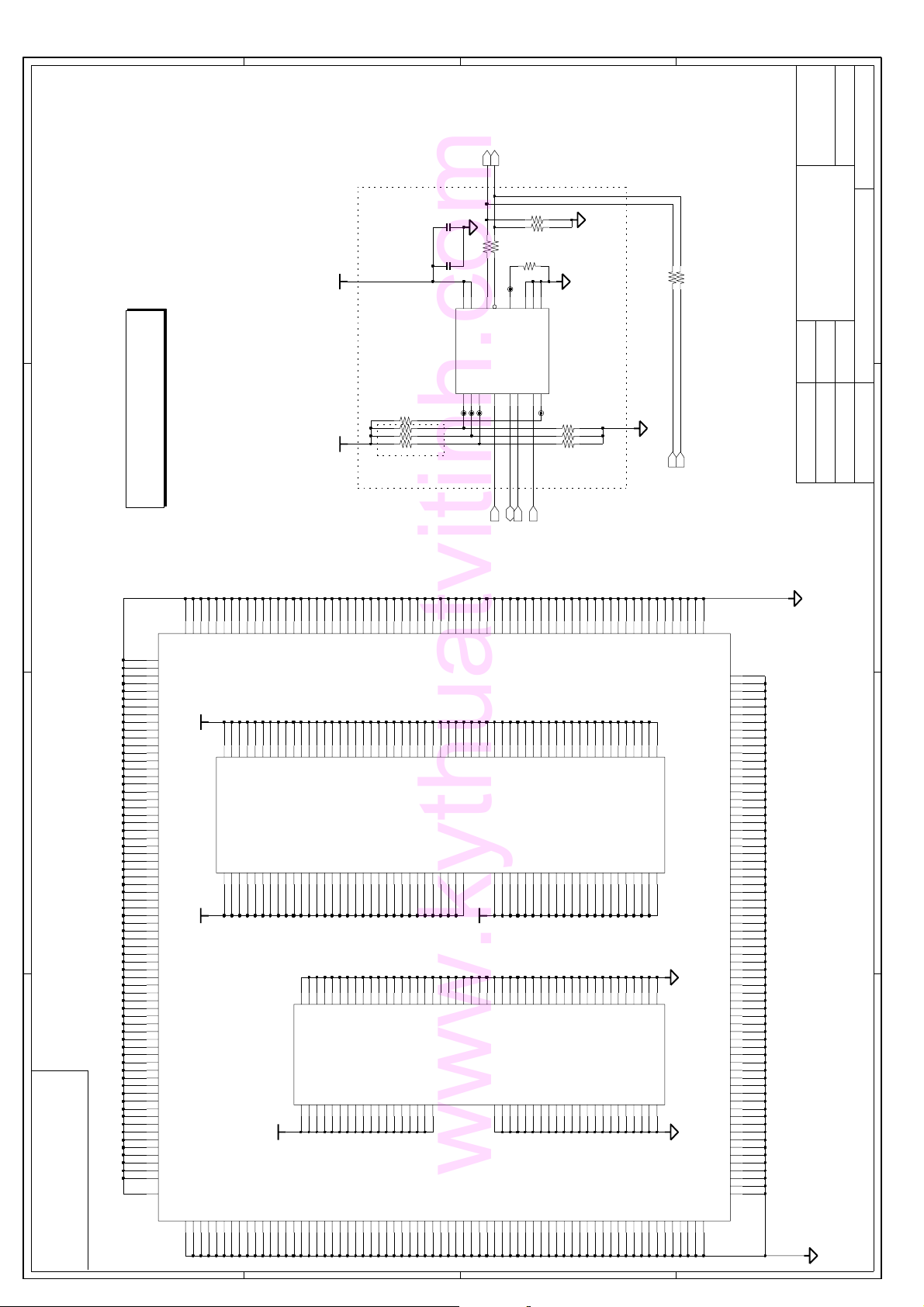

KBC3_VRON

ALVISO-GM

ICH6-M

P1.5V

R5C841

TPM

MiniPCI

EMA(AON)

MICOM

PCMCIA

LEDs

Thermal Sensor

FWH

SODIMM

LCD

MDC

ICH6-M

CK410-M

ALVISO-GM

P3.3V

ICH6-M

R5C841

ALVISO-GM

P2.5V

HDD

MiniPCI

PCMCIA

USB

ICH6-M

ODD

HEATSINK

FAN CIRCUIT

MDC

PS/2

MICOM

R5C841

CRT

DDR II-Termination

P0.9V

GMCH VCC_MCH

CPU VCCP

VTT

VCC_CORE

DOTHAN533 / YONAH

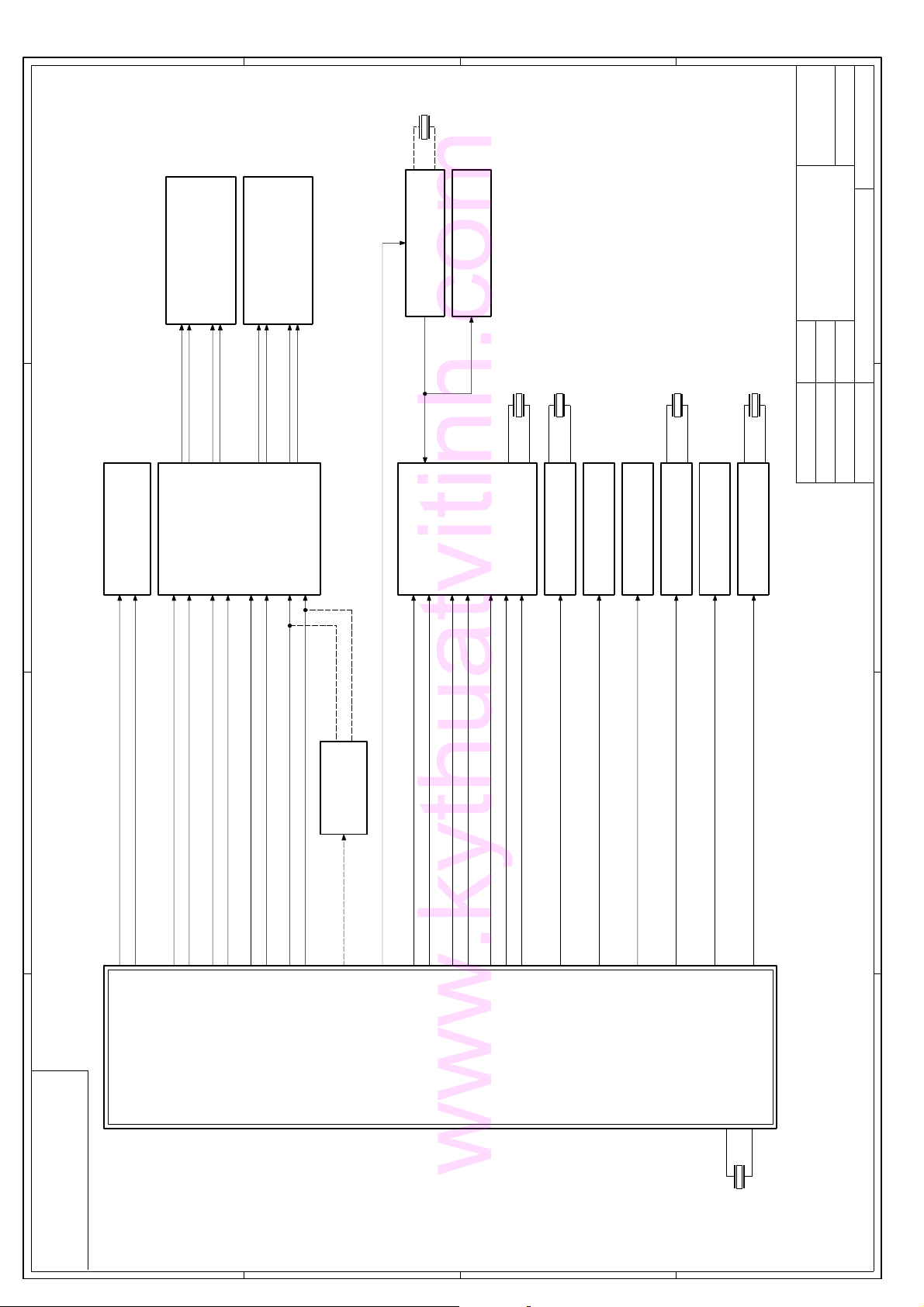

MAIN

POWER DIAGRAM

AQUILA-SONOMA

TITLE

1.0

MP

6/25/2005

DATE

DEV. STEP

ANTONIO

KEVIN LEE

ZHOU & GUO

DRAW

CHECK

APPROVAL

June 25, 2005 12:21:39 PM

LAST EDIT

MODULE CODE

2

KBC3_PWRON

BT

ICH6-M

ICH6-M MDC

LAN

DDR Power

ALVISO-GM

SODIMM (DDR II)

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

P1.5V_AUX

KBC3_SUSPWR

ALWAYS

BATTERY

ADAPTOR

P3.3V_AUX

P3.3V_ALWAYS

P5V_AUX P5V

BRIDGE

BATTERY

P1.8V_AUX

VDC

3

MICOM_P3V

4

D

A

B

C

D

4

3

2

SAMSUNG X06 9-5

1

www.kythuatvitinh.com

CPU1_VID(0:5)

VTT

VCC_CORE

P1.5V

C

VTT

P1.8V_AUX

P1.5V

P2.5V

P3.3V

B

TPM

ODD

MINIPCI

A

SAMSUNG

BA41-00529A

ELECTRONICS

546

PART NO.

PAGE OF

LCD

HOST CLOCK

REF CLOCK

PCI CLOCK

USB CLOCK

CLK GEN.

P3.3V

CHP3_PCISTP*

CHP3_CPUSTP*

CLK3_PWRGD*

KBC3_PWRSW*

P3.3V_AUX

SENSOR

THERMAL

KBC3_PWRGD

CLK3_PWRGD*

CPU

CPU1_A20M*/NMI*

CPU1_SLP*

CPU1_DPSLP*/DPRSLP*

CPU1_INIT*

CPU1_PWRGDCPU

CPU1_STPCLK*

BIST

(24)

CPU1_CPURST*

GMCH

PWROK

RSTIN*

(23-2)

(14-1)

PLT3_RSTF*

KBC3_IMVP4_PWRGD

CPU1_SLP*

CPU1_CPURST*

(27-1)

(26-1)

LCD2_BKLTON

LCD2_VDDEN

VDD_LCD

(26-2)

FDS4465

P3.3V

INV_VDC

(25-2)

FDS4465

VDC

LCD2_VDDEN

LCD3_BKLTON

(27-2)

LCD2_BKLTON

KBC3_BKLTON

CHP3_IVTPWRON

PLT3_RSTF*

FWH

PLT3_RSTF*

FWH3_INIT*

PLT3_RSTF*

HDD

PLT3_RSTF*

PCI3_RST*

CARDBUS

PCI3_RST*

MAIN

AQUILA-SONOMA

TITLE

MP

6/25/2005

DATE

DEV. STEP

ANTONIO

ZHOU & GUO

DRAW

CHECK

1

June 25, 2005 12:21:39 PM

POWER ON SEQUENCE

1.0

REV

LAST EDIT

KEVIN LEE

APPROVAL

MODULE CODE

2

P1.5V_AUX

VTT

(6-2)

(13)

VCC_CORE

IMVP4_PWRGD

(16)

(15)

P5V_AUX

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

P5V

P3.3V_AUX

P1.5V_AUX

P3.3V

P1.5V

P2.5V

VTT

(13)

+-

CHP3_CPUSTP*

CHP3_PCISTP*

CHP3_DPRSLPVR

CPU1_SLP*

(14-1)

(14-1)

(14-1)

(14-1)

PRTC_BAT

CHP3_RTCRST*

(1-0)

(1-1)

+-

RTC BATTERY

VDC

(2-0)

BATTERY

CHP3_IVTPWRON

CPU1_PWRGDCPU

CPU1_A20M*/NMI*

CPU1_DPSLP*/DPRSLP*

CPU1_INIT*

CPU1_STPCLK*

(14-1)

(14-1)

FWH3_INIT*

(22)

(23-1)

(19)

(23-1)

(25-1)

ICH6-M

A20GATE

KBC3_A20G

KBC3_CPURST*

AD_SEL

(2-1)

AC ADAPTOR

CHP3_SUSSTAT*

PCI3_RST*

PLT3_RST*

(20)

(21)

(21)

VRMPWRGD

PWROK

RCIN*

KBC3_IMVP4_PWRGD

KBC3_PWRGD

CHP3_SLPS3*

CHP3_SLPS4*/SLPS5*

(9)

(8-1/2)

CHP3_PWRBTN*

KBC3_RSMRST*

MICOM_P3V

(3-0)

VDC

CHP3_SLPS3*

CHP3_SLPS4*/SLPS5*

KBC3_RST*

P3.3V_AUX

P3.3V

KBC3_RST*

(3-1)

LP2951CM-3.3

CLK3_PWRGD*

CHP3_SUSSTAT*

PLT3_RST*

(10-2)

99ms Later

than 3.3V OK

(7-1)

CHP3_PME*

KBC3_PWRSW*

KBC3_RSMRST*

KBC3_PWRSW*

(4-1)

POWER SWITCH

IMVP4_PWRGD

KBC3_SUSPWR

KBC3_VRON

KBC3_BKLTON

(5)

(12)

(21-1)

MICOM

(7-2)

(18-1)

(18-2)

KBC3_IMVP4_PWRGD

CHP3_PWRBTN*

KBC3_PWRGD

KBC3_PWRON

(10-1)

(17-2)

(17-1)

KBC3_CPURST*

KBC3_A20G

CHP3_PME*

PCI3_RST*

(4-2)

LAN

P2.5V_LAN

P1.2V_LAN

P3.3V_ALWAYS

VDC

P5V_AUX

VDC

P3.3V_AUX

KBC3_PWRON KBC3_SUSPWR KBC3_VRON

SC1485

VCCP / VCC_MCH

KBC3_SUSPWR

KBC3_VRON

P3.3V_ALWAYS

P5V_AUXOn DC/DC Module

(3-2)

(6-0)

LTC3728

KBC3_SUSPWR

AD_SEL

P2.5V

(11-0)

MIC5219

P3.3V_ALWAYS

KBC3_PWRON

(14-2)

VDC

VTTPWRGD

P3.3V_ALWAYS

P3.3V

(11-0)

KBC3_PWRON

P5V

P3.3V_AUX

(6-1)

SI3443

KBC3_SUSPWR

FDS4465

P1.5V_AUX

IMVP-4

LTC3735

CHP3_CPUSTP*

VTTPWRGD

P5V_AUX

VDC

P1.5V

(11-0)

FDS4465

KBC3_PWRON

CHP3_DPRSLPVR

P1.8V_AUX

(6-2)

(11-1)

SC1486

P5V

KBC3_SUSPWR

P5V

(11-0)

FDS4465

P5V_AUX

KBC3_PWRON

P0.9V

MEM1_VREF

(11-1)

DDR II POWER

3

4

1

B

D

D

A

SAMSUNG X06 9-6

2

www.kythuatvitinh.com

C

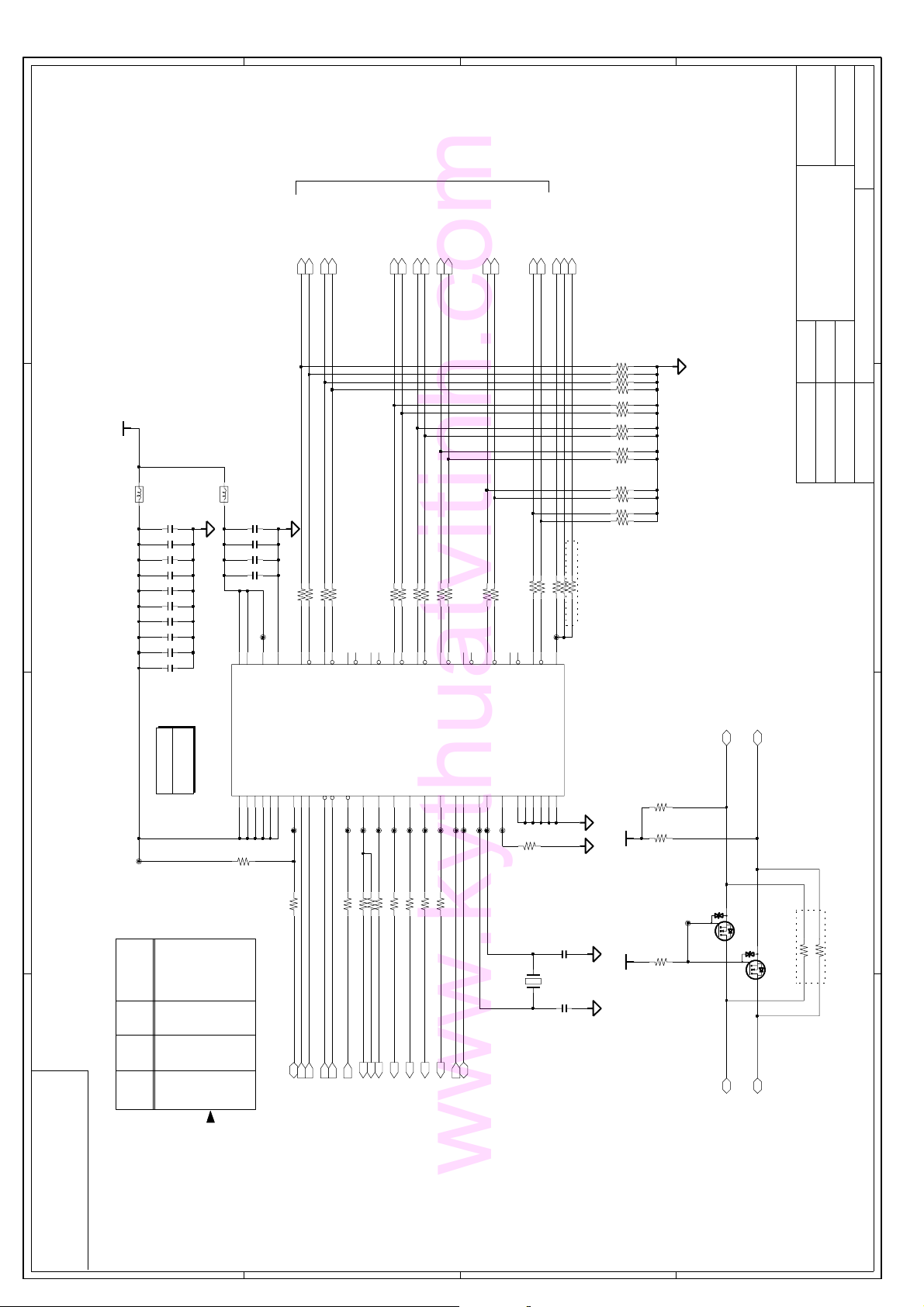

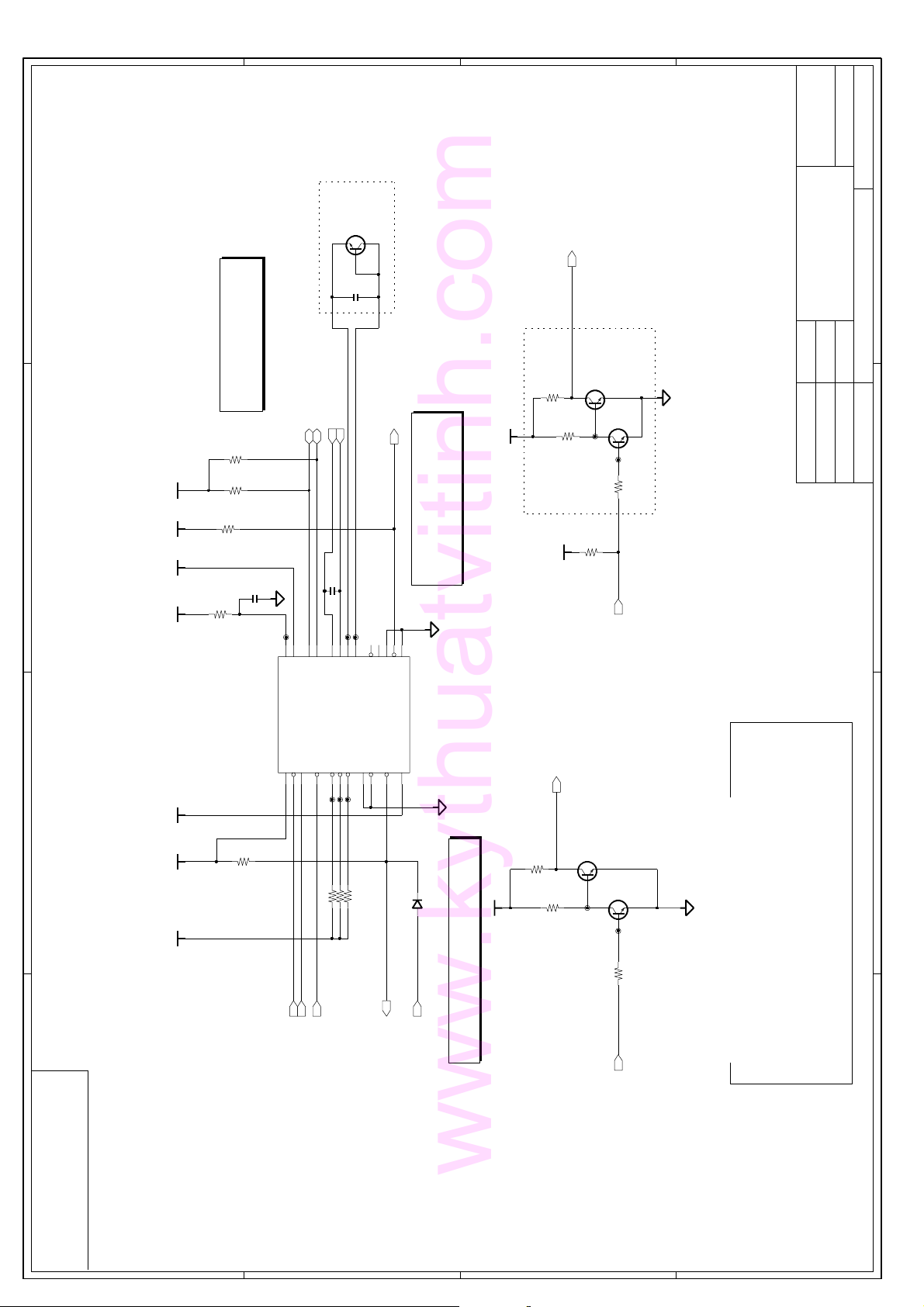

24.576MHz

B

A

SAMSUNG

466

OF

BA41-00529A

ELECTRONICS

PART NO.

PAGE

1

MDC

DDR II

CHANNEL A

CLK0_MCLK0/0*

CLK0_MCLK1/1*

CPU

100MHz496MHz

DDR II

CHANNEL B

200MHz / 266MHz

CLK0_MCLK4/4*

CLK0_MCLK3/3*

GMCH

100MHz

AUDIO CODEC

12.288MHz

CHP3_AC97_AUD_BCLK

RTC CLOCK

CHP3_AC97_MDC_BCLK

ICH6-M

100MHz

100MHz

33MHz

48MHz

14.318MHz

32.768KHz

10MHz

MICOM

33MHz

FWH

33MHz

TPM

33MHz

24.576MHz

1394 CLOCK

MINIPCI

CARDBUS

33MHz

33MHz

25MHz

LAN

33MHz

MAIN

CLOCK DIAGRAM

AQUILA-SONOMA

TITLE

1.0

MP

6/25/2005

DATE

DEV. STEP

REV

ANTONIO

KEVIN LEE

ZHOU & GUO

CHECK

DRAW

APPROVAL

June 25, 2005 12:21:39 PM

LAST EDIT

MODULE CODE

2

100MHz / 133MHz

CLK0_HCLK0

100MHz / 133MHz

CLK0_HCLK1*

CLK0_HCLK1

CLK0_HCLK0*

CLK1_DREFCLK

CLK1_MCH3GPLL*

CLK1_MCH3GPLL

CLK1_DOTCLK

CLK1_DREFCLK*

CLK1_DREFSSCLK

CLK1_DREFSSCLK*

SSC

CY25823ZC

14.318MHz

CLK3_SSCIN

CLK1_DOTCLK*

CLOCK

GENERATOR

CLK1_PCIEICHCCLK3_PCLKICH3CLK3_PCLKMICOM

CLK3_AUD14

14.318MHz

CLK1_SATA

CLK1_SATA*

CLK1_PCIEICH*

CLK3_USB48

CLK3_ICH14

or

CK410-M

CY28411

ICS954201

CLK3_PCLKFWH

CLK3_PCLKCB

CLK3_TPMLPC

CLK3_PCLKLAN

CLK3_PCLKMIN

3

4

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

14.318MHz

3

D

1

2

SAMSUNG X06 9-7

4

www.kythuatvitinh.com

C

B

A

467

OF

BA41-00529A

ELECTRONICS

SAMSUNG

Zdiff=100ohm

PART NO.

PAGE

1

CLK3_AUD14

CLK1_DREFCLK

16-A2

17

18

SRC0

SRC0*

CLK1_DREFCLK*

CLK3_ICH14

13-A1

20-B1

13-A1

46-C3

1%

1%

1%

33

33 1%

12.1

12.1

R614

R579

R581

R611

52

14

15

REF

DOT96

DOT96*

CLK3_SSCIN

16-B246-C3

46-C3 32-D4

1%

1%

1%

1%

1%

1%

1%

1%

1%

1%

1%49.9

1%

1%12.1

R578

NO_STUFF

49.9

49.9

49.9

49.9

49.9

49.9

49.9

49.9

49.9

49.9 1%

49.9 1%

49.9

49.9

R586

R589

R582

R585

R590

R592

R623

R626

R619

R621

R615

R617

R612

Place Termination close to CK-410M

R613

CLK3_SMBCLK

CLK3_SMBDATA

CLK1_SATA

CLK1_MCH3GPLL

CLK1_SATA*

CLK1_MCH3GPLL*

CLK1_PCIEICH

CLK1_PCIEICH*

CLK1_DOTCLK

20-B1

CLK1_DOTCLK*

16-B2

CLK0_HCLK0

CLK0_HCLK1*

CLK0_HCLK1

9-C3

9-C3

12-B2

CLK0_HCLK0*

13-D4

13-D4

19-B4

19-B4

20-B1

P3.3V

MMZ1608S121AT

B18

B512

MMZ1608S121AT

C170

6.3V

10000nF

C646

100nF

100nF

100nF

47nF

47nF

47nF

10nF

10nF

1000nF

C176

C175

C167

C179

C644

C645

C647

C169

C177

100nF

100nF

47nF

11

48

VDD_48

VDD_REF

6.3V

10000nF

C168

C178

C166

37

38

VDD_A

VSS_A

33 1%

R587

41

CPU1

1%33

R588

40

CPU1*

1%33

R583

44

CPU0

33 1%

R584

43

CPU0*

33

32

35

36

SRC6

SRC6*

CPU2_ITP_SRC7

CPU2*_ITP_SRC7*

33 1%

R591

31

SRC5

1%33

R593

30

SRC5*

1%

33

R624

26

SRC4

1%

33

R625

27

SRC4*

1%

33

R620

24

SRC3

1%

33

R622

25

SRC3*

22

23

SRC2

SRC2*

1%33

R616

19

SRC1

1%

33

R618

20

SRC1*

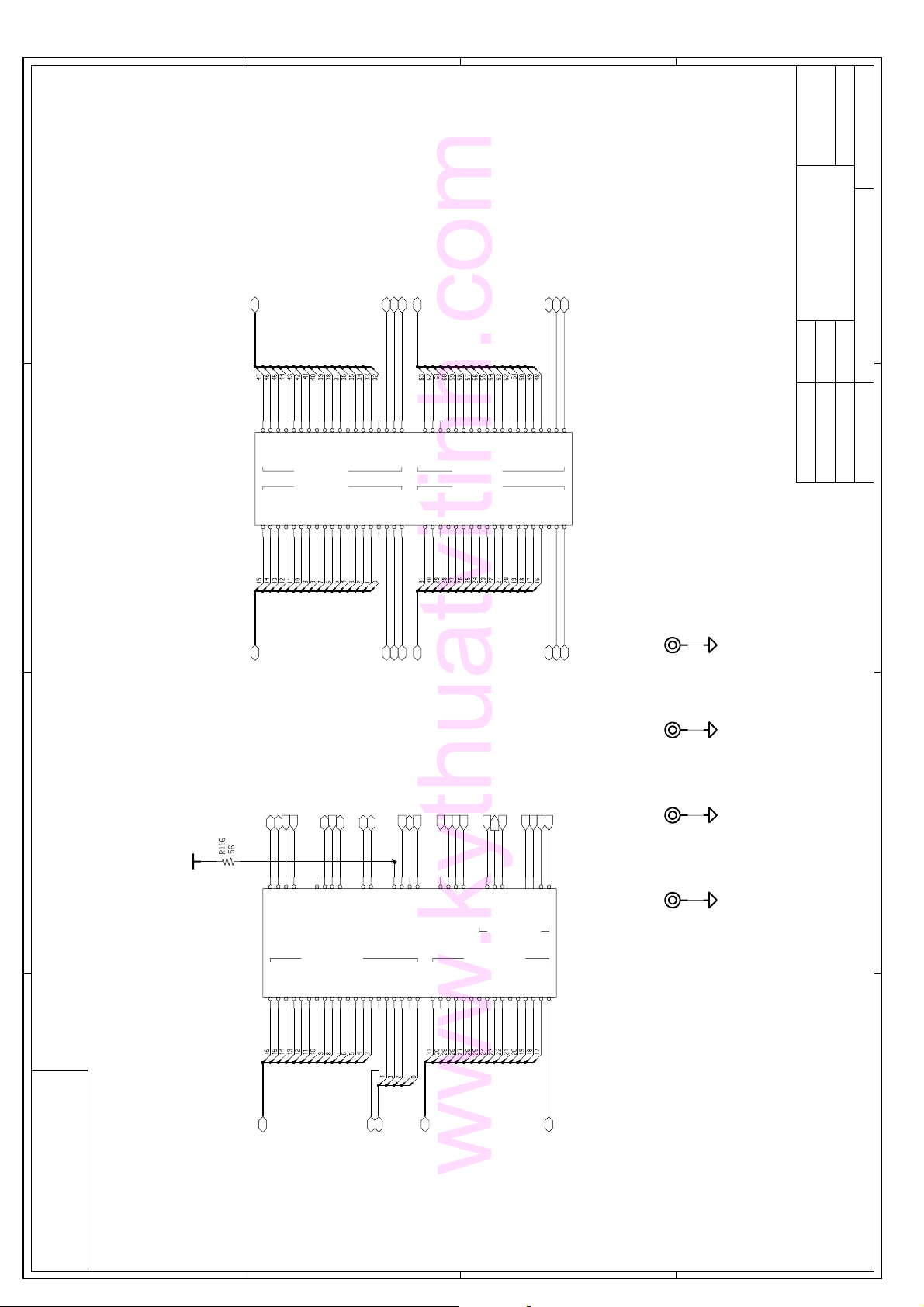

MAIN

CLOCK GENERATOR

AQUILA-SONOMA

TITLE

1.0

MP

6/25/2005

REV

DATE

DEV. STEP

ANTONIO

KEVIN LEE

ZHOU & GUO

DRAW

CHECK

APPROVAL

June 25, 2005 12:21:39 PM

LAST EDIT

MODULE CODE

2

R569

RHU002N06

QF507

S

1

G

D

46-C422-D320-D2

16-B2

17-B217-B4 7-C4

2

QF506

RHU002N06

3

S

1

G

D

20-D2 22-D3 46-A416-B2

SMB3_CLK

17-B4 17-B2 7-B4

2

3

SMB3_DATA

R580

0

R577

0

NO_STUFF

NO_STUFF

3

4

ICS954201

CY28411ZC

CK-410M

HOST CLK

FSC

BSEL0

0 266 MHz

FSBFSA

BSEL1

0

BSEL2

U507

133 MHz

400 MHz

200 MHz

100 MHz

0

1

1

010

0

0 333 MHz

0

01

1

01

1

0

CY28411/ICS954201

10K

VDD_CPU

VDD_PCI01VDD_PCI1

VDD_SRC021VDD_SRC128VDD_SRC2

7

42

34

R156

FSA_USB48

FSB_TESTMODE

FSC_TESTSEL

55

12

16

53

1%

33

R157

PCI_STOP*

CPU_STOP*

VTT_PWRGD*_PD

54

10

1%

100

R610

166 MHz

46-C220-C2

20-A2 46-C3

9-C2 9-C3 13-A4 46-C3

9-C2 9-C3 13-A4 46-C3 12-B2

CLK1_BSEL2

CLK1_BSEL1

CLK3_USB48

CHP3_PCISTP*

46-C242-C4

11-C4 16-B2 36-B2 36-C1 46-C3

20-C2

CLK3_PWRGD*

CHP3_CPUSTP*

1

1

1 RSVD

1

10

PCI33PCI44PCI5

5

56

1%

1%33

1%

33 1%

12.1

33 1%

12.1

R607

R606

R604

R576

R605

46-C334-C2

25-C4 46-C2

26-A4 46-C3

29-C4 46-B2

CLK3_PCLKCB

CLK3_TPMLPC

CLK3_PCLKMIN

CLK3_PCLKFWH

SCLK46SDATA

PCI2

PCIF0_ITPEN

PCIF1

9

8

1%

33

33 1%

R608

R609

46-D2

30-B4 46-C2

36-C2

20-C3 46-C2

CLK3_SMBCLK

CLK3_PCLKICH

CLK3_PCLKLAN

CLK3_PCLKMICOM

IREF

XTAL_IN50XTAL_OUT

47

39

49

7-A3 17-B2 17-B4

7-A3 17-B417-B2

CLK3_SMBDATA

VSS_48

VSS_CPU45VSS_PCI02VSS_PCI1

VSS_SRC

6

13

51

29

1%

475

R145

2

1

Y500

14.31818MHz

Place 14.318MHz within

500mils of CK-410M

VSS_REF

C655

0.033nF

0.033nF

C642

P3.3V

P3.3V

2.2K

R953

R952

2.2K

TP4064

10K

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

D

C

B

A

D

www.kythuatvitinh.com

C

A

OF

BA41-00529A

ELECTRONICS

SAMSUNG X06 9-8

846

SAMSUNG

PART NO.

PAGE

CPU (1/3)

June 25, 2005 12:21:39 PM

1.0

LAST EDIT

REV

KEVIN LEE

APPROVAL

MODULE CODE

1

1

MAIN

AQUILA-SONOMA

AB24

D51*

D19*

L23

D50*

D18*

AC23

D49*

D17*

G25

AB25

H23

12-B2

AD20

D48*

D16*

J26

12-B2

CPU1_DSTBP3*

CPU1_DBI3*

CPU1_DSTBN3*

12-B2

12-B2

AE24

AE25

DINV3*

DSTBP3*

DSTBN3*

DINV1*

DSTBN1*

DSTBP1*

L24

K24

12-B2

12-B2

MT512

RMNT-2.5-1P

TITLE

6/25/2005

DATE

ZHOU & GUO

DRAW

MP

DEV. STEP

ANTONIO

CHECK

CPU1_D*(47:32)

12-D4

V24

U25

V26

Y23

AA26

Y25

D43*

D44*

D45*

D46*

D47*

D42*

U26

D41*

AA23

D40*

R23

V23

R24

R26

D39*

D37*

D38*

DATA GRP 2

D36*

U23

D35*

T25

AA24

D34*

CPU1_DBI2*

CPU1_DSTBN2*

12-B2

12-B2

T24

W25

Y26

D32*

D33*

DINV2*

DSTBN2*

CPU1_D*(63:48)

CPU1_DSTBP2*

12-B2

12-D4

W24

AF25

AF22

AF26

D62*

D63*

DSTBP2*

D61*

AD21

D60*

AE21

D59*

AF20

D58*

AD24

D57*

AF23

AE22

D56*

AC22

AC25

AD23

D52*

D53*

D54*

D55*

DATA GRP 3

AC20

DATA GRP 0DATA GRP 1

D0*

DSTBN0*

D6*

D7*

D8*

D9*

D5*

2

2 / 4

CPU500-2

C25

12-D4

E24

B23

E23

D24

C26

D10*

D11*

D12*

D13*

D14*

D15*

D4*

A21

B20

B24

B26

A24

B21

C20

DSTBP0*

DINV0*

D3*

D2*

D1*

A19

A22

A25

C23

D25

12-B2

12-B2

C22

12-B2

K25

12-D4

D31*

N25

D30*

H26

D29*

M25

D28*

N24

D27*

D20*

D21*

D22*

D23*

D24*

D25*

D26*

J23

J25

L26

F25

H24

G24

M23

M26

CPU1_HITM*

CPU1_HIT*

CPU1_DRDY*

CPU1_DBI0*

CPU1_D*(31:16)

CPU1_DSTBP0*

CPU1_DSTBN0*

CPU1_LOCK*

CPU1_TRDY*

CPU1_INIT*

CPU1_A20M*

CPU1_RS2*

CPU1_RS1*

CPU1_RS0*

CPU1_CPURST*

CPU1_IGNNE*

CPU1_FERR*

CPU1_D*(15:0)

CPU1_ADS*

CPU1_BPRI*

CPU1_BNR*

CPU1_BREQ*

CPU1_DBSY*

CPU1_DEFER*

3

12-C2

12-C2

12-C2

12-C2

12-B2

12-B2

12-B2

12-B2

12-B2

19-C2

12-B2

12-A2

12-C2

12-A2

12-A2

12-A2

19-C246-C3

19-C119-C2

19-C246-B3

CPU1_NMI

CPU1_INTR

CPU1_SMI*

19-C246-D4

19-C246-D4

19-C246-B2

19-C246-C4

CPU1_DBI1*

CPU1_DSTBP1*

CPU1_DSTBN1*

CPU1_STPCLK*

MT511

RMNT-2.5-1P

MT509

RMNT-2.5-1P

3 2

VTT

K1

L2

M3

B5

J2

B11

TRDY*

RS2*

RESET*

RS1*

H1

RS0*

C2

A20M*

N2

ADS*

L1

J3

BNR*

N4

BPRI*

BR0*

A7

M2

DBR*

L4

DBSY*

DEFER*

H2

DRDY*

K3

K4

A4

HIT*

INIT*

IERR*

HITM*

LOCK*

ADDR GROUP 0

1 / 4

CPU500-1

AA2

12-D2

A16*

AA3

A10*W2A11*

A4*

A5*R3A6*

A7*

A8*

A9*

A12*

A13*

A14*Y3A15*

T4

Y4

V3

V2

Y1

U1

P4

U4

W1

ADSTB0*

A3*

U3

12-C2

REQ4*

T1

12-B2

REQ3*

P1

REQ0*

REQ1*T2REQ2*

A31*

A30*

P3

R2

AF1

AE1

12-D2

AF3

A29*

AD6

A28*

AE2

A27*

AD5

A26*

AC6

A25*

A24*

AB4

4

D3

FERR*

A23*

AD2

A3

AE4

IGNNE*

A22*

A21*

AC3

AD3

D1

A20*

AC7

B4

C6

SMI*

LINT0D4LINT1

STPCLK*

LEGENCY CPU

ADDR GROUP 1

ADSTB1*

A17*

A18*

A19*

AF4

AE5

AC4

12-C2

MT508

RMNT-2.5-1P

4

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

D

CPU1_A*(16:3)

C

CPU1_ADSTB0*

CPU1_REQ*(4:0)

CPU1_A*(31:17)

CPU1_ADSTB1*

B B

A

3

2

D

1

SAMSUNG X06 9-9

4

www.kythuatvitinh.com

C

VTT

R113

200

42-C4 46-D4

9-C3

VTT

1K 1%

R122

0

R123

7-C4 46-C313-A49-C3

1%1K

R136

NO_STUFF

0

R137

7-C4 46-C313-A49-C3

NO_STUFF

B

C147

C150C155

C107

C129

C128

C149

C106

C148

C127

EC12

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

100nF

4V

220uF

16V 16V16V

16V

16V

16V

16V

16V

16V

16V

AL

VTT

CPU1_PSI*

CLK1_BSEL1

CLK1_BSEL2

A

SAMSUNG

AQUILA-SONOMA

TITLE

6/25/2005

DATE

ZHOU & GUO

DRAW

BA41-00529A

ELECTRONICS

PART NO.

MAIN

CPU (2/3)

1.0

MP

REV

DEV. STEP

ANTONIO

KEVIN LEE

APPROVAL

CHECK

OF

946

PAGE

14

June 25, 2005 12:21:39 PM

LAST EDIT

MODULE CODE

2

6.3V

10uF

C654

P1.5V

16V

100nF

C165

D14

D16

E11

D12

B1

AC26

D10

F26A15

VCCP3

VCCP4

VCCP5

VCCP2

VCCA0

VCCA1N1VCCA2

VCCA3

VCCP1

VCCAVCCPXDP/ITP

HCLKPWR MGMTVIDTHERMMISC

ITP_CLK1

ITP_CLK0

BCLK0

BCLK1

3 / 4

CPU500-3

A16

B15

B14

VTT

R117

200

7-C1

7-C1

CLK0_HCLK0

CLK0_HCLK0*

SLP*

DPRSTP*

DPSLP*

DPWR*

A6

B7

G1

C19

46-B222-B319-C2

19-C2 22-B3 46-C3

12-A2 19-C2 46-D4

CPU1_SLP*

CPU1_DPWR*

CPU1_DPSLP*

CPU1_DPRSLP*

PWRGOOD

E4

12-B2

CPU1_PWRGDCPU

E13

E15

F10

F12

F14

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

5

4

3

2

46-B342-B142-A2

46-A2

19-C2

CPU1_VID(5:0)

VTT

F16

L21

M6

VCCP11K6VCCP12L5VCCP13

VCCP14

VCCP15

VID0F2VID1F3VID2G3VID3G4VID4H4VID5

THERMDA

PROCHOT*E1PSI*

E2

B18

B17

1

0

11-B2 46-A2

CPU2_THERMDA

CPU1_PROCHOT*

M22

N21

P22

VCCP16N5VCCP17

VCCP18P6VCCP19

VCCP20R5VCCP21

THERMDC

THERMTRIP*

BSEL0

BSEL1

A18

C17

C16

C14

46-C313-A49-C27-C4

19-C219-C113-A111-B4 46-D2

46-B211-C2

46-B211-C2

7-C4 9-C2 13-A4 46-C3

CLK1_BSEL1

CLK1_BSEL2

CPU2_THERMDC

CPU1_THRMTRIP*

R21

T22

U21

VCCP22T6VCCP23

VCCP24

GTLREF0

AD26

9-C2 42-C4 46-D4

CPU1_PSI*

W4

VCCQ1

VCCP25

COMP2

COMP3

AB2

AB1

R110

R109

27.41%

1% 54.9

P23

VCCQ0

COMP1

P26

R144

B10

COMP0

P25

R143

1% 27.4

A10

C9

PRDY*

PREQ*

VSSSENSE

VCCSENSE

AF6

AE7

BPM0*C8BPM1*B8BPM2*A9BPM3*

NC1_RSVD1

RSVD2

RSVD3

B2

C3

AF7

CPU1_TDO

CPU1_TCK

CPU1_TDI

10-A346-C4

46-C4 10-A3

46-C4 10-A3

A13

C12

A12

C11

TDI

TCK

TDO

RSVD4

RSVD5

C5

E26

AC1

R108

54.9

54.9

R121

CPU1_TRST*

CPU1_TMS

10-A3

10-A346-C4

B13

TMS

TRST*

TEST1

TEST2

F23

1K

1K

1%

1%

NO_STUFF

NO_STUFF

R115

R114

NO_STUFF

NO_STUFF

3

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

R111

2K

R112

1% 54.91%

1K

1%

VTT

COMP 0 , 2 <(COMP 1,3) should be connected

Z0=27.4 ohm (55 ohm) trace shorter than

1/2 " to their respective Banias Pins

THERTRIP* should connect to ICH6M & Alviso

OD signal driven by CPU and GMCH

D

C

of the First GTLREF0 with Z0= 55 ohm trace

GTLREF : Keep the Voltage divider within 0.5"

Minimize coupling of any switching signals to this net

B

A

B

4

D

D

1

A

2

C

SAMSUNG X06 9-10

3

www.kythuatvitinh.com

C

B

A

4610

OF

BA41-00529A

ELECTRONICS

SAMSUNG

PART NO.

PAGE

14

AF24

AF21

AF19

AF17

AF15

AF13

AF11

AF9

AF5

AF2

AE26

AE23

AE20

AE18

AE16

AE14

AE12

AE10

AE8

AE6

AE3

AD25

AD22

AD19

AD17

AD15

AD13

AD11

AD9

AD7

AD4

AD1

G23

VSS65

VSS1

A2

G26

VSS67H3VSS68H5VSS69

VSS66

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

VSS161

VSS2

VSS3

A5

A8

A11

H21

VSS4

A14

H25

VSS5

A17

VSS70

VSS6

J22

VSS71J1VSS72J4VSS73J6VSS74

CPU500-4

VSS9

VSS10

VSS8

VSS7

B3

A26

A23

A20

K5

K21

J24

K2

VSS77

VSS78

VSS75

VSS76

AA17

VCC37

VCC1

4 / 4

D6

VCC_CORE VCC_CORE

VSS14

VSS13

VSS12

VSS11

B9

B6

B16

B12

K23

VSS79

AA19

VCC38

VCC2

D8

VSS15

B19

K26

VSS80

VSS81L3VSS82L6VSS83

AA21

AB6

VCC39

VCC40

VCC4

VCC3

D20

D18

VSS17

VSS16

B25

B22

AB8

VCC41

VCC5

D22

VSS18

C1

L22

AB10

VCC42

VCC6

E5

VSS19

C4

M4

L25

VSS84

VSS85M1VSS86

AB12

AB14

AB16

VCC43

VCC44

VCC8

VCC7

E9

E7

E17

VSS20C7VSS21

C10

C13

VSS87M5VSS88

AB18

VCC45

VCC46

VCC10

VCC9

E19

VSS22

VSS23

C15

M21

AB20

VCC47

VCC11

E21

VSS24

C18

M24

VSS89

AB22

VCC48

VCC12

F6

VSS25

C21

N3

N6

VSS90

VSS91

AC9

AC11

VCC49

VCC50

VCC13F8VCC14

F18

VSS26

VSS27D2VSS28

C24

N22

VSS92

AC13

VCC51

VCC15

F20

D5

N23

VSS93

AC15

VCC52

VCC16

F22

VSS29

D7

N26

P2

VSS94

VSS95

AC17

AC19

VCC53

VCC54

VCC17G5VCC18

G21

VSS30D9VSS31

D11

P21

VSS96P5VSS97

AD8

AD10

VCC55

VCC56

VCC19

VCC20

H6

H22

VSS32

VSS33

D13

D15

P24

VSS98

AD12

VCC57

VCC21

J5

VSS34

D17

R1

AD14

J21

D19

R22

VSS99

VSS100R4VSS101R6VSS102

AE9

AD16

AD18

VCC58

VCC59

VCC60

VCC23

VCC24U5VCC25V6VCC26

VCC22

K22

VSS35

VSS36

VSS37

D26

D21

D23

R25

VSS103

AE11

VCC62

VCC61

V22

VSS38

VSS39

E3

T5

T3

VSS105

VSS104

AE13

AE15

VCC63

VCC64

VCC27W5VCC28

W21

VSS40

VSS41E8VSS42

E6

T21

T23

VSS106

AE17

AE19

VCC65

VCC29

Y6

Y22

E10

E12

T26

U2

VSS107

VSS108

AF8

AF10

VCC66

VCC67

VCC30

VCC31

AA7

AA5

VSS43

VSS44

E14

E16

U22

VSS109

VSS110U6VSS111

AF12

AF14

VCC68

VCC69

VCC33

VCC32

AA9

AA11

VSS45

VSS46

E18

E20

U24

VSS112

AF16

AF18

VCC71

VCC70

VCC34

VCC35

AA13

AA15

VSS48

VSS47

E22

E25

VSS113V1VSS114

VCC72

VCC36

VSS49

V4

V21

V25

VSS115V5VSS116

VSS117

VSS118W3VSS119

VSS50F1VSS51F4VSS52F5VSS53F7VSS54

F9

W6

VSS55

F11

W22

W23

VSS120

VSS56

F15

F13

W26

Y2

VSS121

VSS122

VSS58

VSS57

F17

F19

Y21

VSS123

VSS124Y5VSS125

VSS59

VSS60

F21

F24

Y24

VSS126

VSS61

VSS62

G2

AA1

AA4

VSS127

VSS128

VSS63G6VSS64

G22

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

AC8

AC5

AC2

AB9

AB7

AB5

AB3

AA8

AA6

AC24

AC21

AC18

AC16

AC14

AC12

AC10

AB26

AB23

AB21

AB19

AB17

AB15

AB13

AB11

AA25

AA22

AA20

AA18

AA16

AA14

AA12

AA10

MAIN

CPU (3/3)

AQUILA-SONOMA

TITLE

1.0

MP

6/25/2005

REV

DATE

DEV. STEP

ANTONIO

KEVIN LEE

ZHOU & GUO

DRAW

CHECK

APPROVAL

June 25, 2005 12:21:39 PM

LAST EDIT

MODULE CODE

2

6.3V

C115

10000nF

6.3V

C79

10000nF

6.3V

C124

10000nF

6.3V

C119

10000nF

6.3V

C116

10uF,2012 x 35pcs

5mohm ESR, 0.6nH ESL

9mohm ESR, 1.8nH ESL

330uF,7343

Low-frequency Decoupling

AL

2V

330uF

EC506

AL

2V

330uF

EC10EC507

NO_STUFF

2V

AL

330uF

Vcc-core Decoupling (Refer to IMVP-IV Option #4)

VCC_CORE

Mid-frequency Decoupling

VCC_CORE

C80

C153

C121

C118

C77

C151

C120

C117

C76

C152

C122

C104

C84

C154

C105

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

C81

C108

C145

C140

C82

C123

C144

C141

C83

C126

C146

C142

C78

C125

C143

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

6.3V

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

10000nF

VTT

CPU1_TMS

CPU1_TDO

CPU1_TDI

CPU1_TCK

9-B246-C4

9-B246-C4

46-C4 9-B2

46-C4 9-B2

Refer to Sonoma Platform Design Guide(4.6.1.4)

R124

150 1%

R126

54.9 1%

R127

NO_STUFF

39.2 1%

1%

CPU1_TRST*

9-B2

680

27.4

R125

R128

3

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

D

B

1

COM-22C-015(1996.6.5) REV. 3

2

3

C

D

4

A

f:/users/ecad04/mentor/Aquila-S/SR/MP_0625

www.kythuatvitinh.com

C

B

A

4611

OF

BA41-00529A

ELECTRONICS

SAMSUNG

PART NO.

PAGE

1

Q7

Where: Tp = 75 to 106 deg. C

Tp = 1.5V*16 + 75 = 99 deg. C

Guardian Temp-torelance = +/- 3 deg. C

Vset = (Tp-75)/16

10K

R653

R197

10K

P3.3V

R178

10K

P3.3V_AUX

P1.5V

R196

49.9

16V

C233

100nF

1%

MMBT3904

3

2

1

C191

2.2nF

CPU2_THERMDA

KBC3_THERM_SMDATA

CPU2_THERMDC

KBC3_THERM_SMCLK

9-C346-B2

36-C246-C2

46-B2 9-C3

46-C2 36-A2

C190

2.2nF

Nearby MEMORY

MEM3_OVERT*

36-B446-B3

HW_FAILSAFE# output is asserted ’0’ when

the Remote Diodes 1 temp. exceed the temp.

as an input to the THERN_STP# logicExternal interrupt generated on ATF_INT# pin

theshold (Tp) established by the VSET input pin.

HW_FAILSAFE# is an internal signal routed

P3.3V

NO_STUFF

NO_STUFF

NO_STUFF

NO_STUFF

NO_STUFF

R600

10K

R602

VTT

CPU3_ALERT*

46-B3 20-A4

MMBT3904

Q516

3

1

1.5K

1%

3

1%

R603

54.9

2

1

475

R601

MAIN

AQUILA-SONOMA

TITLE

6/25/2005

DATE

DEV. STEP

ZHOU & GUO

2

MMBT3904

Q509

1%

DRAW

CHECK

June 25, 2005 12:21:39 PM

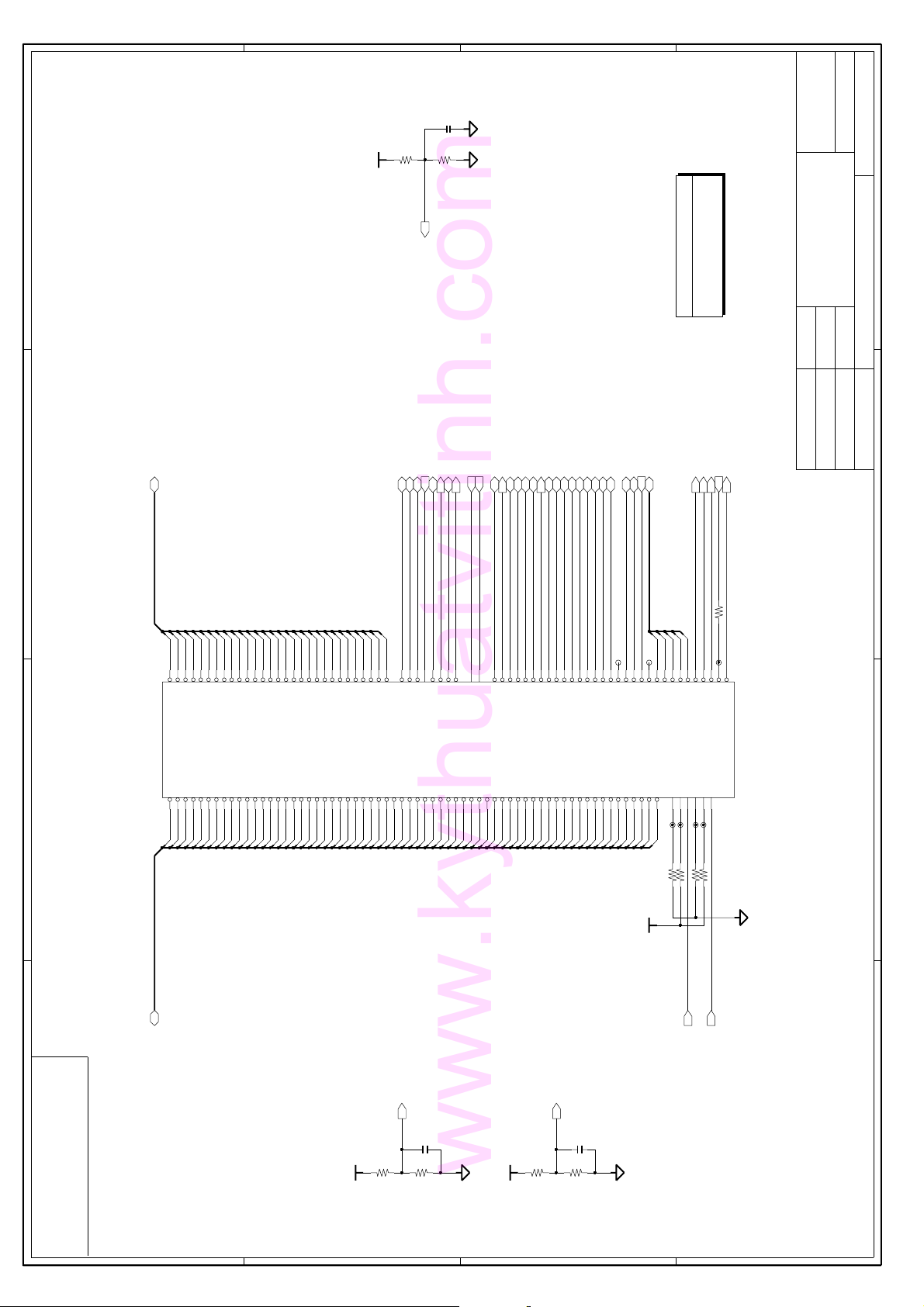

CPU/DDR Thermal Sensor

1.0

MP

REV

LAST EDIT

undefined

ANTONIO

KEVIN LEE

MODULE CODE

APPROVAL

2

46-A29-C3

4

2

1

22

VSET

+3VSUS

THCLK_SMB

THDAT_SMB

+3V_PWROK*

+RTC_PWR3V

POWER_SW*

VSUS_PWRGD

EMC6N300

U11

5

10

21

11

R194

CPU / DDR Thermal Sensor

P3.3V_AUX

P3.3V_AUX P3.3V_AUXP5V_AUX

10K

36-C136-B216-B27-C4 46-C3

36-C426-A422-B320-A2 46-B3

KBC3_PWRGD

CLK3_PWRGD*

KBC3_PWRSW*

19

17

18

REM_DIOD2_P

REM_DIOD2_N

THERMTRIP1*

THERMTRIP2*

6

7

8

100K

100K

100K

46-B336-B2 36-D2 36-D4

R195

R652

R651

37-C3

12

20

16

15

INTRUDER*

REM_DIOD1_P

REM_DIOD1_N

THERMTRIP_SIO

HW_LOCK*

SMBADDRSEL

THERMTRIP3*

9

14

13

46-C236-B4

24

3

VSS

RESERVED

THERM_STP*

SMBUS ADDRESS 5Eh

0101 111X

ATF_INT*

VCP

23

21

D520

MBR0520LT1

OTP(Over Temp. Protection);

43-B2

CPUPWRON

KBC3_THERM_ALERT*

CPU1_PROCHOT*

CHP3_THRMTRIP*

46-D2 36-B2

Q514

R639

1.5K

MMBT3904

3

2

1

3

2

1%

1

1%

475

R637

19-C219-C113-A19-C3 46-D2

MMBT3904

Q515

R638

10K

P3.3V

the 2 monitored voltages VCP and +3VSUS exceed preset limits

when any of the 3 thermal diodes and/or

3

Refer To Thermal Sensor Layout Guidelines.

- Use recommended trace widths and spacings (10mil)

- Place a ground plane under the traces.

- Keep traces away from fast data buses and CRT signal.

- Keep traces away from high voltage (+12V bus)

- Place the Thermal Sensor close to a remote diode.

- Use guard traces flanking DXP and DXN and connecting to GND

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

CPU1_THRMTRIP*

4

2

B

1

4D4

33

12

SAMSUNG X06 9-12

www.kythuatvitinh.com

C

D

D

C

B

A

A

4612

OF

BA41-00529A

ELECTRONICS

SAMSUNG

PART NO.

PAGE

VTT

R119

16V

100nF

C92

100

1%

R120

200

1

12-C2 46-B3

0.7V

MCH1_HVREFMCH1_HVREF

CPU1_A*(31:3)

CPU1_ADS*

CPU1_BREQ*

CPU1_BPRI*

CPU1_BNR*

CPU1_ADSTB1*

CPU1_ADSTB0*

CPU1_CPURST*

CPU1_DBSY*

CPU1_DEFER*

CLK0_HCLK1

CLK0_HCLK1*

CPU1_DBI3*

CPU1_DPWR*

CPU1_DBI2*

CPU1_DBI1*

CPU1_DBI0*

CPU1_DSTBP0*

CPU1_DSTBN3*

CPU1_DSTBN2*

CPU1_DSTBN1*

CPU1_DSTBN0*

CPU1_DRDY*

CPU1_HITM*

CPU1_HIT*

CPU1_DSTBP3*

CPU1_DSTBP2*

CPU1_DSTBP1*

CPU1_REQ*(4:0)

CPU1_LOCK*

(DEFAULT)

ICH : Legancy mode

HSLPCPU*

GMCH: Enhanced mode

CPU1_TRDY*

CPU1_SLP*

CPU1_RS2*

CPU1_RS1*

CPU1_RS0*

MAIN

ALVISO (1/5)

AQUILA-SONOMA

TITLE

1.0

MP

6/25/2005

DEV. STEP

REV

DATE

ANTONIO

KEVIN LEE

ZHOU & GUO

CHECK

APPROVAL

DRAW

June 25, 2005 12:21:39 PM

LAST EDIT

MODULE CODE

8-B4

12-C1

46-B3

J11

HVREF

8-C3

A5

D5

HBNR*

8-C3

E7

HBPRI*

HBREQ0*

8-C308-C3

H10

AB1

HCLKINN

HCPURST*

7-C1

AB2

8-C4

8-C4

8-C3

9627

3

5

8

G9

HA4*C9HA5*E9HA6*B7HA7*

HA3*

6

A10

10

D8

B10

HA8*F9HA9*

E10

HA10*

12

G10

HA11*

HA12*

13

14

E11

HA13*D9HA14*

15

F10

16

G11

HA15*

HA16*

17

G13

HA17*

18

C10

19

C11

HA18*

D11

HA19*

HA20*

21

C12

HA21*

22

B13

A12

HA22*

24

F12

HA23*

HA24*

25

G12

26

E12

HA25*

27

C13

HA26*

28

B11

HA27*

HA28*

29

D13

30

A13

HA30*

HA29*

31

F13

HA31*

F8

E13

HADS*

HADSTB*0B9HADSTB*1

7-C1

C6

HDBSY*

HCLKINP

8-B2

8-C3

8-C2

8-C3

E6

HDINV*0H8HDINV*1K3HDINV*2T7HDINV*3

HDEFER*

8-C1

U5

8-B1

9-C3

G6

F7

HDPWR*

8-C3

8-C2

G4

K1

HDRDY*

HDSTBN*0

HDSTBN*1

8-B1

8-B2

8-C1

R3

V3

HDSTBP*0G5HDSTBP*1

HDSTBN*2

HDSTBN*3

8-B2

8-C1

8-C2

K2

W4

HDSTBP*2R2HDSTBP*3

8-B1

8-C3

TP2658

F6

D4

D6

HHIT*

HEDRDY*

8-C3

8-C3

TP2657

B3

A11

HHITM*

HLOCK*

HPCREQ*

8-C4

1

2

D7

B8

HREQ*0A7HREQ*1

4

3

A8

HREQ*2

HREQ*3C7HREQ*4

A4

HRS0*

8-B3

C5

HRS1*

8-C3

8-C3

0

R568

G8

B4

HRS2*

HCPUSLP*

8-C3

46-D4 19-C2 9-C3

B5

HTRDY*

2

2

HOST

HD48*

HD5*

HD3*

HD0*E4HD1*

HD2*

1 / 5

ALVISO500-1

ALVISO-GMCH

F4

E1

E2

H7

3

2

4

0

HD4*

F1

5

E3

6

HD6*

D3

7

HD7*

HD8*K7HD9*

HD10*J7HD11*J8HD12*H6HD13*F3HD14*K8HD15*H5HD16*

F2

13

11639

10208

142312

15

HD17*

HD18*

HD19*

K5

K6

H1

H2

19

16

18

17

HD21*G3HD22*H3HD23*J1HD24*L5HD25*K4HD26*J5HD27*P7HD28*L7HD29*

HD20*

J4

23427

241%26

22

20

25

21

HD30*

HD31*

HD32*

HD33*

HD34*R6HD35*

HD36*P3HD37*T8HD38*R7HD39*

R5

35

37

36

HD40*U8HD41*R4HD42*T4HD43*T5HD44*R1HD45*

R8

39

41

38

40

43

42

J3

L3

P5

V6

U7

31

33

29

28

34

32

30

HD49*

HD46*

HD47*

HD50*V5HD51*W8HD52*W7HD53*U2HD54*U1HD55*Y5HD56*Y2HD57*V4HD58*Y7HD59*

T3

V8

U3

U6

W6

53

49

51

47145

44

50

46

48

541152

HD60*

HD61*

HD62*

HD63*

HXRCOMPC1HXSCOMPC2HXSWINGD1HYRCOMPT1HYSCOMPL1HYSWING

Y3

Y6

W3

W2

W1

57

55

59

61

60

56

58

P1

1%

1%54.9

24.9 1%

24.9

54.9 1%

3

3

1608

R131

R135

R132

R129

VTT

SAMSUNG PROPRIETARY

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

CPU1_D*(63:0)

D

12-B4 46-B2

8-C1 8-C2

VTT

0.327V

MCH1_HYSWING

46-B2 12-A4

1%

221

R133

C134

R134

B

B

100nF

100

16V

1%

0.327V

MCH1_HXSWING

100nF

C130

10V

46-B2 12-A4

VTT

C

C

R130

R118

100

1%

221

1%

12-C4 46-B2

MCH1_HXSWING

MCH1_HYSWING

4 1

4

A

A

D

B

D

4

A

SAMSUNG X06 9-12

3 1

C

2

www.kythuatvitinh.com

C

B

A

(Def.)

(Def.)

DDR-1

Mobile CPU (Def.)

Normal

Enabled (def.)

VCC 1.5V

P1.8V_AUX

High

DMIx4 (Def.)

Normal(Def.)

VCCP 1.2V

SDVO Present

SAMSUNG

Iris(Grantsdale)

VCC 1.5V

VTT 1.2V

x4 only

DMI1_TXN0

DMI1_TXP0

DMI1_RXN0

DMI1_RXP0

DMI1_TXN1

DMI1_TXP1

DMI1_RXN1

DMI1_RXP1

DMI1_TXN2

DMI1_TXP2

DMI1_RXN2

DMI1_RXP2

DMI1_TXN3

x2 / x4

VCC 1.05V

VTT 1.05V

Alviso

Feature

VCCP

VCC_GMCH

DMI

W36

V32

U36

T32

R36

P32

N36

M32

L36

K32

J36

H32

G36

F32

E36

D32

Y36

W32

V36

U32

TP2592

1%

24.9

R43

T36

R32

P36

N32

M36

L32

K36

J32

H36

G32

F36

E32

W34

V30

U34

T30

R34

P30

N34

M30

L34

K30

J34

H30

G34

F30

E34

D30

Y34

W30

V34

U30

T34

R30

P34

N30

M34

L30

K34

J30

H34

G30

F34

E30

D34

D36

P1.5V

EXP_TXP15

EXP_TXP14

EXP_TXP13

EXP_TXP12

EXP_TXP11

EXP_TXP10

EXP_TXP9

EXP_TXP8

EXP_TXP7

EXP_TXP6

EXP_TXP5

EXP_TXP4

EXP_TXP3

EXP_TXP2

EXP_TXP1

EXP_TXP0

EXP_TXN15

EXP_TXN14

EXP_TXN13

EXP_TXN12

EXP_TXN11

EXP_TXN10

EXP_TXN9

EXP_TXN8

EXP_TXN7

EXP_TXN6

EXP_TXN5

EXP_TXN4

EXP_TXN3

EXP_TXN2

EXP_TXN1

EXP_TXN0

EXP_RXP15

EXP_RXP14

EXP_RXP13

EXP_RXP12

EXP_RXP11

EXP_RXP10

EXP_RXP9

EXP_RXP8

EXP_RXP7

EXP_RXP6

PCI-EXPRESS GRAPHICS

EXP_RXP5

EXP_RXP4

EXP_RXP3

EXP_RXP2

EXP_RXP1

EXP_RXP0

EXP_RXN15

EXP_RXN14

EXP_RXN13

EXP_RXN12

EXP_RXN11

EXP_RXN10CFG5

EXP_RXN9

EXP_RXN8

EXP_RXN7

EXP_RXN6

EXP_RXN5

EXP_RXN4

MISCTVVGALVDS

EXP_RXN3

EXP_RXN2

EXP_RXN1

EXP_RXN0

EXP_ICOMPO

EXP_COMPI

GCLKN

SDVOCTRL_CLK

SDVOCTRL_DATA

GCLKP

H25

H24

AB29

AC29

20-C1

20-C1

AA31

Y31

DMI0RXP

DMI0RXN

20-C1

20-C1

AA33

Y33

DMI0TXP

DMI0TXN

TVDAC_A

TVDAC_B

A15

A17

C16

20-C1

AB35

AA35

DMI1RXP

DMI1RXN

20-C1

20-C1

AB37

DMI1TXN

20-C1

AA37

DMI1TXP

20-C1

20-C1

AB31

AC31

DMI2RXP

DMI2RXN

20-C1

20-C1

AC33

AB33

DMI2TXP

DMI2TXN

AD35

DMI3RXN

DMIDDR MUXING

TV_IRTNC

TV_REFSET

TVDAC_C

TV_IRTNA

J18

B16

B15

TV_IRTNB

B17

DDCCLK

E24

E23

DDCDATA

CLK1_MCLK1

DMI1_TXP3

20-B1

20-B1

AC35

AD37

DMI3RXP

BLUE

E21

D21

CLK1_MCLK3

DMI1_RXN3

DMI1_RXP3

CLK1_MCLK0

20-C1

20-C1

17-C4

17-C4

AC37

AM33

AL1

AE11

AJ34

SM_CK0

SM_CK1

SM_CK2

SM_CK3

DMI3TXP

DMI3TXN

ALVISO500-2

ALVISO-GMCH

VSYNC

RED

RED*

GREEN

GREEN*

HSYNC

BLUE*

A19

B19

B20

H21

C20

G21

CLK1_MCLK4

CLK1_MCLK0*

17-C2

17-C4

17-C2

AN33

AK1

AF6

AC10

SM_CK4

SM_CK5

SM_CK0*

2 / 5

REFSET

J20

CLK1_MCLK1*

CLK1_MCLK3*

CLK1_MCLK4*

17-C2

17-C4

17-C2

AE10

AJ33

AF5

AD10

SM_CK1*

SM_CK2*

SM_CK3*

SM_CK4*

SM_CK5*

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

F25

E25

C23

C22

MEM1_CKE0

MEM1_CKE1

MEM1_CKE2

MEM1_CKE3

17-C218-C4

18-C4 17-C246-B224-A413-A4

18-C4 17-C4

18-C4 17-C4

AP21

AM21

AH21

AK21

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

LDDC_CLK

LDDC_DATA

LIBG

LVDD_EN

F23

F22

F26

C33

MEM1_CS0*

18-D4 17-C4

AN16

AM14

SM_CS0*

SM_CS1*

LVBG

LVREFH

LVREFL

F28

F27

C31

1.5K

R42

MEM1_CS1*

MEM1_CS2*

MEM1_CS3*

17-C218-D4

17-C218-C4

18-D4 17-C4

40.2 1%

R72

AH15

AG16

AF22

SM_CS2*

SM_CS3*

SM_OCDCOMP0

LACLKN

LACLKP

LBCLKN

B30

B29

C25

1%

MEM1_ODT0

MEM1_ODT1

MEM1_ODT2

17-B4

17-B418-C4

18-C4

1%40.2

R103

AF16

AP14

AL15

AM11

SM_ODT0

SM_ODT1

SM_ODT2

SM_OCDCOMP1

LADATAN0

LADATAN1

LADATAN2

LBCLKP

B34

B33

B32

C24

MEM1_ODT3

18-C4 17-B2

18-C4 17-B2

1%

1%

80.6

80.6

R105

R104

AN10

AK10

AK11

AF37

SM_ODT3

SMRCOMPP

SMRCOMPN

LADATAP0

LADATAP1

A34

A33

B31

MEM1_VREF

AD1

SMVREF0

LADATAP2

AE27

AE28

AF9

SMVREF1

SMXSLEWIN

SMXSLEWOUT

CFG/RSVD PM CLK NC

LBDATAN0

C29

D28

’ ’: Current Settings

Default Operations

(Def.):

AF10

SMYSLEWIN

SMYSLEWOUT

LBDATAN2

LBDATAP0

LBDATAN1

C27

C28

Low

DMIx2

CFG#

CFG(5)

NC11

NC10

NC9

NC8

NC7

NC6

NC5

NC4

NC3

NC2

NC1

DREF_SSCLKP

DREF_SSCLKN

DREF_CLKP

DREF_CLKN

RSTIN*

PWROK

THRMTRIP*

EXT_TS1*

EXT_TS0*

BM_BUSY*

RSVD27

RSVD26

RSVD25

RSVD24

RSVD23

RSVD22

RSVD21

CFG20

CFG19

CFG18

CFG17

CFG16

CFG15

CFG14

CFG13

CFG12

CFG11

CFG10

CFG9

CFG8

CFG7

CFG6

CFG4

CFG3

CFG2

CFG1

CFG0

LBDATAP1

LBDATAP2

D27

C26

DDR-2

DT/Transportable

Test Mode

PEG Reversal

CFG(9)

CFG(7)

CFG(6)

CFG(13:12)

CLK1_DREFSSCLK

A37

A36

B37

A2

B1

AN1

AP1

AP2

AP36

AN37

AP37

D37

C37

A23

A24

AE29

AD30

2

F5

H22

J21

J23

D25

D26

A30

A31

J17

G24

G25

D23

G23

G22

H14

J15

H15

C14

H12

E14

D14

E15

D15

J16

P2.5V

D17

E16

G15

F15

F16

G14

H13

G16

13-A3

46-B3

VCCP 1.05V (Def.)

No (Def.)

Disabled

VCC 1.05V (Def.)

FSB Dynamic ODT

SDVOCRTL_DATA

CFG(18)

CFG(19)

CFG(16)

CLK1_DREFCLK*

CLK1_DREFCLK

CLK1_DREFSSCLK*

16-B1

16-B1

7-B1

PLT3_RSTF*

7-B1

20-A225-C434-C2

46-A4 36-C2 35-C2

35-B4

20-A3

1%

100

CPU1_THRMTRIP*

KBC3_IMVP4_PWRGD

46-C2 36-B2 20-B2

46-D2 9-C319-C2 11-B419-C1

R73

1K

1K

NO_STUFF

NO_STUFF

R68

R67

R100

1%

1K

1K

1%

R101

NO_STUFF

VTT

9-C37-C4 46-C39-C2

9-C2 9-C3 46-C37-C4

AQUILA-SONOMA

TITLE

6/25/2005

DEV. STEP

DATE

MCH2_BMBUSY*

ZHOU & GUO

20-C246-B2

CHECK

DRAW

P2.5V

10K

R102

13-A346-B3

OF

BA41-00529A

ELECTRONICS

13 46

PART NO.

PAGE

MAIN

ALVISO (2/5)

June 25, 2005 12:21:39 PM

1.0

MP

LAST EDIT

REV

ANTONIO

KEVIN LEE

MODULE CODE

APPROVAL

R71

R69

10K

10K

1

2

3

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

46-D437-C2

7-C1

46-A4

7-C1

VGA3_Y

VGA3_C

VGA3_COMP

CLK1_MCH3GPLL

CLK1_MCH3GPLL*

37-C1 46-D4

R97

R99

4.99K

75

1%

1%

46-B2

46-A423-C4

23-A4 46-C2

23-C4 46-A4

23-A4

VGA3_BLUE

VGA3_GREEN

VGA2_DDCCLK

VGA2_DDCDATA

46-B423-C4

46-A423-B4

23-B4 46-A4

VGA3_RED

VGA3_VSYNC

1%

255

1%

150

150 1%

150

1%

VGA3_HSYNC

R70

R98

R63

R64

24-C4

24-C4

13-A4 24-C2 46-B3

24-A2 46-A3

LCD2_VDDEN

LVDS1_ACLK-

LVDS1_ACLK+

LCD2_BKLTON

LCD2_BKLTCRL

24-C4

24-C4

24-C4

LVDS1_A0-

LVDS1_A1-

LVDS1_A2-

24-C4

24-C4

24-C4

LVDS1_A0+

LVDS1_A1+

LVDS1_A2+

CLK1_BSEL1

CLK1_BSEL2

MCH1_BSEL0

R66

100K

46-B324-C213-B4

R65

100K

13-B4 24-A4 46-B2

LCD2_VDDEN

LCD2_BKLTCRL

MCH1_BSEL0

4

D

www.kythuatvitinh.com

C

B

A

4614

OF

SAMSUNG X06 9-14

BA41-00529A

ELECTRONICS

SAMSUNG

Ch. B (So-DIMM B)

N/A

SB_CK(2:0)

SB_CK(2:0)*

N/A

N/A

N/A

N/A

SB_CKE(3:2)

SB_ODT(3:2)

SB_CS(3:2)*

PART NO.

PAGE

1

NCNCNC

DDR-I

N/A

SA_CS(1:0)*

SA_CK(2:0)

SA_CK(2:0)*

N/A

Ch. A (So-DIMM A)

N/A

N/A

SA_ODT(1:0)

SA_CKE(1:0)

N/A

EXP_TXP_1

EXP_TXN_1

PEG (SAGP) Mode

EXP_TXN_0

EXP_TXP_0

EXP_TXP_3

EXP_TXN_3

EXP_TXP_2

EXP_TXN_2

EXP_TXN_4

EXP_TXP_4

EXP_TXN_5

EXP_TXP_5

EXP_TXN_6

EXP_TXP_6

EXP_TXN_7

EXP_TXP_7

EXP_RXN_1

EXP_RXN_0

EXP_RXP_0

EXP_RXP_12EXP_RXP_2

EXP_RXN_5

EXP_RXP_5

EXP_RXN_2

MAIN

AQUILA-SONOMA

SDVOB_ALPHA

SDVOB_ALPHA*

SDVOC_RED*

SDVOB_CLK*

SDVOB_CLK

1253

5

4

AH18

AJ18

AK18

AJ19

AK17

SB_MA3

SB_MA4

SB_MA1

SB_MA2

SA_MA1

SA_MA2

SA_MA3

SA_MA4

AP17

AP18

AN18

AM17

AM18

4

3

5

1

SDVOC_RED

7

6886010

AK19

AH19

SB_MA5

SB_MA6

SB_MA7

SA_MA5

SA_MA6

SA_MA7

AL19

AP20

6

7

SDVOB_BLUE*

SDVOB_GREEN*

SDVOB_GREEN

SDVO_RED

4

5

6

AL10

AH7

AF7

SB_DQS3*

SB_DQS4*

SB_DQS5*

SB_DQS6*

SA_DQS3*

SA_DQS4*

SA_DQS5*

SA_DQS6*

AN8

AH1

AM5

4

660

5

SDVOB_BLUE

MEM1_BMA(13:0)

17-D218-C3

0

AB5

AH17

SB_MA0

SB_DQS7*

SA_DQS7*

SA_MA0

AE4

AL17

7

SDVO Mode

SM_CK(5:3)

SM_CS(1:0)*

SM_CS(3:2)*

SA_DQS(7:0)*

SB_DQS(7:0)*

SM_ODT(3:0)

DDR-II ONLY

AD5

63

AD4

62

AF1

61

AF2

60

AC4

59

AD6

AE3

57

AF3

56

AG3

5519

AH3

54

AM2

AL3

AG1

5149

AG2

AK3

AK2

48

AM3

47

AL4

46

AM6

AP6

44

AP3

43

AN3

42

AN6

41

AN5

40

AM7

39

AL7

38

AP10

AP11

36

AP7

35 5037

AL6

34

AL9

33 45

AM9

32

AP22

AN22

30

AM24

29

AL23

28

3

AM22

27

AM23

267

AM27

AP27

24

AL28

23 52

AM28

22

AM30

21

AL30

201

AP28

AN28

AP31

1718

AN31

AM32

15

AL32

14916

AM35

AM34

12

AM31

AP32

10

AN35

AM36

8

AL34

AK37

AJ35

5

AH36

AL37

3

AL35

2

AH35

AG35

0

SADQ9

SADQ8

SADQ7

SADQ6

SADQ5

SADQ4

SADQ3

SADQ2

SADQ1

SADQ0

Dual Channel

MEM1_BBS0*

MEM1_BBS1*

MEM1_BBS2*

MEM1_BDM(7:0)

17-B2

17-C218-C4

17-C2

17-C2

18-C4

18-C4

2

0

1

AJ15

AG17

AG21

AF32

AK34

AK27

SADQ63

SADQ62

SB_DM0

SB_BS0*

SB_BS1*

SB_BS2*

SB_DM1

SADQ61

SADQ60

SADQ59

SADQ58

SADQ57

SADQ56

SADQ55

SADQ54

SADQ53

SADQ52

SADQ51

SADQ50

SADQ49

SADQ48

SADQ47

SADQ46

SADQ45

SADQ44

SADQ43

SADQ42

SADQ41

SADQ40

SADQ39

SADQ38

SADQ37

SADQ36

SADQ35

SADQ34

SADQ33

SADQ32

SADQ31

SADQ30

SADQ29

SADQ28

SADQ27

SADQ26

SADQ25

SADQ24

SADQ23

SADQ22

SADQ21

SADQ20

SADQ19

SADQ18

SADQ17

SADQ16

SADQ15

SADQ14

SADQ13

SADQ12

SADQ11

SADQ10

DDR SYSTEM MEMORY A

SA_BS1*

SA_BS2*

SA_DM0

SA_DM1

SA_BS0*

AJ37

AL21

AK16

AL29

AP35

2

0

1

AK15

SM_CK(2:0)

SM_CK(2:0)*

SM_CK(5:3)*

4

5

3

6

AK24

AJ10

AK5

AE7

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SA_DM2

SA_DM3

SA_DM4

SA_DM5

AJ2

AP9

AP4

AP24

6

325

4

7141

AB7

SB_DM6

SA_DM6

AD3

7

SM_ODT(3:2)

SM_SKE(3:2)

SM_ODT(1:0)

SM_CKE(1:0)

MEM1_BDQS(7:0)

17-B2

072

4

3115137

AK23

AM10

AF34

AK32

AJ28

SB_DM7

SB_DQS4

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

ALVISO500-3

SA_DQS3

SA_DQS4

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

AM8

AP23

AK36

AP33

AN29

3

1

4

0472

6530

AH6

AF8

SB_DQS5

SA_DQS5

AJ1

AM4

5

6

SDVOB_RED*

MEM1_BDQS*(7:0)

17-B2

1

3

2

AJ23

AB4

AF35

AK33

AK28

SB_DQS6

SB_DQS7

SB_DQS0*

SB_DQS1*

SB_DQS2*

3 / 5

ALVISO-GMCH

SA_DQS2*

SA_DQS6

SA_DQS7

SA_DQS0*

SA_DQS1*

AE5

AK35

AP34

AN30

AN23

2

0

3

721

SDVOC_GREEN*

SDVOC_BLUE*

SDVOC_BLUE

SDVOC_GREEN

9

11

12

13

AJ20

AH20

AJ16

AG18

AG20

AG15

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SA_MA10

SA_MA11

SA_MA12

SA_MA8

SA_MA9

AL20

AN20

AM16

AM20

AM15

AM19

9

11413

8

10

12

SDVOC_CLK*

SDVOC_CLK

SDVO_TVCLKIN*

SDVO_TVCLKIN

MEM1_BRAS*

MEM1_BCAS*

17-C218-C4

17-C218-B43117-C218-B4

TP2662

AK14

AF15

AH14

SB_RAS*

SB_CAS*

SB_MA13

SB_RCVENIN*

SA_CAS*

SA_MA13

SA_RAS*

SA_RCVENIN*

AF29

AP16

AN15

SDVOC_INTB

SDVO_STALL

SDVO_STALLB

SDVOC_INT

SDVOB_INT

SDVOB_INT*

MEM1_BWE*

TP2663

AF14

AH16

SBDQ63

AA5

SBDQ62

SBDQ61

SBDQ60

SBDQ59

SBDQ58

SBDQ57

SBDQ56

SBDQ55

SBDQ54

SBDQ53

SBDQ52

SBDQ51

SBDQ50

SBDQ49

SBDQ48

SBDQ47

SBDQ46

SBDQ45

SBDQ44

SBDQ43

SBDQ42

SBDQ41

SBDQ40

SBDQ39

SBDQ38

SBDQ37

SBDQ36

SBDQ35

SBDQ34

SBDQ33

SBDQ32

SBDQ31

SBDQ30

SBDQ29

SBDQ28

SBDQ27

SBDQ26

SBDQ25

SBDQ24

SBDQ23

SBDQ22

SBDQ21

SBDQ20

SBDQ19

SBDQ18

SBDQ17

SBDQ16

SBDQ15

SBDQ14

SBDQ13

SBDQ12

SBDQ11

SBDQ10

SBDQ9

SBDQ8

SBDQ7

SBDQ6

SBDQ5

SBDQ4

SBDQ3

SBDQ2

SBDQ1

SBDQ0

AJ5

AJ8

AJ4

AJ7

AJ9

AA4

AC7

AC8

AA8

AB6

AB8

AC5

AD7

AE8

AG6

AH4

AD9

AD8

AG4

AG5

AK4

AK8

AH5

AK6

AK9

AH8

AG8

AG9

AJ21

AJ22

AJ30

AJ31

AH10

AH11

AG10

AG22

AH23

AH24

AK22

AG23

AF24

AG28

AH27

AH30

AK29

AH28

AH29

AK30

AH31

AG33

AG34

AG30

AK31

AH32

AH33

AF30

AF31

AE33

AE34

AG36

AG32

AE32

AE31

SB_WE*

SB_RCVENOUT*

DDR SYSTEM MEMORY B

SA_RCVENOUT*

SA_WE*

AF28

AP15

TITLE

MP

6/25/2005

DATE

DEV. STEP

MEM1_BDQ(63:0)

ANTONIO

17-D2

63

62

61

58

56

55

54

53

52

51

50

48

46

45 57

44

43

42

41

40

39

38

3713 25

36

34

325 5935

31

3018

2919

28

27

26

24

23

22

21

17

16

15 49

12

111

10

9

7

6

4

3 33

2

020

ZHOU & GUO

DRAW

CHECK

ALVISO (3/5)

June 25, 2005 12:21:39 PM

1.0

LAST EDIT

REV

KEVIN LEE

APPROVAL

MODULE CODE

1

24

3

4

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

SAMSUNG ELECTRONICS CO’S PROPERTY.

THIS DOCUMENT CONTAINS CONFIDENTIAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

D

17-D4

MEM1_ADQ(63:0)

18-C417-C4

18-C417-C4

17-C4 18-C4

17-B4

MEM1_ABS0*

MEM1_ABS1*

MEM1_ABS2*

MEM1_ADM(7:0)

17-B4

MEM1_ADQS(7:0)

C

17-B4

MEM1_ADQS*(7:0)

18-D317-D4

MEM1_AMA(13:0)

TP2660

TP2661