Samsung NP_R530, NP_R730 Schematics

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

D

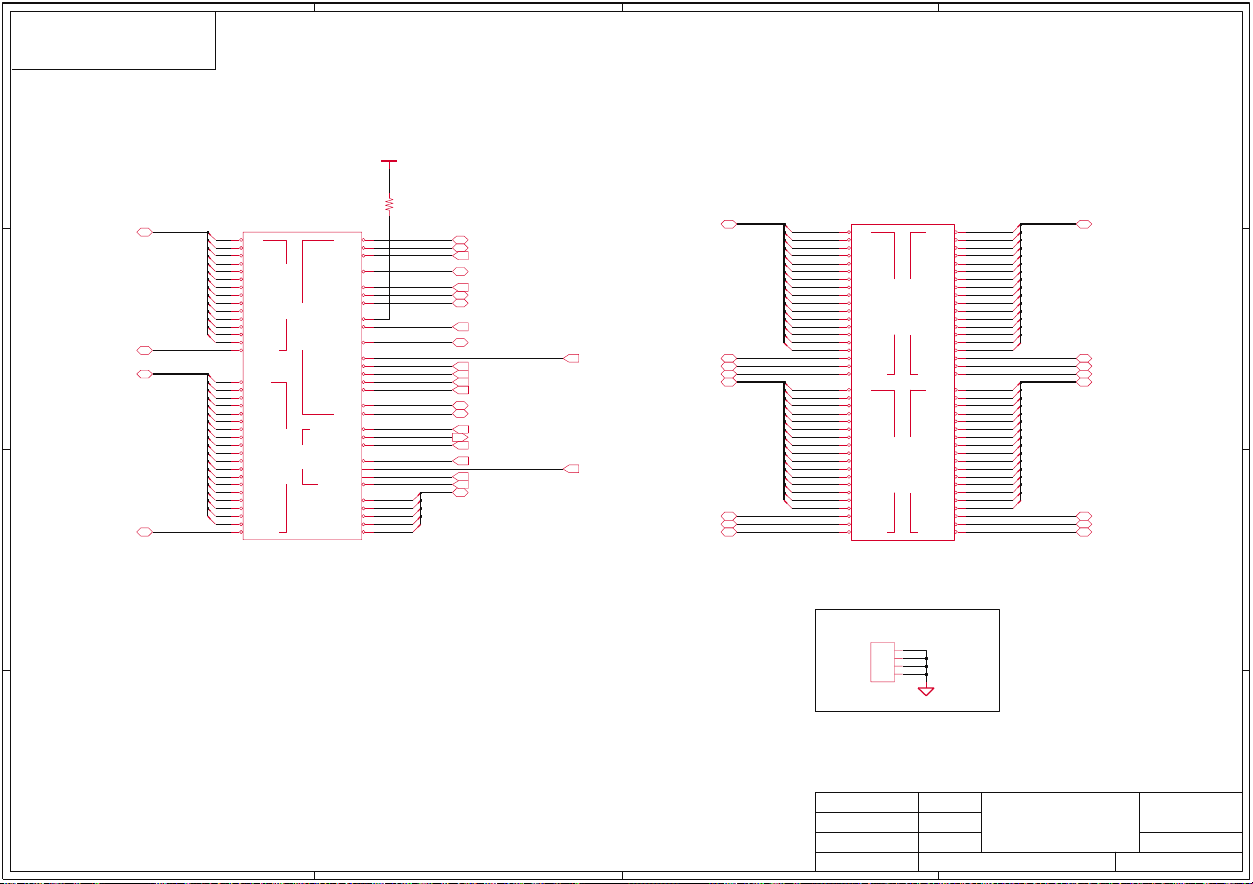

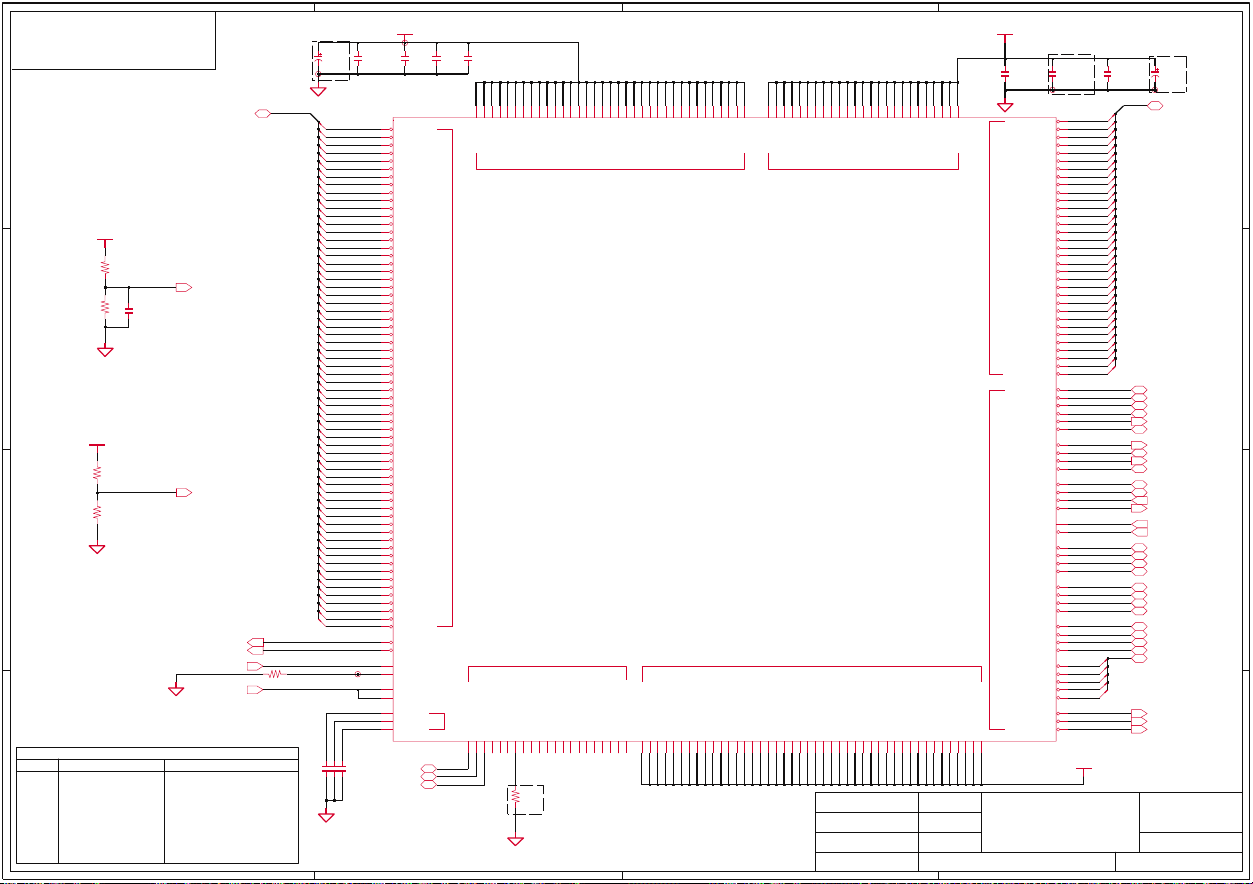

Bremen-UL

CPU :

Chip Set :

C

Remarks :

Model Name : Bremen-UL

PBA Name :

PCB Code :

B

Dev. Step : PV

Revision :

T.R. Date :

Design

Intel Penryn

Intel Cantiga & ICH9M

Montevina Platform

MAIN

GCE : BA41-01177A

NAN : BA41-01178A

HAN : BA41-01179A

1.0

2009.10.19

CHECK

APPROVAL

C

B

ELECTRONICS

BA41-xxxxxA

501

OF

A

A

CHECK

APPROVAL

MODULE CODE

2

4

Owner :

SEC Mobile R & D

Signature :

X

3

TW.Kim

HJ.Kim

SJ.Park

DATEDRAW

DEV. STEP

REV

LAST EDIT

10/10/2008

ADV2nd

TITLE

1.0

Bremen-UL

MAIN

COVER

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

PAGE

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

D

C

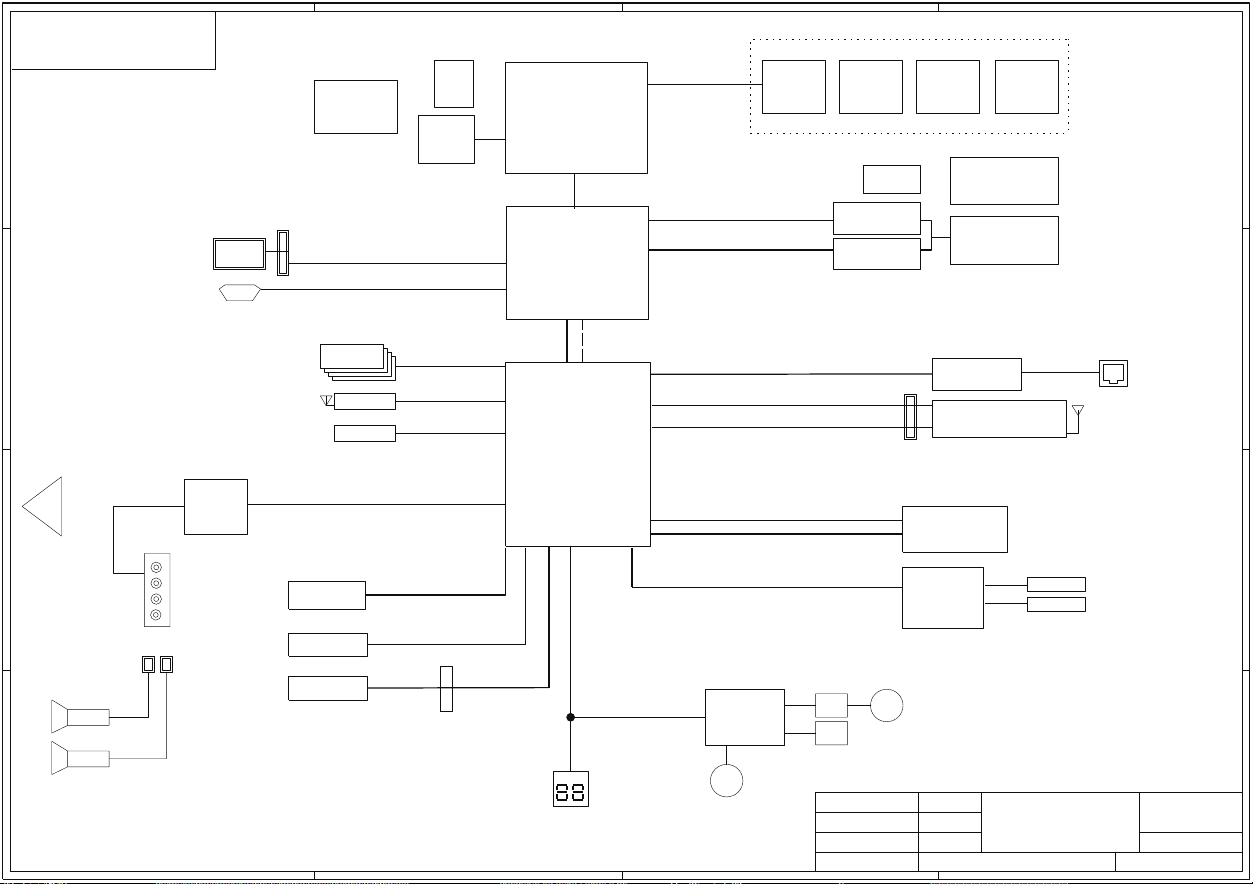

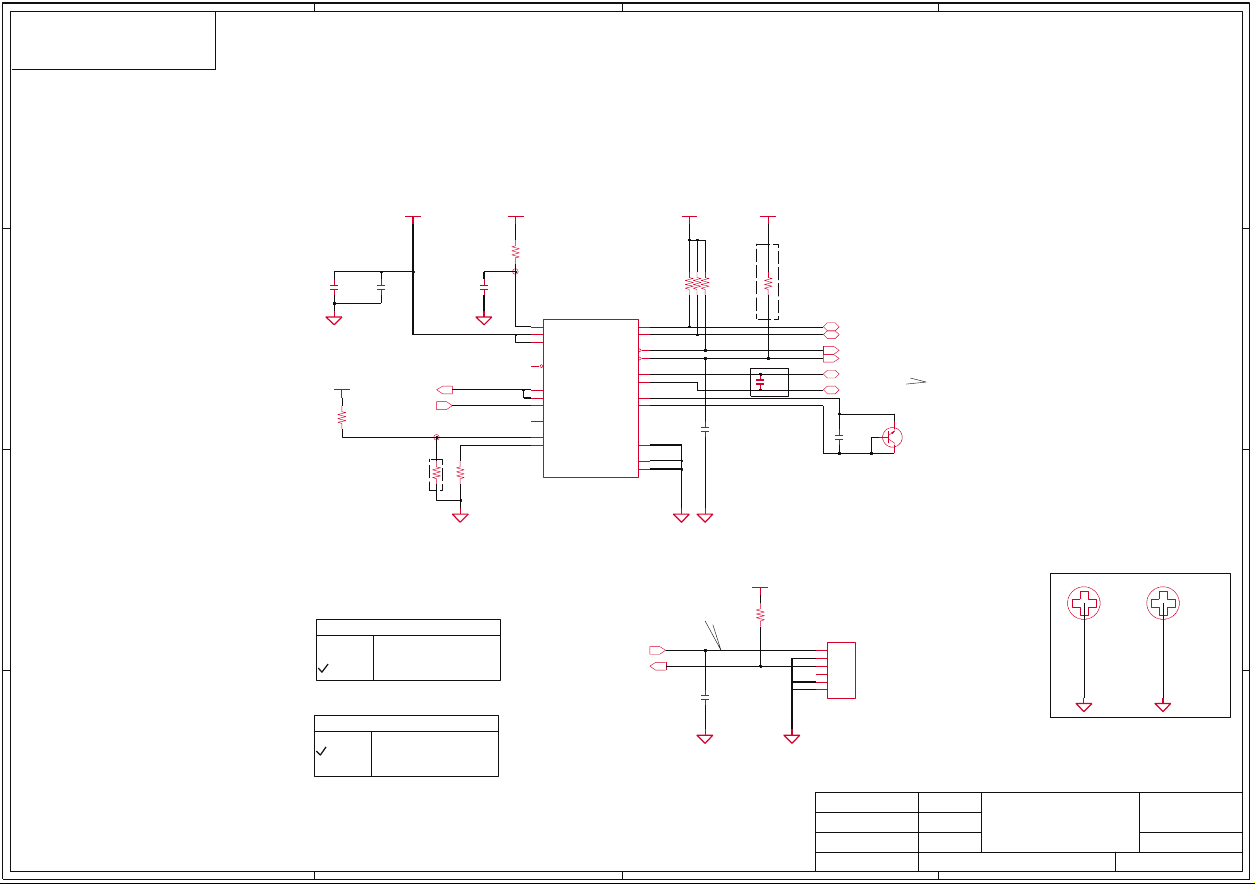

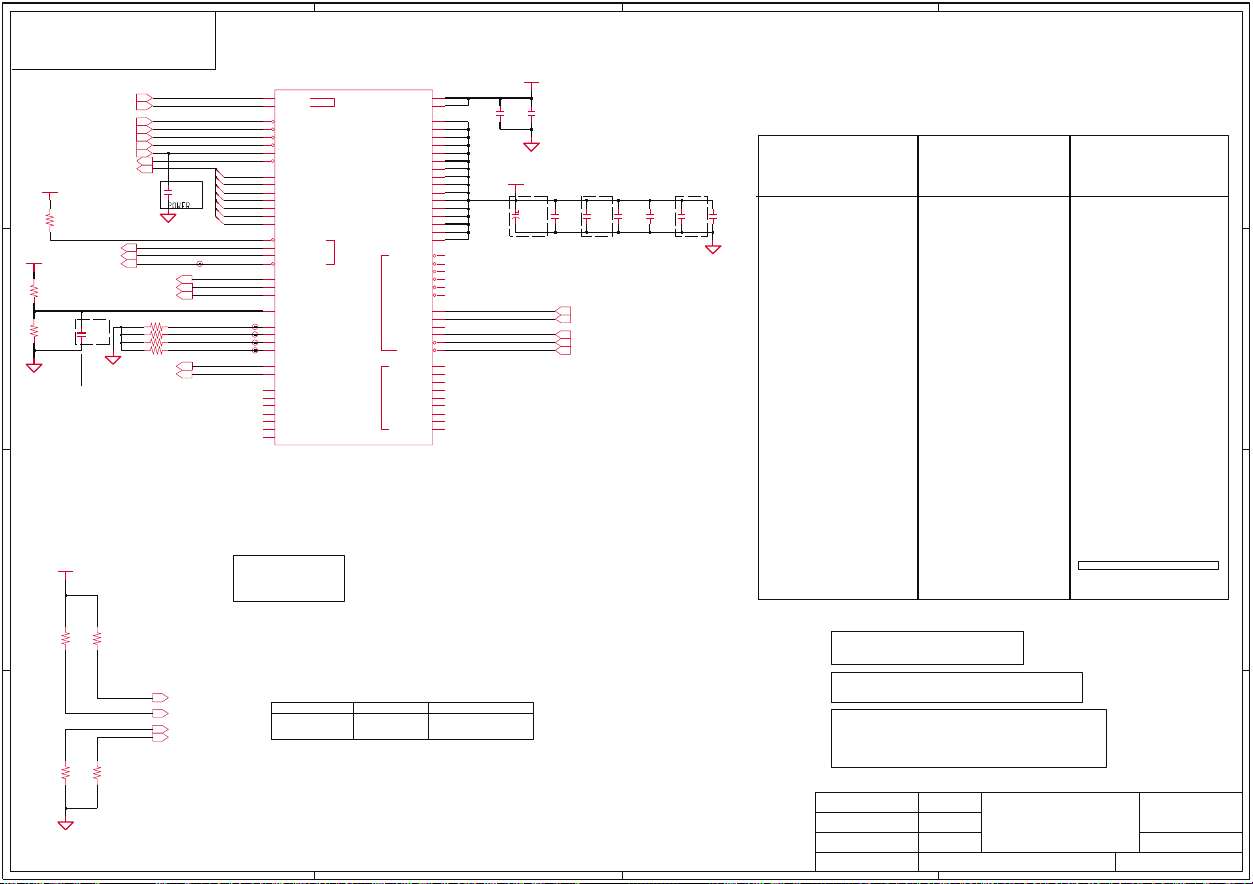

High Definition Audio

SPKR R

SPKR L

PG 31

HP

MIC-IN

PG 33

2P

2P

4

Aud.

AMP

B

A

PG 26

PG 27

PG 31

Audio

ALC269

PG 30

LCD

CRT

PG 25

PG 38

PG 53

PG 42, 52

PG 43

PG 43

SATA

SATA

Clocking

USB 0,2,6

ANT

SPI ROM

HDD

Sub board

CK-505

PG 12

Bluetooth

Camera

ODD

LCD

CRT

OPTION

SPI

SATA 0

SATA 1

FAN

PG 8

CPU

Thermistor

EMC2112

PG 8

HD Audio

12P

PG 38

3

Mobile Processor

PG 9-11

Direct Media Interface

USB 0,2,6

USB 5

USB 8

3

Penryn-6M

FSB 1067

478pin

L2 Cache : 6/3MB

FSB

800/1067 MT/S

GMCH-M

Cantiga-GM

GL40

1329 FCBGA

PG 13-17

CLINK

x4, 1.5V

ICH9-M

676 BGA

PG 20 - 24

LPC

3.3V LPC, 33MHz

80 Port

PG 25

Channel A (Standard)

Dual channel

Channel B (Reverse)

Lane 4

PCIE x1

Lane 1

PCIE x1

USB 1

Lane 3

PCIE x1

USB 7

USB 4

MICOM

MEC1308

TMKBC (TBD)

LED

PG 41

2

CPU

DC/DC

IMVP-6

DDR II 667/800

DDR II 667/800

PG 39

2

PG 40

Touch

PAD

KBD

PG 40

DRAW

CHECK

APPROVAL

Charging

Circuit

ON BOARD

Termination

PG 18,19

DDR II

SODIMM 0

DDR II

SODIMM 1

52P

PG 37

Touchpad

LED

PG 40

undefined

Smart

Battery

Module

PG 18

PG 19

Express Card

GENESIS

DATE

TW.Kim

DEV. STEP

HJ.Kim

REV

SJ.Park

LAST EDITMODULE CODE

RTL103EL

PG 34

Mini Card 1

(WLAN)

PG 35

2 IN 1

PG 36

9/23/2008

ADV2nd

DC/DC

VCCP / DC-DC

PG 48

DDR II Power

PG 47

TITLE

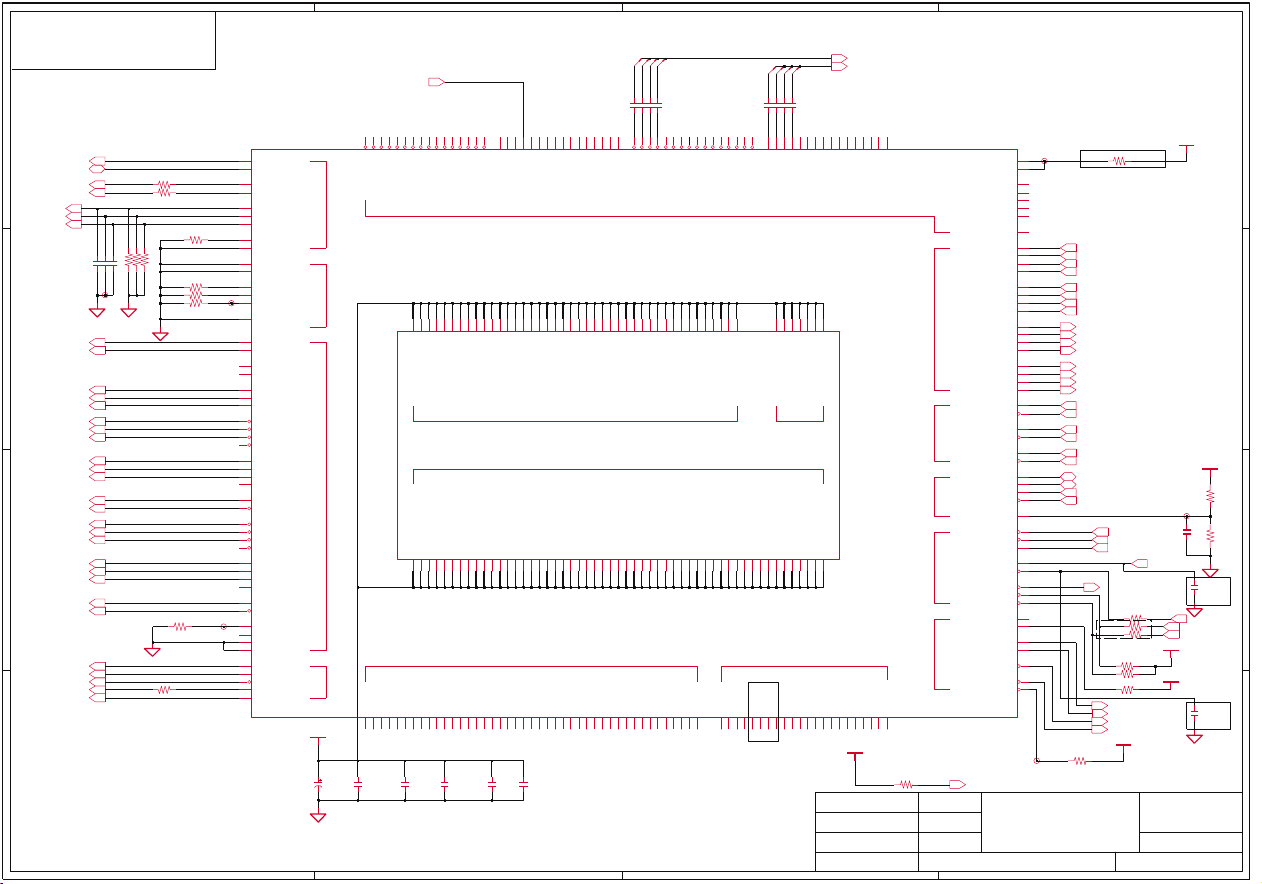

BLOCK DIAGRAM

1.0

October 05, 2009 20:00:56 PM

SD

MMC

Bremen-UL

MAIN

ANT

1

PG 36

PG 36

1

RJ45

PG 34

PAGE

SAMSUNG

ELECTRONICS

PART NO.

BA41-xxxxxA

250

OF

D

C

B

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

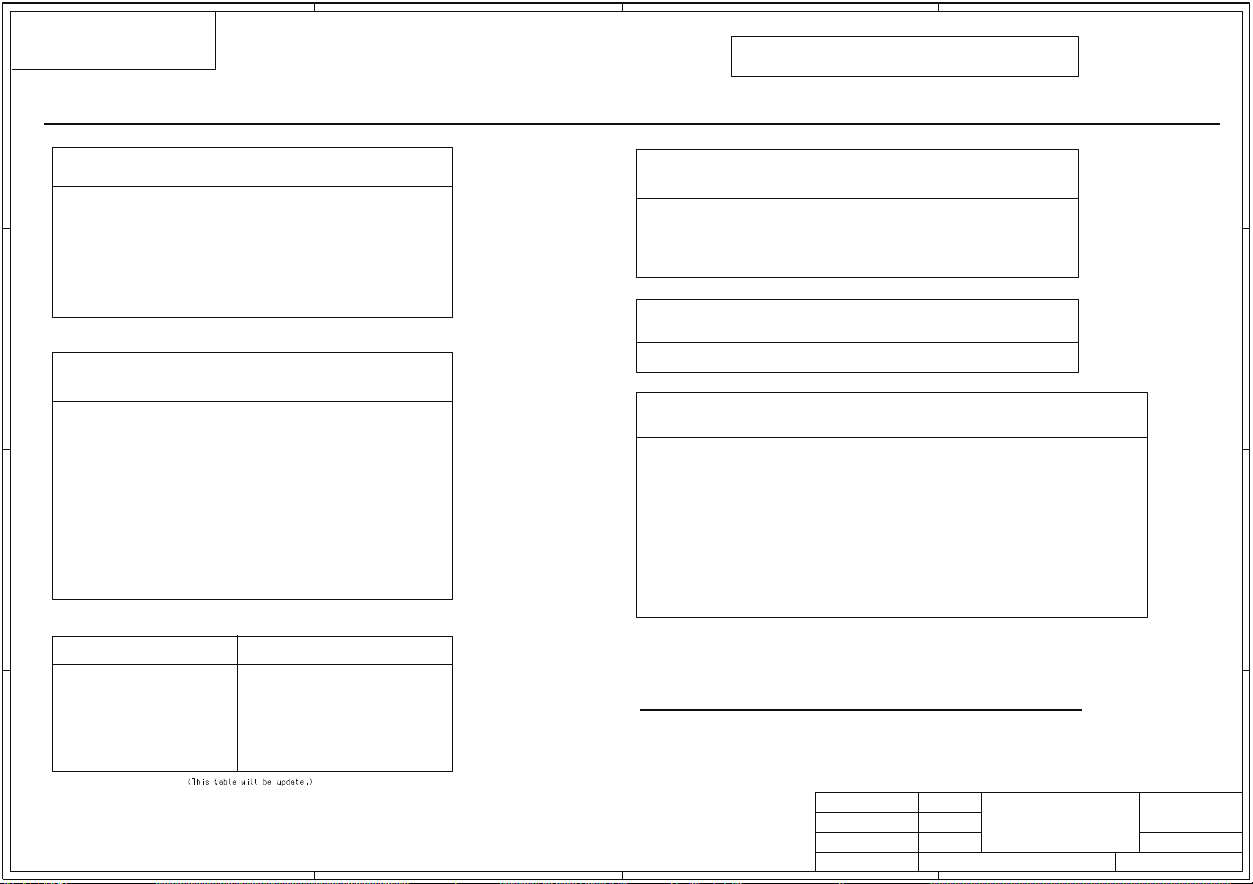

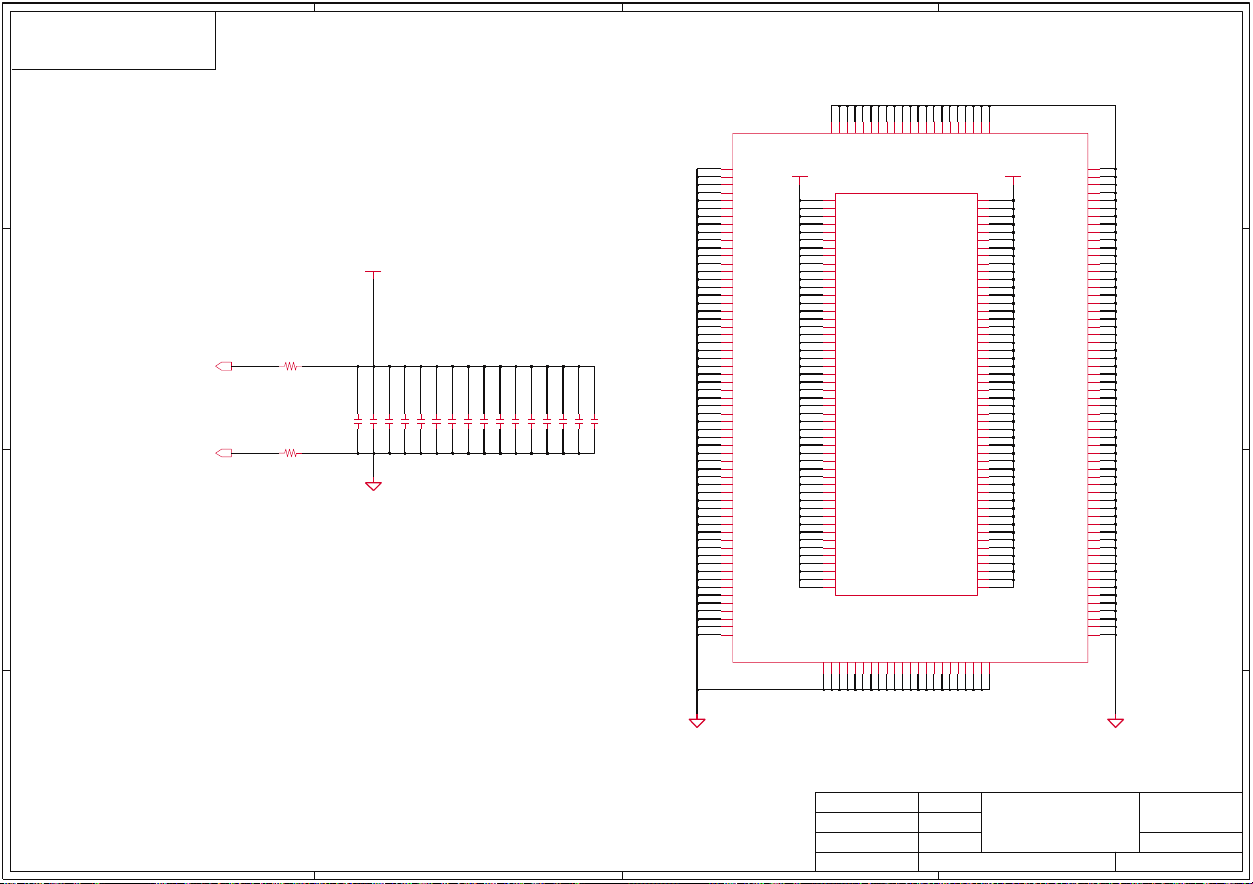

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

D

4

2

BOARD INFORMATION

1

D

C

B

A

PCI Devices

Devices

Cardbus

USB

Hub to PCI

LPC bridge/IDE/AC97/SMBUS

Internal MAC

AC Link

GLAN

Voltage Rails

VDC

VCC_CORE

P1.05V (VCCP)

P3.3V_MICOM

P1.5V

P1.8V

P1.8V_AUX

P0.9V

P3.3V

P3.3V_AUX

P5.0V

P5.0V_AUX

P5.0V_ALW

Primary DC system power supply (9 to 20V)

Core Voltage for CPU

VTT for CPU, Crestline & ICH9-M

3.3V always power rail (for Micom)

1.5V switched power rail (off in S3-S5)

1.8V switched power rail (off in S3-S5)

1.8V power rail for DDR (off in S4-S5)

0.9V power rail for DDR (off in S3-S5)

3.3V switched power rail (off in S3-S5)

3.3V switched on power rail (off in S4-S5)

5.0V switched power rail (off in S3-S5)

5.0V switched on power rail (off in S4-S5)

5.0V always power rail

USB PORT Assign

ASSIGNED TO

PORT #

0

SYSTEM PORT 0

SYSTEM PORT 1

1

SYSTEM PORT 2

2

NC

3

NC

4

5

Bluetooth

Mini PCI Express 2

6

7

Camera

8

NC

NC

4

IDSEL#

AD25

AD29(internal)

AD30(internal)

AD31(internal)

AD24(internal)

-

-

REQ/GNT#9Interrupts

3

-

-

-

-

-

-

A,B,C

USB2.0 #0 (USB0) : A

USB2.0 #1 (USB1) : D

USB2.0 #2 (USB4) : C

USB2.0 #3 (USB5) : E

USB2.0 #4 (EHCI) : H

B

E

B

F

PCI Express Assign

PORT #

ASSIGNED TO

NC

0

1

Mini Card 1 (WLAN)

NC

2

3

LOM

4

Mini Card 2 (ROBSON or DVB-T)

NC

5

Crystal / Oscillator

TYPE

Crystal

Crystal

Crystal

Crystal

FREQUENCY

32.768KHz

10MHz

14.318MHz

25MHz

LCD Pannel Detect

Devices

2

I C / SMB Address

Devices

ICH9-M

CPU Thermal Sensor

SODIMM0

SODIMM1

Thermal Sensor on SODIMM030011 000x

Thermal Sensor on SODIMM1

CK-505M (Clock Generator)

Resolution

Address

Master

0111 101x

1010 000x

1010 010x

0011 010x

1101 001x

(TBD)

DEVICE

M-9

HCI

MICOM

CLOCK-Generator

LAN

Hex

7Ah

A0h

A4h

30h

34h

D2h

USAGE

col

emiT lae

k

R

C

HD64F2169/2160

CK-505

RealTek 88E8057

PANNEL_DETECT_0

Bus

SMBUS Master

Thermal Sensor

-

-

-

Clock, Unused Clock Output Disable

C

B

REVISION HISTORY

See rev notes for more information.

DRAW

CHECK

APPROVAL

MODULE CODE

3

2

TW.Kim

HJ.Kim

SJ.Park

undefined

DATE

DEV. STEP

REV

LAST EDIT

9/23/2008

ADV2nd

TITLE

1.0

Bremen-UL

MAIN

BOARD INFO

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

350

PAGE

A

ELECTRONICS

BA41-xxxxxA

OF

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

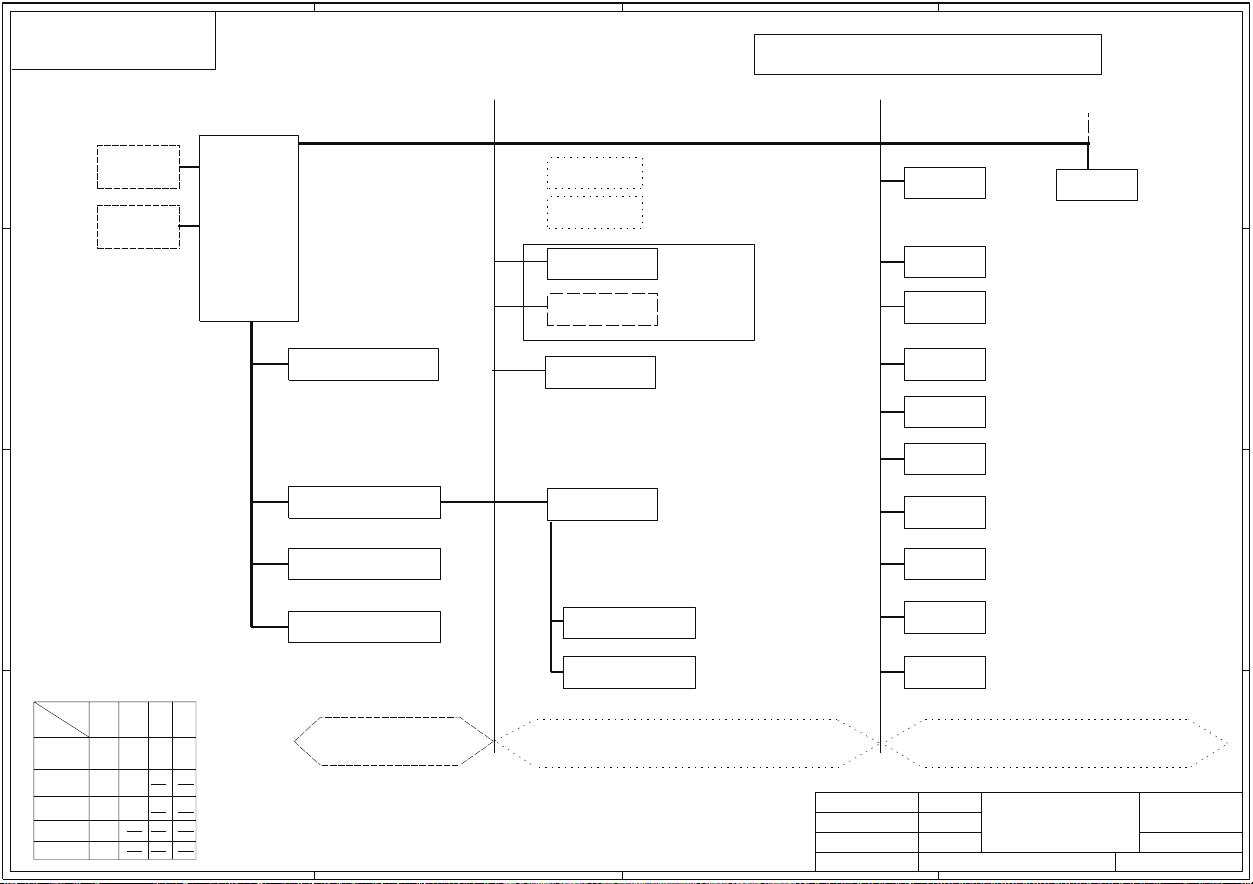

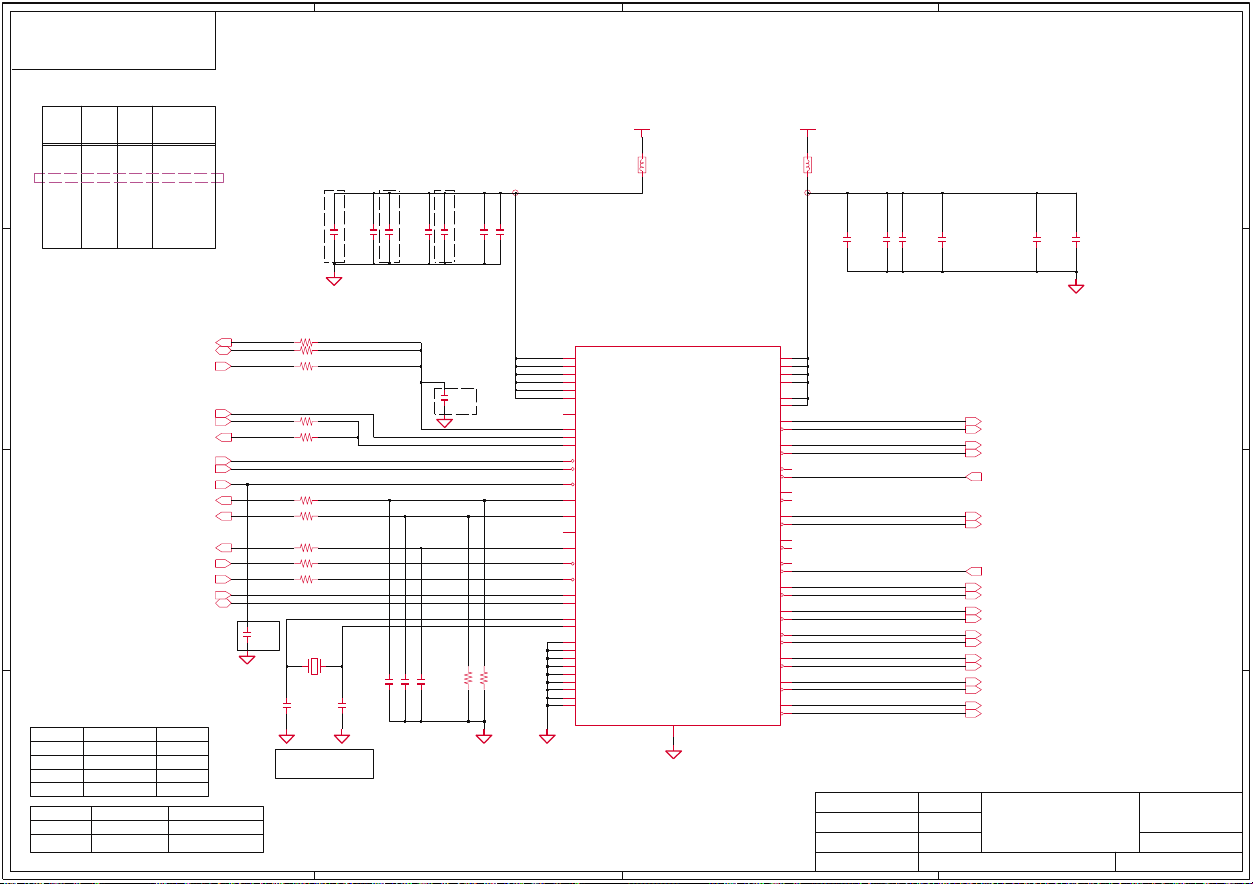

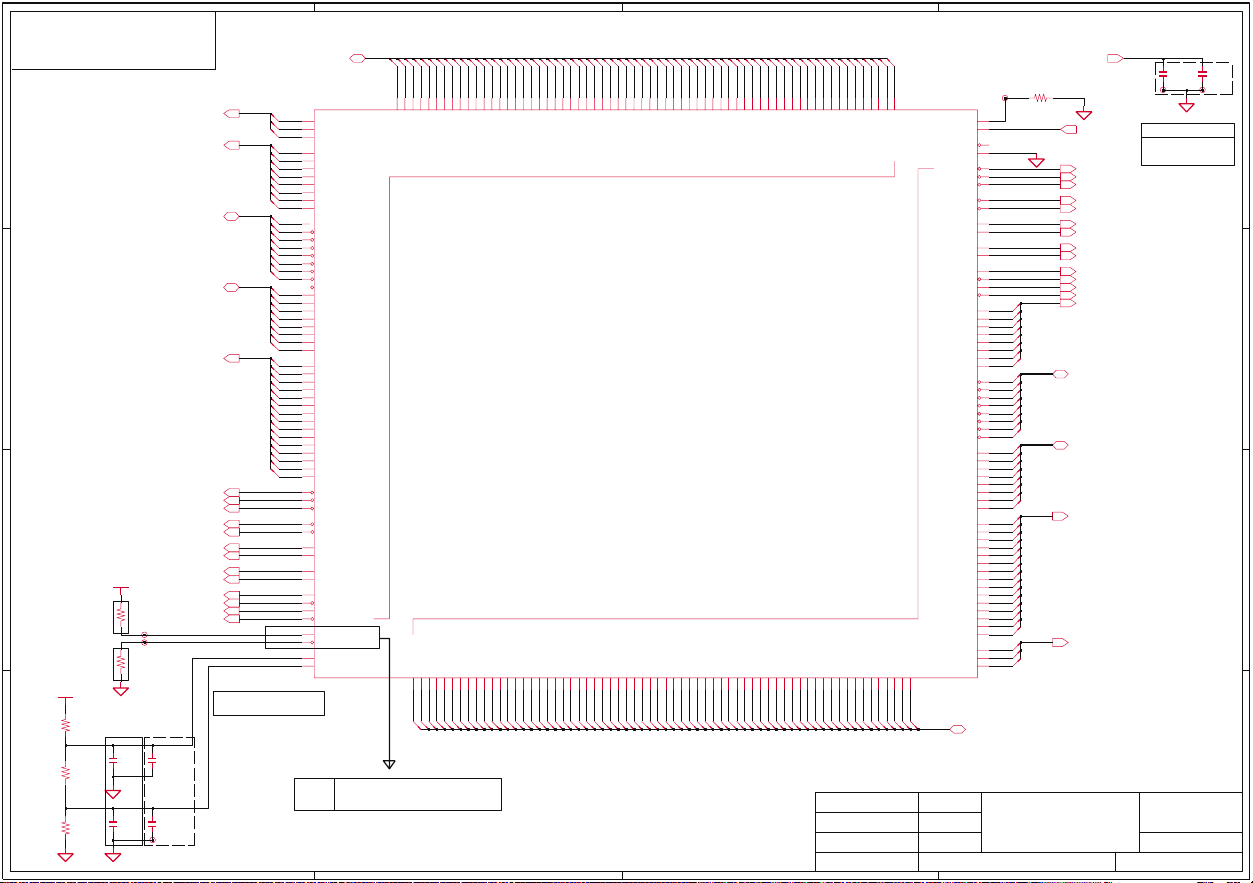

POWER DIAGRAM

1

Rev 0.1

D

C

B

Power On/Off Table by S-state

Rail

State

+V*A(LWS)

+V*LAN

A

+1.8V_AUX

+0.9V

+V*AUX

+V

AC Adapter

Battery DC

S3

S0

ON

ON

ON

ON

ON

ON

ON

ON+V* (CORE)

4

KBC3_SUSPWR

(CHP3_S4_STATE*)

P1.05V_AUX

KBC3_PWRON

(CHP3_SLPS3*)

P1.05V

(VCCP)

MEROM

CRESTLINE

ICH8-M

KBC3_VRON

VCC_CORE

D

MEROM

P1.5V_AUX

VDC

P3.3V_MICOM

MICOM

P3.3V_ALW

P5.0V_ALW

P12.0V_ALW

S5

S4

ON

ON

S5-S4

3

ICH9-M

P1.5V_AUX

P0.9V

OPTION FOR ME

P5V_AUX

P3.3V_AUX

ICH8-M

MDC

P1.2V_LAN

P1.8V_LAN

P2.5V_LAN

LAN

BT

SODIMM (DDR III)

Cantiga

DDR III-Termination

It should be updated

LAN

LAN

S3

P1.8V

P0.9V

P5.0V

IGFX_CORE

P1.5V

EGFX_CORE

P3.3V

P1.25V

P1.2V

PEG

GDDR-3 for PEG

DDR II-Termination

ICH8-M

PCMCIA

USB

FDD

CRT

HEATSINK

MDC

MICOM

PEG

CRESTLINE

CRESTLINE

ICH8-M

nVidia (TBD)

CRESTLINE

ICH8-M

SPI

PEG

MDC

CRESTLINE

ICH8-M

PEG

HDD

M_PCI

FAN CIRCUIT

AUX DISPLAY

Thermal Sensor

SODIMM

PCMCIA

LEDs

MICOM

M_PCI

LCD

C

B

S0

DRAW

CHECK

APPROVAL

MODULE CODE

2

TW.Kim

HJ.Kim

SJ.Park

undefined

DATE

DEV. STEP

REV

LAST EDIT

9/23/2008

ADV2nd

TITLE

1.0

Bremen-UL

MAIN

POWER DIAGRAM

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

PAGE

ELECTRONICS

BA41-xxxxxA

504

OF

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

C

D

C

BLANK

B

B

ELECTRONICS

BA41-xxxxxA

50

OF

A

A

CHECK

APPROVAL

MODULE CODE

4

3

2

TW.Kim

HJ.Kim

SJ.Park

DATEDRAW

DEV. STEP

REV

LAST EDIT

10/10/2008

ADV2nd

TITLE

1.0

Bremen-UL

MAIN

BLANK

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

5

PAGE

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

C

D

C

BLANK

B

B

A

4

3

DRAW

CHECK

APPROVAL

2

TW.Kim

HJ.Kim

SJ.Park

undefined

DATE

DEV. STEP

REV

LAST EDITMODULE CODE

9/23/2008

ADV2nd

TITLE

1.0

Bremen-UL

MAIN

BLANK

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

650

PAGE

A

ELECTRONICS

BA41-xxxxxA

OF

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4 3

2

1

D

C

D

C

BLANK

B

B

A

4

3 2

DRAW DATE TITLE

CHECK DEV. STEP

APPROVAL

MODULE CODE

TW.Kim

HJ.Kim

SJ.Park

undefined

REV

LAST EDIT

9/23/2008

ADV2nd

1.0

Bremen-UL

MAIN

BLANK

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

7 50

PAGE

A

ELECTRONICS

BA41-xxxxxA

OF

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

C

THERMAL SENSOR & FAN CONTROL

P3.3V_AUX

R559

10K

1%

C566

10000nF-X5R

6.3V

P5.0V

C58

100nF

10V

FAN5_VDD

FAN3_FDBACK#

R561

nostuff

0

P3.3V_AUX

R47

49.9

1%

C59

100nF

10V

U502

EMC2112-BP-TR

THM3_VDD_3V_MN

1

16

19

9

17

18

20

THM3_SHDN_SEL_MN

THM3_TRIP_SET_MN

R562

1.5K

1%

TRIP_SET 1500 : 95 degree

10

6

7

VDD_3V

VDD_5V_1

VDD_5V_2

SYS_SHDN#

RESET#

FAN_1

FAN_2

TACH

ADDR_SEL

SHDN_SEL

TRIP_SET

THERMAL_PAD

SMBUS Address 7Ah

SMDATA

SMCLK

ALERT#

DP3_DN2

DN3_DP2

1209-001887

DN1

DP1

CLK

GND

P3.3V

14

15

12

8

2

3

THM3_THERMDN_MN

4

THM3_THERMDP_MN

5

11

13

21

P3.3V_AUX

1%

1%

10K

10K

10K

R541%R53

R574

C845

1000nF-X5R

6.3V

1%

10K

R560

nostuff

C565

2.2nF

50V

KBC3_THERM_SMDATA

KBC3_THERM_SMCLK

THM3_ALERT#

THM3_STP#

CPU2_THERMDC

CPU2_THERMDA

2

C564

2.2nF

1

50V

3

Opposite side of CPU.

10mil width and 10mil spacing.

For Intel 45nm(From penryn)

MMBT3904

Q9

B

P3.3V

C79

10000nF-X5R

6.3V

R48

10K

1%

J2

HDR-4P-1R-SMD

1

2

3

4

5

MNT1

6

MNT2

3711-000456

DESIGN

CHECK

APPROVAL

MODULE CODE

TW.Kim

HJ.Kim

SJ.Park

DATE

DEV. STEP

REV

LAST EDIT

2

9/23/2008

ADV2nd

TITLE

1.0

Bremen-UL

THERMAL SENSOR

THERMAL SENSOR EMC2112

October 05, 2009 20:00:56 PM

HIGH Z

0

1

SHDN_SEL MODE

INTEL TR MODE

AMD CPU/DIODE MODE

EXT.DIODE 2 MODE

FAN3_FDBACK#

FAN5_VDD

Line Width = 20 mil

ADDRESSS_SEL MODE

0

HIGH Z

A

4

0101 111xb

0111 101xb (7A)

1 0101 110xb

3

M500

HEAD

DIA

LENGTH

BA61-01090A

To support heatsink

PAGE

1

SAMSUNG

PART NO.

850

M501

HEAD

DIA

LENGTH

BA61-01090A

ELECTRONICS

BA41-xxxxxA

OF

D

C

B

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4 3

2

1

D

D

P1.05V

R563

ADS#

BNR#

BPRI#

BR0#

INIT#

RS0#

RS1#

RS2#

HIT#

LINT0

LINT1

SMI#

H1

E2

G5

F1

H5

F21

E1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

A6

A5

C4

D5

C6

B4

A3

K3

H2

K2

J3

L1

56

CPU1_IERR#_MN

0

1

2

3

4

CPU1_ADS#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_DEFER#

CPU1_DRDY#

CPU1_DBSY#

CPU1_INIT#

CPU1_LOCK#

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_TRDY#

CPU1_HIT#

CPU1_HITM#

CPU1_A20M#

CPU1_FERR#

CPU1_IGNNE#

CPU1_STPCLK#

CPU1_NMI

CPU1_SMI#

CPU1_REQ#(4:0)

CPU1_CPURST#

CPU1_INTR

CPU1_D#(15:0)

CPU1_DSTBN0#

CPU1_DSTBP0#

CPU1_DBI0#

CPU1_D#(31:16)

CPU1_DSTBN1#

CPU1_DSTBP1#

CPU1_DBI1#

CPU1-1

PENRYN

CPU1_A#(16:3)

C

CPU1_ADSTB0#

CPU1_A#(35:17) CPU1_DBI2#

CPU1_ADSTB1#

B

1 / 4

3

J4

A3#

4

L5

A4#

5

L4

A5#

6

K5

A6#

7

M3

A7#

8

N2

A8#

9

J1

A9#

10

N3

A10#

11

P5

A11#

12

P2

A12#

13

L2

A13#

14

P4

A14#

15

P1

A15#

16

R1

A16#

M1

ADSTB0#

17

Y2

A17#

18

U5

A18#

19

R3

A19#

20

W6

A20#

21

U4

A21#

22

Y5

A22#

23

U1

A23#

24

R4

A24#

25

T5

A25#

26

T3

A26#

27

W2

A27#

28

W5

A28#

29

Y4

A29#

30

U2

A30#

31

V4

A31#

32

W3

A32#

33

AA4

A33#

34

AB2

A34#

35

AA3

A35#

V1

ADSTB1#

0143854500|bga_479p_sock

0

ADDR GROUP

CONTROL

1

ICH

ADDR GROUP

DEFER#

DRDY#

DBSY#

IERR#

LOCK#

RESET#

TRDY#

HITM#

A20M#

FERR#

IGNNE#

STPCLK#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

CPU1-2

PENRYN

2 / 4

0

E22

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

0143854500|bga_479p_sock

DATA GRP 0

DATA GRP 2

DSTBN2#

DSTBP2#

DATA GRP 1

DATA GRP 3

DSTBN3#

DSTBP3#

DINV2#

DINV3#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

CPU1_D#(47:32)

CPU1_DSTBN2#

CPU1_DSTBP2#

CPU1_D#(63:48)

CPU1_DSTBN3#

CPU1_DSTBP3#

CPU1_DBI3#

C

B

CPU Socket : 3704-001153

M502

SUPLECODE

1

MNT1

2

MNT2

3

MNT3

4

MNT4

CPU bracket

A

DRAW

CHECK

APPROVAL

MODULE CODE

4

3

2

TW.Kim

HJ.Kim

SJ.Park

undefined

DATE

DEV. STEP

REV

LAST EDIT

9/23/2008

ADV2nd

TITLE

1.0

Bremen-UL

CPU

PENRYN (1/3)

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

PAGE

ELECTRONICS

BA41-xxxxxA

509

OF

A

CLK0_HCLK0

CLK0_HCLK0#

CPU1_SLP#

CPU1_DPWR#

CPU1_PSI#

C517

100nF

10V

nostuff

CPU1_VCCSENSE

CPU1_VSSSENSE

4

CPU1_BSEL2

CPU1_BSEL1

CPU1_BSEL0

R523

R522

R546

R547

C571

0.1nF

50V

To protect ESD

54.9

27.4

54.9

27.4

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

D

CPU1_DPSLP#

CPU1_DPRSTP#

CPU1_PWRGDCPU

CPU1_VID(6:0)

P1.05V

R564

56

CPU1_PROCHOT#_MN

CPU2_THERMDA

CPU2_THERMDC

P1.05V

CPU1_THRMTRIP#

R526

1K

1%

CPU1_GTLREF_MN

R509

2K

C

1%

SI team request

B

P1.05V

1%

1%

54.9

54.9

R521

1%

54.9

R520

1%

54.9

near the CPU

CPU1_TDI

CPU1_TMS

CPU1_TCK

CPU1_TRST#

A

R524

R525

4

nostuff

CPU1_COMP3_MN

1%

CPU1_COMP2_MN

1%

CPU1_COMP1_MN

1%

CPU1_COMP0_MN

1%

6

5

4

3

2

1

0

A22

A21

D24

AE6

AD6

D21

A24

B25

C21

B23

B22

AD26

AA1

U26

R26

AF7

AE7

C23

D25

C24

AF26

AF1

A26

FSC

0

0

0

CPU1-3

PENRYN

3 / 4

BCLK0

BCLK1

D7

SLP#

B5

DPSLP#

E5

DPRSTP#

DPWR#

D6

PWRGOOD

PSI#

AE2

VID_6

AF3

VID_5

AE3

VID_4

AF4

VID_3

AE5

VID_2

AF5

VID_1

VID_0

PROCHOT#

THRMDA

THRMDC

C7

THERMTRIP#

BSEL2

BSEL1

BSEL0

GTLREF

Y1

COMP3

COMP2

COMP1

COMP0

VCCSENSE

VSSSENSE

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

C3

TEST7

0143854500|bga_479p_sock

FSB

FSA

0

0

0

1

1

1

BSEL

FSB 1067 MHz

FSB 800 MHz

FRQ

266M

200M

166M

H CLK

THERMAL

VCCA_1

VCCA_2

VCCP_1

VCCP_2

VCCP_3

VCCP_4

VCCP_5

VCCP_6

VCCP_7

VCCP_8

VCCP_9

VCCP_10

VCCP_11

VCCP_12

VCCP_13

VCCP_14

VCCP_15

VCCP_16

PREQ#

PRDY#

BPM3#

BPM2#

BPM1#

BPM0#

TCK

TDI

TDO

XDP/ITP SIGNALS

TMS

TRST#

DBR#

RSVD_1

RSVD_2

RSVD_3

RSVD_4

RSVD_5

RSVD_6

RSVD

RSVD_7

RSVD_8

RSVD_9

3

B26

C26

K6

J6

M6

N6

T6

R6

K21

J21

M21

N21

T21

R21

V21

W21

V6

G21

AC1

AC2

AC4

AD1

AD3

AD4

AC5

AA6

AB3

AB5

AB6

C20

M4

N5

T2

V3

B2

D2

D22

D3

F6

Pull-down

BSEL0, BSEL1, BSEL2

BSEL0, BSEL2

3

P1.5V

C594

C578

10000nF-X5R

10nF

6.3V

25V

P1.05V

EC501

220uF

2.5V

nostuff

-> delete and change layout (ECAE)

C559

C554

100nF

100nF

10V

10V

nostuff

CPU1_TCK

CPU1_TDI

CPU1_TMS

CPU1_TRST#

ITP3_DBRESET#

C558

100nF

10V

C557

100nF

10V

C556

100nF

10V

nostuff

C555

100nF

10V

2

CPU Core Voltage Table

Active Mode

VID(6:0)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0 0

0

0

0

1

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

1

0

0

0

0

0

1

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

0

1

0

0

0

11

0

0

0

1

1

0

0

1

0

0

1

1

0

1

0

1

0

0

1

1

0

0

1

0

1

0

1

0

1

1

0

0

1

0

1

0

1

0

1

0

0

0

1

1

0

0

0

0

0

1

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

0

1

0

0

DPRSLPVR

DPRSTP*

PSI2*

Voltage

0

1.5000 V 1

0

0

1

0

0

0

0

1

1.4750 V

1

1

1.4625 V

0

1

1.4500 V

0

1

1.4375 V

0

1

1.4250 V

1

0

1

1

1

1

1

1

1.4125 V

0

0

0

1.4000 V

0

0

1.3875 V

1

0

1

1.3750 V

0

1.3625 V

1

0

1

0

0

1.3500 V

1

1.3375 V

1

0

1

0

1

1.3250 V

1

1

1.3125 V

1

1 1

0

0

0

1.3000 V

1.2875 V

0

0

1

0

1.2750 V

1

0

1.2625 V

1

1

0

0

1.2500 V

1

0

0

1.2375 V

1

1

1.2250 V

1

0

1

1

1

1.2125 V

1

1

1

0

1.2000 V

0

0

1.1875 V

1

0

0

0

0

1.1750 V

1

1

1.1625 V

0

1

1

0

1.1500 V

0

1.1375 V

0

1

1

1

1

0

1.1250 V

1

1

1

1.1125 V

0

0

1.1000 V

0

1

0

0

1.0875 V

1

0

0

1.0750 V

1

0

1

1.0625 V

0

0 1

1

1.0500 V

1

1

0

1.0375 V

1

100

1.0250 V

1

1

1

1

1

1.0125 V

Active

0

1

0 or 1

Active/Deeper Sleep

Dual Mode Region

VID(6:0)

0

0

1

0

1

0

0

1

0

0

1

0

1

0

0

1

0

0

0

1

0

1

0

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

1

0

1

1

0

1

0

1

1

1

0

1

0

1

1

1

0

1

0

1

0

1

0

0

1

0

0

0

1

0

1

0

0

0

1

0

0

1

0

0

1

0

0

1

0

1

0

0

00

1

0

0

1

0

1

0

0

0

1

0

0

0

1

0

0

0

1

1

0

1

DPRSLPVR

DPRSTP*

PSI2*

IMVP-6

0

1

0

0

0V 5784.1

1

1

0

1

1

0

0

1

1

0

1

0

1

0

1

01

1

1

1

1

1

0

1

1

1

1

1

1

0

0

0

0

0

0

0

1

0

0

1

0

1

0

1

0

0

0

1

0

0

1

0

1

1

1

0

0

1

1

1

0

1

0

0

0

1

0

0

1

1

0

1

0

1

1

1

1

1

0

0

1

0

1

1

0

1

1

1

1

1

1

11

1

0

0

0

0

0

1

0

0

0

0

1

0

0

1

0

1

0

0

0

1

1

0

0

1

0

1

0

1

0

1

110.6125 V

1

1

0

0

0

1

0

0

1

1

1

0

1

11

0

0

0

1

1

1

1

0

1

1

1

0

1

1

1

1

1

1

0

0

0

0

0

0

Deeper Slp

1

0

0 or 1

1

Deeper Sleep/Extended Deeper Sleep

Dual Mode Region

Voltage

VID(6:0)

1

1.0000 V

0.9875 V

0.9750 V

0.9625 V

0.9500 V

0.9375 V

0.9250 V

0.9125 V

0.9000 V

0.8875 V

0.8750 V

0.8625 V

0.8500 V

0.8375 V

0.8250 V

0.8125 V

0.8000 V

0.7875 V

0.7750 V

0.7625 V

0.7500 V

0.7375 V

0.7250 V

0.7125 V

0.7000 V

0.6875 V

0.6750 V

0.6625 V

0.6500 V

0.6375 V

0.6250 V

0.6000 V

0.5875 V

0.5750 V

0.5625 V

0.5500 V

0.5375 V

0.5250 V

0.5125 V

0.5000 V

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

11

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

*"1111111" : 0V power good asserted.

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

*Yonah Processor (2.33 GHz / 800 MHz : TBD)

GTLREF : Keep the Voltage divider within 0.5"

of the first GTLREF0 pin with Zo=55ohm trace.

Minimize coupling of any switching signals to this net.

COMP0,2(COMP1,3) should be connected with Zo=27.4ohm(55ohm)

trace shorter than 1/2" to their respective Banias socket pins.

GND test points within 100mil of the VCC/VSSsense at the end of the line.

Route the VCC/VSSsense as a Zo=55ohm traces with equal length.

Observe 3:1 spacing b/w VCC/VSSsense lines and 25mil away

(preferred 50mil) from any other signal. And GND via 100mil away

from each of the VCC/VSS test point vias.

DRAW

CHECK

APPROVAL

MODULE CODE

2

TW.Kim

HJ.Kim

SJ.Park

undefined

DATE

DEV. STEP

REV

LAST EDIT

9/23/2008

ADV2nd

TITLE

1.0

Bremen-UL

CPU

PENRYN (2/3)

October 05, 2009 20:00:56 PM

1

0

0

1

0

0

0

1

0

0

1

1

0

0

0

1

0

0

0

1

1

0

1

0

1

0

1

1

1

0

0

0

1

1

0

0

1

0

1

1

0

1

1

0

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

1

1

0

0

0

0

0

1

0

0

0

0

0

1

0

1

1

00

0

1

0

0

1

0

0

1

1

1

0

0

1

1

0

1

0

0

1

1

0

0

1

1

0

1

1

0

0

1

1

0

1

1

0

1

0

1

0

1

1

1

1

0

1

1

1

1

1

0

0

0

0

0

1

0

0

0

0

0

1

1

1

0

0

0

1

0

0

0

10

1

0

1

1

0

0

1

1

1

0

0

1

0

0

1

1

01

1

0

0

0

1

1

1

0

1

1

0

0

1

1

1

1

1

0

1

1

0

1

1

1

1

1

SAMSUNG

PART NO.

10 50

PAGE

Voltage

0.4875 V

0.4750 V

0.4625 V

0.4500 V

0.4375 V0

0.4250 V

0.4125 V

0.4000 V

0.3875 V

0.3750 V

0.3625 V

0.3500 V

0.3375 V

0.3250 V

0.3125 V

0.3000 V

0.2875 V

0.2750 V

0.2625 V

0.2500 V

0.2375 V

0.2250 V

0.2125 V

0.2000 V

0.1875 V

0.1750 V

0.1625 V

0.1500 V

0.1375 V

0.1250 V

0.1125 V

0.1000 V

0.0875 V

0.0750 V

0.0625 V

0.0500 V

0.0375 V

0.0250 V

0.0125 V1

0.0000 V

0.0000 V

0.0000 V

0.0000 V

0.0000 V

0.0000 V

0.0000 V

0.0000 V

ELECTRONICS

BA41-xxxxxA

OF

D

C

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

D

A11

VSS_1

A14

VSS_2

A16

VSS_3

A19

VSS_4

A2

VSS_5

A23

VSS_6

A25

VSS_7

A4

VSS_8

A8

VSS_9

AA11

VSS_10

AA14

VSS_11

AA16

VSS_12

AA19

CPU_CORE

C

100 1%

CPU1_VCCSENSE

CPU1_VSSSENSE

R508

R507

100 1%

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C534

C533

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C535

C536

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C538

C537

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C539

C540

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C572

C515

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C575

C573

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C516

C574

6.3V

6.3V

10000nF-X5R

10000nF-X5R

C577

C576

Prodlizer & Cbulk common used(Socket inside)

B B

AA22

AA25

AB11

AB13

AB16

AB19

AB26

AC11

AC14

AC16

AC19

AC21

AC24

AD11

AD13

AD16

AD19

AD22

AB23

AD25

AE11

AE14

AE16

AE19

AE23

AE26

AF11

AF13

AF16

AF19

AF21

VSS_13

AA2

VSS_14

VSS_15

VSS_16

AA5

VSS_17

AA8

VSS_18

AB1

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

AB4

VSS_25

AB8

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

AC3

VSS_33

AC6

VSS_34

AC8

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

AD2

VSS_40

VSS_41

VSS_42

VSS_43

AD5

VSS_44

AD8

VSS_45

AE1

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

AE4

VSS_53

AE8

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

AF2

VSS_59

VSS_60

CPU_CORE

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AC10

AC12

AC13

AC15

AC17

AC18

AD10

AD12

AD14

AD15

AD17

AD18

AE10

AE12

AE13

AE15

AE17

AE18

AE20

K23

K26

VSS_121

A10

VCC_1

A12

VCC_2

A13

VCC_3

A15

VCC_4

A17

VCC_5

A18

VCC_6

A20

VCC_7

A7

VCC_8

A9

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

AA7

VCC_17

AA9

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

AB7

VCC_26

AB9

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

AC7

VCC_34

AC9

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

AD7

VCC_42

AD9

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

Y24

L21

L24

L3

VSS_122K4VSS_123

VSS_124

VSS_125

VSS_126

0143854500|bga_479p_sock

VSS_159

VSS_160

VSS_161Y3VSS_162Y6VSS_163

VSS_157

VSS_158

W4

Y21

W23

W26

M25

L6

M22

VSS_130M5VSS_131N1VSS_132

VSS_127M2VSS_128

VSS_129

CPU1-4

PENRYN

4 / 4

VSS_153

VSS_154V5VSS_155W1VSS_156

V22

V25

N23

N26

VSS_133

VSS_150U6VSS_151V2VSS_152

U3

U24

P21

P24

VSS_134N4VSS_135

VSS_136

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VSS_148

VSS_149

T26

U21

R2

P6

VSS_137P3VSS_138

VSS_139

AE9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

AF9

B10

B12

B14

B15

B17

B18

B20

B7

B9

C10

C12

C13

C15

C17

C18

C9

D10

D12

D14

D15

D17

D18

D9

E10

E12

E13

E15

E17

E18

E20

E7

E9

F10

F12

F14

F15

F17

F18

F20

F7

F9

VSS_145

VSS_146T4VSS_147

T23

R22

VSS_140

VSS_141

CPU_CORE

VSS_142R5VSS_143T1VSS_144

R25

VSS_120

VSS_119

VSS_118

VSS_117

VSS_116

VSS_115

VSS_114

VSS_113

VSS_112

VSS_111

VSS_110

VSS_109

VSS_108

VSS_107

VSS_106

VSS_105

VSS_104

VSS_103

VSS_102

VSS_101

VSS_100

VSS_99

VSS_98

VSS_97

VSS_96

VSS_95

VSS_94

VSS_93

VSS_92

VSS_91

VSS_90

VSS_89

VSS_88

VSS_87

VSS_86

VSS_85

VSS_84

VSS_83

VSS_82

VSS_81

VSS_80

VSS_79

VSS_78

VSS_77

VSS_76

VSS_75

VSS_74

VSS_73

VSS_72

VSS_71

VSS_70

VSS_69

VSS_68

VSS_67

VSS_66

VSS_65

VSS_64

VSS_63

VSS_62

VSS_61

K1

J5

J25

J22

J2

H6

H3

H24

H21

G4

G26

G23

G1

F8

F5

F25

F22

F2

F19

F16

F13

F11

E8

E6

E3

E24

E21

E19

E16

E14

E11

D8

D4

D26

D23

D19

D16

D13

D11

D1

C8

C5

C25

C22

C2

C19

C16

C14

C11

B8

B6

B24

B21

B19

B16

B13

B11

AF8

AF6

AF25

D

C

ELECTRONICS

BA41-xxxxxA

5011

OF

A

A

DRAW

CHECK

APPROVAL

MODULE CODE

4

3

2

TW.Kim

HJ.Kim

SJ.Park

undefined

DATE

DEV. STEP

REV

LAST EDIT

9/23/2008

ADV2nd

TITLE

1.0

Bremen-UL

CPU

PENRYN (3/3)

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

PAGE

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

3

2

1

CK505M

D

C

B

A

FSA

BSEL0

0

0

0

0

1

1

1

1

CLK REQ

CLK REQ A

CLK REQ B

CLK REQ E

CLK REQ F

SEL_LCDCLK*

LOW

HIGH

FSC

FSB

BSEL2

BSEL1

0

0

1

1

0

0

1

1

DEVICE

SATA

GMCH

MINI CARD

EXP3_CLKREQ#

Pin 20/21

DOT_96/DOT_96#

SRC_0/SRC_0#

HOST CLK

266 MHz

0

1

333 MHz

200 MHz

0

1

400 MHz

0

133 MHz

1

100 MHz

0

166 MHz

RSVD

1

CLK3_MMC48

CLK3_USB48

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

CLK3_ICH14

CHP3_CPUSTP#

CHP3_PCISTP#

CLK3_PWRGD

CLK3_PCLKICH

CLK3_DBGLPC

CLK3_PCLKMICOM

MCH3_CLKREQ#

CHP3_SATACLKREQ#

SMB3_CLK

SMB3_DATA

To protect ESD

SRC PORT

SRC2

SRC4

SRC6

SRC8

PEG_CLK/PEG_CLK#

27M & 27M_SS

4

Pin 24/25

R67

R66

R68

R580

R577

R579

R578

R583

R582

R581

C778

0.1nF

50V

Y500

nostuff

1

14.31818MHz

2801-004874

C570

0.018nF

50V

Place 14.318MHz within

500mils of CK-505

33

33

2.2K

10K

33 1%

22

22

22

475

475

2

6.3V

10000nF-X5R

C582

nostuff

1%

1%

1%

1%

1%

C569

0.018nF

50V

10V

100nF

C585

6.3V

10000nF-X5R

C81

nostuff

50V

0.033nF

C591

50V

0.033nF

C592

50V

0.033nF

C593

10V

100nF

C567

10000nF-X5R

C586

nostuff

6.3V

C91

0.022nF

50V

10V

100nF

C590

nostuff

CLK3_USB48_R_MN

CLK3_ICH14_R_MN

CLK3_PCLKICH_R_MN

CLK3_DBGLPC_R_MN

CLK3_PCLKMICOM_R_MN

MCH3_CLKREQ#_R_MN

CHP3_SATACLKREQ#_R_MN

1%

1%

10K

10K

R575

R576

3

6.3V

10000nF-X5R

C583

CLK3_VDD_SRC_IO_MN

CLK_XTAL_IN_MN

CLK_XTAL_OUT_MN

P1.5V

B502

BLM18PG181SN1

U5

SLG8SP513

19

VDD_IO

33

VDD_SRC_IO1

43

VDD_SRC_IO2

52

VDD_SRC_IO3

56

VDD_CPU_IO

27

VDD_PLL3_IO

55

NC

17

USB_FS_A

64

FSB_TESTMODE

5

REF_FS_C_TEST_SEL

44

CPUSTOP#

45

PCISTOP#

63

CLKPWRGD_PWRDN#

14

PCIF_5_ITP_EN

13

PCI_4_SEL_LCDCLK#

12

PCI_3

11

PCI_2

10

PCI_1_CLKREQ_B#

8

PCI_0_CLKREQ_A#

7

SCL

6

SDA

3

XTAL_IN

2

XTAL_OUT

18

VSS_48

59

VSS_CPU

22

VSS_IO

15

VSS_PCI

26

VSS_PLL3

1

VSS_REF

30

VSS_SRC1

36

VSS_SRC2

49

VSS_SRC3

1205-003156

THERM_GND

65

This part is 64pin QFN package.

IDT : 1205-003159

SL : 1205-003533

VDD_REF

VDD_48

VDD_PCI

VDD_PLL3

VDD_SRC

VDD_CPU

CPU0

CPU0#

CPU1_MCH

CPU1_MCH#

SRC11_CLKREQH#

SRC11#_CLKREQG#

SRC10

SRC10#

SRC9

SRC9#

SRC8_ITP

SRC8#_ITP#

SRC7_CLKREQF#

SRC7#_CLKREQE#

SRC6

SRC6#

SRC4

SRC4#

SRC3_CLKREQC#

SRC3#_CLKREQD#

SRC2

SRC2#

LCDCLK_27M

LCDCLK#_27M_SS

SRC0_DOT96

SRC0#_DOT96#

2

P3.3V

4

16

9

23

46

62

61

60

58

57

40

39

41

42

37

38

54

53

51

50

48

47

34

35

31

32

28

29

24

25

20

21

B503

BLM18PG181SN1

10V

100nF

C80

CLK3_VDD_REF_MN

DRAW

CHECK

APPROVAL

MODULE CODE

10V

6.3V

10000nF-X5R

100nF

C587

C588

DATE

TW.Kim

DEV. STEP

HJ.Kim

REV

SJ.Park

LAST EDIT

undefined

10V

100nF

C90

9/23/2008

ADV2nd

CLK0_HCLK0

CLK0_HCLK0#

CLK0_HCLK1

CLK0_HCLK1#

LAN3_CLKREQ#

CLK1_PCIELOM

CLK1_PCIELOM#

MIN3_CLKREQ#

CLK1_MINIPCIE

CLK1_MINIPCIE#

CLK1_MCH3GPLL

CLK1_MCH3GPLL#

CLK1_PCIEICH

CLK1_PCIEICH#

CLK1_SATA

CLK1_SATA#

CLK1_DREFSSCLK

CLK1_DREFSSCLK#

CLK1_DREFCLK

CLK1_DREFCLK#

TITLE

1.0

10V

6.3V

10000nF-X5R

100nF

C584

C589

Bremen-UL

MAIN_CLOCK_CIRCUIT

CK_Clock_505M

October 05, 2009 20:00:56 PM

1

SAMSUNG

PART NO.

PAGE

ELECTRONICS

BA41-xxxxxA

5012

OF

D

C

B

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

D

P1.05V

R587

221

1%

R588

C609

100

100nF

1%

10V

C

P1.05V

R586

1K

1%

R584

2K

1%

B

*POCAFEB-12 Only (Remove in MP Model)

CFG#

A

CFG(5)

CFG(6)

CFG(7)

CFG(9)

CFG(10)

CFG(16)

CFG(19)

CFG(20)

Current Setting

Low

DMIx2

iTPM Host Interface Enable

ME Crypto no confidentiality

PEG Reversal (def.)

PCIE Loop Back Enable

Dynamic ODT Disabled

DMI Lane Normal (def.)

SDVO or PCIE X1

Only(def.)

(def. : default Option)

DMIx4 (def.)

iTPM Host Interface Disable (def.)

ME Crypto confidentiality (def.)

Normal

PCIE Loop Back Disable(def)

Dynamic ODT

DMI Lane Reversal

SDVO and PCIE X1

Simultaneously

4

CPU1_D#(63:0)

MCH1_HXSWING

MCH1_HVREF

CPU1_CPURST#

CPU1_SLP#

MCH1_HXSWING

MCH1_HVREF

High

Enabled (def.)

R72

22-D2

MCH1_H_RCOMP_MN

1%24.9

MCH1_VTTLF1_MN

MCH1_VTTLF2_MN

MCH1_VTTLF3_MN

EC504

220uF

2.5V

nostuff

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

1608

16V

16V

470nF

470nF

C664

C608

16V

470nF

C103

C648

10000nF-X5R

6.3V

F2

G8

F8

E6

G2

H6

H2

F6

D4

H3

M9

M11

J1

J2

N12

J6

P2

L2

R2

N9

L6

M5

J3

N2

R1

N5

N6

P13

N8

L7

N10

M3

Y3

AD14

Y6

Y10

Y12

Y14

Y7

W2

AA8

Y9

AA13

AA9

AA11

AD11

AD10

AD13

AE12

AE9

AA2

AD8

AA3

AD3

AD7

AE14

AF3

AC1

AE3

AC3

AE11

AE8

AG2

AD6

C12

E11

C5

E3

B11

A11

A8

AB2

L1

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

P1.05V

C658

100nF

10V

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_CPURST#

H_CPUSLP#

H_SWING

H_RCOMP

H_DVREF

H_AVREF

VTTLF_1

VTTLF_2

VTTLF_3

C650

100nF

10V

3

VTTLF

3

C632

100nF

10V

AA34

AB34

AC26

AA33

AA28

VCC_3

VCC_4

VCC_2

VCC_1

HOST DATA BUS

CFG_2

CFG_3

CFG_4

CFG_0

CFG_1

T25

P25

P20

P24

C25

R25

AC28

AC33

AC34

VCC_5

VCC_6

VCC_7

CFG_5

CFG_6

CFG_7

E21

N24

M24

MCH1_CFG6_MN

R602

2.2K

iTPM option

AE26

VCC_8

CFG_8

C23

AE33

VCC_9

CFG

CFG_9

C24

nostuff

AF23

VCC_10

VCC_11

CFG_10

CFG_11

N21

AF25

VCC_12

CFG_12

P21

AF28

VCC_13

CFG_13

T21

AF33

VCC_14

CFG_14

R20

AG24

VCC_15

CFG_15

M20

AG25

AG26

VCC_16

VCC CORE

CFG_16

L21

H21

AG33

VCC_17

VCC_18

CFG_17

CFG_18

P29

AG34

VCC_19

CFG_19

R28

AH23

VCC_20

CFG_20

T28

AH25

AH28

AJ23

AJ26

VCC_21

VCC_22

VCC_23

VCC_NCTF_1

VCC_NCTF_2

AA29

AA30

AA32

AK33

AM33

T32

AJ33

VCC_25

VCC_26

VCC_27

VCC_24

VCC_NCTF_4

VCC_NCTF_3

VCC_NCTF_5

VCC_NCTF_6

AB30

AC29

AC30

AC32

U33

U34

V33

V34

VCC_28

VCC_29

VCC_30

VCC_31

U7-1

GL40

1 OF 5

0904-002489

VCC_NCTF_10

VCC_NCTF_7

VCC_NCTF_8

VCC_NCTF_9

AF30

AE32

AE29

AE30

W33

Y33

Y34

VCC_35

VCC_32

VCC_33

VCC_34

VCC_NCTF_11

VCC_NCTF_12

VCC_NCTF_13

VCC_NCTF_14

VCC_NCTF_15

AH29

AG29

AG30

AG32

2

T11

T12

T10

VTT_2

VTT_3

VTT_1

VCC_NCTF_16

VCC_NCTF_17

VCC_NCTF_18

VCC_NCTF_19

AJ29

AJ32

AH30

AH32

2

T13

T2

VTT_4

VTT_5

VTT_6T5VTT_7T6VTT_8T7VTT_9

NC

VCC_NCTF_20

VCC_NCTF_21

VCC_NCTF_22

VCC_NCTF_23

AK23

AK24

AK25

AK26

T8

VTT_10T9VTT_11U1VTT_12

VCC_NCTF_24

VCC_NCTF_25

VCC_NCTF_26

AK28

AK29

AK30

AK32

DRAW

CHECK

APPROVAL

MODULE CODE

U10

U11

U12

U13

VTT_13

VTT_14

VTT_15

VTT

VCC_NCTF_27

VCC_NCTF_28

VCC_NCTF_29

VCC_NCTF_30

VCC_NCTF_31

AL26

AL28

AL29

AL30

AL32

undefined

U6

U5

VTT_19

VTT_20U7VTT_21U8VTT_22

VTT_16U2VTT_17U3VTT_18

VCC_NCTF_32

VCC_NCTF_33

VCC_NCTF_34

VCC_NCTF_35

VCC_NCTF_36

U30

U32

AM30

AM32

DATE

TW.Kim

DEV. STEP

HJ.Kim

REV

SJ.Park

LAST EDIT

U9

V1

VTT_23V2VTT_24V3VTT_25

VCC_NCTF_37

VCC_NCTF_38

VCC_NCTF_39

VCC_NCTF_40

V29

V30

W29

W30

9/23/2008

ADV2nd

HOST ADDRESS BUS

HOST CONTROL

VCC_NCTF_41

VCC_NCTF_42

VCC_NCTF_43

VCC_NCTF_44

Y29

Y30

Y32

W32

TITLE

1.0

P1.05V

C653

1000nF-X5R

6.3V

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

HPLL_CLK

HPLL_CLK#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

Bremen-UL

MCH_CANTIGA_GM_DDR2

CANTIGA (1/5)

October 05, 2009 20:00:56 PM

C661

10000nF-X5R

6.3V

nostuff

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

J11

F9

H9

E12

H11

C9

AH7

AH6

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

P1.05V

1

0

1

2

3

4

1

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

C656

10000nF-X5R

6.3V

EC503

220uF

2.5V

nostuff

CPU1_A#(35:3)

CPU1_ADS#

CPU1_ADSTB0#

CPU1_ADSTB1#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_DEFER#

CPU1_DBSY#

CPU1_DPWR#

CPU1_DRDY#

CPU1_HIT#

CPU1_HITM#

CPU1_LOCK#

CPU1_TRDY#

CLK0_HCLK1

CLK0_HCLK1#

CPU1_DBI0#

CPU1_DBI1#

CPU1_DBI2#

CPU1_DBI3#

CPU1_DSTBN0#

CPU1_DSTBN1#

CPU1_DSTBN2#

CPU1_DSTBN3#

CPU1_DSTBP0#

CPU1_DSTBP1#

CPU1_DSTBP2#

CPU1_DSTBP3#

CPU1_REQ#(4:0)

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

SAMSUNG

PART NO.

13 50

PAGE

D

C

B

A

ELECTRONICS

BA41-xxxxxA

OF

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

D

CRT3_DDCCLK

CRT3_DDCDATA

CRT3_HSYNC

CRT3_VSYNC

CRT3_BLUE

CRT3_GREEN

CRT3_RED

Default : TV Disable

C

LCD3_EDID_CLK

LCD3_EDID_DATA

MCH3_LCDVDDON

MCH3_BKLTEN

LCD3_BRIT

LCD1_ADATA0#

LCD1_ADATA1#

LCD1_ADATA2#

LCD1_ADATA0

LCD1_ADATA1

LCD1_ADATA2

LCD1_ACLK

LCD1_ACLK#

LCD1_BDATA0#

LCD1_BDATA1#

LCD1_BDATA2#

B

LCD1_BDATA0

LCD1_BDATA1

LCD1_BDATA2

LCD1_BCLK

LCD1_BCLK#

HDA3_HDMI_BCLK

HDA3_HDMI_SYNC

HDA3_HDMI_RST#

HDA3_HDMI_SDI2

HDA3_HDMI_SDO

R595

R596

1%

1%

50V

50V

50V

150

150

0.033nF

0.033nF

0.033nF

C628

C630

C629

R601

R600

R69

1%

150

R599

R594

R605

R604

R603

R71

40.2

40.2

1.02kohm

MCH_TVO_IREF_MN

MCH_TVA_DAC_MN

MCH_TVB_DAC_MN

MCH_TVC_DAC_MN

CRT_LVDS_IBG_MN

33

HDA3_HDMI_SDI2_MN

A

4

CRT3_HSYNC_MN

1%

1%

CRT3_VSYNC_MN

1K

75

75

75

1%

2.4K

1%

1%

1%

1%

1%

H32

CRT_DDC_CLK

J32

CRT_DDC_DATA

J29

CRT_HSYNC

L29

CRT_VSYNC

E28

CRT_BLUE

G28

CRT_GREEN

J28

CRT_RED

E29

CRT_TVO_IREF

G29

CRT_IRTN

C31

TV_DCONSEL_0

E32

TV_DCONSEL_1

F25

TVA_DAC

H25

TVB_DAC

K25

TVC_DAC

H24

TV_RTN

K33

L_DDC_CLK

J33

L_DDC_DATA

M32

L_CTRL_CLK

M33

L_CTRL_DATA

M29

L_VDD_EN

G32

L_BKLT_EN

L32

L_BKLT_CTRL

H47

LVDSA_DATA#_0

E46

LVDSA_DATA#_1

G40

LVDSA_DATA#_2

A40

LVDSA_DATA#_3

H48

LVDSA_DATA_0

D45

LVDSA_DATA_1

F40

LVDSA_DATA_2

B40

LVDSA_DATA_3

C40

LVDSA_CLK

C41

LVDSA_CLK#

A41

LVDSB_DATA#_0

H38

LVDSB_DATA#_1

G37

LVDSB_DATA#_2

J37

LVDSB_DATA#_3

B42

LVDSB_DATA_0

G38

LVDSB_DATA_1

F37

LVDSB_DATA_2

K37

LVDSB_DATA_3

A37

LVDSB_CLK

B37

LVDSB_CLK#

C44

LVDS_IBG

B43

LVDS_VBG

E37

LVDS_VREFH

E38

LVDS_VREFL

B28

HDA_BCLK

A28

HDA_SYNC

B30

HDA_RST#

B29

HDA_SDI

C29

HDA_SDO

IGFX_CORE

P1.05V

EC502

220uF

2.5V

AGVVT

LVDSHDA

VGA1_HDMI_HPD#

L44

L40

N41

P48

H44

J46

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_0

PEG_RX#_1

NC_1

NC_6B4NC_7

NC_4

NC_3

NC_5

NC_2

A6

A5

A43

A47

A46

A44

C654

10000nF-X5R

6.3V

T43

U43

Y43

Y36

N44

Y48

PEG_RX#_8

PEG_RX#_9

PEG_RX#_6

PEG_RX#_7

PEG_RX#_11

PEG_RX#_10

AA15

AA20

AA23

AA24

AA25

AA21

VCC_AXG_1

VCC_AXG_4

VCC_AXG_5

VCC_AXG_6

VCC_AXG_3

VCC_AXG_2

VCC_AXG_NCTF_10

VCC_AXG_NCTF_11

VCC_AXG_NCTF_12

VCC_AXG_NCTF_13

VCC_AXG_NCTF_8

VCC_AXG_NCTF_9

AF16

AF17

AF19

AE19

AE16

AE17

NC_10

NC_11

NC_12

NC_8

NC_9

B48

B45

B47

BC1

BC48

C633

C659

10000nF-X5R

1000nF-X5R

6.3V

6.3V

3

H43

AA43

AD37

AC47

AD39

PEG_RX_0

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

AB25

AC20

AC21

AB20

AB23

AB15

VCC_AXG_8

VCC_AXG_9

VCC_AXG_7

VCC_AXG_10

VCC_AXG_11

VCC_AXG_12

VCC_AXG_NCTF_14

VCC_AXG_NCTF_15

VCC_AXG_NCTF_16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

VCC_AXG_NCTF_19

AH16

AH17

AH19

AG16

AG17

AG19

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

BF1

BF3

BE2

BD1

BE47

BD48

C686

100nF

10V

3

0

2

31

10V

10V

10V

10V

100nF

100nF

100nF

100nF

C620

C619

C616

L43

L41

J44

PEG_RX_1

PEG_RX_2

N40

P47

N43

PEG_RX_3

PEG_RX_4

PEG_RX_5

T42

U42

Y42

PEG_RX_6

PEG_RX_7

PEG_RX_8

PCIE GFX

W47

Y37

AA42

PEG_RX_9

PEG_RX_10

PEG_RX_11

AD36

AC48

AD40

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

C617

M47

J41

M46

PEG_TX#_2

PEG_TX#_0

PEG_TX#_1

M40

M42

R48

N38

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

T40

U37

U40

PEG_TX#_7

PEG_TX#_8

AA46

AA37

Y40

PEG_TX#_9

PEG_TX#_11

PEG_TX#_12

PEG_TX#_10

U7-2

GL40

AC23

AC24

AE15

AE20

AE21

AE23

AE24

AE25

AF15

AF20

VCC_AXG_13

VCC_AXG_14

VCC_AXG_15

VCC_AXG_16

VCC_AXG_17

VCC_AXG_18

VCC_AXG_19

VCC_AXG_20

VCC_AXG_21

GFX VCC

VCC_AXG_NCTF_26

VCC_AXG_NCTF_20

VCC_AXG_NCTF_21

VCC_AXG_NCTF_27

VCC_AXG_NCTF_28

VCC_AXG_NCTF_22

VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

AJ16

AJ19

AL16

AL19

AL21

AK21

AK16

AK17

AK19

AK20

NC RSVD

NC_26

BF48

NC_20

BG1

NC_21

BG2

C631

100nF

10V

NC_22

BG4

NC_23

BG45

NC_24

BG47

NC_25

BG48

BH2

NC_27

BH3

NC_19

BF46

AG15

AG21

AH15

AH20

AJ15

AJ21

AL15

VCC_AXG_27

VCC_AXG_28

VCC_AXG_22

VCC_AXG_23

VCC_AXG_24

VCC_AXG_25

VCC_AXG_26

2 OF 5

GFX VCC NCTF

VCC_AXG_NCTF_30

VCC_AXG_NCTF_31

VCC_AXG_NCTF_32

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

VCC_AXG_NCTF_29

U16

U19

AM16

AM17

AM19

AM20

AM21

NC_30

NC_31

NC_32

NC_33

NC_34

NC_28

NC_29

C3

BH5

BH6

BH44

BH46

BH47

BH43

AM14

AM15

AN14

T14

T16

T17

U14

VCC_AXG_29

VCC_AXG_30

VCC_AXG_31

VCC_AXG_32

VCC_AXG_33

VCC_AXG_34

VCC_AXG_35

0904-002489

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

VCC_AXG_NCTF_38

VCC_AXG_NCTF_39

VCC_AXG_NCTF_40

VCC_AXG_NCTF_41

VCC_AXG_NCTF_42

V16

V17

V19

V21

V23

U20

U21

NC_36

NC_37

NC_38D2NC_39

NC_40E1NC_41

NC_35

F1

E48

C46

C48

D47

U15

V15

Y15

Y21

Y24

VCC_AXG_36

VCC_AXG_37

VCC_AXG_38

VCC_AXG_39

VCC_AXG_40

VCC_AXG_41

VCC_AXG_NCTF_47

VCC_AXG_NCTF_48

VCC_AXG_NCTF_43

VCC_AXG_NCTF_44

VCC_AXG_NCTF_45

VCC_AXG_NCTF_46

V26

V28

V24

V25

W16

NC_42

NC_43

RSVD_1

RSVD_2

F48

AH12

AH10

ME Debug Port

2

2

1

10V

10V

100nF

100nF

C600

C615

AA40

AD43

AC46

J42

L46

PEG_TX_0

PEG_TX_1

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

AA16

Y26

VCC_AXG_42

VCC_AXG_NCTF_1

GFX VCC NCTF

VCC_AXG_NCTF_49

VCC_AXG_NCTF_50

VCC_AXG_NCTF_51

VCC_AXG_NCTF_52

VCC_AXG_NCTF_53

VCC_AXG_NCTF_54

W17

W19

W20

W21

W23

W24

RSVD13

RSVD10

RSVD11

RSVD12

RSVD_6

RSVD_7

RSVD_8

RSVD_3

RSVD_4

RSVD_5

AH9

AL34

AK34

AN35

AH13

AM35

2

30

10V

10V

100nF

100nF

C621

C618

M48

M39

M43

R47

N37

T39

U36

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

AC16

AC17

AB17

AA19

AB19

AB16

VCC_AXG_NCTF_6

VCC_AXG_NCTF_7

VCC_AXG_NCTF_5

VCC_AXG_NCTF_4

VCC_AXG_NCTF_3

VCC_AXG_NCTF_2

VCC_AXG_NCTF_56

VCC_AXG_NCTF_57

VCC_AXG_NCTF_58

VCC_AXG_NCTF_59

VCC_AXG_NCTF_60

VCC_AXG_NCTF_55

Y16

Y17

Y19

W26

W28

W25

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_9

B2

B31

BF18

BF23

AY21

BH18

BG23

DRAW

CHECK

APPROVAL

MODULE CODE

PEG1_TXN(3:0)

PEG1_TXP(3:0)

Y39

Y46

U39

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

RSVD_15

RSVD_16

RSVD_17

RSVD_18

M1

K12

M36

P3.3V

AA36

AA39

AD42

PEG_TX_12

PEG_TX_13

PEG_TX_14

RSVD_19

RSVD_20

RSVD_21

T24

N36

R33

R590

AD46

PEG_TX_15

PCIE GFX

RSVD_22

T33

TW.Kim

HJ.Kim

SJ.Park

undefined

DMICLKMEPMMISC

10K

DEV. STEP

REV

LAST EDIT

PEG_COMPI

PEG_COMPO

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

PM_SYNC#

PM_DPRSTP#

DPRSLPVR

PWROK

RSTIN#

THERMTRIP#

PM_EXT_TS#_0

PM_EXT_TS#_1

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

TSATN#

MCH3_CLKREQ#

E

TETAD

LTI

9/23/2008

ADV2nd

1.0

1

T37

T36

B33

B32

G33

F33

E33

C34

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B38

A38

E41

F41

F43

E43

AH37

AH36

AN36

AJ35

AH34

R29

B7

R32

AT40

AT11

T20

N33

P32

N28

M28

G36

E36

K36

H36

B12

MCH_CANTIGA_GM_DDR2

October 05, 2009 20:00:56 PM

MCH1_COMPIO_R_MN

DMI1_TXN_0

DMI1_TXN_1

DMI1_TXN_2

DMI1_TXN_3

DMI1_TXP_0

DMI1_TXP_1

DMI1_TXP_2

DMI1_TXP_3

DMI1_RXN_0

DMI1_RXN_1

DMI1_RXN_2

DMI1_RXN_3

DMI1_RXP_0

DMI1_RXP_1

DMI1_RXP_2

DMI1_RXP_3

CLK1_DREFCLK

CLK1_DREFCLK#

CLK1_DREFSSCLK

CLK1_DREFSSCLK#

CLK1_MCH3GPLL

CLK1_MCH3GPLL#

CHP3_CL_CLK_0

CHP3_CL_DATA_0

KBC3_PWRGD

CHP3_CL_RST_0#

MCH1_CL_VREF_MN

35-C1

PLT3_RST#_R_MN

MCH3_EXTTS0#_MN

MCH3_EXTTS1#_MN

R585

Bremen-UL

CANTIGA (2/5)

R589

R598

56

1

1%49.9

1608 size

CHP3_PM_SYNC#

CPU1_DPRSTP#

CHP3_DPRSLPVR

KBC3_PWRGD

CPU1_THRMTRIP#

To protect ESD

100

R634

0

R591

0

R597

nostuff

nostuff

10K

R593

10K

R592

4.7K

MCH3_HDMI_CLK

MCH3_HDMI_DATA

MCH3_CLKREQ#

MCH3_ICHSYNC#

P1.05V

SAMSUNG

PART NO.

PAGE

P1.05V_PEG

P1.05V

C649

100nF

10V

C646

0.1nF

50V

1%

PLT3_RST#

MCH3_EXTTS0#

MCH3_EXTTS1#

P3.3V

1%

1%

P3.3V

1%

C689

0.1nF

50V

nostuff

To protect ESD

ELECTRONICS

BA41-xxxxxA

14 50

OF

D

C

R621

1K

1%

R622

499

1%

B

nostuff

A

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

D

4

MEM1_ABS(2:0)

MEM1_ADM(7:0)

MEM1_ADQS#(7:0)

MEM1_ADQS(7:0)

C

MEM1_AMA(14:0)

MEM1_ACAS#

MEM1_ARAS#

MEM1_AWE#

MEM1_CS0#

MEM1_CS1#

MEM1_ODT0

B

P1.8V_AUX

R648

80.6

1%

R649

80.6

1%

MEM1_ODT1

MEM1_CKE0

MEM1_CKE1

CLK1_MCLK0

CLK1_MCLK0#

CLK1_MCLK1

CLK1_MCLK1#

MCH1_SM_RCOMP_MN

MCH1_SM_RCOMP#_MN

P1.8V_AUX

R633

1K

10nF->100nF

1%

C703

C704

100nF

2200nF-X5R

10V

R646

A

3.01K

1%

R647

1K

1%

C702

100nF

10V

10V

C701

2200nF-X5R

10V

nostuff

nostuff

4

MCH1_SM_RCOMP_V_OH_MN

MCH1_SM_RCOMP_V_OL_MN

Route as short as possible

MEM1_ADQ(63:0)

0

BD21

SA_BS_0

1

BG18

SA_BS_1

2

AT25

SA_BS_2

0

AM37

SA_DM_0

1

AT41

SA_DM_1

2

AY41

SA_DM_2

3

AU39

SA_DM_3

4

BB12

SA_DM_4

5

AY6

SA_DM_5

6

AT7

SA_DM_6

7

AJ5

SA_DM_7

0

AJ43

SA_DQS#_0

1

AT43

SA_DQS#_1

2

BA44

SA_DQS#_2

3

BD37

SA_DQS#_3

4

AY12

SA_DQS#_4

5

BD8

SA_DQS#_5

6

AU9

SA_DQS#_6

7

AM8

SA_DQS#_7

0

AJ44

SA_DQS_0

1

AT44

SA_DQS_1

2

BA43

SA_DQS_2

3

BC37

SA_DQS_3

4

AW12

SA_DQS_4

5

BC8

SA_DQS_5

6

AU8

SA_DQS_6

7

AM7

SA_DQS_7

0

BA21

SA_MA_0

1

BC24

SA_MA_1

2

BG24

SA_MA_2

3

BH24

SA_MA_3

4

BG25

SA_MA_4

5

BA24

SA_MA_5

6

BD24

SA_MA_6

7

BG27

SA_MA_7

8

BF25

SA_MA_8

9

AW24

SA_MA_9

10

BC21

SA_MA_10

11

BG26

SA_MA_11

12

BH26

SA_MA_12

13

BH17

SA_MA_13

14

AY25

SA_MA_14

BD20

SA_CAS#

BB20

SA_RAS#

AY20

SA_WE#

BA17

SA_CS#_0

AY16

SA_CS#_1

BD17

SA_ODT_0

AY17

SA_ODT_1

BC28