Samsung np-r720 Schematics

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

D D

3

4

2

3

1

2

1

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG PROPRIETARY

SAMSUNG ELECTRONICS CO’S PROPERTY.

PROPRIETARY INFORMATION THAT IS

DRAW

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

CHECK

DATE

CANNES-EXT

DEV. STEP

TITLE

1.0

PART NO.

SAMSUNG

APPROVAL

MAIN

ELECTRONICS

X

B B

SEC Mobile R & D

CANNES-EXT(GFX:AMD)

Montevina Platform

Chip Set :

CPU :

Intel Penryn

Remarks :

Model Name :

PCB Code :

PBA Name :

Revision :

Dev. Step :

Graphic :

T.R. Date :

BA41-xxxxxA

M96/M92/gDDR3 1G

2009.04.21

MP

Design

APPROVAL

MODULE CODE

CHECK

A

REV

LAST EDIT

A

C

PAGE OF

C

4

Owner : Signature :

WK.YEO

SH.LEE

KK.BIN

04/21/2009

MP

REV 1.0

December 05, 2008 20:58:56 PM

BA41-#####A

1 65

CANNES-EXT

MAIN

COVER

D:/users/mobile23/Cannes/CANNE-ATI_081204_MAIN

PM45 & ICH9M

- This Document can not be used without Samsung's authorization -

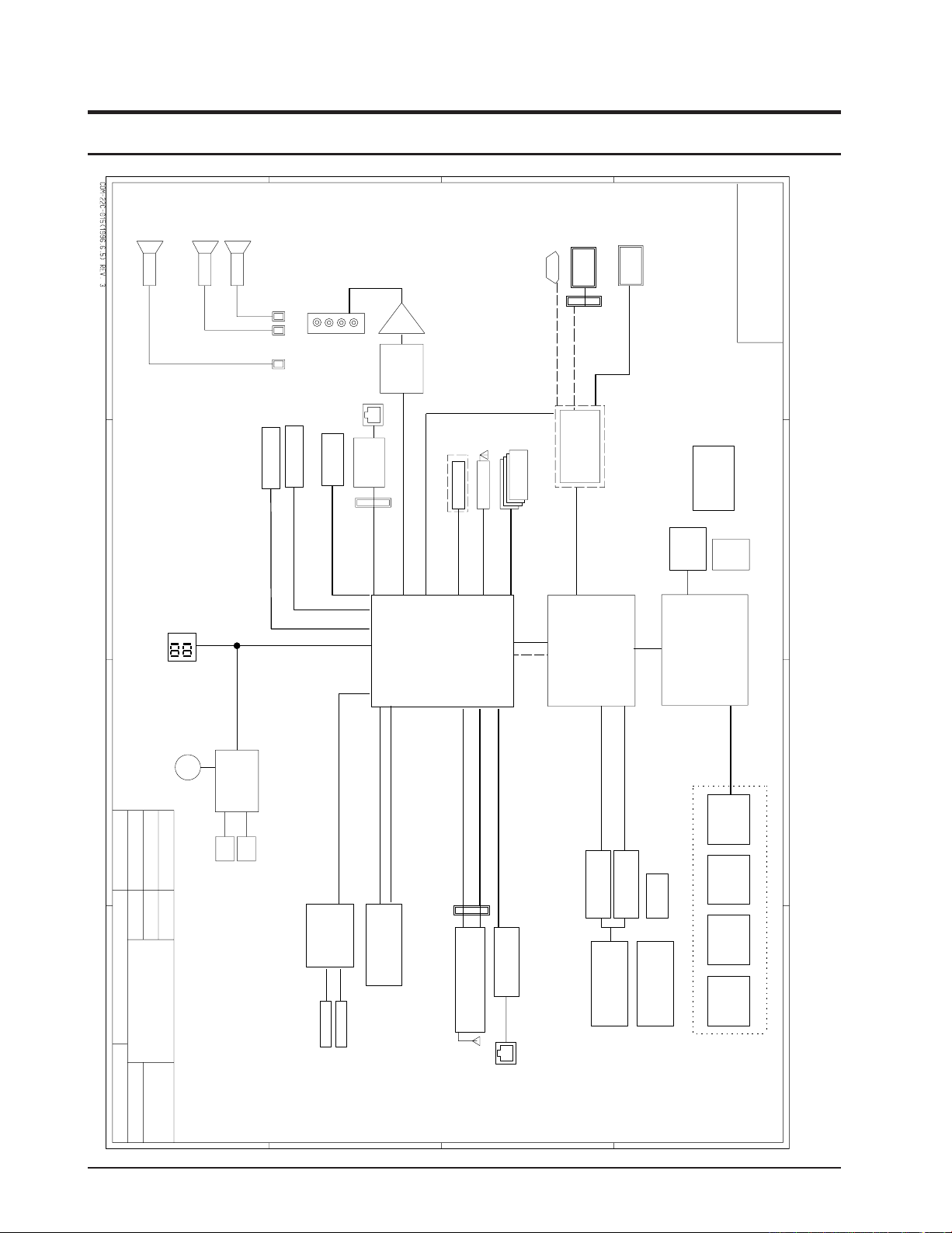

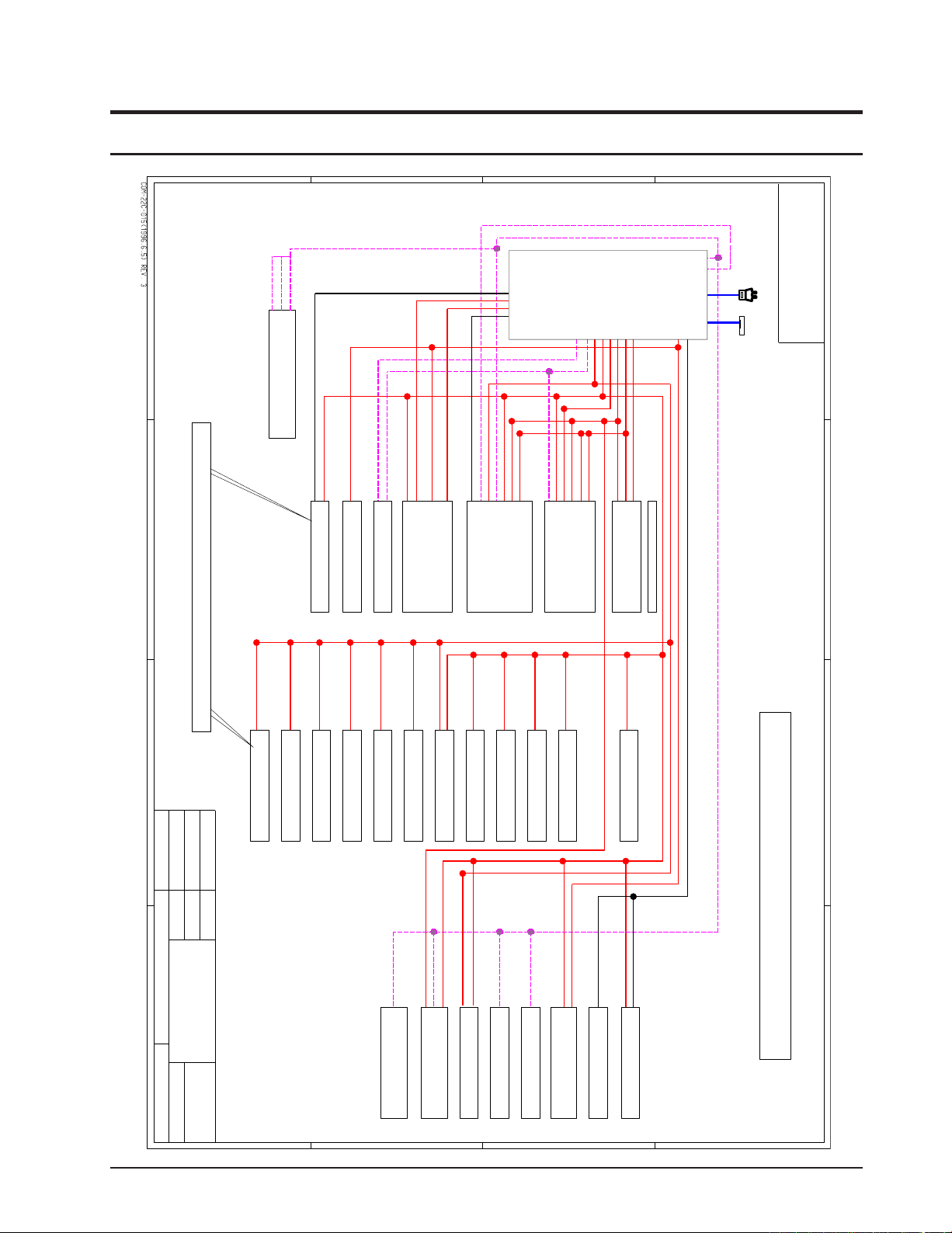

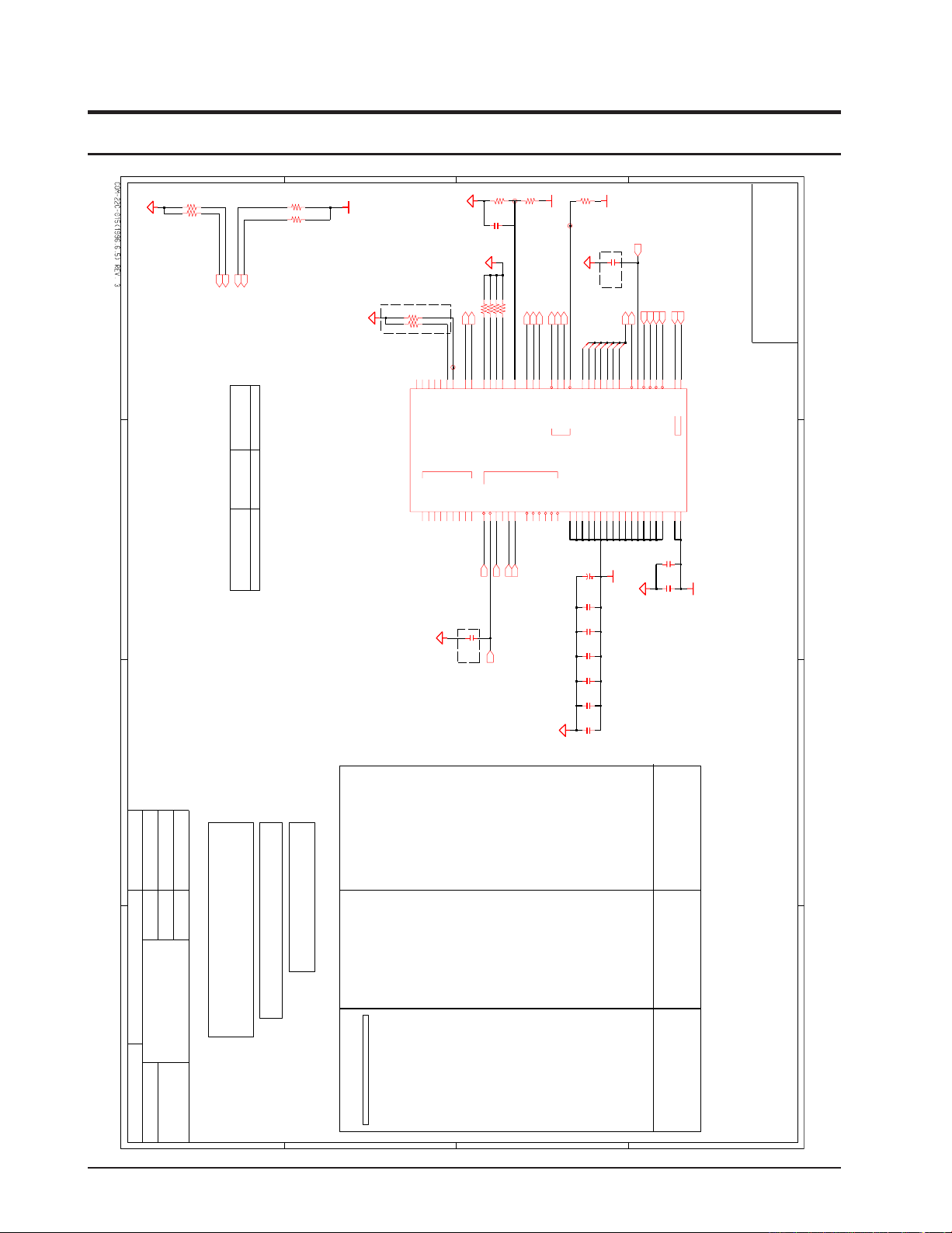

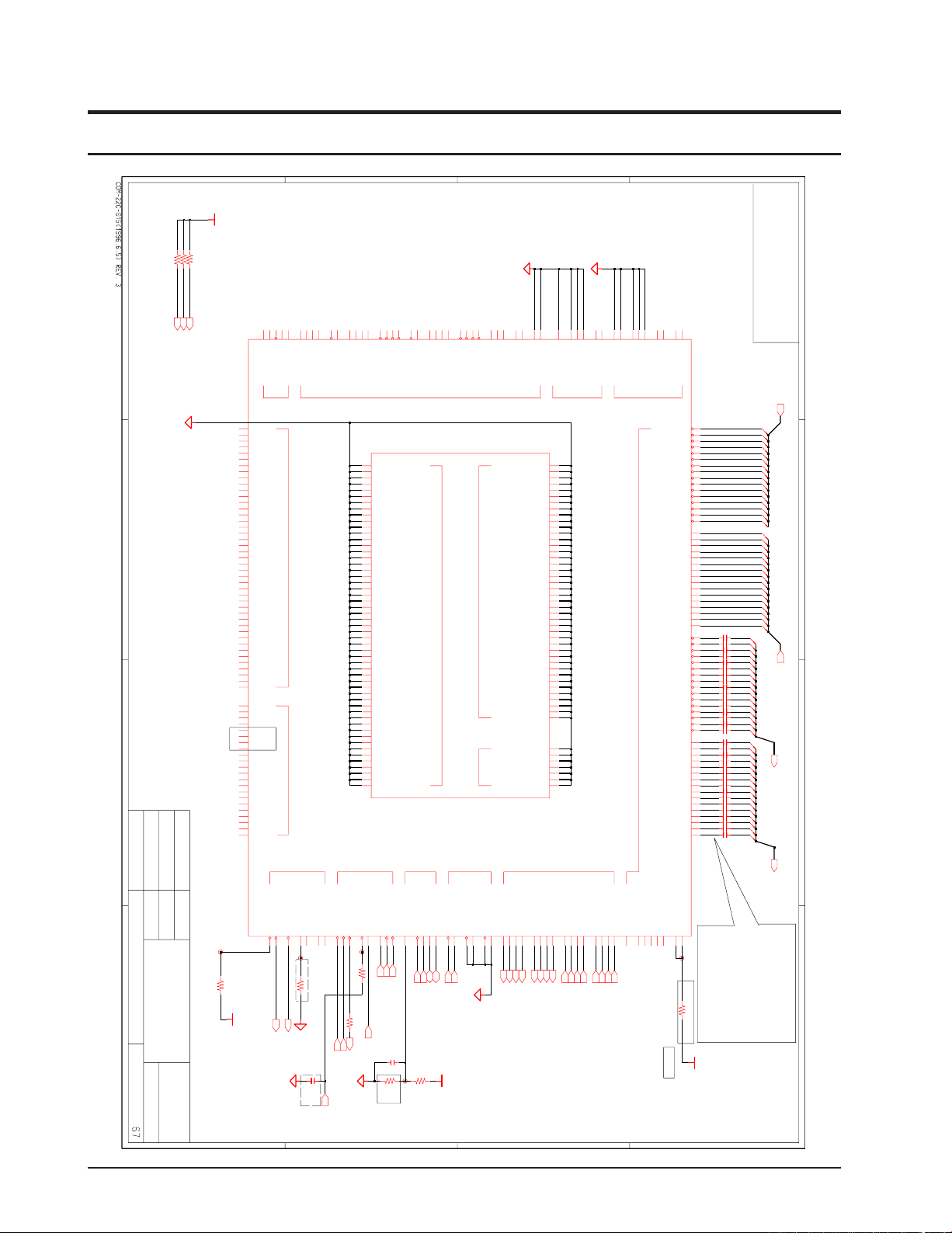

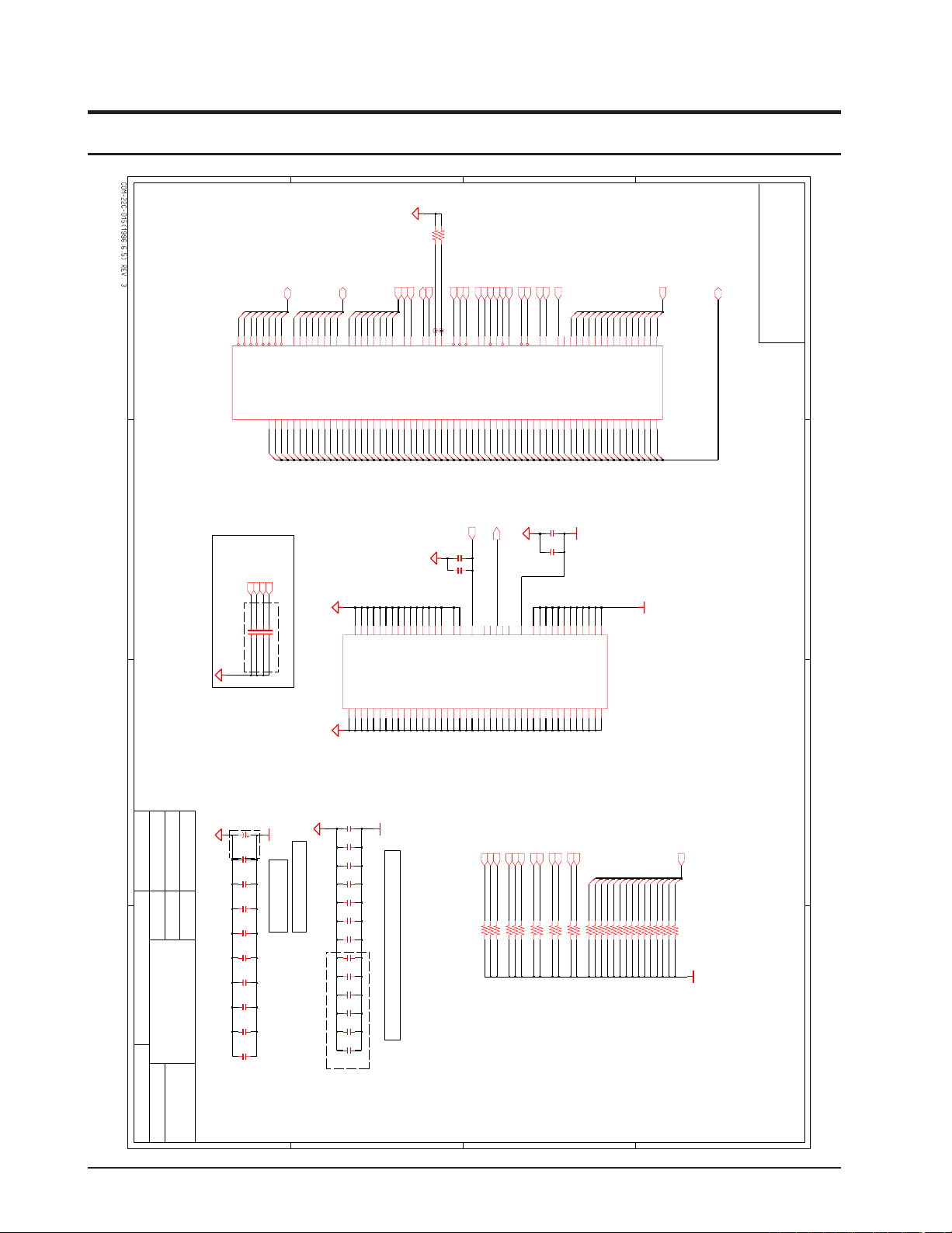

8. Block Diagram and Schematic

R720

8-1

8-2

8. Block Diagram and Schematic

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

R720

Samsung

Confidential

2P

Woofer

gDDR3 512MB/1GB

USB 1

TITLE

KBD

SAMSUNG

PART NO.

2P

A

SAMSUNG ELECTRONICS CO’S PROPERTY.

DEV. STEP

LAST EDIT

REV

1

MODULE CODE

DRAW

CHECK

(TBD)

ELECTRONICS

B

4

Lane 4

OPTION

APPROVAL

3

2

A

SPKR R

ANT

Termination

DDR II

CLINK

Lane 1

x4, 1.5V

Dual channel

Bluetooth

C

PG 54

HD Audio

12P

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

MMC

Mini Card 1

SATA

SODIMM 1

DDR II

PCIE x1

Circuit

1329 FCBGA

ICH9-M

Cantiga-PM

ANT

HP

Penryn-6M

676 BGA

FAN

L2 Cache : 6/3MB

80 Port

800/1067 MT/S

MIC-IN

CK-505

FSB

PG 30 - 34

Marbell

SODIMM 0

ALC272

TMKBC (TBD)

HDMI

Ext. PEG

CPU

DC/DC

IMVP-6

Thermistor

External Graphics

LCD

HD Audio

ON BOARD

Channel B (Reverse)

Channel A (Standard)

CRT

D

1

DDR II 800

LPC

SPI

HDAUDIO

SAMSUNG PROPRIETARY

Camera

PCIE x1

RJ45

SATA 1

SATA ODD

USB 5

Express Card

USB 7

DATE

DC/DC

DDR II 800

PROPRIETARY INFORMATION THAT IS

24

PM45

FSB 1067

3

C

THIS DOCUMENT CONTAINS CONFIDENTIAL

EXCEPT AS AUTHORIZED BY SAMSUNG.

CRT

3 IN 1

AU6336

PAGE OF

Lane 3

USB 4

HD Audio

D

B

PEG x16

Direct Media Interface

MICOM

H8S-2110B

LED

Audio

HDD

3.3V LPC, 33MHz

SPI ROM

SATA 0

High Definition Audio

USB 0,2,6

RJ11

SD(SDHC)

USB 8

Charging

Touch

PAD

LCD

VCCP / DC-DC

Mobile Processor

MDC

Modem

PCIE x1

Smart

Battery

Module

Clocking

CPU

478pin

USB 0,2,6

DDR II Power

Aud.

AMP

M96 / M92

2P

SPKR L

D:/users/mobile23/Cannes/CANNE-ATI_081204_MAIN

BLOCK DIAGRAM

CANNES-EXT

652

BA41-#####A

December 05, 2008 20:58:56 PM

REV 1.0

ADV1

12/05/2008

undefined

JG GOO

GS CHO

YH KIM

MAIN

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

DRAW

CHECK

APPROVAL

MODULE CODE

DATE

DEV. STEP

REV

LAST EDIT

TITLE

PART NO.

PAGE OF

SAMSUNG

ELECTRONICS

BOARD INFORMATION

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

A A

B B

C C

D D

4

4

3

3

2

2

1

1

See rev notes for more information.

PCI Devices

Devices IDSEL#

Cardbus

USB

Hub to PCI

LPC bridge/IDE/AC97/SMBUS

Internal MAC

AD25

AD29(internal)

AD30(internal)

AD31(internal)

AD24(internal)

REQ/GNT#

3

Interrupts

A,B,C

USB2.0 #0 (USB0) : A

B

USB2.0 #1 (USB1) : D

USB2.0 #2 (USB4) : C

-

-

E

---

I C / SMB Address

Devices Address

ICH8-m

CPU Thermal Sensor

SODIMM0

SODIMM1

Master

0111 101x

1010 000x

1010 010x

Hex-7Ah

A0h

Bus

SMBUS Master

Thermal Sensor

--Clock, Unused Clock Output Disable

A4h

D2h

2

CK-505M (Clock Generator) 1101 001x

Voltage Rails

AC Link - B-

USB PORT Assign

PORT # ASSIGNED TO

SYSTEM PORT 0

SYSTEM PORT 1

Bluetooth

012

3

NC4

5

LCD Pannel Detect

Devices Resolution PANNEL_DETECT_0

Crystal / Oscillator

32.768KHzCrystal

TYPE FREQUENCY DEVICE

ICH8-M

USAGE

Real Time Clock

10MHzCrystal MICOM HD64F2169/2160

25MHzCrystal LAN Intel LAN

14.318MHzCrystal CLOCK-Generator CK-505

NC

6

7

USB2.0 #3 (USB5) : E

USB2.0 #4 (EHCI) : H

Camera

(TBD)

PCI Express Assign

PORT # ASSIGNED TO

NC

NC

012

3

Mini Card 2 (ROBSON or DVB-T)45Mini Card 1 (WLAN)

LOM

NC

GLAN - -

8

9 NC

Mini PCI Express 2

NC

-30hThermal Sensor on SODIMM0 0011 000x

0011 010x 34h -Thermal Sensor on SODIMM1

Primary DC system power supply (7 to 21V)

1.5V switched power rail (off in S3-S5)

VDC

VCC_CORE

P1.5V

P1.05V (VCCP)

Core Voltage for CPU

3.3V switched on power rail (off in S4-S5)

3.3V switched power rail (off in S3-S5)

5.0V switched power rail (off in S3-S5)

1.8V power rail for DDR (off in S4-S5)

P3.3V_AUX

P3.3V

P5.0V

P1.8V_AUX

P3.3V_MICOM

P0.9V

VTT for CPU, Crestline & ICH8-M

1.8V switched power rail (off in S3-S5)P1.8V

5.0V switched on power rail (off in S4-S5)P5.0V_AUX

GFX_CORE Core Voltage for GPU

WK.Yeo

SH.Lee

KK.Bin

undefined

12/05/2008

PV

REV 1.0

March 10, 2009 07:55:21 AM

BA41-01060A

3 67

CANNES

MAIN

BOARD INFO

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

3.3V always power rail (for Micom)

0.9V power rail for DDR (off in S3-S5)

P5.0V_ALW 5.0V always power rail

SYSTEM PORT 2

F

REVISION HISTORY

- This Document can not be used without Samsung's authorization -

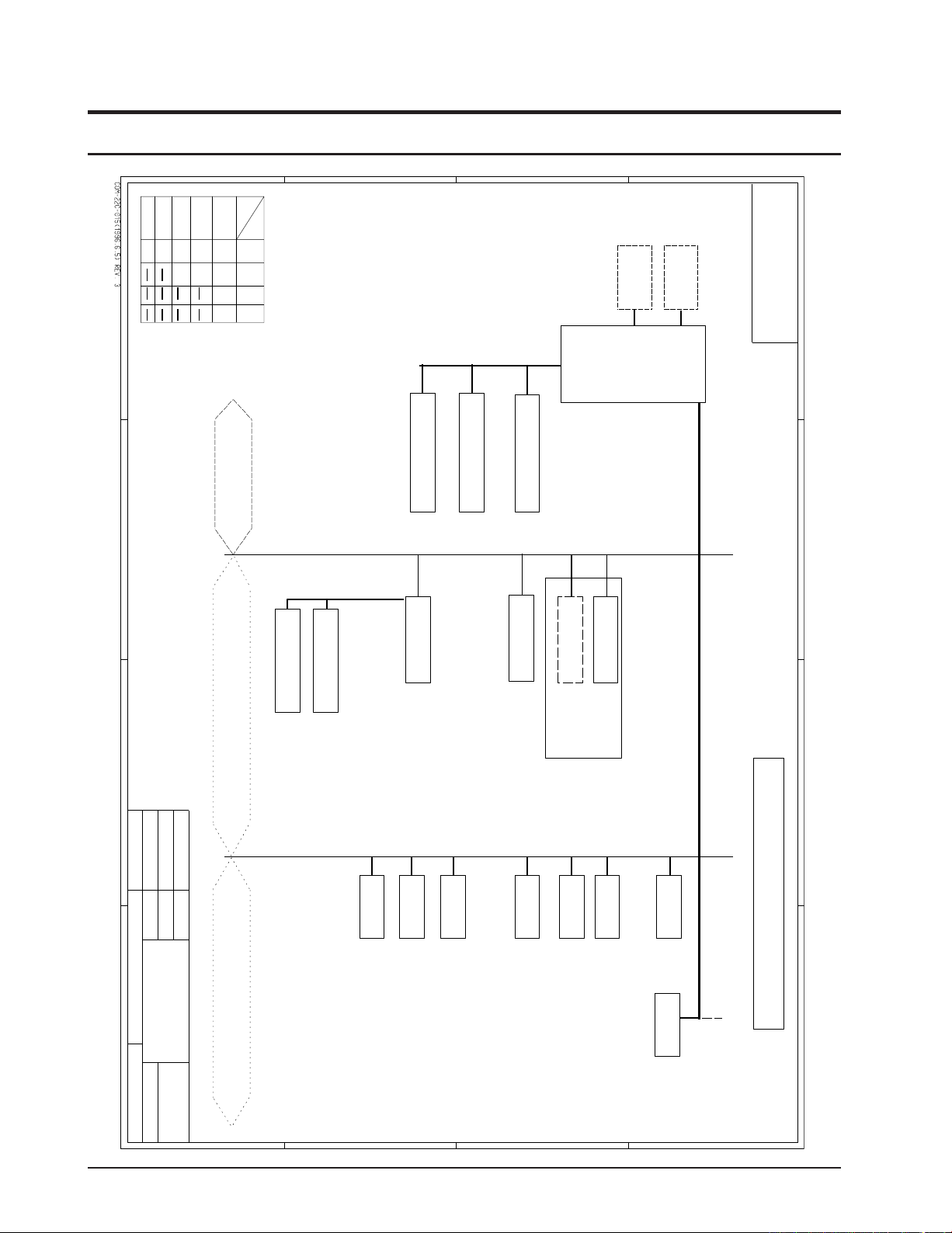

8. Block Diagram and Schematic

R720

8-3

8-4

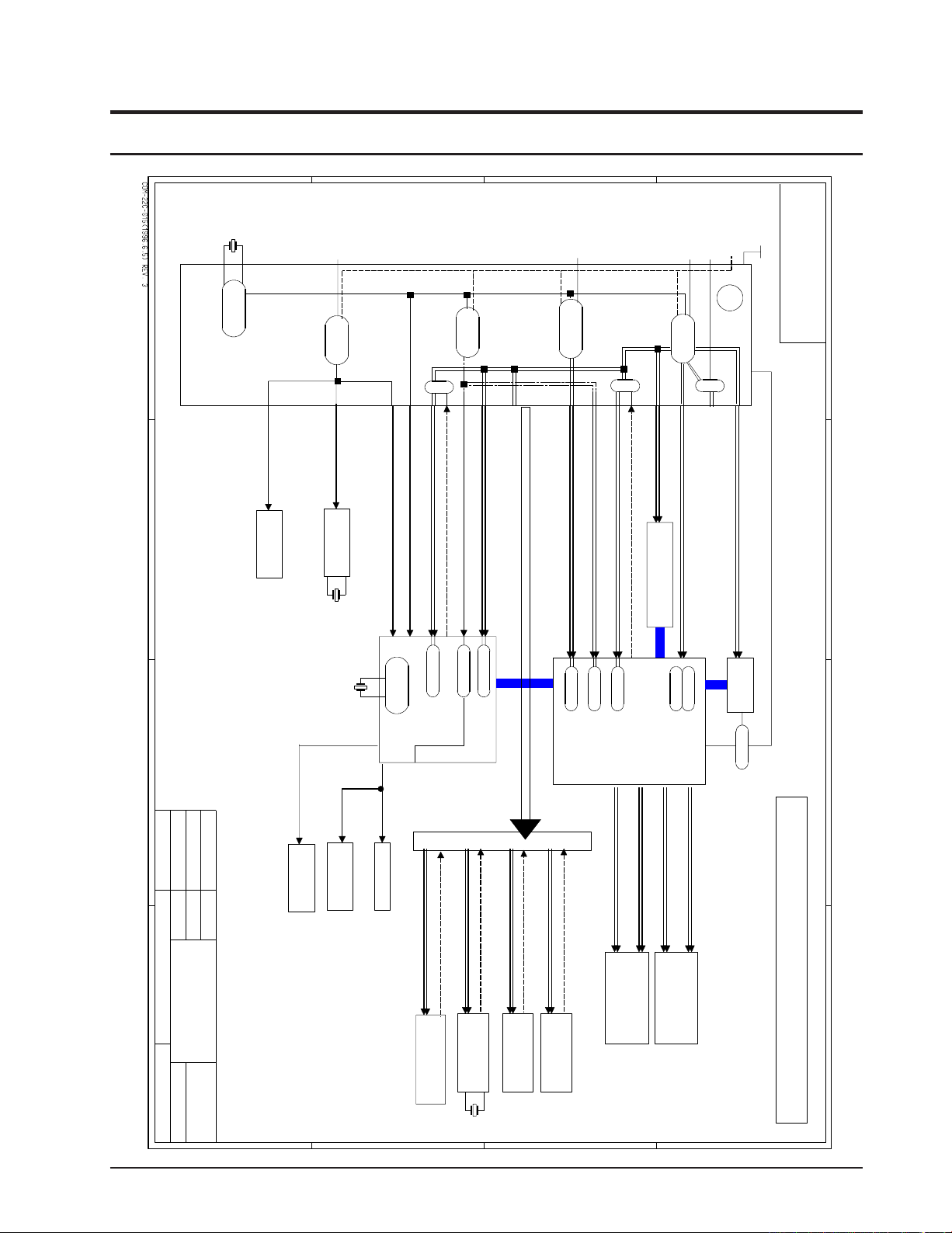

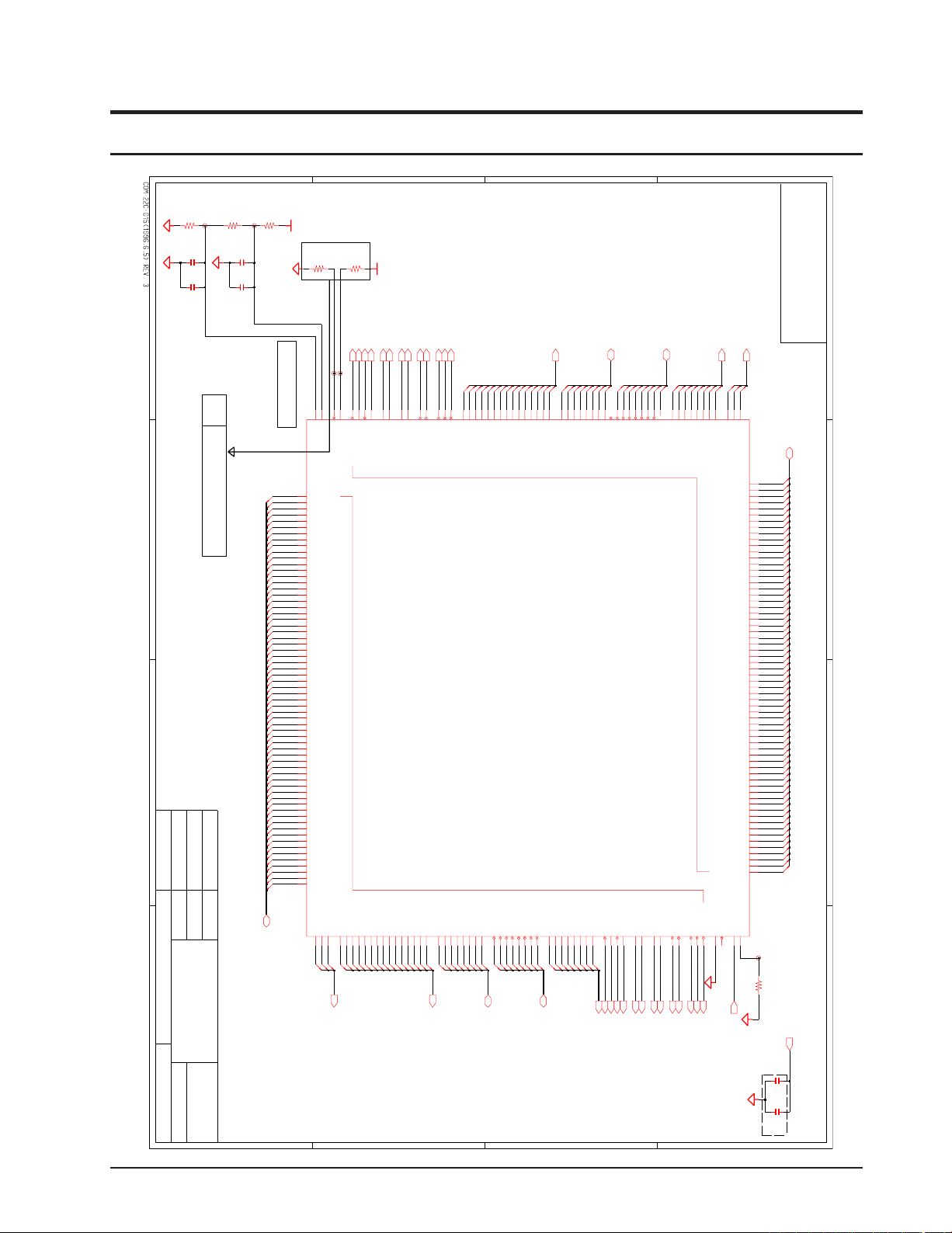

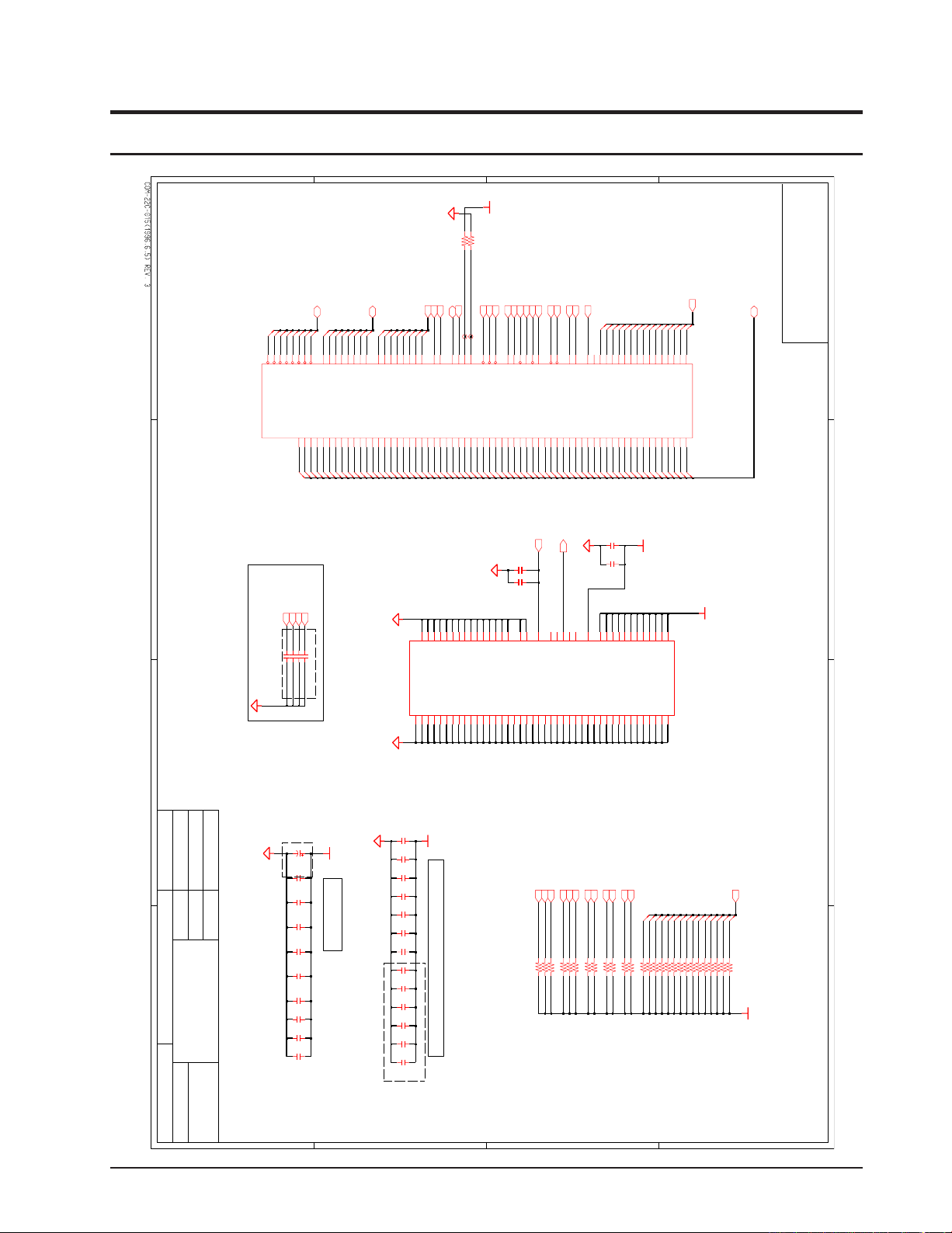

8. Block Diagram and Schematic

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

R720

Samsung

Confidential

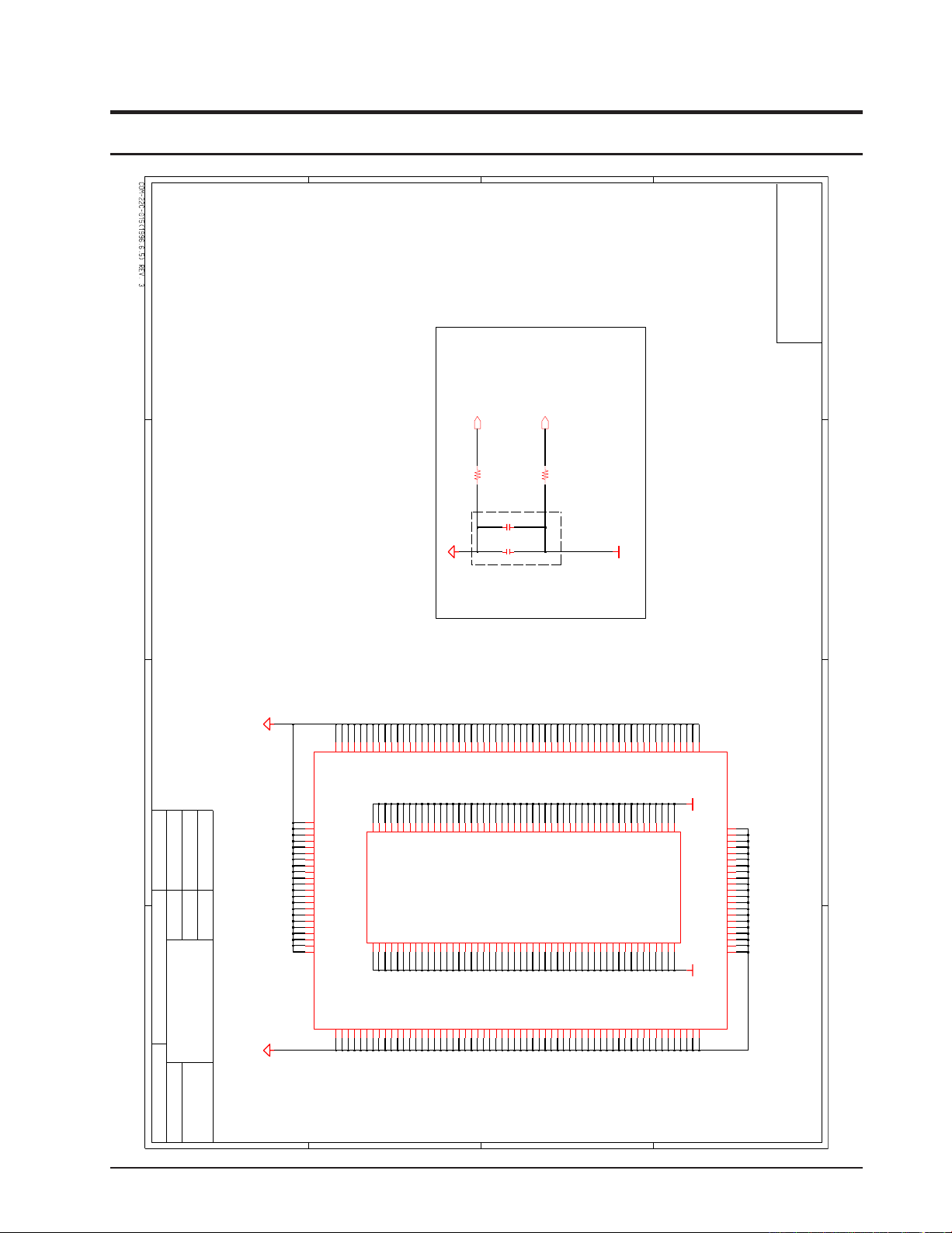

MDC

EXPRESS

LAN

ON

ON

SODIMM (DDR II)

ICH

ICH8-M

P3.3V_AUX

P5V_AUX

P5.0V

VDC

P1.5V

P1.8V

P1.8V_AUX

P12.0V_ALW

P1.1V_PWRGD

MEMORY

HDMI

P1.05V

ICH9-M

POWER DIAGRAM

(CHP3_S4_STATE*)

TOUCHPAD CAMERA

P3.3V_MICOM

ON

KBC3_SUSPWR

P3.3V

ICH9-M

PENRYN

ICH9-M

S3

(CHP3_SLPS3*)

GDDR-3 for PEG

DDR II-Termination

LCD

PEG

MICOM

Battery DC

S3

Cantiga

CRT

ODD

OF

PART NO.

S0

P2.5V_LAN

ON

ON

SPI

CLOCK

CHECK

A

State

ESATA-REPEATER

HDD

PEG

PENRYN

ON

+V*A(LWS)

P5.0V_ALW

CLOCK

KBC3_PWRON

THERMAL SENSOR

PENRYN

Rail

ON

AUDIO

P1.2V_LAN

MICOM

LOM

AC Adapter

Cantiga

1

LIDSWITCH

REV

EXPRESS CARD

HSPA

P1.8V_LAN

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

TITLE

B

D

C

EGFX_CORE

PEG

S5-S4

ON

BLUETOOTH

USB

3

ON

VPU_CORE

KBC3_VRON

P0.9V

+V*LAN

4

LAST EDIT

DRAW

+0.9V

S0

ICH9-M

S4

+V* (CORE)

2

SAMSUNG

ELECTRONICS

PAGE

C

+1.8V_AUX

+V*AUX

+V

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

APPROVAL

ON

S5

Power On/Off Table by S-state

WLAN

MODULE CODE

DATE

DEV. STEP

LEDS

AUDIO

MCH

CANTIGA

ICH

THERMAL SENSOR

23

DDR II-Termination

P0.9V

HSPA

2IN1

EXPRESS

B

4

D

WK.Yeo

SH.Lee

KK.Bin

undefined

12/05/2008

PV

REV 1.0

March 10, 2009 07:55:21 AM

BA41-01060A

4 67

CANNES

MAIN

POWER DIAGRAM

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

A

EXCEPT AS AUTHORIZED BY SAMSUNG.

1

LAN

LAN

SAMSUNG ELECTRONICS CO’S PROPERTY.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

ELECTRONICS

3.3V

0.9V

3.3V_AUX

1

D

1 A (TBD)

THIS DOCUMENT CONTAINS CONFIDENTIAL

3.3V

1.13 A (TBD)

5V

0.374 A (TBD)

3.3V

CHECK

1.05V (VCCP)

SAMSUNG PROPRIETARY

3.3V

DEV. STEP

19V (VDC INV)

5V_AUX

1.5V

PEG

ICH9-M

OF

0.001 A (TBD)

EXCEPT AS AUTHORIZED BY SAMSUNG.

Cantiga

Rev. 0.6 (060920)

SD Card

MODULE CODE

SATA

Penryn-6M

3.3V

C

6.53 A (TBD)

PART NO.

1.5V

4

3.3V

1.8V_AUX

ITP

DATE

MICOM 3V

A

0.13 A (TBD)

B

1.5V

PROPRIETARY INFORMATION THAT IS

1.5 A (TBD)

5V

0.15 A (TBD)

POWER RAILS ANALYSIS

FAN

3

gDDR3

2

0.67 A (TBD)

REV

1.8V

APPROVAL

3.3V

4

2 A (TBD)

0.125 A (TBD)

LAN

0.33 A (TBD)

1.05V (VCCP)

A

3.1 A (TBD)

SAMSUNG

5V

1.8V_AUX

CPU CORE ( TBD A )

4 A (TBD)

0.01 A (TBD)

2.43A (TBD)

RTC_Battery

3

0.015 A (TBD)

D

0.08 A (TBD)

1.8V

0.1 A (TBD)

0.6 A (TBD)

3.3V (LCD 3V)

2.4A (TBD)

0.75 A (TBD)

SAMSUNG ELECTRONICS CO’S PROPERTY.

3.3V

3.3V_AUX

GMCH

LAN (88E8055)

4.48 A (TBD)

5.0V ( TBD A )

0.001 A (TBD)

0.5 A (TBD)

LAST EDIT

1.5 A (TBD)

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

0.5 A (TBD)

1.25V

HD Audio

3.3V_AUX

( ~ 2.0 W )

0.08 A (TBD)

Battery

0.209 A (TBD)

5V

TITLE

5V

3.3V

0.2 A (TBD)

ODD

P1.2V_LAN

0.16 A (TBD)

VGA CORE (TBD A)

17.75 A (TBD)

1.5 A (TBD)

B

Audio AMP

DRAW

MICOM 3V

1.2V (PEX IO)

MICOM 3V ( TBD A )

41 A (TBD)

P1.8V/2.5V_LAN

4.5 A (TBD)

5V

2

3.3V

PAGE

3.3V ( TBD A )

DDR-2

(Dual slots)

3.3V

1.05V

KeyBoard

P3.3V_AUX

1.8V

3.3V

C

Value by Datasheet/Application notes

SPI

( ~ 5.0 W )

0.75A (TBD)

0.29 A (TBD)

0.67 A (TBD)

0.9V( TBD A )

3.3V_AUX

1.05V ( TBD A )

1

( 35 W )

7.7 A (TBD)

0.06 A (TBD)

SATA HDD

0.07 A (TBD)

Sensor

3.3V

MDC

5.0V_AUX ( TBD A )

3.79 A (TBD)

VDC INV ( TBD A )

1.05V (MCH CORE)

CLOCK

1.0V-1.1V (EGFX CORE)

Touch Pad

0.22 A (TBD)

LCD

5V

PEX IO (TBD A)

KBC

1.8V_AUX ( TBD A )

1.05V

0.1 A (TBD)

1.5V

PWR LED

5V

3.3V_AUX ( TBD A )

0.2 A (TBD)

0.08 A (TBD)

5V

(Value by measurement)

1.75 A (TBD)

1.5V ( TBD A )

0.006 A (TBD)

0.1 A (TBD)

0.25 A (TBD)

Adapter

0.5 A (TBD)

1.25V ( TBD A )

USB (x 3)

(8 - 8.5 W )

CPU CORE

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

POWER RAILS

MAIN

CANNES

675

BA41-01060A

March 10, 2009 07:55:21 AM

REV 1.0

PV

12/05/2008

undefined

KK.Bin

SH.Lee

WK.Yeo

1.8V ( TBD A )

Thermal

Mini Card X 2

KBD LED

RTC_Battery

220V

3.3V_AUX

- This Document can not be used without Samsung's authorization -

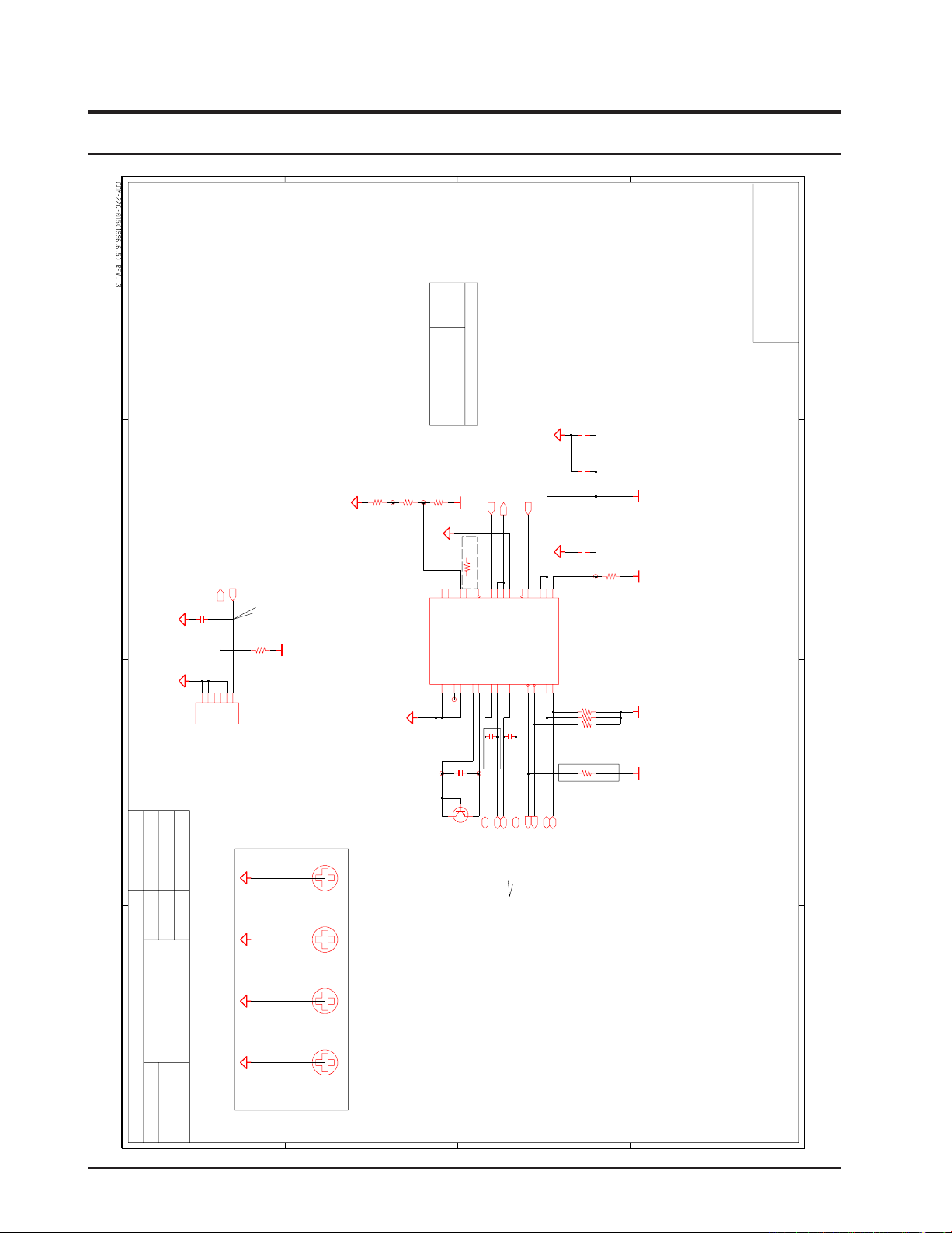

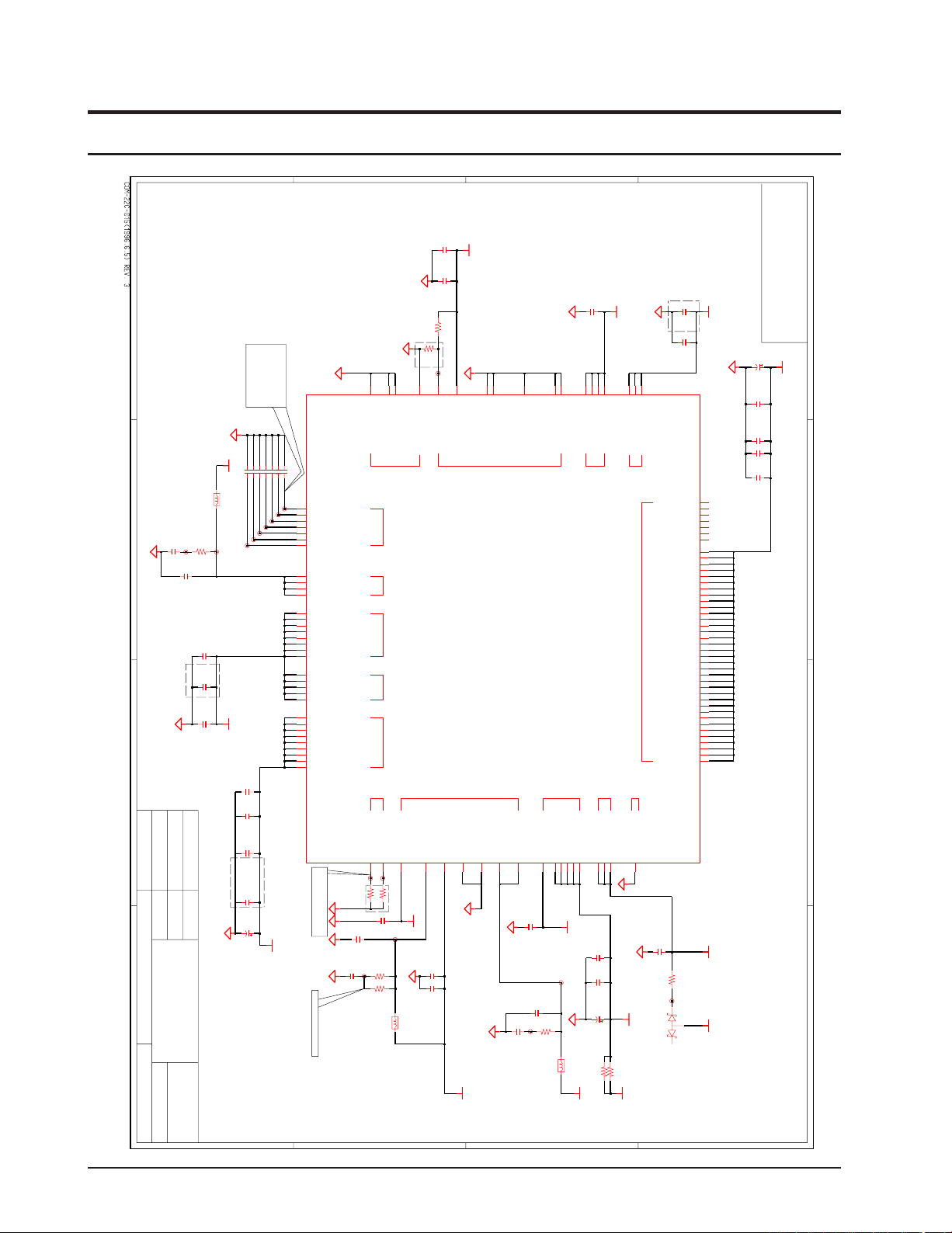

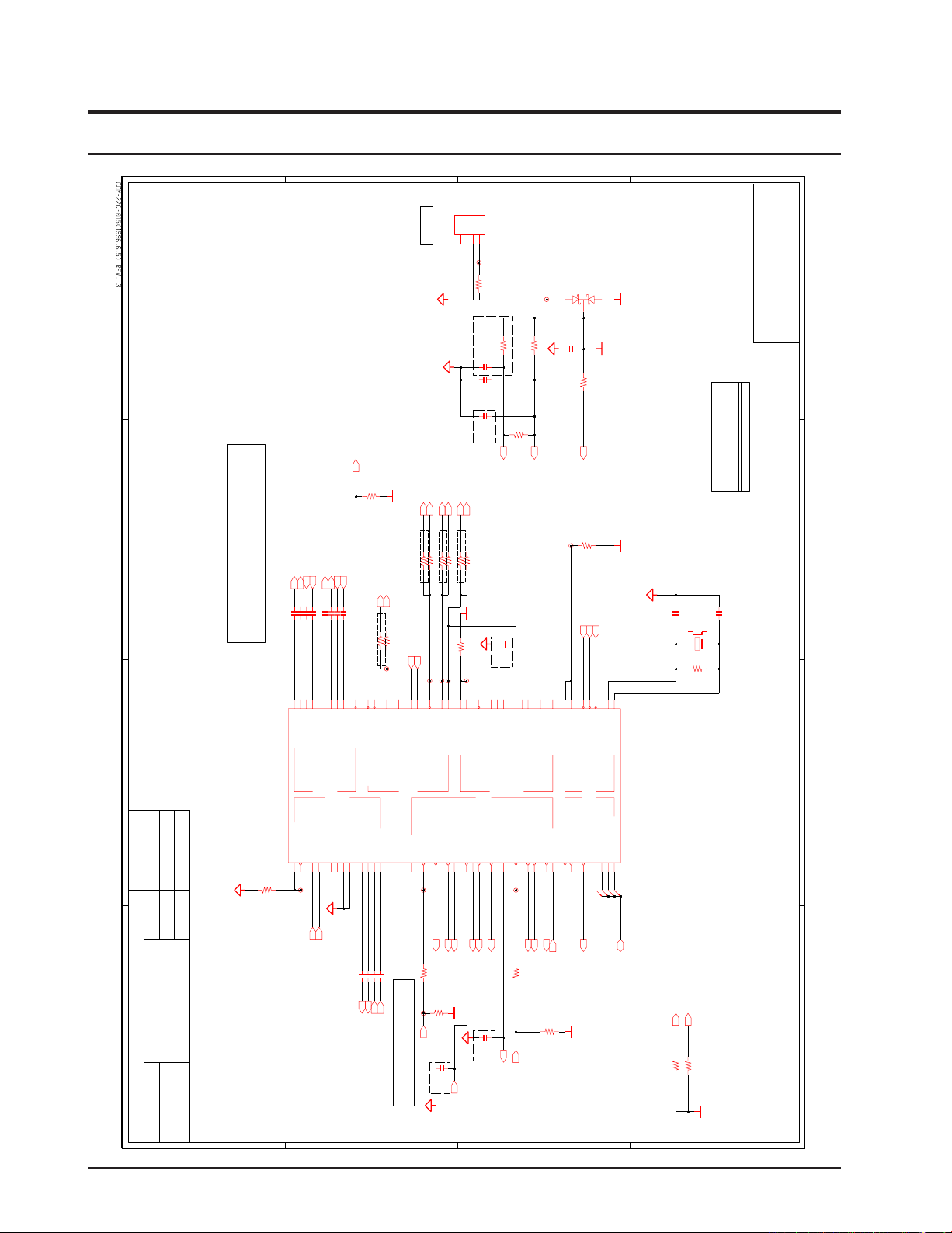

8. Block Diagram and Schematic

R720

8-5

8-6

8. Block Diagram and Schematic

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

R720

Samsung

Confidential

1

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

DRAW

CHECK

APPROVAL

Sheet 50

DATE

DEV. STEP

REV

MODULE CODE

TITLE

PART NO.

PAGE

LAST EDIT

SAMSUNG

ELECTRONICS

POWER SEQUENCE

OF

A A

B

Rev. 0.7

C C

D

B

4

4

3

D

2

2

1

3

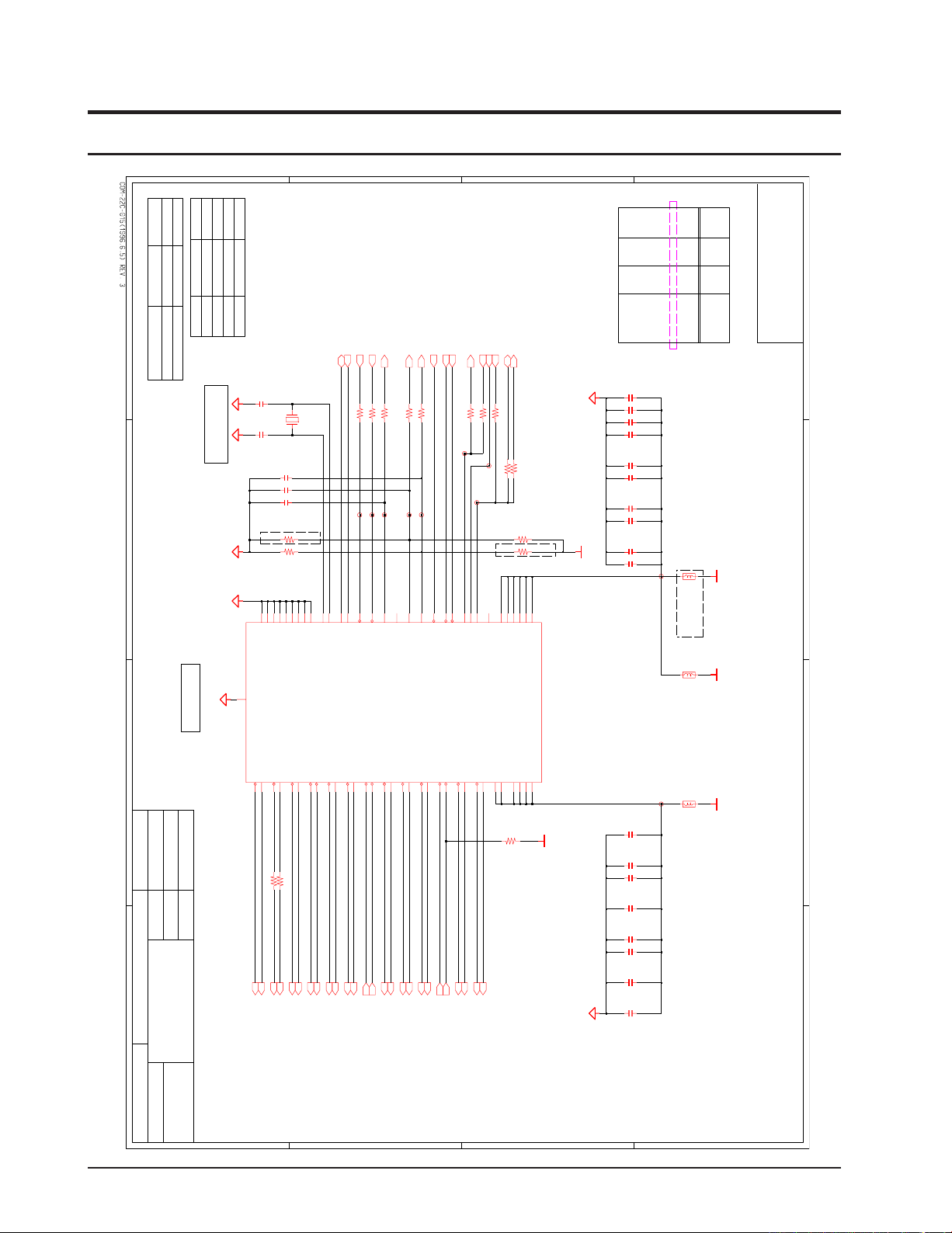

ICH8-M

KBC

RTC

INTVRMEN

AP6680A

CPU

GMCH

Battery

CHP3_RTCRST#

4) POWER_SW*

6) P1.8V_AUX

VRM

9) KBC3_PWRON

10-1) P3.3V

6) MEM1_VREF

5) KBC3_SUSPWR

11) VCCP3_PWRGD

19) PCI3_RST*

20) CPU1_CPURST*

10-1) ICH_CORE (P1.05V)

18) CPU1_PWRGDCPU

POWER

S/W

14) VCC_CORE

DDR3

Memory

CK-505

PCI

P3.3V_AUX & P5V_AUX

SC486

DDR2 POWER

PRTC_BAT

LOM

6-1) P1.8V/P2.5V_LAN

BCP69

10-2) P0.9V

CPU

6) P1.8V_AUX

19) PLT3_RST*

6-1) P1.2V_LAN

10-1) P1.05V

10-1) P1.5V

Sheet 46-47

6) P3.3V_AUX

Sheet 8

TPS51120

AP6680A

Sheet 46

VRMPWRGD

PWROK

Sheet 40

16-1) Clock Running

Sheet 22-25

DC/DC B’d

Sheet 10-12

Sheet 40

2

3

4

1

Sheet 15-19

Sheet 20-21

Marvell

6

PRTC

7) P1.05V_AUX

20

LAN100_SLP

AP4435

10) P5.0V

5

ISL6227

ICSL6256

Adapter

Battery

AC_DC / Battery

Devices

10) P1.1

10) P1.05V

2) VDC

SC486

10) P1.5V

17) KBC3_PWRGD

11-1) P1.8V

PEG

2) VDC

PRTC

7) P1.5V_AUX

9) KBC3_PWRON

9) KBC3_PWRON

13) KBC3_VRON

8) KBC3_SUSPWR

13) KBC3_VRON (Back-up)

16) CLK3_PWRGD

6) P1.8V_AUX

12)GCORE3_PWRGD (PM-model)

6) P1.8V_AUX

10-1) P3.3V

PWROK

10-1) P3.3V

2) VDC

CL_PWROK

PCIe

CL_PWROK

19) PLT3_RST*

(Test Option)

P3.3V_MICOM

Devices

8) CHP3_SLPS5#/4#/3#

5) KBC3_SUSPWR

2) VDC

6) P5.0V_AUX

9

18

16

15) VRM3_CPU_PWRGD

15

19

19

14

6) P3.3V_AUX

19) PCI3_RST*

8

6) P3.3V_AUX

10

17

M-1) KBC3_DDR_PWRON (TBD) = 8) KBC3_SUSPWR

9

M-2) KBC3_ME_PWRON = 15) KBC3_PWRON

Host / ME Boot

(SLPS4* = S4_STATE*) > (SLPM* = SLPS3*)

11) VCCP3_PWRGD

Host S5 / ME Boot

(SLPS4* = S4_STATE*) > SLPM* > SLPS3*

(SLPS4* = SLPM*) > S4_STATE* > SLPS3*

Host Boot / ME Off

3

P5.0V_ALW

7

2-1) P12.0V_ALW

10) P5.0V

9-1) KBC3_PWRON_INV#

9-1

7) KBC3_RSMRST#

11

SC471

11-1) GFX_CORE

10-2) 0.9V

12

13

15)VRM3_CPU_PWRGD

12)GCORE_PWRGD

17) KBC3_PWRGD

17) KBC3_PWRGD

10-1) P3.3V

15)VRM3_CPU_PWRGD

10) P1.5V

10-1) P1.2V

10-1) P3.3V

10-1) P1.8V

10-1) P1.8V

10) P1.5V

17) KBC3_PWRGD

WK.Yeo

SH.Lee

KK.Bin

undefined

12/05/2008

PV

REV 1.0

March 10, 2009 07:55:21 AM

BA41-01060A

6 67

CANNES

MAIN

POWER SEQUENCE

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

17) KBC3_PWRGD

P3.3V_MICOM

110ms Delay

9) KBC3_PWRON

6

PM-model only

10) P1.05V (IGFX_CORE)

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

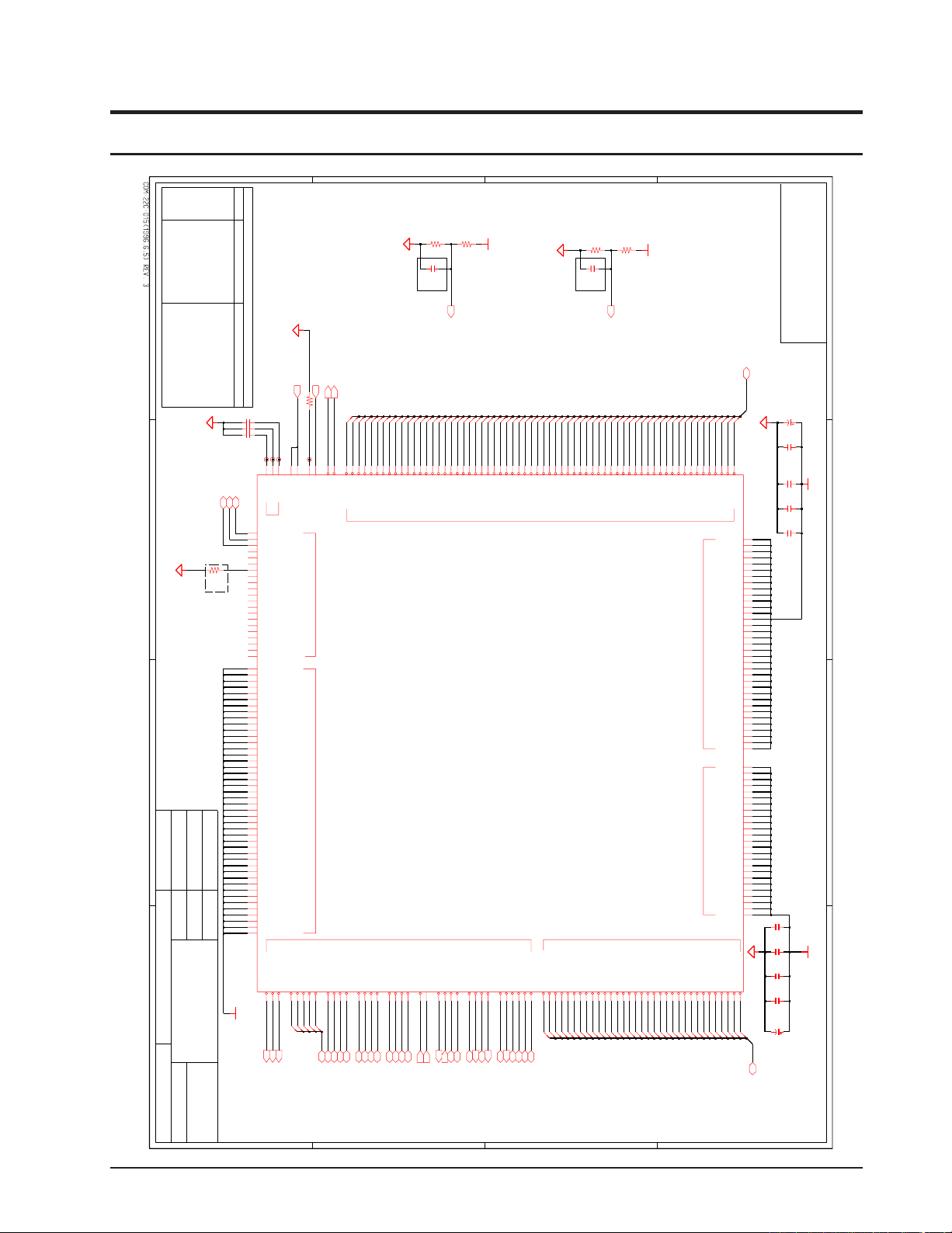

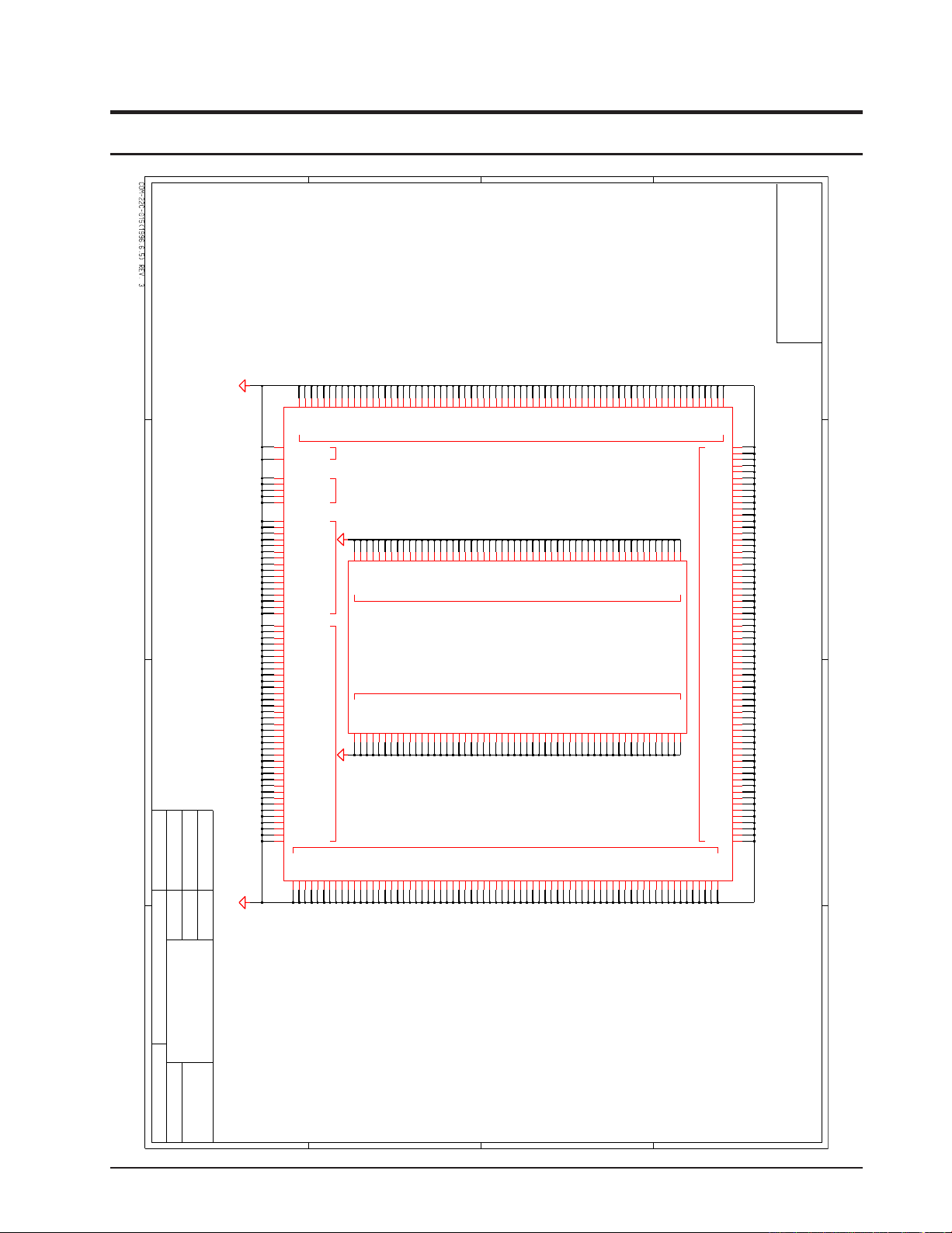

100 MHz

(Marvell)

PORT 80

100 MHz (SRC 9)

CLK3_ICH1414.318 MHz

Page 8

CLK3_PCLKPORT80

33 MHz

1

Main PLL

SSC

DPLLA

PLL3

SSC

TITLE

Buffer

MUX

CLOCK DISTRIBUTION

MUX

FSB

CLK1_MCLK1/1#

DMI

FS(2:0)

CARD

ITP_EN

SS(96/100) SEL

100 MHz (SRC4)

P3.3V

CLK3_PWRGD*

KBC

Cantiga

1

100 MHz (SRC0)

MINI PCIE

CARD 1

96 MHz

MINI PCIE

THIS DOCUMENT CONTAINS CONFIDENTIAL

PCIE LAN

MIN3_CLKREQ*

EXP3_CLKREQ*

32.768 KHz

CLK3_USB48

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

CLK1_SATA/SATA*

333/400 MHz

333/400 MHz

CLK1_PEG/PEG*

CHP3_SATACLKREQ*

CHECK

33 MHz

32.768 KHz

PCIEPLL

SPI3_CLK

CLK3_PCLKMICOM

DATE

14 MHz

HD Audio

MDC

DPLLB

CK-505M (w/ CLKREQ* & SSDC)

LAST EDIT

SATAPLL

CLK1_DREFCLK/CLK*

PCI_STP*

PAGE

100 MHz (SRC 3)

B

OSC

MDC3_BCLK

100 MHz (SRC 6,8,9,10)

667/800 MHz

25 MHz

C

LOM3_CLKREQ*

MCH3_CLKREQ*

CLK1_MINIPCIE/PCIE*

SODIMM #1

CLK1_MINI2PCIE/PCIE*

4

100 MHz (SRC 2)

SPI

333/400 MHz

CLK0_HOST_CPU/CPU*

HPLL

3

33 MHz

MPLL

ITM3_CLKREQ*

HD 24 MHz

USBPLL

1

OSC

PART NO.

B

C

xSLG8SP513r05)

ELECTRONICS

48MHz PLL

Rev. 0.1

D D

CLK1_PCIELOM/LOM*

CLK1_MCLK0/0#

33 MHz

SODIMM #0

4

3

10 MHz

EXPRESS

MUX

266 MHz

2

2

100 MHz (SRC 8)

CLK1_DREFSSC/SSC*

PEG

CLK1_MCH3GPLL/3GPLL*

OF

SAMSUNG

PCIE PLL

MCH

CPU_STP*

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

14.318 MHz

CLK1_MCLK3/3#

CLK1_MCLK4/4#

CLK1_PCIEICH/ICH*

333/400 MHz

CLK1_EXPCARD#

RTC Clock

266 MHz CLK0_HOST_GMCH/GMCH*

100 MHz (SRC 6)

AUD3_BCLK

CPU

17.86 MHz

SAMSUNG PROPRIETARY

ICH9-M

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

PCI Express Gfx

EXCEPT AS AUTHORIZED BY SAMSUNG.

DRAW

CARD 2

APPROVAL

MODULE CODE

48 MHz

DEV. STEP

REV

CLK3_PCLKICH

A A

BSEL

WK.Yeo

SH.Lee

KK.Bin

undefined

12/05/2008

PV

REV 1.0

March 10, 2009 07:55:21 AM

BA41-01060A

7 67

CANNES

MAIN

CLOCK DIAGRAM

- This Document can not be used without Samsung's authorization -

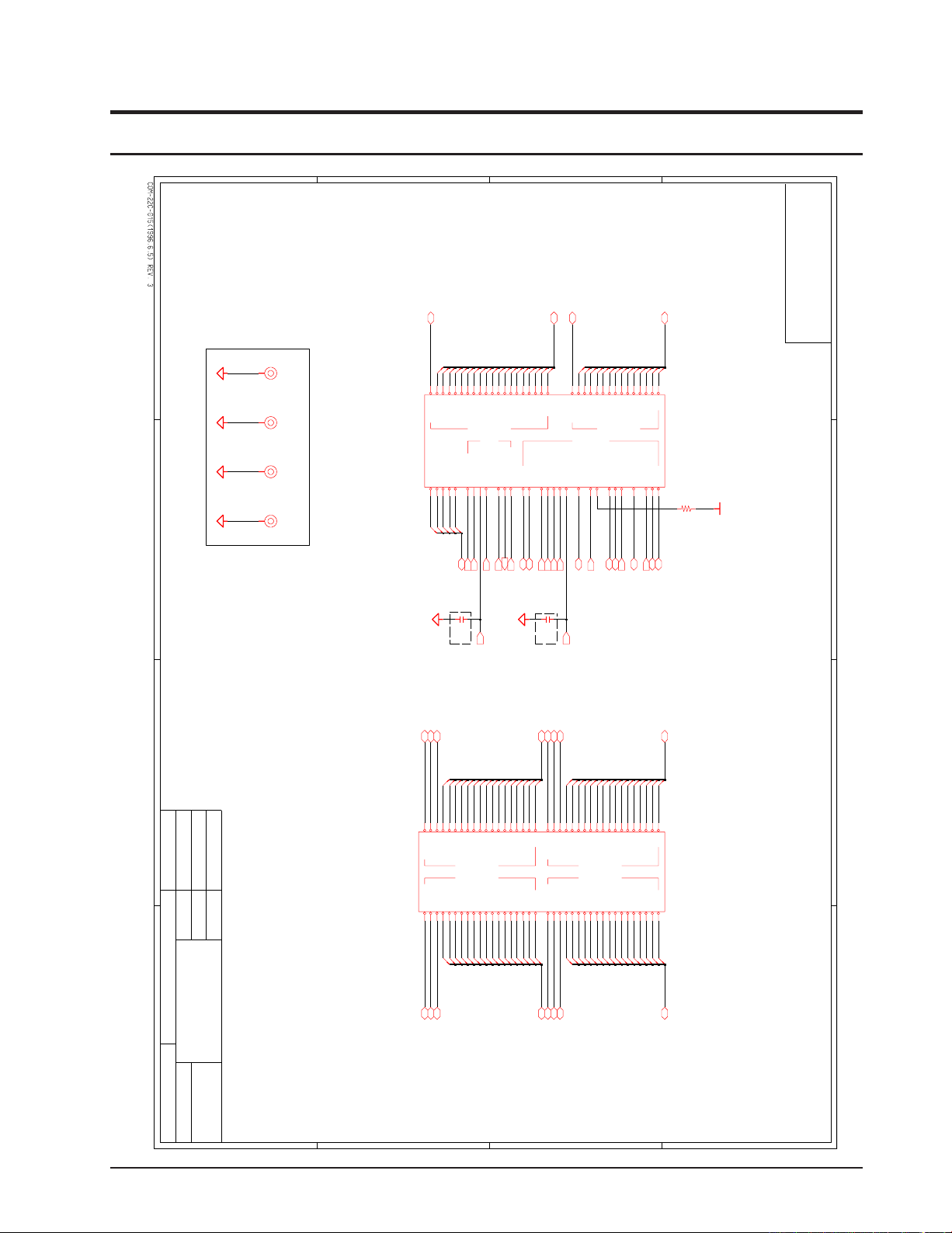

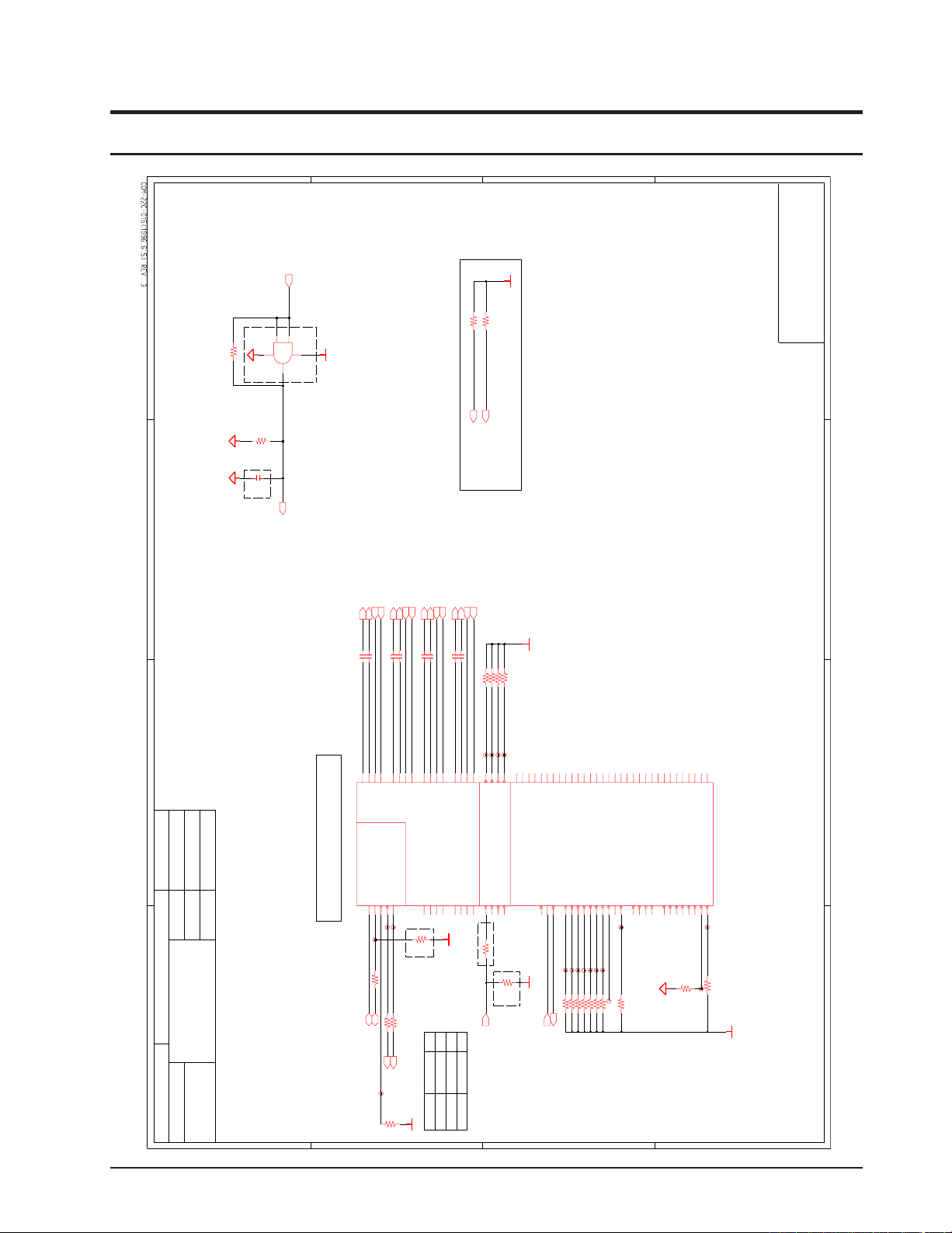

8. Block Diagram and Schematic

R720

8-7

8-8

8. Block Diagram and Schematic

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

R720

Samsung

Confidential

1

1

APPROVAL

CHECK

DESIGN

Check if PU is doubled to Micom Side.

10mil width and 10mil spacing.

PART NO.

TITLE

REV

0

C

SAMSUNG PROPRIETARY

R2

SMBUS Address 7Ah

B

SHDN_SEL MODE

1

2

OF

HIGH Z

3

ELECTRONICS

D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THERMAL SENSOR & FAN CONTROL

A

SAMSUNG

93 degree C

N/A (SHDN# NOT USED)

Line Width = 20 mil

PROPRIETARY INFORMATION THAT IS

2

SAMSUNG ELECTRONICS CO’S PROPERTY.

D

C

Opposite side of CPU.

R1

3.3 * [R2/(R1+R2)] = (T-75)/21

To support heatsink

A

3

4

DEV. STEP

Type:straight

CH3(DIODE MODE)

4

PAGE

For ATI M9x

TRIP_SET pin voltage = (T-75)/21

MODULE CODE

REV 1.0

PV

12/05/2008

KK.Bin

SH.Lee

WK.Yeo

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

THERMAL SENSOR EMC2102

THERMAL SENSOR

CANNES

678

BA41-01060A

March 10, 2009 07:55:21 AM

For Intel 45nm(From penryn)

DATE

CH1(INTEL MODE)

THIS DOCUMENT CONTAINS CONFIDENTIAL

LAST EDIT

B

EXCEPT AS AUTHORIZED BY SAMSUNG.

C111

10000nF-X5R

P3.3V

6.3V

1%

R106

10K

VDD_5V_2

27

RESET#

16

SHDN_SEL

9

SMCLK

23

SMDATA

22

SYS_SHDN#

12

TACH28THERMTRIP#

13

29

THRM_PAD

TRIP_SET

11

VDD_3V1VDD_5V_1

24

DP13DP25DP3

7

FAN_125FAN_226FAN_MODE

10

GND

20

NC_18NC_2

15

21

NC_3

POWER_OK

14

ALERT#

19

CLK_IN

18

CLK_SEL

17

DN12DN24DN3

6

1209-001718

EMC2102

U1

nostuff

0

R16

P3.3V_AUX

51.1K

R29

1%

200K

R26

1%

M3

BA61-01090A

DIA

HEAD

LENGTH

1%

49.9

R509

M2

BA61-01090A

DIA

HEAD

LENGTH

1%

R36

20K

LENGTH

HEAD

DIA

BA61-01090A

M1

P5.0V

C506

P3.3V_AUX

10V

100nF

6.3V

C21

10000nF-X5R

C505

100nF

10V

1

3

2

MMBT3904

Q516

50V

2.2nF

C508

50V

2.2nF

C507

50V

0.47nF

C119

10K

R644

1%

R30

10K

1%

P3.3V

1%

10K

R21

1%

R19

10K

123

45MNT1

MNT2

6

3711-000456

J503

HDR-4P-1R-SMD

FAN3_FDBACK#

P3.3V_AUX

M503

BA61-01090A

DIA

HEAD

LENGTH

FAN5_VDD

FAN3_FDBACK#

THM3_ALERT#

CPU2_THERMDC

THM3_THERMDN_MN

CPU2_THERMDA

GFX3_THERMDP

THM3_THERMDP_MN

FAN5_VDD

KBC3_PWRGD

KBC3_THERM_SMCLK

KBC3_THERM_SMDATA

THM3_STP#

THM3_TRIP_SET_MN

THM3_VDD_3V_MN

THM3_TRIP_SET_R_MN

THM3_SHDN_SEL_MN

GFX3_THERMDN

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

1 / 4

ADDR GROUP

ICH

0

ADDR GROUP

1

CONTROL

2 / 4

DATA GRP 0

DATA GRP 2

DATA GRP 1

DATA GRP 3

SAMSUNG

OFPAGE

PART NO.

TITLE

LAST EDIT

REV

DEV. STEP

DATE

MODULE CODE

APPROVAL

CHECK

DRAW

1

12/05/2008

undefined

KK.Bin

SH.Lee

WK.Yeo

SAMSUNG PROPRIETARY

PROPRIETARY INFORMATION THAT IS

EXCEPT AS AUTHORIZED BY SAMSUNG.

For ESD

For ESD

C

D

A

CPU Socket : 3704-001153

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

D

24

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

3

A

B B

CPU mount

1

C

4

3

2

ELECTRONICS

3

63

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

PENRYN (1/3)

CPU

CANNES

679

BA41-01060A

March 10, 2009 07:55:21 AM

REV 1.0

PV

2

1

28

22

14

10

18

24

52

45

10127469

14

27

31

26

43

172321

393334

60

5

26

1

13

8

58

0.1nF

nostuff

50V

C3896

11

172020

27

4

41

56

R87

331535

18

4

61

51

16

304928

MT6

RMNT-38-70-1P

54

50V

C3895

0.1nF

nostuff

44

5

31

RMNT-38-70-1P

MT4

RMNT-38-70-1P

MT7

REQ2#K2REQ3#J3REQ4#

L1

RESET#

C1

F3

RS0#F4RS1#G3RS2#

A3

SMI#

D5

STPCLK#

G2

TRDY#

FERR#

G6

HIT#

E4

HITM#

D20

IERR#

C4

IGNNE#

B3

INIT#

C6

LINT0B4LINT1

H4

LOCK#

REQ0#K3REQ1#

H2

J1

A9#

H1

ADS#

M1

ADSTB0#

V1

ADSTB1#

E2

BNR#

G5

BPRI#

F1

BR0#

E1

DBSY#

H5

DEFER#

F21

DRDY#

A5

U2

A30#V4A31#W3A32#

A33#

AA4

AB2

A34#

AA3

A35#

L5

A4#L4A5#K5A6#M3A7#N2A8#

A20M#

U4

A21#Y5A22#U1A23#R4A24#T5A25#T3A26#W2A27#W5A28#

Y4

A29#

J4

A3#

P5

A11#P2A12#L2A13#P4A14#P1A15#R1A16#

Y2

A17#U5A18#R3A19#W6A20#

A6

7

PENRYN

J501-1

0143854500|bga_479p_sock

N3

A10#

30

21

23

32

38

2

RMNT-38-70-1P

MT3

35

42

12

59

16

11

24

37

57

13

40

6

25

56

3

25

9

8

P1.05V

48

62

19

6

22

3

4

55

15 47

290

34

36

DSTBP0#

M26

DSTBP1#

AA26

DSTBP2#

AF24

DSTBP3#

K24

D8#

G24

D9#

H25

DINV0#

N24

DINV1#

U22

DINV2#

AC20

DINV3#

J26

DSTBN0#

L26

DSTBN1#

Y26

DSTBN2#

AE25

DSTBN3#

H26

AE22

D55#

AF23

D56#

AC25

D57#

AE21

D58#

AD21

D59#

E25

D6#

AC22

D60#

AD23

D61#

AF22

D62#

AC23

D63#

E23

D7#

D45#

AA24

D46#

AB25

D47#

AE24

D48#

AD24

D49#

G25

D5#

AA21

D50#

AB22

D51#

AB21

D52#

AC26

D53#

AD20

D54#

V23

D36#

T22

D37#

U25

D38#

U23

D39#

F23

D4#

Y25

D40#

W22

D41#

Y23

D42#

W24

D43#

W25

D44#

AA23

P22

D26#

T24

D27#

R24

D28#

L25

D29#

G22

D3#

T25

D30#

N25

D31#

Y22

D32#

AB24

D33#

V24

D34#

V26

D35#

D16#

K25

D17#

P26

D18#

R23

D19#

E26

D2#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

E22

D0#

F24

D1#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

N22

0143854500|bga_479p_sock

J501-2

PENRYN

29

32

19

50

53

0

CPU1_CPURST#

CPU1_INTR

CPU1_BREQ#

CPU1_BPRI#

CPU1_BNR#

CPU1_ADSTB1#

CPU1_ADS#

CPU1_ADSTB0#

CPU1_A20M#

CPU1_TRDY#

CPU1_STPCLK#

CPU1_SMI#

CPU1_RS2#

CPU1_RS1#

CPU1_RS0#

CPU1_LOCK#

CPU1_NMI

CPU1_INIT#

CPU1_IGNNE#

CPU1_IERR#_MN

CPU1_HITM#

CPU1_HIT#

CPU1_FERR#

CPU1_DRDY#

CPU1_DEFER#

CPU1_DBSY#

CPU1_DSTBN1#

CPU1_DBI0#

CPU1_DSTBN2#

CPU1_DSTBP2#

CPU1_DBI2#

CPU1_DSTBN3#

CPU1_DSTBP3#CPU1_DSTBP1#

CPU1_A#(16:3)

CPU1_REQ#(4:0)

CPU1_A#(35:17)

CPU1_D#(47:32)

CPU1_D#(63:48)CPU1_D#(31:16)

CPU1_D#(15:0)

CPU1_DSTBP0#

CPU1_DSTBN0#

CPU1_DBI3#CPU1_DBI1#

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

R720

8-9

8-10

8. Block Diagram and Schematic

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

R720

Samsung

Confidential

3 / 4

RSVD

THERMAL

H CLK

XDP/ITP SIGNALS

1

1

1

1

0.0375 V

0

0

0

000

REV

0

0

1

0.2250 V

0

0

1

1 1

0

0

1

1

0

1

0

1

0.2875 V

0

1

0.5250 V

Dual Mode Region

1

1

0

1 0

0

near the CPU

0

1

1

0

0

1

0

1

1

1

1

1

1

0

Deeper Sleep/Extended Deeper Sleep

1

1

0

1

0

1

0

0

1

1

1

0

1

0

0

1

0

1

1.1875 V

0

1.4625 V

0

1

1

1

0

1

1

1

0

0

1

1

1

1.2250 V

0

0

1

0

0.5375 V

1

0

1

DEV. STEP

0

0.4750 V

0.6000 V

1

1

1

1

1

0

0

0.1625 V

1

(preferred 50mil) from any other signal. And GND via 100mil away

0

0

0

0

0.0250 V

0

1

1

0

0

1

0.5500 V

0

0.5000 V

0

0

1

0

0

1

SAMSUNG

0

0

0

0.1500 V

0

1

1

0

0

1

1

Observe 3:1 spacing b/w VCC/VSSsense lines and 25mil away

0.6375 V

1

0

1

0.1375 V

1

0

1

1.3125 V

Active

FSB 800 MHz

0

A

1

*"1111111" : 0V power good asserted.

1

0

0

1

0

0

0.0625 V

0.9125 V

0

0

0

0

1

0

1

1

1

1

0

0.8500 V

1

0.0125 V

Deeper Slp

1

1

1

0

0

0

0

BSEL

1

1

0

1

1

1

1

0

0

1

Minimize coupling of any switching signals to this net.

0

1

0

0

0

1

0

0

1

0

0

1

0.0000 V

1

0

1

SAMSUNG ELECTRONICS CO’S PROPERTY.

0

1

1

1

1

BSEL0, BSEL1, BSEL2

0

0

0

1

0

1

DPRSTP*

0

1

0

0

FSB 1067 MHz

0

1

1

1

0

1.0375 V

1

0

1

1

0

1

1

0

0

000

0

0

0.4625 V

0

0

0

0

1.1375 V

1

1

3

0

1

0.5125 V

OF

1

0

0

0

1

Active Mode

0

1

0

1

0

1

1

Pull-down

0

1

1

1.3000 V

1

1

0

0

1

0

1

1

1

1

1

0.2500 V

0

0.7125 V

1

0

1

1

0.7000 V

1.0500 V

1.4125 V

1

0

0

0.6875 V

0

0

1

1

1

1

1

0

1.1125 V

1

1

0

0

0.3375 V

11

1

0

0

0

0

1

1

0

1

0

0

1

1

0

C

1

1

0.3750 V

1

BSEL0, BSEL2

0

1

0

0.3500 V

0

1

0.3250 V

0

1

1

0.7875 V

1

1

0

1

0

1

0

0

0

0.7625 V

0

0

0

0

1

GTLREF : Keep the Voltage divider within 0.5"

0

0 or 1

1

0

0

1

2

0

0.0000 V

0.0500 V

1

0

0.5875 V

1

0

0

0

0.0750 V

1

0.8250 V

0

0

01

1 1.1500 V

1.0875 V

1 1

0

Active/Deeper Sleep

1

C

0

0.2375 V

00

0.0000 V

1

0

0

1

IMVP-6

1

1

0.3000 V

0

0

0

0

1

0

0

0.2625 V

0

0

0

1

0

0

1

1

1

0

0

0

1

1

APPROVAL

MODULE CODE

1

1

0

0

1

1

1

1

0

1.4500 V

1

0

Voltage

1

0

0

0

0

1

0

0

1

0

0

1.0125 V

1

1

0

1

0

0

0

0

0

1

EXCEPT AS AUTHORIZED BY SAMSUNG.

0

0

0

0

0

0

1

0

1

0

0

1

1

1.0750 V

1

1

1

0.9625 V

0

1

0

0.9875 V

0.1125 V

1.2750 V

0

1

1

0

1

1

0

1

0.3625 V

1

0

1

1

1

1

0

0.6500 V

0

0.8375 V

0

1

0

0

0

1

1

0

0

1

1.1000 V

0

0.0000 V

1

0

0

DATE

1.4875 V 0

0

VID(6:0)

1

1.0000 V

1

0

1

1

1

1

1

0.4500 V

0.2750 V

DRAW

0 1

0

1

0

1

1

1

1

1

1

0

PSI2*

1

1

1

0

0

1

trace shorter than 1/2" to their respective Banias socket pins.

0

1

11 1

0

1

0

0

1

1

1

10.6250 V

11

1

0

0

1

1

0.0000 V

PAGE

0

4

0.4000 V

1

0

0.3125 V

0

1

0

0

1

1

0

0.4375 V

0.4250 V

0

1

1

1

0

0

0

PSI2*

1

0

LAST EDIT

1

1

0.6625 V0

0

0

1

0

1

0

1

1

0

1

0

1

0

0

1

1

1

0

1

1

0

0

0

D

0

0

4

0

0

0

0

0

0

1

1.4375 V

0

0

1

1.3625 V

1

0.5750 V

1

1

0

1

1

0

0

111

0

1

CHECK

1

0

0

0

0

0.9000 V

0

0

1

0

0

1

0

0

0.9375 V

0.0875 V

0

1

1

1.4000 V

1

1

1

1

0

1

0.8000 V

1

0.7750 V

1

0

1.2125 V

1

0.7375 V

0

1

1

0

1

0

0

0.2000 V

1

0

1.1250 V1

0

1.2625 V

1

0

0

1

0

1.3750 V

0.2125 V

1

0

1

101

1

0

0

1

1.3250 V

1

0

1

1

0

1

0

1

Voltage

0

1

1

0.3875 V

0

1

1

1.2875 V

1

0

0

0

0

0

0

0

1

B

D

0

0

0

0

1

1

1.2000 V

1

0

1

0

1

0.1875 V

1

1

1

0

TITLE

1

0

1

0

0

1

1

1

0

0

0

1

0

1.0250 V

1

1

1

1

0

1

0

1

1

0

0

1

1

1

1.2500 V

0

0

0

1

1

0.0000 V

0

0

0

1

1

0

1

1

0

1

0

PROPRIETARY INFORMATION THAT IS

1

1

1

0

0

1

0

1.5000 V

0

1

1

1

CPU Core Voltage Table

1

1

0

1

1

1

3

0.5625 V

1

DPRSTP*

0

0.6125 V

1

1

0

1

1

0

0

0

0

0

0

THIS DOCUMENT CONTAINS CONFIDENTIAL

0

1

0

0.8125 V

1.0625 V

*Yonah Processor (2.33 GHz / 800 MHz : TBD)

0

0

1

1

1

1.4750 V

1

0

Voltage

0.0000 V

1.1625 V

1

1

1

0

0

0

1

A

1

0

Dual Mode Region

0.6750 V

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

0

0

1

0

0

1

0

1

1

1

0

0

0

1

of the first GTLREF0 pin with Zo=55ohm trace.

1

1

1

0

0

1

0

0

COMP0,2(COMP1,3) should be connected with Zo=27.4ohm(55ohm)

0 0

1

1

1

0 or 1

1.2375 V

1

VID(6:0)

0

1

1

1

0

For ESD

0.1000 V

1

0

0

0

0

1

1

0

SAMSUNG PROPRIETARY

0

0.8875 V

VID(6:0)

1

1

1

1

0.8750 V

0

1

1

0

0

0

0

0

0.0000 V

1

0

1

0

1.3375 V

1

0

0.1750 V

1

PART NO.

from each of the VCC/VSS test point vias.

1

1

0

1

0

0

1

ELECTRONICS

0

1

1

0

0

0

0

1

0

0

1

0

1

1

0

0

0.7250 V

0

0

1

1

0

0

0.9250 V

1

1

1

0

1

DPRSLPVR

1.1750 V

1

1

1

1

1

0

1

1

0

1

1

0

1

1

1

1

0

0

1

0

Route the VCC/VSSsense as a Zo=55ohm traces with equal length.

1

1

1

1

0

00

0.8625 V

0

1

1

0

1

1

1

1

1

1

1

0

0

0.7500 V

0

1

0

1

1

0

1.4250 V

0

1

1

0

1

1

0

1.3875 V

1

0

0

1

0

1

1

000

1

0

1

1

1

0

1

1

0

67

CANNES

CPU

PENRYN (2/3)

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

0

0

0

0

1.3500 V

0

1

0.9750 V

1

0.4125 V

1

0

0.4875 V

DPRSLPVR

1

1

0

2

1

1

0.9500 V

GND test points within 100mil of the VCC/VSSsense at the end of the line.

0

0.1250 V

0

For ESD

WK.Yeo

SH.Lee

KK.Bin

undefined

12/05/2008

PV

REV 1.0

March 10, 2009 07:55:21 AM

BA41-01060A

10

P1.05V

54.9

R35

1%

100nF

C57

10V

10nF

C97

25V

10V

C49

100nF

nostuff

0.1nF

C3894

50V

27.4

P1.05V

VID_3

AE3

VID_4

AF3

VID_5

AE2

VID_6

AE7

VSSSENSE

R42

1%

VCCP_4N6VCCP_5T6VCCP_6R6VCCP_7

K21

VCCP_8

J21

VCCP_9

M21

AF7

VCCSENSE

AD6

VID_0

VID_1

AF5

AE5

VID_2

AF4

VCCA_2

C26

VCCP_1

K6

VCCP_10

N21

VCCP_11

T21

VCCP_12

R21

VCCP_13

V21

VCCP_14

W21

VCCP_15V6VCCP_16

G21

VCCP_2J6VCCP_3

M6

C24

TEST4

AF26

TEST5

AF1

TEST6

A26

C3

TEST7

C7

THERMTRIP#

A24

THRMDA

B25

THRMDC

TMS

AB5

TRST#

AB6

VCCA_1

B26

D2

RSVD_6

D22

RSVD_7D3RSVD_8F6RSVD_9

D7

SLP#

TCK

AC5

TDI

AA6

TDO

AB3

TEST1

C23

TEST2

D25

TEST3

AD26

GTLREF

PRDY#

AC2

PREQ#

AC1

D21

PROCHOT#

AE6

PSI#D6PWRGOOD

M4

RSVD_1

N5

RSVD_2T2RSVD_3V3RSVD_4B2RSVD_5

BSEL0

B23

BSEL1

C21

BSEL2

COMP0

R26

U26

COMP1

AA1

COMP2Y1COMP3

DBR#

C20

E5

DPRSTP#B5DPSLP#

D24

DPWR#

A22

BCLK0

A21

BCLK1

BPM0#

AD4

BPM1#

AD3

BPM2#

AD1

BPM3#

AC4

B22

PENRYN

J501-3

0143854500|bga_479p_sock

1K

R38

1%

10V

C71

100nF

1%54.9

R40

1

0

R88

56

10V

C69

100nF

27.41%

R59

R52

1% 54.9

0.1nF

C3897

50V

3

nostuff

54.9

R39

100nF

C65

10V

5

2

nostuff

R89

1K 1%

2K

R37

1%

100nF

C52

10V

1%1K

R102

nostuff

100nF

C31

6

P1.05V

10V

AD

2.5V

220uF

EC50

P1.5V

1%

R43

54.9

54.9

R41

P1.05V

10000nF

C88

CPU1_TRST#

ITP3_DBRESET#

CPU1_COMP3_MN

CPU1_COMP2_MN

CPU1_COMP0_MN

CPU1_COMP1_MN

CPU1_GTLREF_MN

CPU1_PWRGDCPU

CPU1_TRST#

4

6.3V

CPU1_VCCSENSE

CPU1_BSEL2

CPU1_BSEL1

CPU1_BSEL0

CPU1_PSI#

CPU1_DPWR#

CPU1_THRMTRIP#

CPU2_THERMDC

CPU2_THERMDA

CPU1_DPRSTP#

CPU1_VSSSENSE

CPU1_SLP#

CPU1_DPSLP#

CLK0_HCLK0#

CLK0_HCLK0

CPU1_VID(6:0)

CPU1_PROCHOT#_MN

CPU1_TCK

CPU1_TDI

CPU1_TMS

CPU1_TEST2_MN

CPU1_TEST1_MN

CPU1_TCK

CPU1_TDI

CPU1_TMS

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

4 / 4

LAST EDIT

DEV. STEP

A

ELECTRONICS

MODULE CODE

CHECK

C

DATE

A

C

CANNES

CPU

PENRYN (3/3)

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

OF

1

B B

4

D

APPROVAL

PROPRIETARY INFORMATION THAT IS

4

2

3 1

Prodlizer used

SAMSUNG PROPRIETARY

D

SAMSUNG

3

2

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

EXCEPT AS AUTHORIZED BY SAMSUNG.

PAGE

REV

DRAW

PART NO.

TITLE

CPU_CORE

WK.Yeo

SH.Lee

KK.Bin

undefined

12/05/2008

PV

REV 1.0

March 10, 2009 07:55:21 AM

BA41-01060A

11 67

1%100

R20

22000nF-X5R

C124

6.3V

20%

nostuff

nostuff

CPU_CORE

CPU_CORE

20%

6.3V

C40

22000nF-X5R

1%100

R22

VSS_93

E21

VSS_94

E24

VSS_95E3VSS_96E6VSS_97

VSS_98

E8

F11

VSS_99

D16

VSS_84

D19

VSS_85

D23

VSS_86

D26

VSS_87D4VSS_88D8VSS_89

A8

VSS_9

E11

VSS_90

E14

VSS_91

E16

VSS_92

E19

C16

VSS_74

C19

VSS_75C2VSS_76

C22

VSS_77

C25

VSS_78C5VSS_79

A4

VSS_8

C8

VSS_80D1VSS_81

D11

VSS_82

D13

VSS_83

VSS_64

B13

VSS_65

VSS_66

B16

B19

VSS_67

B21

VSS_68

B24

VSS_69

A25

VSS_7

B6

VSS_70B8VSS_71

C11

VSS_72

C14

VSS_73

AF11

VSS_55

AF13

VSS_56

AF16

VSS_57

AF19

VSS_58

AF2

VSS_59

A23

VSS_6

AF21

VSS_60

AF25

VSS_61

AF6

VSS_62

AF8

VSS_63

B11

AD8

VSS_45

AE1

VSS_46

AE11

VSS_47

AE14

VSS_48

AE16

VSS_49

A2

VSS_5

AE19

VSS_50

AE23

VSS_51

AE26

VSS_52

AE4

VSS_53

AE8

VSS_54

VSS_35

AD11

VSS_36

AD13

VSS_37

AD16

VSS_38

AD19

VSS_39

A19

VSS_4

AD2

VSS_40

AD22

VSS_41

AB23

VSS_42

AD25

VSS_43

AD5

VSS_44

AB8

VSS_26

AC11

VSS_27

AC14

VSS_28

AC16

VSS_29

A16

VSS_3

AC19

VSS_30

AC21

VSS_31

AC24

VSS_32

AC3

VSS_33

AC6

VSS_34

AC8

Y6

VSS_163

AA5

VSS_17

AA8

VSS_18

AB1

VSS_19

A14

VSS_2

AB11

VSS_20

AB13

VSS_21

AB16

VSS_22

AB19

VSS_23

AB26

VSS_24

AB4

VSS_25

VSS_153

V25

VSS_154

V5

VSS_155

W1

VSS_156

W23

VSS_157

W26

VSS_158

W4

VSS_159

AA25

VSS_16

Y21

VSS_160

Y24

VSS_161

Y3

VSS_162

T1

VSS_144

T23

VSS_145

T26

VSS_146

T4

VSS_147

U21

VSS_148

U24

VSS_149

AA22

VSS_15

U3

VSS_150

U6

VSS_151

V2

VSS_152

V22

N26

VSS_134

N4

VSS_135

P21

VSS_136

P24

VSS_137

P3

VSS_138

P6

VSS_139

AA2

VSS_14

R2

VSS_140

R22

VSS_141

R25

VSS_142

R5

VSS_143

VSS_124

L24

VSS_125

VSS_126

L3

L6

VSS_127

M2

VSS_128

M22

VSS_129

AA19

VSS_13

M25

VSS_130

M5

VSS_131

N1

VSS_132

N23

VSS_133

H6

VSS_115J2VSS_116

J22

VSS_117

J25

VSS_118J5VSS_119

AA16

VSS_12

K1

VSS_120

K23

VSS_121

K26

VSS_122

K4

VSS_123

L21

F25

VSS_105F5VSS_106F8VSS_107G1VSS_108

G23

VSS_109

AA14

VSS_11

G26

VSS_110G4VSS_111

H21

VSS_112

H24

VSS_113H3VSS_114

VCC_96

F18

VCC_97

F20

VCC_98F7VCC_99

A11

VSS_1

AA11

VSS_10

F13

VSS_100

F16

VSS_101

F19

VSS_102F2VSS_103

F22

VSS_104

E17

VCC_87

E18

VCC_88

E20

VCC_89

A9

VCC_9

E7

VCC_90E9VCC_91

F10

VCC_92

F12

VCC_93

F14

VCC_94

F15

VCC_95

F17

D12

VCC_77

D14

VCC_78

D15

VCC_79

A7

VCC_8

D17

VCC_80

D18

VCC_81D9VCC_82

E10

VCC_83

E12

VCC_84

E13

VCC_85

E15

VCC_86

VCC_67B9VCC_68

C10

VCC_69

A20

VCC_7

C12

VCC_70

C13

VCC_71

C15

VCC_72

C17

VCC_73

C18

VCC_74C9VCC_75

D10

VCC_76

AF20

VCC_58

AF9

VCC_59

A18

VCC_6

B10

VCC_60

B12

VCC_61

B14

VCC_62

B15

VCC_63

B17

VCC_64

B18

VCC_65

B20

VCC_66

B7

AE17

VCC_48

AE18

VCC_49

A17

VCC_5

AE20

VCC_50

AE9

VCC_51

AF10

VCC_52

AF12

VCC_53

AF14

VCC_54

AF15

VCC_55

AF17

VCC_56

AF18

VCC_57

VCC_38

AD15

VCC_39

A15

VCC_4

AD17

VCC_40

AD18

VCC_41

AD7

VCC_42

AD9

VCC_43

AE10

VCC_44

AE12

VCC_45

AE13

VCC_46

AE15

VCC_47

AC12

VCC_29

A13

VCC_3

AC13

VCC_30

AC15

VCC_31

AC17

VCC_32

AC18

VCC_33

AC7

VCC_34

AC9

VCC_35

AD10

VCC_36

AD12

VCC_37

AD14

AB10

VCC_19

A12

VCC_2

AB12

VCC_20

AB14

VCC_21

AB15

VCC_22

AB17

VCC_23

AB18

VCC_24

AB20

VCC_25

AB7

VCC_26

AB9

VCC_27

AC10

VCC_28

VCC_1

AA10

VCC_10

F9

VCC_100

AA12

VCC_11

AA13

VCC_12

AA15

VCC_13

AA17

VCC_14

AA18

VCC_15

AA20

VCC_16

AA7

VCC_17

AA9

VCC_18

CPU1_VCCSENSE

CPU1_VSSSENSE

0143854500|bga_479p_sock

J501-4

PENRYN

A10

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

R720

8-11

8-12

8. Block Diagram and Schematic

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

R720

Samsung

Confidential

PROPRIETARY INFORMATION THAT IS

DRAW

0

0

SAMSUNG

SAMSUNG PROPRIETARY

D

VDD_CPU_IOVDD_SRC_IO

333 MHz

2

DEVICE

4

0

B

BSEL0

GMCH

PEG_CLK/PEG_CLK#LOW

VDD_PCI

CLK REQ E

CHECK

27M & 27M_SS

0

1

BSEL1

SAMSUNG ELECTRONICS CO’S PROPERTY.

LAST EDIT

1

0

VDD_SRC

FSCFSB

PART NO.

VDD_REF

SRC_0/SRC_0#

1

CLK REQ F

400 MHz

133 MHz

0

Pin 20/21

266 MHz

1

SEL_LCDCLK*

200 MHz

CLK REQ

DATE

1

ELECTRONICS

1

PAGE

0 0

A

1

A

SRC4

REV

SL : 1205-003533

VDD_PLL3

C

OF

1

CLK REQ B

This part is 64pin QFN package.

2

Place 14.318MHz within

1

VDD_PLL3_IO

THIS DOCUMENT CONTAINS CONFIDENTIAL

C

Pin 24/25

HOST CLK

0

4

1

MODULE CODE

APPROVAL

BSEL2

MINI CARD

SATA

1

500mils of CK-505

3

VDD_48

1

B

1

TITLE

IDT : 1205-003159

DOT_96/DOT_96#

1

12

BA41-01060A

March 10, 2009 07:55:21 AM

REV 1.0

PV

12/05/2008

undefined

KK.Bin

SH.Lee

WK.Yeo

SRC2

CK505M

100 MHz

CLK REQ A

0

EXP3_CLKREQ#

RSVD

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

VDD_CPUVDD_IO

SRC PORT

SRC6

D

EXCEPT AS AUTHORIZED BY SAMSUNG.

0

3

FSA

HIGH

0

166 MHz

DEV. STEP

SRC8

nostuff

CK_Clock_505M

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

MAIN_CLOCK_CIRCUIT

CANNES

67

1

2

BLM18PG181SN1

B30

R218

475

2801-004518

14.31818MHz

Y1

1%

nostuff

R223

10K

1%

C700

100nF

10V

R217

33

10V

C409

100nF

C394

100nF

10V

R127

22

22

R589

22

R220

5%

P3.3V

5%22

R222

P3.3V

0.018nF

C395

50V

10000nF-X5R

C433

6.3V

100nF

C430

10V

P3.3V

R224

10K 1%

C424

100nF

10V

B28

BLM18PG181SN1

C400

100nF

10V

33

R235

10V

100nF

C413

10V

R228

22 5%

R236

2.2K

C417

100nF

nostuff

1%10K

R230

1%

R565

10K

6.3V

10000nF-X5R

C431

50V

C418

C401

10000nF-X5R

6.3V

0.033nF

5%

6.3V

C381

10000nF-X5R

4700nF-Y5V

C404

10V

C429

100nF

10V

R234

33

C420

50V

5%

0.033nF

1%

10K

R229

10V

100nF

C397

B31

BLM18PG181SN1

10K

R216

1%

10V

C393

4700nF-Y5V

0.018nF

C396

50V

50V

C422

100nF

C432

10V

P3.3V

0.033nF

5%

VSS_REF1VSS_SRC1

30

36

VSS_SRC2

VSS_SRC3

49

XTAL_IN

3

2

XTAL_OUT

C416

100nF

10V

27

VDD_PLL3_IO

VDD_REF

4

VDD_SRC

46

VDD_SRC_IO1

33

VDD_SRC_IO2

43

VDD_SRC_IO3

52

18

VSS_48

VSS_CPU

59

VSS_IO22VSS_PCI15VSS_PLL3

26

54

SRC9

37

38

SRC9#

65

THERM_GND

USB_FS_A

17

VDD_48

16

VDD_CPU

62

VDD_CPU_IO56VDD_IO

19

VDD_PCI

9

VDD_PLL3

23

28

SRC2#

29

SRC3#_CLKREQD#

32

SRC3_CLKREQC#

31

34

SRC4

35

SRC4#

SRC6

48

SRC6#

47

SRC7#_CLKREQE#

50

SRC7_CLKREQF#

51

SRC8#_ITP#

53

SRC8_ITP

PCI_4_SEL_LCDCLK#13REF_FS_C_TEST_SEL

5

SCL7SDA

6

SRC0#_DOT96#

21

SRC0_DOT96

20

SRC10

41

SRC10#

42

SRC11#_CLKREQG#

39

SRC11_CLKREQH#

40

SRC2

CPUSTOP#44FSB_TESTMODE

64

LCDCLK#_27M_SS

25

LCDCLK_27M

24

55

NC

PCIF_5_ITP_EN14PCISTOP#

45

PCI_0_CLKREQ_A#

8

PCI_1_CLKREQ_B#

10

PCI_211PCI_3

12

SLG8SP513

1205-003156

U12

CLKPWRGD_PWRDN#

63

CPU0

61

CPU0#

60

CPU1_MCH

58

CPU1_MCH#

57

R221

475 1%

P1.5V

CLK3_PCLKICH_R_MN

CLK3_PCLKMICOM_R_MN

CLK3_GFX_27M_SS_R_MN

CLK3_GFX_27M_SS

CLK3_GFX_27M_R_MN

CLK3_GFX_27M

CLK3_ICH14_R_MN

CLK1_MINIPCIE#

CLK1_MINIPCIE2

CLK1_MINIPCIE2#

CLK3_DBGLPC_R_MN

CLK1_PCIEICH

CLK1_PCIELOM

LOM3_CLKREQ#

EXP3_CLKREQ#

CHP3_SATACLKREQ#_R_MN

CLK1_PEG

CLK1_PEG#

CLK3_VDD_SRC_IO_MN

CLK1_MCH3GPLL

CHP3_SATACLKREQ#

CLK3_PCLKMICOM

MCH3_CLKREQ#_R_MN

MCH3_CLKREQ#

CLK3_DBGLPC

MIN3_CLKREQ#

CLK3_PCLKICH

CLK3_FM48

ITM3_CLKREQ#

CLK1_EXPCARD

CLK1_PCIEICH#

CLK1_EXPCARD#

CLK1_PCIELOM#

CLK1_MINIPCIE

CLK1_MCH3GPLL#

CLK0_HCLK1

CLK0_HCLK0#

CLK0_HCLK0

CLK3_USB48

SMB3_CLK

SMB3_DATA

CLK3_PWRGD

CHP3_CPUSTP#

CHP3_PCISTP#

CPU1_BSEL2

CPU1_BSEL0

CLK3_ICH14

CLK3_XTAL_IN_14_MN

CLK3_VDD_REF_MN

CLK3_USB48_R_MN

CLK1_SATA

CLK1_SATA#

CPU1_BSEL1

CLK0_HCLK1#

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

1 OF 5

VTT

HOST DATA BUS

VTTLF

NC

HOST CONTROL

HOST ADDRESS BUS

VCC CORE

CFG

B

D

SDVO and PCIE X1

DRAW

A

1608

Current Setting

DMI Lane Reversal

CFG(20)

(def. : default Option)

Low

PAGE

Dynamic ODT

3

CFG(7)

CFG(9)

Simultaneously

Enabled (def.)

THIS DOCUMENT CONTAINS CONFIDENTIAL

Dynamic ODT Disabled

PEG Reversal (def.)

CFG(16)

*POCAFEB-12 Only (Remove in MP Model)

ME Crypto no confidentiality

LAST EDIT

CFG#

D

SAMSUNG

PART NO.

SI request

MODULE CODE

CFG(19)

Normal

PCIE Loop Back Disable(def)

C

EXCEPT AS AUTHORIZED BY SAMSUNG.

CFG(10)

A

SAMSUNG ELECTRONICS CO’S PROPERTY.

ELECTRONICS

1

DMI Lane Normal (def.)

B

APPROVAL

TITLE

4

4

PROPRIETARY INFORMATION THAT IS

Only(def.)

High

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

ME Crypto confidentiality (def.)

CFG(5)

DATE

CHECK

3

SAMSUNG PROPRIETARY

2

DMIx4 (def.)

OF

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

CANTIGA (1/5)

MCH_CANTIGA_PM_DDR2

CANNES

6713

BA41-01060A

March 10, 2009 07:55:21 AM

REV 1.0

PV

12/05/2008

undefined

KK.Bin

SH.Lee

WK.Yeo

1

DMIx2

iTPM option

SI request

C

2

SDVO or PCIE X1

REV

CFG(6) iTPM Host Interface Enable

iTPM Host Interface Disable (def.)

PCIE Loop Back Enable

DEV. STEP

2419202823

52

7

40

27

1%

100

R159

51

221

R153

16V

1%

3

4

C285

470nF

VTT_8

T7

VTT_9

T8

U7

VTT_21

U8

VTT_22

U9

V1

VTT_23

V2

VTT_24

V3

VTT_25

VTT_3

T12

VTT_4

T13

VTT_5

T2

VTT_6

T5

VTT_7

T6

VTT_11

U1

VTT_12

U10

VTT_13

U11

VTT_14

U12

VTT_15

U13

VTT_16

U2

VTT_17

U3

VTT_18

U5

VTT_19

U6

VTT_2

T11

VTT_20

VCC_NCTF_44

AC29

VCC_NCTF_5

AC30

VCC_NCTF_6

AC32

VCC_NCTF_7

AE29

VCC_NCTF_8

AE30

VCC_NCTF_9

VTTLF_1A8VTTLF_2

AB2

VTTLF_3

L1

VTT_1

T10

VTT_10

T9

VCC_NCTF_34

U30

VCC_NCTF_35

U32

VCC_NCTF_36

V29

VCC_NCTF_37

V30

VCC_NCTF_38

W29

VCC_NCTF_39

AB30

VCC_NCTF_4

W30

VCC_NCTF_40

W32

VCC_NCTF_41

Y29

VCC_NCTF_42

Y30

VCC_NCTF_43

Y32

AK29

VCC_NCTF_25

AK30

VCC_NCTF_26

AK32

VCC_NCTF_27

AL26

VCC_NCTF_28

AL28

VCC_NCTF_29

AA32

VCC_NCTF_3

AL29

VCC_NCTF_30

AL30

VCC_NCTF_31

AL32

VCC_NCTF_32

AM30

VCC_NCTF_33

AM32

VCC_NCTF_15

AH30

VCC_NCTF_16

AH32

VCC_NCTF_17

AJ29

VCC_NCTF_18

AJ32

VCC_NCTF_19

AA30

VCC_NCTF_2

AK23

VCC_NCTF_20

AK24

VCC_NCTF_21

AK25

VCC_NCTF_22

AK26

VCC_NCTF_23

AK28

VCC_NCTF_24

AC26

VCC_6

AC28

VCC_7

AC33

VCC_8

AC34

VCC_9

AE26

AA29

VCC_NCTF_1

AE32

VCC_NCTF_10

AF30

VCC_NCTF_11

AG29

VCC_NCTF_12

AG30

VCC_NCTF_13

AG32

VCC_NCTF_14

AH29

T32

VCC_28

U33

VCC_29

VCC_3

AA34

U34

VCC_30

V33

VCC_31

V34

VCC_32

W33

VCC_33

Y33

VCC_34

Y34

VCC_35

VCC_4

AB34

VCC_5

VCC_18

AG34

VCC_19

VCC_2

AA33

AH23

VCC_20

AH25

VCC_21

AH28

VCC_22

AJ23

VCC_23

AJ26

VCC_24

AJ33

VCC_25

AK33

VCC_26

AM33

VCC_27

C5

C9

H_TRDY#

VCC_1

AA28

VCC_10

AE33

VCC_11

AF23

VCC_12

AF25

VCC_13

AF28

AF33

VCC_14

AG24

VCC_15

AG25

VCC_16

AG26

VCC_17

AG33

H11

H_LOCK#

H_RCOMP

E3

B15

H_REQ#_0

K13

H_REQ#_1

F13

H_REQ#_2

B13

H_REQ#_3

B14

H_REQ#_4

B6

H_RS#_0

F12

H_RS#_1C8H_RS#_2

H_SWING

H_DSTBN#_0

M7

H_DSTBN#_1

AA5

H_DSTBN#_2

AE6

H_DSTBN#_3

L9

H_DSTBP#_0

M8

H_DSTBP#_1

AA6

H_DSTBP#_2

AE5

H_DSTBP#_3

H_DVREF

B11

H9

H_HIT#

E12

H_HITM#

H_D#_7D4H_D#_8H3H_D#_9

B10

H_DBSY#

E9

H_DEFER#

J8

H_DINV#_0

L3

H_DINV#_1

Y13

H_DINV#_2

Y1

H_DINV#_3

J11

H_DPWR#

F9

H_DRDY#

L10

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

H2

H_D#_6

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

F6

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

H6

H_D#_5

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

H_D#_35

Y12

H_D#_36

Y14

H_D#_37Y7H_D#_38W2H_D#_39

G2

H_D#_4

AA8

H_D#_40Y9H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

N6

H_D#_26

P13

H_D#_27N8H_D#_28L7H_D#_29

E6

H_D#_3

N10

H_D#_30M3H_D#_31Y3H_D#_32

AD14

H_D#_33Y6H_D#_34

Y10

H_D#_16L2H_D#_17R2H_D#_18N9H_D#_19

F8

H_D#_2

L6

H_D#_20M5H_D#_21J3H_D#_22N2H_D#_23R1H_D#_24N5H_D#_25

H_BREQ#

C12

H_CPURST#

E11

H_CPUSLP#

F2

H_D#_0G8H_D#_1

M9

H_D#_10

M11

H_D#_11J1H_D#_12J2H_D#_13

N12

H_D#_14J6H_D#_15

P2

H13

H_A#_6

C18

H_A#_7

M16

H_A#_8

J13

H_A#_9

H12

H_ADS#

B16

H_ADSTB#_0

G17

H_ADSTB#_1

H_AVREF

A11

A9

H_BNR#

F11

H_BPRI#

G12

H_A#_28

H20

H_A#_29

A14

H_A#_3

B18

H_A#_30

K17

H_A#_31

B20

H_A#_32

F21

H_A#_33

K21

H_A#_34

L20

H_A#_35

C15

H_A#_4

F16

H_A#_5

H_A#_17

B19

H_A#_18

J16

H_A#_19

E20

H_A#_20

H16

H_A#_21

J20

H_A#_22

L17

H_A#_23

A17

H_A#_24

B17

H_A#_25

L16

H_A#_26

C21

H_A#_27

J17

C23

CFG_9

HPLL_CLK

AH7

AH6

HPLL_CLK#

P16

H_A#_10

R16

H_A#_11

N17

H_A#_12

M13

H_A#_13

E17

H_A#_14

P17

H_A#_15

F17

H_A#_16

G20

CFG_17

P29

CFG_18

R28

CFG_19

P25

CFG_2

T28

CFG_20

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

T25

CFG_0

R25

CFG_1

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

32

U513-1

EB88CTPM

0904-002376

31

55

56

63

1%24.9

R158

59

11

12

1K

R154

1%

15

16

33

35

13

15

470nF

C365

16V

434439

P1.05V

48

1

2

47

60

3

6

57

4700nF

C346

10V

23

26

10

61

62

21

nostuff

R179

2.2K

36

AD

2.5V

220uF

EC7

35

P1.05V

220nF

C339

C3921

100nF

10V

8

10V

14

7 11

22000nF-X5R

C304

P1.05V

27

P1.05V

6.3V

20%

13

16

32

34

19

22

49

50

0 4

10V

C369

4700nF

2200nF

C377

10V

P1.05V

58

17

20

0

8

9

12

29

30

5

25

28

C204

470nF

16V

R151

2K

1%

34

10V

C221

100nF

31

33

37

38

10V

C376

220nF

22-D2

29

100nF

C317

10V

4

18

53

54

14

1

2

3

18

5

6

30

17

414245

46

10

EC8

220uF

2.5V

AD

21

229262425

470nF

C335

MCH1_CFG6_MN

16V

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_TRDY#

CPU1_REQ#(4:0)

CPU1_DPWR#

MCH1_HVREF

MCH1_VTTLF1_MN

MCH1_VTTLF2_MN

MCH1_VTTLF3_MN

MCH1_H_RCOMP_MN

MCH1_HXSWING

MCH1_HVREF

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

CPU1_D#(63:0)

CPU1_A#(35:3)

CPU1_ADS#

CPU1_ADSTB0#

CPU1_ADSTB1#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_SLP#

CPU1_CPURST#

CLK0_HCLK1#

CLK0_HCLK1

CPU1_DBSY#

CPU1_DEFER#

CPU1_DBI0#

MCH1_HXSWING

CPU1_DBI1#

CPU1_DBI2#

CPU1_DBI3#

CPU1_DRDY#

CPU1_DSTBN0#

CPU1_DSTBN1#

CPU1_DSTBN2#

CPU1_DSTBN3#

CPU1_DSTBP0#

CPU1_DSTBP1#

CPU1_DSTBP2#

CPU1_DSTBP3#

CPU1_HIT#

CPU1_HITM#

CPU1_LOCK#

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

R720

8-13

8-14

8. Block Diagram and Schematic

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

R720

Samsung

Confidential

2 OF 5

LVDSHDA

NC RSVD

GFX VCC NCTF

GFX VCC NCTF

GFX VCC

TV VGA

PCIE GFX

PCIE GFX

DMICLKMEPMMISC

1608 Size

RSVD10

RSVD11

RSVD12

RSVD13

ELECTRONICS

DEV. STEPCHECK

A

SAMSUNG ELECTRONICS CO’S PROPERTY.

1

D

PART NO.

OF

SAMSUNG

REV

1

DRAW

Added by EMC

500 ohm for Cantiga

24

B

3

A

B

TITLE

EXCEPT AS AUTHORIZED BY SAMSUNG.

APPROVAL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

WK.Yeo

SH.Lee

KK.Bin

undefined

12/05/2008

PV

REV 1.0

March 10, 2009 07:55:21 AM

BA41-01060A

14

CANNES

MCH_CANTIGA_PM_DDR2

CANTIGA (2/5)

D:/users/mobile20/mentor/cannes/PV1/Backup/cannes_PV_090309

3

MODULE CODE LAST EDIT

PAGE

C

DATE

SAMSUNG PROPRIETARY

C

PROPRIETARY INFORMATION THAT IS

4

THIS DOCUMENT CONTAINS CONFIDENTIAL

D

2

1310

100nF

C627

10

C614

100nF

R203

499

1%

14

C664

100nF

100nF

C658

P3.3V

R170

10K

VCC_AXG_NCTF_59

Y17

VCC_AXG_NCTF_6

AC16

VCC_AXG_NCTF_60

Y19

VCC_AXG_NCTF_7

AC17

VCC_AXG_NCTF_8

AE16

VCC_AXG_NCTF_9

AE17

VCC_AXG_NCTF_49

W17

VCC_AXG_NCTF_5

AB19

VCC_AXG_NCTF_50

W19

VCC_AXG_NCTF_51

W20

VCC_AXG_NCTF_52

W21

VCC_AXG_NCTF_53

W23

W24

VCC_AXG_NCTF_54

VCC_AXG_NCTF_55

W25

VCC_AXG_NCTF_56

W26

VCC_AXG_NCTF_57

W28

VCC_AXG_NCTF_58

Y16

V16

VCC_AXG_NCTF_4

AB17

VCC_AXG_NCTF_40

V17

VCC_AXG_NCTF_41

V19

VCC_AXG_NCTF_42

V21

VCC_AXG_NCTF_43

V23

VCC_AXG_NCTF_44

V24

V25

VCC_AXG_NCTF_45

V26

VCC_AXG_NCTF_46

VCC_AXG_NCTF_47

V28

VCC_AXG_NCTF_48

W16

VCC_AXG_NCTF_3

AB16

VCC_AXG_NCTF_30

AM16

VCC_AXG_NCTF_31

AM17

VCC_AXG_NCTF_32

AM19

VCC_AXG_NCTF_33

AM20

VCC_AXG_NCTF_34

AM21

VCC_AXG_NCTF_35

U16

VCC_AXG_NCTF_36

U19

VCC_AXG_NCTF_37

U20

VCC_AXG_NCTF_38

U21

VCC_AXG_NCTF_39

VCC_AXG_NCTF_2

AA19

VCC_AXG_NCTF_20

AJ16

VCC_AXG_NCTF_21

AJ19

VCC_AXG_NCTF_22

AK16

VCC_AXG_NCTF_23

AK17

VCC_AXG_NCTF_24

AK19

AK20

VCC_AXG_NCTF_25

VCC_AXG_NCTF_26

AK21

VCC_AXG_NCTF_27

AL16

VCC_AXG_NCTF_28

AL19

VCC_AXG_NCTF_29

AL21

AA16

VCC_AXG_NCTF_10

AE19

VCC_AXG_NCTF_11

AF16

VCC_AXG_NCTF_12

AF17

VCC_AXG_NCTF_13

AF19

VCC_AXG_NCTF_14

AG16

VCC_AXG_NCTF_15

AG17

AG19

VCC_AXG_NCTF_16

AH16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

AH17

VCC_AXG_NCTF_19

AH19

VCC_AXG_38

Y15

VCC_AXG_39

VCC_AXG_4

AA23

Y21

VCC_AXG_40

Y24

VCC_AXG_41

Y26

VCC_AXG_42

VCC_AXG_5

AA24

VCC_AXG_6

AA25

VCC_AXG_7

AB15

VCC_AXG_8

AB20

VCC_AXG_9

AB23

VCC_AXG_NCTF_1

VCC_AXG_29

AL15

VCC_AXG_3

AA21

VCC_AXG_30

AM14

VCC_AXG_31

AM15

VCC_AXG_32

AN14

VCC_AXG_33

T14

T16

VCC_AXG_34

VCC_AXG_35

T17

U14

VCC_AXG_36

U15

VCC_AXG_37

V15

AE24

VCC_AXG_2

AA20

VCC_AXG_20

AE25

VCC_AXG_21

AF15

VCC_AXG_22

AF20

VCC_AXG_23

AG15

VCC_AXG_24

AG21

AH15

VCC_AXG_25

AH20

VCC_AXG_26

VCC_AXG_27

AJ15

VCC_AXG_28

AJ21

H24

VCC_AXG_1

AA15

VCC_AXG_10

AB25

VCC_AXG_11

AC20

VCC_AXG_12

AC21

VCC_AXG_13

AC23

VCC_AXG_14

AC24

VCC_AXG_15

AE15

VCC_AXG_16

AE20

VCC_AXG_17

AE21

VCC_AXG_18

AE23

VCC_AXG_19

RSVD_9

AY21

G36

SDVO_CTRLCLK

E36

SDVO_CTRLDATA

T20

THERMTRIP#

B12

TSATN#

TVA_DAC

F25

H25

TVB_DAC

TVC_DAC

K25

TV_DCONSEL_0

C31

TV_DCONSEL_1

E32

TV_RTN

RSVD_19

RSVD_2

AH12

RSVD_20

R33

RSVD_21

T24

RSVD_22

T33

RSVD_3

AH13

RSVD_4

AH9

RSVD_5

AK34

RSVD_6

AL34

AM35

RSVD_7

AN35

RSVD_8

AT11

RSVD_1

AH10

RSVD_10

B2

RSVD_11

B31

RSVD_12

BF18

RSVD_13

BF23

RSVD_14

BG23

RSVD_15

BH18

K12

RSVD_16

RSVD_17

M1

M36

RSVD_18

N36

PEG_TX_5

R47

N37

PEG_TX_6

T39

PEG_TX_7

PEG_TX_8

U36

U39

PEG_TX_9

B7

PM_DPRSTP#

N33

PM_EXT_TS#_0

P32

PM_EXT_TS#_1

R29

PM_SYNC#

AT40

PWROK

RSTIN#

J42

L46

PEG_TX_1

Y39

PEG_TX_10

Y46

PEG_TX_11

AA36

PEG_TX_12

AA39

PEG_TX_13

AD42

PEG_TX_14

AD46

PEG_TX_15

M48

PEG_TX_2

M39

PEG_TX_3

M43

PEG_TX_4

AA40

PEG_TX#_14

AD43

AC46

PEG_TX#_15

M47

PEG_TX#_2

PEG_TX#_3

M40

M42

PEG_TX#_4

R48

PEG_TX#_5

N38

PEG_TX#_6

T40

PEG_TX#_7

U37

PEG_TX#_8

U40

PEG_TX#_9

PEG_TX_0

PEG_RX_5

P47

N43

PEG_RX_6

T42

PEG_RX_7

PEG_RX_8

U42

Y42

PEG_RX_9

J41

PEG_TX#_0

M46

PEG_TX#_1

Y40

PEG_TX#_10

AA46

PEG_TX#_11

AA37

PEG_TX#_12

PEG_TX#_13

H43

J44

PEG_RX_1

W47

PEG_RX_10

Y37

PEG_RX_11

AA42

PEG_RX_12

AD36

PEG_RX_13

AC48

PEG_RX_14

AD40

PEG_RX_15

L43

PEG_RX_2

L41

PEG_RX_3

N40

PEG_RX_4

AD37

PEG_RX#_14

AC47

AD39

PEG_RX#_15

L44

PEG_RX#_2

PEG_RX#_3

L40

N41

PEG_RX#_4

P48

PEG_RX#_5

N44