Samsung np-r610 Schematics

Samsung

Confidential

SRP Sheet Number: 1 of 73

Intel PENRYN

EXCEPT AS AUTHORIZED BY SAMSUNG.

3

A

SAMSUNG PROPRIETARY

EXCEPT AS AUTHORIZED BY SAMSUNG.

4

SAMSUNG ELECTRONICS CO’S PROPERTY.

PCB Code :

Model Name :

Owner :

00

D

1

C

CPU :

SEC Mobile R & D

T.R. Date :

13

MAIN

TPT : BA41-00919A

DRAW

D

Montevina Platform (NB9M)

ISTANBUL

SAMSUNG ELECTRONICS CO’S PROPERTY.

ISTANBUL

4

APPROVAL

4

A

Remarks :

THIS DOCUMENT CONTAINS CONFIDENTIAL

Revision :

THIS DOCUMENT CONTAINS CONFIDENTIAL

4

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

2

1

Intel CANTIGA PM + ICH9M

PV

ELECTRONICS

NAN : BA41-00921A

Chip Set :

C

Dev. Step :

1

X

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

SAMSUNG

4

PROPRIETARY INFORMATION THAT IS

GCE : BA41-00920A

2

2008.07.18

2

CHECK

2

BB

PBA Name :

3

3

PROPRIETARY INFORMATION THAT IS

Signature :

SAMSUNG PROPRIETARY

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

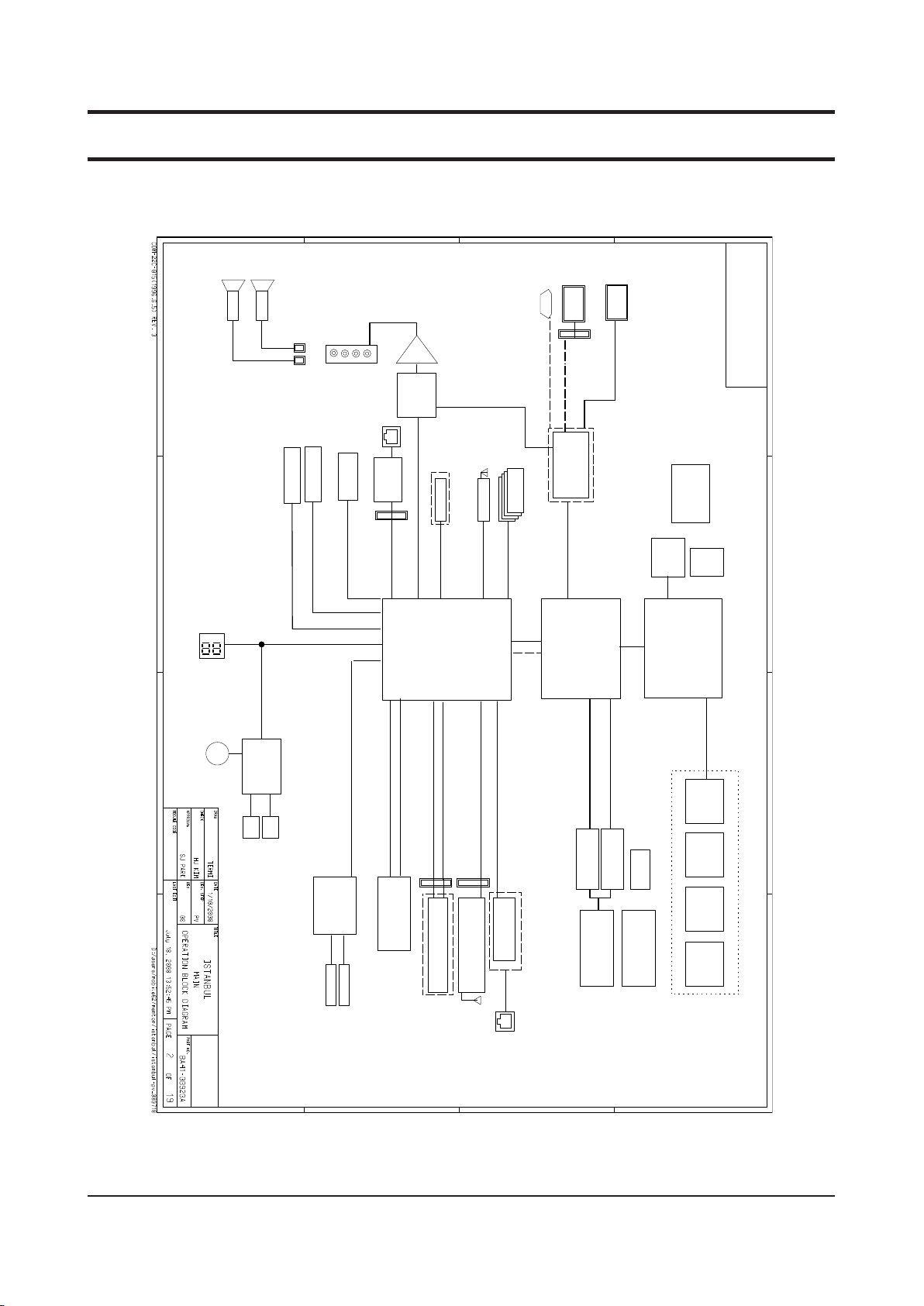

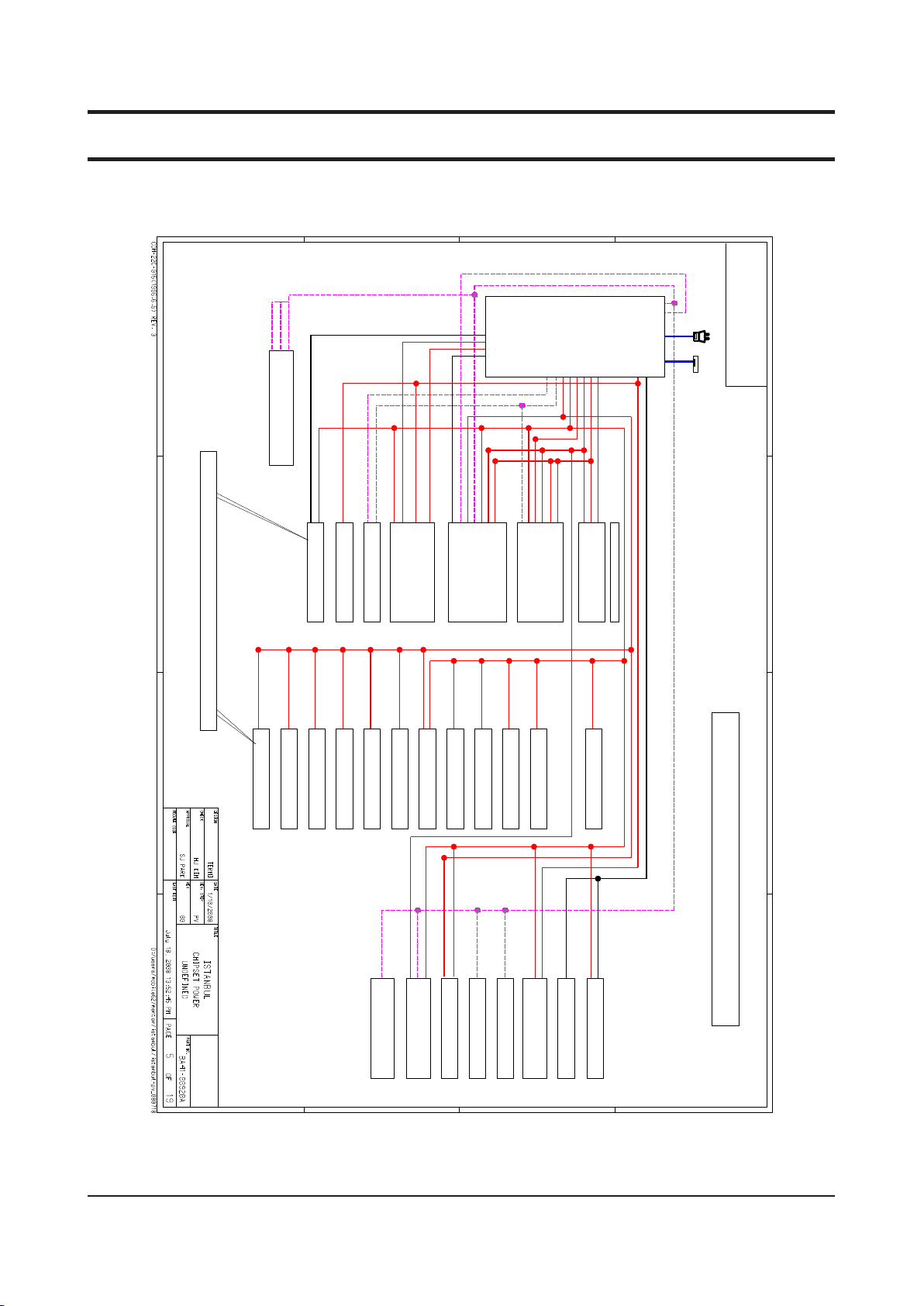

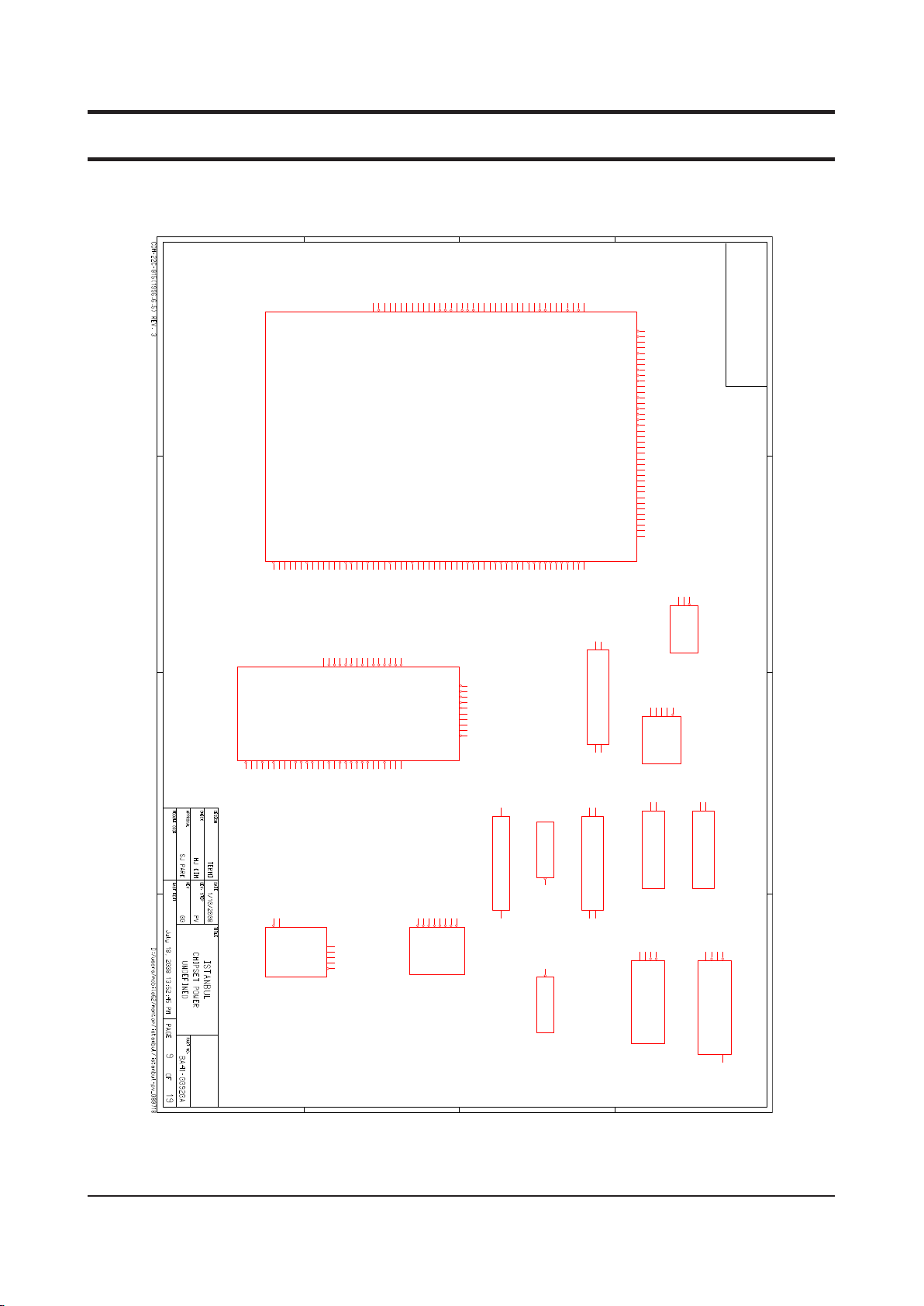

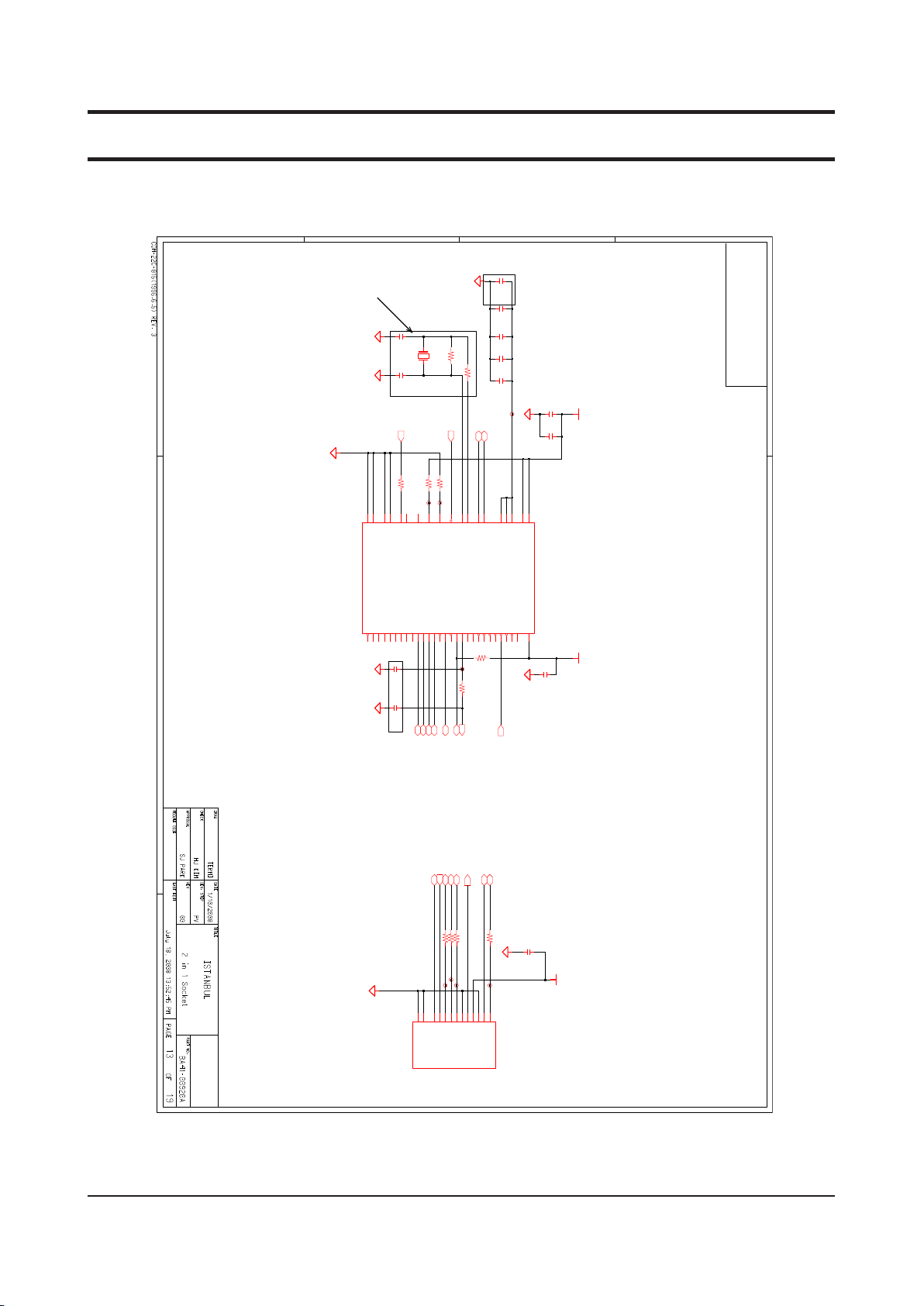

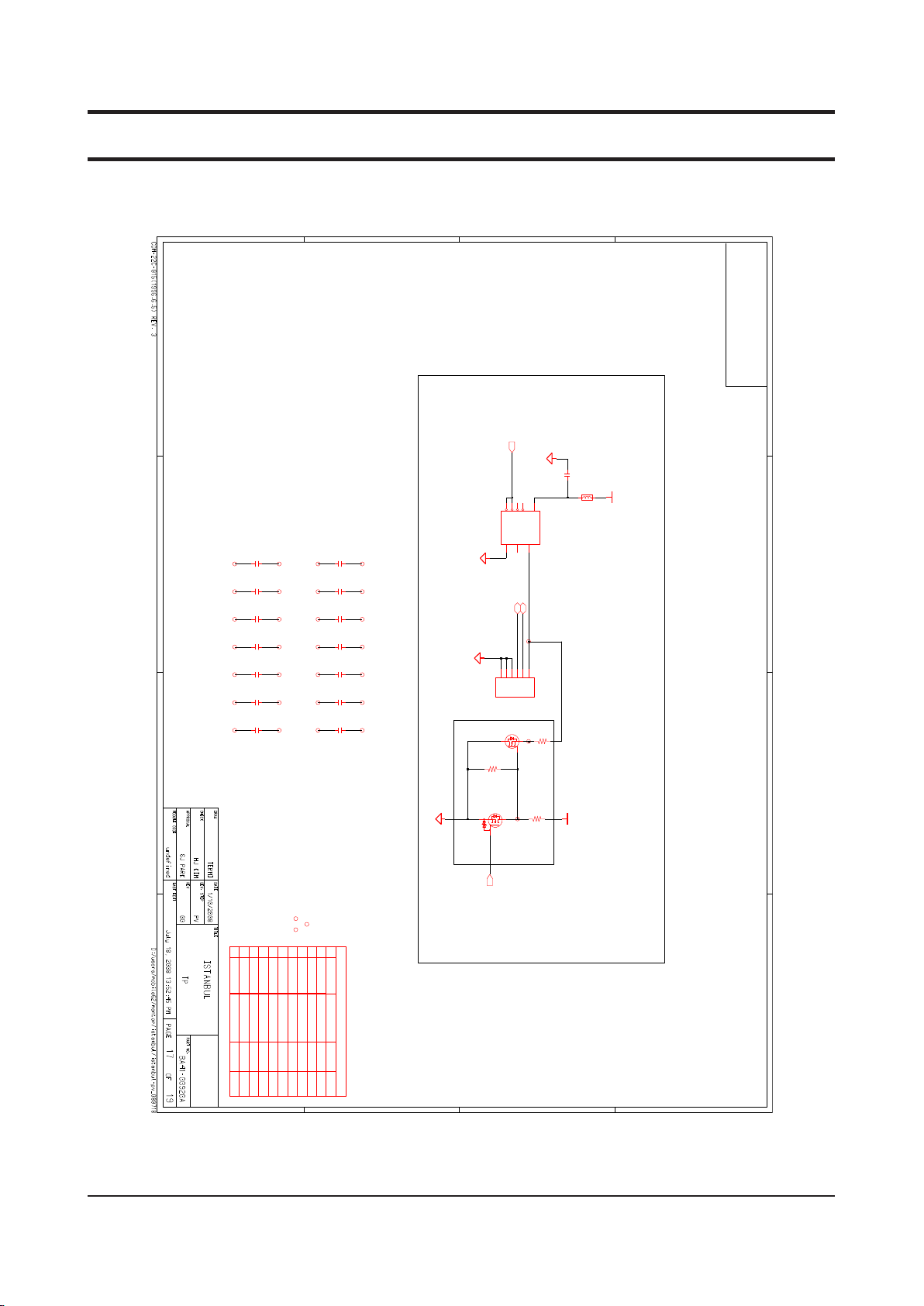

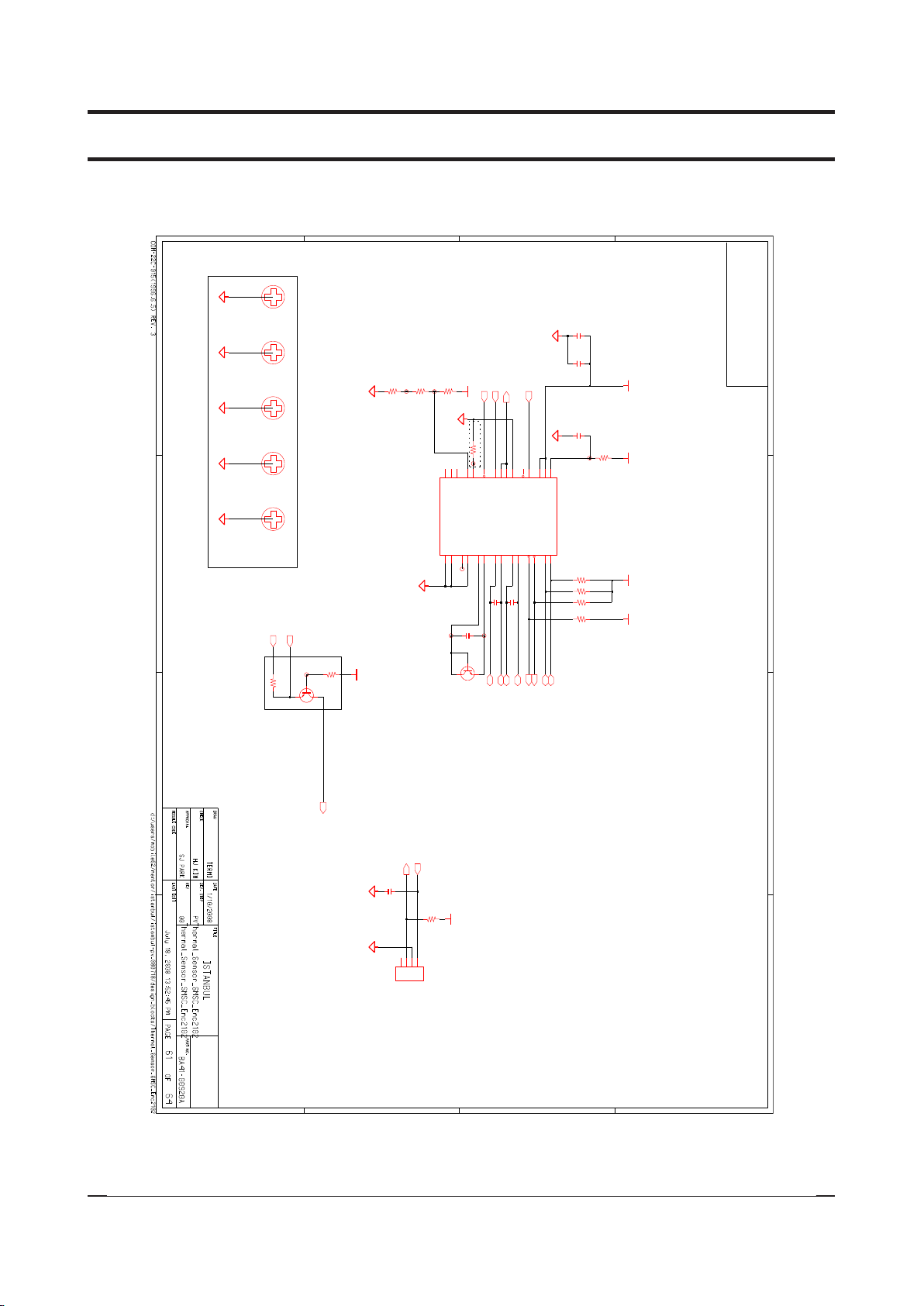

8. Block Diagram and Schematic

8-1

8-1

8-2

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

2

3

1

4

SPDIF.

PG 48

USB 0,1,2

USB 0,1,2

Direct Media Interface

x4, 1.5V

CLINK

C

PG 30

PG 33

HDMI

LCD

CRT

PG 30

LCD

CRT

OPTION

Ext. PEG

NB9X

PEG x16

External Graphics

Cantiga-PM

MCH-M

1299 FCBGA

PG 13 - 17

PM975

667/800 MT/S

FSB

A

SPKR L

SPKR R

MIC-IN

4

3

80 Port

PG 25

2P

2P

PG 43

PG 41

PG 41

SATA

SATA

HDD

ODD

Confidential

Confidential

Confidential

SATA 1

SATA 0

3.3V LPC, 33MHz

LPC

HP

PG 25

SPI ROM

SPI

B

High Definition Audio

PG 43

AMP

Aud.

ALC262

Audio

12P

HD Primary

PG 20 - 24

HDAUDIO

PG 50

Camera

OPTION

USB 7

676 BGA

PG 50

ANT

Bluetooth

USB 5

ICH9-M

PG 45

PG 42

PG 48

RJ11

Modem

MDC

Samsung

Samsung

Samsung

PG 48

HD Secondary

PG 8 PG 55

Thermistor

(TBD)

CPU

PG 9

PG 10,11,12

FSB 1067

478pin

L2 Cache : 6/3MB

D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

Clocking

CK-505

PG 9

FAN

Mobile Processor

Penryn-6M

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

LED

2

1

SRP Sheet Number: 2 of 73

PG 51

SAMSUNG

ELECTRONICS

A

PG 49

TMKBC (TBD)

H8S-2110B

MICOM

Touch

KBD

PAD

PG 50

PG 50

PG 28

AU6371

CardBus

PG 39

USB X

2 IN 1

M/S(SD...)

PG 39

OPTION

B

USB X

PCIE x1

Lane X

Express Card

PG 27

PCIE x1

USB 6

Lane 4

PG 40

52P

Mini Card 2

PG 40

Mini Card 1

PG 48

PCIE x1

Lane 1

52P

ANT

PG 47

PCIE x1

Lane 3

8055

RJ45

Channel A (Reverse)

Channel B (Reverse)

Dual channel

DDR III 1067/800

DDR III 1067/800

DC/DC

IMVP-6

CPU

PG 57

ON BOARD

Module

PG 55

PG 56

D

Charging

Circuit

Battery

DC/DC

Smart

DDR III

SODIMM 1

DDR III

SODIMM 0

Termination

PG 18,19

PG 19

PG 18

VCCP / DC-DC

DDR III Power

PG 53

PG 54

C

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

2

4

3

1

- This Document can not be used without Samsung's authorization -

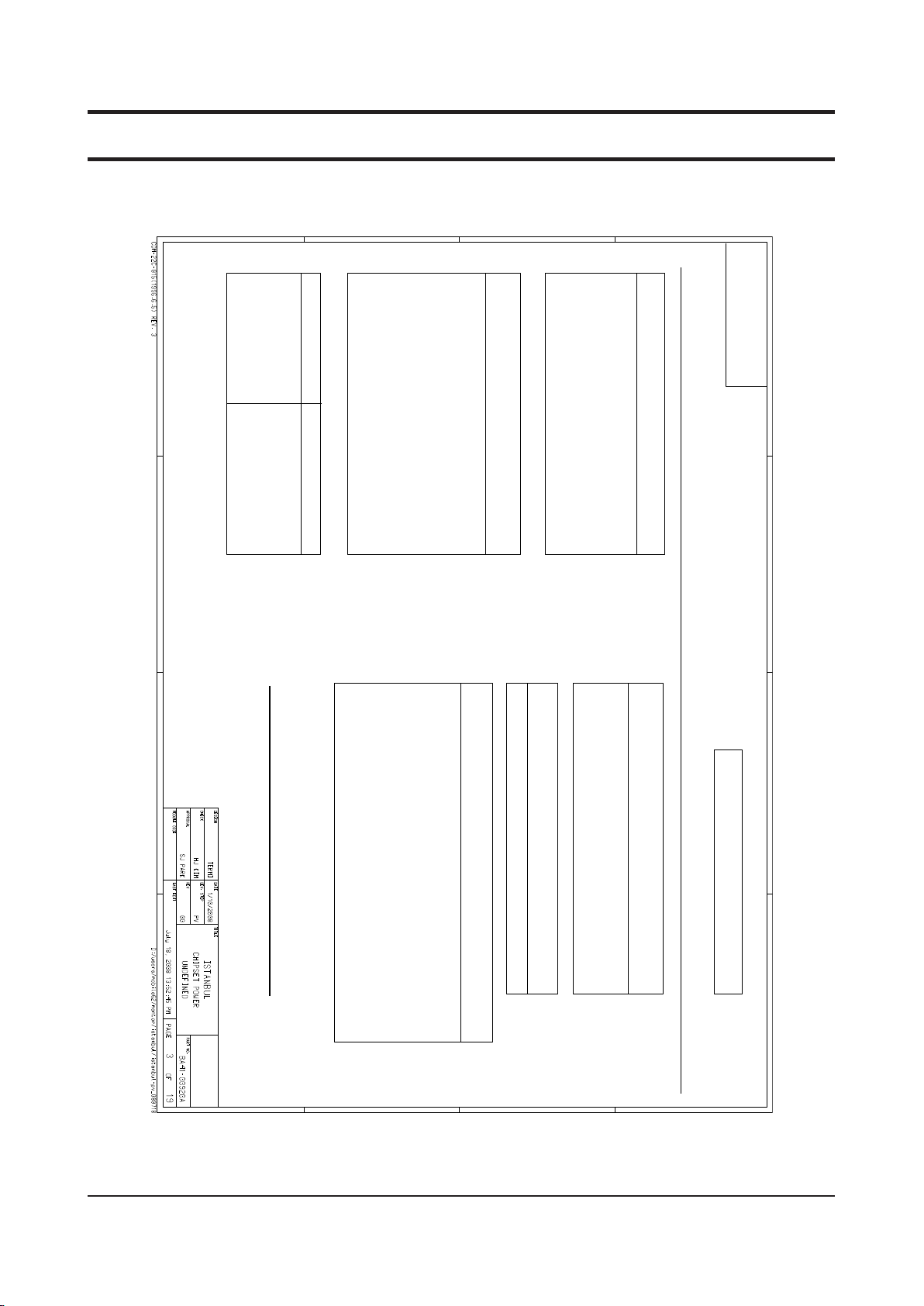

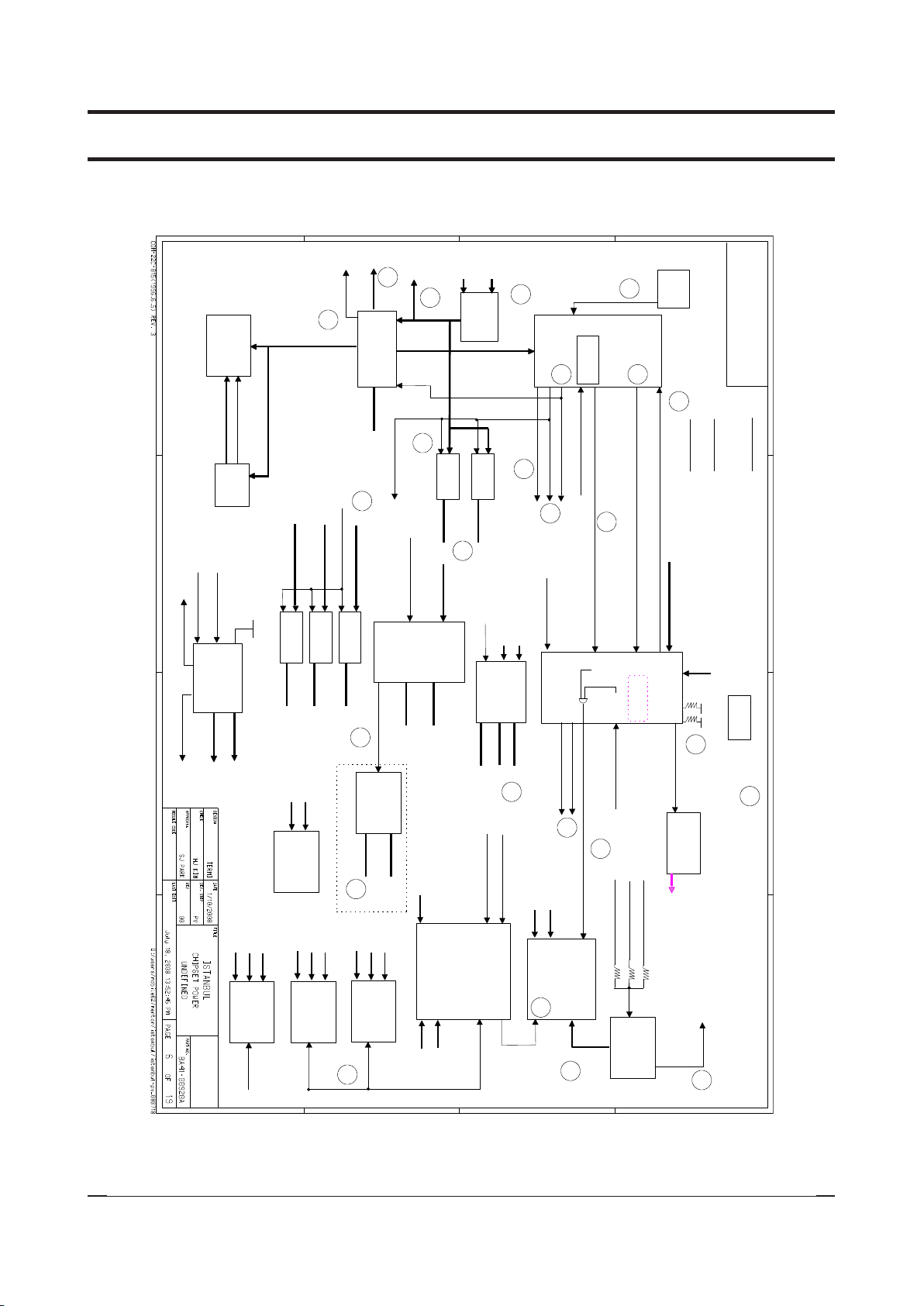

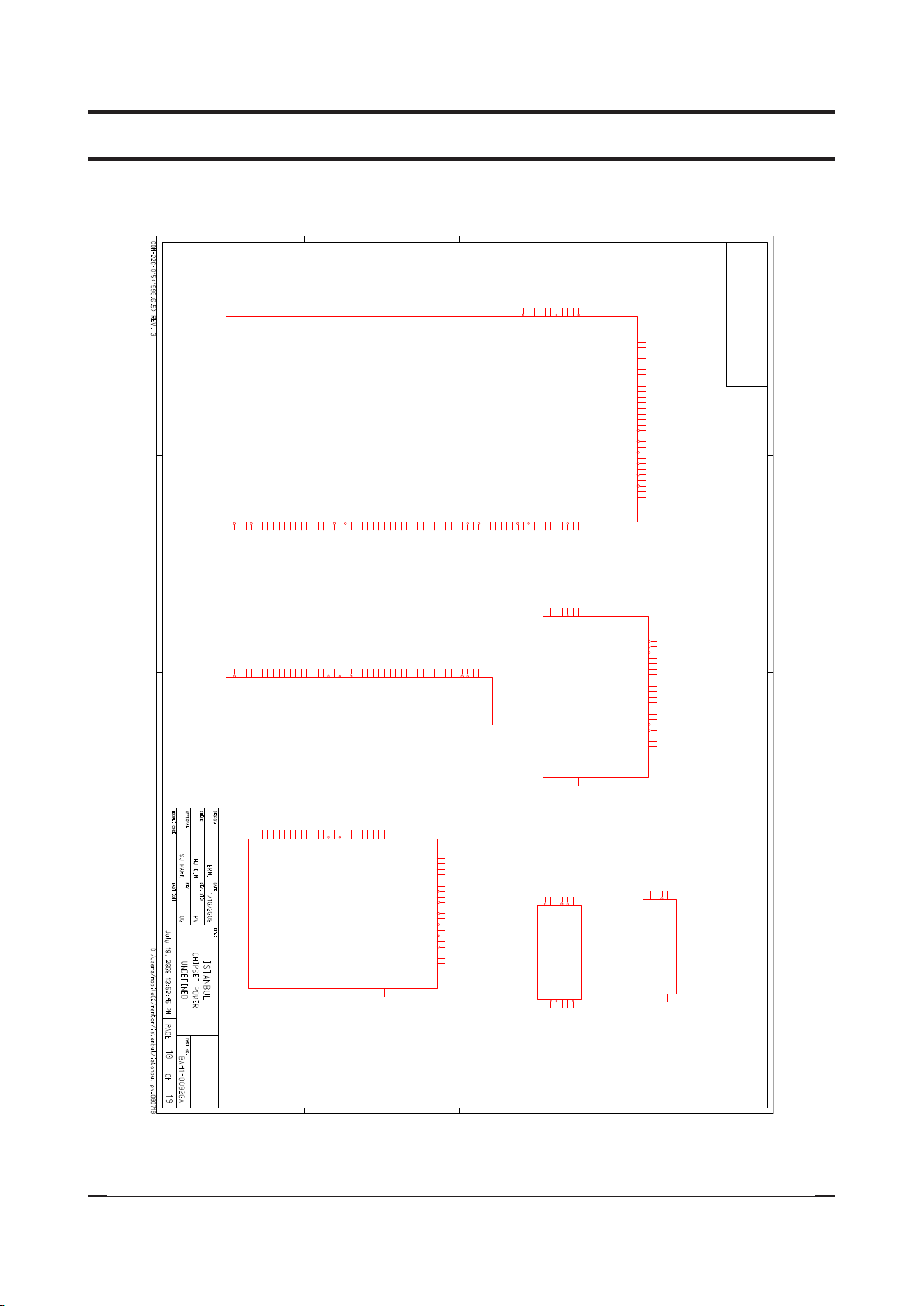

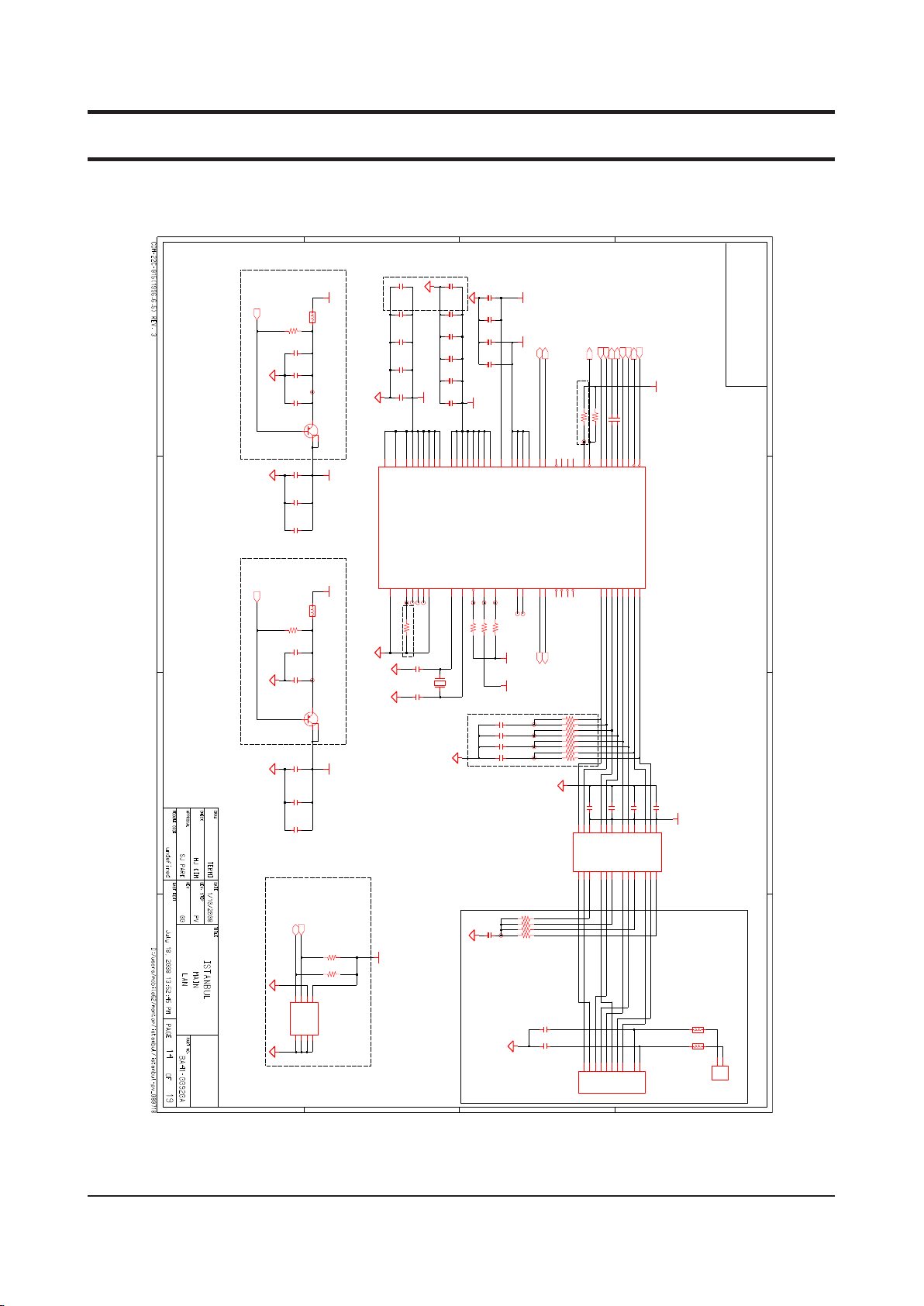

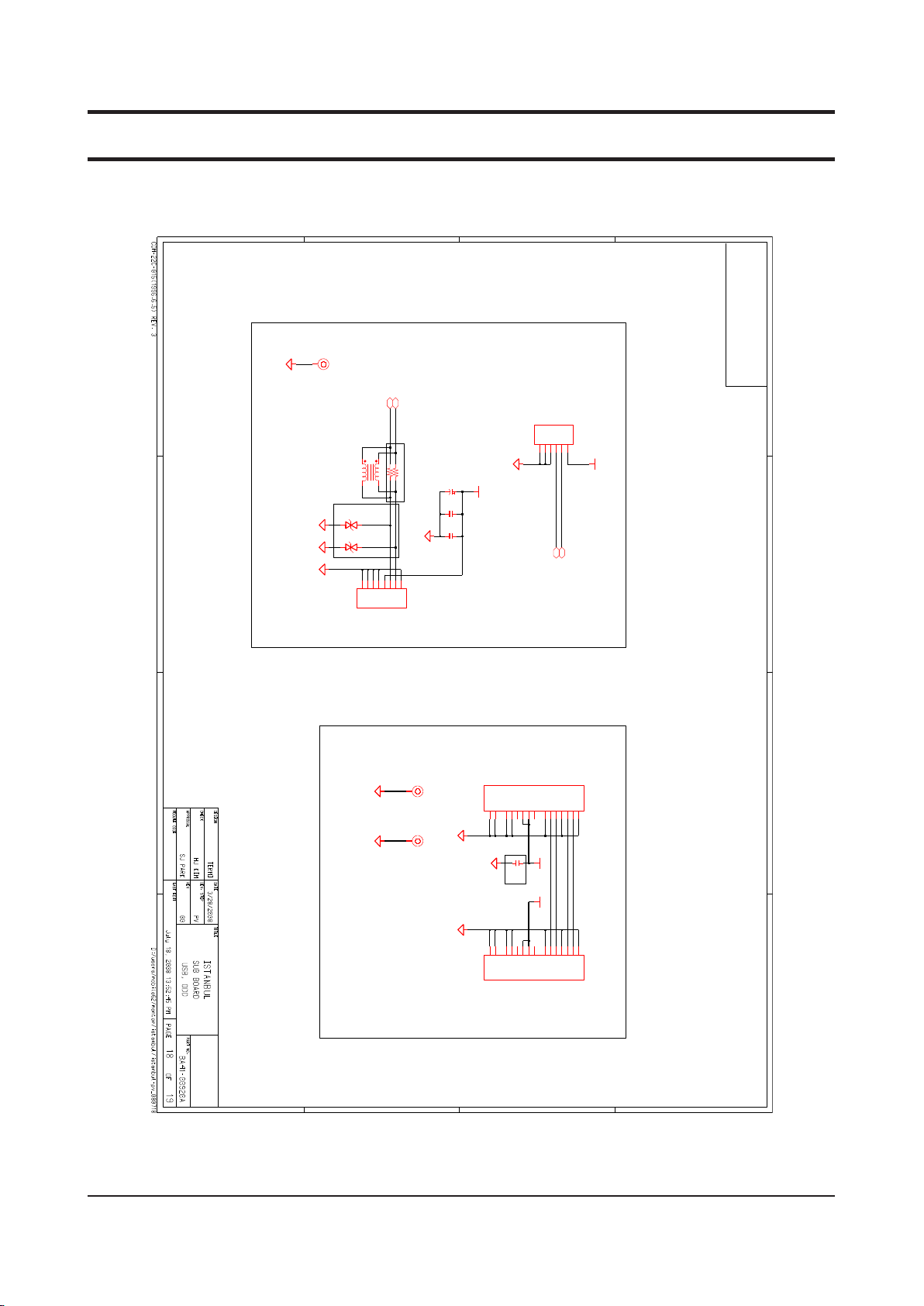

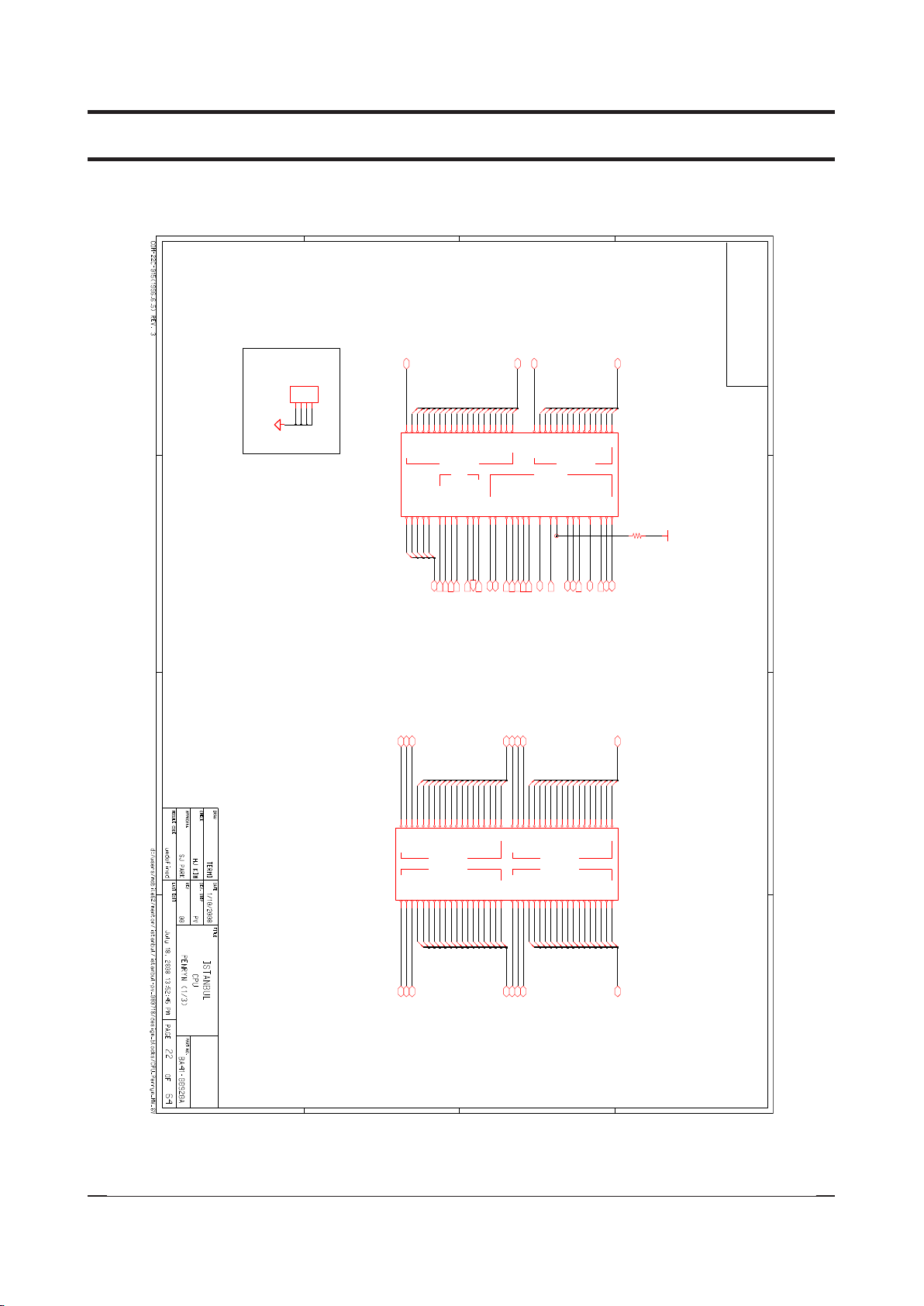

8. Block Diagram and Schematic

A

PORT #

USB PORT Assign

NC

NC

Mini PCI Express 2

SYSTEM PORT 1

ASSIGNED TO

SYSTEM PORT 0

NC

Camera

Bluetooth

SYSTEM PORT 2

4

3

NC

PORT #

4

5

NC

Mini Card 2 (ROBSON or DVB-T)

PCI Express Assign

3

0

1

2

NC

Mini Card 1 (WLAN)

NC

LOM

ASSIGNED TO

Confidential

Confidential

Confidential

B

P5.0V_AUX

P0.9V

P3.3V

P1.8V

P1.05V (VCCP)

P3.3V_AUX

P3.3V_MICOM

P5.0V

P1.5V

VCC_CORE

P5.0V_ALW

5.0V always power rail

5.0V switched on power rail (off in S4-S5)

5.0V switched power rail (off in S3-S5)

Samsung

Samsung

Samsung

GFX_CORE

P1.8V_AUX

VDC

VTT for CPU, Crestline & ICH8-M

1.8V switched power rail (off in S3-S5)

0.9V power rail for DDR (off in S3-S5)

1.5V switched power rail (off in S3-S5)

1.8V power rail for DDR (off in S4-S5)

3.3V switched on power rail (off in S4-S5)

Core Voltage for CPU

3.3V always power rail (for Micom)

3.3V switched power rail (off in S3-S5)

Primary DC system power supply (7 to 21V)

Core Voltage for GPU

C C

Voltage Rails

GLAN

-

-

F

A B

C

L

i

n

k

-

-

LPC bridge/IDE/AC97/SMBUS

Internal MAC

USB

Hub to PCI

AD30(internal)

AD24(internal)

AD29(internal)

AD31(internal)

-

-

-

-

USB2.0 #3 (USB5) : E

USB2.0 #0 (USB0) : A

-

B

USB2.0 #1 (USB1) : D

USB2.0 #4 (EHCI) : H

E

USB2.0 #2 (USB4) : C

Cardbus

AD25

3

A,B,C

D

PCI Devices

e

iv

ec

s

I

D

ES

#L

REQ/GNT#

Interrupts

D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

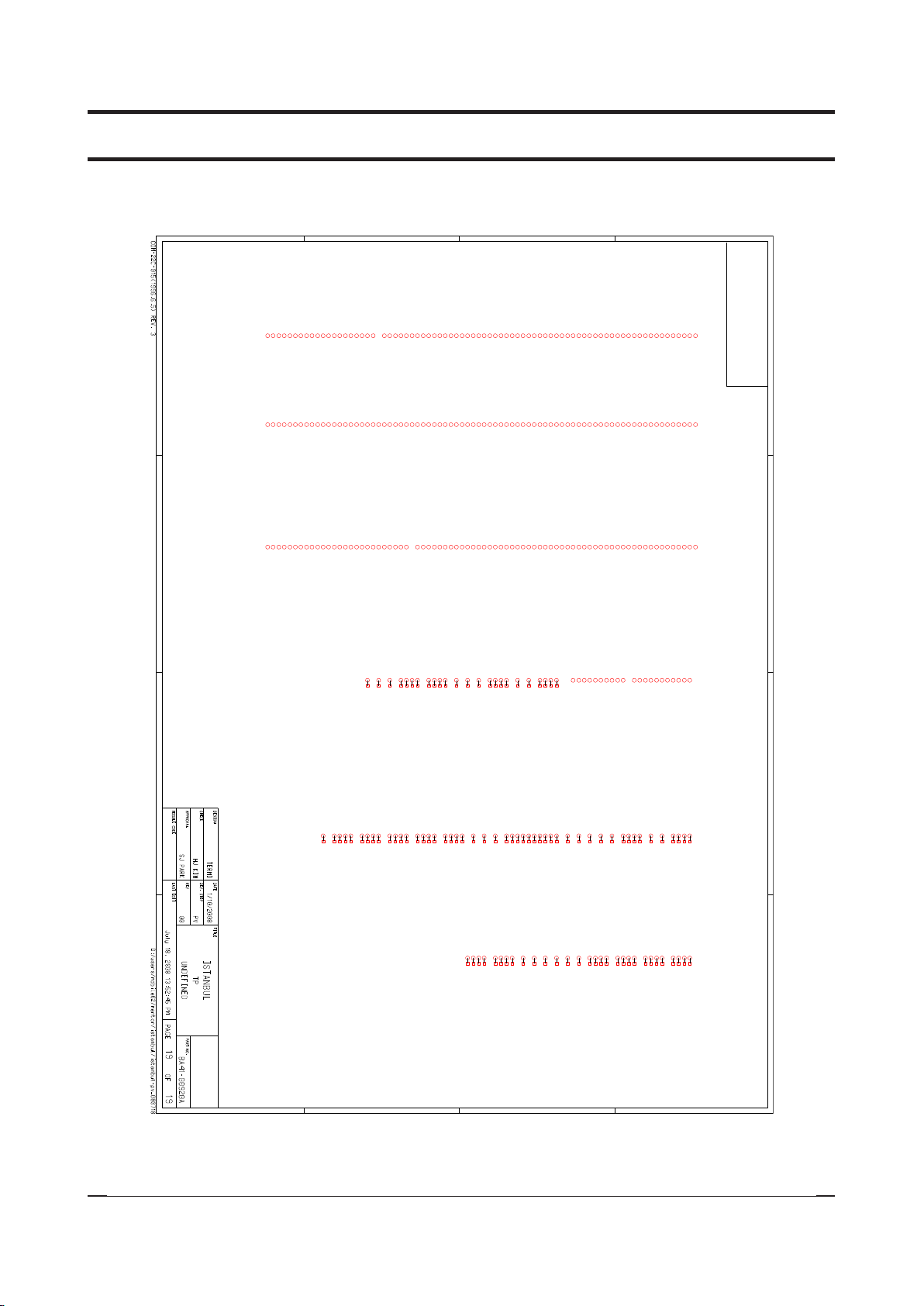

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

SAMSUNG PROPRIETARY

2

1

SRP Sheet Number: 3 of 73

SAMSUNG

ELECTRONICS

REVISION HISTORY

See rev notes for more information.

A

CK-505M (Clock Generator) 1101 001x

D2h

Clock, Unused Clock Output Disable

B

SODIMM0

I C / SMB Address

D

Thermal Sensor on SODIMM1

SODIMM1

ICH8-m

CPU Thermal Sensor

Thermal Sensor on SODIMM0

e

v

i

c

e

0011 000x

1010 010x

0011 010x

0111 101x

1010 000x

Master

dAs

d

r

e

s

s

-

A0h

34h -

A4h

Hex

7Ah

30h

SMBUS Master

Thermal Sensor

-

-

Bus

-

LCD Pannel Detect

Devices

Resolution

(TBD)

PANNEL_DETECT_0

Crystal

25MHz

LAN

Intel LAN

Crystal

Crystal / Oscillator

Crystal

Crystal

TYPE

32.768KHz

14.318MHz

10MHz

FREQUENCY

M

CLOCK-Generator

DEVICE

ICH8-M

I

C

O

M

H

CK-505

USAGE

Real Time Clock

D

F46

2

961

/

612

0

BOARD INFORMATION

D

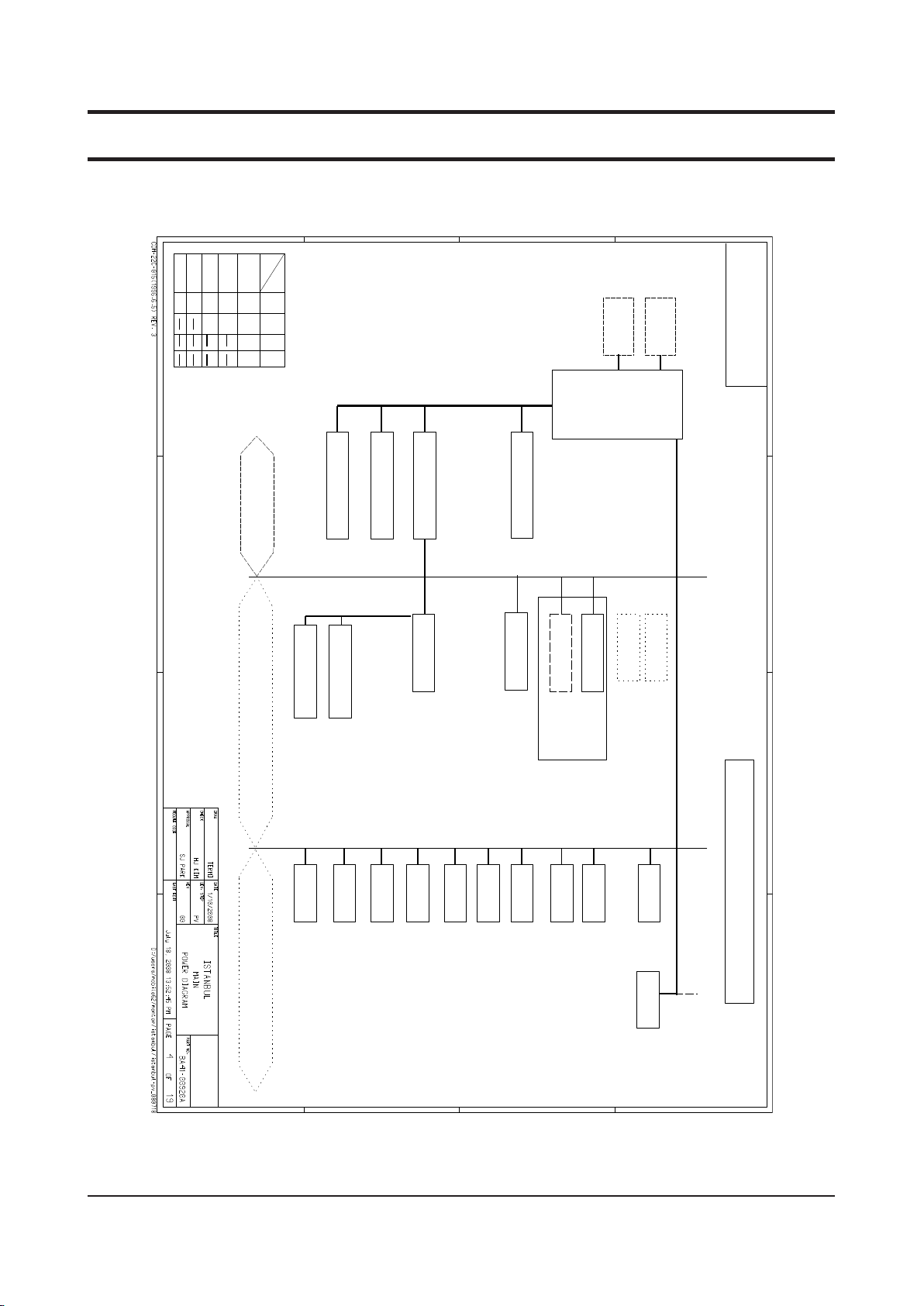

8-3

8-4

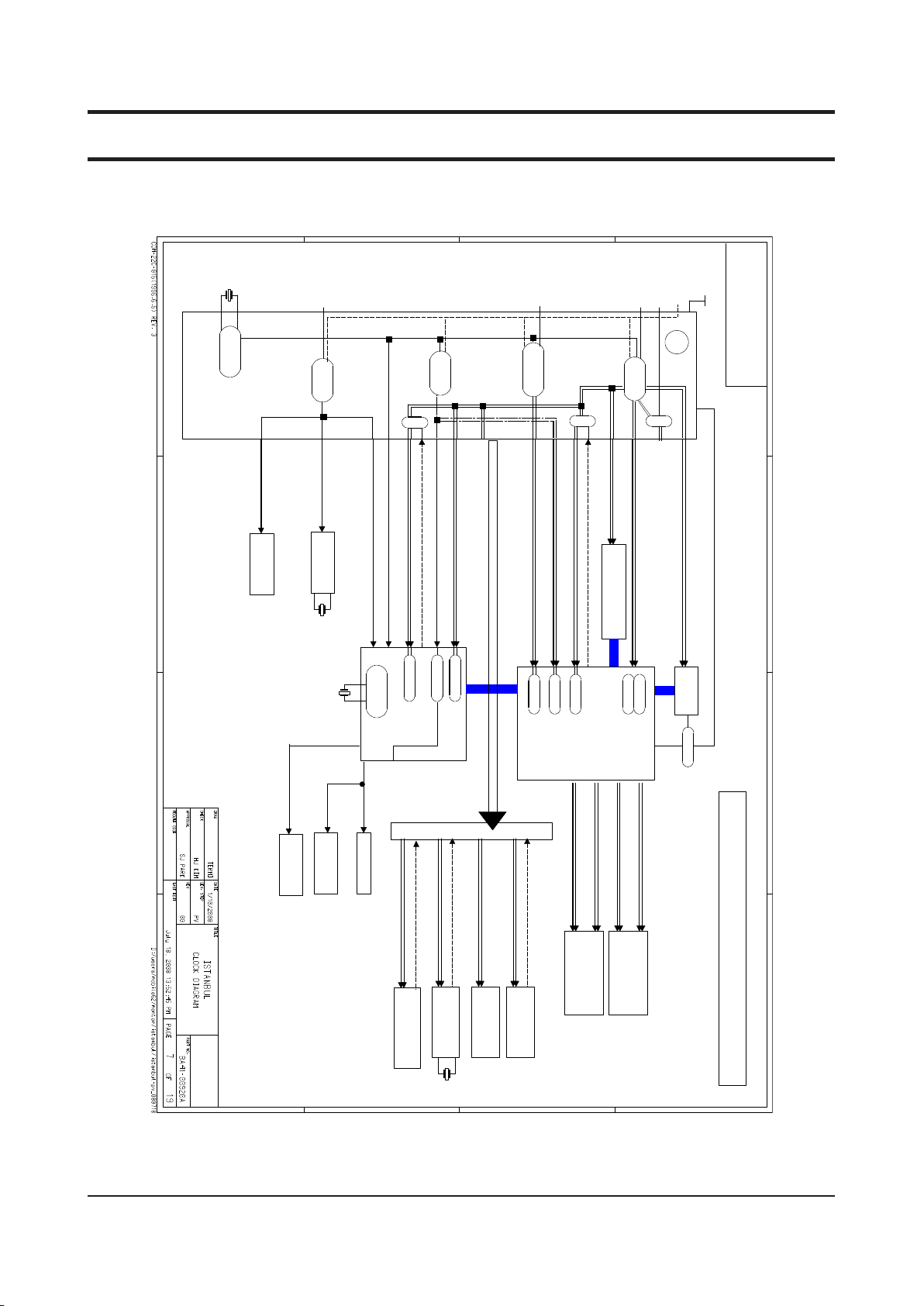

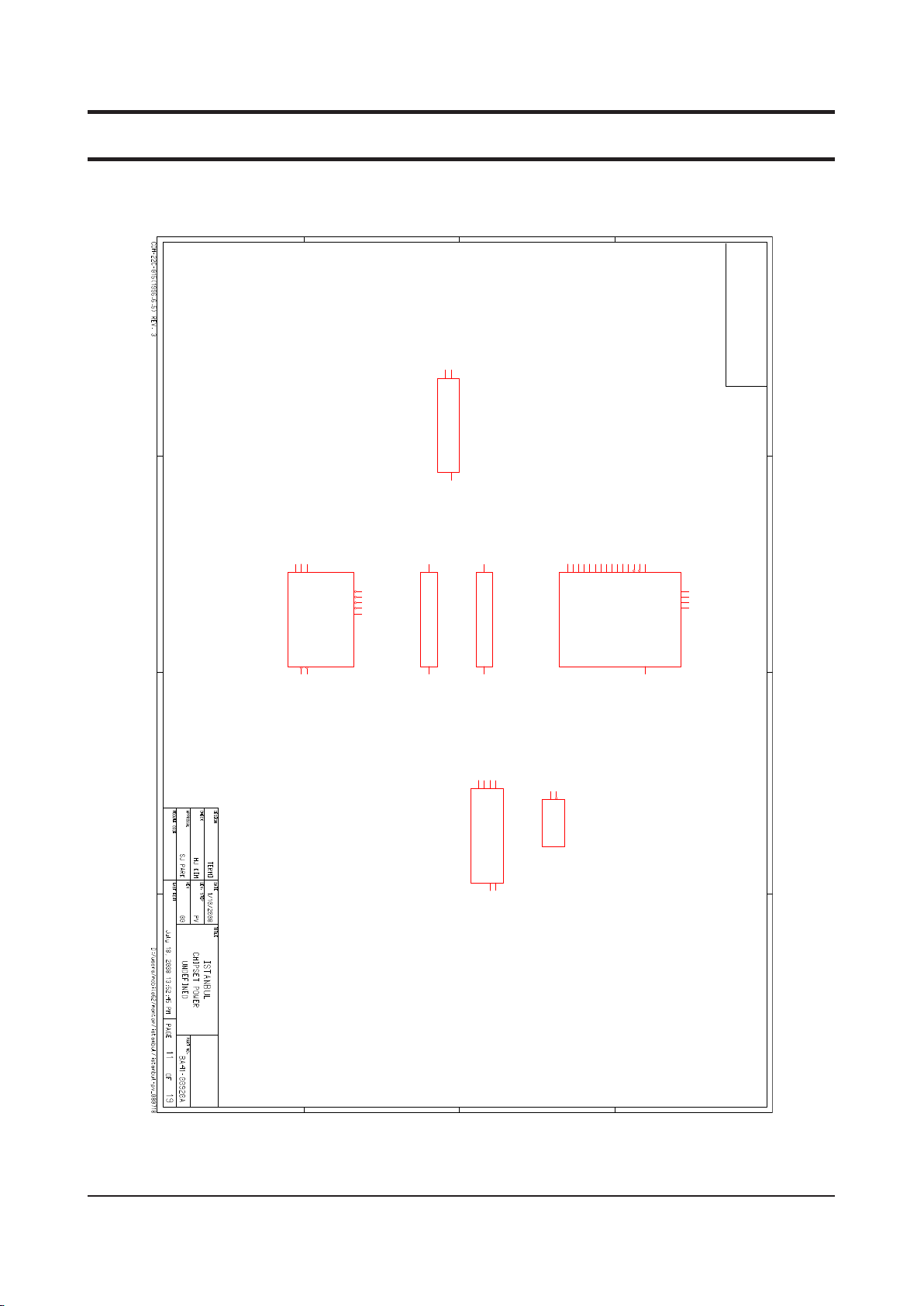

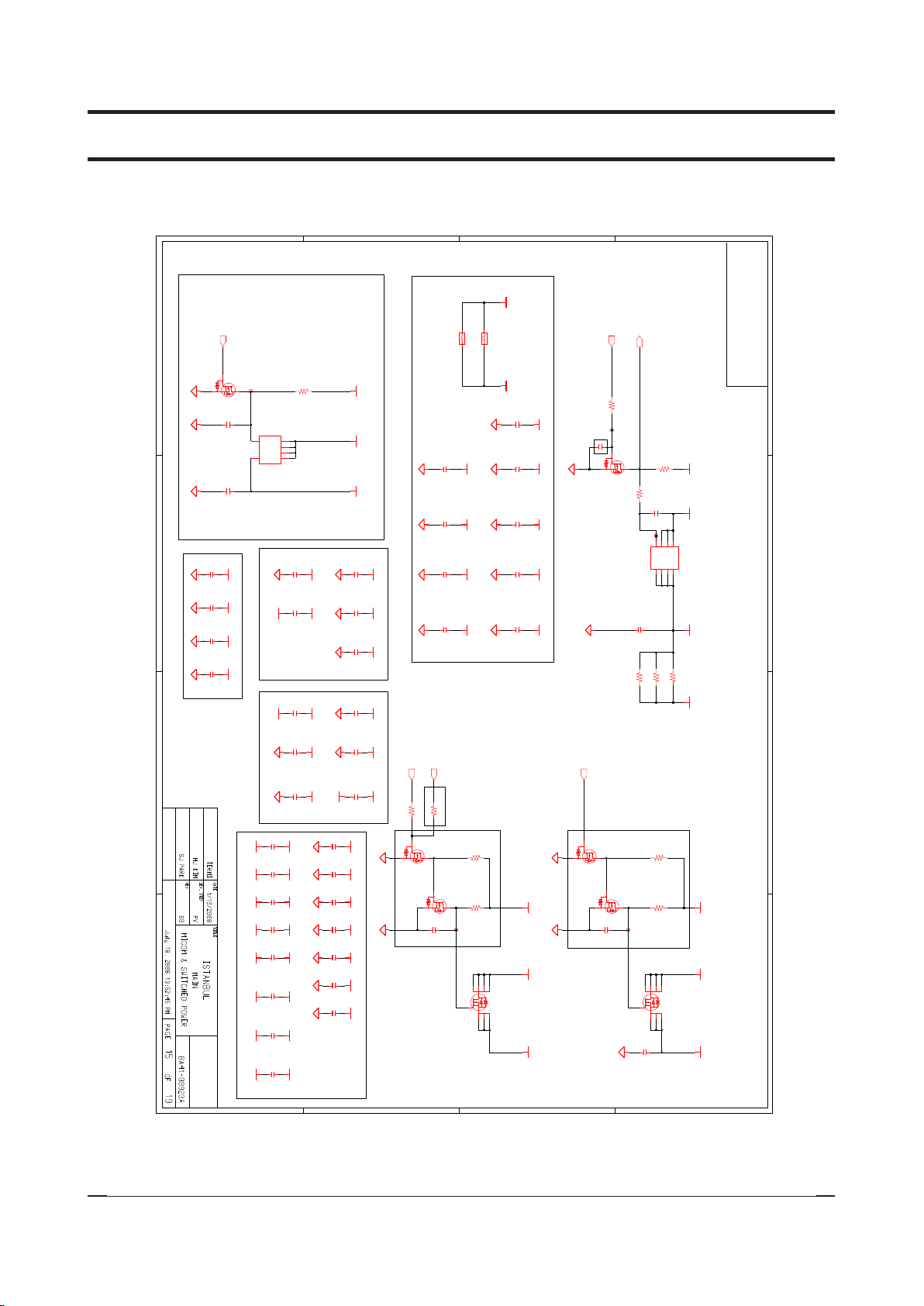

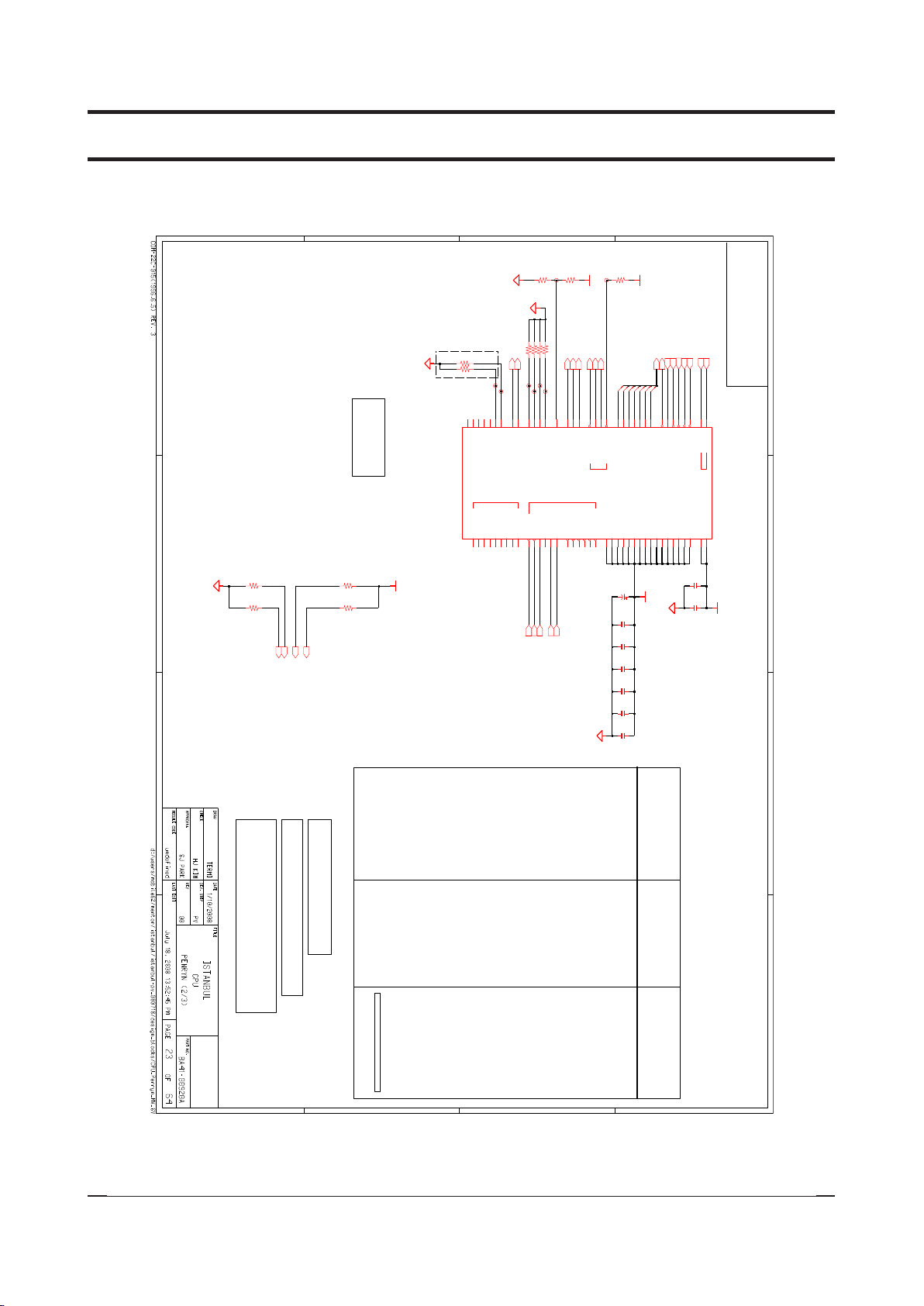

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

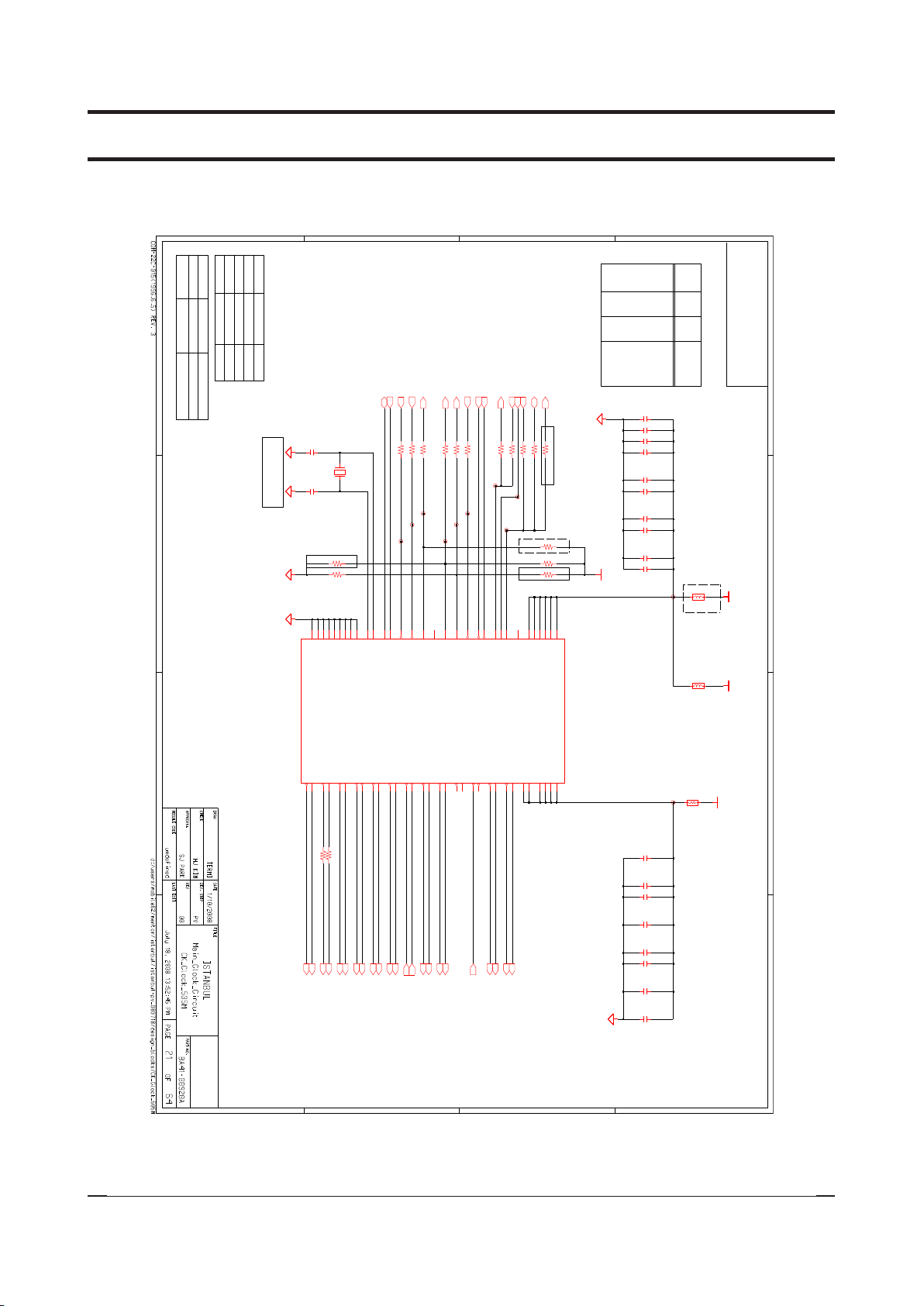

8. Block Diagram and Schematic

1

4

3

2

AC Adapter

D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

A

Power On/Off Table by S-state

+V* (CORE)

+V*AUX

+V

ON

ON

ON

4

ON

+1.8V_AUX

+0.9V

ON

ON

+V*A(LWS)

+V*LAN

ON

ON

ON

ON

State

Rail

S0

S3

S4

S5

B

C

Battery DC

VDC

P3.3V_ALW

P5.0V_ALW

P12.0V_ALW

S5-S4

Confidential

Confidential

Confidential

3

P1.2V_LAN

P1.8V_LAN

P2.5V_LAN

LAN

LAN

S3

Samsung

Samsung

Samsung

P3.3V_AUX

ICH8-M

MDC

LAN

BT

P3.3V_MICOM

MICOM

P5V_AUX

P0.9V

OPTION FOR ME

DDR III-Termination

It should be updated

P1.5V_AUX

ICH9-M

SODIMM (DDR III)

Cantiga

P1.5V_AUX

(CHP3_S4_STATE*)

P1.05V_AUX

KBC3_SUSPWR

2

1

SRP Sheet Number: 4 of 73

SAMSUNG

ELECTRONICS

POWER DIAGRAM

MDC

P3.3V

PEG

SPI

LEDs

PCMCIA

M_PCI

B

ICH8-M

CRESTLINE

Thermal Sensor

SODIMM

MICOM

EGFX_CORE

nVidia (TBD)

P1.25V

P1.2V

ICH8-M

CRESTLINE

PEG

S0

LCD

A

P1.5V

ICH8-M

CRESTLINE

IGFX_CORE

P5.0V

MICOM

CRT

CRESTLINE

HEATSINK

PEG

MDC

FAN CIRCUIT

AUX DISPLAY

FDD

USB

M_PCI

ICH8-M

PCMCIA

HDD

C

P0.9V

P1.8V

GDDR-3 for PEG

DDR II-Termination

(VCCP)

P1.05V

KBC3_PWRON

(CHP3_SLPS3*)

CRESTLINE

MEROM

ICH8-M

VCC_CORE

MEROM

Rev 0.1

KBC3_VRON

D

PEG

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

1.8V

3.1 A (TBD)

GDDR

( ~ 5.0 W )

5V

B

VDC INV ( TBD A )

PEX IO (TBD A)

VGA CORE (TBD A)

RTC_Battery

0.9V

3.3V

1.8V

1.2V (PEX IO)

1.8V_AUX

1 A (TBD)

3.1 A (TBD)

DDR-3

(Dual slots)

5V

1.0V-1.1V (EGFX CORE)

RTC_Battery

5V_AUX

3.3V

1.5V

3.3V_AUX

5V

Samsung

Samsung

Samsung

6.53 A (TBD)

0.001 A (TBD)

2.4A (TBD)

0.001 A (TBD)

1.75 A (TBD)

0.67 A (TBD)

PEG

5V

17.75 A (TBD)

3.3V

5V

0.209 A (TBD)

0.006 A (TBD)

( ~ 2.0 W )

3.3V

0.374 A (TBD)

ICH9-M

3.3V

1.05V

1.13 A (TBD)

3.3V

C

0.9V( TBD A )

1.05V (VCCP)

3.3V

1.25V

1.5V

1.8V_AUX

0.125 A (TBD)

0.33 A (TBD)

3.79 A (TBD)

4.48 A (TBD)

2.43A (TBD)

(8 - 8.5 W )

Cantiga

GMCH

3.3V

1.05V ( TBD A )

3.3V ( TBD A )

5.0V ( TBD A )

1.8V_AUX ( TBD A )

1.25V ( TBD A )

1.5V ( TBD A )

1.05V (MCH CORE)

1.05V (VCCP)

1.5V

7.7 A (TBD)

0.13 A (TBD)

4.5 A (TBD)

( 35 W )

3.3V_AUX ( TBD A )

5.0V_AUX ( TBD A )

CPU CORE ( TBD A )

CPU CORE

1.05V

0.1 A (TBD)

41 A (TBD)

Penryn-6M

ITP

3.3V

MICOM 3V ( TBD A )

Adapter

1.8V ( TBD A )

Battery

D

EXCEPT AS AUTHORIZED BY SAMSUNG.

220V

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

3

A

P1.2V_LAN

P3.3V_AUX

P1.8V/2.5V_LAN

4

0.08 A (TBD)

0.15 A (TBD)

0.29 A (TBD)

LAN (88E8055)

Value by Datasheet/Application notes

3

(Value by measurement)

5V

3.3V (LCD 3V)

19V (VDC INV)

Confidential

Confidential

Confidential

0.67 A (TBD)

0.5 A (TBD)

LCD

5V

5V

2

1

SRP Sheet Number: 5 of 73

SAMSUNG

ELECTRONICS

A

0.2 A (TBD)

2 A (TBD)

Touch Pad

USB (x 3)

1.5 A (TBD)

0.16 A (TBD)

Audio AMP

FAN

1.5 A (TBD)

0.22 A (TBD)

ODD

SATA HDD

SATA

3.3V_AUX

0.5 A (TBD)

MDC

B

0.06 A (TBD)

0.07 A (TBD)

HD Audio

1.5V

5V

3.3V

3.3V_AUX

0.5 A (TBD)

1.5 A (TBD)

0.75A (TBD)

Mini Card X 2

0.015 A (TBD)

SPI

3.3V

0.1 A (TBD)

SD Card

0.01 A (TBD)

KBD LED

3.3V_AUX

0.6 A (TBD)

LAN

0.2 A (TBD)

KeyBoard

3.3V_AUX

0.25 A (TBD)

CLOCK

3.3V

1.8V

C

Sensor

MICOM 3V

0.1 A (TBD)

PWR LED

0.75 A (TBD)

Thermal

MICOM 3V

3.3V

0.08 A (TBD)

0.08 A (TBD)

KBC

POWER RAILS ANALYSIS

2

Rev. 0.6 (060920)

1

D

8-5

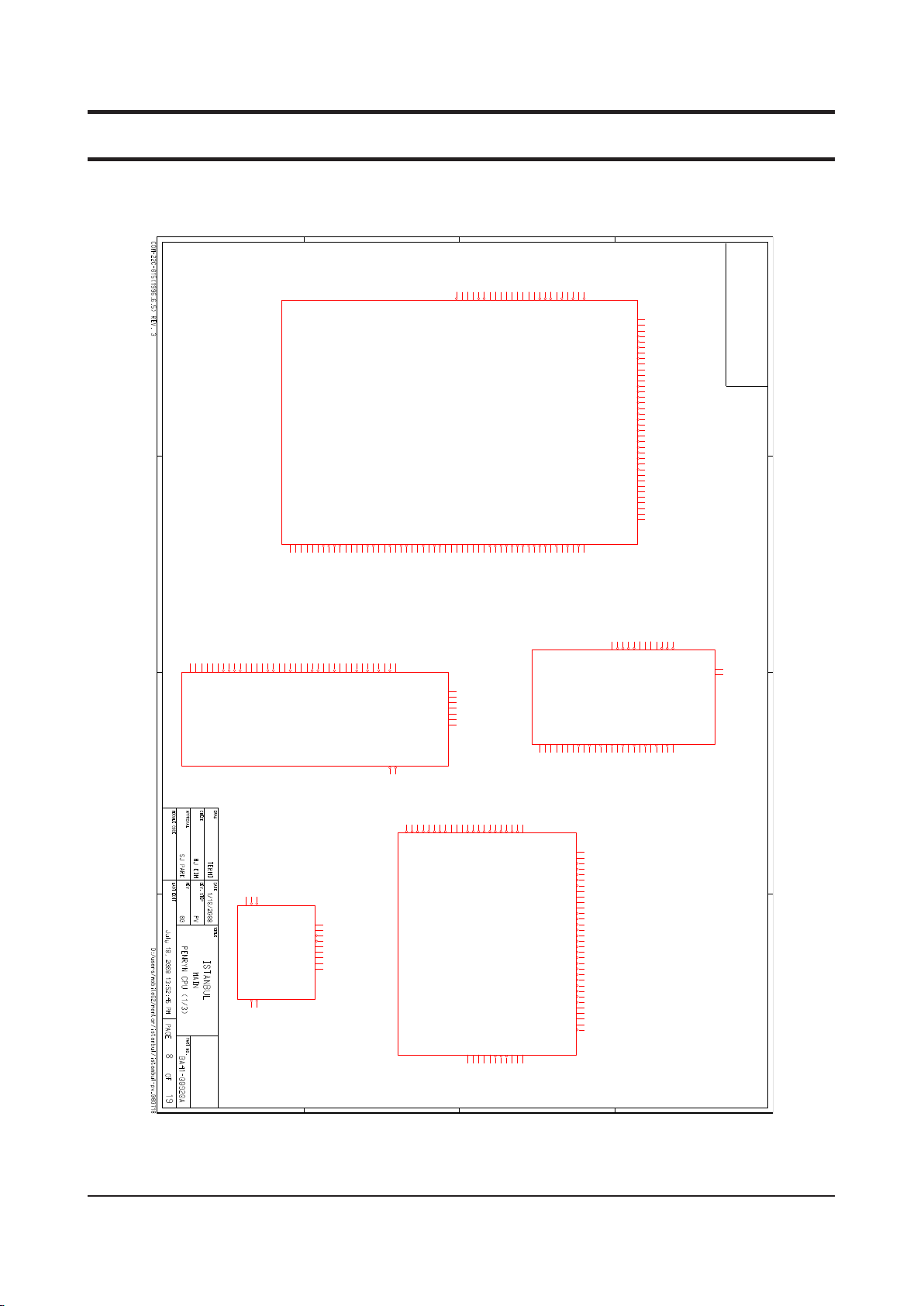

8-6

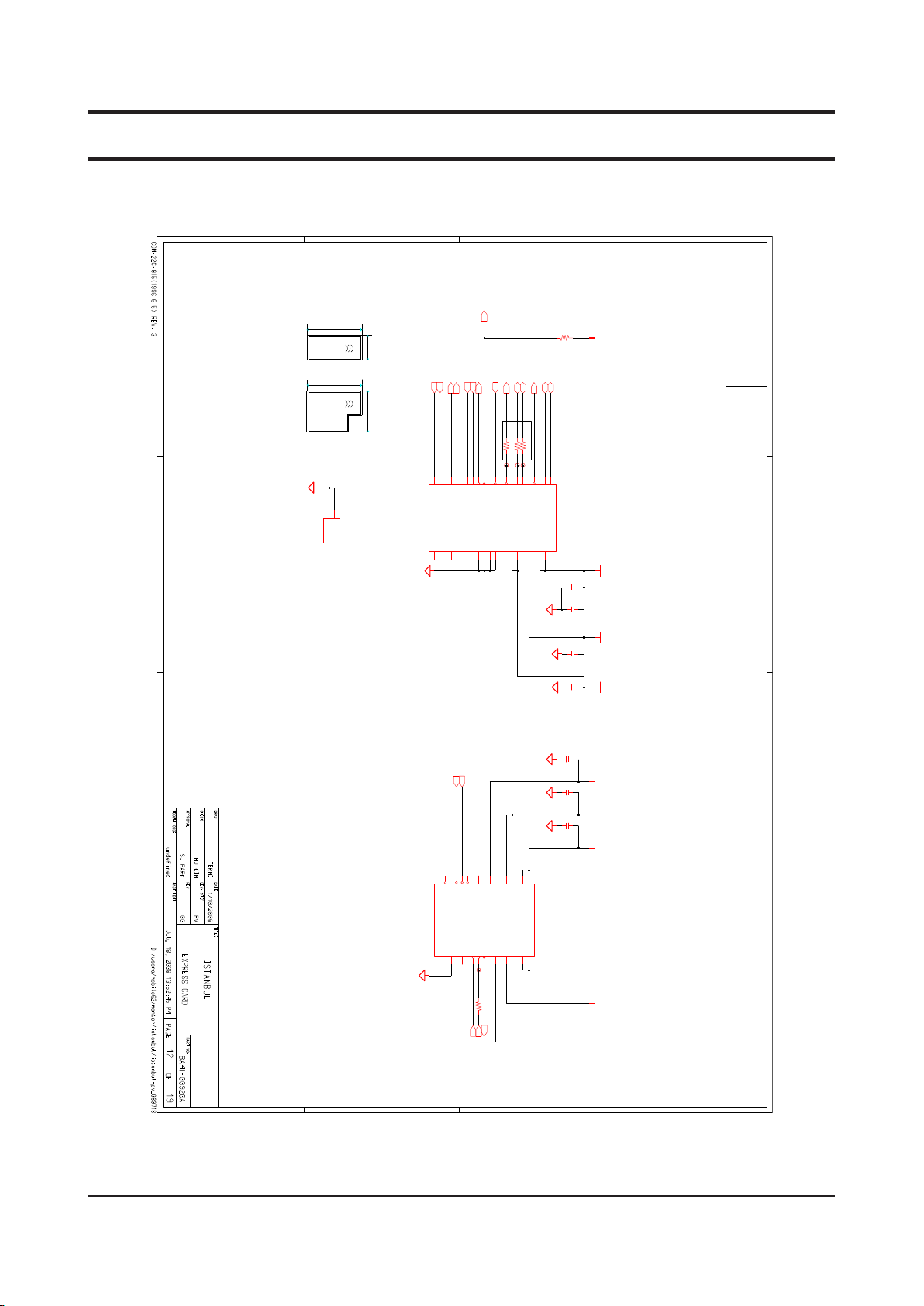

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

Samsung

Confidential

Samsung

Confidential

Samsung

Confidential

SRP Sheet Number: 6 of 73

PROPRIETARY INFORMATION THAT IS

4

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

PRTC

SC486

MAX 1909

PRTC

LOM

11) VCCP3_PWRGD (GM-model)

12

SAMSUNG ELECTRONICS CO’S PROPERTY.

17) KBC3_PWRGD

10-1) P1.2V

Need to be updated!!

10-1) P3.3V

17) KBC3_PWRGD

6

3

CPU

C

4

Rev. 0.7

10-1) P1.05V

C

D

19

Sheet 20-21

KBC

(Test Option)

10-1) P3.3V

SC4435

10

9) KBC3_PWRON

Sheet 15-19

D

9) KBC3_PWRON

10-1) P3.3V

P5.0V_ALW

Host S5 / ME Boot

2

(SLPS4* = SLPM*) > S4_STATE* > SLPS3*

7

9-1

ADP3209

ICH8-M

THIS DOCUMENT CONTAINS CONFIDENTIAL

ELECTRONICS

7) P1.5V_AUX

FDS6680A

M-2) KBC3_ME_PWRON = 15) KBC3_PWRON

PEG

11) VCCP3_PWRGD

14) VCC_CORE

Devices

LAN100_SLP

13) KBC3_VRON

6-1) P1.8V/P2.5V_LAN

6) P1.8V_AUX

9-1) KBC3_PWRON_INV#

(SLPS4* = S4_STATE*) > SLPM* > SLPS3*

CL_PWROK

6) P1.8V_AUX

15)VRM3_CPU_PWRGD

PWROK

PCIe

P3.3V_MICOM

2) VDC

P3.3V_AUX & P5V_AUX

10) P1.5V

3

15) VRM3_CPU_PWRGD

20) CPU1_CPURST*

B

SAMSUNG

9

1

6) P3.3V_AUX

CL_PWROK

18

19) PCI3_RST*

19) PCI3_RST*

17) KBC3_PWRGD

TPS51124

Sheet 22-25

8

M-1) KBC3_DDR_PWRON (TBD) = 8) KBC3_SUSPWR

CPU

5) KBC3_SUSPWR

9-1

17) KBC3_PWRGD

17

7) P1.05V_AUX

10) P5.0V

Adapter

10) P1.25

19

Host Boot / ME Off

13

10) P1.05V (IGFX_CORE)

POWER SEQUENCE

SAMSUNG PROPRIETARY

3

FDC653N

SC486

20

Sheet 40

2

10-1) P1.8V

11

12)GCORE_PWRGD

9) KBC3_PWRON

13) KBC3_VRON (Back-up)

2-1) P12.0V_ALW

2) VDC

DC/DC B’d

16) CLK3_PWRGD

1

18) CPU1_PWRGDCPU

10-1) P3.3V

6) P1.8V_AUX

15)VRM3_CPU_PWRGD

10-1) P1.5V

10-1) P1.25

10-2) P0.9V

1

Sheet 46-47

17) KBC3_PWRGD

10-1) P1.8V

A

Sheet 46

16-1) Clock Running

B

12)GCORE3_PWRGD (PM-model)

Sheet 8

10) P1.5V

FDS6680A

8) CHP3_SLPS5#/4#/3#

110ms Delay

10) P1.05V (IGFX_CORE)

BCP69

CK-505

4

16

Sheet 10-12

15

6

INTVRMEN

ISL6227

10-1) P1.8V

12) P1.5

6) MEM1_VREF

Host / ME Boot

A

GMCH

PWROK

(SLPS4* = S4_STATE*) > (SLPM* = SLPS3*)

2

VRM

5) KBC3_SUSPWR

6) P3.3V_AUX

CHP3_RTCRST#

VRMPWRGD

6) P1.8V_AUX

2) VDC

10) P5.0V

Marvell

14

11-1) GFX_CORE

10-1) P1.2V

6) P5.0V_AUX

7) KBC3_RSMRST#

4) POWER_SW*

19) PLT3_RST*

5

2) VDC

DDR2 POWER

Memory

10-1) ICH_CORE (P1.05V)

PRTC_BAT

Sheet 50

6-1) P1.2V_LAN

2) VDC

EXCEPT AS AUTHORIZED BY SAMSUNG.

POWER

Sheet 40

10-1) P3.3V

S/W

9-1) KBC3_PWRON_INV#

DDR3

6) P3.3V_AUX

19) PLT3_RST*

10) P1.5V

8) KBC3_SUSPWR

10-2) 0.9V

P3.3V_MICOM

MAX 8734

Battery

Devices

PCI

RTC

12) P1.05V_M

Sheet 40

11) KBC3_PWRON

Battery

AC_DC / Battery

3

PM-model only

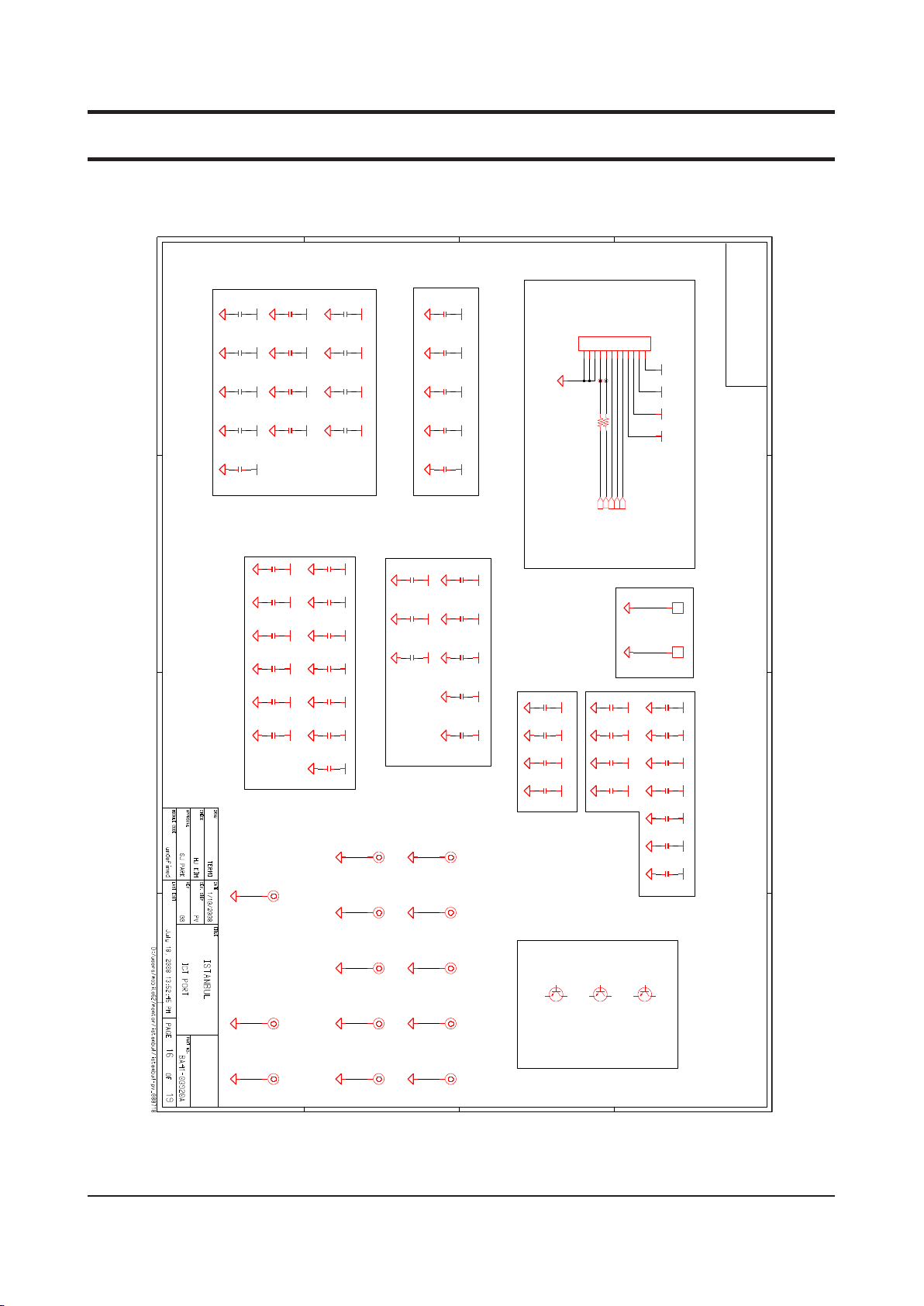

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

ITP_EN

MUXMUX

FSB

D

CLK3_PWRGD*

1

200 MHz

CLK0_HOST_CPU/CPU*

CPU

BSEL

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

P3.3V

4

FS(2:0)

3

A

14.318 MHz

PCI_STP*

4

3

Page 8

OSC

14 MHz

33 MHz

Buffer

33 MHz

CLK3_PCLKPORT80

Confidential

Confidential

Confidential

PORT 80

33 MHz

CLK3_PCLKMICOM

KBC

10 MHz

32.768 KHz

RTC Clock

B

CK-505M (w/ CLKREQ* & SSDC)

xSLG8SP513r05)

48MHz PLL

MUX

33 MHz

100 MHz (SRC 2)

14.318 MHz

Samsung

Samsung

Samsung

CLK3_ICH14

CLK3_PCLKICH

32.768 KHz

OSC

CLK1_SATA/SATA*

CHP3_SATACLKREQ*

SATAPLL

USBPLL

48 MHz

CLK1_PCIEICH/ICH*100 MHz (SRC 10)

CLK3_USB48

PCIEPLL

ICH9-M

C

SS(96/100) SEL

SSC

PLL3

Need to be updated!!

100 MHz (SRC 6,8,9)

DPLLB

DMI

100 MHz (SRC4)

100 MHz

96 MHz

CLK1_DREFCLK/CLK*

CLK1_DREFSSC/SSC*

CLK1_MCH3GPLL/3GPLL*

PCIE PLL

DPLLA

MCH3_CLKREQ*

MCH

CPU_STP*

Main PLL

SSC

100 MHz (SRC0)

200 MHz

CLK1_PEG/PEG*

PCI Express Gfx

CLK0_HOST_GMCH/GMCH*

PEG

MPLL

HPLL

Cantiga

2

1

SRP Sheet Number: 7 of 73

SAMSUNG

ELECTRONICS

17.86 MHz

MDC3_BCLK

AUD3_BCLK

MDC

HD 24 MHz

HD Audio

B

EXP3_CLKREQ*

CLK1_EXPCARD#

EXPRESS CARD

25 MHz

LOM3_CLKREQ*

CLK1_PCIELOM/LOM*100 MHz (SRC 9)

PCIE LAN

(Marvell)

100 MHz (SRC 6)

100 MHz (SRC 8)

CLK1_MINI2PCIE/PCIE*

CARD 1

MINI PCIE

CARD 2

MIN3_CLKREQ*

CLK1_MINIPCIE/PCIE*

MINI PCIE

SPI3_CLK

SPI

A

533/400 MHz

CLK1_MCLK4/4#

SODIMM #1

C

533/400 MHz

533/400 MHz

CLK1_MCLK3/3#

CLK1_MCLK1/1#

SODIMM #0

533/400 MHz

CLK1_MCLK0/0#

1067/800 MHz

D

2

CLOCK DISTRIBUTION

1

Rev. 0.1

8-7

8-8

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

Samsung

Confidential

Samsung

Confidential

Samsung

Confidential

SRP Sheet Number: 8 of 73

A

THIS DOCUMENT CONTAINS CONFIDENTIAL

1

C

3

EXCEPT AS AUTHORIZED BY SAMSUNG.

B

2

A

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

SAMSUNG PROPRIETARY

SAMSUNG

4

B

1

D

2

ELECTRONICS

SAMSUNG ELECTRONICS CO’S PROPERTY.

PROPRIETARY INFORMATION THAT IS

D

C

34

MEM1_CKE3

MEM1_CS0#

MEM1_CS1#

MEM1_CS2#

MEM1_CS3#

MEM1_ODT0

MEM1_ODT1

MEM1_ODT2

MEM1_ODT3

MEM1_VREF

SMB3_CLK

SMB3_DATA

MEM1_ARAS#

MEM1_AWE#

MEM1_BBS(0)

MEM1_BBS(1)

MEM1_BBS(2)

MEM1_BCAS#

MEM1_BDM(7:0)

MEM1_BDQ(63:0)

MEM1_BDQS#(7:0)

MEM1_BDQS(7:0)

MEM1_BMA(14:0)

MEM1_BRAS#

MEM1_BWE#

MEM1_CKE0

MEM1_CKE1

MEM1_CKE2

CLK1_MCLK1#

CLK1_MCLK2

CLK1_MCLK2#

CLK1_MCLK3

CLK1_MCLK3#

MCH3_EXTTS0#

MCH3_EXTTS1#

MEM1_ABS(0)

MEM1_ABS(1)

MEM1_ABS(2)

MEM1_ACAS#

MEM1_ADM(7:0)

MEM1_ADQ(63:0)

MEM1_ADQS#(7:0)

MEM1_ADQS(7:0)

MEM1_AMA(14:0)

MEM1_ODT0

MEM1_ODT1

MEM1_ODT2

MEM1_ODT3

MEM1_VREF

PEG1_RXN(15:0)

PEG1_RXP(15:0)

PEG1_TXN(15:0)

PEG1_TXP(15:0)

PLT3_RST#

SODIMM_DDR2

CLK1_MCLK0

CLK1_MCLK0#

CLK1_MCLK1

MEM1_BCAS#

MEM1_BDM(7:0)

MEM1_BDQ(63:0)

MEM1_BDQS#(7:0)

MEM1_BDQS(7:0)

MEM1_BMA(14:0)

MEM1_BRAS#

MEM1_BWE#

MEM1_CKE0

MEM1_CKE1

MEM1_CKE2

MEM1_CKE3

MEM1_CS0#

MEM1_CS1#

MEM1_CS2#

MEM1_CS3#

MCH1_HVREF

MCH1_HXSWING

MCH3_CLKREQ#

MCH3_EXTTS0#

MCH3_EXTTS1#

MCH3_ICHSYNC#

MEM1_ABS(2:0)

MEM1_ACAS#

MEM1_ADM(7:0)

MEM1_ADQ(63:0)

MEM1_ADQS#(7:0)

MEM1_ADQS(7:0)

MEM1_AMA(14:0)

MEM1_ARAS#

MEM1_AWE#

MEM1_BBS(2:0)

DMI1_RXN_1

DMI1_RXN_2

DMI1_RXN_3

DMI1_RXP_0

DMI1_RXP_1

DMI1_RXP_2

DMI1_RXP_3

DMI1_TXN_0

DMI1_TXN_1

DMI1_TXN_2

DMI1_TXN_3

DMI1_TXP_0

DMI1_TXP_1

DMI1_TXP_2

DMI1_TXP_3

KBC3_PWRGD

CPU1_DSTBN3#

CPU1_DSTBP0#

CPU1_DSTBP1#

CPU1_DSTBP2#

CPU1_DSTBP3#

CPU1_HIT#

CPU1_HITM#

CPU1_LOCK#

CPU1_REQ#(4:0)

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_SLP#

CPU1_THRMTRIP#

CPU1_TRDY#

DMI1_RXN_0

CPU1_BSEL1

CPU1_BSEL2

CPU1_CPURST#

CPU1_D#(63:0)

CPU1_DBI0#

CPU1_DBI1#

CPU1_DBI2#

CPU1_DBI3#

CPU1_DBSY#

CPU1_DEFER#

CPU1_DPRSTP#

CPU1_DPWR#

CPU1_DRDY#

CPU1_DSTBN0#

CPU1_DSTBN1#

CPU1_DSTBN2#

CLK1_MCLK0

CLK1_MCLK0#

CLK1_MCLK1

CLK1_MCLK1#

CLK1_MCLK2

CLK1_MCLK2#

CLK1_MCLK3

CLK1_MCLK3#

CPU1_A#(35:3)

CPU1_ADS#

CPU1_ADSTB0#

CPU1_ADSTB1#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_BSEL0

LOM3_CLKREQ#

MCH3_CLKREQ#

MIN3_CLKREQ#

SMB3_CLK

SMB3_DATA

MCH_CANTIGA_GM_DDR2

CHP3_CL_CLK_0

CHP3_CL_DATA_0

CHP3_CL_RST_0#

CHP3_DPRSLPVR

CHP3_PM_SYNC#

CLK0_HCLK1

CLK0_HCLK1#

CLK1_MCH3GPLL

CLK1_MCH3GPLL#

CLK1_PEG#

CLK1_SATA

CLK1_SATA#

CLK3_DBGLPC

CLK3_FM48

CLK3_GFX_27M

CLK3_GFX_27M_SS

CLK3_ICH14

CLK3_PCLKICH

CLK3_PCLKMICOM

CLK3_PWRGD

CLK3_USB48

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

EXP3_CLKREQ#

CHP3_SATACLKREQ#

CLK0_HCLK0

CLK0_HCLK0#

CLK0_HCLK1

CLK0_HCLK1#

CLK1_EXPCARD

CLK1_EXPCARD#

CLK1_MCH3GPLL

CLK1_MCH3GPLL#

CLK1_MINIPCIE

CLK1_MINIPCIE#

CLK1_PCIEICH

CLK1_PCIEICH#

CLK1_PCIELOM

CLK1_PCIELOM#

CLK1_PEG

CPU3_THRMTRIP#

FAN3_FDBACK#

FAN5_VDD

GFX3_THERM#

GFX3_THERMDN

GFX3_THERMDP

KBC3_PWRGD

KBC3_THERM_SMCLK

KBC3_THERM_SMDATA

THM3_ALERT#

THM3_STP#

CK_Clock_505M

CHP3_CPUSTP#

CHP3_PCISTP#

CPU1_TDI

CPU1_THRMTRIP#

CPU1_TMS

CPU1_TRDY#

CPU1_TRST#

CPU1_VCCSENSE

CPU1_VID(6:0)

CPU1_VSSSENSE

CPU2_THERMDA

CPU2_THERMDC

ITP3_DBRRESET#

Thermal_Sensor_SMSC_Emc2102

CPU1_THRMTRIP#

CPU2_THERMDA

CPU2_THERMDC

CPU1_HITM#

CPU1_IGNNE#

CPU1_INIT#

CPU1_INTR

CPU1_LOCK#

CPU1_NMI

CPU1_PSI#

CPU1_PWRGDCPU

CPU1_REQ#(4:0)

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_SLP#

CPU1_SMI#

CPU1_STPCLK#

CPU1_TCK

CPU1_DBSY#

CPU1_DEFER#

CPU1_DPRSTP#

CPU1_DPSLP#

CPU1_DPWR#

CPU1_DRDY#

CPU1_DSTBN0#

CPU1_DSTBN1#

CPU1_DSTBN2#

CPU1_DSTBN3#

CPU1_DSTBP0#

CPU1_DSTBP1#

CPU1_DSTBP2#

CPU1_DSTBP3#

CPU1_FERR#

CPU1_HIT#

CPU1_ADSTB1#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

CPU1_CPURST#

CPU1_D#(15:0)

CPU1_D#(31:16)

CPU1_D#(47:32)

CPU1_D#(63:48)

CPU1_DBI0#

CPU1_DBI1#

CPU1_DBI2#

CPU1_DBI3#

CLK3_GFX_27M

CLK3_GFX_27M_SS

PEG1_RXN(15:0)

PEG1_RXP(15:0)

PEG1_TXN(15:0)

PEG1_TXP(15:0)

GFX3_THERMDN

GFX3_THERMDP

GFX3_THERM#

CPU_Penryn_MV_SV

CLK0_HCLK0

CLK0_HCLK0#

CPU1_A#(16:3)

CPU1_A#(35:17)

CPU1_A20M#

CPU1_ADS#

CPU1_ADSTB0#

MEM1_CKE0

MEM1_CKE1

MEM1_CKE2

MEM1_CKE3

MEM1_CS0#

MEM1_CS1#

MEM1_CS2#

MEM1_CS3#

MEM1_ODT0

MEM1_ODT1

MEM1_ODT2

MEM1_ODT3

MEM1_VREF

SMB3_CLK

SMB3_DATA

CLK1_PEG

CLK1_PEG#

MEM1_ABS(1)

MEM1_ABS(2)

MEM1_ACAS#

MEM1_ADM(7:0)

MEM1_ADQ(63:0)

MEM1_ADQS#(7:0)

MEM1_ADQS(7:0)

MEM1_AMA(14:0)

MEM1_ARAS#

MEM1_AWE#

MEM1_BBS(0)

MEM1_BBS(1)

MEM1_BBS(2)

MEM1_BCAS#

MEM1_BDM(7:0)

MEM1_BDQ(63:0)

MEM1_BDQS#(7:0)

MEM1_BDQS(7:0)

MEM1_BMA(14:0)

MEM1_BRAS#

MEM1_BWE#

CPU3_THRMTRIP#

FAN3_FDBACK#

FAN5_VDD

KBC3_PWRGD

KBC3_THERM_SMCLK

KBC3_THERM_SMDATA

THM3_ALERT#

THM3_STP#

CLK1_MCLK0

CLK1_MCLK0#

CLK1_MCLK1

CLK1_MCLK1#

CLK1_MCLK2

CLK1_MCLK2#

CLK1_MCLK3

CLK1_MCLK3#

MCH3_EXTTS0#

MCH3_EXTTS1#

MEM1_ABS(0)

CPU1_IGNNE#

CPU1_INIT#

CPU1_INTR

CPU1_LOCK#

CPU1_NMI

CPU1_PSI#

CPU1_PWRGDCPU

CPU1_REQ#(4:0)

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_SLP#

CPU1_SMI#

CPU1_STPCLK#

CPU1_TCK

CPU1_TDI

CPU1_THRMTRIP#

CPU1_TMS

CPU1_TRDY#

CPU1_TRST#

CPU1_VCCSENSE

CPU1_VID(6:0)

CPU1_VSSSENSE

CPU2_THERMDA

CPU2_THERMDC

ITP3_DBRRESET#

CPU1_THRMTRIP#

CPU2_THERMDA

CPU2_THERMDC

CPU1_DEFER#

CPU1_DPRSTP#

CPU1_DPSLP#

CPU1_DPWR#

CPU1_DRDY#

CPU1_DSTBN0#

CPU1_DSTBN1#

CPU1_DSTBN2#

CPU1_DSTBN3#

CPU1_DSTBP0#

CPU1_DSTBP1#

CPU1_DSTBP2#

CPU1_DSTBP3#

CPU1_FERR#

CPU1_HIT#

CPU1_HITM#

CLK0_HCLK0#

CPU1_A#(16:3)

CPU1_A#(35:17)

CPU1_A20M#

CPU1_ADS#

CPU1_ADSTB0#

CPU1_ADSTB1#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

CPU1_CPURST#

CPU1_D#(15:0)

CPU1_D#(31:16)

CPU1_D#(47:32)

CPU1_D#(63:48)

CPU1_DBI0#

CPU1_DBI1#

CPU1_DBI2#

CPU1_DBI3#

CPU1_DBSY#

CLK1_SATA#

CLK3_DBGLPC

CLK3_FM48

CLK3_ICH14

CLK3_PCLKICH

CLK3_PCLKMICOM

CLK3_PWRGD

CLK3_USB48

CPU1_BSEL0

CPU1_BSEL1

CPU1_BSEL2

EXP3_CLKREQ#

LOM3_CLKREQ#

MCH3_CLKREQ#

MIN3_CLKREQ#

SMB3_CLK

SMB3_DATA

CLK0_HCLK0

CLK1_EXPCARD

CLK1_EXPCARD#

CLK1_MCH3GPLL

CLK1_MCH3GPLL#

CLK1_MINIPCIE

CLK1_MINIPCIE#

CLK1_PCIEICH

CLK1_PCIEICH#

CLK1_PCIELOM

CLK1_PCIELOM#

CLK1_SATA

MEM1_BDM(7:0)

MEM1_BDQ(63:0)

MEM1_BDQS#(7:0)

MEM1_BDQS(7:0)

MEM1_BMA(14:0)

MEM1_BRAS#

MEM1_BWE#

MEM1_CKE0

MEM1_CKE1

MEM1_CKE2

MEM1_CKE3

MEM1_CS0#

MEM1_CS1#

MEM1_CS2#

MEM1_CS3#

MEM1_ODT0

MEM1_ODT1

MEM1_ODT2

MEM1_ODT3

MEM1_VREF

PLT3_RST#

CHP3_CPUSTP#

CHP3_PCISTP#

CHP3_SATACLKREQ#

CLK0_HCLK0

CLK0_HCLK0#

CLK0_HCLK1

CLK0_HCLK1#

DMI1_TXP_0

DMI1_TXP_1

DMI1_TXP_2

DMI1_TXP_3

KBC3_PWRGD

MCH1_HVREF

MCH1_HXSWING

MCH3_CLKREQ#

MCH3_EXTTS0#

MCH3_EXTTS1#

MCH3_ICHSYNC#

MEM1_ABS(2:0)

MEM1_ACAS#

MEM1_ADM(7:0)

MEM1_ADQ(63:0)

MEM1_ADQS#(7:0)

MEM1_ADQS(7:0)

MEM1_AMA(14:0)

MEM1_ARAS#

MEM1_AWE#

MEM1_BBS(2:0)

MEM1_BCAS#

DMI1_RXN_1

DMI1_RXN_2

DMI1_RXN_3

DMI1_RXP_0

DMI1_RXP_1

DMI1_RXP_2

DMI1_RXP_3

DMI1_TXN_0

DMI1_TXN_1

DMI1_TXN_2

DMI1_TXN_3

CPU1_BSEL2

CPU1_CPURST#

CPU1_D#(63:0)

CPU1_DBI0#

CPU1_DBI1#

CPU1_DBI2#

CPU1_DBI3#

CPU1_DBSY#

CPU1_DEFER#

CPU1_DPRSTP#

CPU1_DPWR#

CPU1_DRDY#

CPU1_DSTBN0#

CPU1_DSTBN1#

CPU1_DSTBN2#

CPU1_DSTBN3#

CPU1_DSTBP0#

CPU1_DSTBP1#

CPU1_DSTBP2#

CPU1_DSTBP3#

CPU1_HIT#

CPU1_HITM#

CPU1_LOCK#

CPU1_REQ#(4:0)

CPU1_RS0#

CPU1_RS1#

CPU1_RS2#

CPU1_SLP#

CPU1_THRMTRIP#

CPU1_TRDY#

DMI1_RXN_0

CHP3_CL_CLK_0

CHP3_CL_DATA_0

CHP3_CL_RST_0#

CHP3_DPRSLPVR

CHP3_PM_SYNC#

CLK0_HCLK1

CLK0_HCLK1#

CLK1_MCH3GPLL

CLK1_MCH3GPLL#

CLK1_MCLK0

CLK1_MCLK0#

CLK1_MCLK1

CLK1_MCLK1#

CLK1_MCLK2

CLK1_MCLK2#

CLK1_MCLK3

CLK1_MCLK3#

CPU1_A#(35:3)

CPU1_ADS#

CPU1_ADSTB0#

CPU1_ADSTB1#

CPU1_BNR#

CPU1_BPRI#

CPU1_BREQ#

CPU1_BSEL0

CPU1_BSEL1

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

A

ICH_9M_B

B B

VRM3_CPU_PWRGD

THM3_ALERT#

SAT1_RXN1

SAT1_RXP0

SAT1_RXP1

VRM3_CPU_PWRGD

THM3_ALERT#

SAT1_RXN0

SAT1_RXN1

SAT1_RXP0

SAT1_RXP1

PEX1_GLAN_RXP4

PEX1_MINIRXN1

PEX1_MINIRXP1

SAT1_RXN0

PEX1_GLAN_RXP4

PEX1_MINIRXN1

PEX1_MINIRXP1

PEX1_EXPCARDRXN3

PEX1_EXPCARDRXP3

PEX1_GLAN_RXN4

MCH3_ICHSYNC#

KBC3_WAKESCI#

KBC3_WAKESCI#

MCH3_ICHSYNC#

PEX1_EXPCARDRXN3

PEX1_EXPCARDRXP3

PEX1_GLAN_RXN4

KBC3_PWRBTN#

KBC3_RSMRST#

KBC3_EXTSMI#

KBC3_PWRGD

KBC3_EXTSMI#

KBC3_PWRBTN#

KBC3_PWRGD

KBC3_RSMRST#

ITP3_DBRRESET#

HDA3_HDMI_SDI2

HDA3_MDC_SDI1

HDA3_AUD_SDI0

HDA3_HDMI_SDI2

HDA3_AUD_SDI0

HDA3_MDC_SDI1

ITP3_DBRRESET#

4

Confidential

Confidential

Confidential

PEX1_EXPCARDTXN3

PEX1_EXPCARDTXP3

PEX1_GLAN_TXN4

PEX1_GLAN_TXP4

PEX1_MINITXN1

PEX1_MINITXP1

SAT1_TXN0

SAT1_TXN1

SAT1_TXP0

SAT1_TXP1

PLT3_RST#

SPI3_CS0#

SPI3_CLK

Samsung

Samsung

Samsung

HDA3_HDMI_SYNC

HDA3_HDMI_BCLK

HDA3_HDMI_RST#

HDA3_MDC_SYNC

HDA3_MDC_BCLK

HDA3_AUD_SYNC

HDA3_MDC_SDO

LPC3_LFRAME#

KBC3_RUNSCI#

HDA3_MDC_RST#

HDA3_HDMI_SDO

HDA3_AUD_SDO

HDA3_AUD_BCLK

HDA3_AUD_RST#

DMI1_TXP_2

DMI1_TXP_3

DMI1_TXN_3

DMI1_TXP_0

DMI1_TXP_1

DMI1_TXN_0

DMI1_TXN_1

DMI1_TXN_2

CPU1_PWRGDCPU

CPU1_STPCLK#

CPU1_SMI#

CPU1_NMI

CPU1_INTR

3

CPU1_INTR

CPU1_NMI

CPU1_PWRGDCPU

CPU1_SMI#

CPU1_STPCLK#

DMI1_TXN_0

SAT1_TXN0

SAT1_TXN1

SAT1_TXP0

SAT1_TXP1

PEX1_MINITXP1

PEX1_EXPCARDTXN3

PEX1_EXPCARDTXP3

PLT3_RST#

SPI3_CLK

SPI3_CS0#

MICOM_Renesas2110_100p

KBC3_THERM_SMCLK

KBC3_USBPWRON#

KBC3_WAKESCI#

KBC3_SPKMUTE

KBC5_KSO(8:15)

LID3_SWITCH#

KBC5_KSO(8:15)

2

LID3_SWITCH#

KBC5_KSO(0:7)

KBC3_VRON

KBC3_VRON

KBC3_WAKESCI#

KBC5_KSO(0:7)

KBC3_RUNSCI#

KBC3_SUSPWR

KBC3_SCLED#

KBC3_USBPWRON#

KBC3_SUSPWR

KBC3_THERM_SMCLK

KBC3_SCLED#

KBC3_SPKMUTE

PEX1_MINITXN1

KBC3_RSMRST#

KBC3_RFOFF#

KBC3_PWRON

KBC3_PWRON

KBC3_RFOFF#

KBC3_RSMRST#

KBC3_RUNSCI#

LPC3_LFRAME#

PEX1_GLAN_TXN4

PEX1_GLAN_TXP4

VRM3_CPU_PWRGD

THM3_ALERT#

PEX3_WAKE#

THM3_STP#

PLT3_RST#

LPC3_LFRAME#

PEX3_WAKE#

PLT3_RST#

THM3_ALERT#

THM3_STP#

VRM3_CPU_PWRGD

KBC3_LED_CHARGE#

KBC3_LED_POWER#

KBC3_PWRBTN#

KBC3_NUMLED#

KBC3_PRECHG

KBC3_PWRGD

KBC3_PRECHG

KBC3_LED_POWER#

KBC3_NUMLED#

KBC3_PWRBTN#

KBC3_PWRGD

HDA3_HDMI_SYNC

HDA3_MDC_BCLK

HDA3_MDC_RST#

HDA3_MDC_SDO

HDA3_MDC_SYNC

KBC3_RUNSCI#

CLK3_PCLKMICOM

CHP3_SUSSTAT#

LPC3_LFRAME#

KBC3_PWRSW#

CHP3_SLPS5#

KBC5_KSI(0:7)

KBC5_KSI(0:7)

CHP3_SLPS4#

CHP3_SLPS5#

CHP3_SUSSTAT#

CLK3_PCLKMICOM

KBC3_PWRSW#

KBC3_LED_ACIN#

KBC3_CAPSLED#

KBC3_CPURST#

KBC3_EXTSMI#

KBC3_CHG4.2V

KBC3_CHGEN

KBC3_CHG4.2V

KBC3_CHGEN

KBC3_CPURST#

KBC3_EXTSMI#

KBC3_LED_ACIN#

KBC3_LED_CHARGE#

HDA3_AUD_SYNC

HDA3_HDMI_BCLK

HDA3_HDMI_RST#

HDA3_HDMI_SDO

BAT3_DETECT#

CHP3_SLPS3#

CHP3_SLPS4#

ADT3_SEL#

ADT3_SEL#

BAT3_DETECT#

CHP3_SLPS3#

KBC3_BKLTON

CHP3_SERIRQ

KBC3_A20G

KBC3_CAPSLED#

CHP3_SERIRQ

KBC3_A20G

KBC3_BKLTON

HDA3_AUD_SDO

KBC3_THERM_SMDATA

DMI1_TXP_0

DMI1_TXP_1

DMI1_TXP_2

DMI1_TXP_3

HDA3_AUD_BCLK

HDA3_AUD_RST#

KBC3_BLCKPWRSW#

KBC3_CHKPWRSW#

KBC3_RST#

KBC3_SMCLK#

KBC3_SMDATA#

KBC5_TCLK

KBC5_TDATA

LPC3_LAD(0:3)

PCI3_CLKRUN#

DMI1_TXN_1

DMI1_TXN_2

DMI1_TXN_3

KBC3_BLCKPWRSW#

KBC3_CHKPWRSW#

KBC3_RST#

KBC3_SMCLK#

KBC3_SMDATA#

KBC3_THERM_SMDATA

KBC5_TCLK

KBC5_TDATA

LPC3_LAD(0:3)

PCI3_CLKRUN#

DMI1_RXP_2

DMI1_RXP_3

DMI1_RXP_3

DMI1_RXP_1

DMI1_RXP_2

CPU1_DPSLP#

CPU1_IGNNE#

CPU1_INIT#

CPU1_IGNNE#

CPU1_INIT#

DMI1_RXN_3

DMI1_RXP_0

DMI1_RXP_1

DMI1_RXN_2

DMI1_RXN_3

DMI1_RXP_0

CPU1_DPRSTP#

CLK3_PWRGD

CPU1_A20M#

CPU1_A20M#

CPU1_DPRSTP#

CPU1_DPSLP#

C C

CPU1_THRMTRIP#

DMI1_RXN_0

DMI1_RXN_1

DMI1_RXN_2

CPU1_THRMTRIP#

DMI1_RXN_0

DMI1_RXN_1

CHP3_SUSSTAT#

CHP3_SLPS4#

CHP3_SLPS5#

CHP3_SLPS4#

CHP3_SLPS5#

CHP3_SUSSTAT#

CLK3_PWRGD

CLK3_PCLKICH

CPU1_FERR#

CLK3_USB48

CLK3_ICH14

CLK3_PCLKICH

CLK3_USB48

CPU1_FERR#

CHP3_SATACLKREQ#

CHP3_PM_SYNC#

CHP3_SATALED#

CHP3_SLPS3#

CHP3_SATACLKREQ#

CHP3_SATALED#

CHP3_SLPS3#

CLK1_PCIEICH#

CLK1_PCIEICH

CLK1_SATA#

CLK3_ICH14

CLK1_SATA

CLK1_PCIEICH

CLK1_PCIEICH#

CLK1_SATA

CLK1_SATA#

CHP3_DPRSLPVR

CHP3_CPUSTP#

CHP3_PCISTP#

AUD3_SPKR

AUD3_SPKR

CHP3_CPUSTP#

CHP3_DPRSLPVR

CHP3_PCISTP#

CHP3_PM_SYNC#

HDD_IF_Conn

CHP3_BIOSWP#

CHP3_BIOS_CRI#

CHP3_CL_CLK_0

CHP3_CL_DATA_0

CHP3_CL_RST_0#

CHP3_GPIO18

CHP3_GPIO20

CHP3_INTRUDER#

CHP3_ME_RTCRST#

CHP3_RTCRST#

CHP3_SERIRQ

KBC3_A20G

KBC3_CPURST#

LPC3_LAD(3:0)

PCI3_CLKRUN#

PEX3_WAKE#

PLT3_RST_ORG#

SMB3_ALERT#

SMB3_CLK

SMB3_DATA

SPI3_MISO

SPI3_MOSI

USB3_P0+

USB3_P0USB3_P10+

USB3_P10-

USB3_P2+

USB3_P2-

USB3_P3+

USB3_P3-

USB3_P4+

USB3_P4-

USB3_P5+

USB3_P5-

USB3_P6+

USB3_P6-

USB3_P8+

USB3_P8-

SAT1_TXN0

SAT1_TXP0

SAT1_TXN0

SAT1_TXP0

SAT1_RXN0

SAT1_RXP0

SAT1_RXN0

SAT1_RXP0

SAT1_TXN1

SAT1_TXP1

CHP3_BIOSWP#

CHP3_BIOS_CRI#

CHP3_CL_CLK_0

CHP3_CL_DATA_0

CHP3_CL_RST_0#

CHP3_GPIO18

CHP3_GPIO20

CHP3_INTRUDER#

CHP3_ME_RTCRST#

CHP3_RTCRST#

CHP3_SERIRQ

KBC3_A20G

KBC3_CPURST#

LPC3_LAD(3:0)

PCI3_CLKRUN#

PEX3_WAKE#

PLT3_RST_ORG#

SMB3_ALERT#

SMB3_CLK

SMB3_DATA

SPI3_MISO

SPI3_MOSI

USB3_P0+

USB3_P0USB3_P10+

USB3_P10USB3_P2+

USB3_P2USB3_P3+

USB3_P3USB3_P4+

USB3_P4USB3_P5+

USB3_P5USB3_P6+

USB3_P6USB3_P8+

USB3_P8-

USB_2Port

USB3_P6-

USB3_P8+

USB_1Port

USB3_P0+

USB3_P6+

USB3_P0-

USB3_P6-

USB3_P0+

USB3_P0-

USB3_P6+

USB3_P8- T_R_BUTTON#

D D

KBC3_USBPWRON#

USB3_P2+

USB3_P2-

KBC3_USBPWRON#

USB3_P2+

USB3_P2-

KBC3_USBPWRON#

KBC3_USBPWRON#

USB3_P5+

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

3

USB3_P5-

2

1

SRP Sheet Number: 9 of 73

SAMSUNG

ELECTRONICS

USB3_P8-

PLT3_RST#

Other_Debug_80

PLT3_RST#

CLK3_DBGLPC

CLK3_DBGLPC

LPC3_LAD(0)

LPC3_LAD(1)

LPC3_LAD(2)

LPC3_LAD(3)

LPC3_LFRAME#

LPC3_LAD(0)

LPC3_LAD(1)

LPC3_LAD(2)

LPC3_LAD(3)

LPC3_LFRAME#

LED_Switch

KBC3_NUMLED#

KBC3_SCLED#

WLON_LED#

KBC3_NUMLED#

KBC3_SCLED#

WLON_LED#

KBC3_LED_CHARGE#

KBC3_LED_POWER#

KBC3_LED_ACIN#

KBC3_CAPSLED#

CHP3_SATALED#

CHP3_SATALED#

KBC3_CAPSLED#

KBC3_LED_ACIN#

KBC3_LED_CHARGE#

KBC3_LED_POWER#

KBD_IF_Conn

KBC5_KSI(0:7)KBC5_KSO(0:15)

KBC5_KSI(0:7)KBC5_KSO(0:15)

LID_Switch

MIO_Switch

LID3_SWITCH#

LID3_SWITCH#

KBC3_PWRSW#

KBC3_PWRSW#

ODD_IF_Conn

SAT1_TXP1

SAT1_RXP1

SAT1_TXN1

SAT1_RXN1

SAT1_RXN1

SAT1_RXP1

Camera_IF_Conn

T_L_BUTTON#

KBC5_TDATA

KBC5_TCLK

KBC5_TCLK

KBC5_TDATA

Touchpad_IF_Conn

USB3_P8+

T_L_BUTTON#

T_R_BUTTON#

USB3_P5+

USB3_P5-

Bluetooth_IF_Conn

SPI_BIOS_ROM

SPI3_MOSI

SPI3_MOSI

SPI3_CS0#

SPI3_CLK

SPI3_CS0#

CHP3_BIOSWP#

SPI3_CLK

CHP3_BIOSWP#

1

SPI3_MISO

SPI3_MISO

A

8-9

8-10

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

Samsung

Confidential

Samsung

Confidential

Samsung

Confidential

SRP Sheet Number: 10 of 73

SAMSUNG

ELECTRONICS

A

B B

A

C C

D D

4

4

3 1

13

2

2

SAMSUNG PROPRIETARY

THIS DOCUMENT CONTAINS CONFIDENTIAL

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

EXCEPT AS AUTHORIZED BY SAMSUNG.

WDQSA(4)

WDQSA(5)

WDQSA(6)

WDQSA(7)

WEA#

MCLKA1

MCLKA1#

ODT

RASA#

RDQSA(0)

RDQSA(1)

RDQSA(2)

RDQSA(3)

RDQSA(4)

RDQSA(5)

RDQSA(6)

RDQSA(7)

WDQSA(0)

WDQSA(1)

WDQSA(2)

WDQSA(3)

DQMA(0)

DQMA(1)

DQMA(2)

DQMA(3)

DQMA(4)

DQMA(5)

DQMA(6)

DQMA(7)

MAA(12:0)

MAB(2)

MAB(3)

MAB(4)

MAB(5)

MCKEA

MCLKA0

MCLKA0#

PEX1_MINITXN1

PEX1_MINITXP1

PEX3_WAKE#

PLT3_RST#

WLON_LED#

Graphics_Memory_Nvidia

BAA0

BAA1

BAA2

CASA#

CSA0#

DQA(15:0)

DQA(31:16)

DQA(47:32)

DQA(63:48)

HDA3_AUD_SDO

HDA3_AUD_SYNC

KBC3_SPKMUTE

SPK5_L+

SPK5_L-

SPK5_R+

SPK5_R-

PCIE_Minicard_Slot

CLK1_MINIPCIE

CLK1_MINIPCIE#

KBC3_RFOFF#

MIN3_CLKREQ#

PEX1_MINIRXN1

PEX1_MINIRXP1

AUD5_HP_O_RIGHT

AUD5_LINE_O_LEFT

AUD5_LINE_O_RIGHT

AUD5_MIC1_LEFT

AUD5_MIC1_RIGHT

AUD5_MIC1_VREF_LEFT

AUD5_MIC1_VREF_RIGHT

AUD5_MIC2_LEFT

AUD5_MIC2_RIGHT

AUD5_MIC2_VREF

AUD5_SENS_A

AUD5_SENS_HP#

AUD5_SENS_MIC#

HDA3_AUD_BCLK

HDA3_AUD_RST#

HDA3_AUD_SDI0

PEG3_TX1P_HDMI

PEG3_TX2N_HDMI

PEG3_TX2P_HDMI

PEG3_TXCN_HDMI

PEG3_TXCP_HDMI

PEG5_HDMI_CLK

PEG5_HDMI_DATA

HDA_Codec_Alc262

AUD3_BEEP

AUD3_GPIO0#

AUD3_GPIO1#

AUD3_SHDN#

AUD3_SPKR

AUD5_HP_O_LEFT

LCD1_BCLK#

LCD1_BDATA0

LCD1_BDATA0#

LCD1_BDATA1

LCD1_BDATA1#

LCD1_BDATA2

LCD1_BDATA2#

LCD3_BKLTON

LCD3_BRIT

LCD3_EDID_CLK

LCD3_EDID_DATA

PEG3_BKLTEN

PEG3_HPD_HDMI

PEG3_LCDVDDON

PEG3_TX0N_HDMI

PEG3_TX0P_HDMI

PEG3_TX1N_HDMI

CRT3_VSYNC

CRT5_DDCCLK

CRT5_DDCDATA

CRT5_HSYNC

CRT5_VSYNC

KBC3_BKLTON

LCD1_ACLK

LCD1_ACLK#

LCD1_ADATA0

LCD1_ADATA0#

LCD1_ADATA1

LCD1_ADATA1#

LCD1_ADATA2

LCD1_ADATA2#

LCD1_BCLK

WEA#

HDA_Modem

HDA3_MDC_BCLK

HDA3_MDC_RST#

HDA3_MDC_SDI1

HDA3_MDC_SDO

HDA3_MDC_SYNC

Graphics_IF_CRT

CRT3_BLUE

CRT3_DDCCLK

CRT3_DDCDATA

CRT3_GREEN

CRT3_HSYNC

CRT3_RED

PEG3_HPD_HDMI

PEG3_LCDVDDON

PEG3_TX0N_HDMI

PEG3_TX0P_HDMI

PEG3_TX1N_HDMI

PEG3_TX1P_HDMI

PEG3_TX2N_HDMI

PEG3_TX2P_HDMI

PEG3_TXCN_HDMI

PEG3_TXCP_HDMI

PEG5_HDMI_CLK

PEG5_HDMI_DATA

PLT3_RST#

RASA#

RDQSA(0:7)

WDQSA(0:7)

MAB(2)

MAB(3)

MAB(4)

MAB(5)

MCKEA

MCLKA0

MCLKA0#

MCLKA1

MCLKA1#

ODT

PEG1_RXN(15:0)

PEG1_RXP(15:0)

PEG1_TXN(15:0)

PEG1_TXP(15:0)

PEG3_BKLTEN

LCD1_BDATA2#

LCD3_BRIT

LCD3_EDID_CLK

LCD3_EDID_DATA

MAA(0)

MAA(1)

MAA(10)

MAA(11)

MAA(12)

MAA(2)

MAA(3)

MAA(4)

MAA(5)

MAA(6)

MAA(7)

MAA(8)

MAA(9)

HDA3_HDMI_SYNC

LCD1_ACLK

LCD1_ACLK#

LCD1_ADATA0

LCD1_ADATA0#

LCD1_ADATA1

LCD1_ADATA1#

LCD1_ADATA2

LCD1_ADATA2#

LCD1_BCLK

LCD1_BCLK#

LCD1_BDATA0

LCD1_BDATA0#

LCD1_BDATA1

LCD1_BDATA1#

LCD1_BDATA2

GFX3_I2CSDATA

GFX3_ROMSCLK

GFX3_ROMSI

GFX3_ROMSO

GFX3_STRAP0

GFX3_STRAP1

GFX3_STRAP2

GFX3_THERM#

GFX3_THERMDN

GFX3_THERMDP

GFX3_VOLTID_0

GFX3_VOLTID_1

HDA3_HDMI_BCLK

HDA3_HDMI_RST#

HDA3_HDMI_SDI2

HDA3_HDMI_SDO

CRT3_DDCCLK

CRT3_DDCDATA

CRT3_GREEN

CRT3_HSYNC

CRT3_RED

CRT3_VSYNC

CSA0#

DQA(63:0)

DQMA(7:0)

GFX3_HCLK

GFX3_HDATA

GFX3_I2CBCLK

GFX3_I2CBDATA

GFX3_I2CECLK

GFX3_I2CEDATA

GFX3_I2CSCLK

LCD1_BDATA1

LCD1_BDATA1#

LCD1_BDATA2

LCD1_BDATA2#

Gfx_External_Nvidia_Nb9x_64bit

BAA0

BAA1

BAA2

CASA#

CLK1_PEG

CLK1_PEG#

CLK3_GFX_27M

CLK3_GFX_27M_SS

CRT3_BLUE

CRT3_HSYNC

CRT3_GREEN

CRT3_DDCDATA

CRT3_DDCCLK

CRT3_BLUE

CLK3_GFX_27M_SS

CLK3_GFX_27M

CLK1_PEG#

CLK1_PEG

CASA#

BAA2

BAA1

BAA0

LCD1_BCLK

LCD1_BCLK#

LCD1_BDATA0

LCD1_BDATA0#

LCD1_BDATA1

LCD1_BDATA1#

LCD1_BDATA2

LCD1_BDATA2#

LCD1_BCLK

LCD1_BCLK#

LCD1_BDATA0

LCD1_BDATA0#

HDA3_HDMI_SYNC

HDA3_HDMI_SDO

HDA3_HDMI_SDI2

HDA3_HDMI_RST#

HDA3_HDMI_BCLK

GFX3_VOLTID_1

GFX3_VOLTID_0

GFX3_THERMDP

GFX3_THERMDN

GFX3_THERM#

GFX3_STRAP2

GFX3_STRAP1

GFX3_STRAP0

GFX3_ROMSO

GFX3_ROMSI

GFX3_ROMSCLK

GFX3_I2CSDATA

GFX3_I2CSCLK

GFX3_I2CEDATA

GFX3_I2CECLK

GFX3_I2CBDATA

GFX3_I2CBCLK

GFX3_HDATA

GFX3_HCLK

DQMA(7:0)

DQA(63:0)

CSA0#

CRT3_VSYNC

CRT3_RED

MAA(11)

MAA(10)

MAA(1)

MAA(0)

LCD3_EDID_DATA

LCD3_EDID_CLK

LCD3_BRIT

LCD1_ADATA2#LCD1_ADATA2LCD1_ADATA1#LCD1_ADATA1LCD1_ADATA0#LCD1_ADATA0

LCD1_ACLK#

LCD1_ACLK

PEG3_BKLTEN

PEG1_TXP(15:0)

PEG1_TXN(15:0)

PEG1_RXP(15:0)

PEG1_RXN(15:0)

ODT

MCLKA1#

MCLKA1

MCLKA0#

MCLKA0

MCKEA

MAB(5)

MAB(4)

MAB(3)

MAB(2)

MAA(9)

MAA(8)

MAA(7)

MAA(6)

MAA(5)

MAA(4)

MAA(3)

MAA(2)

MAA(12)

WDQSA(1)

WDQSA(2)

WDQSA(3)

WDQSA(4)

WDQSA(5)

WDQSA(6)

WDQSA(7)

WEA#WEA#

WDQSA(0:7)

RDQSA(0:7)

RASA#

PLT3_RST#

PEG5_HDMI_DATA

PEG5_HDMI_CLK

PEG3_TXCP_HDMI

PEG3_TXCN_HDMI

PEG3_TX2P_HDMI

PEG3_TX2N_HDMI

PEG3_TX1P_HDMI

PEG3_TX1N_HDMI

PEG3_TX0P_HDMI

PEG3_TX0N_HDMI

PEG3_LCDVDDON

PEG3_HPD_HDMI

MCKEA

MCLKA0

MCLKA0#

MCLKA1

MCLKA1#

ODT

RASA#

RDQSA(0)

RDQSA(1)

RDQSA(2)

RDQSA(3)

RDQSA(4)

RDQSA(5)

RDQSA(6)

RDQSA(7)

WDQSA(0)

CSA0#

DQA(15:0)

DQA(31:16)

DQA(47:32)

DQA(63:48)

DQMA(0)

DQMA(1)

DQMA(2)

DQMA(3)

DQMA(4)

DQMA(5)

DQMA(6)

DQMA(7)

MAA(12:0)

MAB(2)

MAB(3)

MAB(4)

MAB(5)

SPK5_LSPK5_R+

SPK5_R-

CLK1_MINIPCIE

CLK1_MINIPCIE#

KBC3_RFOFF#

MIN3_CLKREQ#

PEX1_MINIRXN1

PEX1_MINIRXP1

PEX1_MINITXN1

PEX1_MINITXP1

PEX3_WAKE#

PLT3_RST#

WLON_LED#

PEG3_BKLTEN

PEG3_HPD_HDMI

PEG3_LCDVDDON

BAA0

BAA1

BAA2

CASA#

AUD3_SPKR

AUD5_HP_O_LEFT

AUD5_HP_O_RIGHT

AUD5_LINE_O_LEFT

AUD5_LINE_O_RIGHT

AUD5_MIC1_LEFT

AUD5_MIC1_RIGHT

AUD5_MIC1_VREF_LEFT

AUD5_MIC1_VREF_RIGHT

AUD5_MIC2_LEFT

AUD5_MIC2_RIGHT

AUD5_MIC2_VREF

AUD5_SENS_A

AUD5_SENS_HP#

AUD5_SENS_MIC#

HDA3_AUD_BCLK

HDA3_AUD_RST#

HDA3_AUD_SDI0

HDA3_AUD_SDO

HDA3_AUD_SYNC

KBC3_SPKMUTE

SPK5_L+

PEG3_TX0P_HDMI

PEG3_TX1N_HDMI

PEG3_TX1P_HDMI

PEG3_TX2N_HDMI

PEG3_TX2P_HDMI

PEG3_TXCN_HDMI

PEG3_TXCP_HDMI

PEG5_HDMI_CLK

PEG5_HDMI_DATA

HDA3_MDC_BCLK

HDA3_MDC_RST#

HDA3_MDC_SDI1

HDA3_MDC_SDO

HDA3_MDC_SYNC

AUD3_BEEP

AUD3_GPIO0#

AUD3_GPIO1#

AUD3_SHDN#

CRT3_BLUE

CRT3_DDCCLK

CRT3_DDCDATA

CRT3_GREEN

CRT3_HSYNC

CRT3_RED

CRT3_VSYNC

CRT5_DDCCLK

CRT5_DDCDATA

CRT5_HSYNC

CRT5_VSYNC

KBC3_BKLTON

LCD1_ACLKLCD1_ACLK#

LCD1_ADATA0

LCD1_ADATA0#

LCD1_ADATA1

LCD1_ADATA1#

LCD1_ADATA2

LCD1_ADATA2#

LCD3_BKLTON

LCD3_BRIT

LCD3_EDID_CLK

LCD3_EDID_DATA

PEG3_TX0N_HDMI

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

VRM_ISEN1

VRM_ISEN2

VRM_PRM

VRM_VSUM

D D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

3

VRM_ISEN1

VRM_ISEN2

VRM_PRM

VRM_VSUM

A A

4

Confidential

Confidential

Confidential

KBC3_CHG4.2V

KBC3_PRECHG

KBC3_CHGEN

3

PWR_MV_Charger_ISL6256

KBC3_CHG4.2V

KBC3_CHGEN

KBC3_PRECHG

BAT3_SMCLK#

BAT3_SMDATA#

KBC3_SMCLK#

KBC3_SMDATA#

VDC_SGATE

BAT3_DETECT#

ADT3_SEL#

ADT3_SEL#

BAT3_DETECT#

B

KBC3_SUSPWR

AUX_PG

PWR_MV_MeMory

AUX_PG

KBC3_SUSPWR

MEM1_VREF

MEM1_VREF

Samsung

Samsung

Samsung

KBC3_PWRON VCCP3_PWRGD

BAT3_SMCLK#

BAT3_SMDATA#

KBC3_SMCLK#

KBC3_SMDATA#

VDC_SGATE

PWR_MV_3V_5V

AUX_PGKBC3_SUSPWR

AUX_PGKBC3_SUSPWR

PWR_MV_Cantiga

KBC3_PWRON VCCP3_PWRGD

C

PWR_CPU_MV_ISL6262

GCORE3_PWRGD

P1.1V_PWRGD

KBC3_VRON

CPU1_VSSSENSE

GCORE3_PWRGD

KBC3_VRON

P1.1V_PWRGD

CPU1_VSSSENSE

CPU1_VID(3)

CPU1_VID(4)

CPU1_VID(5)

CPU1_VID(6)

CPU1_VID(3)

CPU1_VID(4)

CPU1_VID(5)

CPU1_VID(6)

CPU1_VID(1)

CPU1_VID(2)

CPU1_VID(0)

CPU1_VID(1)

CPU1_VID(2)

CPU1_VCCSENSE

CPU1_DPRSTP#

CPU1_VID(0)

CPU1_PSI#

CHP3_DPRSLPVR

CPU1_DPRSTP#

CPU1_PSI#

CPU1_VCCSENSE

VRM3_CPU_PWRGD

CHP3_DPRSLPVR

VRM3_CPU_PWRGD

2

1

SRP Sheet Number: 11 of 73

SAMSUNG

ELECTRONICS

GFX3_VOLTID_0

GFX3_VOLTID_1

VCCP3_PWRGD

KBC3_PWRON

PWR_Gfx_MV_Ext

GFX3_VOLTID_1

KBC3_PWRON

VCCP3_PWRGD

GCORE3_PWRGDGFX3_VOLTID_0

P1.1V_PWRGD

GCORE3_PWRGD

P1.1V_PWRGD

B

KBC3_PWRON_INV#

KBC3_SUSPWR

PWR_MV_DisCharger

KBC3_PWRON_INV#

KBC3_SUSPWR

C

2

1

8-11

8-12

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

A

4

3

5.00 mm H

5.00 mm H

75.00 mm

34.00 mm W

75.00 mm L

EXPRESS CARD

INSERT

X

X

X

Confidential

Confidential

Confidential

75.00 mm L

X

54.00 mm W

THIS SIDE UP

75.00 mm

EXPRESS CARD

INSERT

THIS SIDE UP

3709-001491

MNT12MNT2

34.00 mm 54.00 mm

1

EXPRESS-26P-FRAME

J10

B

EXP3_CLKREQ#

PEX1_EXPCARDRXN3

PEX1_EXPCARDRXP3

PEX1_EXPCARDTXN3

Type 1 module

Type 2 module

PEX1_EXPCARDTXP3

CLK1_EXPCARD#

CLK1_EXPCARD

22

PERN021PERP0

PETN024PETP025REFCLK+19REFCLK-

RESERVED_15RESERVED_2

MNT1

MNT2

27

28

6

EXP3_CPPE#

17

18

CLKREQ#16CPPE#

GND_11GND_220GND_323GND_4

EXPRESS CARD

3711-006496

Samsung

Samsung

Samsung

EXP3_PERST#

PEX3_WAKE#

SMB3_DATA

nostuff

nostuff

R670

R710

0

0

11

13

WAKE#

PERST#

+1.5V_1

+1.5v_2

10

9

26

C

EXP3_CPUSB#

SMB3_CLK

USB3_P4+

USB3_P4-

nostuff

R669

0

4

2

CPUSB#

SMB_CLK7SMB_DATA8USB_D+3USB_D-

+3.3V_AUX

+3.3V_114+3.3V_2

15

12

P3.3V

R709

10K

J9

EDGE-XPRESS-26P

100nF

10V

C774

100nF

C773

10V

C772

10V

100nF

C771

10V

100nF

P3.3V_EXP

P3.3V_AUX_EXP

P1.5V_EXP

D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

3

2

1

SRP Sheet Number: 12 of 73

SAMSUNG

ELECTRONICS

CHP3_SLPS3#

PLT3_RST#

17

19

18

12

CPUSB*

16

EXP3_CPUSB#

RCLKEN20SHDN*

PERST*

CPPE*

10

9

8

SHORT503

0

EXP3_CPPE#

EXP3_PERST#

AUXIN

AUXOUT

15

14

1.5VIN_1

1.5VIN_2

1.5VOUT_1

1.5VOUT_2

11

13

3.3VIN_2

3.3VOUT_2

6

1205-002807

STBY*1SYSRST*

OC*

THERMAL

NC_5

GND

7

21

A

B

2

4

U519

R5538D001-TR-F

3.3VIN_1

3.3VOUT_1

3

5

C

C769

100nF

10V

P3.3V_AUX P1.5V_EXP

10V

100nF

C770

P1.5V

C729

100nF

10V

P3.3V

P3.3V_EXP

P3.3V_AUX_EXP

D

2

1

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

A

4

Confidential

Confidential

Confidential

3

B

Place the resistor as close as possible

to prevent 48MHz stub

nostuff

nostuff

nostuff

nostuff

nostuff

nostuff

2801-004666

12MHz

2

1

R289

47K

29

CFD8_SDD4_XDD0

CFD4_SDD0

CFD5_SDD1

CFD6_SDD2

CFD7_SDD3

35

36

37

38

39

MCD3_SDDATA1

MCD3_SDDATA2

MCD3_SDDATA0

MCD3_SDDATA3

R297

Y4

R296

1M

0

PLT3_RST#

R295

330

8

2

XI7XO

CFAD1_MSCLK_XDCLE

CFAD0_SDCLK_MSBS

CFD0_MSD0_SDCMD

CFD1_MSD1_XDWP#

CFD3_MSD3_XDRB#

CFD2_MSD2_SDWP

31

32

33

34

28

27

30

R279

33

MCD3_SDWP

MCD3_SDCLK

MCD3_SDCMD0

USB3_P10+

USB3_P10-

4

DM5DP

CFRESET_XDWR#

CFWR#_XDRD#

CFRD#_XDCE#

CFAD2_XDALE

25

23

24

26

10K

1%

R290

C483

0.018nF

50V

C485

0.018nF

50V

CLK3_FM48

Add for AU6372

(2008.02.29)

R298

0

Samsung

Samsung

Samsung

0904-002225

NC_111NC_212READER_EN16RESET#47REXT

GND6GNDH17GND_U9GND_VDD48GPON6

CFD10_SDD6_XDD2

CFD11_SDD7_XDD3

CFD9_SDD5_XDD1

CFD15_XDD7

CFD12_XDD4

CFD13_XDD5

CFD14_XDD6

CFWT#

46

44

45

40

41

42

43

EMC Solution(’07.10.18)

C467

50V

0.022nF

nostuff

50V

nostuff

0.022nF

C468

C876

1000nF

6.3V

6.3V

1000nF

C484

C481

10V

100nF 100nF

10V

C480

C475

100nF

10V

10

1

VDD_U

V1813VCC3VDD

SMCD#

XDCD#

SDCD#

CFCD#

22

21

19

20

MCD3_SDCD#

14

VDDH

CARD_POWER

MS_INS

18

15

C

10V

10V

AU6371

U15

100nF

10V

100nF

100nF

C476

C474

C482

P3.3V

P3.3V_MCD

40mil trace

D

2 IN 1 CARD

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

3

1

SRP Sheet Number: 13 of 73

SAMSUNG

ELECTRONICS

MCD3_SDDATA2

MCD3_SDDATA3

MCD3_SDDATA1

MCD3_SDDATA0

MCD3_SDCMD0

MCD3_SDCD#

MCD3_SDCLK

MCD3_SDWP

R864

R863

R862

R861

49.9

49.9

49.9

49.9

6.3V

3

1%

1

2

CD_DAT3

J515

EDGE-SD-9P

10000nF

C831

P3.3V_MCD

2-in-1 Socket

A

3709-001492

MNT2

12

13

MNT1

WRITE_PROTECT

1%

1%

1%

11

10

7

9

CARD_DETECT

DAT08DAT1

DAT2

6

VSS2

CLK5CMD

VDD4VSS1

8-13

8-14

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

A

NO_STUFF @ 88E8040

CTRL_12 CTRL18_25

Confidential

Confidential

Confidential

34

NO_STUFF @ 88E8040

2

NO_STUFF @ 88E8040

4.7K

R21

10V

100nF

C63

C34

4700nF

10V 6.3V

6.3V

20%

22000nF-X5R

C33

1

C14

10000nF

4700nF

10V

C15

10V

100nF

C13

R533

4.7K

C534

10V

4700nF

C533

100nF

10V

1

10000nF

6.3V

C532

C531

4700nF

10V

100nF

C21

10V

LAN3_VPDDATA

LAN3_VPDCLK

P3.3V_AUX

B8

BLM18PG181SN1

3

U2

BCP69-16

2 4

P1.2V_LAN

P3.3V_AUX

B505

BLM18PG181SN1

U507

BCP69-16

3

2 4

P1.8V_P2.5V_LAN

88E8040: 2.5V

88E8055: 1.8V

B

Place Nearby Pin39, Pin64

4.7uF @ 88E8040

C530

6.3V

10000nF

C528

100nF

10V

100nF

10V

C41

100nF

10V

C529

100nF

10V

C19

23

51

64

Pin Compatible with 88E8040 (1205-003399)

1205-003091|sqfn64e-therm

AVDD

NC_AVDDL_4

NC_VDD25

Samsung

Samsung

Samsung

THERMAL

RSET

65

88E8040: 2Kohm

88E8055: 4.99Kohm

R16

1%

6.3V

10V

10V

10V

P1.8V_P2.5V_LAN

10V10V

28

22

19

32

57

52

AVDD_AVDDL_1

AVDD_AVDDL_2

AVDD_AVDDL_3

NC_AVDDL_1

NC_AVDDL_2

NC_AVDDL_3

RESERVED_HSDDACP

RESERVED_HSDACN

RESERVED_TSTPT

TESTMODE

25

24

29

16

46

4.99K

2801-004668

C16

0.015nF

50V

1 2

50V

0.015nF

C17

It must be placed on bottom side

10000nF

100nF

100nF

100nF

100nF

100nF

58

XTALO

14

25MHz

Y1

C23

C35

C40

C44

C38

C24

13

7

VDD_6

VDD_72VDD_8

VDD_5

XTALI

15

100nF

10V

10V

100nF

10V

100nF

10V

100nF

P1.2V_LAN

48

44

39

VDD_1

VDD_2

VDD_333VDD_4

LOM_DISABLE_DISABLE#

VMAIN_AVLBL

10

47

R22

R23

4.7K

0

C18

C20

C22

C25

C61

C39

C36

C37

61

8

1

AVDDH_VDDO_TTL

VDDO_TTL_3

VDDO_TTL_4

SWITCH_VCC

VAUX_AVLBL

12

11

R17

0

P3.3V_AUX

P3.3V

100nF

100nF

100nF

100nF

C

P3.3V_AUX

LAN3_VPDDATA

LAN3_VPDCLK

P3.3V_AUX

45

40

41

VDDO_TTL_1

VDDO_TTL_2

VPD_CLK38VPD_DATA

CTRL18_CTRL25

SWITCH_VAUX

CTRL12

4

9

CTRL_12

CTRL18_25

10V

10V

10V

10V

LOM3_CLKREQ#

STUFF @ 88E8040

nostuff

R24

4.7K

42

43

37

36

35

34

CLKREQ#_PU_VDDO_TTL

RESERVED_PU_VDDO_TTL

SPI_CLK_NC

SPI_CS#_NC

SPI_DI_NC

SPI_DO_NC

LED_LINK10_100#_LED_SPEED#

LED_LINK1000#_NC

LED_ACTIVE#

LED_LINK#

3

59

63

62

60

NO_STUFF @ 88E8040

Place nearby LOM chip

49.9

1%

R510

1%

49.9

R511

49.9

1%

R512

1%

49.9

R513

49.9

1%

R514

1%

49.9

R515

49.9

1%

R516

1%

49.9

R517

10V

10

12

2603-000107

TCT4

TD4-

MCT4

MX4+

MX4-

13

14

15

PEX1_GLAN_RXN4

PEX1_GLAN_RXP4

PEX1_GLAN_TXN4

PEX1_GLAN_TXP4

CLK1_PCIELOM#

CLK1_PCIELOM

R18

C43

C42

100nF

100nF

4.7K

10V

10V

54

53

55

56

49

50

RX+_PCIE_RXP

RX-_PCIE_RXN

REFCLK+

REFCLK-

TX+_PCIE_TXP

TX-_PCIE_TXN

MDI+1_RXP

MDI+0_TXP

MDI-1_RXN

MDI-0_TXN

MDI+2_NC26MDI+3_NC

MDI-2_NC

21

27

18

17

20

LAN3_MDI0P

LAN3_MDI1P

LAN3_MDI2P

LAN3_MDI0N

LAN3_MDI1N

LAN3_MDI2N

C514

C515

10V

100nF

100nF

7

8

9

TCT3

TD2-6TD3+

TD3-11TD4+

MCT3

MX3+

MX2+

MX2-

MX3-

19

17

16

18

20

PEX3_WAKE#

PLT3_RST#

5

6

PERST#

WAKE#

88E8055

U503

MDI-3_NC

30

31

LAN3_MDI3P

LAN3_MDI3N

C516

10V

100nF

4

2

3

TCT1

TCT2

TD1+

TD1-5TD2+

MCT1

MCT2

MX1+

MX1-

21

23

22

P3.3V

C517

10V

100nF

1

LFE9261A-R

LT500

24

D

P1.8V_P2.5V_LAN

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

3

2

1

SRP Sheet Number: 14 of 73

SAMSUNG

ELECTRONICS

75 1%

R4

75

1%

R5

1%

75

R6

1%75

R7

P3.3V_AUX

4.7K

R519

4.7K

R518

6

8

7

AT24C08AN-10SU-2.7

U504

SCL

SDA5VCC

WP

1103-001333

GND

A13A2

A0

4

1

2

A

B

3KVC61nF

Need at least 2.5mm or more clearance

from conductive material

1nFC83KV

1nFC73KV

C

JACK-MODULE-10P

3

1

2

J502

RD+

TD+

TD-4TERM15TERM2

1

B4

CIC21J601NE

B3

CIC21J601NE

10

6

7

8

3722-001692

RD-

RING

TERM3

TERM49TIP

3711-000541

1

2

HDR-2P-SMD

J504

D

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

Samsung

Confidential

Samsung

Confidential

Samsung

Confidential

SRP Sheet Number: 15 of 73

Switched Power On (P3.3V & 1.8V)

C

Audio Power (nostuff)

Add for EMI(2008.04.29)

LAST EDIT

Add for SI(2008.03.07)Add for SI(2007.12.6)

3

MODULE CODE

12

Add for EMC(’08.01.16)

5th Layer

Add for EMI(2008.04.26)

B

1

Place near to

D

SAMSUNG PROPRIETARY

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

2

THIS DOCUMENT CONTAINS CONFIDENTIAL

D:/users/mobile62/mentor/istanbul/istanbul-pv_080718

ELECTRONICS

DRAW

PROPRIETARY INFORMATION THAT IS

SAMSUNG ELECTRONICS CO’S PROPERTY.

APPROVAL

CHECK

A

3

Place near to

SAMSUNG

Switched Power On (P5.0V)

4

PART NO.

B

EXCEPT AS AUTHORIZED BY SAMSUNG.

C

A

D

4

COM-22C-015(1996.6.5) REV. 3

undefined

EGFX_CORE

C888

1nF

50V

C404

10V

C400

10V

100nF

50V

P1.1V

100nF100nF

C550

C889

1nF

P5.0V_AUD

P5.0V_AUX

P5.0V_AUX_USB

10V

P1.8V

10V

C883

100nF

P1.1V

EGFX_CORE

100nF

C882

10V10V

C881

100nF100nF

C880

10V

P1.1V

Q20

RHU002N06

3

D

G

1

S

2

P3.3V

P3.3V

10V

C879

100nF

470K

R203

1%

10V

C549

100nF

100nF

C535

10V

P1.1V

P1.8V

C892

1nF

50V 50V

1nF

C885

100nF

C884

10V

P1.8V

50V

1nF

C891

P1.1V

C523

10V

P1.1V

P1.8V

P5.0V_AUX

P12.0V_ALW

100nF

C854

2200nF

10V

P1.1V

B506

HU-1M2012-121JT

100nF

C878

10V

P1.1V

10nF

C853

25V

R806

0

P1.1V

P1.8V

P1.8V_AUX

3

S3

P5.0V_AUX_USB

P5.0V

50V

C800

1nF

AP6680AGM

Q19

D1

5 6D27D38

D4

4

G

S1

1S22

50V

1nF

C890

P5.0V_AUX_USB

P1.1V

EGFX_COREP1.8V

SHORT514

0

10V

C285

100nF

1nF

C504

50V

P1.8V_AUX

2

S

B509

HU-1M2012-121JT

nostuff

RHU002N06

Q523

D

3

1

G

C832

10V

nostuff

100nF

P5.0V_AUX

6.3V

C804

10000nF

P5.0V_AUX_USB

P5.0V_AUX

EGFX_CORE

nostuff

P1.1V

EGFX_CORE

P1.8V

10V

C893

100nF

50V

1nF

C887

50V

C341

22nF

50V

10V

C415

100nF

P1.8V

P1.8V_AUX

EGFX_CORE

C886

1nF

2S23

S3

50V

C509

1nF

D1

8

7

D2

D36D4

5

G4S1

1

P5.0V_AUX_USB

AP4435GM

Q535

P5.0V_AUX_USB

25V

C803

10nF

RHU002N06

Q530

D

3

1

G

2

S

P5.0V_AUX_USB

nostuff

1%

R200

50V

C507

1nF

200K

1%

P5.0V_AUX_USB

470K

R199

100K

R758

1%

nostuff

30.1K

nostuff

0

R201

0

1%

R802

P3.3V

R808

3

1

G

2

S

100nF

C512

10V

EGFX_CORE

P5.0V_AUX_USB

RHU002N06

Q21

D

5

D1 D26D37D4

8

G

4

1

S12S2 S3

3

EGFX_CORE

P1.8V_AUX

100nF

C342

10V

Q28

AP6680AGM

10nF

C830

50V

P12.0V_ALW

100nF

C895

10V

P5.0V_AUX

R809

1%

200K

0

P3.3V_AUX

R801

100nF

10V

C810

RHU002N06

Q29

D

3

1

G

2

S

P5.0V_AUX

470K

R278

1%

100nF

1

D1

D2

2

D3

5

6

D4G

3

4

S

P5.0V_AUX

C809

10V

P12.0V_ALW

nostuff

Q524

FDC653N

10V

C674

100nF

P1.8V_AUX

P12.0V_ALW

10V

C464

2200nF

1nF

C511

50V

50V

C508

1nF

Q527

D

3

1

G

2

S

P3.3V

P5.0V_AUX_USB

P1.8V

P5.0V_AUX_USB

RHU002N06

P5.0V_AUX

R202

0

P5.0V_AUD

10V

C896

100nF100nF

C894

10V

P5.0V_AUX

10V

C506

100nF

KBC3_PWRON

KBC3_PWRON_INV#

KBC3_PWRON_INV#

KBC3_PWRON

P1.1V_PWRGD

VCCP3_PWRGD

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

8-15

8-16

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

COM-22C-015(1996.6.5) REV. 3

Top Side

Add for EMC (’08.01.16)

4

3

2

SRP Sheet Number: 16 of 73

SAMSUNG

ELECTRONICS

A

VDC

C56

50V

1nF

1nF

50V

C289

C679

25V

100nF

C92

100nF

25V

C51

100nF

25V

Add for EMC (’08.03.05)

C388

50V

1nF

VDC

1nF

50V

C68

VDC

C93

50V

1nF

VDC

1nF

C88

50V

VDC

Confidential

Confidential

Confidential

P3.3V

C286

10V

100nF

P3.3V

C665

50V

1nF

P3.3V P3.3V

C617

50V

1nF

50V

1nF

C616

P3.3V

50V

1nF

C31

P3.3V

1nF

C654

50V

RMNT-25-70-1P

MT2004

RMNT-25-90-1P

MT4 MT5

RMNT-25-90-1P

VDC

10V

VDC

10V

VDC

10V

VDC

10V

C91

100nF

10V

C212

10V

100nF

10V

100nF

C78

C405

100nF

10V

10V

100nF

C83

C565

100nF

10V

C409

10V

100nF

Board

Keyboard

B

Add for EMC (’08.01.16)

5th Layer

P1.8V_AUX

100nF

C138

P1.05V

C107

100nF

P1.05V

100nF

C66

P1.05V

C132

100nF

Samsung

Samsung

Samsung

Add for EMC (’08.01.16)

Bottom Side

P3.3V

C609

10V

P3.3V

P3.3V

P3.3V

P3.3V

P3.3V

P3.3V

100nF

C581

10V

100nF

C578

100nF

10V

RMNT-30-100-1P

MT6

RMNT-30-100-1P

MT2

100nF

10V

C548

10V

100nF

C556

C554

100nF

10V

C536

10V

100nF

100nF

10V

C537

P5.0V_AUX

P5.0V_AUX

P5.0V_AUX

P5.0V_AUX

P5.0V_AUX

P5.0V_AUX

P5.0V_AUX

P5.0V_AUX

VDC

25V

C57

100nF

P1.8V_AUX

C603

10V

100nF

P1.8V_AUX

100nF

10V

C94

P1.8V_AUX

C577

10V

100nF

P1.8V_AUX

100nF

10V

C340

RMNT-35-100-1P

MT500

RMNT-30-100-1P

MT9

C C

3711-005753

nostuff

nostuff

nostuff

P5.0V

10V

C904

100nF

P5.0V

10V

100nF

C905

P5.0V

C906

10V

100nF

P5.0V

100nF

10V

C907

Add for EMC (’08.06.09)

Bottom Side

MNT1

MNT2

8

9

7

11

12

R794

R795

1K

1K

1%

1%

AUX_PG

VRM3_CPU_PWRGD

CPU1_PWRGDCPU

CPU1_CPURST#

VCCP3_PWRGD

Add for EMC (’08.04.22)

VDC

C909

100nF

25V

VDC

C910

25V

100nF

VDC

25V

100nF

C911

VDC

100nF

C912

25V

Add for EMC (’08.06.09)

4th Layer

HDR-10P-1R-SMD

J13

11023456

VDC

P1.8V

P3.3V

P5.0V

CONTACT-PLATE-EMI

EMI503

CONTACT-PLATE-EMI

EMI504

10V

100nF

10V

100nF

10V

100nF

10V

100nF

10V

100nF

10V

100nF

100nF

10V

C897

C898

C899

C900

C901

C902

C903

EMI

EMI

P1.5V

P1.5V P1.5V

P1.5V

P1.5V

P1.5VP1.5V

System

RMNT-30-100-1P

MT7

RMNT-30-100-1P

MT8

RMNT-30-100-1P

MT3

RMNT-30-100-1P

MT501

RMNT-30-100-1P

MT502

RMNT-30-100-1P

MT1

2

1

3

MMBT3904

U9

2

1

3

MMBT3904

Q12

nostuff

nostuff

nostuff

2

1

3

MMBT3904

U8

D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

ICT PORT

3 2

For Debugging

1

A

B

D

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

8. Block Diagram and Schematic

KBC3_USBPWRON#

3

4 1

5

1205-002596

EN1*

EN2*

OC2*

OUT2

GND

6

USB3_P3+

6

45MNT1

MNT2

8

IN2OC1*

OUT1

7

USB3_P3-

HDR-4P-SMD

123

C C

TPS2062

J3

U528

C869

100nF

10V

P5.0V_AUX

B525

HU-1M2012-121JT

A A

4

Confidential

Confidential

Confidential

3

50V

0.1nF

C574

0.01nF

0.5pF

50V

C572

50V

0.018nF

C570

C576

0.022nF

50V

C573

0.027nF

0.047nF

50V

C571

50V

50V

50V50V

50V50V

0.5pF

0.1nF

0.01nF

0.018nF

0.022nF

0.027nF

0.047nF

C105

C104

C102

C99

C103

B

Samsung

Samsung

Samsung

C101

3711-000922

D D

DO NOT DISCLOSE TO OR DUPLICATE FOR OTHERS

THIS DOCUMENT CONTAINS CONFIDENTIAL

SAMSUNG ELECTRONICS CO’S PROPERTY.

EXCEPT AS AUTHORIZED BY SAMSUNG.

PROPRIETARY INFORMATION THAT IS

SAMSUNG PROPRIETARY

4

Sub Board Connector (Istanbul Only)

3

2

1

SRP Sheet Number: 17 of 73

SAMSUNG

ELECTRONICS

50V

2 3

REV1

1

1

N.C.

1-2

2-3

0.0033nF

C100

NO CONNECTION

PCB REVISION CONTROL ( ICT )