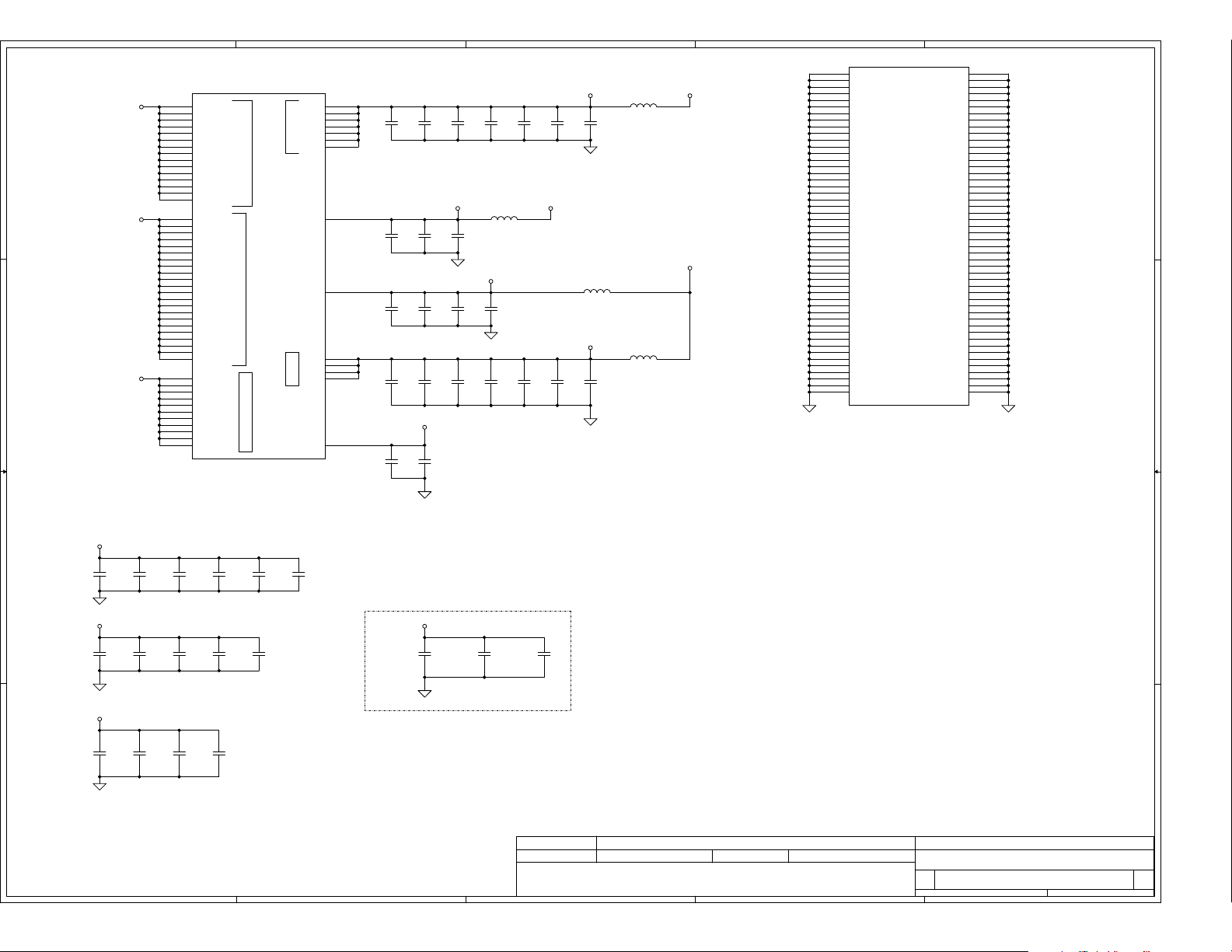

Samsung LA-8868P VBLE4 Eureka, NP355E5X, LA-8868P VBLE5 Eureka Schematic

A

1 1

B

C

D

E

VBLE4 / VBLE5

2 2

Eureka

LA-8868P SchematicREV 1.0

3 3

4 4

AMD Brazos 2.0 / Zacate APU / Hudson-M3L FCH

2012-07-12 Rev 1.0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

4019K4

4019K4

4019K4

147Saturday, September 07, 2013

147Saturday, September 07, 2013

147Saturday, September 07, 2013

E

B

B

B

of

of

of

A

B

C

D

E

CRT

Two DIMM/One Channel

page 20

1 1

LVDS Conn.

page 19

HDMI Conn.

page 21

AMD Zacate APU

FT1

BGA 413-Ball

19mm x 19mm

PCIE-Express 4X 5GHz

page 5,6,7,8

x4 UMI Gen. 1

2.5GT/s per lane

VGA (DDR3)

ATI Seymour XTX S3 64bit with 1GB

2 2

page 11~18

Hudson M3L

(A38M)

BGA 656-Ball

23mm x 23mm

HDMI Conn.

page 21

3 3

LCD Conn. CRT

RJ45

USB PORT 3.0 x2(Left)

USB3.0 port 0,1

RTL8105E-VB 10/100M

RTL811F Giga

page 20page 19

PCIe port 0

page 28

TPM

page 36page 36

page 32

PCIe 1x

1.5V 2.5GHz(250MB/s)

USB3.0x2

Debug Port

page 34

LPC BUS

ENE KB9012

page 33

page 22~26

HD Audio

3.3V 33 MHz

1.5V DDRIII 800MHZ

Memory BUS(DDRIII)

1.5V DDRIII 1066

USB2.0x6

5V 480MHz

PCIe 1x

1.5V 2.5GHz(250MB/s)

SATA port 0

5V 3GHz(300MB/s)

SATA port 1

5V 3GHz(300MB/s)

3.3V/1.5V 24MHz

200pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

USB PORT 2.0 x2(Right)

USB port 0,1

USB PORT 2.0 x2(Left)

USB port 10, 11

2IN1

RTS5129

USB port 7

Int. Camera

USB port 5

PCIeMini Card

WiMax

USB port 8

page 29

PCIeMini Card

WLAN

PCIe port 1

page 29

SATA HDD

page 27

SATA ODD

page 27

HDA Codec

ALC259-GR

page 31

page 27

page 28

page 32

page 19

page9,10

Daughter board

Daughter board

RTC CKT.

Power On/Off CKT.

RUSB+Power/B

LS-8865P

page 27

JTP

(Touch Pad)

page 35

Int.KBD

page 34

SPK Conn

page 31

JCRIO

(HP & MIC)

page 32

Audio+CR/B

LS-8864P

DC/DC Interface CKT.

4 4

Power Circuit DC/DC

A

ODD/B

LS-8862P

TP/B

LS-8863P

page 32

page 27

page 35

Daughter board

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

4019K4

4019K4

4019K4

247Saturday, September 07, 2013

247Saturday, September 07, 2013

247Saturday, September 07, 2013

E

of

of

of

B

B

B

A

B

C

D

E

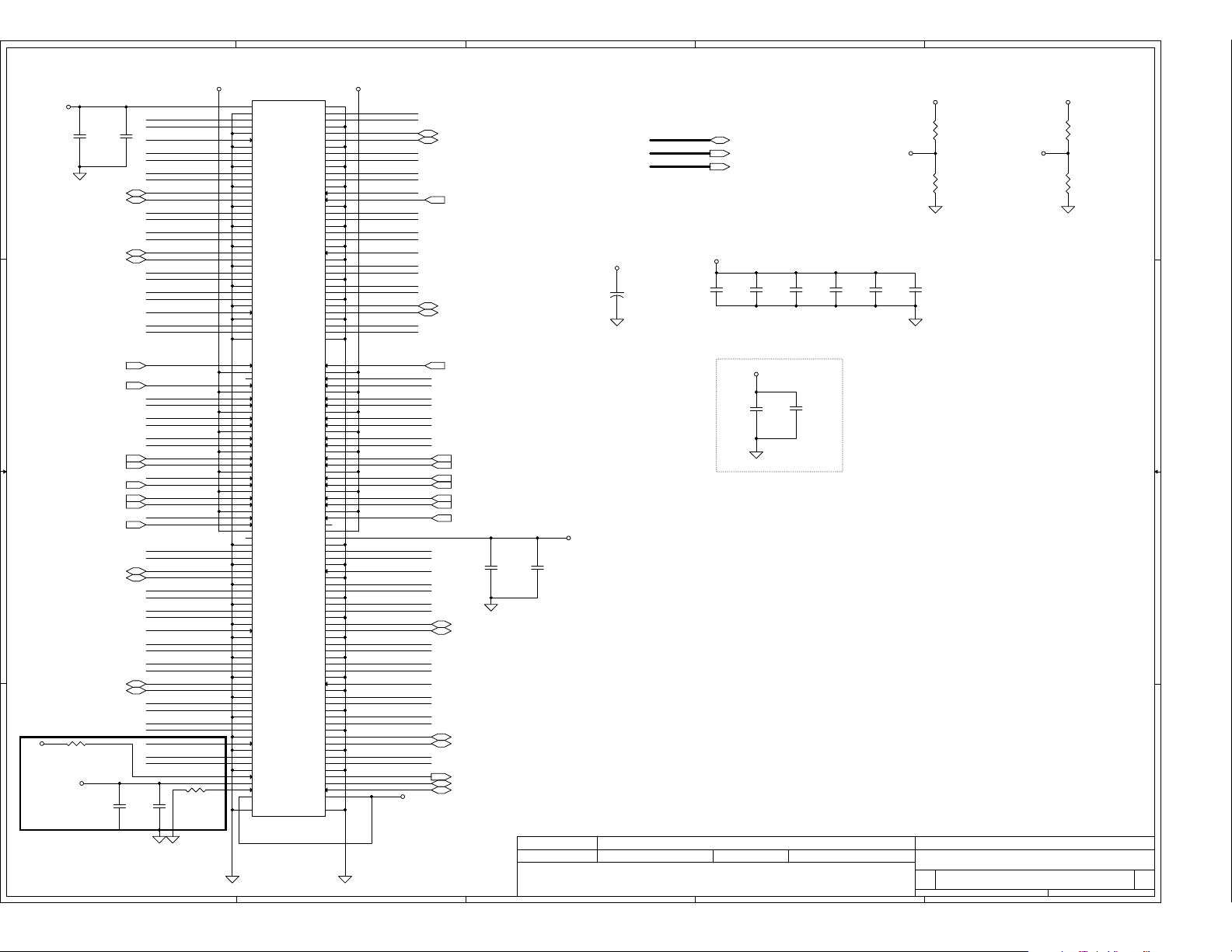

PCIE_CTX_GRX_P[3..0]<11>

PCIE_CTX_GRX_N[3..0]<11>

PCIE_CRX_GTX_P[3..0]<11>

PCIE_CRX_GTX_N[3..0]<11>

1 1

2 2

PCIE_CTX_GRX_P[3..0]

PCIE_CTX_GRX_N[3..0]

PCIE_CRX_GTX_P[3..0]

PCIE_CRX_GTX_N[3..0]

+1.05VS

1 2

R1

2K_0402_1%

UMI_RX0P<22>

UMI_RX0N<22>

UMI_RX1P<22>

UMI_RX1N<22>

UMI_RX2P<22>

UMI_RX2N<22>

UMI_RX3P<22>

UMI_RX3N<22>

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_N3

DIS@

U1A

E1R1@

AA6

P_GPP_RXP0

Y6

P_GPP_RXN0

AB4

P_GPP_RXP1

AC4

P_GPP_RXN1

AA1

P_GPP_RXP2

AA2

P_GPP_RXN2

Y4

P_GPP_RXP3

Y3

P_GPP_RXN3

Y14

P_ZVDD_10

AA12

P_UMI_RXP0

Y12

P_UMI_RXN0

AA10

P_UMI_RXP1

Y10

P_UMI_RXN1

AB10

P_UMI_RXP2

AC10

P_UMI_RXN2

AC7

P_UMI_RXP3

AB7

P_UMI_RXN3

S IC E SERIES EME450GBB22GVA 1.65G BGA

PCIE I/F

UMI I/F

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_ZVSS

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

AB6

PCIE_CTX_C_GRX_P0

AC6

PCIE_CTX_C_GRX_N0

AB3

PCIE_CTX_C_GRX_P1

AC3

PCIE_CTX_C_GRX_N1

Y1

PCIE_CTX_C_GRX_P2

Y2

PCIE_CTX_C_GRX_N2

V3

PCIE_CTX_C_GRX_P3

V4

PCIE_CTX_C_GRX_N3

AA14

P_ZVSSP_ZVDD_10

AB12

UMI_TX0P_C

AC12

UMI_TX0N_C

AC11

UMI_TX1P_C

AB11

UMI_TX1N_C

AA8

UMI_TX2P_C

Y8

UMI_TX2N_C

AB8

UMI_TX3P_C

AC8

UMI_TX3N_C

1 2

C518 0.1U_0402_16V7KDIS@

1 2

C519 0.1U_0402_16V7KDIS@

1 2

C520 0.1U_0402_16V7KDIS@

1 2

C521 0.1U_0402_16V7KDIS@

1 2

C522 0.1U_0402_16V7KDIS@

1 2

C523 0.1U_0402_16V7KDIS@

1 2

C524 0.1U_0402_16V7KDIS@

1 2

C525 0.1U_0402_16V7KDIS@

1 2

R2

DIS@

1.27K_0402_1%

1 2

C2 0.1U_0402_16V7K

1 2

C1 0.1U_0402_16V7K

1 2

C4 0.1U_0402_16V7K

1 2

C3 0.1U_0402_16V7K

1 2

C5 0.1U_0402_16V7K

1 2

C6 0.1U_0402_16V7K

1 2

C8 0.1U_0402_16V7K

1 2

C7 0.1U_0402_16V7K

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_N3

UMI_TX0P <22>

UMI_TX0N <22>

UMI_TX1P <22>

UMI_TX1N <22>

UMI_TX2P <22>

UMI_TX2N <22>

UMI_TX3P <22>

UMI_TX3N <22>

To FCHFrom FCH

FAN Control Circuit

+5VS

1A

3 3

EN_DFAN1<33>

4 4

A

+FAN

10mil

1

C36

10U_0805_10V6K

2

B

10U_0805_10V6K

U3

1

EN

GND

2

VIN

GND

3

VOUT

GND

4

VSET

GND

APL5607KI-TRG_SO8

8

7

6

5

+FAN

2

2

C18

C20

1000P_0402_50V7K

@

1

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

JFAN

@

1

1

2

2

3

3

4

GND

5

GND

ACES_85204-0300N

R63 10K_0402_5%

12

+3VS

1

C19

0.01U_0402_25V7K

@

2

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

FAN_SPEED1 <33>

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

4019K4

4019K4

4019K4

547Saturday, September 07, 2013

547Saturday, September 07, 2013

547Saturday, September 07, 2013

E

B

B

B

of

of

of

1

A A

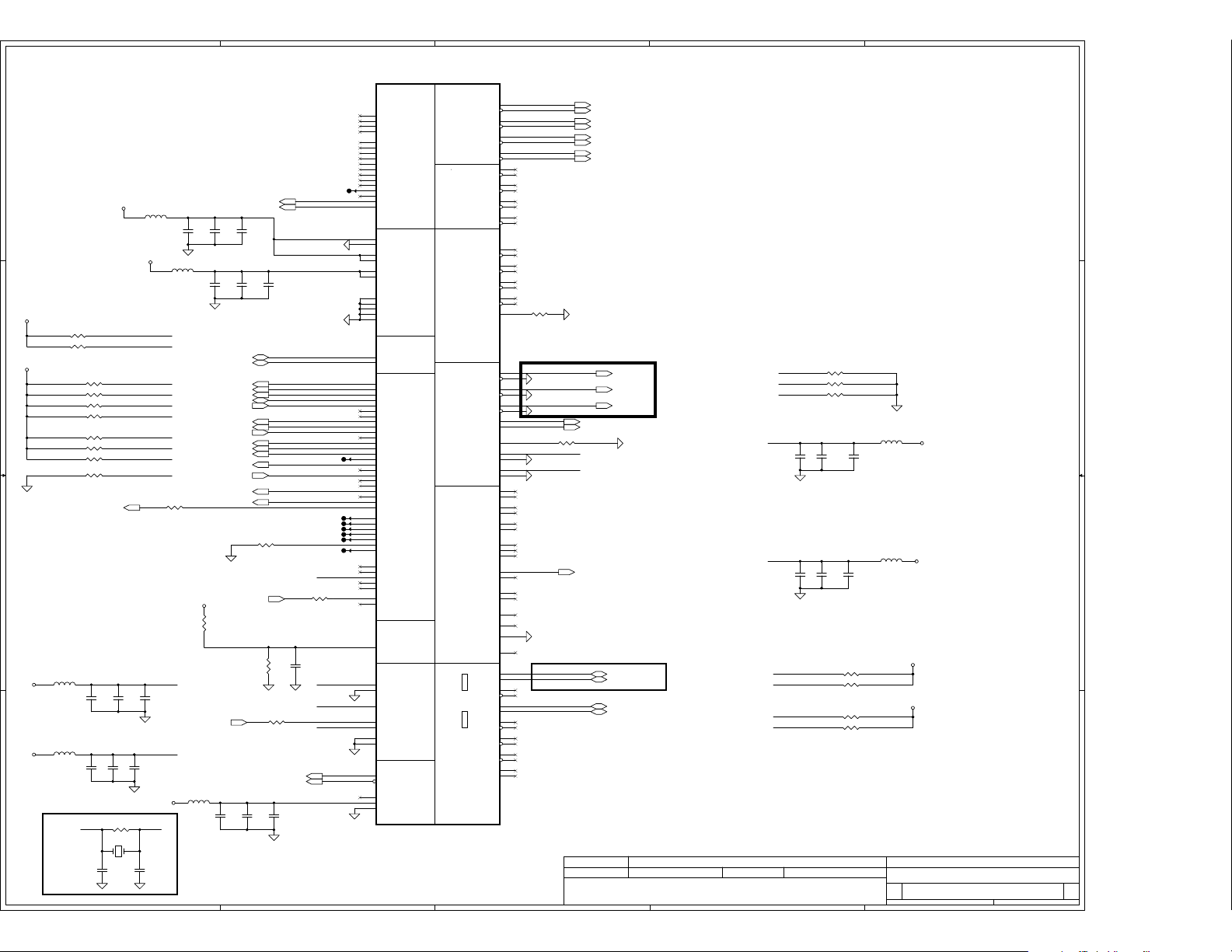

DDR_A_BS#0<9,10>

DDR_A_BS#1<9,10>

DDR_A_BS#2<9,10>

B B

DDR_A_CLK0<9>

DDR_A_CLK#0<9>

DDR_A_CLK1<9>

DDR_A_CLK#1<9>

DDR_B_CLK2<10>

DDR_B_CLK#2<10>

DDR_B_CLK3<10>

+1.5V

1 2

R4 1K_0402_5%

C C

MA_EVENT_L

8/6 Add C78 for ESD request

DDR_RST#

1

C78

180P_0402_50V8J

2

DDR_B_CLK#3<10>

DDR_RST#<9,10>

MA_EVENT_L<9,10>

DDR_CKE0_DIMMA<9,10>

DDR_CKE1_DIMMA<9,10>

DDR_A_ODT0<9>

DDR_A_ODT1<9>

DDR_B_ODT0<10>

DDR_B_ODT1<10>

DDR_CS0_DIMMA#<9>

DDR_CS1_DIMMA#<9>

DDR_CS0_DIMMB#<10>

DDR_CS1_DIMMB#<10>

DDR_A_RAS#<9,10>

DDR_A_CAS#<9,10>

DDR_A_WE#<9,10>

2

U1E

E1R1@

DDR_A_MA0<9,10>

DDR_A_MA1<9,10>

DDR_A_MA2<9,10>

DDR_A_MA3<9,10>

DDR_A_MA4<9,10>

DDR_A_MA5<9,10>

DDR_A_MA6<9,10>

DDR_A_MA7<9,10>

DDR_A_MA8<9,10>

DDR_A_MA9<9,10>

DDR_A_MA10<9,10>

DDR_A_MA11<9,10>

DDR_A_MA12<9,10>

DDR_A_MA13<9,10>

DDR_A_MA14<9,10>

DDR_A_MA15<9,10>

DDR_A_DM0<9,10>

DDR_A_DM1<9,10>

DDR_A_DM2<9,10>

DDR_A_DM3<9,10>

DDR_A_DM4<9,10>

DDR_A_DM5<9,10>

DDR_A_DM6<9,10>

DDR_A_DM7<9,10>

DDR_A_DQS0<9,10>

DDR_A_DQS#0<9,10>

DDR_A_DQS1<9,10>

DDR_A_DQS#1<9,10>

DDR_A_DQS2<9,10>

DDR_A_DQS#2<9,10>

DDR_A_DQS3<9,10>

DDR_A_DQS#3<9,10>

DDR_A_DQS4<9,10>

DDR_A_DQS#4<9,10>

DDR_A_DQS5<9,10>

DDR_A_DQS#5<9,10>

DDR_A_DQS6<9,10>

DDR_A_DQS#6<9,10>

DDR_A_DQS7<9,10>

DDR_A_DQS#7<9,10>

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK1

DDR_A_CLK#1

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK3

DDR_B_CLK#3

DDR_RST#

MA_EVENT_L

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_A_ODT0

DDR_A_ODT1

DDR_B_ODT0

DDR_B_ODT1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS0_DIMMB#

DDR_CS1_DIMMB#

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

R17

M_ADD0

H19

M_ADD1

J17

M_ADD2

H18

M_ADD3

H17

M_ADD4

G17

M_ADD5

H15

M_ADD6

G18

M_ADD7

F19

M_ADD8

E19

M_ADD9

T19

M_ADD10

F17

M_ADD11

E18

M_ADD12

W17

M_ADD13

E16

M_ADD14

G15

M_ADD15

R18

M_BANK0

T18

M_BANK1

F16

M_BANK2

D15

M_DM0

B19

M_DM1

D21

M_DM2

H22

M_DM3

P23

M_DM4

V23

M_DM5

AB20

M_DM6

AA16

M_DM7

A16

M_DQS_H0

B16

M_DQS_L0

B20

M_DQS_H1

A20

M_DQS_L1

E23

M_DQS_H2

E22

M_DQS_L2

J22

M_DQS_H3

J23

M_DQS_L3

R22

M_DQS_H4

P22

M_DQS_L4

W22

M_DQS_H5

V22

M_DQS_L5

AC20

M_DQS_H6

AC21

M_DQS_L6

AB16

M_DQS_H7

AC16

M_DQS_L7

M17

M_CLK_H0

M16

M_CLK_L0

M19

M_CLK_H1

M18

M_CLK_L1

N18

M_CLK_H2

N19

M_CLK_L2

L18

M_CLK_H3

L17

M_CLK_L3

L23

M_RESET_L

N17

M_EVENT_L

F15

M_CKE0

E15

M_CKE1

W19

M0_ODT0

V15

M0_ODT1

U19

M1_ODT0

W15

M1_ODT1

T17

M0_CS_L0

W16

M0_CS_L1

U17

M1_CS_L0

V16

M1_CS_L1

U18

M_RAS_L

V19

M_CAS_L

V17

M_WE_L

S IC E SERIES EME450GBB22GVA 1.65G BGA

DDR SYSTEM MEMORY

M_ZVDDIO_MEM_S

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_VREF

3

B14

A15

A17

D18

A14

C14

C16

D16

C18

A19

B21

D20

A18

B18

A21

C20

C23

D23

F23

F22

C22

D22

F20

F21

H21

H23

K22

K21

G23

H20

K20

K23

N23

P21

T20

T23

M20

P20

R23

T22

V20

V21

Y23

Y22

T21

U23

W23

Y21

Y20

AB22

AC19

AA18

AA23

AA20

AB19

Y18

AC17

Y16

AB14

AC14

AC18

AB18

AB15

AC15

M23

M22

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

M_ZVDDIO_MEM_S

DDR_A_D0 <9,10>

DDR_A_D1 <9,10>

DDR_A_D2 <9,10>

DDR_A_D3 <9,10>

DDR_A_D4 <9,10>

DDR_A_D5 <9,10>

DDR_A_D6 <9,10>

DDR_A_D7 <9,10>

DDR_A_D8 <9,10>

DDR_A_D9 <9,10>

DDR_A_D10 <9,10>

DDR_A_D11 <9,10>

DDR_A_D12 <9,10>

DDR_A_D13 <9,10>

DDR_A_D14 <9,10>

DDR_A_D15 <9,10>

DDR_A_D16 <9,10>

DDR_A_D17 <9,10>

DDR_A_D18 <9,10>

DDR_A_D19 <9,10>

DDR_A_D20 <9,10>

DDR_A_D21 <9,10>

DDR_A_D22 <9,10>

DDR_A_D23 <9,10>

DDR_A_D24 <9,10>

DDR_A_D25 <9,10>

DDR_A_D26 <9,10>

DDR_A_D27 <9,10>

DDR_A_D28 <9,10>

DDR_A_D29 <9,10>

DDR_A_D30 <9,10>

DDR_A_D31 <9,10>

DDR_A_D32 <9,10>

DDR_A_D33 <9,10>

DDR_A_D34 <9,10>

DDR_A_D35 <9,10>

DDR_A_D36 <9,10>

DDR_A_D37 <9,10>

DDR_A_D38 <9,10>

DDR_A_D39 <9,10>

DDR_A_D40 <9,10>

DDR_A_D41 <9,10>

DDR_A_D42 <9,10>

DDR_A_D43 <9,10>

DDR_A_D44 <9,10>

DDR_A_D45 <9,10>

DDR_A_D46 <9,10>

DDR_A_D47 <9,10>

DDR_A_D48 <9,10>

DDR_A_D49 <9,10>

DDR_A_D50 <9,10>

DDR_A_D51 <9,10>

DDR_A_D52 <9,10>

DDR_A_D53 <9,10>

DDR_A_D54 <9,10>

DDR_A_D55 <9,10>

DDR_A_D56 <9,10>

DDR_A_D57 <9,10>

DDR_A_D58 <9,10>

DDR_A_D59 <9,10>

DDR_A_D60 <9,10>

DDR_A_D61 <9,10>

DDR_A_D62 <9,10>

DDR_A_D63 <9,10>

1 2

R6 39.2_0402_1%

+1.5V

4

1000P_0402_25V8J

5

+1.5V

R5

15 mil

+MEM_VREF

1

1

C14

C13

0.1U_0402_16V7K

2

2

1K_0402_1%

1 2

R7

1K_0402_1%

1 2

Close to CPU within 1"

D D

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

4019K4

4019K4

4019K4

5

of

647Saturday, September 07, 2013

of

647Saturday, September 07, 2013

of

647Saturday, September 07, 2013

B

B

B

5

4

3

2

1

+1.8VS

1 2

R10 1K_0402_5%

1 2

R23 1K_0402_5%

1 2

R24 300_0402_5%

1 2

R22 300_0402_5%

D D

1 2

R26 510_0402_1%

1 2

R25 1K_0402_5%

C103 100P_0402_50V8J@

C104 100P_0402_50V8J@

1 2

1 2

APU_RST#

APU_PWRGD

12/13 For debug if layout cross mote

+3VS

1 2

R16 1K_0402_5%

1 2

R17 1K_0402_5%

C C

1 2

R19 1K_0402_5%

1 2

R31 1K_0402_5%

APU_SVC

APU_SVD

APU_RST#

APU_PWRGD

TEST_25_L

TEST36

APU_ALERT#

APU_PROCHOT#

APU_SIC

APU_SID

Check

TO EC

APU_VDDNB_RUN_FB_H<43>

APU_VDD0_RUN_FB_H<43>

UMA_HDMI_TX2+<21>

UMA_HDMI_TX2-<21>

UMA_HDMI_TX1+<21>

UMA_HDMI_TX1-<21>

UMA_HDMI_TX0+<21>

UMA_HDMI_TX0-<21>

UMA_HDMI_TXC+<21>

UMA_HDMI_TXC-<21>

UMA_TXOUT2+<19>

UMA_TXOUT2-<19>

UMA_TXOUT1+<19>

UMA_TXOUT1-<19>

UMA_TXOUT0+<19>

UMA_TXOUT0-<19>

UMA_TXCLK+<19>

UMA_TXCLK-<19>

APU_CLK<22>

APU_CLK#<22>

APU_DISP_CLK<22>

APU_DISP_CLK#<22>

APU_SVC<43>

EC_SMB_CK2<18,33>

EC_SMB_DA2<18,33>

H_PROCHOT#<22,33>

APU_VDD0_RUN_FB_L<43>

APU_VDDNB_RUN_FB_L<43>

T13PAD

APU_SVD<43>

R809 0_0402_5%

R810 0_0402_5%

APU_RST#<22>

APU_PWRGD<22,43>

1 2

@

R34 0_0402_5%

1 2

R931 0_0402_5%

1 2

R932 0_0402_5%

1 2

@

1 2

@

APU_SVC

APU_SVD

APU_SIC

APU_SID

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_THERMTRIP#_R

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

VDDIO_MEM_S_SENSE

9/26 Add R931 R932 for AMD common design

U1B

E1R1@

A8

TDP1_TXP0

B8

TDP1_TXN0

B9

TDP1_TXP1

A9

TDP1_TXN1

D10

TDP1_TXP2

C10

TDP1_TXN2

A10

TDP1_TXP3

B10

TDP1_TXN3

B5

LTDP0_TXP0

A5

LTDP0_TXN0

D6

LTDP0_TXP1

C6

LTDP0_TXN1

A6

LTDP0_TXP2

B6

LTDP0_TXN2

D8

LTDP0_TXP3

C8

LTDP0_TXN3

V2

CLKIN_H

V1

CLKIN_L

D2

DISP_CLKIN_H

D1

DISP_CLKIN_L

J1

SVC

J2

SVD

P3

SIC

P4

SID

T3

RESET_L

T4

PWROK

U1

PROCHOT_L

U2

THERMTRIP_L

T2

ALERT_L

N2

TDI

N1

TDO

P1

TCK

P2

TMS

M4

TRST_L

M3

DBRDY

M1

DBREQ_L

F4

VDDCR_NB_SENSE

G1

VDDCR_CPU_SENSE

F3

VDDIO_MEM_S_SENSE

F1

VSS_SENSE

B4

RSVD_1

W11

RSVD_2

V5

RSVD_3

S IC E SERIES EME450GBB22GVA 1.65G BGA

SA00005DX00

DISPLAYPORT 1

DISPLAYPORT 0

CLK

SER

JTAG CTRL

DP MISC

DAC_GREENB

VGA DAC

TEST

DMAACTIVE_L

DP_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

TDP1_AUXP

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_REDB

DAC_GREEN

DAC_BLUE

DAC_BLUEB

DAC_HSYNC

DAC_VSYNC

DAC_SCL

DAC_SDA

DAC_ZVSS

TEST4

TEST5

TEST6

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST31

TEST33_H

TEST33_L

TEST34_H

TEST34_L

TEST35

TEST36

TEST37

TEST38

H3

G2

H2

H1

B2

C2

C1

A3

B3

D3

C12

D13

A12

B12

A13

B13

E1

E2

F2

D4

D12

R1

R2

R6

T5

E4

K4

L1

L2

M2

K1

K2

L5

M5

M21

J18

J19

U15

T15

H4

N5

R5

K3

T1

DP_ZVSS

UMA_HDMI_CLK

UMA_HDMI_DATA

LCD_EDID_CLK

LCD_EDID_DATA

UMA_CRT_CLK

UMA_CRT_DATA

DAC_ZVSS

TEST_18

TEST_19

TEST25_H

TEST_25_L

TEST28_H

TEST28_L

TEST31

TEST33_H

TEST33_L

TEST34_H

TEST34_L

TEST35

TEST36

TEST37

1 2

R20 150_0402_1%UMA@

UMA_ENBKL <19>

UMA_ENVDD <19>

UMA_PWM <19>

UMA_HDMI_CLK <21>

UMA_HDMI_DATA <21>

UMA_HDMI_HPD <21>

UMA_EDID_CLK <19>

UMA_EDID_DATA <19>

1 2

R12 100K_0402_5%UMA@

UMA_CRT_R <20>

UMA_CRT_G <20>

UMA_CRT_B <20>

UMA_CRT_HSYNC <20>

UMA_CRT_VSYNC <20>

UMA_CRT_CLK <20>

UMA_CRT_DATA <20>

1 2

R30 499_0402_1%UMA@

T3

PAD

T4

PAD

T5

PAD

T6

PAD

T7

PAD

1 2

R33 1K_0402_5%

1 2

R35 1K_0402_5%

1 2

R36 510_0402_1%

T9

PAD

T8

PAD

T10

PAD

1 2

C15 0.1U_0402_16V4Z

1 2

C16 0.1U_0402_16V4Z

T11

PAD

T12

PAD

T15

PAD

1 2

R40 1K_0402_5%

DMA_ACTIVE# <22>

1 2

R37 51_0402_1%

1 2

R38 51_0402_1%

1 2

R39 1K_0402_5%@

1 2

R283 1K_0402_5%

+1.8VS

UMA_ENBKL

UMA_CRT_R

UMA_CRT_G

UMA_CRT_B

UMA_CRT_CLK

UMA_CRT_DATA

UMA_EDID_CLK

UMA_EDID_DATA

UMA_HDMI_CLK

UMA_HDMI_DATA

12/22 Change R510, R511,R515,R516

to 2k that meet AMD check list

+1.8VS

1 2

R933 100K_0402_5%UMA@

1 2

R407 150_0402_1%UMA@

1 2

R408 150_0402_1%UMA@

1 2

R409 150_0402_1%UMA@

+3VS

12

R834.7K_0402_5% UMA@

12

R824.7K_0402_5% UMA@

12

R5102K_0402_1% UMA@

12

R5112K_0402_1% UMA@

12

R5152K_0402_1% UMA@

12

R5162K_0402_1% UMA@

B B

+1.8VS

1 2

R44 1K_0402_5%

1 2

R45 1K_0402_5%

1 2

R46 1K_0402_5%

1 2

R47 1K_0402_5%

1 2

R48 1K_0402_5%

APU_TRST#

R846 0_0402_5%@

A A

R847 10K_0402_5%@

R848 10K_0402_5%@

R849 10K_0402_5%@

AMD HDT Debug Conn

APU_TRST#

APU_TCK

APU_TMS

APU_TDI

APU_DBREQ#

+1.8VS

JHDT

1

3

5

12

12

12

12

5

7

9

11

13

15

17

19

2

1

2

4

3

4

6

5

6

8

7

8

10

9

10

12

11

12

14

13

14

16

15

16

18

17

18

20

19

20

SAMTE_ASP-136446-07-B

@

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PWRGD_R

APU_RST#_R

APU_DBRDY

APU_DBREQ#

J108_PLLTST0

J108_PLLTST1

1 2

R854 0_0402_5%@

1 2

R853 0_0402_5%@

To close APU side

1 2

R851 0_0402_5%@

1 2

R852 0_0402_5%@

4

APU_PWRGD

APU_RST#

TEST_19

TEST_18

1K_0402_5%

APU_THERMTRIP#_R

12/22 PCH side has internal pull up +3VLAW_PCH,

so need to level shift

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+3VS

R41

12

1 2

B

2

E

3 1

MMBT3904_NL_SOT23-3

1 2

R927 0_0402_5%

@

2

10K_0402_5%

R926

Q39

C

H_THERMTRIP# <24>

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

4019K4

4019K4

4019K4

1

747Saturday, September 07, 2013

747Saturday, September 07, 2013

747Saturday, September 07, 2013

of

of

of

B

B

B

A

U1C

E1R1@

+APU_CORE

11000mA

1 1

+APU_VDDNB

10000mA

2 2

+1.5V

2000mA

E5

VDDCR_CPU_1

E6

VDDCR_CPU_2

F5

VDDCR_CPU_3

F7

VDDCR_CPU_4

G6

VDDCR_CPU_5

G8

VDDCR_CPU_6

H5

VDDCR_CPU_7

H7

VDDCR_CPU_8

J6

VDDCR_CPU_9

J8

VDDCR_CPU_10

L7

VDDCR_CPU_11

M6

VDDCR_CPU_12

M8

VDDCR_CPU_13

N7

VDDCR_CPU_14

R8

VDDCR_CPU_15

E8

VDDCR_NB_1

E11

VDDCR_NB_2

E13

VDDCR_NB_3

F9

VDDCR_NB_4

F12

VDDCR_NB_5

G11

VDDCR_NB_6

G13

VDDCR_NB_7

H9

VDDCR_NB_8

H12

VDDCR_NB_9

K11

VDDCR_NB_10

K13

VDDCR_NB_11

L10

VDDCR_NB_12

L12

VDDCR_NB_13

L14

VDDCR_NB_14

M11

VDDCR_NB_15

M12

VDDCR_NB_16

M13

VDDCR_NB_17

N10

VDDCR_NB_18

N12

VDDCR_NB_19

N14

VDDCR_NB_20

P11

VDDCR_NB_21

P13

VDDCR_NB_22

G16

VDDIO_MEM_S_1

G19

VDDIO_MEM_S_2

E17

VDDIO_MEM_S_3

J16

VDDIO_MEM_S_4

L16

VDDIO_MEM_S_5

L19

VDDIO_MEM_S_6

N16

VDDIO_MEM_S_7

R16

VDDIO_MEM_S_8

R19

VDDIO_MEM_S_9

W18

VDDIO_MEM_S_10

U16

VDDIO_MEM_S_11

S IC E SERIES EME450GBB22GVA 1.65G BGA

TSense/PLL/DP/PCIE/IO

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

VDD_18_5

VDD_18_6

CPU CORE

VDD_18_7

DAC

VDD_18_DAC

GPU AND NB CORE

POWER

DIS PLL

VDDPL_10

PCIE/IO/DDR3 Phy

VDD_10_1

VDD_10_2

VDD_10_3

VDD_10_4

DDR3

DP Phy/IO

VDD_33

B

600mA

U8

W8

U6

U9

W6

T7

V7

0.1U_0402_16V7K

1

C75

@

2

180P_0402_50V8J

C23

1

C24

2

1U_0402_6.3V6K

1

2

NOTE-->VDD_18+VDD_18_DAC=600mA

NOTE-->VDDPL_10+VDD_10=2500mA

W9

U11

U13

W13

V12

T12

A4

180P_0402_50V8J

2500mA

500mA

0.1U_0402_16V7K

1

C76

2

180P_0402_50V8J

1

C77

2

1

C94

2

180P_0402_50V8J

1

C40

2

1U_0402_6.3V6K

1

C28

@

2

1U_0402_6.3V6K

1

C30

@

2

0.1U_0402_16V7K

0.1U_0402_16V7K

1

@

C34

2

0.1U_0402_16V7K

+3VS

1

C41

1U_0402_6.3V6K

2

+1.8VS_DAC

C29

C31

C35

1

2

1

2

1

2

1U_0402_6.3V6K

C25

1 2

FBMA-L11-201209-221LMA30T_0805

10U_0603_6.3V6M

+1.05VS_VDDPL

C32

1U_0402_6.3V6K

C99

1

C26

2

1U_0402_6.3V6K

L2

1

10U_0603_6.3V6M

2

1

C37

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C21

2

+1.8VS

FBMA-L11-201209-221LMA30T_0805

10U_0603_6.3V6M

1

C38

2

C

+1.8VS_VDD

FBMA-L11-201209-221LMA30T_0805

1

1

C22

10U_0603_6.3V6M

2

2

L3

1 2

+1.05VS_VDD

FBMA-L11-201209-221LMA30T_0805

1

1

C39

10U_0603_6.3V6M

2

2

L1

1 2

L4

1 2

+1.8VS

+1.05VS

D

U1D

E1R1@

A7

VSS_1

B7

VSS_2

B11

VSS_3

B17

VSS_4

B22

VSS_5

C4

VSS_6

D5

VSS_7

D7

VSS_8

D9

VSS_9

D11

VSS_10

D14

VSS_11

B15

VSS_12

D17

VSS_13

D19

VSS_14

E7

VSS_15

E9

VSS_16

E12

VSS_17

E20

VSS_18

F8

VSS_19

F11

VSS_20

F13

VSS_21

G4

VSS_22

G5

VSS_23

G7

VSS_24

G9

VSS_25

G12

VSS_26

G20

VSS_27

G22

VSS_28

H6

VSS_29

H11

VSS_30

H13

VSS_31

J4

VSS_32

J5

VSS_33

J7

VSS_34

J20

VSS_35

K10

VSS_36

K14

VSS_37

L4

VSS_38

L6

VSS_39

L8

VSS_40

L11

VSS_41

L13

VSS_42

L20

VSS_43

L22

VSS_44

M7

VSS_45

N4

VSS_46

N6

VSS_47

N8

VSS_48

N11

VSS_49

S IC E SERIES EME450GBB22GVA 1.65G BGA

GND

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSSBG_DAC

N13

N20

N22

P10

P14

R4

R7

R20

T6

T9

T11

T13

U4

U5

U7

U12

U20

U22

V8

V9

V11

V13

W1

W2

W4

W5

W7

W12

W20

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

AA4

AA22

AB2

AB5

AB9

AB13

AB17

AB21

AC5

AC9

AC13

A11

E

+1.5V

10U_0603_6.3V6M

0.1U_0402_16V7K

C61

0.1U_0402_16V7K

C85

+1.5V

C96

+1.5V

3 3

4 4

1

C86

2

10U_0603_6.3V6M

0.1U_0402_16V7K

1

C97

2

1

C60

@

2

0.1U_0402_16V7K

A

1U_0402_6.3V6K

1

C87

2

1

C98

2

0.1U_0402_16V7K

180P_0402_50V8J

1

@

C100

2

1

C89

2

1U_0402_6.3V6K

180P_0402_50V8J

1

C90

2

1

C101

@

2

180P_0402_50V8J

1U_0402_6.3V6K

1

C92

2

1

C91

2

180P_0402_50V8J

1

@

2

1

C93

2

1U_0402_6.3V6K

1

2

1

2

Add for EMI request on DVT

+1.5V

B

C95

1U_0402_6.3V6K

1

0.1U_0402_16V7K

2

C102

1

180P_0402_50V8J

2

1

C105

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

4019K4

4019K4

4019K4

E

B

B

847Saturday, September 07, 2013

847Saturday, September 07, 2013

847Saturday, September 07, 2013

B

of

of

of

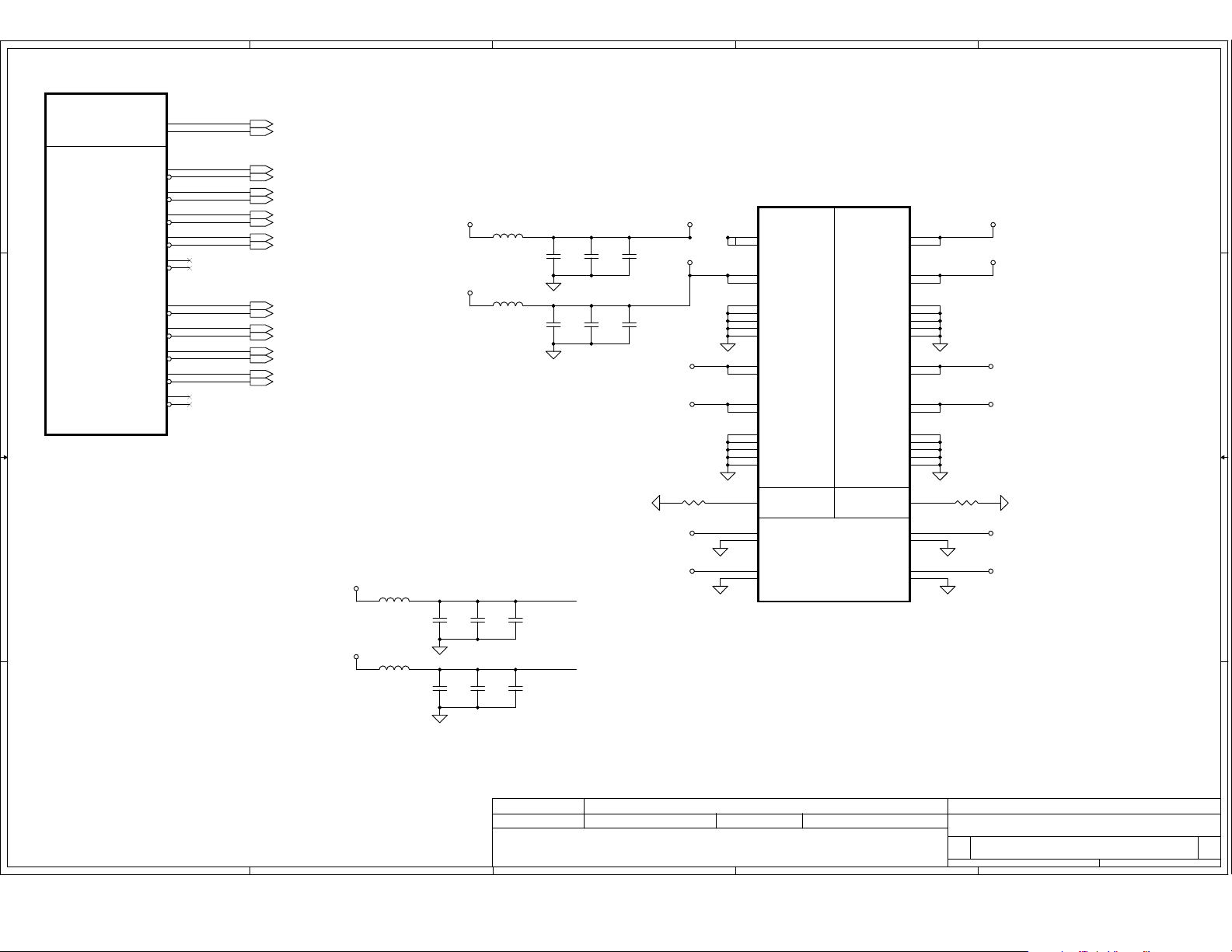

5

+1.5V

+VREF_DQA

1

C626

C627

2

C464

0.1U_0402_16V4Z

DDR_A_DQS#1<6,10>

DDR_A_DQS1<6,10>

DDR_A_DQS#2<6,10>

DDR_A_DQS2<6,10>

DDR_CKE0_DIMMA<6,10>

DDR_A_BS#2<6,10>

DDR_A_CLK0<6>

DDR_A_CLK#0<6>

DDR_A_BS#0<6,10>

DDR_A_WE#<6,10>

DDR_A_CAS#<6,10>

DDR_CS1_DIMMA#<6>

DDR_A_DQS#4<6,10>

DDR_A_DQS4<6,10>

DDR_A_DQS#6<6,10>

DDR_A_DQS6<6,10>

12

C647

5

D D

C C

B B

A A

+3VS

2.2U_0603_10V6K

1

2

1000P_0402_50V7K

1

2

0.1U_0402_16V4Z

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

R445 10K_0402_5%

1 2

12

R446

10K_0402_5%

JDDR3L

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

LCN_DAN06-K4406-0102

@

VSS3

DQS#0

DQS0

VSS6

VSS8

DQ12

DQ13

VSS10

DQ14

DQ15

DQ20

DQ21

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

VTT2

DQ4

DQ5

DQ6

DQ7

DM1

DM2

CK1

NC2

DM4

DM6

SDA

SCL

4

+1.5V

2

4

DDR_A_D4

6

DDR_A_D5

8

10

12

14

16

DDR_A_D6

18

DDR_A_D7

20

22

DDR_A_D12

24

DDR_A_D13

26

28

DDR_A_DM1

30

32

34

DDR_A_D14

36

DDR_A_D15

38

40

DDR_A_D20

42

DDR_A_D21

44

46

DDR_A_DM2

48

50

DDR_A_D22

52

DDR_A_D23

54

56

DDR_A_D28

58

DDR_A_D29

60

62

64

66

68

DDR_A_D30

70

DDR_A_D31

72

74

76

78

A15

A14

A11

A7

A6

A4

A2

A0

BA1

S0#

G2

DDR_A_MA15

80

DDR_A_MA14

82

84

DDR_A_MA11

86

DDR_A_MA7

88

90

DDR_A_MA6

92

DDR_A_MA4

94

96

DDR_A_MA2

98

DDR_A_MA0

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+0.75VS

4

DDR3 SO-DIMM A

Standard Type

DDR_A_DQS#0 <6,10>

DDR_A_DQS0 <6,10>

DDR_RST# <6,10>

DDR_A_DQS#3 <6,10>

DDR_A_DQS3 <6,10>

DDR_CKE1_DIMMA <6,10>

DDR_A_CLK1 <6>

DDR_A_CLK#1 <6>

DDR_A_BS#1 <6,10>

DDR_A_RAS# <6,10>

DDR_CS0_DIMMA# <6>

DDR_A_ODT0 <6>

DDR_A_ODT1 <6>

1

C669

2

0.1U_0402_16V4Z

DDR_A_DQS#5 <6,10>

DDR_A_DQS5 <6,10>

DDR_A_DQS#7 <6,10>

DDR_A_DQS7 <6,10>

MA_EVENT_L <6,10>

FCH_SDATA0 <10,24,29>

FCH_SCLK0 <10,24,29>

H=4.0mm

1000P_0402_50V7K

3

DDR_A_D[0..63]

DDR_A_MA[0..15]

DDR_A_DM[0..7]

+1.5V

2

C628

1

0.1U_0402_16V4Z

+VREF_CAA

1

C670

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

0.1U_0402_16V4Z

2

C629

1

DDR_A_D[0..63] <6,10>

DDR_A_MA[0..15] <6,10>

DDR_A_DM[0..7] <6,10>

0.1U_0402_16V4Z

2

C630

1

0.1U_0402_16V4Z

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

C631

1

0.1U_0402_16V4Z

2

2

1

2

0.1U_0402_16V4Z

C632

+1.5V

+VREF_DQA

0.1U_0402_16V4Z

2

2

2

C633

1

0.1U_0402_16V4Z

1

C635

C634

@

@

1

0.1U_0402_16V4Z

CRB 0.1u X1 4.7u X1

+0.75VS

2

C641

C642

1

0.1U_0402_16V4Z

Place near JDIMML

Title

Title

Title

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

R440

1K_0402_1%

1 2

R442

1K_0402_1%

1 2

2

1

1

2

4.7U_0603_6.3V6K

4019K4

4019K4

4019K4

0.1U_0402_16V4Z

C636

@

1

+VREF_CAA

2

C638

@

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C637

@

1

CRB 100U X2

+1.5V

1

+

2

1

+1.5V

R441

1K_0402_1%

1 2

R443

1K_0402_1%

1 2

2

C639

@

1

C643

330U_B2_2.5VM_R15M

<BOM Structure>

of

of

of

947Saturday, September 07, 2013

947Saturday, September 07, 2013

947Saturday, September 07, 2013

B

B

B

5

4

3

2

1

VSS3

DQS0

VSS6

VSS8

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

CK1#

RAS#

ODT0

ODT1

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQS5

DQ46

DQ47

DQ52

DQ53

DQ54

DQ55

DQ60

DQ61

DQS7

DQ62

DQ63

VTT2

DQ4

DQ5

DQ6

DQ7

DM1

DM2

CK1

BA1

NC2

DM4

DM6

SDA

SCL

+1.5V

2

4

DDR_A_D4

6

DDR_A_D5

8

10

12

14

16

DDR_A_D6

18

DDR_A_D7

20

22

DDR_A_D12

24

DDR_A_D13

26

28

DDR_A_DM1

30

32

34

DDR_A_D14

36

DDR_A_D15

38

40

DDR_A_D20

42

DDR_A_D21

44

46

DDR_A_DM2

48

50

DDR_A_D22

52

DDR_A_D23

54

56

DDR_A_D28

58

DDR_A_D29

60

62

64

66

68

DDR_A_D30

70

DDR_A_D31

72

74

76

78

A15

A14

A11

A7

A6

A4

A2

A0

S0#

G2

DDR_A_MA15

80

DDR_A_MA14

82

84

DDR_A_MA11

86

DDR_A_MA7

88

90

DDR_A_MA6

92

DDR_A_MA4

94

96

DDR_A_MA2

98

DDR_A_MA0

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

4

+0.75VS

DDR_A_DQS#0 <6,9>

DDR_A_DQS0 <6,9>

DDR_A_DQS#3 <6,9>

DDR_A_DQS3 <6,9>

DDR3 SO-DIMM B

Standard Type

DDR_RST# <6,9>

DDR_CKE1_DIMMA <6,9>

DDR_B_CLK3 <6>

DDR_B_CLK#3 <6>

DDR_A_BS#1 <6,9>

DDR_A_RAS# <6,9>

DDR_CS0_DIMMB# <6>

DDR_B_ODT1 <6>

1

C665

2

0.1U_0402_16V4Z

DDR_A_DQS#5 <6,9>

DDR_A_DQS5 <6,9>

DDR_A_DQS#7 <6,9>

DDR_A_DQS7 <6,9>

MA_EVENT_L <6,9>

FCH_SDATA0 <9,24,29>

FCH_SCLK0 <9,24,29>

H=8.0mm

DDR_A_D[0..63]

DDR_A_MA[0..15]

DDR_A_DM[0..7]

+1.5V

1

+

C199

330U_B2_2.5VM_R15M

@

2

+VREF_CAB

1

C666

2

1000P_0402_50V7K

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

DDR_A_D[0..63] <6,9>

DDR_A_MA[0..15] <6,9>

DDR_A_DM[0..7] <6,9>

+1.5V

0.1U_0402_16V4Z

2

2

1

0.1U_0402_16V4Z

C650

C651

1

0.1U_0402_16V4Z

CRB 0.1u X1 4,7uX1

+0.75VS

2

C663

1

0.1U_0402_16V4Z

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

C664

2

C652

1

1

2

4.7U_0603_6.3V6K

2

0.1U_0402_16V4Z

2

C653

1

0.1U_0402_16V4Z

+VREF_DQB

2

C654

1

+1.5V

R444

1K_0402_1%

1 2

R447

1K_0402_1%

1 2

2

C655

0.1U_0402_16V4Z

1

Title

Title

Title

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

4019K4

4019K4

4019K4

Date: Sheet

Date: Sheet

Date: Sheet

+VREF_CAB

+1.5V

R450

1K_0402_1%

1 2

R451

1K_0402_1%

1 2

10 47Saturday, September 07, 2013

10 47Saturday, September 07, 2013

10 47Saturday, September 07, 2013

of

of

1

of

B

B

B

+1.5V

+VREF_DQB

1

C649

C648

D D

C C

B B

+3VS

A A

2

0.1U_0402_16V4Z

DDR_A_DQS#1<6,9>

DDR_A_DQS1<6,9>

DDR_A_DQS#2<6,9>

DDR_A_DQS2<6,9>

DDR_CKE0_DIMMA<6,9>

DDR_A_BS#2<6,9>

DDR_B_CLK2<6>

DDR_B_CLK#2<6>

DDR_A_BS#0<6,9>

DDR_A_WE#<6,9>

DDR_A_CAS#<6,9> DDR_B_ODT0 <6>

DDR_CS1_DIMMB#<6>

DDR_A_DQS#4<6,9>

DDR_A_DQS4<6,9>

DDR_A_DQS#6<6,9>

DDR_A_DQS6<6,9>

1 2

R84 4.7K_0402_5%

+3VS

2.2U_0603_10V6K

C667

12

1

2

1000P_0402_50V7K

1

C668

2

0.1U_0402_16V4Z

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

1 2

R449

10K_0402_5%

Check SMB address

5

JDDR3H

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

VDD999VDD10

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

LCN_DAN06-K4806-0102

@

DQS#0

VSS10

VSS17

VSS19

VSS21

VDD12

VDD14

VDD16

VDD18

VREF_CA

VSS28

VSS30

VSS31

VSS33

VSS35

DQS#5

VSS38

VSS40

VSS42

VSS43

VSS45

VSS47

DQS#7

VSS50

VSS52

EVENT#

5

4

3

2

1

PCIE_CRX_GTX_P[3..0]

PCIE_CRX_GTX_N[3..0]

AH30

PCIE_CRX_C_GTX_P0

AG31

PCIE_CRX_C_GTX_N0

AG29

PCIE_CRX_C_GTX_P1

AF28

PCIE_CRX_C_GTX_N1 PCIE_CRX_GTX_N1

AF27

PCIE_CRX_C_GTX_P2

AF26

PCIE_CRX_C_GTX_N2

AD27

PCIE_CRX_C_GTX_P3

AD26

PCIE_CRX_C_GTX_N3 PCIE_CRX_GTX_N3

AC25

AB25

Y23

Y24

AB27

AB26

Y27

Y26

W24

W23

V27

U26

U24

U23

T26

T27

T24

T23

P27

P26

P24

P23

M27

N26

Y22

AA22

1 2

RV1 1.27K_0402_1%DIS@

1 2

RV2 2K_0402_1%DIS@

PCIE_CRX_GTX_P[3..0] <5>

PCIE_CRX_GTX_N[3..0] <5>

12

CV10.1U_0402_16V7K DIS@

12

CV20.1U_0402_16V7K DIS@

12

CV30.1U_0402_16V7K

12

CV40.1U_0402_16V7K DIS@

12

CV50.1U_0402_16V7K

12

CV60.1U_0402_16V7K DIS@

12

CV70.1U_0402_16V7K

12

CV80.1U_0402_16V7K DIS@

+1.0VS

DIS@

DIS@

DIS@

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P3

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_N3

1 2

PCIE_CTX_GRX_P[3..0]

PCIE_CTX_GRX_N[3..0]

PCIE_CTX_GRX_P[3..0]<5>

PCIE_CTX_GRX_N[3..0]<5>

D D

C C

B B

CLK_PCIE_VGA<22>

CLK_PCIE_VGA#<22>

RV133 10K_0402_5%DIS@

APU_PCIE_RST#<22,29,30,32>

UV1A

AF30

PCIE_RX0P

AE31

PCIE_RX0N

AE29

PCIE_RX1P

AD28

PCIE_RX1N

AD30

PCIE_RX2P

AC31

PCIE_RX2N

AC29

PCIE_RX3P

AB28

PCIE_RX3N

AB30

PCIE_RX4P

AA31

PCIE_RX4N

AA29

PCIE_RX5P

Y28

PCIE_RX5N

Y30

PCIE_RX6P

W31

PCIE_RX6N

W29

PCIE_RX7P

V28

PCIE_RX7N

V30

PCIE_RX8P

U31

PCIE_RX8N

U29

PCIE_RX9P

T28

PCIE_RX9N

T30

PCIE_RX10P

R31

PCIE_RX10N

R29

PCIE_RX11P

P28

PCIE_RX11N

P30

PCIE_RX12P

N31

PCIE_RX12N

N29

PCIE_RX13P

M28

PCIE_RX13N

M30

PCIE_RX14P

L31

PCIE_RX14N

L29

PCIE_RX15P

K30

PCIE_RX15N

CLOCK

AK30

PCIE_REFCLKP

AK32

PCIE_REFCLKN

N10

PWRGOOD

AL27

PERSTB

2160809024A11SEYMOU_FCBGA631

SEYMOURR1@

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCI EXPRESS INTERFACE

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

CALIBRATION

PCIE_CALRP

PCIE_CALRN

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2012/05/18 2013/10/05

2012/05/18 2013/10/05

2012/05/18 2013/10/05

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

SCHEMATIC, MB A8868

4019K4

4019K4

4019K4

11 47Saturday, September 07, 2013

11 47Saturday, September 07, 2013

11 47Saturday, September 07, 2013

1

B

B

B

of

of

of

5

D D

+1.8VS

LV8

12

DIS@

+1.0VS

BLM18PG121SN1D_0603

VGA_EDID_CLK

VGA_EDID_DATA

VGA_PWRSEL0

VGA_PWRSEL1

THERM#_VGA

CLKREQ_PEG#_R

GENERIC_C

GPU_SMB_DA2

GPU_SMB_CK2

VGA_ENBKL

+DPLL_PVDD

1

CV42

1U_0402_6.3V4Z

DIS@

2

+DPLL_VDDC

1

DIS@

CV45

2

1U_0402_6.3V4Z

+1.8VS

@

XTALINXTALOUT

CV103

18P_0402_50V8J

10U_0603_6.3V6M

1

DIS@

CV54

2

LV10

DIS@

1 2

@

RV27 0_0402_5%

RV20

499_0402_1%

DIS@

BLM18PG121SN1D_0603

LV7

DIS@

10U_0603_6.3V6M

@

1U_0402_6.3V4Z

12

+1.8VS

12

VGA_X1<29>

BLM18PG121SN1D_0603

+3VS

12

RV139 4.7K_0402_5%DIS@

12

RV140 4.7K_0402_5%DIS@

+3VS

C C

B B

BLM18PG121SN1D_0603

+1.8VS

LV3

DIS@

BLM18PG121SN1D_0603

+1.0VS

LV5

DIS@

A A

10U_0603_6.3V6M

@

1 2

CLKREQ_PEG#<24>

12

1

DIS@

CV40

2

10U_0603_6.3V6M

12

0.1U_0402_16V4Z

1

CV43

DIS@

2

27MHZ_16PF_X5H027000FG1H

CV94

18P_0402_50V8J

12

RV3010K_0402_5%

12

RV13110K_0402_5%

12

RV3210K_0402_5%DIS@

12

RV3310K_0402_5%@

12

RV3510K_0402_5%@

12

RV3110K_0402_5%@

12

RV14210K_0402_5%@

RV1710K_0402_5%DIS@

0.1U_0402_16V4Z

1

CV41

DIS@

2

1

CV44

DIS@

2

RV97

1M_0402_5%

YV1

@

2 1

5

VRAM_ID1<18>

VRAM_ID0<18>

0.1U_0402_16V4Z

1

1

DIS@

DIS@

CV53

CV55

2

2

0.1U_0402_16V4Z

1

DIS@

CV6110U_0603_6.3V6M

2

LCD

VGA_EDID_CLK<19>

VGA_EDID_DATA<19>

GPU_GPIO0<18>

GPU_GPIO1<18>

GPU_GPIO2<18>

GPU_SMB_DA2<18>

GPU_SMB_CK2<18>

VGA_ENBKL<19>

SOUT_GPIO8<18>

SIN_GPIO9<18>

GPU_GPIO11<18>

GPU_GPIO12<18>

GPU_GPIO13<18>

VGA_PWRSEL0<45>

THERM#_VGA<18>

VGA_PWRSEL1<45>

ROMSE_GPIO22<18>

1

1

DIS@

CV60

2

2

1U_0402_6.3V4Z

DIS@

RV19 10K_0402_5%

VGA_HDMI_HPD<21>

12

RV21

249_0402_1%

DIS@

DIS@

CV59

VGA_EDID_CLK

VGA_EDID_DATA

GPU_SMB_DA2

GPU_SMB_CK2

VGA_ENBKL

VGA_PWRSEL0

THERM#_VGA

VGA_PWRSEL1

CLKREQ_PEG#_R

Check voltage level

1 2

DIS@

RV28 0_0402_5%

GPU_THERMAL_D+<18>

GPU_THERMAL_D-<18>

12

0.1U_0402_16V4Z

1

DIS@

CV50

2

1

1

DIS@

CV51

2

2

12

CV52

1U_0402_6.3V4Z

DIS@

Need to check

+DPC_VDD18

+DPC_VDD18

+DPC_VDD10

0_0402_5%

1 2

RV143

DIS@

+VGA_VREF

1

CV49

0.1U_0402_16V4Z

2

DIS@

+TSVDD

4

TV15

TV11

TV14

TV9

TV12

TV13

TV10

TV18

GENERIC_C

+DPLL_PVDD

+DPLL_VDDC

XTALIN

XTALOUT

4

UV1B

Y11

DVCLK

AE9

DVCNTL_0

L9

DVCNTL_1

N9

DVCNTL_2

AE8

DVDATA_12

AD9

DVDATA_11

AC10

DVDATA_10

AD7

DVDATA_9

AC8

DVDATA_8

AC7

DVDATA_7

AB9

DVDATA_6

AB8

DVDATA_5

AB7

DVDATA_4

AB4

DVDATA_3

AB2

DVDATA_2

Y8

DVDATA_1

Y7

DVDATA_0

W6

DPC_VDD18#3

V6

DP_VSSR#13

AC6

DPC_VDD18#1

AC5

DPC_VDD18#2

AA5

DPC_VDD10#1

AA6

DPC_VDD10#2

U1

DP_VSSR#14

W1

DP_VSSR#15

U3

DP_VSSR#16

Y6

DP_VSSR#17

AA1

DP_VSSR#18

I2C

R1

SCL

R3

SDA

GENERAL PURPOSE I/O

U6

GPIO_0

U10

GPIO_1

T10

GPIO_2

U8

GPIO_3_SMBDATA

U7

GPIO_4_SMBCLK

T9

GPIO_5_AC_BATT

T8

GPIO_6

T7

GPIO_7_BLON

P10

GPIO_8_ROMSO

P4

GPIO_9_ROMSI

P2

GPIO_10_ROMSCK

N6

GPIO_11

N5

GPIO_12

N3

GPIO_13

Y9

GPIO_14_HPD2

N1

GPIO_15_PWRCNTL_0

M4

GPIO_16

R6

GPIO_17_THERMAL_INT

W10

GPIO_18_HPD3

M2

GPIO_19_CTF

P8

GPIO_20_PWRCNTL_1

P7

GPIO_21_BB_EN

N8

GPIO_22_ROMCSB

N7

GPIO_23_CLKREQB

L6

JTAG_TRSTB

L5

JTAG_TDI

L3

JTAG_TCK

L1

JTAG_TMS

K4

JTAG_TDO

K7

TESTEN

AF24

TESTEN_LEGACY

AB13

GENERICA

W8

GENERICB

W9

GENERICC

W7

GENERICD

AD10

GENERICE_HPD4

AC14

HPD1

AB16

PX_EN

AC16

VREFG

PLL/CLOCK

AF14

DPLL_PVDD

75mA

AE14

DPLL_PVSS

AD14

125mA

DPLL_VDDC

AM28

XTALIN

AK28

XTALOUT

AC22

XO_IN

AB22

XO_IN2

THERMAL

T4

DPLUS

T2

DMINUS

R5

TS_FDO

AD17

TSVDD

AC17

TSVSS

20mA

2160809024A11SEYMOU_FCBGA631

SEYMOURR1@

DVO

TXCAP_DPA3P

TXCAM_DPA3N

TX0P_DPA2P

TX0M_DPA2N

DPA

TX1P_DPA1P

TX1M_DPA1N

TX2P_DPA0P

TX2M_DPA0N

TXCBP_DPB3P

TXCBM_DPB3N

TX3P_DPB2P

TX3M_DPB2N

DPB

TX4P_DPB1P

TX4M_DPB1N

TX5P_DPB0P

TX5M_DPB0N

DPC

TXCCP_DPC3P

TXCCM_DPC3N

TX0P_DPC2P

TX0M_DPC2N