Page 1

DVD MINI COMPONENT

MAX945D

SERVICE

Manual

DVD MINI COMPONENT SYSTME CONTENTS

S.BASS

1. Reference Information

2. Alignment and Adjustments

3. Disassembly and Reassembly

4. Circuit Description

5. Exploded Views and Parts List

6. Electrical Parts List

7. Block Diagrams

8. PCB Diagrams

9. Wiring Diagram

10. Schematic Diagrams

Page 2

ELECTRONICS

© Samsung Electronics Co.,Ltd. AUG. 1999

Printed in Korea

Code no. AH68-00073H

Page 3

Samsung Electronics 1-1

1. Reference Information(DVD Part)

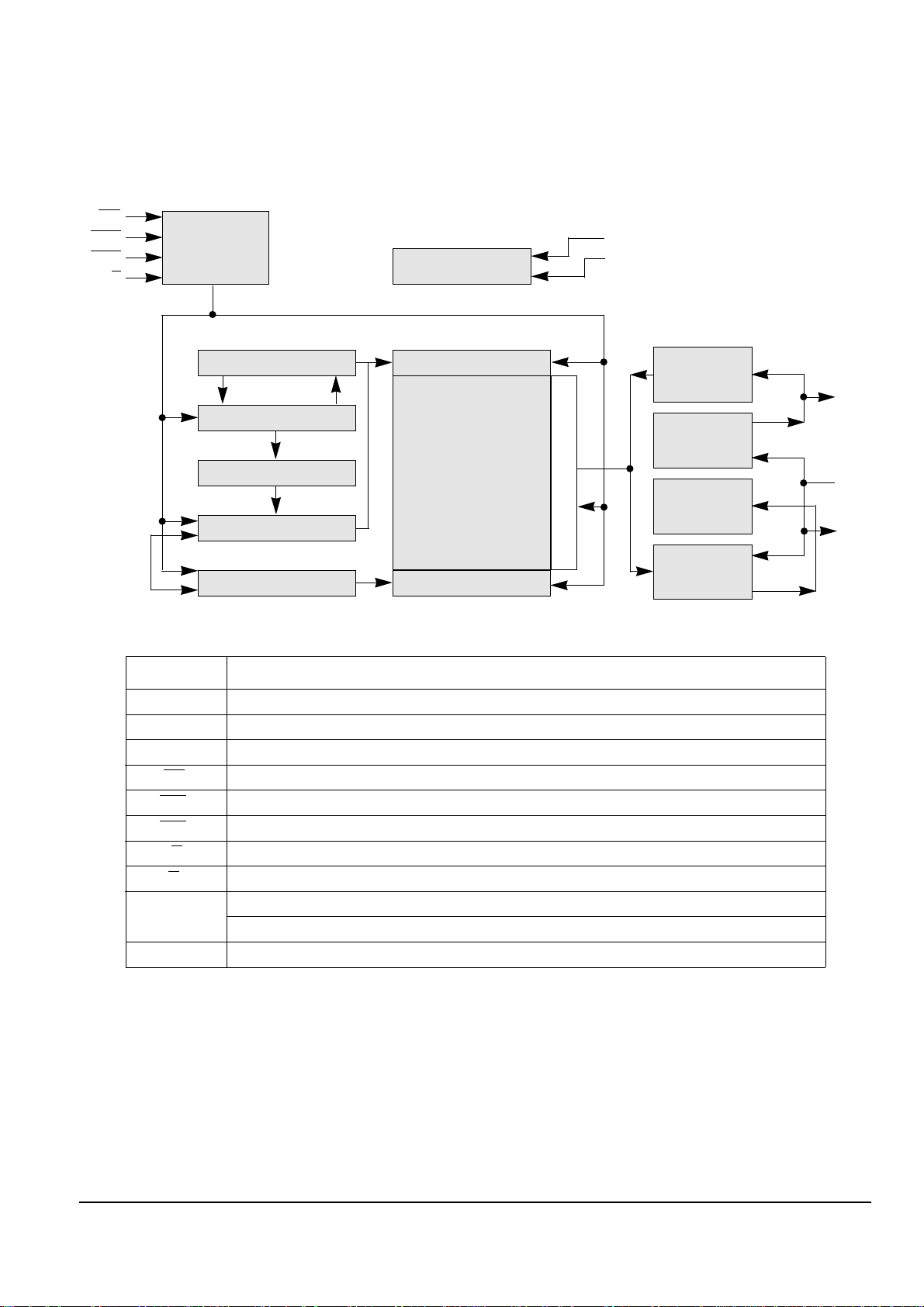

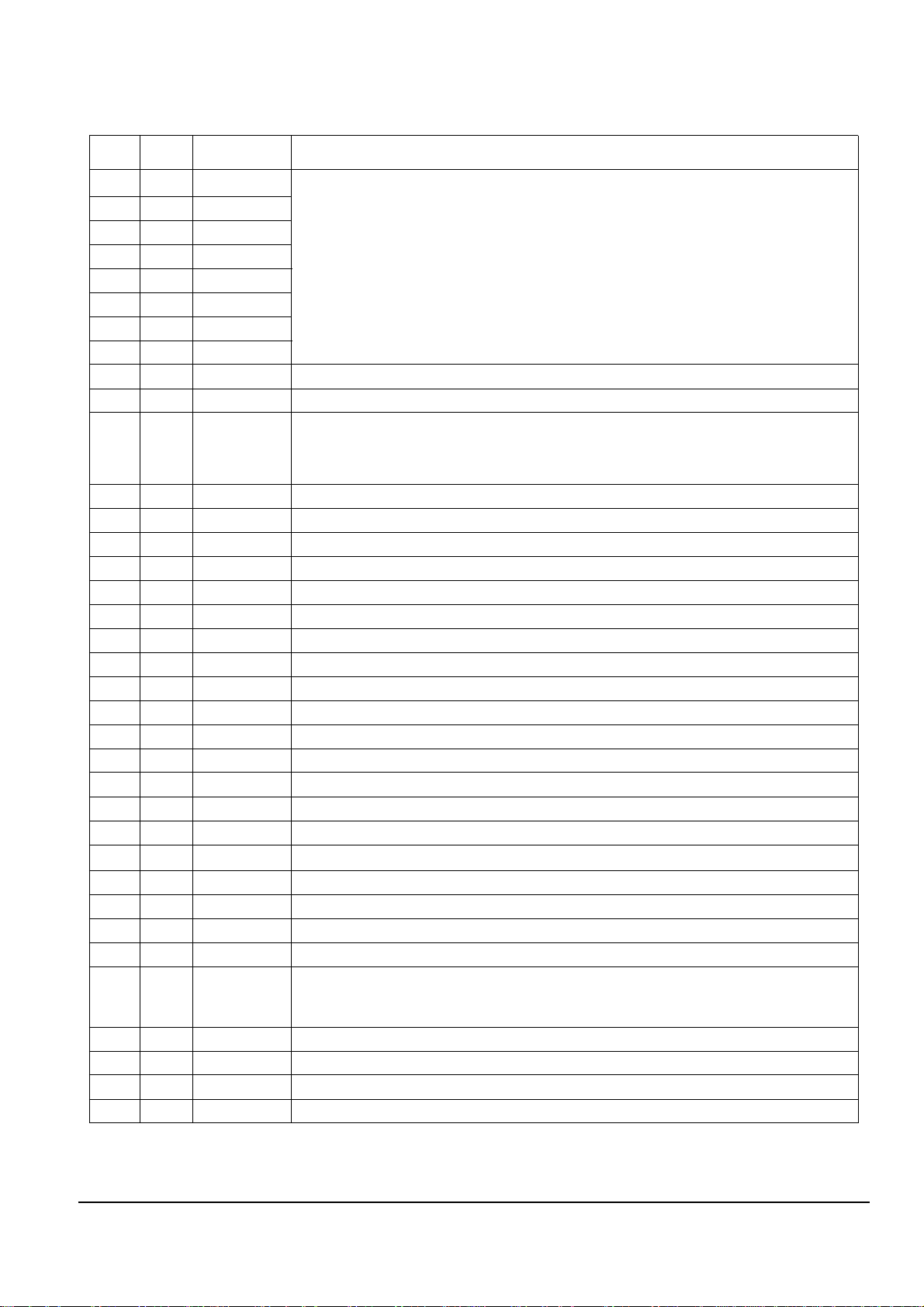

1-1 IC Dsecriptions

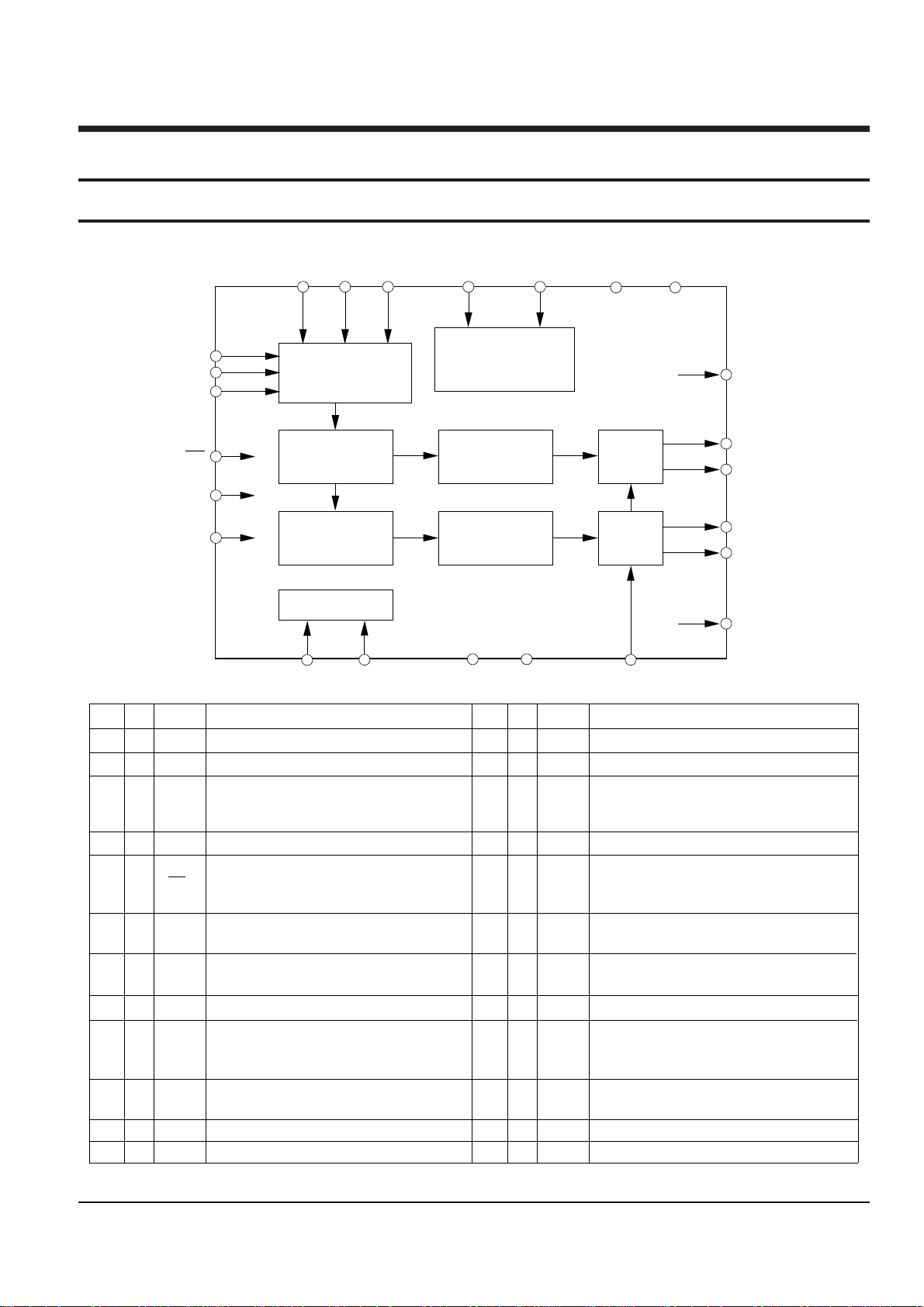

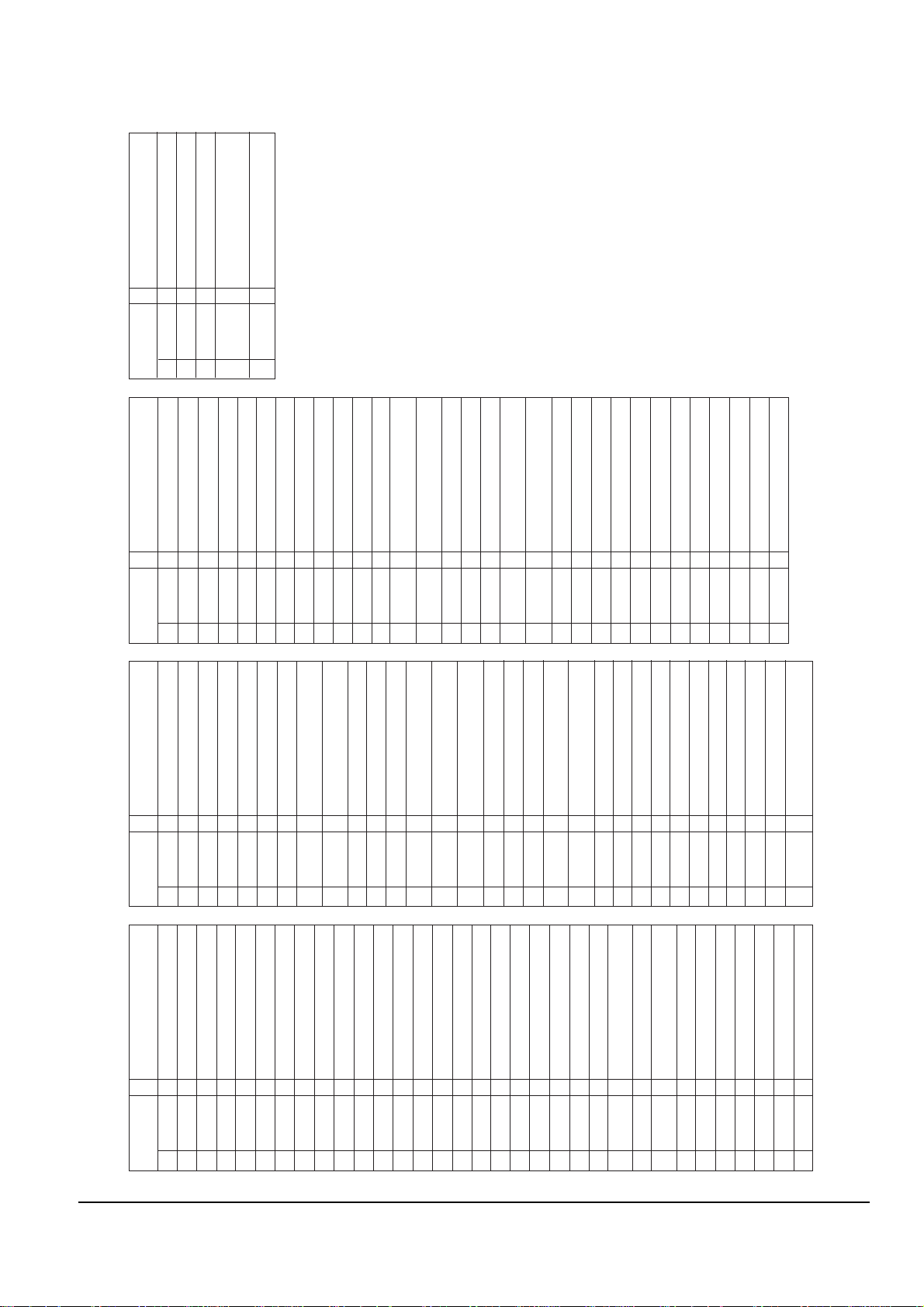

1-1-1 AIC1 (AK4324 ; Digital-to-Analog Converter)

Serial Input

Interface

De-emphasis

Control

8X

Interpolator

8X

Interpolator

∆ ∑

Modulator

SCF

SCF

∆ ∑

Modulator

Clock Divider

DIF0 DIF1 DIF2 DEM0 DEM1 AVDD AVSS

VREFDVSSDVDDCKSMCLK

LRCK

BICK

SDATA

SMUTE

DFS

DZFL

AOUTL+

AOUTL-

AOUTR+

AOUTR-

DZFR

PD

NAME

DVSS

DVDD

CKS

MCLK

BICK

SDATA

PD

I/O

I

I

I

I

I

PIN

1

2

3

4

5

6

I

7

LRCK

I

8

FUNCTION

NAME

I/O

PIN

FUNCTION

Digital ground pin

Digital power supply

Master clock select pin (Internal pull-down pin)

Nomal speed "L":MCLK = 256fs, "H":MCLK = 384fs

Double speed "L":MCLK = 128fs, "H":MCLK = 192fs

Master clock input pin

Power-Down mode pin. When at "L", the AK4324 is in

power-down and is held in rest.

The AK4324 should always be reset upon power-pin

I SMUTE

9

I DFS

10

I DEM0

11

Soft mute pin

When this pin goes "H", soft mute cycle is initiated

When returning "L", the output mute releases.

Audio serial data input pin

64fs clock is recommended to be input on this pin

Audio serial data input pin

2's complement MSB-first data is input on this pin.

Double speed sampling mode pin (Internal pull-down pin)

"L":normal speed, "H":double speed

L/R clock pin.

De-emphasis frequency select pin

I DEM1

12

De-emphasis frequency select pin

Note : Allinput pins except internal pull-down pins should not be left floating.

-

DZFL

O

Lch positive analog output pin

Analog ground pin

Voltage reference input pin

Analog power supply pin.

Rch zero input detect pin

Lch zero input detect pin

I DIF0

13

Digital input format pin

I DIF1

14

Digital input format pin

I DIF2

15

Digital input format pin

0 AOUTR-

16

Rch negative analog output pin

O AOUTR+

17

Rch positive analog output pin

O AOUTL-

AOUTL+

18

O

19

AVSS

-

20

VREF

O

21

AVDD

O

22

DZFR

O

23

24

Lch negative analog output pin

Page 4

Reference Information

1-2 Samsung Electronics

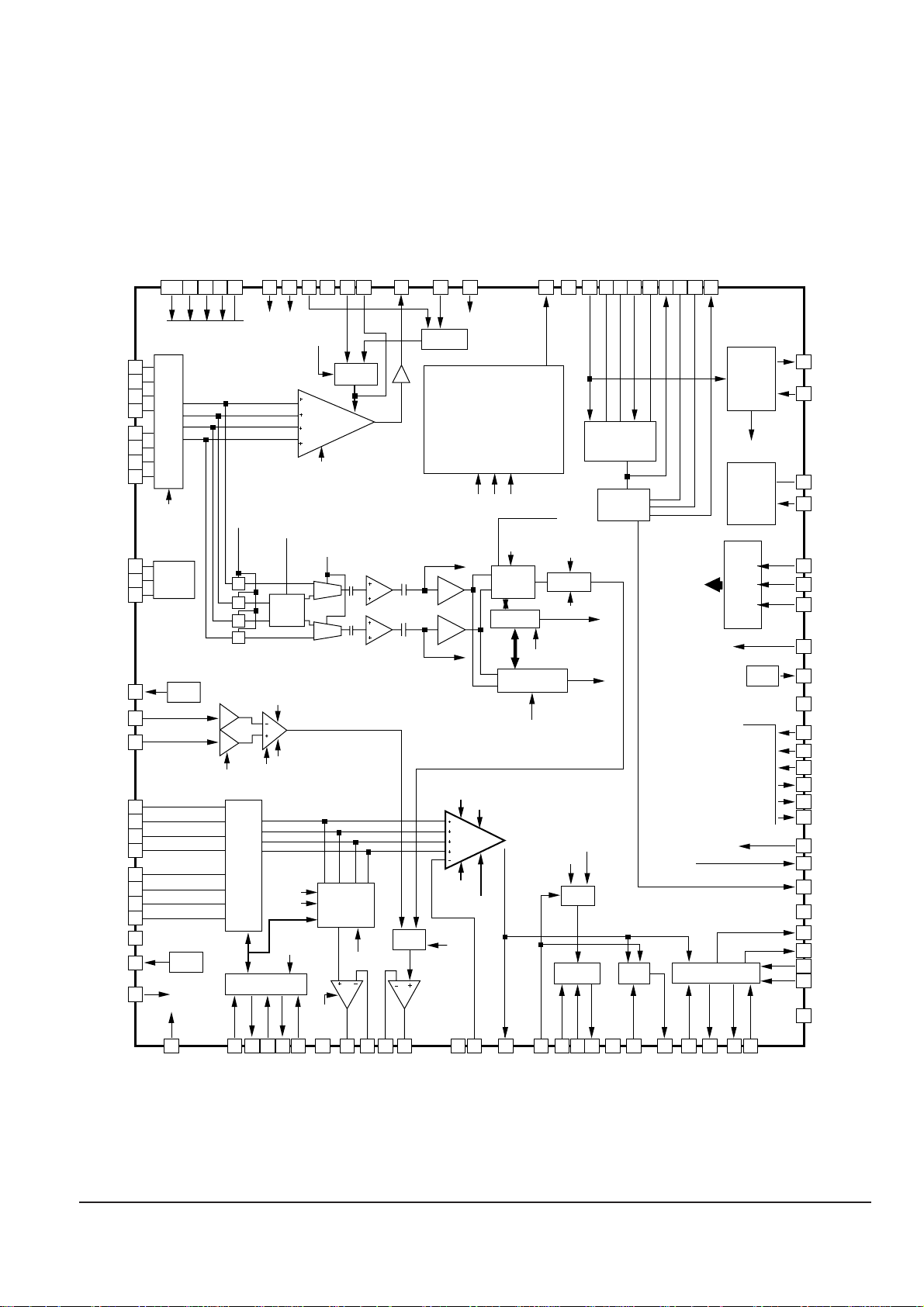

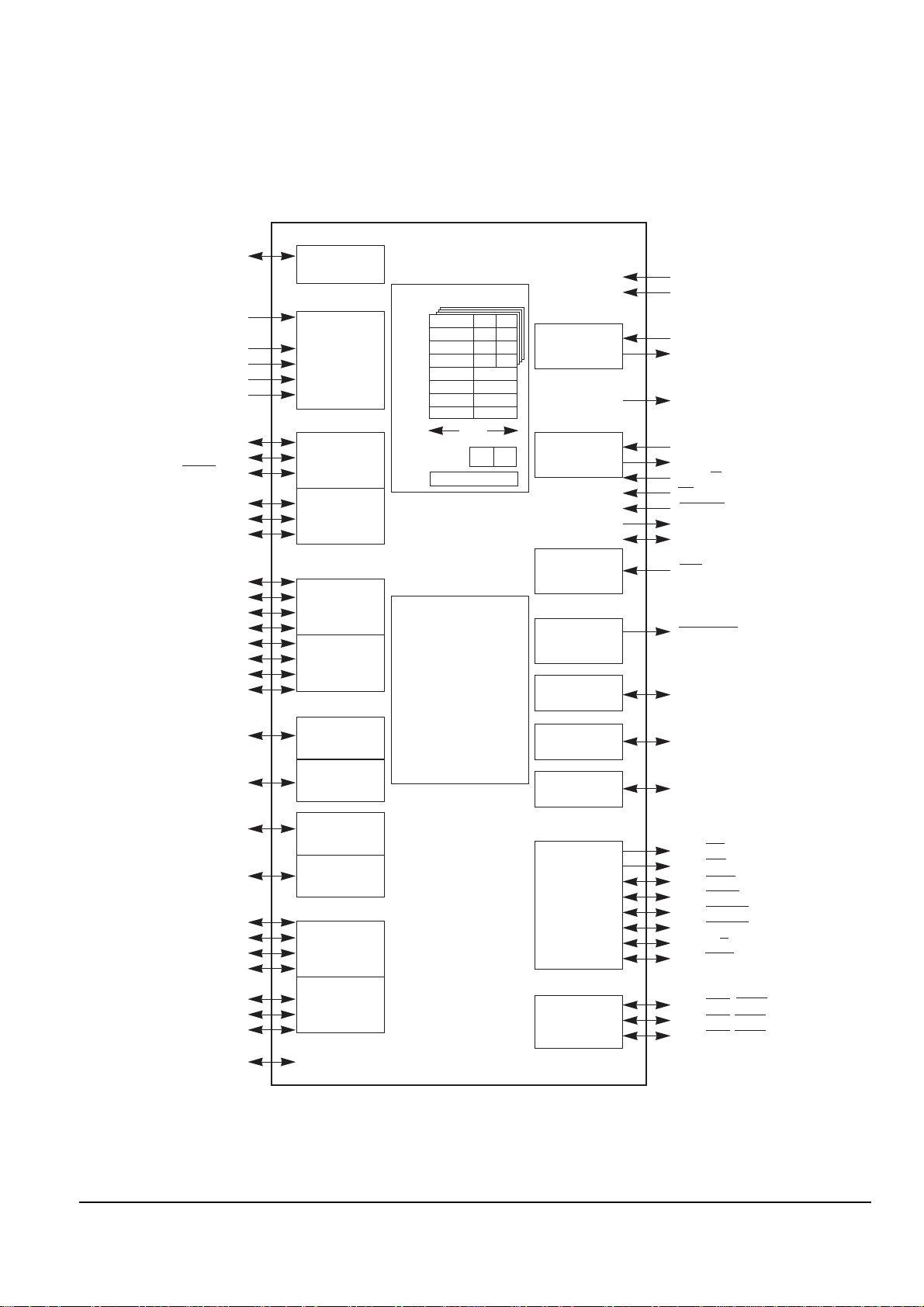

1-1-2 RIC1 (KS1461 ; RF)

100 99 98 97 96 95 94 93 92 91 90

VZOCTL

PLLGF

EQF

EQG

RDPF

AGCP

AGCB

AGCLEVEL

EQGND

AGCI

AGCC

89

RFAGCO

88

EQIN

87

BCATH

86

RFEQO

85

EQVCC

84

MIRRI

83

CP 1

81

MROFST

80

RFRPN

82

CB 1

78

CP 2

77

CB 2

76

RFCT

79

RFRP

75 BCAO

74 BCAI

73 RESET

72 OSC

71 STB

70 CLOCK

69 DATA

68 RREFDLY

67 VREFDPD

66 DPDGND

65 TE1RES

64 PLLCTL

63 DPDMUTE

62 FAUL TOUT

61 DPDEQ2

60 DPDEQ1

59 TE30FST

58 BCA

56 DPDVCC

55 DFCT2

54 DFCT1

53 DFCTTH1

52 DFCTTH2

51 DVCC

50

CC2

49

CC1

48

DFCT_CP2

47

DFCT_CP1

46

FOKB

45

FOKTH

44

DGND

43

ENV42ENVB

41

ENVP

40

ABCDI

39

ABCD

38

ABCDN

37

PDLIMITRES

36TE35

TEN

34

FEN

33

FE

32

AGND

31

PDCD

30

LDOCD

29

PDVD

28

LDODVD

27

VREFLP_BGI

26

OFSTHOLD

25

FOFST

24

VREFA

23

AVCC

22

DCD1

21

CCD1

20

BCD1

19

ACD1

18

DDVD1

17

CDVD1

16

BDVD1

15

ADVD1

14

F

13

E

12

VREFEQ

11

RREF

10

RREFEQ

9

RREFBF

8

DDVD

7

CDVD

6

BDVD

5

ADVD

4

DCD

3

CCD

2

BCD

1

ACD

to RF EQ

TUNING BLOCK

AGC-HOLD(OOH)

MUX

AGC_DET

RF

MUX

VREF

GENERATOR

CDRSEL(00H)

EQ

VC AMP

D

D

D

D

MUX3

GAIN_TE3(02H)

GCA

OFSTHOLD

TEOFST(04H)

TBAL(01H)

TE38

SUB

RF

MUX

D1

B1

C1

A1

FE

GAIN_FE(03H)

FE_0FST(05H)

CDRSEL(00H)

ANALOG

VC AMP

ALPC

LDONB(00H)

FOFST

OFSTHOLD

MUX

TESEL(OOH)

OFSTHOLD

ABCD_OFST(O6H)

ENVELOPE FOK DEFECT

MUX

ENV_SEL(02H)

EQIN

CDRSEL(OOH)

ABCD

SUM

GAIN_ABCD(OOH)

DELAY_SEL(00H)

PLLCTL

FAULTOUT

PDLIMITRES

TEOPST(04H)

PD,LPFDELAY

TE1_LIMIT

DELAY_SEL(OOH)

PLLCTL

TBAL(O1H)

HOLD_CTL(O8H)

DPDMUTE

DPD_MUTE(O2H)

SEOFHOLD

FLT_CTL(OOH)

CAL_ENDB(O2H)

COM

COM

DPDEQ2

DPDEQ1

GCA

GCA

EQ

EQ

CD1

S12

DVD1

DVD2

LDONB

FLT_CTL

CDRSEL

TESEL

AGC-HOLD

TBAL

GAIN_TE3

ENV_SEL

DVCTL_SEL

DPD_MUTE

GAIN_EQ

GAIN_FE

GAIN_ABCD

TE_OFST

FE_OFST

ABCD_OFST

DELAY_CD

DELAY_AB

PDLIMIT

ga_RFSUM

HOLD_CTL

ga_PLLDP

ga_PLLDN

to DPD

BLOCK

DPD

BLOCK

S/IF

BLOCK

AUTO

OFSTCTL

BCA

BLOCK

BCA

RFCT

&

MIRR

RFRP

TE1RES

CD1 S12 DVD1.2

RF

Equalizer

RF SLM

& AGC

A

B

C

D

GAIN_EQ(02H)

MIRR57

Page 5

Reference Information

Samsung Electronics 1-3

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

CD optical main beam A AC coupling input port for RF

CD optical main beam B AC coupling input port for RF

CD optical main beam C AC coupling input port for RF

CD optical main beam D AC coupling input port for RF

DVD optical main beam A AC coupling input port for RF

DVD optical main beam B AC coupling input port for RF

DVD optical main beam C AC coupling input port for RF

DVD optical main beam D AC coupling input port for RF

RF AMP I/O buffer bias resistance connection port

RF EQ bias resistance connection port

Analog block bias resistance connection port

CAP connection port for RF EQ center voltage

CD optical sub beam E input port for SERVO

CD optical sub beam F input port for SERVO

DVD optical main beam A input port for SERVO

DVD optical main beam B input port for SERVO

DVD optical main beam C input port for SERVO

1 ACD

BCD

CCD

DCD

ADVD

BDVD

CDVD

DDVD

RREFBF

RREFEQ

RREF

VREFEQ

E

F

ADVD1

BDVD1

CDVD1

FUNCTIONPIN NAME I/O

I

I

I

I

I

I

I

I

-

-

O

I

I

I

I

I

-

38

37

36

35

34 FE Input port for AMP GAIN setting

Input port for TE AMP GAIN setting

TE AMP output port

Bias resistance port for PDLIMIT

Input port for ABCD AMP GAIN setting

FEN

TEN

TE

PDLIMTRES

ABCDN

FUNCTIONPIN NAME I/O

I

I

O

-

I

28

27

26

25

24

23

22

21

20

19

DVD optical main beam D input port for SERVO

CD optical main beam F input port for SERVO

CD optical main beam F input port for SERVO

CD optical main beam F input port for SERVO

CD optical main beam F input port for SERVO

Power voltage input port for analog part

CAP connection port for analog part

center voltage, Use at other block

CAP connection port for focus auto offset (OPEN)

ON/OFF connection port for auto offset block (L :

auto offset adjustment H : serial offset adjustment)

BANDGAP voltage input port for ALPC

DVD optical laser diode driving voltage output port

18 DDVD1

ACD1

BCD1

CCD1

DCD1

AVCC

VREFA

FOFST

OFSTHOLD

VREFLP_BGI

LDODVD

I

I

I

I

I

-/O

O

IOI

P

32

31

30

29 DVD optical laser monitor diode voltage input port

CD optical laser diode driving voltage output port

CD optical laser monitor diode voltage input port

Power GND port for analog part

PDDVD

LDOCD

PDCD

AGND

I

O

I

P

33 FE AMP output portFE

O

ABCD AC coupling input port for SERVO monitorABCDI I

48

47

46

45

44

43

42

41

40

ABCD AMP output port

Peak hold time constant setting RC

connection port for RF envelope detect

Bottom hold time constant setting RC

connection port for RF envelope detect

RF envelope detect output port

Power GND input port for digital circuit

Focus OK comparing level input port

Focus OK comparator output port

(L: FOCUS OK)

Peak hold time constant connection port SERVO

defect max. time setting

Peak hold time constant connection port PLL defect

min. time setting

39 ABCD

ENVP

ENVB

ENV

DGND

FOKTH

FOKB

DFCT_CP1

DFCT_CP2

O

-

-

O

I

O

-

-

P

62

61

60

59

58

57

56

55

54

53

52

51

50

49 Output port of peak detector for defect

AC coupling input port for defect

Power voltage input port for digital circuit

Resistance connection port for PLL defect comparat-

ing level setting

Resistance connection port for SERVO defect com-

parating level setting

Defect output port for SERVO

Defect output port for PLL

Power voltage input port for DPD TE

Mirror output port

BCA output port

Resistance connection port for 3BTE offset

DPD EQ (A+C) output port

DPD EQ (B+D) output port

DPD defect waveform output port (MONITOR)

CC1

CC2

DVCC

DVCTTH2

DFCTTH1

DFCT1

DFCT2

DPDVCC

MIRR

BCA

TE3OFST

DPDEQ1

DPDEQ2

FAULTOUT

O

P

-

-

I

O

O

P

O

O

-

O

O

O

64

DPD TE MUTE control port (H : MUTE)

DPD TE PLL variable input port

63 DPDMUTE

PLLCTL

I

I

FUNCTIONPIN NAME I/O FUNCTIONPIN NAME I/O

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65 DPD TE PLL variable bias resistance

Power GND input port for DPD TE

CAP connection port for DPD TE center

Bias resistance connection port for delta block

Data input port

Clock input port

Data enable input port

OSC time constant input port for auto offset block

Reset input port for auto offset block (L : RESET)

BCA FILTER1

BCA FILTER2

RF ripple center voltage output port for mirror

Bottom hold time constant RC connection port for

RFCT generation

Peak hold time constant RC connection port for

RFCT generation

RF ripple AMP output port for mirror

RF ripple AMP GAIN input port for mirror

RF ripple offset control port for mirror

Bottom hold time constant RC connection port for

RFCT generation

Peak hold time constant RC connection port for

RFCT generation

Input port for MIRR signal generation

Power voltage input port for RF EQ

RF EQ output port

BCA comparating level control port

TE1RES

DPDGND

VREFDPD

RREFDLY

DATA

CLOCK

STB

OSC

RESET

BCAI

BCAO

RFCT

CB2

CP2

RFRP

RFRPN

MROFST

CB1

CP1

MIRRI

EQVCC

RFEQO

BCATH

I

P

O

-

I

I

I

I

I

O

O

-

-

O

I

I

-

-

I

P

O

I

91

90

89

RFAGCO input port for RF EQ

RF AGC AMP output port

AGC time constant CAP connection port

When AGC is “HOLD”, AGC voltage input port

88 EQIN

RFAGCO

AGCC

AGCI

I

O

-

I

95

94

93

92 Power GND input port for RF EQ

AGC level control voltage input port

RF bottom hold time constant RC connection port for RF AGC

RF peak hold time constant RC connection port for RF AGC

EQGND

AGCLEVEL

AGCB

AGCP

P

I

-

-

100

99

98

97

96

Bias resistance connection port for RF EQ frequency setting

RF EQ boost gain control voltage input port

RF EQ peak frequency control voltage input port

RF EQ boost, peak frequency gain control port corre-

sponding to wideband PLL (PLLG. PLLF resistance

internal design)

RF EQ control port (When No. PLLG isn’t adjusted,

apply DC CTL voltage.)

RDPF

EQG

EQF

PLLGF

VZOCTL

-

I

I

I

I

Page 6

Reference Information

1-4 Samsung Electronics

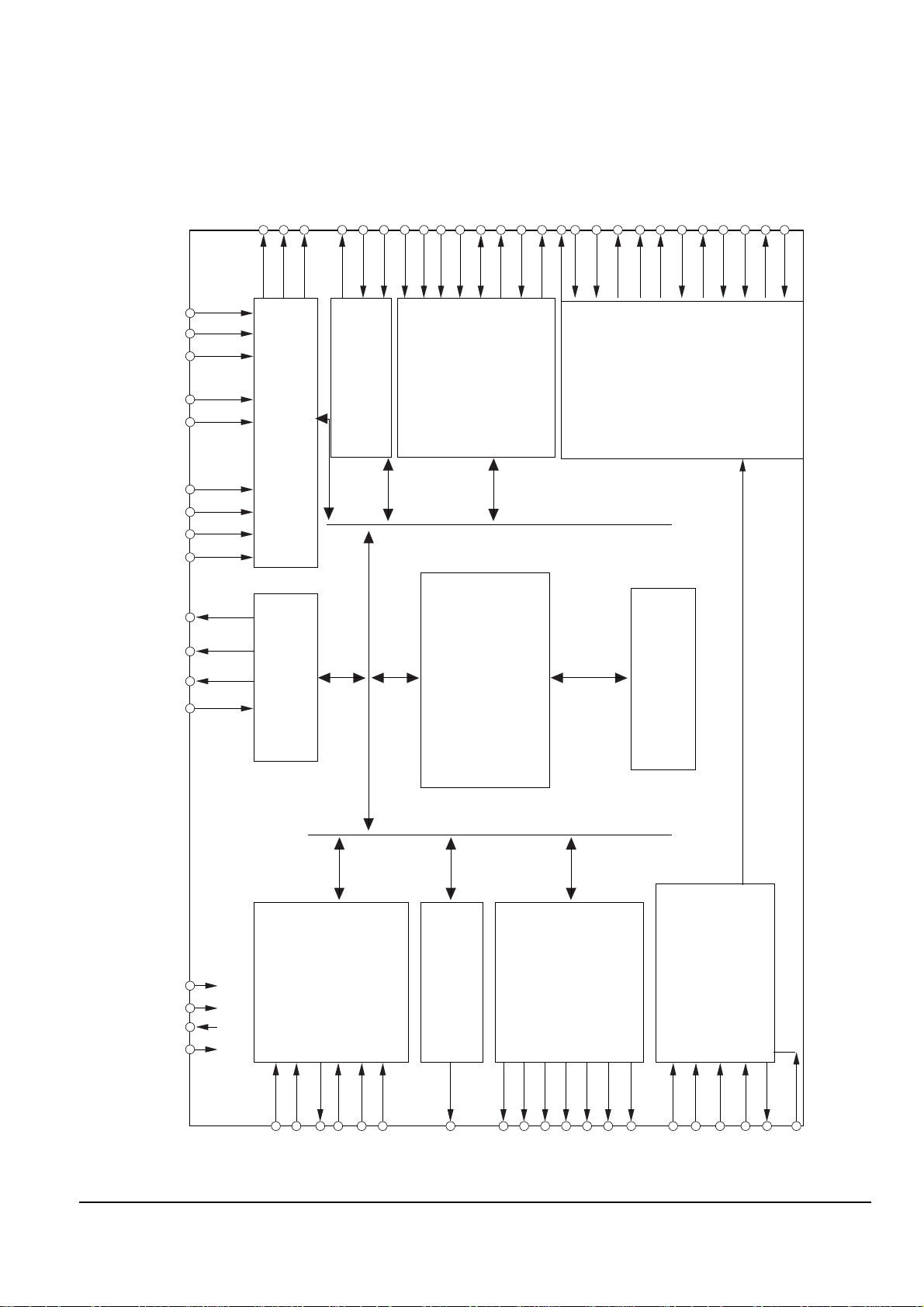

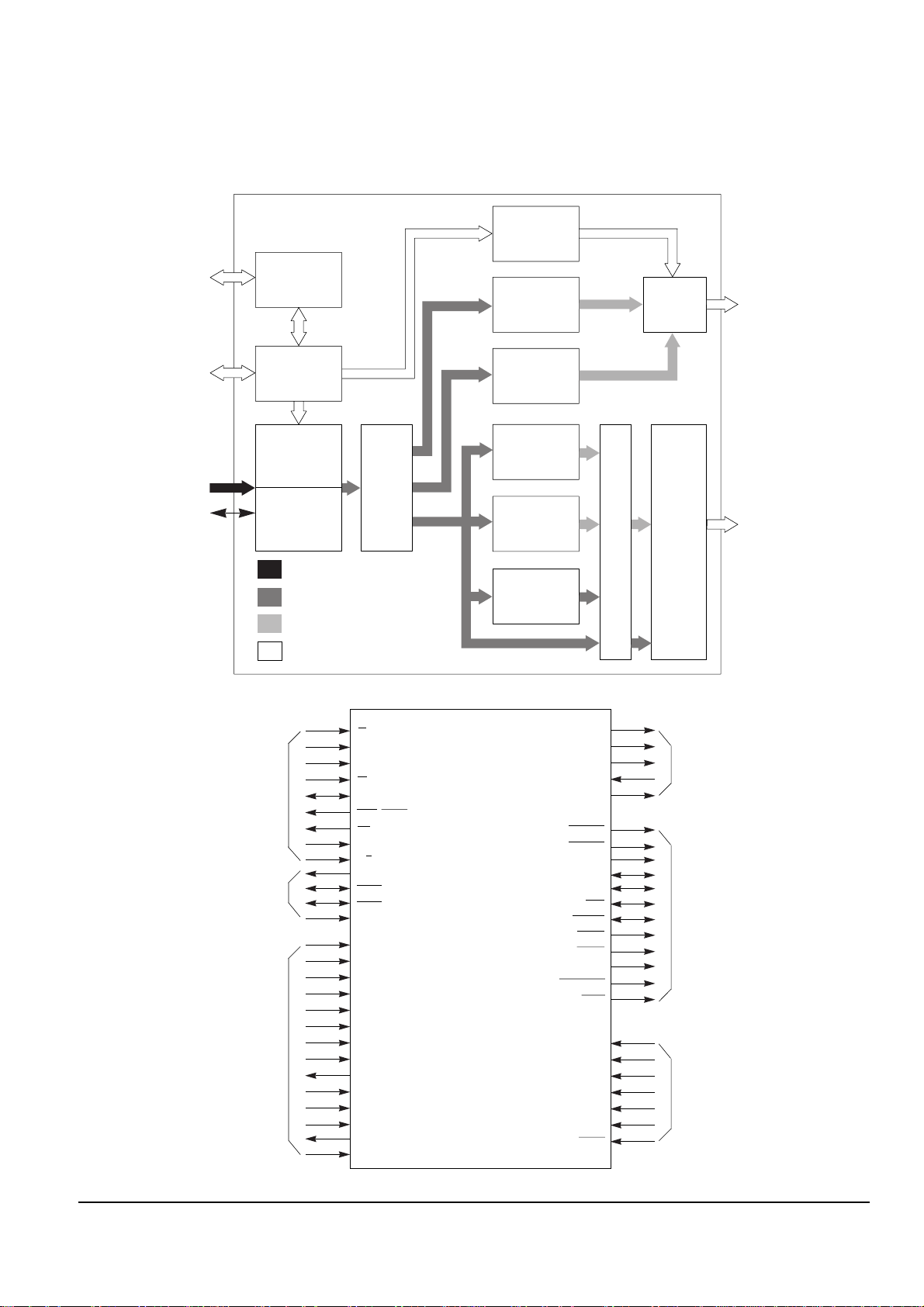

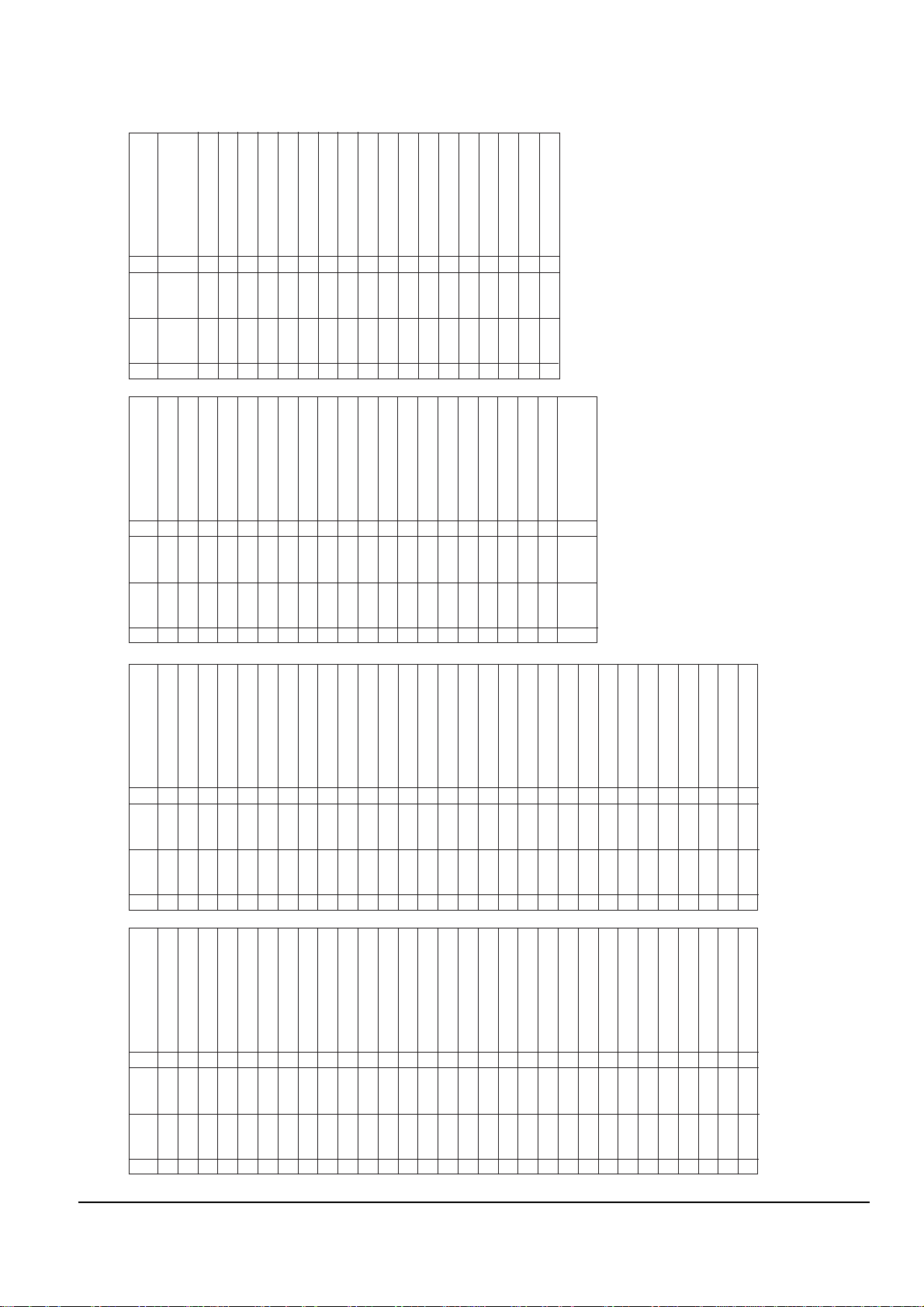

1-1-3 SIC1 (KS1452 ; Digital Servo)

A/D

CONVERTER

BLOCK

D/A

CONVERTER

BLOCK

TRACK

COUNTER

EFM

ASYMETRY

VREF

ENV

TZCO

SME

TE

FE

COUT

FOD

TRD

SLD

SPD

FBAL

TBAL

DVCTL

EFMI

RFI

ASYDVD

ASYCD

EFM

EFMOA

PLLHD

INTO_224

FDCTL

MAGICO

EQCTL

VCTRL

RVCO

PLCK

EFMRTD

RPD

RFD

PLLLOCK

MDOUT[3:0]

PSB

SENSE

MDATA[7:0]

MRDB

MWRB

CSB

DAB

SCOR

SQSI

SQCK

LDONB

TLKB

FLKB

DIRC

PS1

SSTOP

/PSO

SMON

LOCK

DFCT

FOKB

MIRR

TZCA

PHI1

XOUT

XO

XI

TEST

RSTB

TILTO

TILTI

ROM

DSP CORE

FOR

DIGITAL SERVO

TIMING

GENERATOR

I/O INTERFACE

BLOCK

SUB CODE

READ BLOCK

SYSCON

INTERFACE

BLOCK

WIDE

CAPTURE

RANGE PLL

Page 7

Reference Information

Samsung Electronics 1-5

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

Mode data3 out controlled by micom

Limit switch/sled position sensor input pin0

Sled motor position sensor input pin 1

Test pin (L : normal H : test)

Counter clock

Focus servo lock signal output pin

Tracking servo lock signal output pin

0 : 1BIT 1 : 8BIT

System reset signal input pin

Micom chip select pin

Micom data/address select pin

Micom write clock signal input pin

Micom read clock signal input pin

Micom data pin 0

Micom data pin 1

Micom data pin 2

Micom data pin 3

Micom data pin 4

Micom data pin 5

Micom data pin 6

Micom data pin 7

Internal status monitor pin

Servo logic & ROM VDD power supply pin

System clock signal input pin

System clock signal output pin

Clock out (33.9688MHz) to DSP

Servo logic & ROM VSS power supply pin

Clock output pin for subcode data read

Subcode data input pin

Timing detection input pin for subcode data read

Motor ON signal input pin

Lock signal input pin

Direct jump control (for 1 track jump)

1 MDOUT3

SSTOP/PSO

PS1

TEST

COUT

FLKB

TLKB

PSB

RSTB

CSB

DAB

MWRB

MRDB

MDATA0

MDATA1

MDATA2

MDATA3

MDATA4

MDATA5

MDATA6

MDATA7

SENSE

DVDD

XI

XO

XOUT

DVSS

SQCK

SQSI

SCOR

SMON

LOCK

DIRC

FUNCTIONPIN NAME I/O

O

I

I

I

O

O

O

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

P

I

O

O

P

O

I

I

I

I

I

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

Focus OK signal input pin

PLL frequency detect control input pin

Laser diode ON signal output pin

Defect Detection signal input pin

Mirror signal input pin

PLL hold signal from micom

Servo interrupt monitor pin

PLL logic block VDD power supply pin

PLCK

Frequency lock detect output

(H : Lock L : Unlock)

Latched EFM output signal

PLL logic block VSS power supply pin

Resistor pin for VCO GAIN

Gain adjust resister for frequence detector

Gain adjust resister for phase detector

Control voltage for VCO

Input for hysteresis control of FD output (for test)

EFM offset adjustment pin

Tracking zero cross output pin

Servo CPU VDD power supply pin

EQ control signal

EFM signal for test

EFM signal

Asymmetric input signal for DVD

Asymmetric input signal for CD

RF input signal

Servo CPU VSS power supply pin

Analog block VSS power supply pin

Spindle error input pin

Reference voltage input pin

Tracking error signal input pin

34 FOKB

FDCTL

LDONB

DFCT

MIRR

PLLHD

INTO_224

PVDD

PLCK

PLLLOCK

EFMRTD

PVSS

RVCO

RFD

RPD

VCTL

MAGICO

EFMOA

TZCO

SVDD

EQCTL

EFMI

EFMO

LPFDVD

LPFCD

RFI

SVSS

AVSS

SME

VREF

TE

FUNCTIONPIN NAME I/O

I

I

O

I

I

I

O

P

O

O

O

P

I

I

I

I

I

I

O

P

O

I

O

I

I

I

P

P

I

I

I

72

71

70

69

68

67

66

Focus error signal input pin

RF envelope input pin

Tilt in (reserved)

Analog block VDD power supply pin

Tilt out (reserved)

Depth variation control signal output pin

Tracking balance signal output pin

Focus balance signal output pin

65 FE

ENV

TILTI

AVDD

TILTO

DVCTL

TBAL

FBAL

FUNCTIONPIN NAME I/O

I

I

I

P

O

O

O

O

80

79

78

77

76

75

74

73 Sled motor drive signal output pin

Spindle motor drive signal output pin

Focus actuator drive signal output pin

Tracking actuator drive signal output pin

TE signal for tracking zero cross input pin

Mode data 0 out controlled by micom

Mode data 1 out controlled by micom

Mode data 2 out controlled by micom

SLD

SPD

FOD

TRD

TZCA

MDOUT0

MDOUT1

MDOUT2

FUNCTIONPIN NAME I/O

O

O

O

O

I

O

O

O

Page 8

Reference Information

1-6 Samsung Electronics

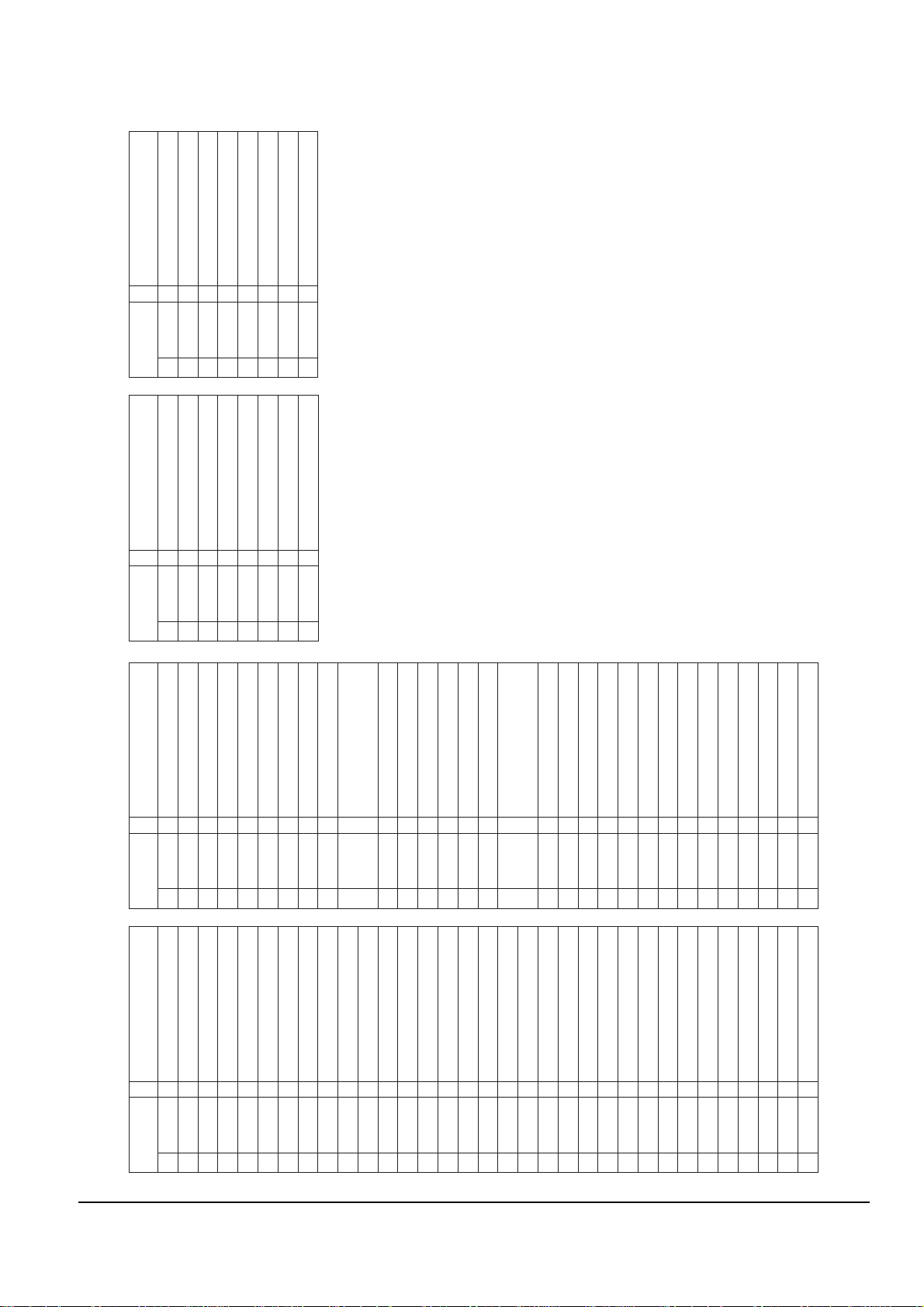

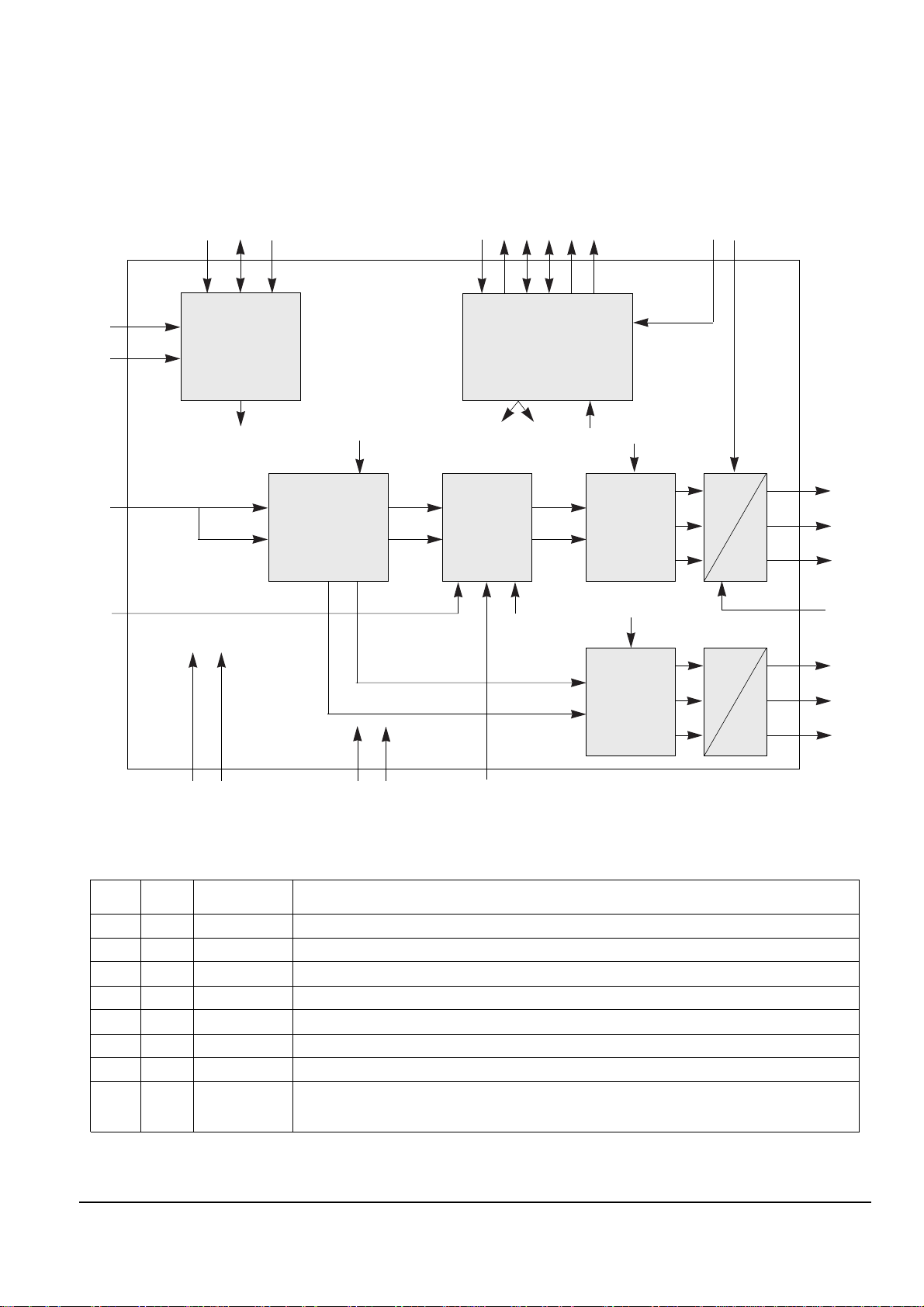

1-1-4 DIC1 (KS1453 ; DVD Data Processor)

X'TAL &

TIMING GEN

RFCK 17.58/7.35KHz

DVD CLV/CAV

CD CLV/CAV

M

23BIT SR

26.16MHz

32BIT SR 16-8 DEMOD

ECSY

FRAME SYNC

DET/PROT/INS

(17.57KHz)

(6, 4, 3)

efmwr ID ECC

WFCK 17.58/7.35KHz

M

VCO TIMING

GENERATOR

17.58KHz = 26.16M/1488

676.08Hz

(208, 192, 17)

(182, 172, 11)

ECC

VCO TIMING

GENERATOR

7.35KHz = 4.3218M/588

75Hz

(32, 28, 5)

(28, 24, 5)

CIRC

FRAME SYNC

DET/PROT/INS

(7.35KHz)

EFM DEMOD

SUBCODE I/F

CD-G

V-CD, CD-DA

SQ-VCD

DVDP,

DEINTERLEAVE

&

RAM CONTROL

(6, 4, 3)

trans ID ECC

EDC

DESCRAMBLER

MICOM I/F

MM

TO MICOM (15)

MDAT(7:0), MRZA, ZCS, MWR,

MRD, ZIRQZD, ZWAIT, ZRST

TO DRAM

256K*16

(32)

DD(15:0)

DADR(8:0)

ZRAS

ZUCAS

ZLCAS

ZOE(1:0)

ZWE(1:0)

TO AV (13)

SDATA[0] / CDATA

SDATA[1] / LRCK

SDATA[2] / BCLK

SDATA[3] / C2PO

SDATA[4] / SQDT

SDATA[5] / WFSY

SDATA[6] / SOS1

SDATA[7] / SQCK

DATREQ

CSTROBE

DTER

DATACK

TOS

TO (12)

XTI1

XTO1

CK33MI

CK33MO

FG

MON

MDP

MDS

FSW

PLL_LOCK

CLV_LOCK

SERVO_LOCK

FROM R/F,

PLL(3)

EFMI

PLCK

BCARZ

TO D-EQ (8)

PWMO(7:0)

Monitor(8) GFS, FRSYZ, TX, EFMO, WFCK, RFCK, CK 16M, DEMPHA Power(34)=VDD(11)+GND(23) Test Pin(3) TEST0, TEST1, TEST2

Page 9

Reference Information

Samsung Electronics 1-7

DRAM data bus32 DD9_BI

Digital GND (0V)31 DVSS

DRAM data bus30 DD5_BI

DRAM data bus29 DD10_BI

DRAM data bus28 DD4_BI

DRAM data bus27 DD11_BI

Digital power (+5V)26 DVDD

DRAM data bus25 DD3_BI

DRAM data bus24 DD12_BI

DRAM data bus23 DD2_BI

DRAM data bus22 DD13_BI

Digital GND (0V)21 DVSS

DRAM data bus20 DD1_BI

DRAM data bus19 DD14_BI

DRAM data bus18 DD0_BI

DRAM data bus17 DD15_BI

Digital GND (0V)16 DVSS

System clock output for 26.16 MHz15 XTO_OUT

System clock input for 26.16 MHz14 XTI_IN

Digital power (+5V)13 DVDD

Micom data bus12 MDAT0_BI

Micom data bus11 MDAT1_BI

Micom data bus10 MDAT2_BI

Micom data bus9 MDAT3_BI

Micom data bus8 MDAT4_BI

Micom data bus7 MDAT5_BI

Micom data bus6 MDAT6_BI

Micom data bus5 MDAT7_BI

Digital GND (0V)4 DVSS

Micom register select

(L -> Register H -> Data)

3

MRZA_IN

Chip select (Active Low)2 ZCS_IN

Digital GND (0V)1 DVSS

FUNCTIONPIN NAME

DVD data/Sub code frame sink (WFSY)65 SDATA5_OUT

DVD data/Sub code serial data (SQDT)64 SDATA4_OUT

DVD data/CD data error flag (C2P0)63 SDATA3_OUT

DVD data/CD data bit clock (BLCK)62 SDATA2_OUT

DVD data/CD data L/R clock (LRCK)61 SDATA1_OUT

DVD data/CD data bitstream output60 SDATA0_OUT

Digital power (+5V)59 DVDD

Data acknowledge signal output58 DATACK_OUT

Top of sector57 TOS_OUT

Digital GND (0V)56 DVSS

Digital GND (0V)55 DVSS

DRAM address bus54 DADR3_OUT

DRAM address bus53 DADR4_OUT

DRAM address bus52 DADR2_OUT

DRAM address bus51 DADR5_OUT

DRAM address bus50 DADR1_OUT

DRAM address bus49 DADR6_OUT

DRAM address bus48 DADR0_OUT

Digital GND (0V)47 DVSS

DRAM address bus46 DADR7_OUT

DRAM address bus45 DADR8_OUT

DRAM row address strobe44 ZRAS_OUT

DRAM output enable 043 ZOEO_OUT

Digital power (+5V)42 DVDD

DRAM output enable 1 (16M, --------, 16M)41 ZOE1_OUT

DRAM write enable 0 (4M, 8M, 16M)40 ZWE0_OUT

DRAM write enable 1 (8M ONLY)39 ZWE1_OUT

DRAM upper column address strobe38 ZUCAS_OUT

DRAM row column address strobe37 ZLCAS_OUT

Digital GND (0V)36 DVSS

DRAM data bus35 DD7_BI

DRAM data bus34 DD8_BI

DRAM data bus33 DD6_BI

FUNCTIONPIN NAME

Digital GND (+5V)97 DVSS

System clock output for 33.8688MHz96 CK33MO_OUT

System clock input for 33.8688MHz95 CK33MI_IN

Digital out92 TX_OUT

Good frame sync detection result output (“H”

active)

93 GFS_OUT

Frame sync out91 FRSYZ_OUT

Digital GND (0V)90 DVSS

Digital GND (0V)89 DVSS

Digital GND (0V)88 DVSS

Digital GND (0V)87 DVSS

Digital power (+5V)86 DVDD

Digital power (+5V)85 DVDD

Digital GND (0V)84 DVSS

Digital GND (0V)83 DVSS

Digital GND (0V)82 DVSS

PWM output signal81 PWM00_OUT

PWM output signal80 PWM01_OUT

PWM output signal79 PWM02_OUT

PWM output signal78 PWM03_OUT

Digital power (+5V)77 DVDD

PWM output signal76 PWM04_OUT

PWM output signal75 PWM05_OUT

PWM output signal74 PWM06_OUT

PWM output signal73 PWM07_OUT

Digital GND (0V)72 DVSS

DVD data error output71 DTER_OUT

Data request from A/V decoder or ROM decoder70 DATREQ_IN

Data strobe (clock) output69

CSTROBE_OUT

Digital GND (0V)68 DVSS

DVD data/Sub code serial clock (SQCK)67 SDATA7_BI

DVD data/Sub code block sink (S0S1)66 SDATA6_OUT

FUNCTIONPIN NAME

Micom write strobe (schmidt trigger)128 MWR_IN

Micom read strobe (schmidt trigger)127 MRD_IN

Interrupt request from micom126 ZIRQZD_OUT

Micom read/write access wait (“L” wait)125 ZWAIT_OUT

Hardware reset active low124 ZRST_IN

Digital GND (0V)123 DVSS

BCA input signal122 BCARZ_IN

When DEEMPHASIS is ON, “HIGH”.121 DEMPHA_OUT

2∫–¡÷ clock of CK33M/16.934MHz120 CK16M_OUT

Digital power (+5V)119 DVDD

Digital power (+5V)118 DVDD

Spindle motor output filter conversion output (3-

state)

115

FSW_OUT

Digital power (+5V)117 DVDD

EFM/EFM+ signal input116 EFMI_IN

Reference signal for CAV114 FG_IN

Spindle motor ON/OFF control output113 MON_OUT

Spindle motor speed control signal

(3-state)

110 MDS_OUT

Spindle motor phase control signal

(3-state)

109 MDP_OUT

Digital GND (0V)112 DVSS

Digital GND (0V)111 DVSS

Lock signal for SERVO108 SERLOCK_OUT

Lock signal for CLV107 CLVLOCK_OUT

Lock signal for PLL106 PLLLOCK_OUT

Digital GND (0V)105 DVSS

Phase locked clock104 PLCK_IN

Reference frame pulse103 RFCK_OUT

Write frame pulse102 WFCK_OUT

EFM out101 EFMO_OUT

Test mode setting port100 TEST2_IN

Test mode setting port99 TEST1_IN

Test mode setting port98 TEST0_IN

FUNCTIONPIN NAME

Digital GND (0V)94 DVSS

Page 10

Reference Information

1-8 Samsung Electronics

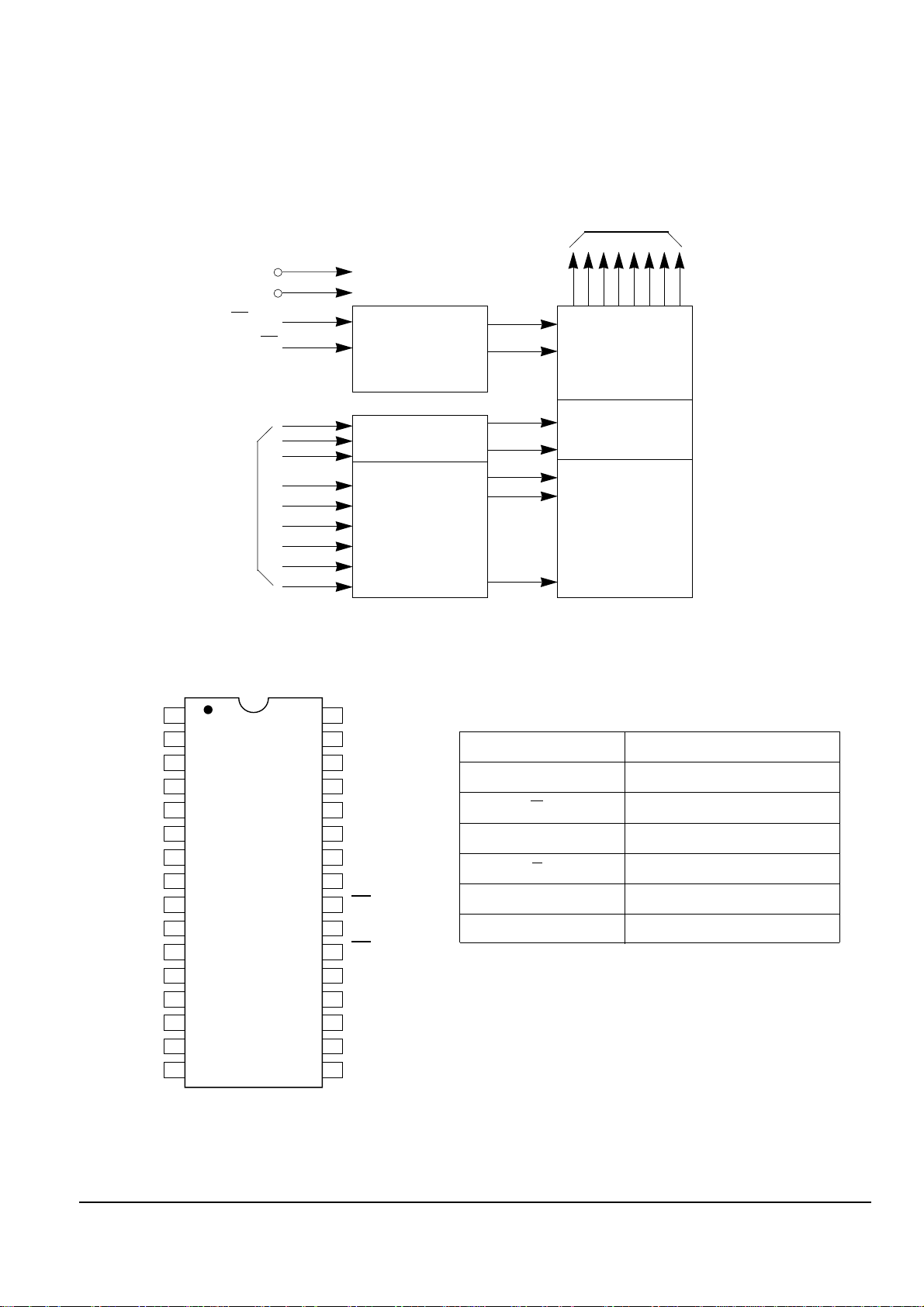

1-1-5 DIC2 (KM416C254BJ-6 ; CMOS DRAM)

NAME

A0-A8

DQ0-15

VSS

RAS

UCAS

LCAS

W

OE

V

CC

N.C

BLOCK DIAGRAM

Control

Clocks

VBB Generator

Lower

Data in

Buffer

DQ0

to

DQ7

OE

DQ8

to

DQ15

Lower

Data out

Buffer

Upper

Data in

Buffer

Upper

Data out

Buffer

Vcc

Vss

RAS

UCAS

LCAS

W

FUNCTION

Address Inputs

Data in/Out

Ground

Row Address Strobe

Upper Column Address Strobe

Lower Column Address Strobe

Read/Write Input

Data Output Enable

Power (+5V)

Power (+3.3V)

No Connection

Refresh Timer

Refresh Control

AO

.

.

A8

Refresh Counter

Row Address Buffer

Col. Address Buffer

Row Decoder

Column Decoder

Memory Array

262,144 x 16

Cells

Page 11

Reference Information

Samsung Electronics 1-9

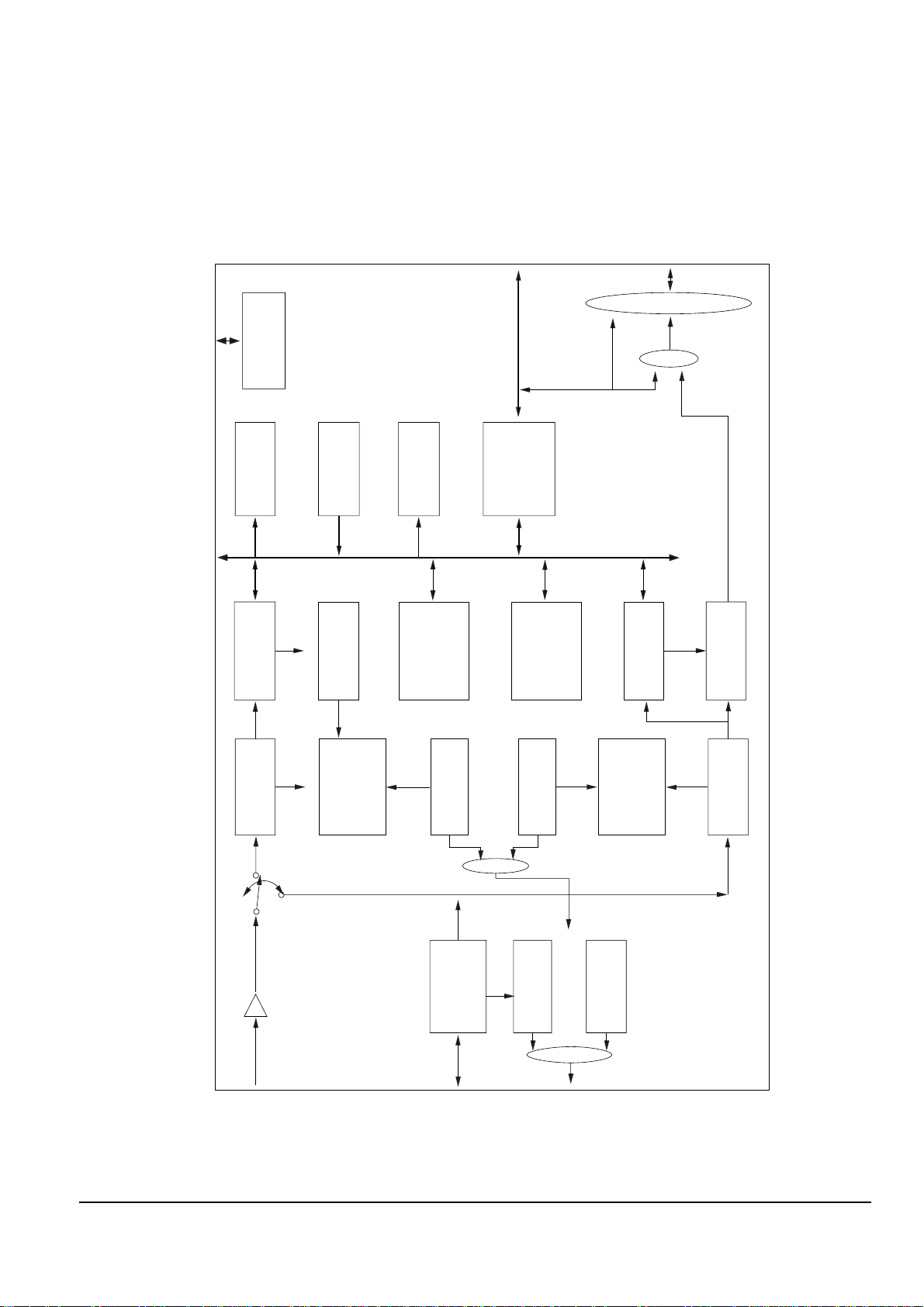

1-1-6 VIC1 (ZiVA-3 ; Audio/Video Decoder)

Memory

Controller

OSD

Decoder

Video

Interface

Audio

Interface

Subpicture

Decoder

MPEG

Video

Decoder

CD-DA and

LPCM

Decoder

Dolby Digital

Audio

Decoder

MPEG

Audio

Decoder

Host

Interface

Control Logic

Secure View

CSS

Descrambling

Bus Key

Authentication

(Optional)

SDRAM/

EDO/ROM

Interface

Host

Interface

DVD/CD

Interface

BLOCK DIAGRAM

Video

Mixer

ZiVA-3 Decoder

Stream

Program

Decoder

Audio

DSP

Audio

Interface

Digital

Scrambled, Compressed Content

Descrambled, Compressed Content

Decompressed Content

Display Content

LOGIC DIAGRAM

HADDR[2:0]

RD

HDATA[7:0]

WAIT/DTACK

INT

HOST8SEL

Host

Interface

Signals

Video

Interface

Signals

DVD/CD

Interface

Signals

Audio

Interface

Signals

SDRAM/EDO

Interface

Signals

Global

Interface

Signals

DA-DATA[0:3]

DA-LRCK

DA-BCK

DA-XCK

DA-IEC

EDO-CAS

EDO-RAS

LDQM

MDATA[15:0]

MADDR[20:0]

MWE

ROM-CS

SD-CLK

SD-CAS[1:0]

UDQM

SYSCLK

VDD

VSS

A_VSS

A_VDD

P10[10:0]

RESET

VDATA[7:0]

VCLK

DVD-DATA0/CD-DATA

DVD-DATA1/CD-LRCK

DVD-DATA2/CD-BCK

DVD-DATA3/CD-C2PO

DVD-DATA4/CDG-SDATA

DVD-DATA5/CDG-VFSY

DVD-DATA6/CDG-SOS1

DVD-DATA7/CDG-SCLK

VREQUEST

VSTROBE

ERROR

V-DACK/ASTROBE

AREQUEST

A-DACK

DTACKSEL

CS

R/W

VSYNC

HSYNC

SD-CAS

SD-RAS

ZiVA Decoder

Page 12

Reference Information

1-10 Samsung Electronics

1-1-7 VIC50 (SAA7128 ; Digital Video Encoder)

I2C-

INTERFACE

SYNC/

CLOCK

MP

MP

9..16

44

20

21

I

2

C-Control

I

2

C-Control

I

2

C-Control

I

2

C-Control

I

2

C-Control

Clock&Timing

RESN

40

42

41

35

34

7

8

43

37

4

25,28,31,36

SDA

SCL

XTALI

XTAL

RCV1

RCV2

TTXRQ

XCLK

LLC1

VDDA

VDD I2C

SA

MP(7:0)

TTX

FADER

ENCODER

OUTPUT-

INTERFACE

D

A

RGB-

PROCESSOR

D

22,32,33

23

26

29

30

27

Y

C

Y

5,18,38

6,17,39

2

3

VSS

VDD

SP

AP

19

RTC1

CbCr

Y

CbCr

24

R(Cr)

VSSA

G(Y)

B(Cb)

CVBS

(CSYNC)

VBS

(CVBS)

C

(CVBS)

A

BLOCK DIAGRAM

NAME

res.

SP

AP

LLC1

V

SS1

VDD1

RCV1

RCV2

I/O

I

I

I

I

I

I/O

I/O

PIN

1

2

3

4

5

6

7

8

FUNCTION

Reserved pin, do not connect

Test Pin;connected to digital ground for normal operation

Test Pin;connected to digital ground for normal operation

Line-Locked Clock input;this is the 27 MHz master clock

Digital supply ground 1

Digital supply 1

Raster Contral 1 for video port. This pin receives/provides a VS/FS/FSEQ signal.

Raster Contral 2 for video port. This pin provides an HS pulse of programmable length or receives

an HS pulse.

Page 13

Reference Information

Samsung Electronics 1-11

NAME

MP7

MP6

MP5

MP4

MP3

MP2

MP1

MP0

V

DD2

VSS2

RTCI

VDD

12C

SA

V

SSA1

R(Cr)

C

V

DDA1

G(Y)

VBS

V

DDA2

B(Cb)

CVBS

V

DDA3

VSSA2

VSSA3

XTAL

XTAL1

I/O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

I

O

O

I

O

O

I

I

I

O

I

PIN

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

FUNCTION

Digital supply voltage 2

Digital ground 2

Real Time Control input. If the LLC1 clock is provided by an SAA7111 or SAA7151B, RTCI should be

connected to the RTCO pin of the respective decoder to improve the signal quality.

Sense input for 12C bus voltage;connect to 12C bus supply

Select 12C address; low selects slave address 88h, high selects slave address 8Ch.

Analog ground 1 for Red (Cr), C(CVBS), Green(Y) outputs

Analog ground 3 for the DAC reference ladder and the oscillator

Crystal oscillator output

Crystal oscillator input; if the oscillator is not used, this pin should be connected to ground.

Analog output of Red (Cr)signal

Analog output of Chrominance (CVBS) signal

Analog supply voltage 1 for R(Cr), C(CVBS) outputs

Analog output of Green(Y) signal

Analog output of VBS (CVBS) signal

Analog supply voltage 2 for VBS(CVBS), Green(Y) outputs

Analog output of Blue(Cb) signal

Analog output of CVBS(CSYNC) signal

Analog supply voltage 3 for Blue(Cb)and CVBS(CSYNC), outputs

Analog ground 2 for VBS (CVBS), Blue(Cb), CVBS(CSYNC)outputs

Double speed 54 MHzMPEG port. It is an input for "

CCIR 656"

style multiplexed Cb, Y, Cr data.

Data are sampled on the rising and falling clock edge;data sampled on the risting edge then are sent to

the encoding part of the device, data sampled on the falling edge are sent to the RGB part of the device.

(or vice verse, depending on programming)

V DDA4

XCLK

V

SS3

VDD3

RESN

SCL

SDA

TTXRQ

TTX

I

O

I

I

I

I

I/O

O

I

36

37

38

39

40

41

42

43

44

Analog supply voltage 4 for the DAC reference ladder and the oscillator

Clock output of the crystal oscillator

Digital supply ground 3

Digital supply 3

12C serial clock input

12C serial data input/output

Teletext Request output, indicating when text bits are requested

Teletext bit stream input

Reset input, active LOW. After reset is applied, all digital I/Os are in input mode; PALBlackburst on CVBS, VBS and C;RGB outputs set to lowest voltage.

The 12C-bus receiver waits for the START condition.

Page 14

Reference Information

1-12 Samsung Electronics

1-1-8 MIC1 (TMP93CM41F ; Main Micom)

PAO~PA6

PA7(SCOUT)

P50 to P57

(ANO to AN7)

AVCC

AVSS

VREFH

VREFL

(TXD0)P90

(RXD0)P91

(SCLK0/CTS0)P92

(TXD1)P93

(RXD1)P94

(SCLK1)P95

(PG 00)P60

(PG 01)P61

(PG 02)P62

(PG 03)P63

(PG 10)P64

(PG 11)P65

(PG 12)P66

(PG 13)P67

(T10)P70

(T01)P71

(T02)P72

(T03)P73

(INT4/T14)P80

(INT5/T15)P81

(T04)P82

(T05)P83

(INT6/T16)P84

(INT7/T17)P85

(T06)P86

(INTO)P87

VCC[3]

VSS[3]

X1

X2

CLK

XT1

XT2

AM8/16

EA

RESET

ALE

TEST2,1

NMI

WDTOUT

P00 to P07

(AD0 to AC7)

P10 to P17

(AD8 to AD15/A8 toA15

P20 to P27

(A0 to A7/A16 to A23)

P30(RD)

P31(WR)

P32(HWR)

P33(WAIT)

P34(BUSRQ)

P35(BUSAK)

P36(R/W)

P37(RAS)

P40(CS0/CAS0)

P41(CS1/CAS1)

P42(CX2/CAS2)

PORT A

High

Frequency

OSC

Low

Frequency

OSC

INTERRUPT

CONTROLLER

WATCH-DOG

TIMER

PORT 0

PORT 2

PORT 3

CS/WAIT

CONTROLLER

(3-BLOCK)

PORT 1

10-BIT 8CH

A/D

CONVERTER

SERIAL I/O

(CH,0)

SERIAL I/O

(CH,1)

PATTERN

GENERATOR

(CH,0)

PATTERN

GENERATOR

(CH,1)

16BIT TIMER

(TIMER 4)

16BIT TIMER

(TIMER 5)

8BIT TIMER

(TIMER 0)

8BIT TIMER

(TIMER 1)

8BIT PWM

(TIMER 2)

8BIT PWM

(TIMER 3)

900L-CPU

2KB RAM

XWA

XBC

ADE

XHL

XIX

XIY

XIZ

XSP

W

B

D

H

IX

IY

IZ

SP

A

C

E

L

32bit

F

SR

P C

Page 15

Reference Information

Samsung Electronics 1-13

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

-31 XT1P96

-XT2P97

Test pin. connect to TEST2TEST1TEST1

Test pin. connect to TEST1TEST2TEST2

EEPROM CLOCKECKPA0

EEPROM DATA I/OEDTPA1

EEPROM WRITE PROTECTEWCPA2

-PA3

-PA4

-PA5

-PA6

-PA7

Address latch enableALEALE

VCCVcc

Address/Data 0HAD0AD0

Address/Data 1HAD1AD1

Address/Data 2HAD2AD2

Address/Data 3HAD3AD3

Address/Data 4HAD4AD4

Address/Data 5HAD5AD5

Address/Data 6HAD6AD6

Address/Data 7HAD7AD7

Address 8HA8A8

Address 9HA9A9

Address 10HA10A10

Address 11HA11A11

Address 12HA12A12

Address 13HA13A13

Address 14HA14A14

Address 15HA15A15

FUNCTION

ASSIGNED

NAME

PORT

NAME

No

I/O

O

O

-

-

O

I/O

O

O

O

O

O

O

O

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

A/D Ref input (L)1 GNDVREFL

A/D GND inputAGNDAVss

A/D VCC inputAVCCAVcc

Non-maskable interrupt-/NMI

DSP H/W resetZRSTP70

Master clock selectMCK_SELP71

AV-DEC H/W resetZIVA_RSTP72

Open/close blinkingLEDP73

Interrupt from AV-DECDVDINT/INT4

Interrupt from front micomSRQINT5

Open switchOPENP82

Close switchCLOSEP83

Interrupt from spindle motor FGFGINT/INT6

-

INT7

Request to front micomRRQP86

Interrupt from DSPZINTINTO

Serial data outputRXDTXDO

Serial data inputTXDRXDO

Serial data clockSCLKSCLKO

RF control dataMDTXD1

RF data latchSTB094

RF control clockMCSCLK1

Address mode (H: 8 bit mode)AM8AM8/16

Clock output (System clock÷2)CLKCLK

VCCVcc

GNDGNDVss

High frequency OSC inX1X1

High frequency OSC outX2X2

External access CS41/CS40/EA/EA

Master reset from FRONT/MRST/RESET

FUNCTION

ASSIGNED

NAME

PORT

NAME

No

I/O

I

-

-

I

O

O

O

O

I

I

I

I

I

I

O

I

O

I

I

O

I/O

O

I

O

-

-

I

O

I

I

808179

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

Watch dog timer output61 WDTOUT/WDTOUT

GNDVSS

VCCVcc

Address 16HA16A16

Address 17 (AV-DECODER)HA17A17

Address 18 (Data processor)HA18A18

Address 19HA19A19

Address 20 (D. SERVO)HA20A20

Address 21HA21A21

Address 22HA22A22

Address 23HA23A23

/Read strobe/RD/RD

/Write strobe/WR/WR

-P32

/Wait/MWAIT/WAIT

RCODEP34

-P35

-P36

-P37

Chip select 1

(SRAM, 1M Bit, 128KB)

/CS1

/CS1

-P40/CS0

FUNCTION

ASSIGNED

NAME

PORT

NAME

No

I/O

O

-

-

O

O

O

O

O

O

O

O

O

O

I/OII/O

I/OOI/O

-

O

99

98

97

96

95

94

93

LOCK monitor from DSP92 SLOCKP50

Monitor signalTILTOP51

Spindle direction from SP driverFRP52

SENSE monitor from SERVOSENSEP53

Focus lock monitor from RFFOKBP54

Tracking lock monitor from SERVO

RFRP1P55

RF sum signalRFOP56

VREFOP57

FUNCTION

ASSIGNED

NAME

PORT

NAME

No

I/O

I

I

I

I

I

I

I

100

A/D Ref input (H)AVCCVREFH

I

O

I/O

O

O

O

I/O

O

O

O

-

91

90

89

88

87

86

85

84

83

82

Chip slect 2

(EPROM, 4M Bit, 512KB)

/CS2

/CS2

-P60

Tray in control outputTRAY-INP61

Tray out control outputTRAY-OUTP62

IIC clock (VIDEO ENCODER)SCLP63

IIC clock (VIDEO ENCODER)SDAP64

D.Servo IC data/Address selectDABP65

D.Servo IC chip selectCSBP66

D.Servo IC resetRSTBP67

GNDVss

Page 16

Reference Information

1-14 Samsung Electronics

1-1-9 MIC8 (M27C801 ; 8MB (1M x 8-bit) CMOS EPROM)

NAME

A0-A19

CE

DQ0-DQ7

OE

Vcc

Vss

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

A16

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

Vss

Vcc

A17

A14

A13

A8

A9

A11

OE/VPP

A10

CE

DQ7

DQ6

DQ4

DQ4

DQ3

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

TOP VIEW

Output Enable

Chip Enable and

Prog Logic

Output Buffers

Y

Gating

2,097,152-Bit

Cell Matrix

Y

Decoder

A0-A19

Address

Inputs

OE/VPP

.

.

.

.

.

.

.

X

Decoder

Data Outputs

DQ0-DQ7

CE

Vcc

Vss

BLOCK DIAGRAM

FUNCTION

Address Inputs

Chip Enable Input

Data Input/Outputs

Output Enable Input

Vcc Syply Voltage

Ground

A19

A18

Page 17

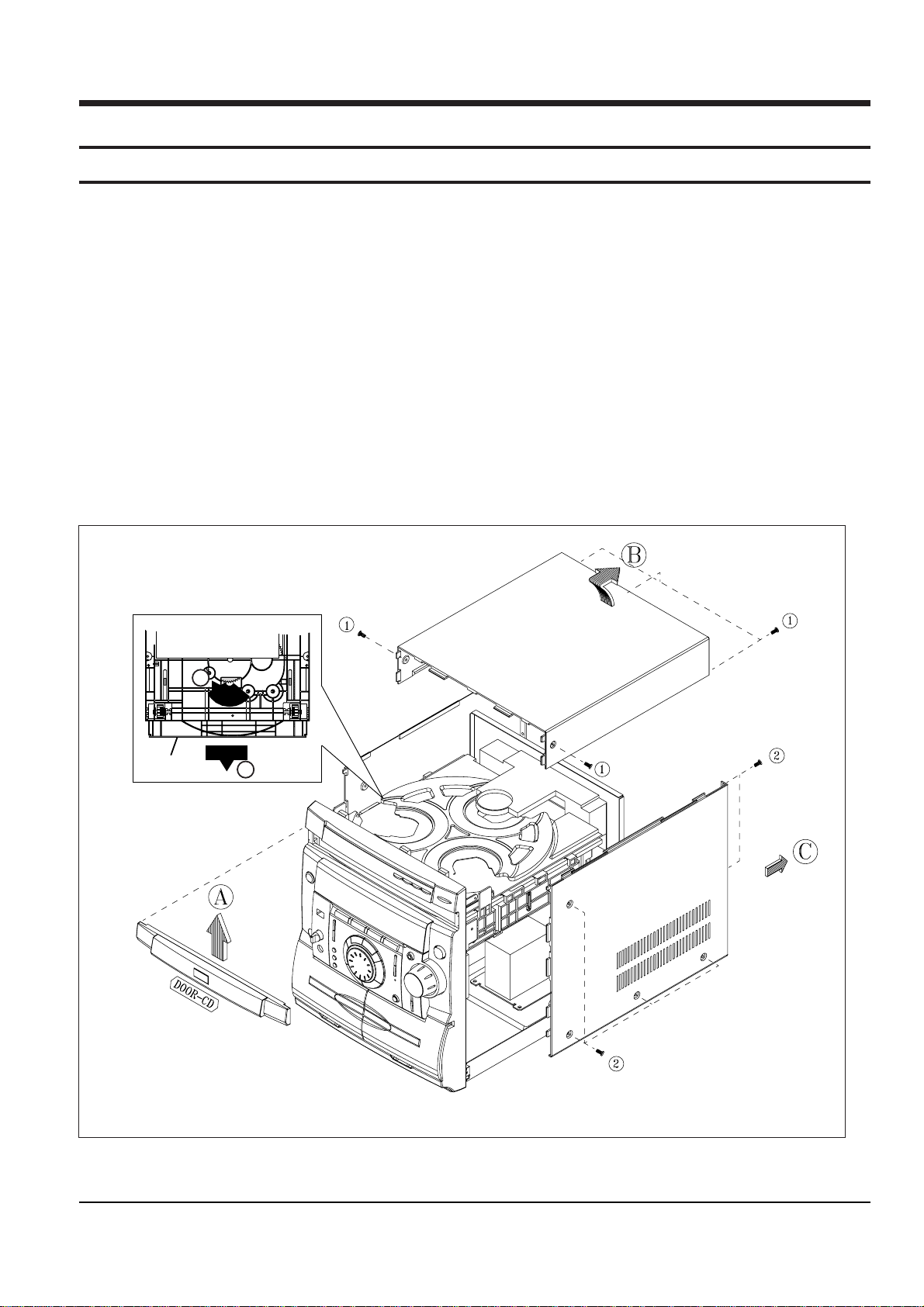

Samsung Electronics

3-1

Diassembly and Reassembly

3. Disassembly and Reassembly

3-1 Cabinet-Top

* If power is connected ;

1. Turn power on and open the CD - TRAY ,push the Door-CD in the direction of arrow A to remove.

2. Close the CD - TRAY and turn power off, and remove the power plug(cord) from main power

3. Remove 5 screws of ! holding the Cabinet-Top in the direction of arrow B.

Lift the back of the Cabinet-Top and shade it to the rear to remove.

4. Remove 12 screws of @ holding the Cabinet-Top in the direction of arrow C.

* If power is not connected ;

1. Remove 5 screws of ! holding the Cabinet-Top in the direction of arrow B.

Lift the back of the Cabinet-Top and shade it to the rear to remove.

2. Remove 12 screws of @ holding the Cabinet-Top in the direction of arrow C.

3. Remove the Cabinet-Top and Turn the Gear the clockwise using the hand as shown in figure 3-1-1.

Open the Door-CD and pull the Tray in the direction of arrow @ as shown in figure 3-1-1.

2

TRAY

1

Figure 3-1

Figure 3-1-1

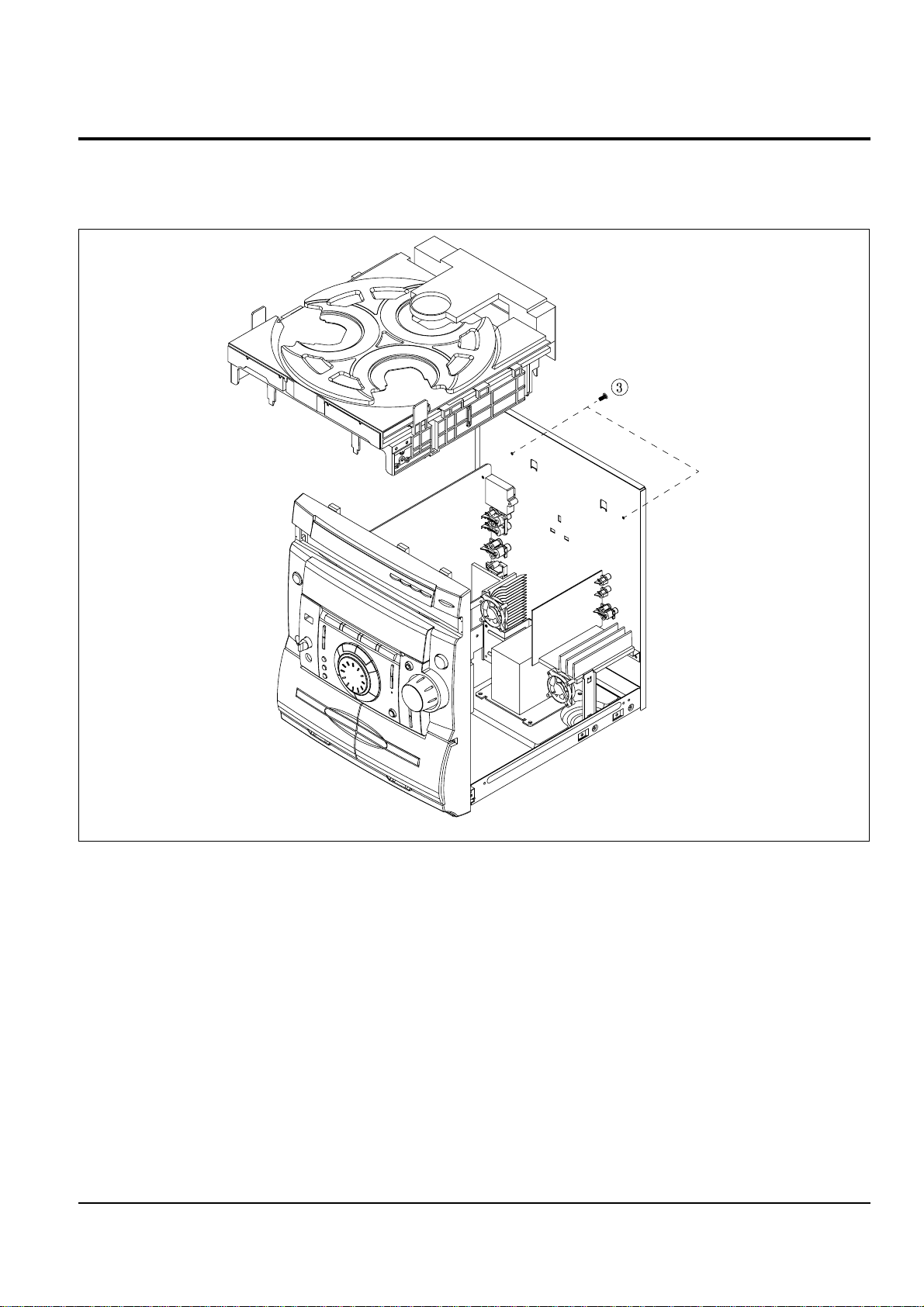

Page 18

Samsung Electronics

3-2

Diassembly and Reassembly

Figure 3-2

3-2 CD-Mecha, Door-CD

1. Remove 2 screws of # .

2. Lift the back of the CD-Mecha to remove.

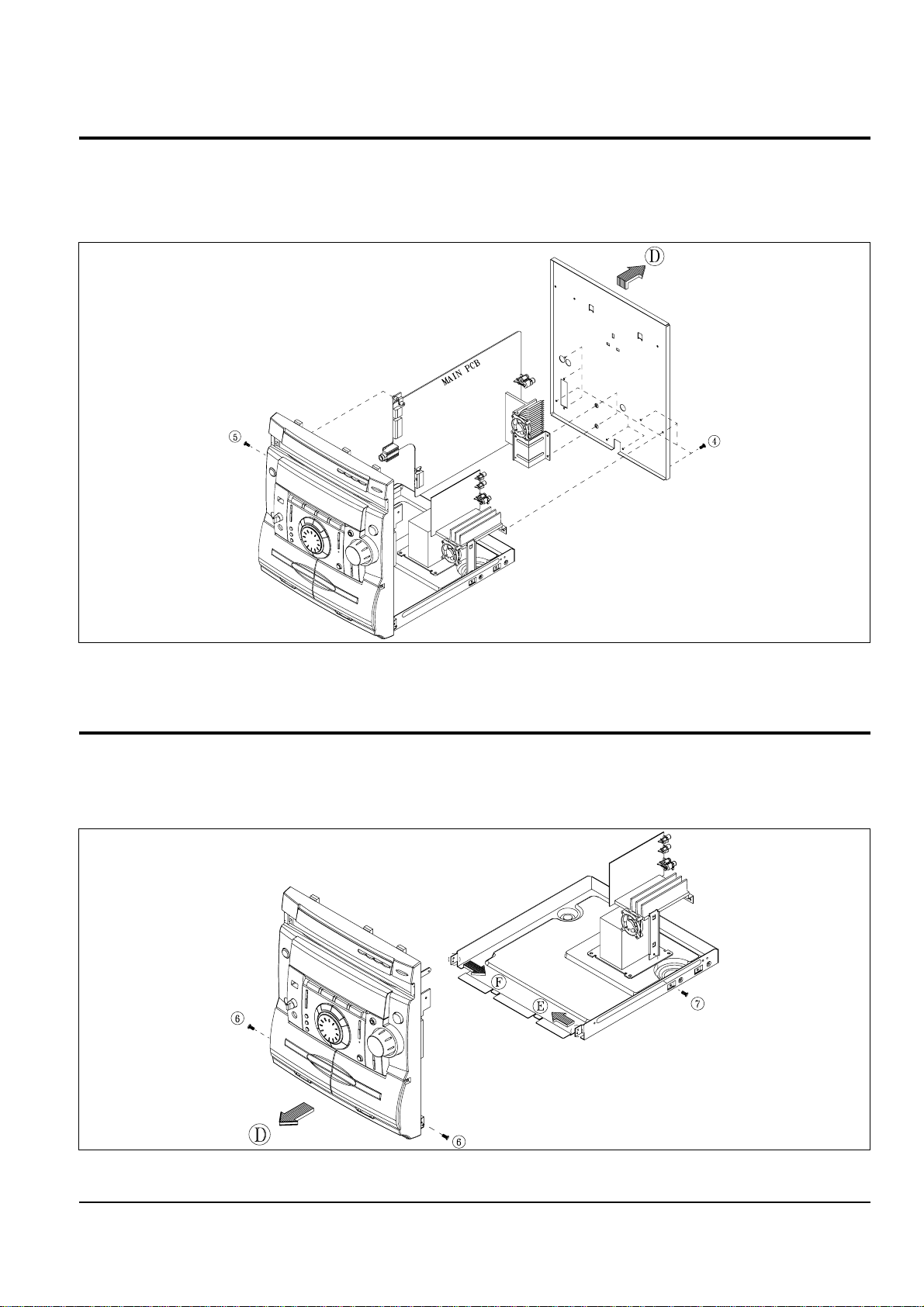

Page 19

Samsung Electronics

3-3

Diassembly and Reassembly

3-3 Cabinet-Rear and Main PCB

1. Remove 19 screws of $ .

2. Lift the Cabinet-Rear in the direction of arrow B and slide it to the rear

by releasing the hook of Cabinet-Bottom.

3. Remove 1 screws of % and slide the Main PCB to the rear to remove.

1. Remove 2 screws of ^ .

2. Slide it to the front by releasing two hooks in the direction of arrow E,F on the bottom of Cabinet-Front to remove.

3. Remove 1 screws of & and slide the PRO-LOGIC PCB to the top to remove .

Figure 3-3

Figure 3-4

3-4 Cabinet-Front and Cabinet-Bottom

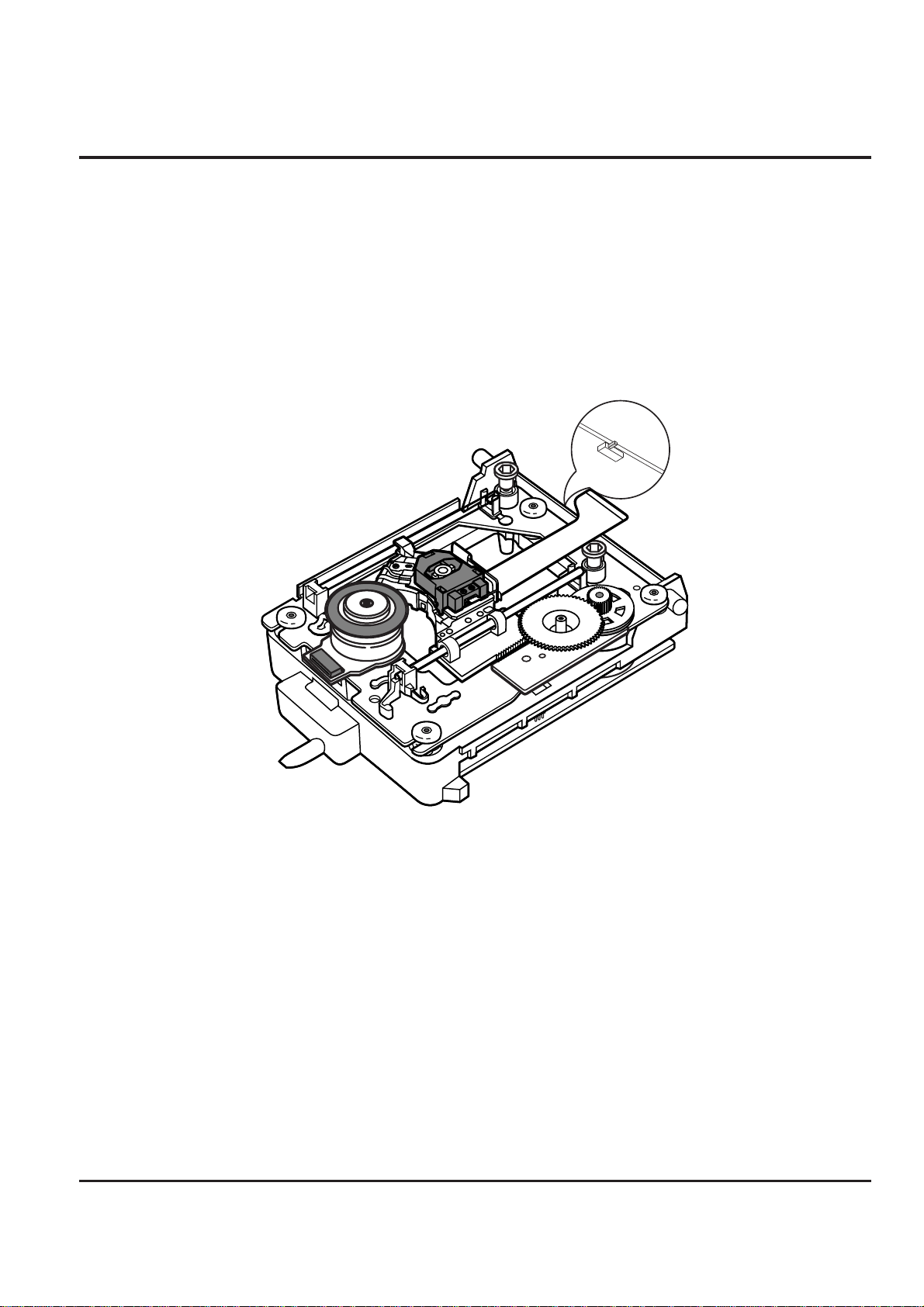

Page 20

Diassembly and Reassembly

3-4 Samsung Electronics

3-5-1 Disassembly

1) Remove the power cable.

2) Switch LD SW1 on deck PCB to ÔOFFÕ before

removing the FPC

( Inserted into Main PCB CN6. See Fig. 1-4)

3) Disassemble the deck.

4) Disassemble the deck PCB.

3-5-2 Assembly

1) Replace the Pick-up.

2) Assemble the deck PCB.

3) Reassemble the deck.

4) Switch LD SW1 on deck PCB to ÔONÕ and insert

FPC into Main PCB CN6 (See Fig 1-4).

3-5 Pick-up disassembly and reassembly

SW1

ON

OFF

Note : If the assembly and disassembly are not done in correct sequence, the Pick-up may be damaged.

Fig. 1-4

Page 21

OUTPUT

AM SSG

450KHZ

INPUT

AM ANT

IN

Speaker Terminal

60cm

TL2

VTVM Oscilloscope

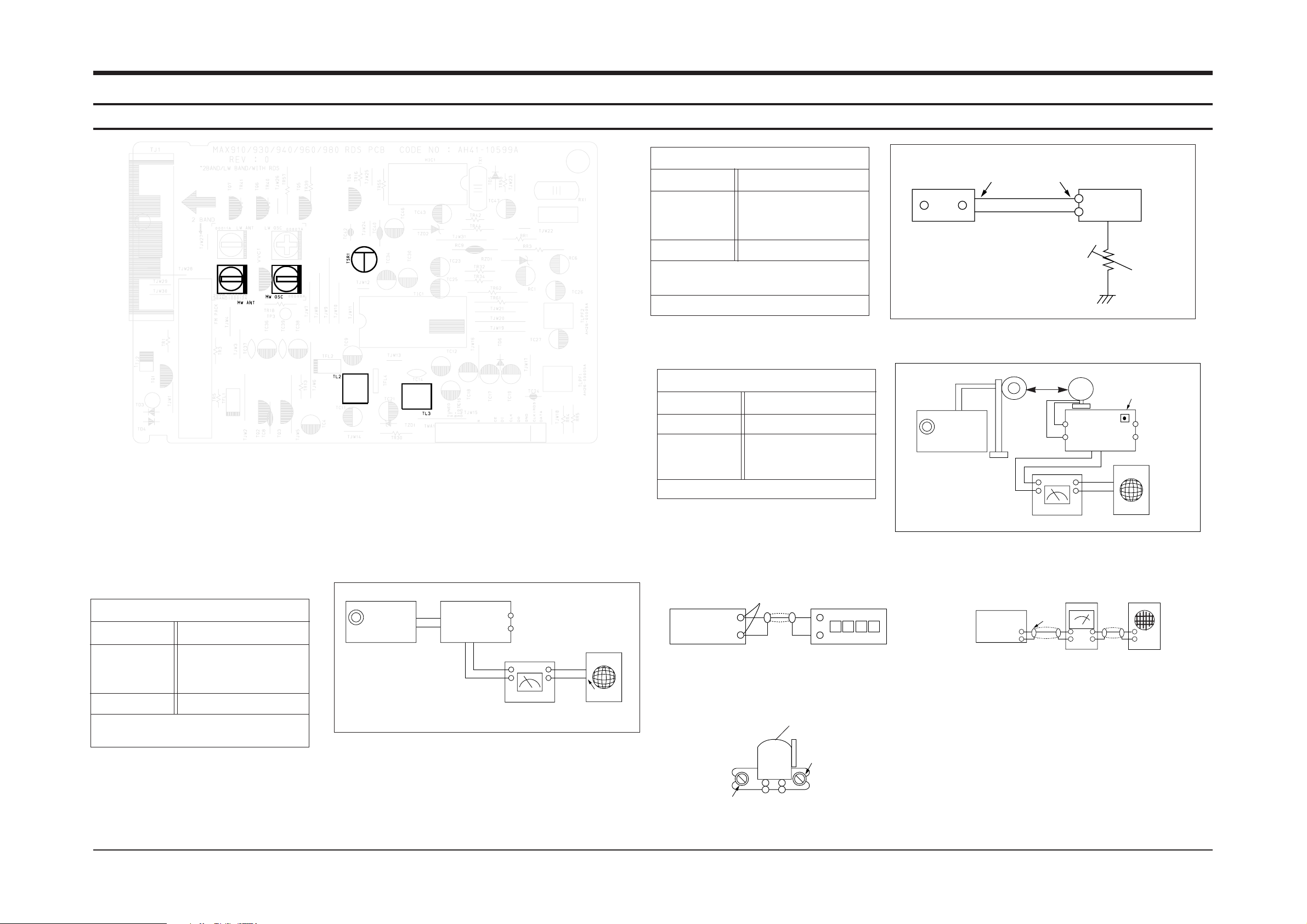

2. Alignment and Adjustments

2-1 Tuner

Samsung Electronics 2-1

FM THD Adjustment

Output

Output

1kHz 28dB

60 dB

Minumum Distortion (0.3% below)

(Figure 2-2)

SSG FREQ.

Adjustment

point

(TL3)

98 MHz

FM DETECTOR COIL

AM(MW) I.F Adjustment

Maximum output (Figure 2-4)

SSG FREQ.

Frequency

Adjustment

point

(TL2)

450 kHz

522 kHz

AM I.F COIL

FM Search Level Adjustment

Adjust IVR1 so that “TUNED” of FLT is

lighted (Figure 2-3)

4Gain : 20dB(CE standard)

Figure2-3 FM Auto Search Level Adjustment

Figure2-4 AM I.F Adjustment

Figure2-2 IF CENTER and THD Adjustment

SSG FREQ.

Adjustment

point

(TSR1)

98 MHz

BEACON

SENSITIVITY

SEMI-VR(10KΩ)

FM SSG

GND

28 dB

FM SSG

Output

GND

Speaker

Terminal

FM

Antenna

Terminal

Distortion Meter

Input

SET

Input

output

Oscilloscope

FM IN

FM Antenna

SET

TSR1

10KHz

* When adjusting T.H.D., readjust I/F coil on the Tuner Pack.

OUTPUT

Fig2-1. Adjustment location of Tuner Part

Speaker

Terminal

output

Frequency Counter

Figure 2-5

Figure 2-6

In Out

Cassette Deck

Oscilloscope

SET

(GND)

VTVM

V H

SPEAKER

Figure 2-7

Recording /Play head

AZIMUTH control

Page 22

2-2-1 To Adjust Tape Speed

* Measuring tape: i) MTT-111 (or equivalent)

(Tapes recorded with 3kHz)

ii) MTT-5512 (or equivalent)

Notes

SPEED

Control

1

2

MTT-111N

(3KHZ)

MTT-111

(3KHZ)

3 kHZ ±1%

Fig. 2-5

Fig. 2-5

-

5200~6600Hz

Check

Remark

Standard

Figure

Adjust

Point

Item

Step

Tape

UVR2(COMMON)

DVR3(Only

MAX909/910/916)

No

Adjustment

HI SPEED

Control

Azimuth

1

MTT-113CN

8KHZ

Fig. 2-7

Output:Maximum

Remark

Standard

Figure

Adjust

Point

Item

Step

Tape

Adjustment

screw of HEAD

L,R

Unbalance

1

2

MTT-112B

(1KHZ)

MTT-5512

±0.5dB

Fig. 2-6

Fig. 2-6

SPEAKER

VTVM (A-DECK)

60KHZ±1KHZ

(Only MAX909/910/916)

85KHZ±1KHZ(COMMON)

DCW4

Remark

Frequency

Range

Figure

Adjust

Point

Item

Step

Tape

DVR4

DL4

Record

Frequency

2-2 Cassette Deck

Alignment and Adjustments

2-2

Samsung Electronics

PreSetup

Press play

button after

puting tape into

the Deck1

PreSetup

Press Rec button

after connecting

(Fig1-6)

PreSetup

Rec Bias

Voltage

1

MTT-5512

(3KHZ)

7V±0.5V

Connect to MWF6 from

AC Meter.

Remark

Votage

Range

Adjust

Point

Item

Step

Tape

SVR1

SVR2

PreSetup

- Adjust SPEED Control

- Adjust Record Frequency

- Adjust Azimuth

- Adjust Rec Bias Voltage

Fig 2-8. Adjustment location of Deck Part

3 kHZ ±1%

Fig. 2-5

Front PCB

Main PCB

Page 23

Circuit Descriptions

4. Circuit Descriptions

4-1 RF

4-1-1 RIC1 (KS1461)

KS1461 is combined with KS1452 and KS1453 as bipolar IC developed for DVD SERVO system.

Main features include DVD waveform equalizing, CD waveform equalizing, focus error signal generation, 3-beam

tracking error signal generation, DPD 1-beam tracking error, defect, envelope, MIRR output, etc. after receiving the

pick-up output converted into I/V.

4-2-1 (a) Basic Potentiometer

KS1461 uses a single power method and each circuit is based on V of 2.5V.

V (Pin 12, 20, 24, 67) terminal is needed for IC, which uses the peripheral V.

4-2-1(b) RF signal

Fig. 4-1shows the flow of signal generated by the pick-up.

A, B, C, D signals detected from pick-up are converted in to RF signal(A+B+C+D) via RF summing AMP.

104

PICK-UP

RFAGCO EQIN

104

A

B

C

D

EFLDPD

104

104

104

5

6

7

8

13

14

15

16

17

18

RE SUM

& AGC

DPD

TE

TE

ABCD

SUM

FE

474

TESEL

Mhx

ENV

FOK

DEFECT

MIRRI

RF EG

MIRR

57

86

36

40

39

43

46

55

54

33

MIRR

RFEQO

TE

ABCDI

103

ABCD

ENV

FOKB

DFCT2

DFCT1

FE

28

29

ALPC

Fig. 4-1

Fig. 4-2 shows the waveform-equalizing block diagram for the RF signal.

It outputs to EQout (Pin 86) terminal by initially changing switching AMPgain of DVD and CD, and then adjusting the level in RF SUM & AGC. It controls RF SUM & AGC gain by means of Pin 89-95 and interfaces with PWM

signal, (output from PWM terminal of KS1453, via low-pass filter to adjust boost gain and peak frequency.

EQout terminal is connected with EQin (Pin 86).

Samsung Electronics 4-1

Page 24

Circuit Descriptions

474

REAGCO 8

The control parameters of DVD EQ and CD EQ are as follows.

9 RFEQO

?

EQIN

.

RF EQ

EQG

Fig. 4-2

EQF

PWM1

¡

PLLGF

PWM2

Æ

VZOCTL

VREFEQ

,

RFDVCC

1) DVD CD EQ control parameter

˛EQG (Pin 97) : Changes the gain of peak frequency with EQ frequency characteristic. Convert PWM signal,

output from KS1453, into DC via low-pass filter.

«EQF (Pin 98) : Changes the peak frequency with EQ frequency characteristic. Convert PWM signal, output

from KS1453, into DVD via low-pass filter.

4-2 Samsung Electronics

Page 25

Circuit Descriptions

Samsung Electronics 4-3

4-2 System Control

4-2-1 Outline

The main micom peripheral circuit is composed of 16bit Micom (MIC1 ; TMP93CM41F), 8M EPROM (MIC8 ; AM27C080) for Microcode and data save, 512 byte EE-PROM (MIC5 ; KS24C020) for permanent storage of data needed at

power off, MIC4 (74AC573) to latch only address in the bus where address and data are mixed, address decoder

(MIC7 ; 74HC00) for selection of ex-ternal device chip and 20MHz clock oscillator for micom operation. The Micom

(MIC1 ; TMP93CM41F) mounted in main board analizes the key commands of front panel or instructions of remote

control through communication with Micom (FIC1 ; LC86P6232) of front and controls the devices on board to execute the corresponding commands after initializing the devices connected with micom on board at power on.

4-2-2 Block Diagram

RIC1

RF AMP

KS1461

SIC1

DIGITAL SERVO

KS1452

VIC1

A/V DECODER

ZIVA-3

VIC50

VIDEO ENCODER

SAA7128/7120

AIC1,2,3,4

D/A CONVERTER

AK4324

DIC1

DATA PROCESSOR

KS1453

MIC2

ADDR LATCH

74AC573

MIC1

MAIN MICOM

TMP93CM41F

MIC8

EPROM

AT27C080

MIC5

EEPROM

KS24C020

MICOM

BLOCK

HIGH ADDRESS

LOW ADDRESS

DATA BUS

UIC1

FRONT MICOM

LC86P6548

MIC7

ADDR DECODER

74HC00

Fig. 4-3

Page 26

Circuit Descriptions

4-4 Samsung Electronics

4-2-3 Waveform Description

When micom accesses each device sharing bus, it falls the chip select signal of corresponding chip to (CS2:MIC8-22,

/DSPCS:DIC1-2, /DVDCS:VIC1-206/SRVCS:SIC1-10) 0 (Low) before trial.

So to speak, the bus is used by time-division as shown in Fig 4-4, 4-5, 4-6.

Two and more devices can't be accessed simultaneously.

• CH1 : CS2 (MIC8-22, EPROM CHIP SELECT)

• CH2 : DSPCS (DIC1-2, DATA PROCESSOR CHIP SELECT)

• CH3 : DVDCS (VIC1-206, A/V DECODER CHIP SELECT)

• CH4 : SRVCS (SIC1-10, DIGITAL SERVO CHIP SELECT)

• CH5 : WR (MIC1-73, MICOM OUTPUT WRITE SIGNAL)

• CH6 : RD (MIC1-72, MICOM OUTPUT READ SIGNAL)

/CS2

/DSPCS

/DVDCS

/SRVCS

/RD

/WR

Fig. 4-4

• CH1 : CS2 (MIC8-22, EPROM CHIP SELECT)

• CH2 : DSPCS (DIC1-2, DATA PROCESSOR CHIP SELECT)

• CH3 : DVDCS (VIC1-206, A/V DECODER CHIP SELECT)

• CH4 : SRVCS (SIC1-10, DIGITAL SERVO CHIP SELECT)

• CH5 : WR (MIC1-73, MICOM OUTPUT WRITE SIGNAL)

• CH6 : RD (MIC1-72, MICOM OUTPUT READ SIGNAL)

/CS2

/DSPCS

/DVDCS

/SRVCS

/RD

/WR

Fig. 4-5

Page 27

Circuit Descriptions

Samsung Electronics 4-5

• CH1 : CS2 (MIC8-22, EPROM CHIP SELECT)

• CH2 : DSPCS (DIC1-2, DATA PROCESSOR CHIP SELECT)

• CH3 : DVDCS (VIC1-206, A/V DECODER CHIP SELECT)

• CH4 : SRVCS (SIC1-10, DIGITAL SERVO CHIP SELECT)

• CH5 : WR (MIC1-73, MICOM OUTPUT WRITE SIGNAL)

• CH6 : RD (MIC1-72, MICOM OUTPUT READ SIGNAL)

/CS2

/DSPCS

/DVDCS

/SRVCS

/RD

/WR

Fig. 4-6

Page 28

Circuit Descriptions

4-3 Servo

4-3-1 Outline

SERVO system of DVD is divided into Focusing SERVO, Tracking SERVO, SLED Linked SERVO and CLV

SERVO (DISC Motor Control SERVO).

1) Focusing SERVO

Focuses the optical spot output from object lens onto the disc surface. Maintains a uniform distance between

object lens of Pick-up and disc (for surface vibration of disc).

2) Tracking SERVO

Make the object lens follow the disc track in use of tracking error signal (created from Pick-up).

3) SLED Linked SERVO

When the tracking actuator inclines outwardly as the object lens follows the track during play, the SLED motor

moves slightly (and counteracts the incline).

4) CLV SERVO (DISC Motor Control SERVO)

Controls the disc motor to maintain a constant linear velocity (necessary for RF signal).

4-3-2 Block Diagram

SLED M/T

HALL

PCB

LD

PD

FOCUSING

TRACKING

DISC

SPINDLE M/T

CN1

HA1+

HA1–

HA2–

HA2+

SLED+

SLED–

AO

DO

CO

BO

FO

EO

PD

LD

F–

T+

T–

F+

SPINDLE

3

SIC8

2

NJM2903

5

6

+

34

11

12

18

17

KA3010D

1

2

KA3011D

DRIC2

DRIC1

7

20

MIC1

TMP 93CS41F

RIC1

KS1461

SIC1

KS1452

1

94

Fig. 4-7

4-6 Samsung Electronics

Page 29

Circuit Descriptions

Samsung Electronics 4-7

4-3-3 Operation

1) FOCUSING SERVO

(1) FOCUS INPUT

The focus loop is changed from open loop to closed loop, and the triangular waveform moves the object lens up

and down (at pin 75 of SIC1 during Focus SERVO ON.) At that time, S curve is input to pin 65 of SIC1.

ABAD (pin 39 of RIC1) signal, summing signal of PD A, B, C, D, is generated, and zero cross(2.5V) point occurs

when S curve is focused and ABAD signal exceeds a preset,constant value. The focus loop is changed to

closed loop, and the object lens follows the disc movement, maintaining a constant distance from the disc.

(these operations are same in CD and DVD).

Fig. 4-8

Vref

Vref

1.5V

Pin75 of SIC1 (FOD)

Pin65 of SIC1 (FEI)

Pin39 of RIC1 (ABCD)

(2) PLAY

When focus loop closes the loop during focus servo on, both pin 65 and pin 75 of SIC1 are controlled by VREF

voltage (approx. 2.5V), and pin 1, 2 of DRIC2 are approximately 4.5V.

2) TRACKING SERVO

(1) NORMAL PLAY MODE

˛ For DVD

Composite : The signal output from PD A, B, C, D of Pick-up, the tracking error signal (pin36 of RIC1) uses the

phase difference of A+C and B+D in RIC1, and inputs to terminal 64 of SIC1. Then, it is output to SIC1 pin 76 via

digital equalizer, and applied to the tracking actuator through DRIC2.

Pins 17, 18 of SIC1 are controlled by VREF(approx. 2.5V) during normal play.

Meanwhile, DVD repeats the track jump from 1 to 4 in inner direction at normal play (because data- read speed

from disc is faster than data output speed on screen).

« For CD, VCD

Receive the signal output through E, F of Pick-up, from RIC1. The tracking error signal is similar to DVD.

Page 30

Circuit Descriptions

4-8 Samsung Electronics

(2) SEARCH Mode :

Search mode : Fine seek,(Moving the tracking actuator slightly little below 255 track) and coarse search, moving

much in use of sled motor. The coarse search will be described in sled linked servo and now, the fine seek is

explained shortly.

If the object lens is located near target, cut off the tracking loop and give the control signal as many as desired

count to move the tracking actuator via SIC1 pin 76 terminal(TRD).

3) SLED LINKED SERVO

¥ Normal play mode

Move SLED motor slightly by means of PWM signal in SIC1 pin 73, as the tracking actuator moves along with

track during play. Control to move the entire Pick-up as the tracking actuator moves.

¥ Coarse serach mode

In case of long-distance search (such as chapter serach), SIC1 uses sled FG (SIC8 pin 1, 7, which is generated) by

rotation of sled motor via hall PCB. Then, read ID and compute the existing track count after input of next

track. If the existing track count is within fine seek range, tracking begins using fine seek.

4) CLV SERVO(DISC MOTOR CONTROL SERVO)

Input RF signal (from Pick-up) to SIC1 pin59. Detect SYNC signal from RF in SIC1, and output PWM signal to

SIC1 pin 55 for constant linear velocity.

Page 31

Circuit Descriptions

Samsung Electronics 4-9

4-4 DVD Data Processor

4-4-1 Outline

DIC1(KS1453) performs Sync detection, EFM/EFM demodulation and error correction and Spindle motor control

(CLV control) after inputting sliced EFM signal of RF signal at disc playback and EFM read clock (PLCK) signal generated from PLL. Outputs data which converted to the last audio and video from A/V decoder(VIC1). KS1453 uses

external memory(4M DRAM) as buffer as well as for error correction and carries out Variable Bit Rate transfer function. VBR function uses the external buffer as buffer to absorb the difference of transfer rate occurring because the

transfer rate of disc playback is faster than data transfer rate demanded by A/V decoder(Video/Audio Signal

Process Chip).

In case of general disc refresh, the memory is almost filled up periodically. It is because Write rate to memory after

disc playback and signal process is faster than Read of A/V decoder. When the memory is filled, this status is reported by interrupt to main micom, which controls the servo to kick back the pick-up to the previous track after memorizing the last data read from disc until now. It takes some times to jump to the previous track and return to the

original(jump location) again. The memory will have an empty space because A/V decoder reads out data of memory.

When the memory has an empty space, where data can be processed and written and the pick-up correctly gets to

the original location(before kick back location) again, it reads data again avoids the interrupt of data read previously. The basic operation repeats to perform as described above.

4-4-2 Block Diagram

Fig. 4-9

AD[7..0]

HA[23..8]

*WR(73)

INTO(ZIRQZD)

INT4(/INT)

*RD(72)

MIC1 TMP93CM41F

HDATA[7..0]

HADDR[3..0]

/CS

/RD

/WR

/INT

DVD-D[7..0]

VSTROBE

REQUEST

DACK

*ERR

VIC1

(ZiVA-3)

192

191

196

200

177, 178

CLOCK 27MHz

CLOCK 33.8688MHz

CLOCK 27MHz

14

95

69

70

58

71

57

SDATA[7..0]

CSTROBE

DATREQ

DATACK

DTER

TOS

OEW

E

C

A

S

R

A

S

[

[

D

1

5

.

.

0

[

[

A

8

.

.

0

[

[

D

D

1

5

.

.

0

[

[

D

A

D

R

8

.

.

0

Z

R

A

S

Z

C

A

S

Z

W

E

O

Z

O

E

O

MDAT[7:0]

MRZA(3)

ZCS(2)

MWR(128)

MRD(127)

ZIRQZD(126)

EFMI

PLCK

116

104

109

110

MDP

MDS

EFM

PLCK

DIC1

(KS1453)

DIC2

(KM416C254)

Page 32

Circuit Descriptions

4-10 Samsung Electronics

4-4-3 Waveform Description

It measures the timing that data processed in DIC1 at DVD playback.

STROBE

REQ

DACK

SDATA all

220 1 0

Fig. 4-10

• CH1 : STROBE (DIC1-69, CLOCK)

• CH2 : REQ (DIC1-70, DATA REQUEST)

• CH3 : DACK (DIC1-58, DATA ACKNOWLEDGE)

• CH4 : SDATA (DIC1-60~67, DATA)

Page 33

Circuit Descriptions

Samsung Electronics 4-11

4-5 Video

4-5-1 Outline

VIC50 sends VSYNC and HSYNC from VIC1(A/V decoder) and receives 8bit video data.

VIC50 does RGB encoding, copy guard processing and D/A conversion of 8bit video data inputted from VIC1(A/V

decoder) by control of MIC1(Micom).

Video signal converted into analog signal is outputted via amplifier of analog part.

(Main Board) (Output Board)

VIC1

A/V Decoder

ZiVA-3

MIC1

Main Micom

TMP93CM41F

Video

data

VIC50

SAA7128

Video

encoder

VIC52

Amplifier

BA7660

CVBS-1

Fig. 4-11 Video Output Block Diagram

Page 34

Circuit Descriptions

4-12 Samsung Electronics

4-5-2 NTSC/PAL Digital Encoder (VIC50 : SAA7128)

VIC50 inputted from pin4 with 27MHz generates HSYNC and VSYNC which are based on video signal. Each

HSYNC and VSYNC outputted from Pin8 and Pin7 are inputted to Pin157 and Pin158 of A/V decoder VIC1(ZIVA-

3). VIC1 is the synchronous signals with the video signal and control the output timing of 8bit video signal of ITUR601 format. (Pin180, 182, 184 ~ 189 (MSP))

8bit data is inputted to Pin9(MSB) and Pin16 of VIC50 and the inputted data is demuxed with each 8bit of Y/R-Y/BY. The separate signal is encoded to NTSC or PAL by control of MIC1. The above signals, that is CVBS

(Composite Video Burst Synchronized)(Pin30), S-Video (Y:Pin27, C:Pin24), Y/Pb/Pr(Pin27/Pin29/Pin23) and

GB(Pin26/Pin29/Pin23). In course of encoding, 8bit data can extend to 10bit or more. To convert the extended data

to quantization noise as possible, VIC50 adopts 10bit D/A converter. VIC50 perform video en-coding as well as

copy protection.

VDATA

[7:0]

VSYNC

HSYNC

27M

MRST

SDA

SCL

9~16

7

8

4

40

42

41

Demultiplexer

Y

CR-CB

RGB encoding

Luminace

processing

MACROVISION

7.0.1/6.1

Cloed captions

CGMS

Chrominance

processor

CTRL+CFG

register

Trap

10-bit DAC

30

27

24

23

26

29

CVBS

Y

C

Cr/R

G

Cb/B

VIC1 (SSA7128)

Fig. 4-12

4-5-3 Amplifier (VIC51, VIC52 : BA7660)

VIC51 and VIC52 are 6dB amplifier. Based on CVBS signal, the final output level must be 2Vpp without 75ohm terminal resistance. Because the level of video encoder output is only 1.1Vpp, the level is adjusted with the special

amplifier. When mute of pin1 is high active, if the pin is floating and connected to power, the output signal is never

outputted. CVBS, Y, C, Cr and Cb outputted from video encoder are inputted to VIC52 (Pin7, Pin2 and Pin4) and

VIC51 (Pin7 and Pin4) respectively and outputted from VIC52 (Pin10, Pin15 and Pin13) and VIC51 (Pin10 and Pin

13). Pin9, Pin12 and Pin14 of VIC51 and VIC52 are feedback pin to SAG compensation(DC characteristic compensation of signal). Resistance(VR3-VR14) which is inserted to input terminal is bias resistance for input offset. The

signal to which gain is adjusted by amplifier is outputted from jack via 75ohm.

Page 35

Circuit Descriptions

Samsung Electronics 4-13

4-6 Audio

4-6-1 Outline

The four data (Data 0~3) outputted from A/V decoder (VIC1 ; ZiVA-3) are supplied to DATA 0 for 2-channel

mixed audio output and to DATA 1~3 for Analog audio output (5.1-channel).

The audio data (0~3) transmitted from A/V decoder (VIC1 ; ZiVA-3) are converted into analog signal via audio

D/A converter and outputted via post filter and amplifier.

CD and VCD are outputted with only 2 channels audio data and transmit them to Data 0 and Data 1.

Front L/R channel is outputted in mixed audio output (L/R output) and analog audio output and surround L/R,

center and subwoofer arenÕt outputted.

If DVD of 2 channels source disc is used, it is outputted by the same way with CD and VCD.

AIC1

AK4324

D/A CONVERTER

POST

FILTER

POST

FILTER

AMP

AMP

VIC1

(ZiVA-3)

A/V Decoder

DATA0

LRCK

BCK

L

R

Mixed Audio Output (2-Channel)

Fig. 4-13 Audio Output Block Diagram

Page 36

Circuit Descriptions

4-14 Samsung Electronics

4-6-2 DVD Audio Output

1) Compressed Data

The audio data inputted to VIC1 (ZiVA-3) A/V decoder is divided into compressed data and uncompressed data.

It is compressed data that is compressed with multi-channel audio data such as Dolby digital, MPEG, DTS, etc.

The compressed data inputted to VIC1 (ZiVA-3) is converted into the uncompressed data of 2, 4, and 6 channels

through ZiVA-3 built-in audio decoder and is outputted to Data 0, 1, 2, and 3 through digital audio interface.

The compressed data is transmitted to external AC-3 amplifier or MPEG/DTS amplifier as IEC-958/1937 transmission data format compressed by ZiVA-3 built-in IEC-958 output process.

2) Uncompressed Data

The uncompressed data is that data isnÕt compressed, so it is called CD-DA, LPCM data.

The 2 channels data is converted through audio decoder 2-channel data and Data 0 and Data 1 are outputted in

digital audio interface.Via IEC-958 output process, they is transmitted to digital amplifier or AC-3/MPEG/DTS

amplifier built in the external digital input source with IEC-958/1937 transmission format.

AUDIO INPUT

BUFFER

AUDIO OUTPUT

BUFFER

RECEIVER

or

DECODER

(IEC-958/1937)

AUDIO

DAC

HOST or DVD/CD

INTERFACE

IEC-958/1937

OUTPUT PROCESS

IEC-958/1937

INTERFACE

AUDIO DECODER

(MPEG, DOLBY DIGITAL,

CD-DA, LPCM

DIGITAL AUDIO

INTERFACE

2-, 4, or 6-

CHANNEL OUTPUT

PROCESS

Uncompressed 16- or 24-bit

LPCM camples at

fs=44.1,48,96KHz

2-Channel LPCM, Decoder

Dolby Digital, Decoded MPEG

Compressed Data

(MPEG, Dolby Digital),

CD-DA, LPCM

VIC4, 10 (LOCAL DRAM)

VIC1 (ZiVA-3 ; A/V DECODER)

Source Data Types :

MPEG-1,-2, Dolby Digital,

CD-DA, LPCM

Fig. 4-14 Audio Decoder and Output Interface Datapath

Page 37

Samsung Electronics

5-1

Exploded Views and Parts List

5.Exploded Views and Parts List

5-1 Cassette Deck Exploded View and Parts List :

4

5

2

1

8

4

3

7

6

8

No. Code No. Description Specification Remarks

AH59-20006B DECK-CASSETTE ADR2113MW3

1 AH81-11052G MOTOR ASS’Y EG530YD2BH

2 AH81-10798Y HEAD ASS’Y(R/P) YK56RAA4N3

3 AH81-10022E HEAD ASS’Y(P/B) MS15RAA2N1

4 AH81-10798K PINCH ARM(F) ADR2100-06

5 AH81-10798M PINCH ARM(R) ADR2100-07

6 AH81-10798Q MAIN BELT(R/P) ADR2113MW-02

7 AH81-10798T MAIN BELT(P/B) ADR2113MW-03

8 AH81-10798U SUB BELT ADR2100-09

Page 38

Samsung Electronics

5-2

Exploded Views and Parts List

5-2 Total Exploded View and Parts List

52

5-2-1 Total Exploded1 - MINI Part

Page 39

Samsung Electronics

5-3

Exploded Views and Parts List

5-2-2 Parts List of Total Exploded view1 - MINI Part

1 AH64-40457B WINDOW-CD PMMA 850-71129 BASIC

AH64-40457C ” PMMA 850-71129 RDS

2 AH64-70003H BADGE-BRAND ABS BLK(H/STAMPING)

3 AH64-00130B DOOR-CD ABS L/GRAY(G6236)

4 AH67-00006A FILTER-DVD KIMO 100

5 AH67-00007B LENS-DVD ACRYL CLR

6 AH64-00131B WINDOW-DOOR,CD PMMA 850-71129

7 AH67-40036A FILTER-VFD PC 0.3T BLK

8 AH64-40459A WINDOW-VFD PMMA 850-41802

9 AH61-20535Q CAP-FRONT,E MIPS D/GRAY 945 DVD + RDS

AH61-20535T “ “ BASIC

AH61-20536J CAP-FRONT,D “ MAX945 DVD + MIC

AH61-20536K “ “ MAX945 DVD + MIC + RDS

10 AH64-11214C KNOB-MIC D/GRAY(G3174) BUYER OPTION

11 AH64-11321B KNOB-VOLUME L/GRAY(G6236)

12 AH64-11322B KNOB-JOG ABS NATURAL

13 AH64-40462A DECO-JOG ABS 94HB BLK

14 AH61-20537B CAP-TIMER ABS NATURAL

15 AH64-11317B KNOB-TIMER ABS NATURAL

16 AH64-40460A WINDOW-DOOR,A PMMA 850-71129

17 AH64-40461A WINDOW-DOOR,B PMMA 850-71129

18 AH64-50351E DOOR-CASS.A ABS L/GRAY(G6236)

19 AH64-50352G DOOR-CASS.B ABS L/GRAY(G6236)

20 AH61-62004A SPRING-EJECT,A STS φ1.1

21 AH61-62005A SPRING-EJECT,B STS φ1.1

22 AH64-30441F CABINET-FRONT MIPS L/GRAY(G6236)

23 AH61-80030A DAMPER-ASSY POM

24 AH95-50001A LATCH-ASSY POM

25 AH64-11316D KNOB-POWER L/GRAY(G6236)

26 AH67-10182A LENS-COM,L PMMA MILKY

27 AH67-10183A LENS-COM,R PMMAMILKY

28 AH61-20541A HOLDER-COM,L ABS WHT

29 AH61-20542A HOLDER-COM,R ABS WHT

30 AH64-11319A KNOB-DEMO D/GRAY(G3174)

31 AH67-10187A LENS-REC PMMAMILKY

32 AH64-11318A KNOB-DUBBING D/GRAY(G3174)

33 AH67-10184B LENS-TURBO ACRYL CLR

34 AH67-40038A FILTER-TURBO KIMO 100

35 AH61-20543A HOLDER-TURBO ABS WHT

36 AH67-10186E LENS-FUNTION PMMA CLEAR

37 AH67-40037A FILTER-FUNCTION KIMO 100

38 AH61-20544A HOLDER-FUNCTION ABS WHT

39 AH64-11315A KNOB-DISC L/GRAY(G3174)

40 AH61-00021A SUPPORT-PCB ABS 94HB BLK

No. Code No. Description Specification Remarks No. Code No. Description Specification Remarks

41 AH62-32009A HEAT-SINK,M AL

42 AH61-10767A BRKT-H/SINK SECC 1.0T

43 AH61-00111A BRKT-SIDE SECC 1.0T

44 AH62-00009A HEAT-SINK,DVD AL

45 AH61-00110A BRKT-REAR SECC 1.0T

46 AH61-20540A HOLDER-TUNER PC + ABS BLK

47 AH64-30444A CABINET-SIDE,L MIPS M/GRAY

48 AH64-30445A CABINET-SIDE,R MIPS M/GRAY

49 AH64-30443A CABINET-TOP MIPS M/GRAY

50 AH64-30416A CABINET-BOTTOM SECC 1.0T

51 AH64-00132D CABINET-REAR SECC 0.8T 2 VOL + DVD + SW

AH64-00132E “ “ 1 VOL + DVD

AH64-00132F “ “ 1 VOL + DVD + SW

AH64-00132H “ “ 2 VOL + DVD

52 AH67-10185A LENS-REMOCON ACRYL BROWN

Page 40

Samsung Electronics

5-4

Exploded Views and Parts List

5-3 DVD Mecha Exploded View and Parts list

1

2

4

22

6

5

7

9

10

11

12

8

3

DV-P32

ASSY PCB-DECK

13

14

15

16

20

18

19

17

ASSY PCB SENSOR

CMS-300DVD

21

25

23

24

No. Code No. Description Specification Remarks

AH97-00223A CMS3000-L DVD MECHA ASS’Y

1 AH61-20428A-1 BASE-MAIN ABS WHT

2 AH66-90055A TRAY-DISC ABS BLK

3 AH66-90056A ROULLETTE ABS BLK

4 AJ66-20001A GEAR-CAM DOM WHITE

5 AH66-20190A GEAR-CONVERT POM(M90-44)

6 AH66-20189A GEAR-TRAY POM(M90-44)

7 AH66-80022A SLIDE-CAM ABS

8 AH66-20191A GEAR-SYNCRO ABS(HF-380)

9 AH66-20186A GEAR-PULLEY POM(M90-44) WHT

10 AH66-60034A BELT-LOAD CR T1.5

11 AH66-10008A PULLEY-MOTOR POM,BLK,CMS-CR3

12 AH31-10021A MOTOR-DC RE-500TB,9VDC/130MA

14 AH61-00070A PLATE-CHUCK M90-44(DURACON)

15 AH33-00002A MAGNET RARE EARTH MAGNET

16 AH66-00027A CLAMPER M90-44(DURACON)

17 AH60-10016A SCREW PH,+,-,M2.6,L4 ,YEL,-,

18 AH66-20192A GEAR-WORM POM(M90-44)

19 AH31-12001A MOTOR-ROULETTE FF-030PN-09210

20 AH39-00049A CABLE-DIN-FLAT DP,-,160,UL2896 36P,BD,WHT,5,21 AC60-10059A SCREW-TAPPING BH,+,-,1.7X5,ZPC2