Page 1

LCD-TV

Chassis Model

VN32EO LW32A23W

VN40EO LW40A23W

SERVICE

Manual

LCD-TV CONTENTS

Block Diagram

Wiring Diagram

Schematic Diagrams

Page 2

Block Diagram

❈ This Document can not be used without Samsung’s authorization.

Worldwide Full Multi-System Block diagram

LTN325W/LTN406W

Page 3

Block Diagrams

LW32A23W/LW40A23W

Sound Block diagram

Page 4

Block Diagrams

LW32A23W/LW40A23W

Video Block diagram

Page 5

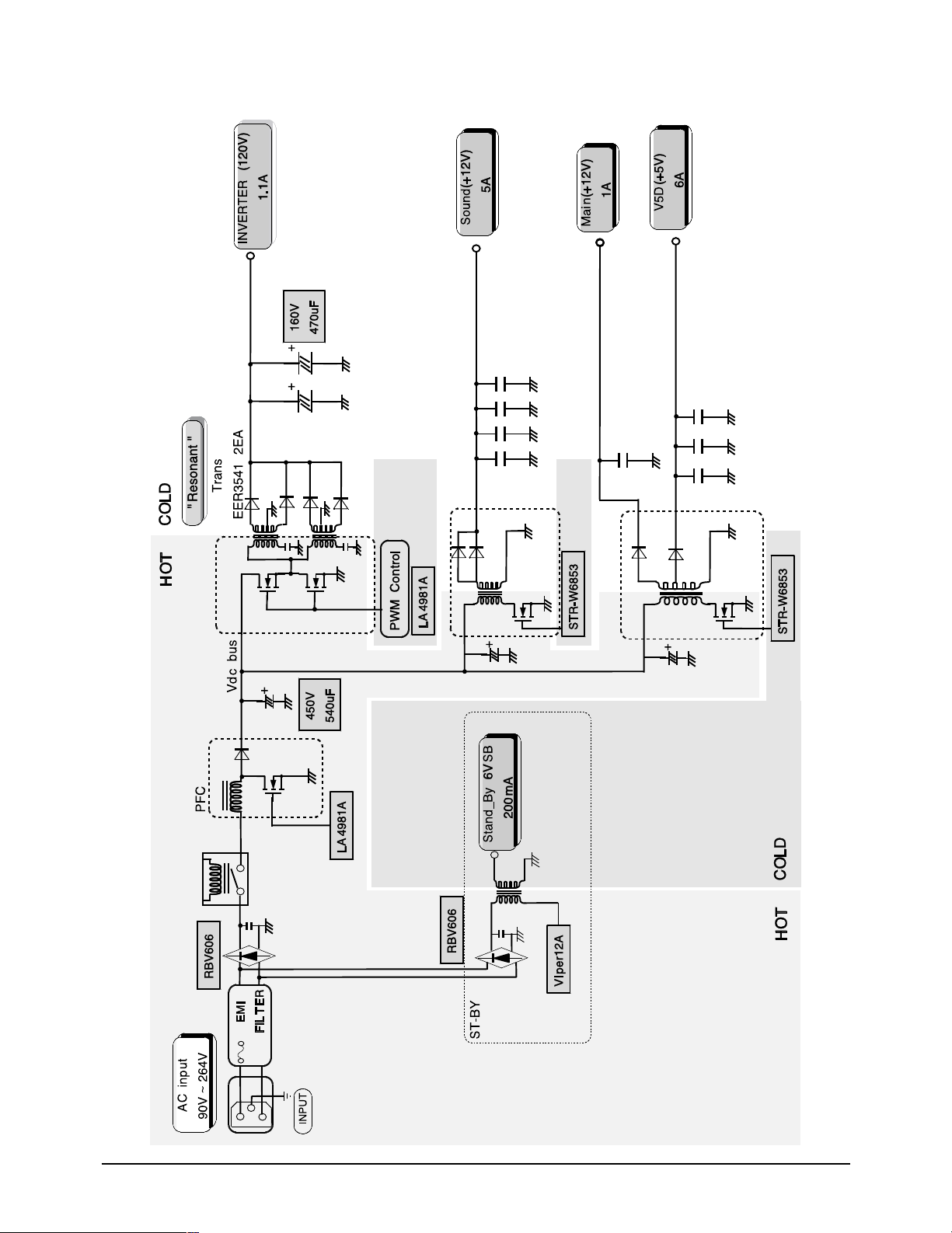

Block Diagrams

LW32A23W/LW40A23W

Power Block diagram

Page 6

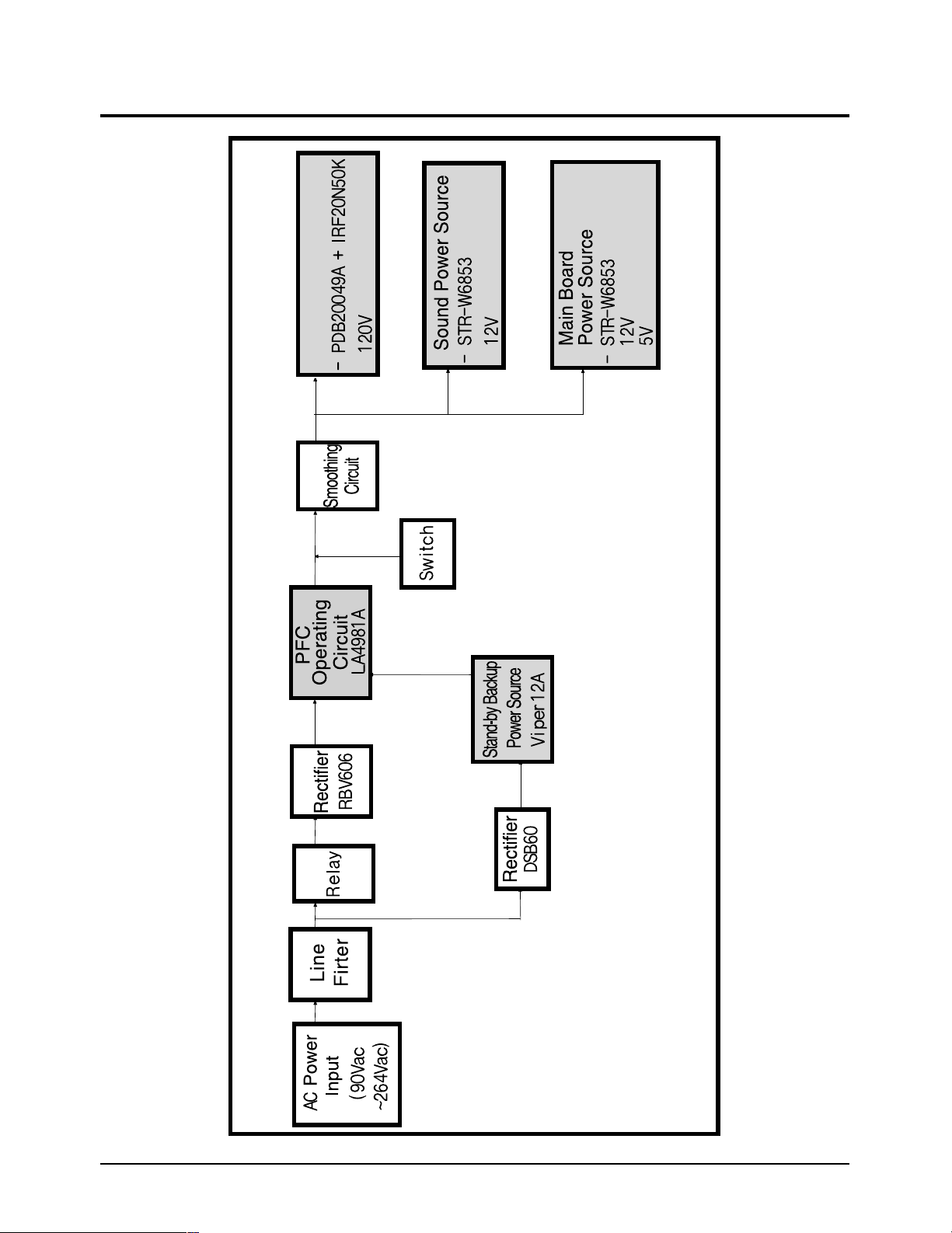

LCD-TV 32”, 40” Power Block diagram

Block Diagrams

LW32A23W/LW40A23W

Inverter Power Source

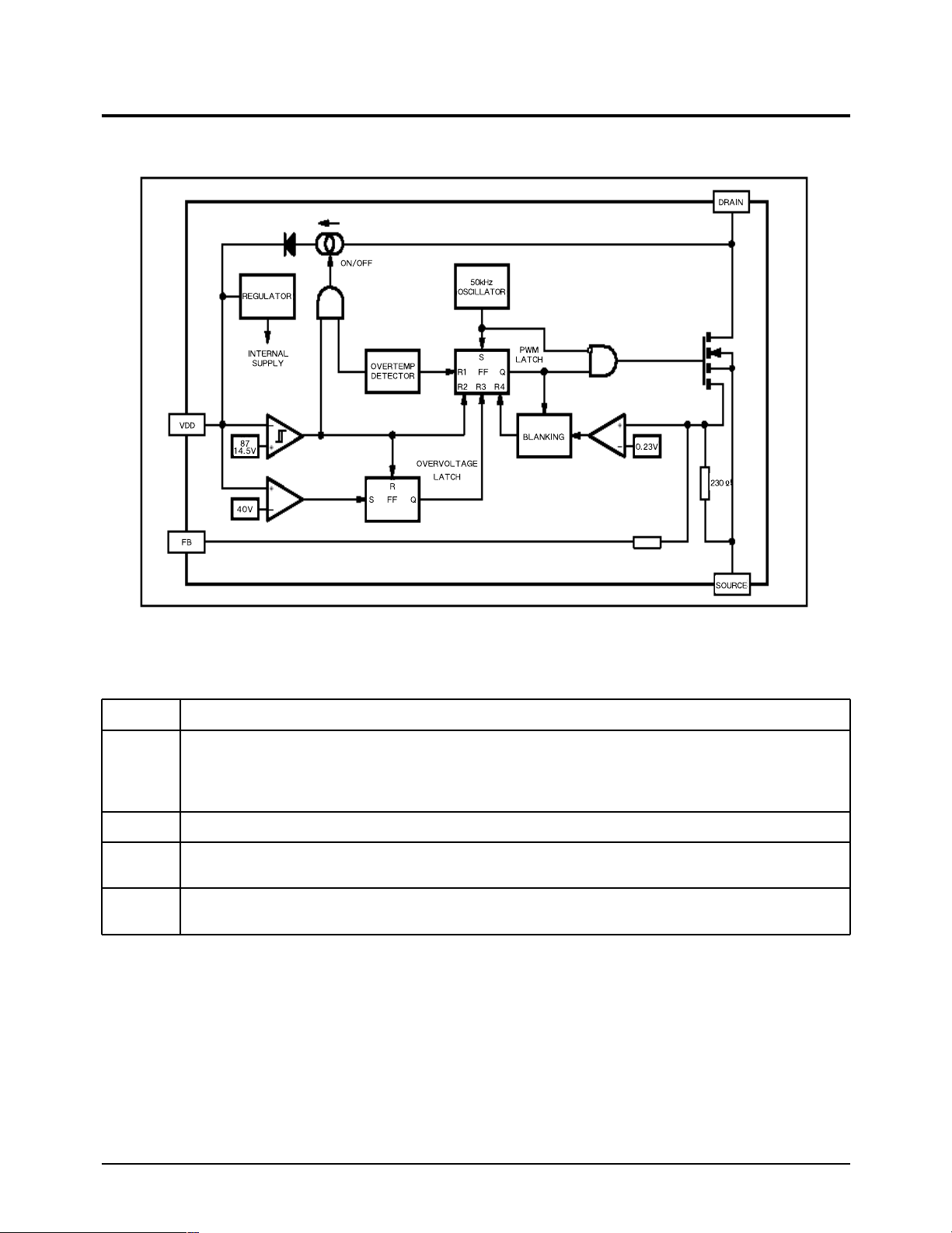

Page 7

function

For supplying power to the control circuit,dividing the charged current of the high-voltage current source connected to the drain

during startup,and comparing VDD voltage hysteresis.

Divided into two threshold voltages VDDon to start switching and to disconnect the startup current source (normally 14.5V), and

VDDoff to stop switching and to operate the startup current source (normally 8V)

Power MOSFET source and the circuit reference ground (GND)

Power MOSFET drain.Also used during startup as the internal high-voltage current source

until the external VDD capacitor is charged.

Feedback input.Operating voltage range of 0V ~1V.Determined by the maximum MOSFET current value.

The current limit in due consideration of the maximum drain current is included in the FB pin that is connected to the source pin.

Block Diagrams

LW32A23W/LW40A23W

Backup Power Source

Viper 12A Block Diagram

Pin Functions

Name

VDD

SOURCE

DRAIN

FB

Page 8

Block Diagrams

LW32A23W/LW40A23W

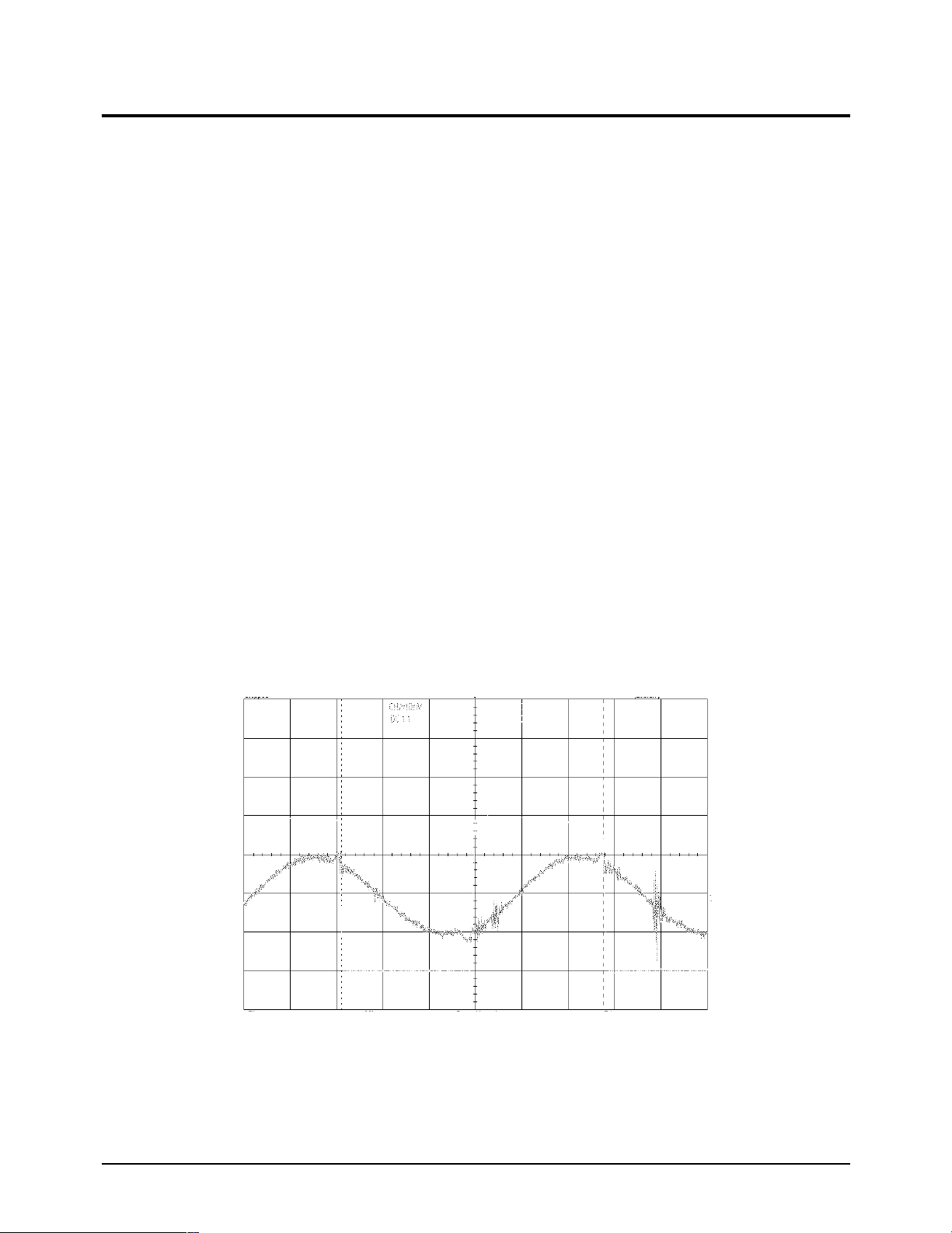

PFC Circuit

Operating Principles

As the stand-by power circuit starts oscillating,the control IC of the PFC circuit (L4981) is applied with Vcc

and starts oscillating. The oscillation frequency is determined by the resistance (RP824) connected to 17Pin

and the condenser (CP816) connected to 18Pin. For regulation,the output voltage is divided by resistors and

monitored by 14Pin. The 4Pin voltage, which is entered after dividing this voltage and the AC voltage by

resistors, is calculated in the IC and the command value of the main FET is prepared. Therefore, the output

voltage is controlled by the voltage determined by the dividing resistors, and the input current has the

same waveform (sine wave) as the AC voltage, producing a power factor of almost 100%.

Protections

1. Overvoltage

The circuit has an overvoltage protection function of the voltage limit type. In the event of a sudden

interruption of the input, of overshooting [overload?] during a sudden change of load,or non-control

status, this function protects the circuit by narrowing the ON width of the FET and preventing the

voltage from rising above the overvoltage setting. The overvoltage can be set with RP834, RP835, RP836

and RP840. (The power source is set to approximately 385V)

2. Overcurrent

The current is converted into the voltage value through RP831 and RP832,and monitored by 2 Pin and 8

Pin of the control IC. If the voltage of the detecting resistor rises above the set value due to an increase in

current, the pulse width is narrowed to limit the output.

3. Thermal Shutdown

Although the IC has a thermal shutdown function, a thermistor (TH) is installed on the heat-radiating fin

of the main FET and the circuit is stopped if overheated by overload, etc.

FET VDS Waveform (Input of 100V) FET VDS Waveform (Input of 230V)

Page 9

Block Diagrams

LW32A23W/LW40A23W

Resonance Circuit (Power Source for Inverter)

Operating Principles

Explains the circuit of the power source for the inverter. With the operation of the MULTI block, a voltage is

generated in the ancillary windings (4-5Pin) of T804S and is applied to 1 Pin (Vcc terminal) of the resonance

circuit to start oscillation. High side FET (Q4) and low side FET (Q5) are turned on alternately, delivering

energy to the secondary circuit. For voltage regulation, the output voltage is divided along resistors and

monitored by the transistor (QI809), and the photo coupler (PC801S) is turned on or off. If the output ,

voltage rises, PC801S is turned on and draws current from 13 Pin of the resonance circuit. The switching

frequency then increases, reducing the charge period of the resonance condenser (CI811) and thereby

limiting the output voltage. On the other hand , if the output voltage decreases, no current is drawn from

13 Pin of the resonance circuit and the switching frequency decreases, extending the charge period of the

resonance condenser and thereby raising the output voltage.

Protections

1. Overvoltage

The output voltage is divided along the resistors and monitored by QI810. If the output voltage rises, the

QI810 voltage also rises, which triggers QO810 to turn PC802S on. This will increase the voltage at 5 Pin

of the resonance IC, which stops oscillation in the latch mode.

2. Overcurrent

The current flowing in the resonance condenser (CI811) is divided through CI808, converted into voltage

at the resistors (RI809, RI816) and is monitored by 3 Pin of theresonance IC. If the output current rises,

the current in the primary winding wire also rises, which triggers the voltage at 3 Pin of the IC to rise as

well. If the voltage exceeds the set value, the pulse width is narrowed to limit the current.

3. Thermal Shutdown

The resonance IC has a built-in thermal shutdown function and stops oscillation at over 125 ˚C

FET VDS Waveform of the resonance circuit

Page 10

Block Diagrams

LW32A23W/LW40A23W

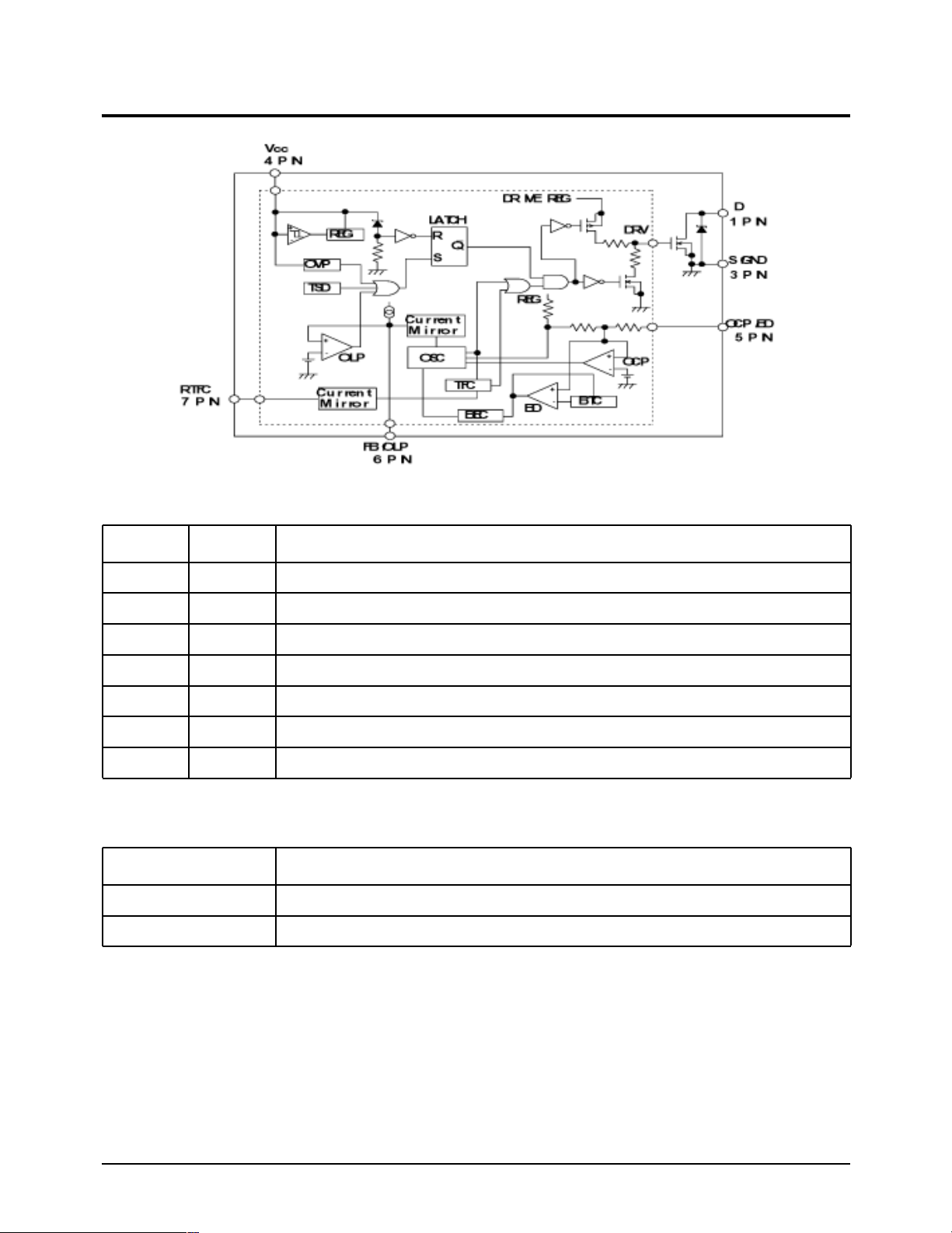

Main Board Supply &Sound Exclusive IC of STR-W6853

Outlines

1. A new 7 Pin package has been developed from the existing 5 Pin package. High-power MOSFET is

embedded in a small package to save space.

2. The distance between the pins of MOSFET drain & source has been widened to 1.8mm where high

voltage is applied,allowing the loading of high anti-pressure MOSFET.

3. The operation mode changes in 3 stages according to the load applied, and saves power consumption.

TFC, MBS, and pseudo-oscillation are available.

Features

1. Improvement of power efficiency through automatic conversion of operation modes the controlling MIC

part saves power consumption through a BCD processor. W6800 series changes the operation mode in 3

stages according to the load applied and saves power consumption.

1) Pseudo-oscillation under load

2) If MBS (Multi, Bottom, Skip) frequency exceeds 70 kHz under medium or small loads, the bottom is

skipped while bottom, ON is maintained.

3) If TFC (Time, Fix, Control)operation extends the ON time forcibly under St-By load, the OFF time is

controlled to lower the oscillating frequency. In the event of compulsory ON, control by external

resistors is possible.

2. Major Features

1) Embedded overcurrent protection (OCP) of pulse by pulse

2) Embedded overload protection (OLP) of latch shut down.

3) Embedded thermal shutdown function.

4) Embedded overvoltage protection for input voltage

5) Adjustable frequency for TFC operation

Page 11

Block Diagrams

LW32A23W/LW40A23W

Block Diagram

Terminal Functions

Other Functions

Terminal

Number

Symbol Name and Functions

1

2

3

4

5

6

7

D

NC

S/GND

Vcc

OCD/BD

FB/OLP

RTFC

MOSFET Drain terminal

Not Connect

MOSFET Source / Ground terminal

Control circuit power input terminal

Overcurrent detection signal input terminal / Bottom detection signal input terminal

Voltage control signal input terminal / Overload protection detection terminal

Fixed ON time adjustment terminal

Symbol Functions

TSD

OVP

Thermal Shutdown Circuit

Overvoltage circuit

Page 12

Block Diagrams

LW32A23W/LW40A23W

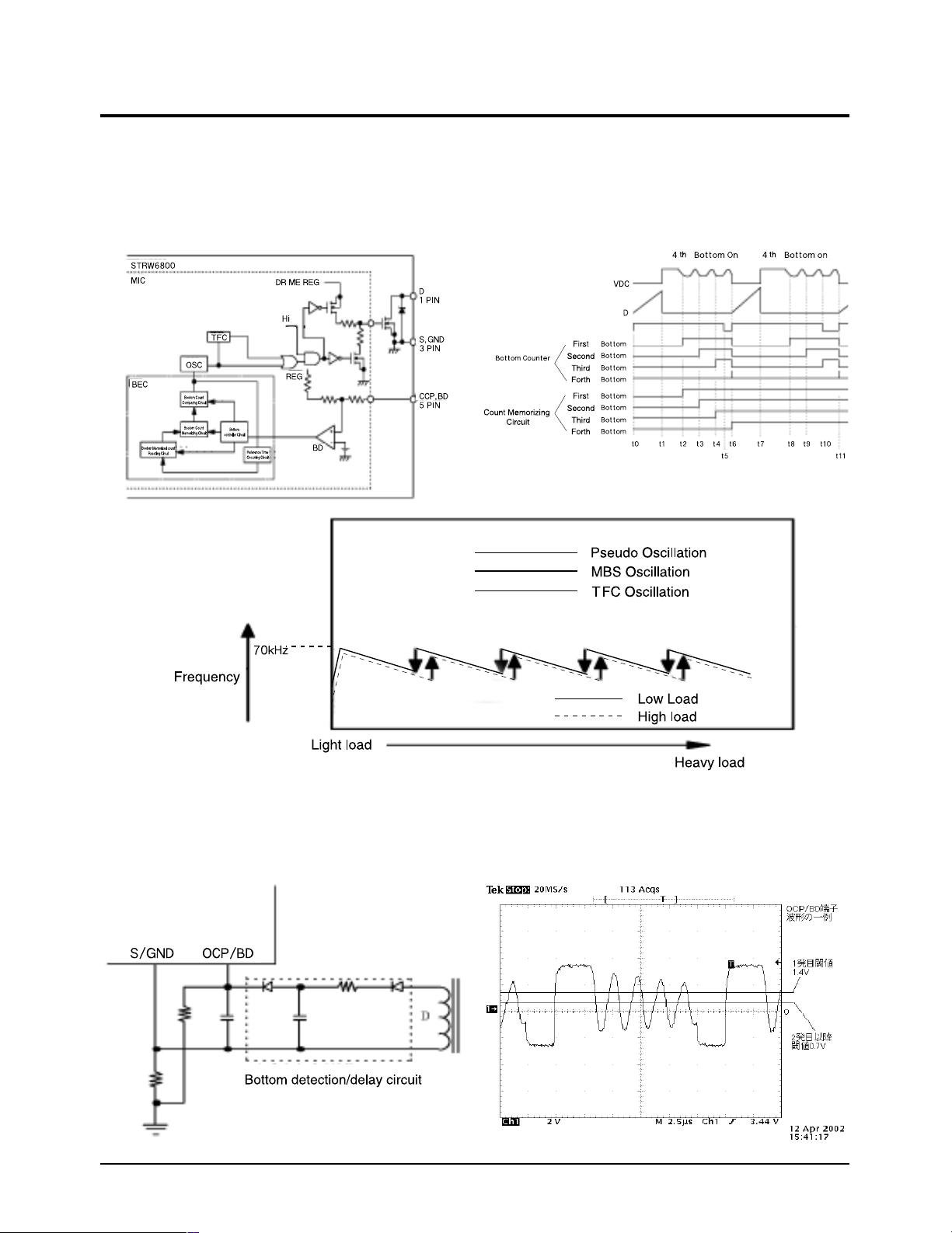

Operation of W6853

Outlines

1. MBS : Multi bottom skip (medium load area)

The circuit has the PWM reference time T=14uS, 70 kHz internally and is designed to turn on at a bottom

less than 14uS.

Note : MBS operations should not be counted in the overload, overcurrent area. (Bottom is not extended)

If the overload condition continues, OLP will be triggered to shut down the operation. Normally ,it

is not counted during startup, and if the down edge is detected only once after a count of 2, it is

considered abnormal and the oscillation is stopped.

Sub circuit

MIC internal reference time

On at a Bottom after the Reference Time that starts with ON.

On with the Bottom Count same as memorizing circuit.

Circuit

Page 13

Block Diagrams

LW32A23W/LW40A23W

2. TFC : Time fix controller (Lighter load area during stand-by) TFC operation forcibly outputs to DRV an

ON time (T2) that is longer than the fixed Ton (T1) inside the MIC to control the OFF time for stabilizing

the output voltage. If MBS operation under light load moves toward the light load area again, the MBS

operation is released at Ton=350 us and shifted to the TFS operation.

3. OLP

Page 14

Block Diagrams

LW32A23W/LW40A23W

4. Vcc Terminal,Startup Circuit

Startup is performed by the startup resistor and the condenser between Vcc and S/GND.

The startup voltage, Vcc is 18.2V (typ)and starts the circuit by charging C2 from the startup resistor.

After startup, operation continues with power supplied from the transistor drive winding wire .

(Near the drive winding wire and stand-by power source;Startup of Vcc)

Startup resistor

Peck charge

prevention resistor

5. OCP / OLP

From the transistor design, under medium load with only one bottom left,it is possible for Id to exceed

50%of the normal pseudo oscillation duty.In particular,if there is still a bottom under the maximum load at

VinAC (Min), confirming the condition is required. The following is an explanation of the pseudo

oscillation signal input of the OCP/BD terminal.

Page 15

Block Diagrams

LW32A23W/LW40A23W

6. RTFC Terminal

Adjustment should be performed while checking the actual operation in the range of 100k to 1 M.During

an IC examination, you may sometimes find minimum oscillating frequency at the RTFC resistor, but as

the secondary circuit performs feedback control, Id determined by ton at RTFC shows changes in the

peak value due to the primary inductance lp of the transistor and the winding ratio. If the load

consumed by the secondary circuit is constant, the peak value of Id increases and the frequency

decreases as lp becomes smaller and the ton setting becomes larger.

7. Phase Correction

When you have an unusual type of secondary feedback circuit and

load specifications, if the phase correction of the error amp on the

secondary circuit is not sufficient, due to the capacity of the

smoothing input condenser being too small and the ripple voltage

being too high, you can get a good result by adding a condenser

between the FB/OLP terminal of W6800 and S/GND. The FB/OLP

terminal is fitted with latch delay CR.If R is small, it may improve

the shift start during startup,but may also cause extreme delay.

Therefore ,care should be taken to avoid excessive response in

changing the loads.

Page 16

LW32A23W/LW40A23W

SW_SMPS

GND

STD_VCCGA

AGND

CH+_OUT

VOL+_OUT

BUZER_IN

AGND

CH-_OUT

VOL-_OUT

SOURCE_OUT

AGND

STD_VCC3B

VCC5B

AGNDIRLED_GRN

LED_RED

AGND

AV_CVBS

AGND

SVHS_Y

MENU_OUT

AGND

STD_VCC5B

VCC5DDC

AGND

SVHS_C

AGND

SC1_RGB_FB

CN800

GND_AMP

HP_IDENT

GND_AMP

HP_OUT_L

GND_AMP

HP_OUT_R

GND_AMP

WOOFER_OUT

GND_AMP

MAIN_L_OUT1

MAIN_L_OUT2

MAIN_R_OUT1

MAIN_R_OUT2

GND_AMP

SUR_L_OUT1

SUR_L_OUT2

GND_AMP

SUR_R_OUT1

SUR_R_OUT2

GND_AMP

CENTER_OUT1

CENTER_OUT2

GND_AMP

GND_AMP

CN510

VCC5I

VCC5P

VCC5P

VCC5P

VCC5P

GND_PANEL

GND_PANEL

GND_PANEL

PANEL_Y_DEC

PANEL_Y_INC

SW_ACCE

GND_PANEL

TXOUT 3+

TXOUT 3-

GND_PANEL

TXCLKOUT+

TXCLKOUT-

GND_PANEL

TXOUT 2+

TXOUT 2-

VCC12A

GND

VCC5A

VCC5A

VCC5A

GND

GND

GND

VCC12BS

VCC12BS

VCC12BS

GND_AMP

GND_AMP

GND_AMP

GND_PANEL

TXOUT 1+

TXOUT 1-

GND_PANEL

TXOUT 0+

TXOUT 0-

GND_PANEL

SW_INVERTER

ANA_DIMMING

PWM_DIMMING

CN505

SC1_R_SC1_SVHS_CI

SC1_G

SC1_B_SC1_SVHS_C0

AGND

SC1_CVBS_IN

AGND

SC1_CVBS_OUT

AGND

SC2_CVBS_IN

AGND

SC2_SVHS_CI

AGND

Y_D1

AGND

PB_D1

PR_D1

AGND

Y_D2

AGND

PB_D2

PR_D2

AGND

AGND

SC2_CVBS_OUT

ANGD

SC2_SVHS_CO

Y_COMP1

AGND

PB_COMP1

PR_COMP1

CN506

Y_COMP2

AGND

PB_COMP2

PR_COMP2

D4_1_CON1

D4_1_CONT2(SC1_S)

D4_1_CONT3

D4_2_CONT1

D4_2_CONT2(SC2_S)

D4_2_CONT3

AV_L

AGND

SC1_L_OUT

SC1_R_OUT

AGND

SC2_L_IN

SC2_R_IN

AGND

SC2_L_OUT

SC2_R_OUT

AGND

COMP1_L

AV_R

GND

SC1_L_IN

SC1_R_IN

COMP1_R

AGND

COMP2_L

COMP2_R

CN509

PC_L

PC_R

AGND

COAXIAL_IN

AGND

OPTICAL_IN

AGND

PC_RED

PC_GREEN

PC_BLUE

AGND

DDC_DVI_SDAS

IDENT_PC

RX0-

RX0+

DGND

RX1-

RX1+

DGND

RX2-

RX2+

DGND

PC_DDC_HSYNC

PC_DDC_VSYNC

AGND

DDC_DVI_SCLS

RXC-

RXC+

DGND

DDC_VCC5D

CN507 CN508

Wiring Diagram

Page 17

LW32A23W/LW40A23W

AGND

AGND AGND

GND

OUT8

VCCOUT1

OUT2

OUT3

OUT4

OUT7

OUT6

OUT5

IN6

VCCP

IN1

SDA

IN2

GND

OUT8

VCC

OUT1

OUT2

OUT3

OUT4

OUT7

OUT6

OUT5

IN6

VCCP

IN1

SDA

IN2

SCL

IN3

IN5

SUB

IN4

COMP_9883_PR

COMP_9883_PB

COMP_99883_Y

COMP_9883_PB

COMP_99883_Y

COMP_9883_PR

PRY

PB

SCL1

SDA1

3230_DCLK

OUT1

OUT2

OUT3

OUT4

OUT7

OUT6

OUT5

IN6

VCCP

IN1

SDA

IN2

SCL

IN3

IN5

SUB

IN4

GND

OUT8

VCC

PIN

PIN

PIN

PIN

PIN

23

66

94

110

140

3.3V

PIN

PIN

PIN

SCL

IN3

IN5

SUB

IN4

9883A_VSYNC

9883A_HSYNC

9883A_COAST

SC2_CVBS_IN

SC1_CVBS_IN

DPTV_CVBS

3230C(0:7)

3230Y(0:7)

3230C(0:7)

3230Y(0:7)

3230C(0:7)

3230C(0:7)

OPTION

10uF

3230Y(0:7)

DPTV_SVHS_C

DPTV_SVHS_C

DPTV_CVBS

DPTV_CVBS

DPTV_SVHS_Y

DPTV_SVHS_Y

3230_SVHS_C

3230_SVHS_Y

3230_VS

3230_HS

3230_VS

3230_HS

DPTV_CR

DPTV_Y

DPTV_CB

V_SYNC

H_SYNC

PIN

PIN

52

80

125

156

174

2.5V

10uF

C740

C738

10uF

C736

10uF

10uF

C737

C735

C733

10uF

MO

1/16W

10K

R9484

R9483

16V

100nF

C8304

R9482

75

R9481

75

R9471

75

R9475

180

4.7K

1/16W

1/16W

1K

B

Q907

E

C

B

KSA1182

GND_9883

R9474

VCC3D_DPTV

FT940

C

3

2

1

A

LFB30-3A1E223M

75

75

R279

C2187

220nFC2181

10pF

R281

R2827575

C2185

10pF

R280

10pF

C2184

220nF

10pF

C2183

220nF

C2180

R271

C2182

R9451

75

R288

75

75

R286

7575R275

75R276

3

21

D718

D715

3

21

D717

D714

3

21

D716

1

MMBD4148SE

D713

3

21

MMBD4148SE

3

21

MMBD4148SE

D712

3

2

3

21

MMBD4148SE

D711

3

21

MMBD4148SE

D710

3

21

MMBD4148SE

R9450

100

1/16W

R284

5.1K

5.1K

R283

R265

22

4.7K

22

R237

R239

VCC5C

C2167

R238

22

100nF

3.3K

R260

470

C2170

10uF

16V

R261

50V

1uF

C2169

3.3K

R263

R264

470

3.3K

FT210

3

R258

R259

470

C2168

C

B

2

1

A

LFB30-3A1E223M

R262

IC205

100nF

GS1881-CKA

680K

1.5nF

8

7

6

5

4

3

2

1

C229

C204

C233

1.5nF

1.5nF

1.5nF

C220

C224

1.5nF

1

T230

C253

100nF

RA204

8765432

1

3

2

1

SUPLECODE

SUPLECODE

RA205

876

87654

432

1

SUPLECODE

RA206

RA207

87654352

1

SUPLECODE

L200

B

2

3.3UH

FT205

3

C

B

21

A

LFB30-3A1E223M

FT206

3

C

220nF

A

1

LFB30-3A1E223M

100nF

C741

R255

C722

220nF

10K

C721

10

100

R746

R207

100R745

20K

R743

1/16W

10K

R744

R741

R742 4.7K

4.7K

4.7K

R739

R740

4.7K

4.7KR737

VCC8B

R738 4.7K

LFB30-3A1E223M

C

3

2

B

A

1

FT712

16V

47uF

C732

C739

C742

220nF

TEA6425D

100nF

19

S

R

18

Q

17

P

16

O

15

14

N

12

L

11

K10J

9

I

8

H

7

G

6

20

T

R726

F

5

E

4

D

3

C

2

B

1

A

IC702

VCC3A_DPTV

13

M

7

6

4.7K

1

RA209

88

7

6

5

4

35

4

3

2

1

RA208

8765432

1

RA211

2

8

100nF

765

432

1

RA210

C265

100nF

C261

100nF

C263C262 C264

100nF

C2160

1uF

50V

100nF

C2157

1uF

50V

50V

1uF

C2156

3.3UH

L201

47R253

R254

16V

100uF

22

22

16V

100uF

R256

10nF

C2149

33pF

C2152

100nF

C2148

C2138C2133

C2144

C2139

C2143

100nF

33pF

C2137

33pF33pF

100nF100nF

C2136C2135

C2142

100nF

C2141

33pF33pF

100nF

C2134

C2145

100nF

100nF

C2140

C2151

C2162

100nF

100nF

C2153

C2165

C2154

100nF

16V

100nF

C2132

100

C2163

100nF

R251

100

100uF

R252

1nF

C2155

C2161

100nF

C2159

100nF

100nF

C2158

R250

10K

C2146

R248

3.3K

39nF

C2147

10K

3.9nF

100nF

C2150

R249

23

22

VDD2

11

100nF

C2164

VD10

62

26

VD1

65

MST9883A-110

31

VSYNC

64

VSOUT

VDD6

79

78

VDD5

69

VDD4

VDD3

74

RED3

75

RED2

VDD1

59

VD9

52

VD851VD746VD6

VD5

45

42

VD4

39

VD3

27

VD2

2

3

GREEN6

4

SOGOUT

49

SOGIN57SDA56SCL58REF_BYPASS

70

RED7

71

RED6

72

RED5

RED4

73

GND6

25

24

GND5

21

76

RED1

77

RED0

54

RAIN

35

PVD2

34

PVD1

MIDSCV

37

30

HSYNC

66

HSOUT

GREEN7

50

GND1447GND13

GREEN55GREEN46GREEN37GREEN28GREEN1

GREEN0

9

36

GND9

32

GND8

28

GND7

CLAMP

38

12

BLUE7

GND4

20

GND3

80

GND20

10

GND2

68

GND19

63

GND18

61

GND17

60

GND16

GND15

53

BLUE317BLUE2

BLUE1

18

44

GND1241GND11

40

GND10

1

GND1

48

GAIN

FILT

33

67

DATACK

29

COAST

A0

IC202

R708

4.7K

13

BLUE614BLUE515BLUE4

16

16V

10uF

19

BLUE0

43

BAIN

55

C709

R725 4.7K

4.7KR724

4.7KR723

R722 4.7K

16V

10uF

C720

C717

10uF

16V

16V

10uF

C716

C715

10uF

16V

16V

10uF

C719

C718

10uF

16V

4.7KR721

R719

R720 100

100

2

B

A

1

FT711

VCC8B

C723

47uF

16V

N

IC701

C

3

T

20

S

19

18

R

17

Q

16

P

15

O

14

M

13

L

12

K11J

10

I

9

H

8

G

7

C205_OP

F

6

E

5

D

4

C

3

B

2

A

1

TEA6425D

10pF

1/16W

100

10pF

R202

R201

C206_OP

R220

100

100

1/16W

R701

R700

47

100

C240

33pF33pF

C239C238

33pF

33pF

C256 C260

33pF33pF

C259C257

C231

33pF

100

33pF

C258

R236

R235

100nF

100

75

R230

R229

75

75

R228

R227

75

75

R226

R225

75

3

C

B

2

1

A

C2120

10uF

16V

3

C

B

2

A

1

C235

FT201

16V

FT200

100nF

1

SUPLECODE

RA202

8

C234

10uF

876

57

65432

1

SUPLECODE

RA203

8

7

6

5

4

3

2

432

1

RA201

SUPLECODE

SUPLECODE

C207

8

7

6

5

4

3

2

1

RA200

680NF

4.7K

680NF

C214

R706

4.7K

R705

R715

R707

4.7K

R716

R714

22

22

22K

R710

22K

12K

22uF

R711

12K

R709

16V

16V

47uF

C711

C710

22uF

16V

VCC5C

75

C700

R718

Q701

3

C

B

2

1

A

FT710

E

C

B

2SC2412K-Q

C712

100pF

1K

R717

R702

4.7K

C706

10uF

16V

2SC2412K-Q

VCC5C

R712

Q700

VCC8B

75

C705

C704

10uF

16V

E

C

B

16V

10uF

16V

10uF

C703

C702

10uF

16V

R704

4.7K

TEA6425D

20

T

19

S

16V

10uF

C701

O

15

14

N

13

M

12

L

11

K

H

7

G

6

F

5

E

4

D

3

CR

18

Q

17

P

16

IC700

100pF

10

J

9

I

8

C714

R713

2

B

1

A

1K

4.7K

R703

C754

220nF

220nF

C707

22

R200

C226

0.39nF

C223

47nF

C227

10uF

16V

220nF

680NF

C222

C225

C221

220nF

C219

0.39nF

47nF

C217

C210

16V

10uF

C218

4.7pF

C213

10uF

16V

C211

VCC5C

C203

47nF

4.7pF

68nF

C202

C200

68nF

VCC3D_DPTV

68nF

C201

R206

47nF

C232

R204

0.39nF

C228

100

R205

C230

100

220nF

100

IC201

18

YCOEQ

31

Y7

Y633Y5

Y4

34

37

Y3

Y2

38

39

Y1

Y0

40

XTAL2

63 62

XTAL1

VSUPY

36

52

VSUPSY

26

29

VSUPLLC

69

VSUPF

10

VSUPD

9

VSUPCAP

VSUPC

45

VSUPAI

76

VSTBY

59

VS

57

VRT

66

VREF

32

27

LLC2

LLC1

78

VOUT

70

75

VIN4

VIN3

74

73

VIN2

VIN1

72

17

VGAV

16

TEST

14

SDA

13

VSUPPA

GNDPA

GNDLLC

30

65

GNDF

11

GNDD

12

SCL

15

RESQ

6

R2

3

R1

NC_2

61

8

NC_1

56

MSY

G2

2

G1

FSY

5558

FPDAT

20

FFWE

28

ISGND

68

INTLC

53

67

I2CSEL

35

GNDY

GNDSY

51

25

B2

21

FFRSTW

22

FFRE

23

FFOE

19

FFIE

79

FB1IN

60

CLK5

24

CLK20

GNDCAP

46

GNDC

77

GNDAI

5

71

CIN

C7

4142

C6

C5

4344

C4

C3

4748

C2

C1

4950

C0

41

B1

54

AVO

64

ASGF_2

7

ASGF_1

AISGND

80

VPC3230D-C5

HC-49/SM5H(20.25MHz)

Q1

Q0

X201

1

C212

100nF

10K

1

T204

R224

T203

1

T202

T201

C286

22uF

1

16V

100nF

VCC3D_DPTV

C280

C281

100nF

100nF

C284

C282

C283

100nF100nF

100nF

C

3

2

B

A

1

FT207

C285

100nF

100nF

C275

C274

C276

100nF

100nF

C277

R247

C278

100nF

100nF

C279

K4S643232E-TC60

33

84

VSSQ8

78

VSSQ7

VSSQ6

52

46

VSSQ5

VSSQ4

38

32

VSSQ3

12

VSSQ2

VSSQ1

6

86

VSS4

VSS3

72

58

VSS1

44

81

VDDQ8

75

VDDQ7

VDDQ6

55

49

VDDQ5

VDDQ4

41

35

VDDQ3

VDDQ2

9

3

VDDQ1

VDD4

17

WE_

DQM1

71

DQ9

76

43

29

VDD3

VDD2

15

VDD1

1

RAS_

19

N_C7

73

N_C6

70

N_C5

69

N_C4

VSS2

7

DQ3

53

DQ29

DQ28

51

50

DQ27

57

N_C3

30

N_C2

21

14

N_C1

16

DQMO

DQM3

5928

DQM2

37

DQ2

5

36

DQ19

DQ18

34

33

DQ8

7413

DQ7

11

DQ6

10

DQ5

DQ4

8

DQ31

56

DQ30

54

DQ10

77

DQ1

4

DQ0

2

CS_

20

48

DQ26

DQ25

47

DQ24

45

DQ23

42

DQ22

40

DQ21

39

DQ20

A7

64

63

A6

62

A5

61

A4

DQ17

31

DQ16

DQ15

85

83

DQ14

82

DQ13

80

DQ12

79

DQ11

22uF

16V

68

CLK

67

CKE

18

CAS_

BA1

23

BA0

22

66

A9

65

A8

C273

60

A3A2

27

A10

24

A1

26

A0

25

IC204

C271

100nF

C270

100nF

C269C268

100nF100nF 100nF100nF

C267C266

17

WE_

84

VSSQ8

78

VSSQ7

VSSQ6

52

46

VSSQ5

VSSQ2

VSSQ1

6

86

VSS4

VSS3

72

VSS2

58

44

VSS1

81

VDDQ8

VDDQ7

75

K4S643232E-TC60

35

VDDQ3

VDDQ2

9

3

VDDQ1

43

VDD4

29

VDD3

VDD2

15

VDD1

1

RAS_

19

VSSQ4

38

32

VSSQ3

12

10

DQ5

DQ4

8

N_C7

73

N_C6

70

N_C5

69

N_C4

5730

N_C3

N_C2

21

VDDQ6

55

49

VDDQ5

VDDQ4

41

DQ24

42

DQ23

DQ22

14

N_C1

DQMO

16

DQM3

5928

DQM2

71

DQM1

DQ9

76

74

DQ8

13

DQ7

11

DQ6

83

DQ14

82

DQ13

56

DQ31

DQ30

54

DQ3

7

DQ29

53

DQ28

51

50

DQ27

DQ26

48

47

DQ25

45

23

BA1

BA0

22

40

DQ21

39

DQ20

37

DQ2

5

36

DQ19

34

DQ18

33

DQ17

DQ16

31

DQ15

85

24

A1

26

25

80

DQ12

79

DQ11

DQ10

77

DQ1

4

2

DQ0

CS_

20

CLK

68

CKE

67

18

CAS_

A9

66

65

A8

64

A7

63

A6

62

A5

61

A4

60

A3A2

27

A10

100nF

A0

IC203

VCC3D_DPTV

3

C

B

2

A

1

FT204

R215 100

C272

100

1

T200

R214

3.3UHL204

47pF

C2126

47pF

C2125

C2129

47uF

16V

33pF

C2118

33pF

1/16W

4.7K

33pF

C237

C236

R223

C251

R241

22

100nF

VCC3A_DPTV

LFB30-3A1E223M

22

C

3

2

B

A

1

FT203

R240

16V

47uF

C

3

2

BA

1

FT202

C2166

47uF

16V

R245

C241

3333R246

R244

16V

22uF

33

C296

C2119

100nF

R221 100

C250 100nF

16V

22uF

C2116

16V

22uF

C2105

C297

22uF

16V

3.3UH

3.3UHL202

L207

3.3UH

100nF

L205

C287

C2117

100nF100nF

HC-49/S-SMD(14.31818MHZ)

Q1

Q0

X200

3.3UH

C288

L208

C289

22uF

16V

VCC2.5D_DPTV

C292

3.3UH

L209

16V

1nF

C290

22uF

C291

16V

100uF

C2123

100nF

1nF

C2124

C2101

22uF

16V

22uF

C2110

C299

22uF

16V

C29522uF 16V

16V

100pF

C249

C2115

100nF

VCC5C

1uF

C252

22uF

1uF

C2113

C2112

C2114

22uF

C2109

100nF

C2108

100uF

3.3UH

L206

100nF

C2111

C2107

100pF

C2106

100nF

100nF

100nF

C2103

100nF

C2104

VCC3A_DPTV

C2102

L203

VCC2.5D_DPTV

R210

10K

3.3UH

C2100

100nF

100nF

C298

100nF

C255

100

R234

R218

22

100

R290

100

C293

R233

20pF

20pF

VCC3D_DPTV

VCC2.5D_DPTV

C294

C242

100nF

100nF

C243

C244

100nF

C245

100nF

33

C247

R243

C246

C248

100nF

100nF

100nF

R231

33

75

R232

R242

VSYNC

35

VSS9

155

VSS8

141

126

DPTV-3D-6830-C

390

VSS10

173

24

VSS1

VPROT

37

26

VM

VLF

XTLO

164

XTLI

163

WR

176

WE

101

40

VSYNCPIP

43

VSYNCMP

140

VDD5

110

VDD4

94

VDD3

66

VDD2

VSS7

VSS6

111

95

VSS5

VSS4

81

67

VSS3

VSS2

53

193

VSS11

RT2

RT1

202

RESET

5

RD

177

RB2

204

161

192

VDD_ADC

174

VDDC5

156

VDDC4

VDDC3

125

80

VDDC2

52

VDDC1

MD9

MD8

79

82

MD7

154

MD63

MD62

153

152

VDD1

23

V5SF

1

2

TEST

SD

178

SC

179

203

147

146

MD55

MD54

145

144

MD53

MD52

143

142

201

RB1

99

RAS

R

27

6

PS

MLF

158

78

MD46

135

134

MD45

MD44

133

132

MD43

MD42

131

MD61

151

MD60

MD6

83

150

MD59

MD58

149

148

MD57

MD56

MD37

MD36

123

122

MD35

MD34

121

120

MD33

MD32

MD51

139

MD50

84

MD5

138

MD49

137

MD48

136

MD47

MD27

MD26

59

60

MD25

MD24

61

62

MD23

MD22

130

MD41

MD40

129

MD4

85

128

MD39

127

MD38

124

70

MD17

MD16

71

72

MD15

MD14

73

74

MD13

119

54

MD31

MD30

55

86

MD3

56

MD29

MD28

57

58

MCLK

MA9

113

112

MA8

MA7

109

108

MA6

MA5

63

MD21

64

MD20

65

MD2

87

MD19

68

MD18

69

31

INT2

3

180

INT

HSYNCPIP

39

HSYNCMP

42

34

MD12

75

76

MD11

MD10

77

88

MD1

89

MD0

96

DQM4

115

DQM3

93

92

DQM2

DQM1

91

90

DQM0

107

MA4

106

MA3

105

104

MA2

MA1

103

102

MA0

IRSET

185

CVBS3

CVBS2

184

183

CVBS1

98

CS1

CS0

HSYNC

36

HFLB

28

G

118

DQM7

117

DQM6

116

DQM5

CLKPIP

41

CLKMP

CCLP3

208

198

CCLP2

187

CCLP1

207

CB

100

CAS

CAPD9

21

CVBS_OUT2

189

188

CVBS_OUT1

CVBS4

186

CAPD6

45

46

CAPD5

CAPD4

47

48

CAPD3

CAPD23

7

8

CAPD22

CAPD21

9

10

CAPD20

CAPD2

49

97

197

CR

38

CAPD18

CAPD17

13

14

CAPD16

CAPD1515CAPD1416CAPD13

17

18

CAPD12

CAPD11

19

20

CAPD10

50

22

CAPD8

44

CAPD7

C

196

114

BA

B

29

AVSS_1

25

AVSSA5

206

200

AVSSA4

195

AVSSA3

191

AVSSA2

AVSSA1

182

CAPD19

11

12

AVSS2

AVSS1

159

AVSS

30

AVDDA5

205

199

AVDDA4

AVDDA3

194

AVDDA2

190

AVDDA1

181

162

AVDD2

AVDD1

CAPD1

CAPD0

51

175

ALE

4

ADDRSEL

AD7

165

166

AD6

AD5

167

168

AD4

AD3

169

170

AD2

AD1

AVSS3

33

160

PPMM_VS_PIP

PPMM_HS_PIP

PPMM_DFCLK

AGND

AGND

AGND

DG_DPTV GND_9883

DG_DPTVGND_3230 AG_DPTVAGND

AG_DPTV

GND_9883

171

172

AD0

IC200

SC1_RGB_FB

GND_3230

SC1_G

SC1_B_SC1_SVHS_CO

SC1_R_SC1_SVHS_CI

157

32

AVDD

3230C(1)

COMP1_PB

COMP1_Y

COMP_PPMM_Y

COMP_PPMM_PB

AGND

COMP2_PR

COMP2_PB

COMP2_Y

COMP1_PR

CSYNC_DTV

SCL3

SDA3

AGND

AGND

AGND

AGND

GND_DPTV

GND_9883

AGND

AGND

AGND

AGND

3230Y(5)

3230Y(4)

3230C(3)

3230Y(3)

3230Y(2)

3230Y(1)

3230Y(0)

3230C(6)

3230C(7)

GND_9883

GND_9883

3230C(2)

3230C(3)

3230C(4)

3230C(5)

COMP_PPMM_PR

AGND

3230C(0)

SC2_SVHS_CI

GND_9883

GND_9883

GND_9883

GND_9883

GND_9883

GND_9883

DG_DPTV

GND_9883

3230C(6)

3230C(5)

3230C(4)

3230C(2)

3230C(1)

3230C(0)

3230C(7)

3230Y(7)

3230Y(6)

3230C(7)

3230C(5)

3230C(3)

AGND

3230_DCLK

SCL3

SDA3

DG_DPTVDGND

GND_3230

AGND

AGND

SC1_R_SC1_SVHS_CI

SVHS_C

SVHS_Y

GND_9883

SCL2

SDA2

CVBS_OUT

AG_DPTV

GND_3230

DPTV_FLD

DG_DPTV

GND_3230

3230Y(7)

AG_DPTV

DG_DPTVDG_PPMMDG_DPTV

3230C(6)

3230C(4)

DG_DPTV GND_DPTV

AG_DPTV

3230C(2)

3230C(1)

3230C(0)

GND_3230

DPTV_DCLK

GND_3230

GND_3230

GND_3230

GND_3230

GND_3230

GND_3230

GND_3230

GND_3230

SC1_CVBS_OUT

AGND

AGND

PIP_CVBS

SC1_CVBS_IN

TUNER_CVBS

SCL3

SDA3

AGND

SC2_CVBS_OUT

SC2_CVBS_IN

AV_CVBS

AGND

DPTV_DE

AGND

AGND

DG_DPTV

AG_DPTV

DG_DPTV

AG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

SCL1

SDA1

DG_DPTV

DG_DPTVGND_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

GND_DPTV

GND_3230

RST_3230

3230Y(4)

AG_DPTV

GND_DPTV

AG_DPTV

AG_DPTV

AG_DPTV

DPTV#31

DG_DPTV

AG_DPTV

DG_DPTV

AG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

DG_DPTV

RST_DPTV

DPTV_VS

DPTV_HS

AG_DPTV

MD(62)

MD(61)

MD(60)

MD(59)

3230Y(1)

3230Y(2)

3230Y(3)

3230Y(7)

3230Y(4)

3230Y(5)

3230Y(6)

3230Y(0)

3230Y(3)

3230Y(2)

3230Y(1)

3230Y(0)

GND_DPTV

AG_DPTV

3230Y(6)

3230Y(5)

MA(1)

MA(0)

MA(8)

MA(9)

MD(45)

MD(44)

MD(43)

MD(42)

MD(41)

MD(40)

MD(58)

MD(57)

MD(56)

MD(47)

MD(46)

MD(63)

MD(26)

MD(27)

MD(28)

MD(29)

MD(30)

MD(24)

MA(2)

MA(1)

MA(0)

MA(8)

MD(15)

MD(25)

MA(7)

MA(6)

MA(5)

MA(4)

MA(3)

MA(2)

DQMA(2)

DQMA(3)

MD(7)

MD(6)

MD(5)

MD(4)

MD(13)

MD(14)

MD(8)

DQMA(0)

DQMA(1)

MD(31)

MD(9)

MD(10)

MD(11)

MD(12)

MD(22)

MD(23)

MD(31)

MD(30)

MD(29)

MD(28)

MD(17)

MD(18)

MD(19)

MD(20)

MD(21)

MD(3)

MD(2)

MD(1)

MD(0)

MD(16)

MA(0)

MA(7)

MA(5)

MA(4)

MA(3)

MA(2)

MA(1)

MD(0:63)

MA(6)

MA(9)

MA(8)

MD(32)

MD(0:63)

MD(35)

MD(34)

MD(33)

DQMA(7)

DQMA(6)

DQMA(5)

DQMA(4)

MD(41)

MD(40)

MD(39)

MD(38)

MD(37)

MD(36)

MD(48)

MD(47)

MD(46)

MD(45)

MD(44)

MD(43)

MD(42)

MD(54)

MD(53)

MD(52)

MD(51)

MD(50)

MD(49)

MD(60)

MD(59)

MD(58)

MD(57)

MD(56)

MD(55)

DPTV_D_C

MD(63)

MD(62)

MD(61)

PAR(6)

PAR(1)

PAR(2)

PAR(3)

PAR(0)

DPTV_D_Y

PAR(7)

PAR(4)

PAR(5)

PAG(4)

PAG(5)

PAG(0)

PAG(1)

PAG(2)

MD(33)

MD(32)

PAG(6)

PAG(7)

PAG(3)

MD(39)

MD(38)

MD(37)

MD(36)

MD(35)

MD(34)

MD(52)

MD(51)

MD(50)

MD(49)

MD(48)

DQMA(0:3)

MD(55)

MD(54)

MD(53)

DQMA(5)

DQMA(3)

DQMA(2)

DQMA(1)

DQMA(7)

DQMA(6)

DQMA(4)

MA(7)

MA(6)

MA(5)

MA(4)

MA(3)

DQMA(0)

MD(4)

MD(3)

MD(2)

MD(1)

MD(0)

MA(9)

MD(11)

MD(10)

MD(9)

MD(8)

MD(7)

MD(6)

MD(5)

MD(17)

MD(16)

MD(15)

MD(14)

MD(13)

MD(12)

MD(23)

MD(22)

MD(21)

MD(20)

MD(19)

MD(18)

MD(27)

MD(26)

MD(25)

MD(24)

6

7

15

23

24

4

25

5

19

20

22

21

Schematic Diagrams

❈ This Document can not be used without Samsung’s authorization.

DPTV, VPC3230, MST 9883 Block Schematic Diagram

Page 18

Schematic Diagrams

4

CVBS Signal

20

IC202,#64,H-Sync Output Signal21IC202,#56 Communichion Data Signal22IC202,#57 Communichion Clock Signal23IC202,#30 H-Sync intput Signal24IC202,#31 V-Sync Intput Signal25IC202,#71~78, 2~10 Data Puls Signal

5

IC200,#3 Clock Signal

6

IC200,#178 Communichion Data Signal7IC200,#179 Communichion Clock Signal

19

IC202,#66,H-Sync Output Signal

15

S-Video signal,CN505,#26(Y),28(C),

IC701,#18(Y),19(C)

Page 19

DVI INTERFACE

R9240_M,R9241_M,R9242_M,R9243_M

FT916_M,FT918_M

Y_D2

Y_COMP2

PR_COMP2

R313_SIL161B

(VCC_14V)

EO MTTX OPTION

C8130_M,C8131_M,C8132_M,C8133_M,C8150_M,C8152_M

B TYPE (RECIEV)

OR SIL169

R316_SIL169

PB_COMP2

NO USE IN ASIA,USA

R305_SIL169

PR_D1

PB_D1

DDC_DVI_SCLS

DDC_DVI_SDAS

DDC_DVI_SCLS

DDC_DVI_SDAS

32bit

RF Input

PB_COMP1

PB_D2

Y_COMP1

PR_D2

PR_COMP1

RF Ant

Y_D1

DVI

Q906_M,Q907_M,Q908_M

DELETE THE PARTS IN BOX.

R304_SIL169

D805

BAT54A

12

3

R141

33K

7

6

D2

D2_1

5

2

G1

4

G2

S1

1

S2

3

20

21

GND3

GND4

22

SI9933ADY-T1

IC804

8

D1

D1_1

D

4

E

5

F

6

G

7

H

8

9

I

J

10

19

GND1

GND2

L

12

M

13

N

14

O

15

P

16

Q

17

18

R

C

3

VO2

4

CN126

SUPLVAL

A

1

B

2

K

11

GND_1

3

6

GND_2

5

N_F

2

VCC

VO1

1

100nF

C886

VCC5I

IC815

BA33B00FP

B

3

C

L913

1.5uH

STD_VCC6A

FT830

1

A

2

C320

100nF

T131

1

R816

10

T105

1

C801

100nF

1

A

2

B

3

C

1uF

C8122C8121

FT831

16V

100uF

C800

1uF

100uF

C881

100uF

16V

1

T259

1

C8127

R9472

4.7K

1/16W

T265

2N7002L

Q909

D

G

S

T106

1

T107

1

KSC1623-Y

Q100

B

C

E

220pF

C107

47nF

C108

L801

0.12nF

C846

16V

100uF

C326

100nF

C824

100nF

C823

1

T260

1

2N7002L

Q908

D

G

S

T261

33K

C119

1uF

T271

1

R140

C109

2.2nF

R101

22K

L802

N

R823

13K

1/10W

1

23

4

C8128

47uF

16V

1

23

4

L917

INSTPAR

T119

1

L916

INSTPAR

1

2

3

4

5

6

7

8

C179

100nF

4

5

6

7

8

RA310

22

22

1

2

3

ACM2012-361-2P

FT304

I1

1

I22O1

3

O2

4

RA311

ACM2012-361-2P

FT303

I1

1

I22O1

3

O2

4

R8304

1/16W

6.2K

R8303

1/16W

12K

R136

33K

FT100

A

1

B

2

C

3

1

100nF

C827

56K

T274

33K

R9357

1

T122

1

R142

MO

25V

39nF

C8188

T121

C170

D111

12

3

100nF

T264

1

1

A

2

B

3

C

680uH

L111

T272

1

VCC2.5T

FT101

2K

1/16W

R319

VCC5A

100nF

C313

E

10V

1uF

C872

VCC2.5D_DPTV

2SC2412K-Q

Q807

B

C

R809

1W

0.33

3

390R318

1

D115

12

Q820

B

C

E

T142

5

GND

SD

14

SENSE

2

VIN VOUT

3

KSC1623-Y

T110

1

IC814

LP3961EMP-2.5

R121 100

R9358

56K

8

C8101

16V

100uF

22

1

2

3

4

5

6

7

RA303

R9276

0

1/16W

C114

22uF

16V

1

T143

1

1

T268

1

T267

T269

1

T284

1

2

3

4

5

6

7

8

VCC5C

RA309

22

R814

C305

10pF

12

3

33K

12

3

D109

T243

1

D110

1

TP35

1

R9480

TP34

47K

R9479

47K

R135

33K

1

T109

1

100nF

C806

T290

C807

100uF

STD_VCC5A

R122

33K

C818

100nF

VCC12AS

100uF

C858

STD_VCC3B

T108

1

47pF

C184_OP

L107

N

100nF

C327 C328

100nF

0R311

100uF

C873

4.7nF

C125

A2B

220pF

C123

FT847

1

C325

100nF

R818

33K

1/16W

3

4

5

6

7

8

C874

100nF

1

RA302

22

1

2

T287

1

T288

C8292 1nF

1/16W

100

R9478

1/16W

100

R9477

R9473

4.7K

1/16W

VCC3DuP

T277

1

100nF

C310

3

STD_VCC6A

VCC12B

100nF

C324

2

3

D103

MMBD4148SE

12

D108

1

R126

33K

I1

1

I22O1

3

O2

4

1.5uHL912

TP33

1

ACM2012-361-2P

FT305

TP32

1

1

C8105

100uF

33K

T257

100nF

C8152M

R129

T115

1

R110

100K

C8133M

16V

100uF

10uF

16V

C167

100pF

C126

IC807

GND

2

IN1OUT

3

16V

22uF

C118

1A2

B

C

3

BA178M08FP

FT301

A

1

B

2

C

3

FT300

1/16W

3.6K

R811

C826

100uF

16V

1/16W

316

R8305

T283

1

C8192

33nF

16V

MO

MO

16V

100nF

C112

T117

1

T118

1

16V

10uF

C164

C833

100uF

16V

16V

C165

10uF

1

33K

R802

C8102

100nF

T285

C885

VCC3D_PPMM

100uF

16V

10K

R800

10uF

C168

C169

10uF

16V

R113

75

16V

1

2

3

4

5

6

7

8

RA301

22

N

L112

33K

10nF

C102

0

R317

R125

D114

12

3

T255

1

T262

1

T256

1

R312

4.7K

R9241M

10pF

C304

4

C_2

9

GND

8

6

INH

VCC

16

VEE

7

33K

AX

12

AY

13

A_1

11

A_2

14

BX

2

BY

1

B_1

10

B_2

15

CX

5

CY

3

C_1

T116

1

74VHC4053MX

IC101

R132

33K

T232

1

T231

1

4.7K

R820

16V

47uF

C8129

ACM2012-361-2P

FT302

I1

1

I22O1

3

O2

4

C302

15pF

1/16W

1.2K

R810

C803

100uF

STD_VCC5B

N

L100

C103

22uF

16V

Q803

2SC2412K-Q

B

C

E

T258

1

VCC5DDC

C333

100nF

1

S1

3

S2

C100

100nF

IC809

SI9933ADY-T1

D1

8

7

D1_1

D2

6

5

D2_1

G1

2

G2

4

C8132M

100uF

16V

33K

R9240M

T278

1

R138

33K

12

3

R137

33K

1

A

B

2

3

C

MMBD4148SE

D101

FT104

1

T250

1

R117 100

T103

1

T104

T102

1

100nF

C312

C319

100nF

MBRM130LT3

D803

T140

1

VCC12BS

VCC5C

T112

1

C8108

100uF

15pF

C303

C111

100uF

Q908M

D1

8

7

D1_1

D2

6

5

D2_1

G1

2

G2

4

1

S1

3

S2

T240

1

SI9933ADY-T1

C810

100uF

16V

T245

1

T291

1

C847

100uF

16V

T125

1

T292

1

T124

1

23

24

25

26

C897

100uF

13

14

15

16

17

18

19

20

21

22

1

2

3

4

5

6

7

8

9

10

11

12

CN509

dcon30p_j

27

28

29

30

100nF

C866

OUT

4

D116

12

3

MC33269DTRK-5.0

IC800

GND

1

IN

3

VCC1.8_DNI

VCC12A

100nF

C331

10K

R803

2.2nF

C124

22K

R109

1

C841

1uF

10V

FT103

A

1

B

2

C

3

VCC5C

T279

1

C817

100uF

16V

VCC3_DNI

T111

10nF

C121

100nF

C329

16V

100uF

C330

C845

100nF

T236

1

R301

22

C321

100nF

TP40

1

TP41

1

TP39

1

BZX84C33

D102

VCC3DuP

C861

100uF

C316

16V

100uF

100nF

C802

R825

100K

1/16W

L803

T266

1

MO

16V

100nF

C8193

1nF

50V

MO

C8189

T282

1

C865

100uF

C

E

75R106

2SC2412K-Q

Q802

B

1/16W

56K

R807

B

C

E

C830

1uF

10V

STD_VCC5B

2SC2412K-Q

Q906M

1

A

2

B

3

C

C8123

1uF

VCC5DDC

FT832

20

GND2

GND3

21

22

GND4

100nF

C811

C

4

D

5

E

6

F

G

7

8

H

I

9

10

J

GND1

19

K

12

L

13

M

14

N

15

O

16

P

17

Q

R

18

3

SUPLVAL

CN125

1

A

2

B

11

0

1/16WR313_1

R316_9

680

1/16W

0

R305_9

0

1/16W

R304_9

100nF

C840

22

R300

T286

1

C868

100uF

56K

R808

100uF

C8106

R805

TP38

1

33K

C311

100nF

C854

100nF

VCC3D_DPTV

VCC3A_DPTV

16V

100uF

C853

R139

33K

R824

30K

1/16W

100nF

C862

18

19

20

21

22

23

24

25

26

8

9

10

11

12

13

14

15

16

17

27

28

29

30

1

2

3

4

5

6

7

CN505

dcon30p_j

2.2uHL911

L910 2.2uH

C

3

D4E

5

F

6

G

7

H

8

IC806

MC34063ACD

A

1

B

2

T247

1

3

4

5

6

7

8

NL110

VCC3B

RA308

22

1

2

16V

47uF

C171

1

BA033FP

IC803

GND

2

IN1OUT

3

T281

1

T101

15

16

17

18

19

20

21

22

23

24

5

6

7

8

9

10

11

12

13

14

1

CN508

dcon24p_j

1

2

3

4

T280

1

T126

R308

4.7K

1nFC8293

R128

33K

2.2uHL908

1.5uH

L915

6

5

D2_1

G1

2

G2

4

1

S1

3

S2

C8120

22uF

16V

IC810

SI9933ADY-T1

D1

8

7

D1_1

D2

10V

1uF

C860

C332

100uF

16V

100nF

C898

47pF

C180_OP

C181_OP

47pF

22

R302

L909 2.2uH

R303 22

100uF

C8107

100uF

C116

C821

100uF

GND

5

1

SD SENSE

4

VIN

23

VOUT

D800

UZ15BSA

100nF

C314

LP3961EMP-2.5

IC812

16V

100uF

C839

50V

1uF

C104

T246

1

C105

100nF

MC33269DTRK-12

IC805

GND

1

IN3OUT

4

TP37

1

C183_OP

47pF

8

C8190

6.3V

MO

1000nF

22

1

2

3

4

5

6

7

B

C

E

RA304

KSC1623-Y

Q101

33K

1/16W

C814

100uF

16V

R817

T289

1

100nF

C848

R819

100K

1/16W

VCC8B

C117

10nF

C

E

C306

100nF

B

C

E

2SC2412K-Q

Q801

B

1K

Q804

2SC2412K-Q

100

SDA

IN

3

STAG_OUT

IN

7

6

IN

VCC

38

IN

VCC1

67

IN

VCC2

VSYNC

IN

47

R321

RESET

IN

1

RX0+

IN

90 91

IN

RX0-

85

IN

RX1+

RX1-

IN

86

RX2+

IN

80 81

IN

RX2-

93

IN

RXC+

RXC-

IN

94

8

IN

SCDT

SCL

IN

IN

74

75

IN

QO22

77

IN

QO23

QO3

IN

52

53

IN

QO4

QO5

IN

54

55

IN

QO6

QO7

IN

56

59

IN

QO8

QO9

IN

60

99

IN

RESERVED

62

63

IN

QO12

QO13

IN

64

65

IN

QO14

QO15

IN

66

69

IN

QO16

QO17

IN

70

71

IN

QO18

QO19

IN

72

51

IN

QO2

73

IN

QO20

QO21

36

IN

QE22

QE23

IN

37

QE3

IN

13

14

IN

QE4

QE5

IN

15

16

IN

QE6

QE7

IN

17

20

IN

QE8

QE9

IN

21

61

IN

QO10

QO11

IN

IN

QE12

QE13

IN

25

26

IN

QE14

QE15

IN

2730

IN

QE16

QE17

IN

3132

IN

QE18

QE19

IN

33

12

IN

QE2

34

IN

QE20

QE21

IN

35

PD

PD0

IN

9

PGND

IN

98

4

IN

PIXS

97

IN

PVCC

Q00

IN

4950

IN

Q01

10

IN

QE0

QE1

IN

11

22

IN

QE10

QE11

IN

23

24

OGND

IN

19

28

IN

OGND2

OGND3

IN

45

OGND4

IN

58

OGND5

IN

76

18

IN

OVCC

OVCC2

IN

29

OVCC3

IN

43

57

IN

OVCC4

OVCC5

IN

78

2

IN

IN

AVCC3

42

IN

CTL3

46

IN

DE

EXT_RES

IN

96

GND

IN

5

GND1

IN

39

GND2

IN

68

48

IN

HSYNC

40

IN

HS_DJTR

OCK_INV

IN

4144

IN

ODCK

79

IN

AGND

83

IN

AGND1

87

IN

AGND2

89

IN

AGND3

AGND4

IN

92

AVCC

IN

82

AVCC1

IN

84

AVCC2

IN

88 95

MO

6.3V

C8191

IC300

SII169CT100

FT846

1A2

B

1000nF

R115

1/16W

120

TP36

1

T113

1

VCC3DuP

1

100nF

C115

R822

T141

R821

20K

D113

12

3

4.7K

D112

MMBD4148SE

12

3

MTZ7.5C

D801

D100

BZX84C33

330

R100

33K

R145

33K

R120

R144

CX

3

CY

4

C_1

9

C_2

8

GND

6

INH

16

VCC

7

VEE

100

12

AX

13

AY

11

A_1

14

A_2

2

BX

1

BY

10

B_1

15

B_2

5

10K

IC102

74VHC4053MX

R320

R812

D300

A

1

B

2

3

C

220

C318

10nF

1

2

3

4

5

6

7

8

VCC3A_PPMM

1

RA305

22

1

A2B

3

C

T252

3

4

5

6

7

8

FT806

LFB30-3A1E223M

RA300

22

1

2

R130

33K

VCC2.5DuP

C106

10nF

VCC5B

4.7K

D107

12

3

R306

18

1/16W

VCC5P

6

FB

GND

3

LGATE

4

PHASE

8

UGATE

2

5

VCC

R8307

1B2

C

3

IC822

ISL6520IB

BOOT

1

7

COMP_OCSET

VCC3T

SGM32F1E104-2A

FT816

A

DRAIN2_2

6

2

GATE1

4

GATE2

1

SOURCE1

3

SOURCE2

T270

1

IC823

ITF86110DK8T

DRAIN1_1

7

DRAIN1_2

8

DRAIN2_1

5

VCC1.8B

C8186

82uF

6.3V

2

C

3

C110

4.7nF

FT823

A

1

B

1

R131

33K

MO

16V

100nF

C832

T254

NL104

T233

1

C882

100nF

L108

N

N

L106

L109 N

B

C

E

C178

47uF

16V

Q907M

2SC2412K-Q

FAN1117AD-1.8

IC824

GND

1

IN3OUT

4

16V

10uF

C175

2

3

T100

1

VCC5C

MMBD4148SE

D106

1

1

75R114

C177

10uF

16V

T296

1A2

B

C

3

FT860

1

R9242M

100K

T293

1

T234

R143

33K

VCC8B

T123

1

16V

16V

10uF

C174

C172

10uF

16V

10uF

C173

STD_VCC3B

C166

10uF

16V

B

C

E

100

R804

T239

1

2SC2412K-Q

Q800

1uF

C8131M

MO

10V

FT821

SGM32F1E104-2A

1A2

B

C

3

C869

100nF

T114

1

R133

33K

T244

1

C831

100uF

1

T242

1

T295

1

T294

C315

100nF

B

C

3

10uF

C317

SGM32F1E104-2A

FT839

A

12

12

13

14

N

L102

1

2

3

4

5

6

7

8

9

10

11

22

23

24

25

26

slcon14p

CN800

12

13

14

15

16

17

18

19

20

21

1

2

3

4

5

6

7

8

9

10

11

26

dcon30p_j

CN507

27

28

29

30

16

17

18

19

20

21

22

23

24

25

4

5

6

7

8

9

10

11

12

13

14

15

CN506

27

28

29

30

1

2

3

1

T241

1

dcon30p_j

100nF

C834

T237

STD_VCC5B

MO

16V

C113

100pF

75R105

47nF

C122

1

MO

10V

1uF

C8130M

T276

1

T238

1

C323

100nF

T299

100nF

C804

R813

100K

C101

100uF

10V

1uF

C857

16V

10uF

C176

VCC3DuP

16V

47uF

C805

100

R116

VCC5B

100K

R801

16V

22uF

C127

C867

100nF

33K

R806

33K

R124

33K

100

R123

100

R103

1uF

R104

R127

33K

C8124

16V

100uF

C844

C8150M

100nF

100nF

C308

1

C309

100nF

T297

1

T298

R107

C8151

100nF

120

VCC2.5D_PPMM

100nF

C120

1

Q806

2SC2412K-Q

B

C

E

5

GND

1

SD SENSE

4

VIN

23

VOUT

T235

1

LP3961EMP-2.5

IC802

T248

T253

1

100nF

C322

16V

100uF

C825

1

A

2

B

3

C

L105 N

1

A

2

B

3

C

FT833

T251

1

FT834

1

T275

1

T273

R108

1/16W

330

16V

10uF

C301

1

A

2

B

3

C

C300

100nF

VCC2.5AuP

FT102

C8302

100nF

16V

MO

100uF

C8297 C8301

100nF

16VMO16V

IC301

1AB2C3

C8300

47uF

16V

2

3

4

5

6

7

8

KIA7029F

6

7

8

RA312

22

1

22

1

2

3

4

5

T249

1

VCC5C

RA313

100

R111

100

R112

100K

R102

B

C

E

L103

680uH

2SC2412K-Q

Q805

R9243M

R815

100K

100K

2

GND

1IN3

OUT

L914

1.5uH

IC801

BA033FP

1

T120

1

100nF

C307

R8306

T263

1/16W

1K

12

3

R134

33K

D117

Y_D2

Y_COMP2

DDC_DVI_SCLS

DDC_DVI_SDAS

GND_AMP

10V

1uF

C871

TUNER_GND_2 TUNER_33_2

TUNER_GND_1 TUNER_33_1

GND_AMP

PR_D2

PR_COMP2

PB_COMP2

PB_D2

DGND

AGND

TUNER_GND_2

AGND SGND

AGND

AGND

TUNER_GND_1

SUR_L_OUT2

SUR_R_OUT1

SUR_R_OUT2

HP_IDENT

AGND

GND_AMP

AGND

AGND

AFT_MASTER

AFT_SLAVE

TUNER_GND_2

MAIN_L_OUT2

CENTER_OUT2

CENTER_OUT1

MAIN_R_OUT2

WOOFER_OUT

MAIN_L_OUT1

SUR_L_OUT1

HP_OUT_L

HP_OUT_R

MAIN_R_OUT1

DGND

SW_POWER

SC1_B_SC1_SVHS_CO

COMP1_Y

COMP1_PB

COMP1_PR

AGND

AGND

SW_DVD

AGND

COMP2_Y

COMP2_PB

COMP2_PR

AGND

AGND

SW_DTV

AGND

PRO_SMPS

MUTE_HW

RX1_

D4_1_CONT1

D4_1_CONT2(SC1_SW)

D4_1_CONT3

D4_2_CONT3

D4_2_CONT1

D4_2_CONT2(SC2_SW)

SC2_SVHS_CO

SC1_CVBS_IN

SC1_CVBS_OUT

SC2_CVBS_IN

SC2_SVHS_CI

SC2_CVBS_OUT

Y_COMP1

PB_COMP1

PR_COMP1

Y_D1

PB_D1

PR_D1

SC1_R_SC1_SVHS_CI

SC1_G

SC2_R_IN

SC2_L_IN

SC2_R_OUT

SC2_L_OUT

PC_R

PC_RED

PC_BLUE

PC_DDC_HSYNC

RX0_

PC_DDC_VSYNC

IDENT_PC

RX0+

PC_GREEN

DDC_VCC5D

RXC_

RXC+

RX2_

RX2+

RX1+

AGND

VOL+_OUT

BUZER_IN

CH+_OUT

COMP1_L

COMP1_R

COMP2_L

COMP2_R

SC1_R_IN

COAXIAL_IN

OPTICAL_IN

AV_R

PC_L

AV_L

SC1_L_IN

SC1_R_OUT

SC1_L_OUT

TUNER_GND_1

TUNER_GND_1

TUNER_33_1

TUNER_33_1

TUNER_33_1

AGND

TUNER_GND_1

TUNER_GND_1

SDA3

SCL3

TUNER_GND_1

SIF1

TUNER_CVBS

TUNER_GND_2

SW_SMPS

CH-_OUT

VOL-_OUT

SOURCE_OUT

MENU_OUT

IR

LED_GRN

LED_RED

AV_CVBS

SVHS_Y

SVHS_C

SC1_RGB_FB

SW_SMPS

GND_AMP

SW_PVCC

SIF2

PIP_CVBS

TUNER_GND_2

TUNER_33_2

TUNER_33_2

TUNER_33_2

TUNER_33_2TUNER_33_2

TUNER_33_2

AGND

GND_AMP

SDA3

SCL3

TUNER_GND_2TUNER_GND_2

P1R2

P1R3

P1R4

P1R5

P1R6

P1R7

P1G6

P1G7

P1G0

P1G1

P1G2

P1G3

P1G(0:7)

P1R(0:7)

P1R1

P1R0

DGND

P1B(0:7)

P1B1

P1B0

P1B2

P1B3

P1B4

P1B5

P1B6

P1B7

P1G4

P1G5

RXC_

DGND

PD_CLK

DGND

DGND

PC_DVI_HSYNC

PC_DVI_VSYNC

DGND

DGND

DGND

DGND

DGND

PD_DE

DGND DGND DGND DGND

DGND

POR1

POR0

DGND

DGND

DGND

DGND

RX0+

RX0_

RX1+

RX1_

RX2+

RX2_

RXC+

GND_AMPSGND

POB(0:7)

POB6

POB7

POB5

POB4

POB3

POB2

POB1

POB0

POG(0:7)

POG6

POG7

POG5

POG4

POG3

POG2

POG1

POG0

POR(0:7)

POR6

POR7

POR5

POR4

POR3

POR2

SW_POWER

3

1

2

15

26

27

28

29

17

16

18

LW32A23W/LW40A23W

Schematic Diagrams

❈ This Document can not be used without Samsung’s authorization.

Power, DVI, Tuner Block Schematic Diagram

Page 20

Schematic Diagrams

15

S-Video signal,CN505,#26(Y),28(C),

IC701,#18(Y),19(C)

16

DTV,DVD,Y Signal

IC101,IC102,#14,IC702,#18

17

DTV,DVD,Pb(Cb) Signal

IC101,IC102,#15,IC702,#17

29

PC Digtal Input Signal

#18,19,21,22,24,25,27,28

18

DTV,DVD,Pr(Cr) Signal

IC101,IC102,#4,IC702,#16

1

DC 6V

2

DC 5V

26

CN507 PC RGB Signal #8,9,1027PC H-Sync Input Signal

28

PC V-Sync Input Signal

3

DC 3V

Page 21

PANEL_Y_INC

PPMM

REV_D ADD

FOR PLL

2.5V

TO DPTV 3D PRO

FOR PLL

ANALOG

BL ON/OFF

PANEL_Y_DEC

DIMMING

POWER

DIGITAL

GND_PANEL

CHI MEI OPTION

PLL

POWER

PPMM

VCC5P

FROM SNI_OUTPUT_RGB

TO TORISAN RTA

TO TORISAN RTA

PPMM

BLUE

PPMM

POWER

GREEN

RED

FOR

TO SNI_INPUT

FROM SNI_OUTPUT

100nF 100nF

C473C475

C426

C476

100nF

22uF

C428

0.56NF

C403 100nF

R501 47

10pF

C410

10pF

C409

100nF

C431

VCC2.5D_PPMM_1 PGA3V_1

22uF

C534

16V

C4109

47uF

16V

C

3

FT500

1

A

B

2

C

3

FT502

1

A

B

2

T521

1

R410

100

R457

1

100

C510

10pF

T534

R429 47

R428 47

100nF

VCC3D_PPMM_2

C469C472

R9330

100nF

21

22

23

24

25

26

1/16W

100

9

10

11

12

13

14

15

16

17

18

19

20

29

30

1

2

3

4

5

6

7

8

2I23

O1

4

O2

CN511C

slcon30p

27

28

O1

4

O2

FT523

ACM2012-361-2P

1

I1

FT521

ACM2012-361-2P

1

I1

2I23

C418 1uF

1uFC419

C4104 C4103

22uF22uF

T538

1

C456

22uF

T519

1

10pF

C509

R451 1M

C423

10uF

B

2

3

C

10pF

C411

B

3

C

FT407

1

A

FT410

1

A

2

100nF

C4108

1/16W

51K

R418

1/16W

2.4K

R419

R462 75

5

6

7

8

75R463

RA457D

10

1

2

3

4

R406

100nF

C434

R405

100

FT413

1A2

B

3

C

VCC3D_PPMM

100

1

A

2

B

3

C

FT405

FT409

A

1

B

2

3

C

C437

100nF

C449

100nF

C440

C439

100nF

100nF

DLL_AV

VCC3D_PPMM_2

100nF

C4101

100nF

C4102

1uFC413

0

R411

R464

47

AE1

AF15

WR

XTLI

H1

XTLO

H2

YCbCr_HS

B18

YCbCr_VS

A18

C424

33pF

SCL

B20

SDA

SMODE

AD14

TELX_FAST

W2

AC14

UP_CKO

VBOT

AF1

A4

VCLK1

F23

VCLK2

E23

VCLK3

VLF

B2

VREF

AF2

VTOP

P_SW

M24

AB2

Pb

Pr

AA2

Py

AE2

RBOT

AF5

AE15

RD

RED

Y3

RMID

AE4

C19

RST

RTOP

AD4

A20

G2

PORT0

AD21

AC22

PORT1

AD22

PORT2

PORT3

AE22

PORT4

AF22

PORT5

AC23

PORT6

AD23

PORT7

AE23

AD15

PSEN

P_BL