Samsung KM62256CLP-4L, KM62256CLP-4, KM62256CLRGE-10L, KM62256CLRGE-10, KM62256CLRG-7 Datasheet

...

PRELIMINARY

KM62256C Family CMOS SRAM

32Kx8 bit Low Power CMOS Static RAM

GENERAL DESCRIPTIONFEATURES

¡Ü

Process Technology : 0.7

¡Ü

Organization : 32Kx8

¡Ü

Power Supply Voltage : Single 5V

¡Ü

Low Data Retention Voltage : 2V(Min)

¡Ü

Three state output and TTL Compatible

¡Ü

Package Type : JEDEC Standard

§-

CMOS

¡¾

10%

28-DIP, 28-SOP, 28-TSOP I -Forward/Reverse

PRODUCT FAMILY

The KM62256C family is fabricated by SAMSUNG's advanced

CMOS process technology. The family can support various

operating temperature ranges and has various package types

for user flexibility of system design. The family also support low

data retention voltage for battery back-up operation with low

data retention current.

Product

Family

KM62256CL

Commercial (0~70¡É) 45*/55/70ns

KM62256CL-L

KM62256CLE

Extended (-25~85¡É) 70/100ns

KM62256CLE-L

KM62256CLI

Industrial (-40~85¡É) 70/100ns

KM62256CLI-L

* The parameter is measured with 30pF test load.

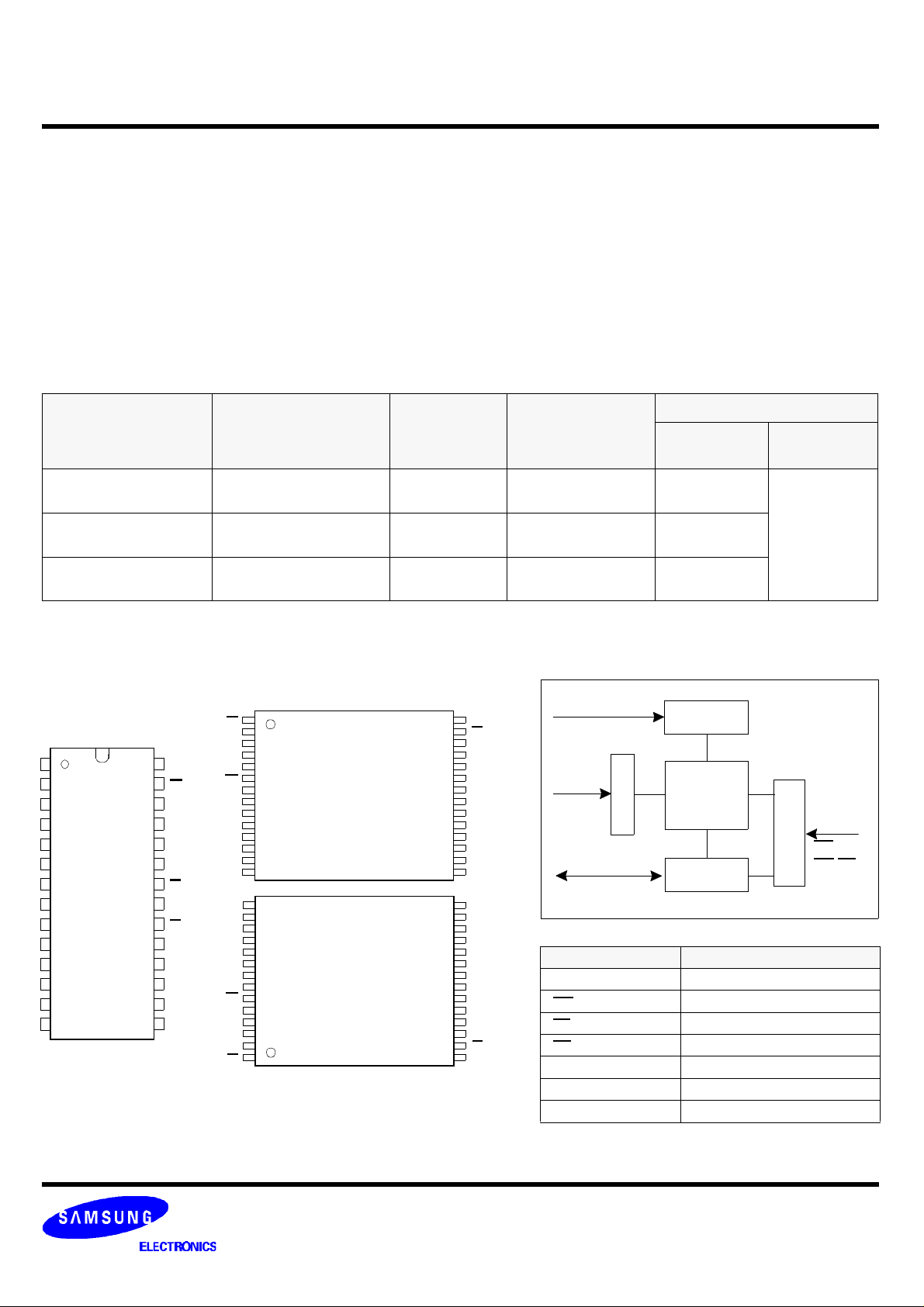

PIN DESCRIPTION

OE

A11

A9

WE

VCC

WE

A8

A13

A14

A12

A7

A6

A5

A4

A3

A3

A4

A5

A6

A7

A12

A14

VCC

A13

A8

A9

A11

OE

14

1

2

12

3

7

4

6

5

5

6

4

28-DIP

7

3

28-SOP

8

2

9

1

10

0

11

1

12

2

13

3

14

SS

VCC

28

WE

27

26

A13

A8

25

24

A9

23

A11

22

OE

21

A10

20

CS

19

I/O8

18

I/O7

17

I/O6

16

I/O5

15

I/O4

Operating

Temperature.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

14

13

12

11

10

9

8

7

6

5

4

3

2

1

28-TSOP

Type I - Forward

28-TSOP

Type I - Reverse

Speed

(ns)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

15

16

17

18

19

20

21

22

23

24

25

26

27

28

A10

CS

I/O8

I/O7

I/O6

I/O5

I/O4

VSS

I/O3

I/O2

I/O1

A0

A1

A2

A2

A1

A0

I/O1

I/O2

I/O3

VSS

I/O4

I/O5

I/O6

I/O7

I/O8

CS

A10

Power Dissipation

PKG Type

Standby

(ISB1, Max)

28-DIP, 28-SOP

28-TSOP I R/F

28-SOP

28-TSOP I R/F

28-SOP

28-TSOP I R/F

100

20

100

50

100

50

§Ë

§Ë

§Ë

§Ë

§Ë

§Ë

FUNCTIONAL BLOCK DIAGRAM

A0~A2, A9~11

X-Decoder

A3~A8,

A12~14

I/O1~8

Y-Decoder

Cell

Array

I/O Buffer

NameName Function

A0~A14 Address Inputs

WE Write Enable Input

CS Chip Select Input

OE Output Enable Input

I/O1~I/O8 Data Inputs/Outputs

Vcc Power(5V)

Vss Ground

Operating

(Icc2)

70mA

Control Logic

CS

WE,OE

Revision 3.0

April 1996

PRELIMINARY

Package Type : G=SOP, P=DIP, TG=TSOP Forward, RG=TSOP Reverse

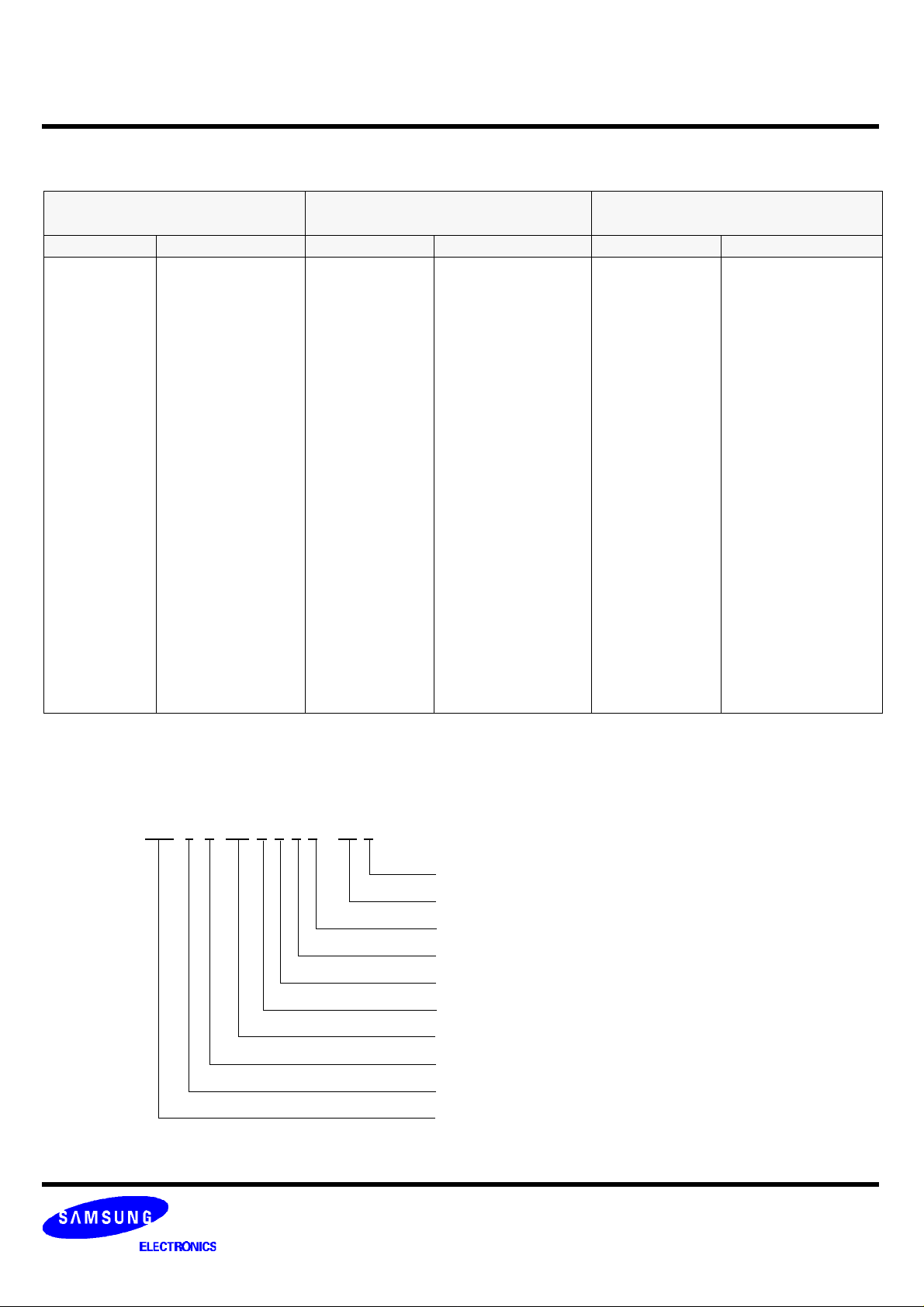

KM62256C Family CMOS SRAM

PRODUCT LIST & ORDERING INFORMATION

PRODUCT LIST

Commercial Temp Product

(0~70¡É)

Extended Temp Products

(-25~85¡É)

Industrial Temp Products

(-40~85¡É)

Part Name Function Part Name Function Part Name Function

KM62256CLP-4

KM62256CLP-4L

KM62256CLP-5

KM62256CLP-5L

KM62256CLP-7

KM62256CLP-7L

KM62256CLG-4

KM62256CLG-4L

KM62256CLG-5

KM62256CLG-5L

KM62256CLG-7

KM62256CLG-7L

KM62256CLTG-4

KM62256CLTG-4L

KM62256CLTG-5

KM62256CLTG-5L

KM62256CLTG-7

KM62256CLTG-7L

KM62256CLRG-4

KM62256CLRG-4L

KM62256CLRG-5

KM62256CLRG-5L

KM62256CLRG-7

KM62256CLRG-7L

28-DIP, 45ns, L-pwr

28-DIP, 45ns, LL-pwr

28-DIP, 55ns, L-pwr

28-DIP, 55ns, LL-pwr

28-DIP, 70ns, L-pwr

28-DIP, 70ns, LL-pwr

28-SOP, 45ns, L-pwr

28-SOP, 45ns, LL-pwr

28-SOP, 50ns, L-pwr

28-SOP, 50ns, LL-pwr

28-SOP, 70ns, L-pwr

28-SOP, 70ns, LL-pwr

28-TSOP F, 45ns, L-pwr

28-TSOP F, 45ns, LL-pwr

28-TSOP F, 55ns, L-pwr

28-TSOP F, 55ns, LL-pwr

28-TSOP F, 70ns, L-pwr

28-TSOP F, 70ns, LL-pwr

28-TSOP R, 45ns, L-pwr

28-TSOP R, 45ns, LL-pwr

28-TSOP R, 55ns, L-pwr

28-TSOP R, 55ns, LL-pwr

28-TSOP R, 70ns, L-pwr

28-TSOP R, 70ns, LL-pwr

KM62256CLGE-7

KM62256CLGE-7L

KM62256CLGE-10

KM62256CLGE-10L

KM62256CLTGE-7

KM62256CLTGE-7L

KM62256CLTGE-10

KM62256CLTGE-10L

KM62256CLRGE-7

KM62256CLRGE-7L

KM62256CLRGE-10

KM62256CLRGE-10L

28-SOP, 70ns, L-pwr

28-SOP, 70ns, LL-pwr

28-SOP, 100ns, L-pwr

28-SOP, 100ns, LL-pwr

28-TSOP F, 70ns, L-pwr

28-TSOP F, 70ns, LL-pwr

28-TSOP F, 100ns, L-pwr

28-TSOP F, 100ns, LL-pwr

28-TSOP R, 70ns, L-pwr

28-TSOP R, 70ns, LL-pwr

28-TSOP R, 100ns, L-pwr

28-TSOP R, 100ns, LL-pwr

KM62256CLGI-7

KM62256CLGI-7L

KM62256CLGI-10

KM62256CLGI-10L

KM62256CLTGI-7

KM62256CLTGI-7L

KM62256CLTGI-10

KM62256CLTGI-10L

KM62256CLRGI-7

KM62256CLRGI-7L

KM62256CLRGI-10

KM62256CLRGI-10L

28-SOP, 70ns, L-pwr

28-SOP, 70ns, LL-pwr

28-SOP, 100ns, L-pwr

28-SOP, 100ns, LL-pwr

28-TSOP F, 70ns, L-pwr

28-TSOP F, 70ns, LL-pwr

28-TSOP F, 100ns, L-pwr

28-TSOP F, 100ns, LL-pwr

28-TSOP R, 70ns, L-pwr

28-TSOP R, 70ns, LL-pwr

28-TSOP R, 100ns, L-pwr

28-TSOP R, 100ns, LL-pwr

ORDERING INFORMATION

KM6 2 X 256 C X X X - XX X

L-Low Low Power, Blank-Low Power or High Power

Access Time : 4=45ns, 5=55ns, 7=70ns, 10=100ns

Operating temperature : Blank=Commercial, I=Industrial, E=Extended

L-Low Power or Low Low Power, Blank-High Power

Die Version : C=4th generation

Density : 256=256K bit

Blank=5V, V=3.0~3.6V, U=2.7~3.3V

Organization : 2=x8

SEC Standard SRAM

Revision 3.0

April 1996

PRELIMINARY

KM62256C Family CMOS SRAM

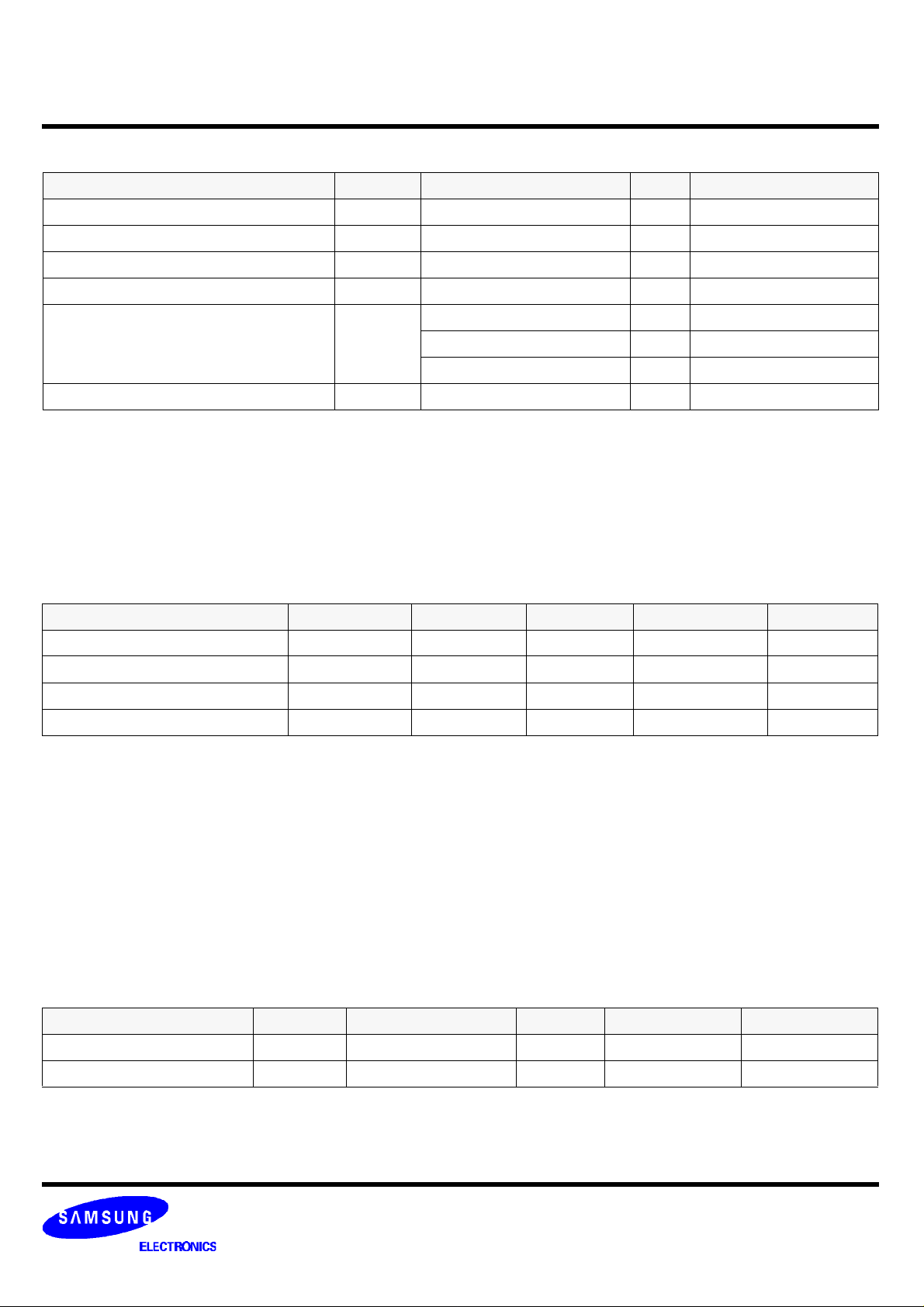

ABSOLUTE MAXIMUM RATINGS*

Item Symbol Ratings Unit Remark

Voltage on any pin relative to Vss VIN,VOUT -0.5 to VCC+0.5 V Voltage on Vcc supply relative to Vss VCC -0.5 to 7.0 V Power Dissipation PD 1.0 W Storage temperature TSTG -65 to 150

TA 0 to 70

Operating Temperature

Soldering temperature and time TSOLDER 260¡É, 10sec (Lead Only) - -

* Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect reliability.

-25 to 85

-40 to 85

¡É

¡É

¡É

¡É

KM62256CL/L-L

KM62256CLE/LE-L

KM62256CLI/LI-L

RECOMMENDED DC OPERATING CONDITIONS*

Item Symbol Min Typ** Max Unit

Supply voltage Vcc 4.5 5.0 5.5 V

Ground Vss 0 0 0 V

Input high voltage VIH 2.2 - Vcc+0.5V V

Input low voltage VIL -0.5*** - 0.8 V

* 1) Commercial Product : TA=0 to 70¡É, unless otherwise specified

2) Extended Product : TA=-25 to 85¡É, unless otherwise specified

3) Industrial Product : TA=-40 to 85¡É, unless otherwise specified

¡É

** TA=25

*** VIL(min)=-3.0V for ¡Â 50ns pulse width

CAPACITANCE* (f=1MHz, TA=25

Item Symbol Test Condition Min Max Unit

¡É

)

Input capacitance CIN VIN=0V - 6 pF

Input/Output capacitance CIO VIO=0V - 8 pF

* Capacitance is sampled not 100% tested

Revision 3.0

April 1996

Loading...

Loading...