Samsung KD16903 Datasheet

DATA PROCESSOR KD16903

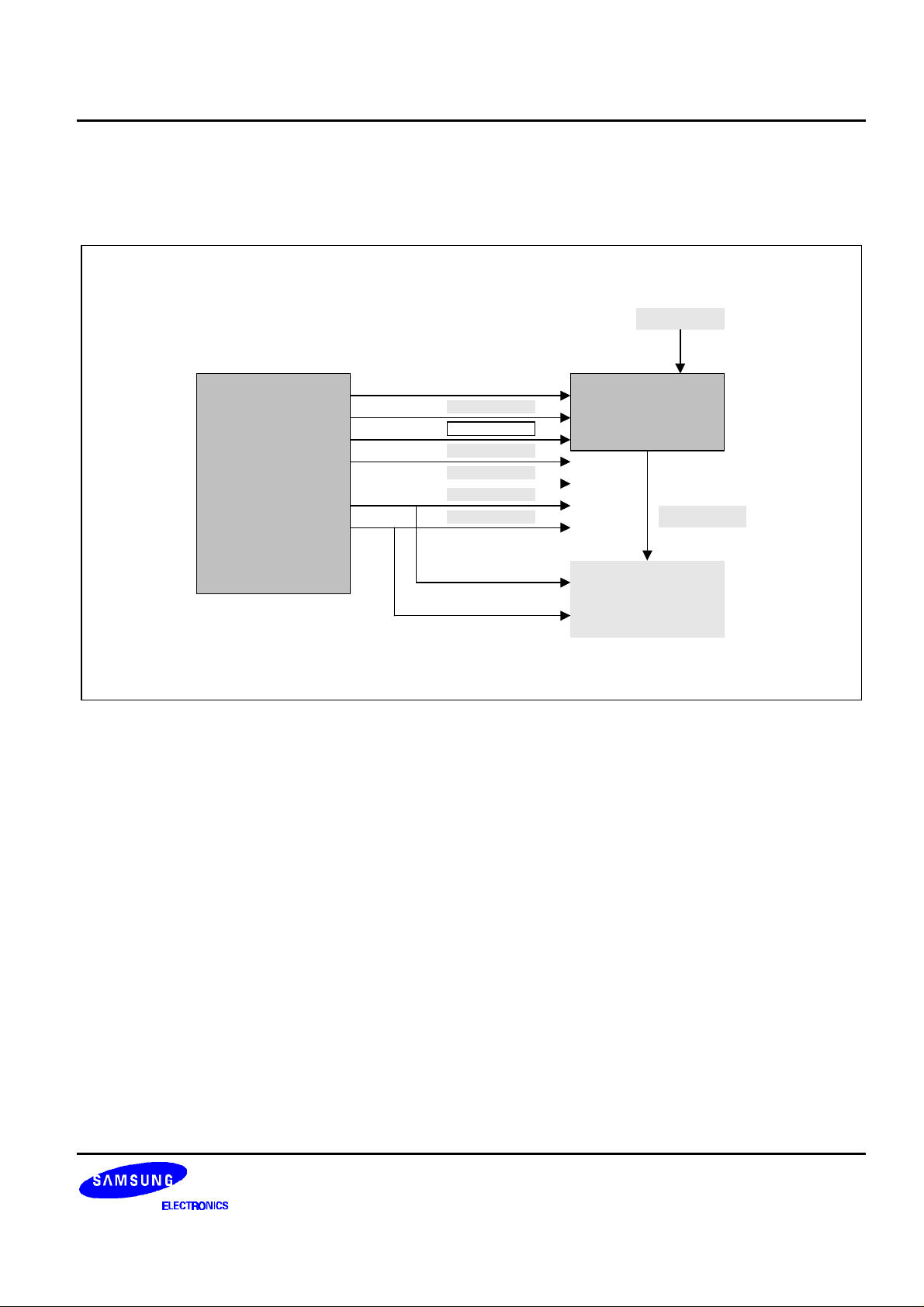

1. BLOCK DIAGRAM

1.1 SYSTEM BLOCK DIAGRAM

CKIN

VOCODER

RESB

SCL

SDA

DIN

FS

MCLK

VIP

DOUT

VOICE

CODEC

1

KD16903 DATA PROCESSOR

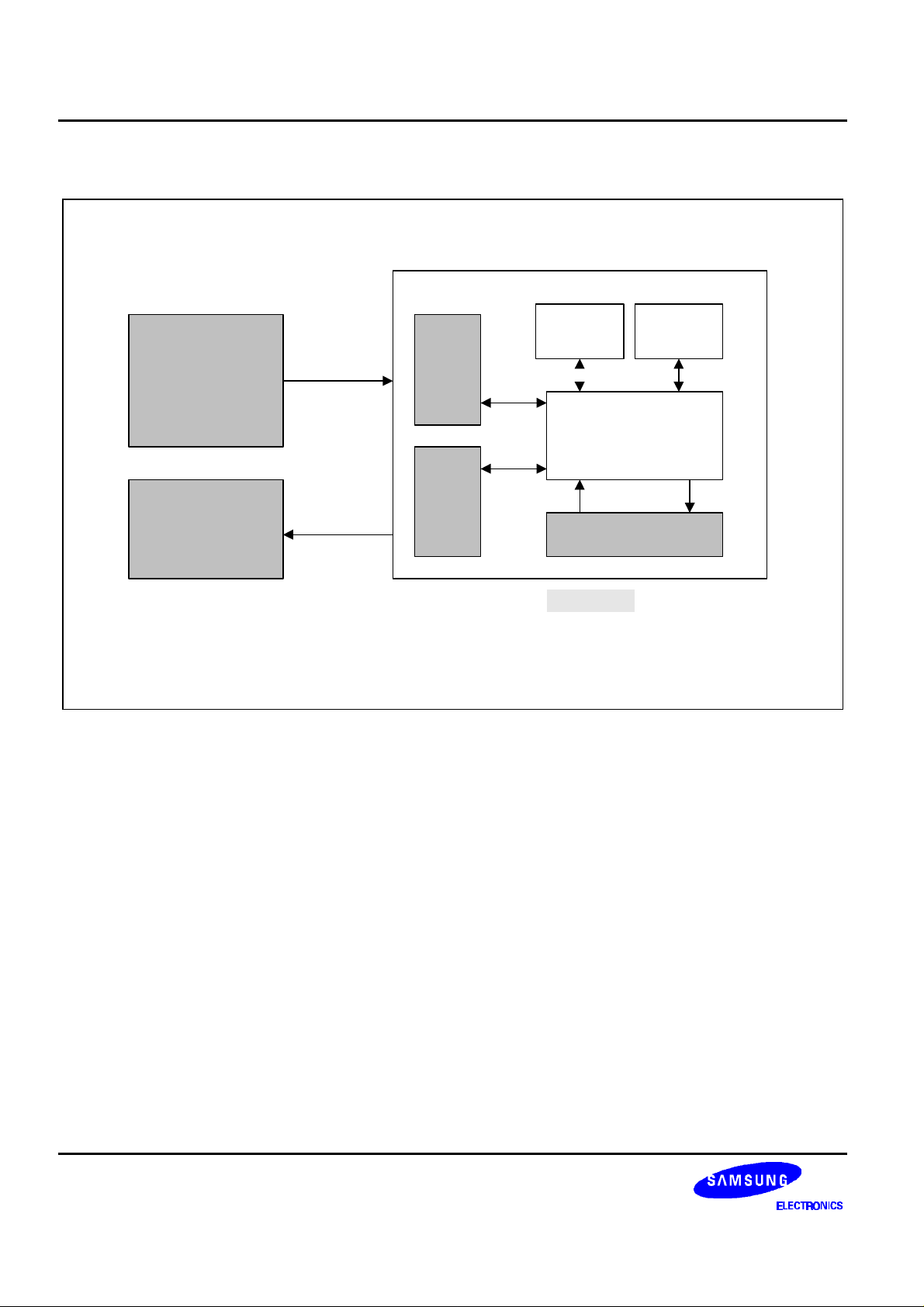

1.2 CHIP BLOCK DIAGRAM

MSM

VOCODER

CODEC

I2C

I/F

Digital

I/F

SRAM

256

VIP

SRAM

256

SSP1611

P.ROM 2K

NOTE: Not Scaled

2

DATA PROCESSOR KD16903

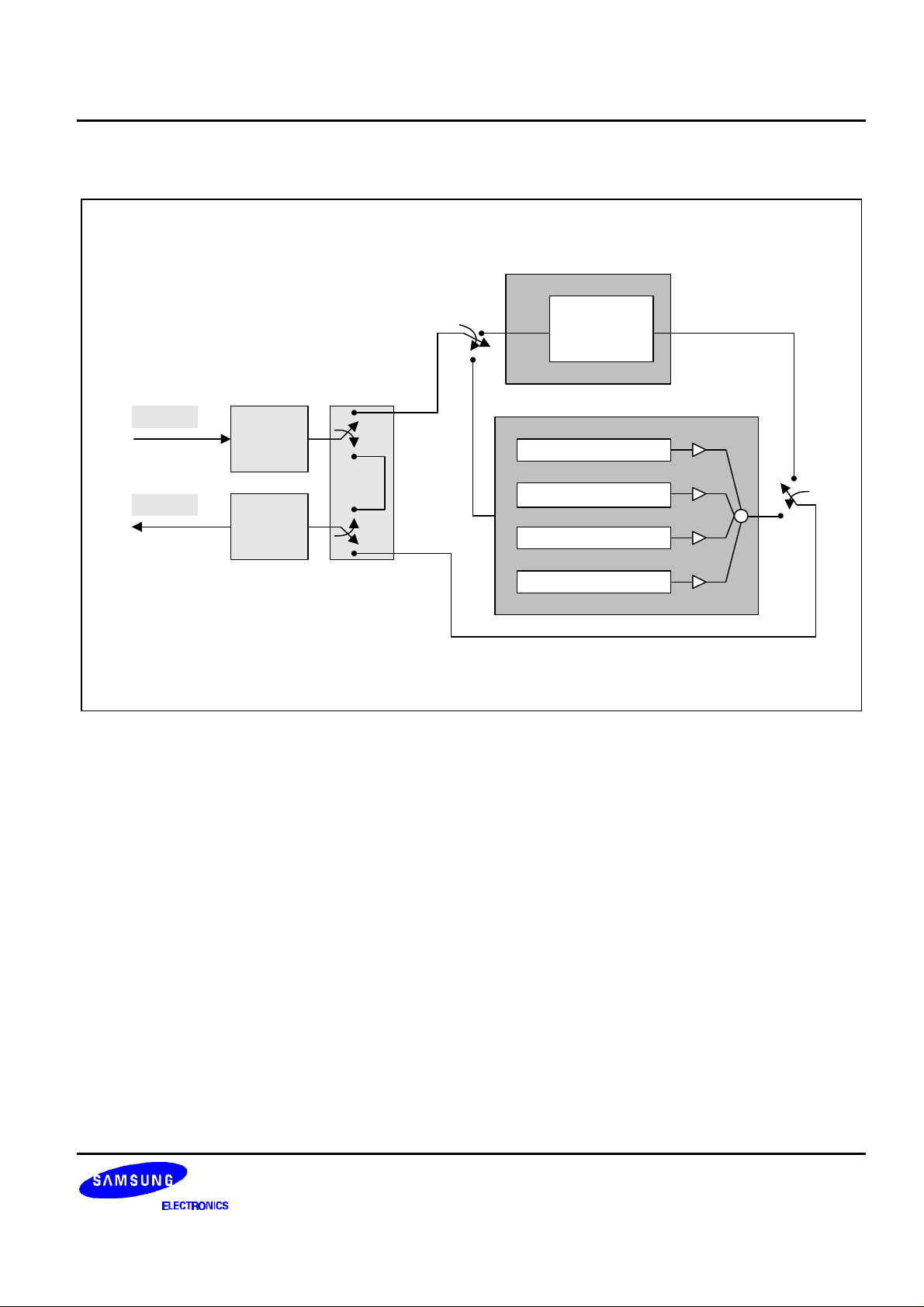

1.3 FUNCTIONAL BLOCK DIAGRAM

Voice

Intelligibility

Proces

DIN

DOUT

PCM

INPUT

I/F

PCM

OUTPUT

I/F

BPF (Center: 300HZ)

BPF (Center: 600HZ)

+

BPF (Center: 1.2kHZ)

HPF (Cutoff: 2.4kHZ)

3

KD16903 DATA PROCESSOR

GPO0

VDD1

GPI0

GPI1

GPI2

GPI3

GND1

RESB

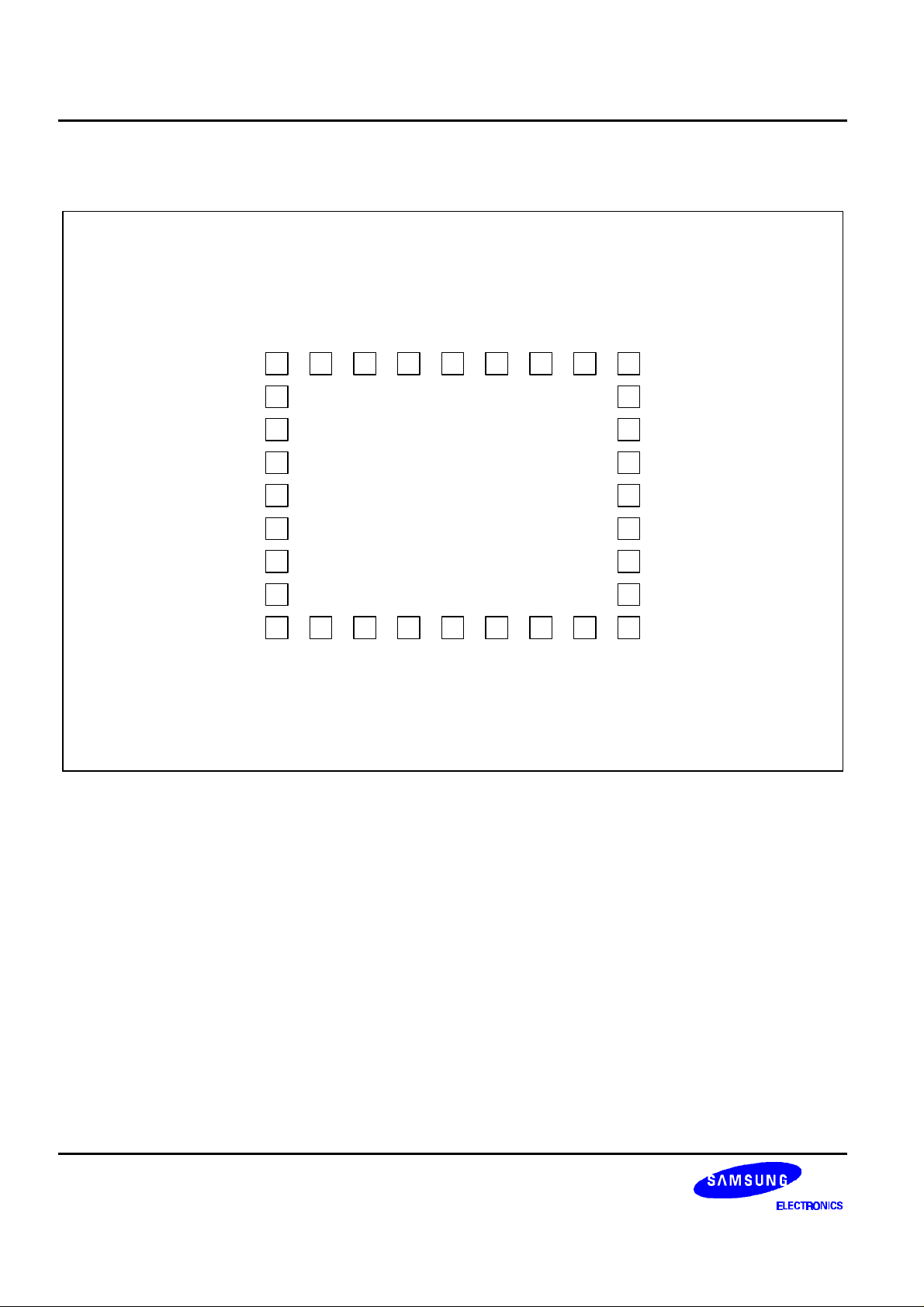

2. PIN ASSIGNMENTS

TCLKDR

TIDR

TSHFTDR

GND3

TUPDDR

TSELDR1

TSEKDR0

VDD3

SAS

VDD4

TODR

GPO3

GPO2

DOUT

GND4

GPO1

25

24 23 22 21 20 19 18

26

27

28

KA16903

29

30

31

32

1 2 3 4 5 6 7 8 9

32BCC

(Top View)

17

16

15

14

13

12

11

10

SCL

SDA

GND2

CKIN

VDD2

MCLK

DIN

FS

4

DATA PROCESSOR KD16903

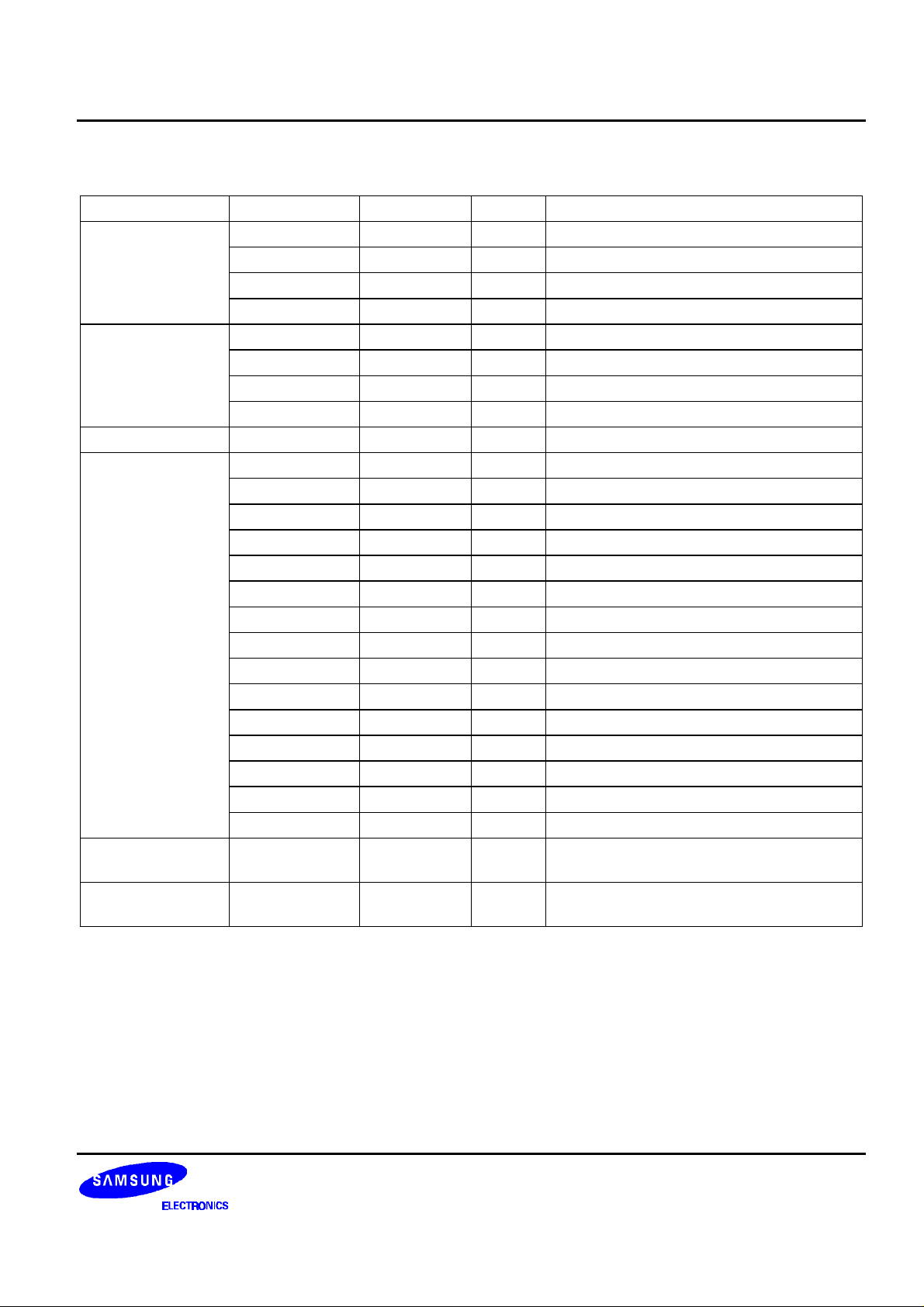

3. PIN DESCRIPTION

Related Block PIN NAME PIN NO. I/O Description

RESB 8 I Reset: Active Low with CKIN(Min 10 cycle)

HIU SDA 15 I/O I2C Serial Data

SCL 16 I I2C Serial Clock

SAS 17 I I2C Address Selection

DIN 10 I 16 Bit PCM Serial Data In

CIU DOUT 30 O 16 Bit PCM Serial Data Out

FS 9 I PCM Data Frame Sync.

MCLK 11 I PCM Data Bit Clock

System CKIN 13 I System Clock (9.84MHz)

GPI0 3 I Test Pin0 (Host INT. Indicator)

GPI1 4 I Test Pin1(0:No Fade, 1:Fade)

GPI2 5 I Test Pin2 (0:RAM Test)

GPI3 6 I Test Pin3 (0:Codec Bypass)

TSELDR0 19 I Test Pin for JTAG

TSELDR1 20 I Test Pin for JTAG

TEST TUPDDR 21 I Test Pin for JTAG

TSHFTDR 23 I Test Pin for JTAG

TIDR 24 I Test Pin for JTAG

TCLKDR 25 I Test Pin for JTAG

TODR 27 O Test Pin for JTAG

GPO0 1 O Host Ack. Pin

GPO1 32 O Host Test Output

GPO2 29 O Host Test Output

GPO3 28 O Host Test Output

Power VDD1, VDD2

VDD3, VDD4

Ground GND1, GND2

GND3, GND4

2, 12,

18, 26

7, 14,

22, 31

P Digital Power (+3.0V)

G Digital GND

5

KD16903 DATA PROCESSOR

~

~

4. DSP PORT ASSIGNMENT FOR I/F WITH PERIPHERALS

I/F Read/ Write Port Interrupt

HIU Read EXT1

INT1

Write EXT1

CIU Read EXT0

INT0

Write EXT0

5. HARDWARE SPECIFICATION

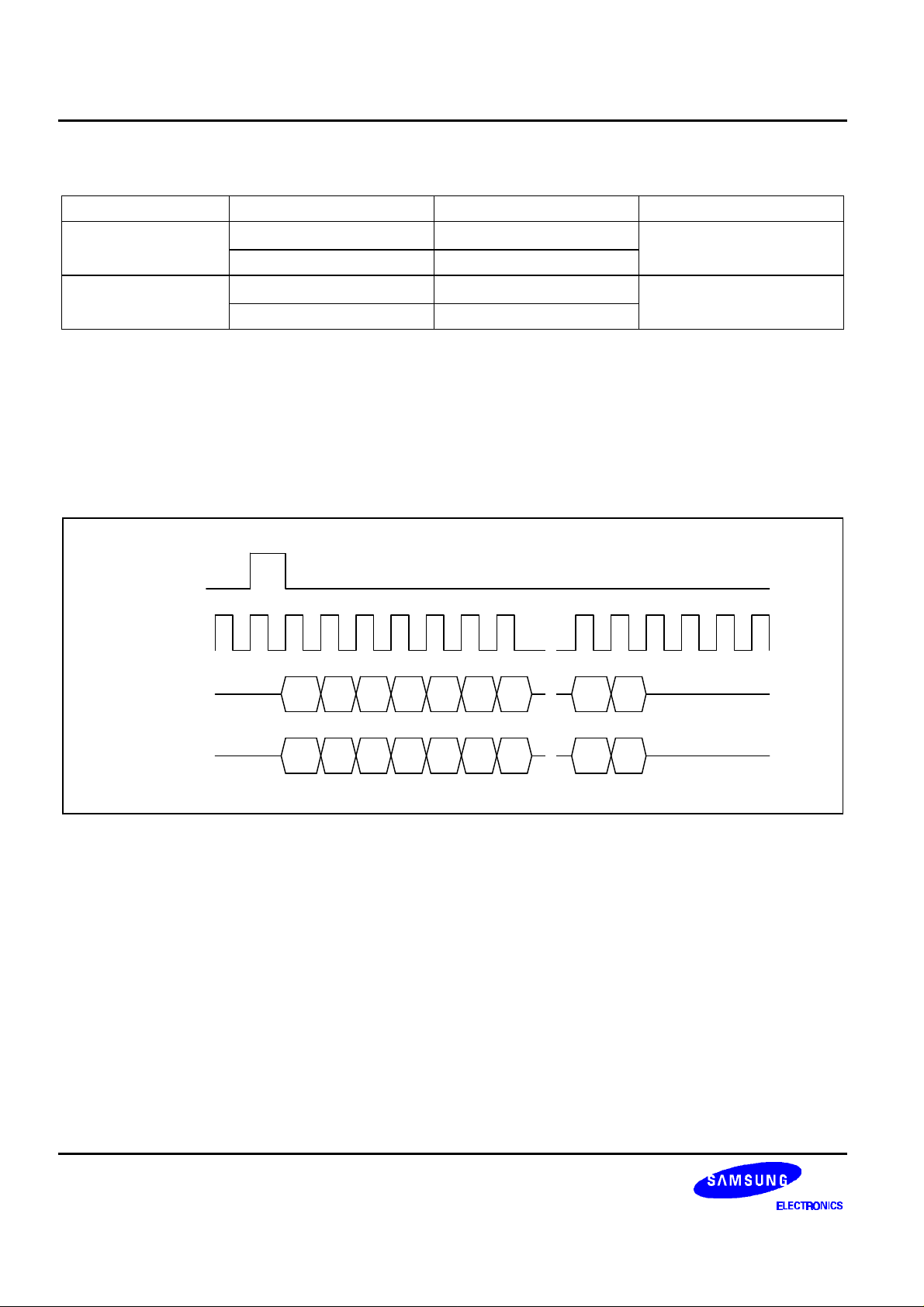

5.1 CODEC INTERFACE UNIT (CIU)

- Time Diagram

FS

MCLK

~

~

DIN

DOUT

1 2 3 4 5 6 15 16

1 2 3 4 5 6 7

7

~

~

15 16

Important!:

During FS (Frame Sync. Clock) high, the falling edge of MCLK (PCM Bit Clock) should exist one time.

6

Loading...

Loading...