Samsung KB9223, KB9223-L Datasheet

KB9223 / KB9223-L

OVERVIEW

PRELIMINARY

RF AMP & SERVO SIGNAL PROCESSOR

The KB9223 is a 1-chip BICMOS integrated circuit to perform the function of RF amp and servo signal processor for

compact disc player applications.It consist of blocks for RF

signal processing ,focus, tracking, sled and spindle

servo.Also this IC has adjustment free function and embedded opamp for audio post filter.

FEATURES

• RF amplifier & RF equalizer

• Focus error amplifier & servo control

• Tracking error amplifier & servo control

• Mirror & defect detector circuit

• Focus OK detector circuit

• APC(Auto Laser Power Control) circuit for constant laser

power

• FE bias & focus servo offset adjustment free

• EF balance & tracking error gain adjustment free

• Embedded audio post filter

• The circuit for Interruption countermeasure

• Double speed play available

• Operating voltage range

KB9223 : 5V

80-QFP-1420C

ORDERING INFORMATION

Device Package Tempe. Range

KB9223

KB9223-L

APPLICATIONS

• CD Player

• Video-CD

RELATED PRODUCT

• KS9286 Data Processor

• KS9284 Data Processor

• KA9258D/KA9259D Motor Driver

80-QFP-1420C -20°C ~ +70°C

KB9223-L : 3.4V

M/M-97-P006

1997. 10. 17

1

KB9223 / KB9223-L

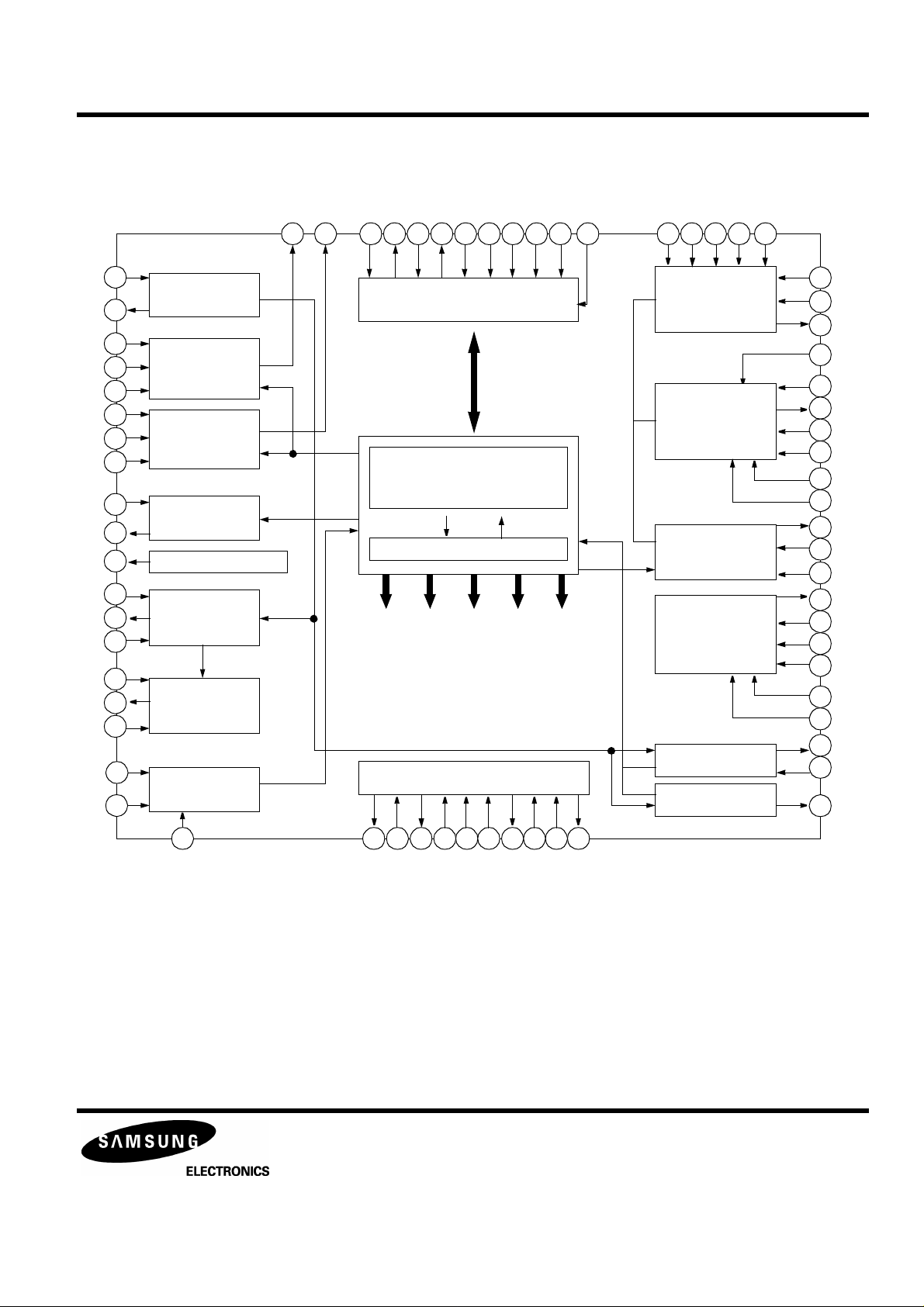

BLOCK DIAGRAM

PRELIMINARY

RF AMP & SERVO SIGNAL PROCESSOR

RF-

RFO

PD1

PD2

FEBIAS

EQC

EQO

IRF

ASY

EFM

RFI

DCB

DCC2

FE1

TE1

WDCH

TRCNT

LOCK

ISTAT

59

54 22 30 29 31 38 37 36 35 51 52 58 26 28 27

73

RF Amp

74

65

Focus Error Amp

66

FE-BIAS Adjustment

63

67

F

E

EI

68

79

Tracking Error Amp

E/F Balance & Gain

Control

Micom Data

Interface Logic

MICOM TO SERVO CONTROL

MLT

RESET

MDATA

MCK

TZC

ATSC

FE2

FLB

Focus Phase

Compensation

& Offset cancel circuit

Tracking Phase

Compensation Block

& Jump Pulse GEN.

AUTO SEQUENCER

PD

69

LD

70

VR

71

78

76

75

32

33

77

APC Amp

Center Voltage Amp.

RF Level AGC

&

Equalizer

EFM

Comparator

LDON

ADJUSTMENT-FREE CONTROL

TM1~

TM6

BAL1~

BAL5

FS1~

FS4

PS1~

PS4

GA1~

GA5

Sled Servo Amplifier

& Sled Kick GEN.

Spindle Servo LPF

( Double Speed )

Mirror Detection

2

Defect Detection

Circuit

4

Built-in Post Filter Amp ( L&R )

Circuit

FOK Detection

Circuit

FS3

FGD

FRSH

3

FDFCT

60

47

FE-

FEO

48

TDFCT

57

49

TE-

TEO

50

TE2

53

LPFT

55

TG2

62

TGU

61

SLO

43

SL-

44

SL+

42

46

SPDLO

SPDL-

45

SMDP

23

SMON

24

SMEF

25

FSET

6

MIRROR

39

MCP

1

FOK

40

5 15 16 13 14 19 17 12 11 9 10

RRC

GC1I

DCC1

GC1O

CH1I

CH1O

MUTEI

CH2I

GC2I

CH2O

Figure 1. Block diagram

M/M-97-P006

1997. 10. 17

GC2O

2

KB9223 / KB9223-L

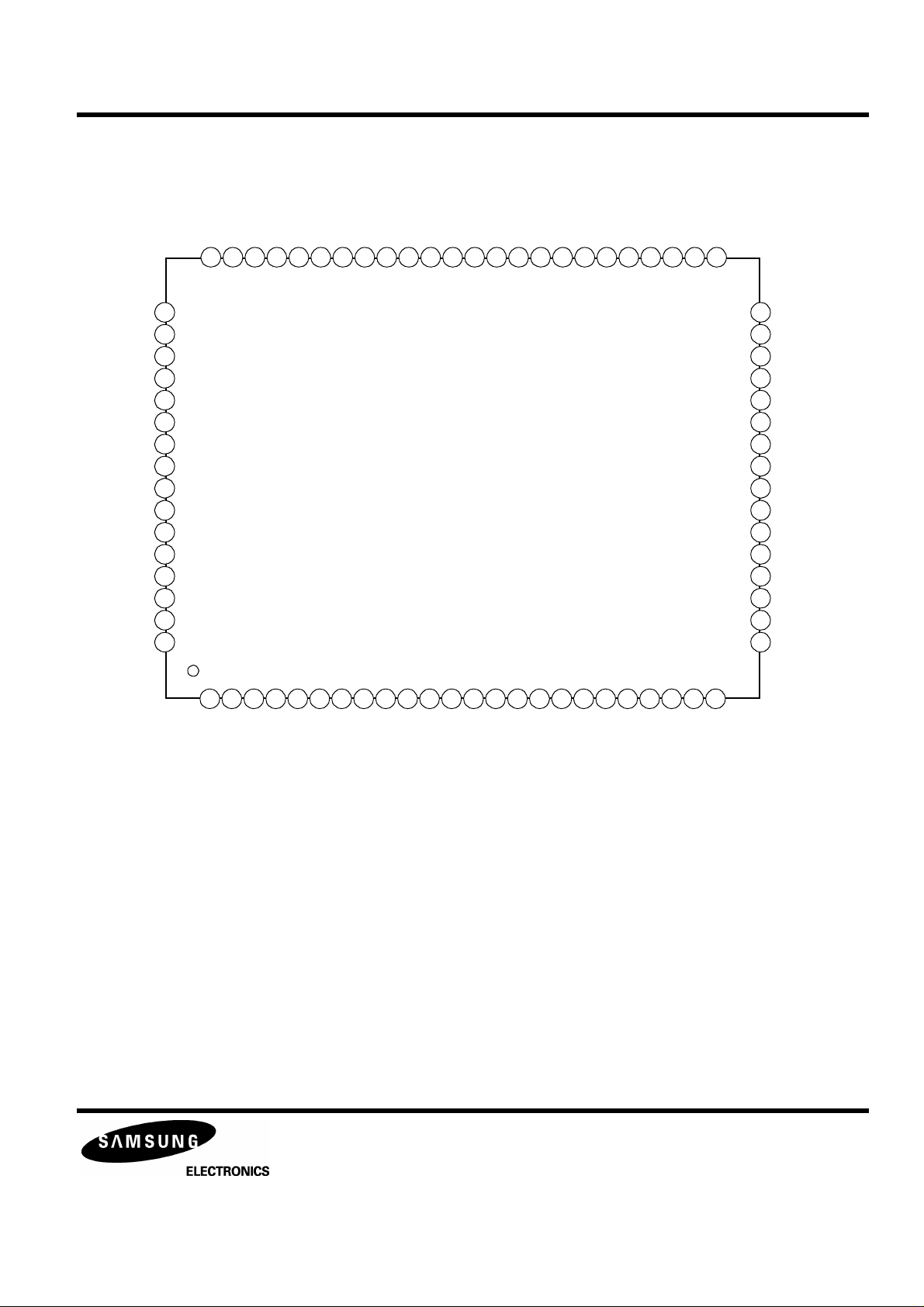

PIN CONFIGURATION

PRELIMINARY

RF AMP & SERVO SIGNAL PROCESSOR

64 63 62 61 60 59 58 57 56 55 54

TG2

DVEE

65

PD1

66

PD2

67

F

68

E

69

PD

70

LD

71

VR

72

VCC

73

RF-

74

RFO

75

IRF

76

EQO

77

RFI

78

EQC

79

EI

80

GND

FEBIAS

MCP

DCB

FRSH

1 2 3 4 5 6 7 8 9

FE1

TGU

FDFCT

DCC2

DCC1

FSET

53 52 51 50 49 48 47 46 45 44 43 42 41

TE-

FE2

TDFCT

TE1

TE2

TZC

LPFT

DVDD

TEO

ATSC

FE-

FEO

KB9223

VDDA

VCCP

GC2I

10 11

CH2O

CH1O

CH1I

GC1O

GC1I

RRC

VSSP

GC2O

CH2I

12 13 14 15 16 17 18 19 20 21 22 23 24

MUTEI

SL-

SL+

SLO

SPDL-

SPDLO

ISET

VREG

WDCK

MIRROR

RESET

MDATA

VSSA

ISTAT

TRCNT

LOCK

SMEF

SMDP

SMON

SSTOP

FOK

MLT

MCK

EFM

ASY

FGD

FS3

FLB

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

Figure 2. Pin configuration

M/M-97-P006

1997. 10. 17

3

KB9223 / KB9223-L

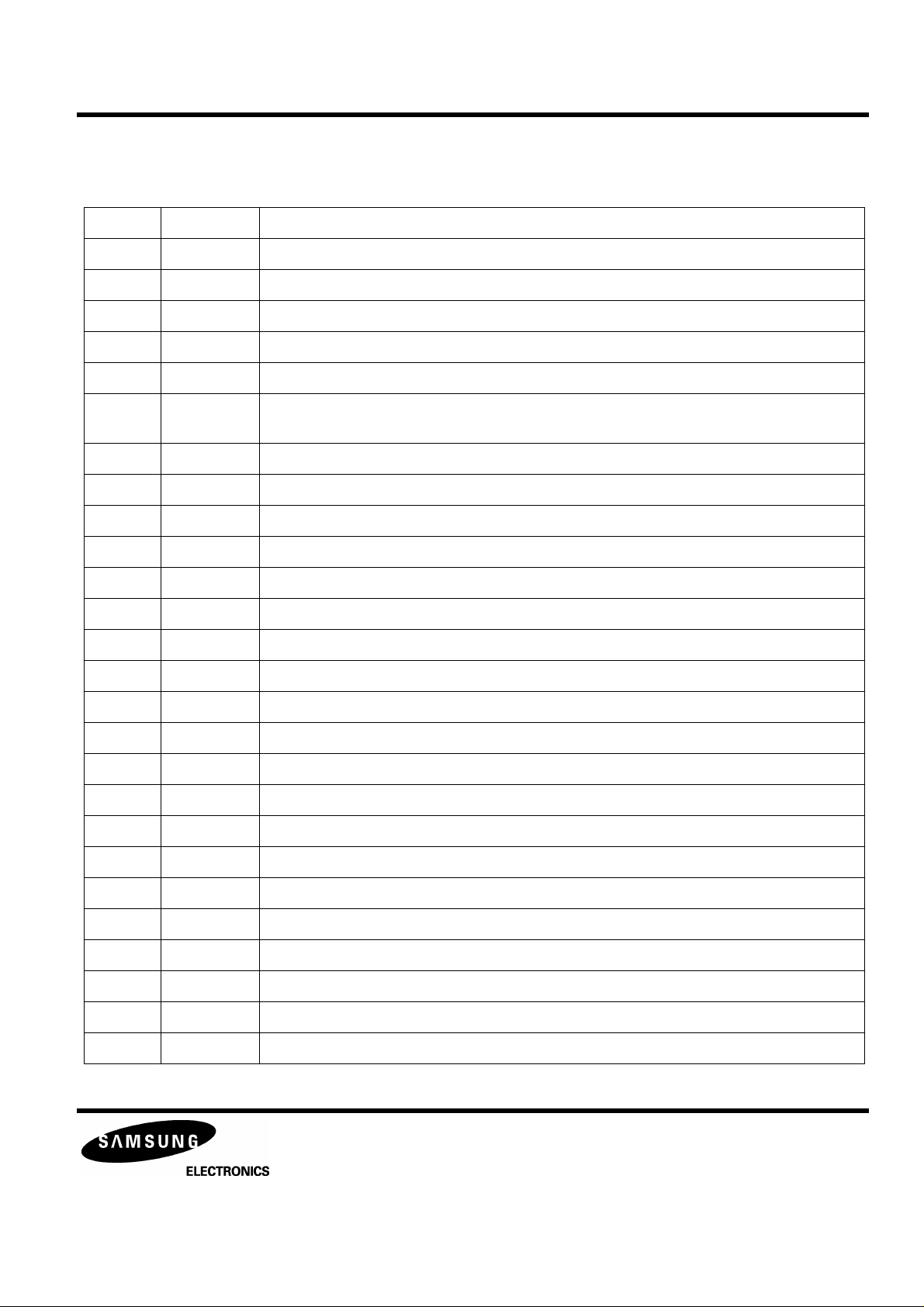

PIN DESCRIPTION

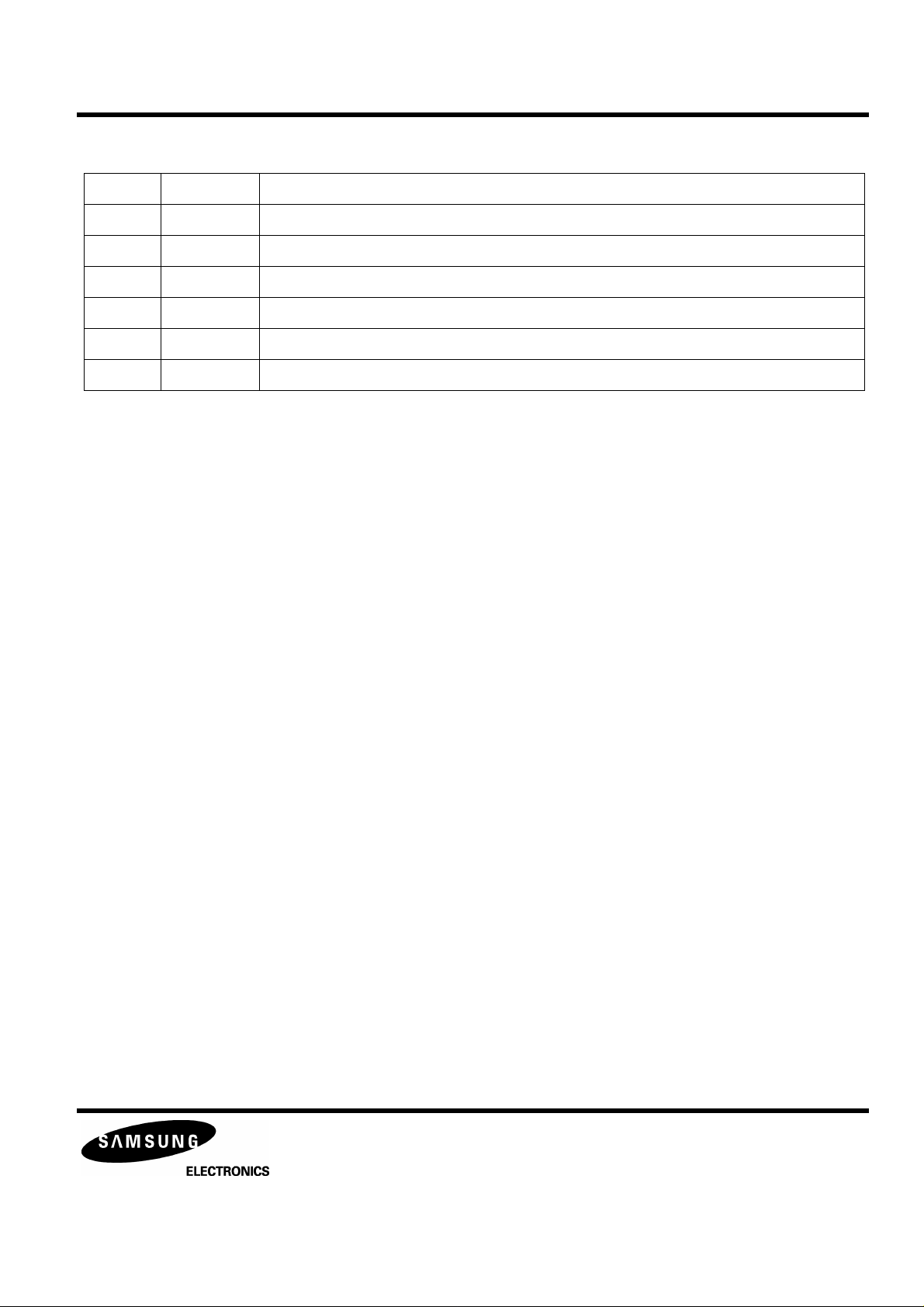

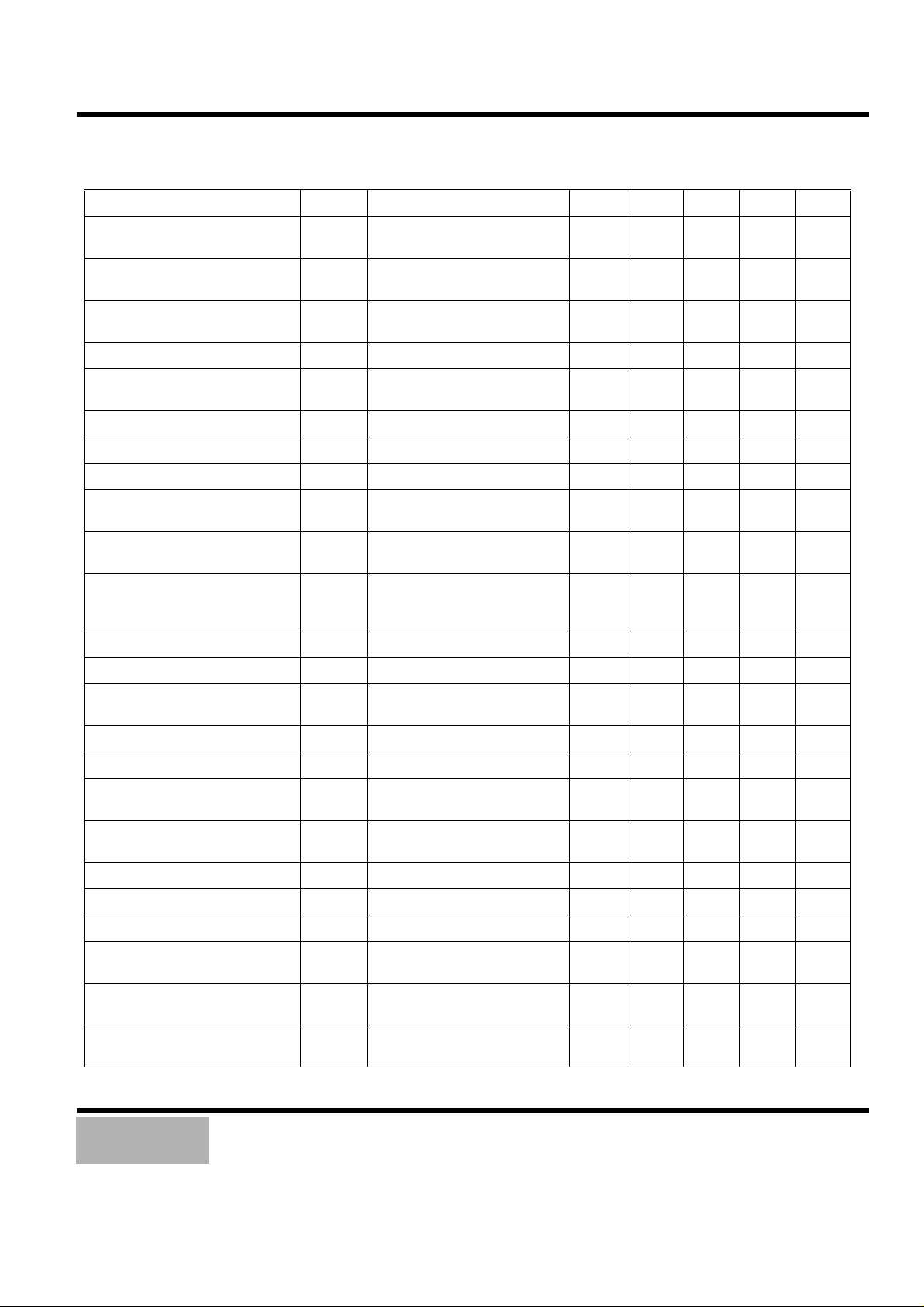

Table 1. PIN DESCRIPTION

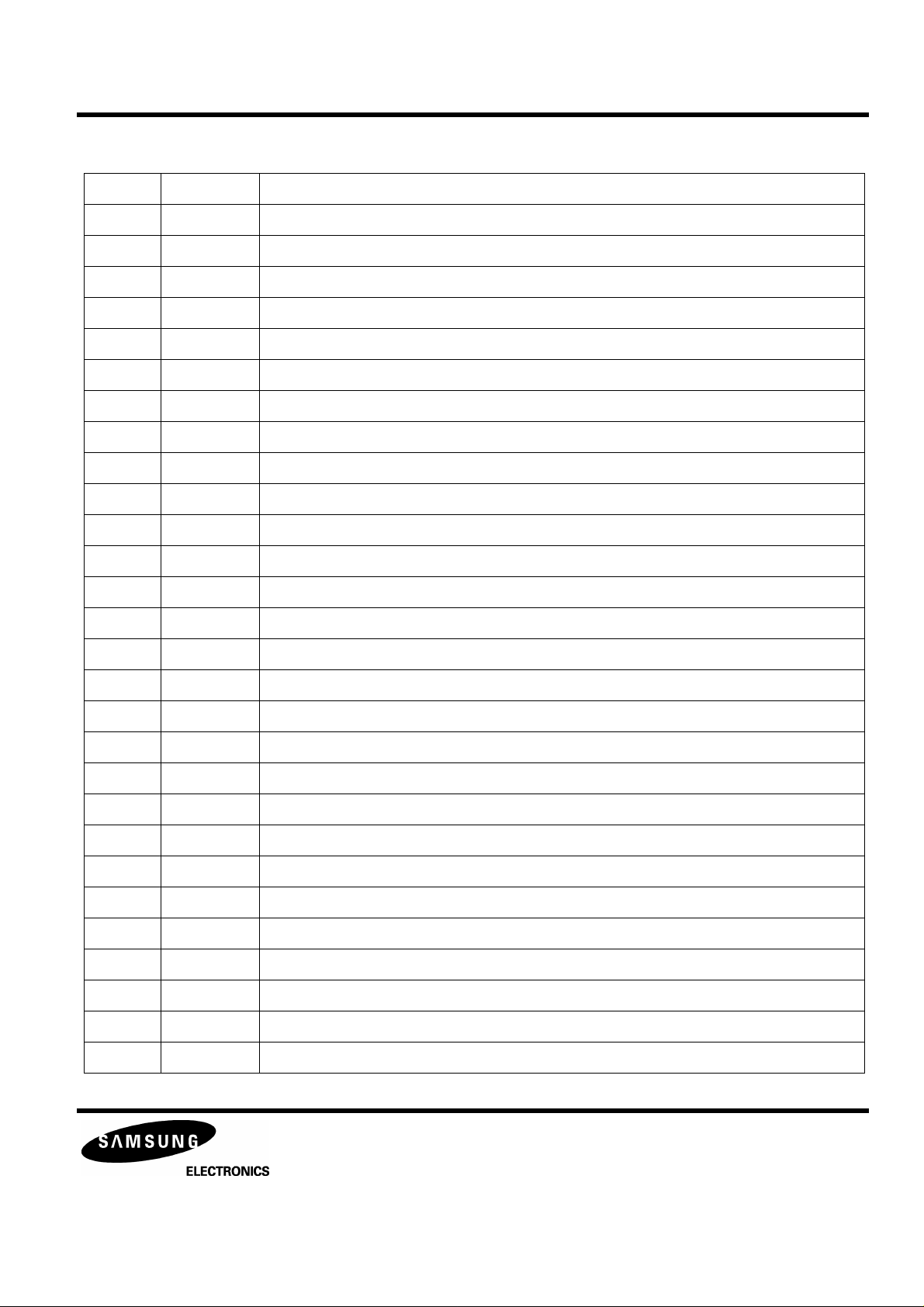

Pin No. Symbol Description

1 MCP Capacitor connection pin for mirror hold

2 DCB Capacitor connection pin for defect Bottom hold

3 FRSH Capacitor connection pin for time constant to generate focus search waveform

4 DCC2 The input pin through capacitor of defect bottom hold output

5 DCC1 The output pin of defect bottom hold

6 FSET The peak frequency setting pin for focus,tracking servo and cut off frequency of CLV

LPF

7 VDDA Analog VCC for servo part

8 VCCP VCC for post filter

9 GC2I Amplifier negative input pin for gain and low pass filtering of DAC output CH2

RF AMP & SERVO SIGNAL PROCESSOR

PRELIMINARY

10 GC2O Amplifier output pin for gain and low pass filtering of DAC output CH2

11 CH2I The input pin for post filter channel2

12 CH2O The output pin for post filter channel2

13 CH1O The output pin for post filter channel1

14 CH1I The input pin for post filter channel1

15 GC1O Amplifier output pin for gain and low pass filtering of DAC output CH1

16 GC1I Amplifier negative input pin for gain and low pass filtering of DAC output CH1

17 RRC The pin for noise reduction of post filter bias

18 VSSP VSS for post filter

19 MUTEI The input pin for post filter muting control

20 ISET The input pin for current setting of focus search,track jump and sled kick voltage

21 VREG The output pin of regulator

22 WDCK The clock input pin for auto sequence

23 SMDP The input pin of CLV control output pin SMDP of DSP

24 SMON The input pin for spindle servo ON through SMON of DSP

25 SMEF The input pin of provide for an external LPF time constant

26 FLB Capacitor connection pin to perform rising low bandwidth of focus loop

M/M-97-P006

1997. 10. 17

4

KB9223 / KB9223-L

Table 1. PIN DESCRIPTION (Continued)

Pin No. Symbol Description

27 FS3 The pin for high frequency gain change of focus loop with internal FS3 switch

28 FGD Reducing high frequency gain with capacitor between FS3 pin

29 LOCK Sled runaway prevention pin

30 TRCNT Track count output pin

31 ISTAT Internal status output pin

32 ASY The input pin for asymmetry control

33 EFM EFM comparator output pin

34 VSSA Analog VSS for servo part

35 MCK Micom clock input pin

36 MDATA Micom data input pin

RF AMP & SERVO SIGNAL PROCESSOR

PRELIMINARY

37 MLT Micom data latch input pin

38 RESET Reset input pin

39 MIRROR The mirror output for test

40 FOK The output pin of focus OK comparator

61 TGU The capacitor connection pin for high frequency tracking gain switch

62 TG2 The pin for high frequency gain change of tracking servo loop with internal TG2 switch

63 FEBIAS Focus error bias voltage control pin

64 DVEE The DVEE pin for logic circuit

65 PD1 The negative input pin of RF I/V amplifier1(A+C signal)

66 PD2 The negative input pin of RF I/V amplifier2(B+D signal)

67 F The negative input pin of F I/V amplifier (F signal)

68 E The negative input pin of E I/V amplifier(E signal)

69 PD The input pin for APC

70 LD The output pin for APC

71 VR The output pin of (AVEE+AVCC)/2 voltage

72 VCC VCC for RF part

73 RF- RF summing amplifier inverting input pin

74 RFO RF summing amplifier output pin

M/M-97-P006

1997. 10. 17

5

KB9223 / KB9223-L

Table 1. PIN DESCRIPTION (Continued)

Pin No. Symbol Description

75 IRF The input pin for AGC

76 EQO The output pin for AGC

77 RFI Tne input pin for EFM comparision

78 EQC The capacitor connection pin for AGC

79 EI Feedback input pin of E I/V amplifier for EF Balance control

80 GND GND for RF part

RF AMP & SERVO SIGNAL PROCESSOR

PRELIMINARY

M/M-97-P006

1997. 10. 17

6

KB9223 / KB9223-L

RF AMP & SERVO SIGNAL PROCESSOR

ABSOLUTE MAXIMUM RATINGS

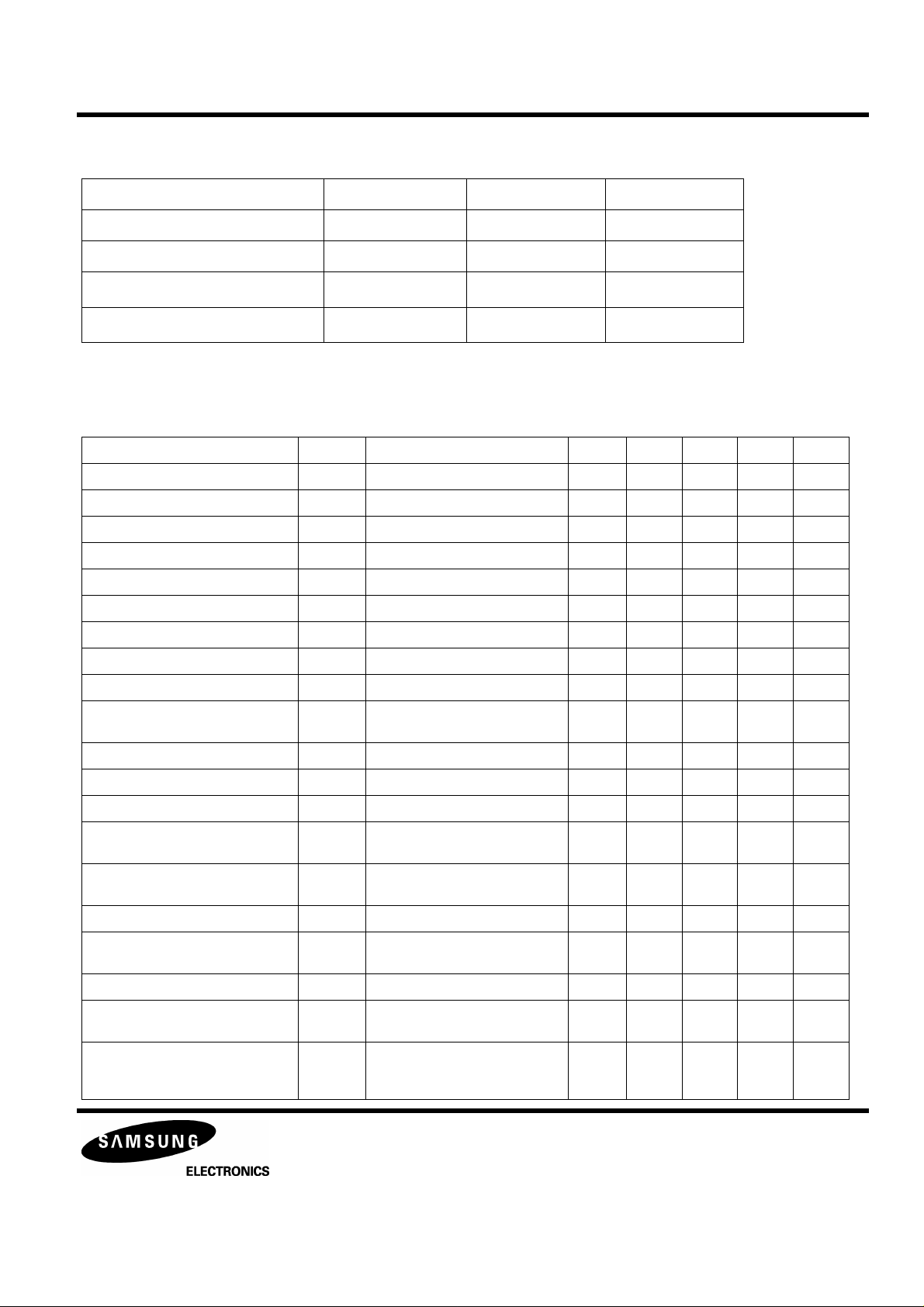

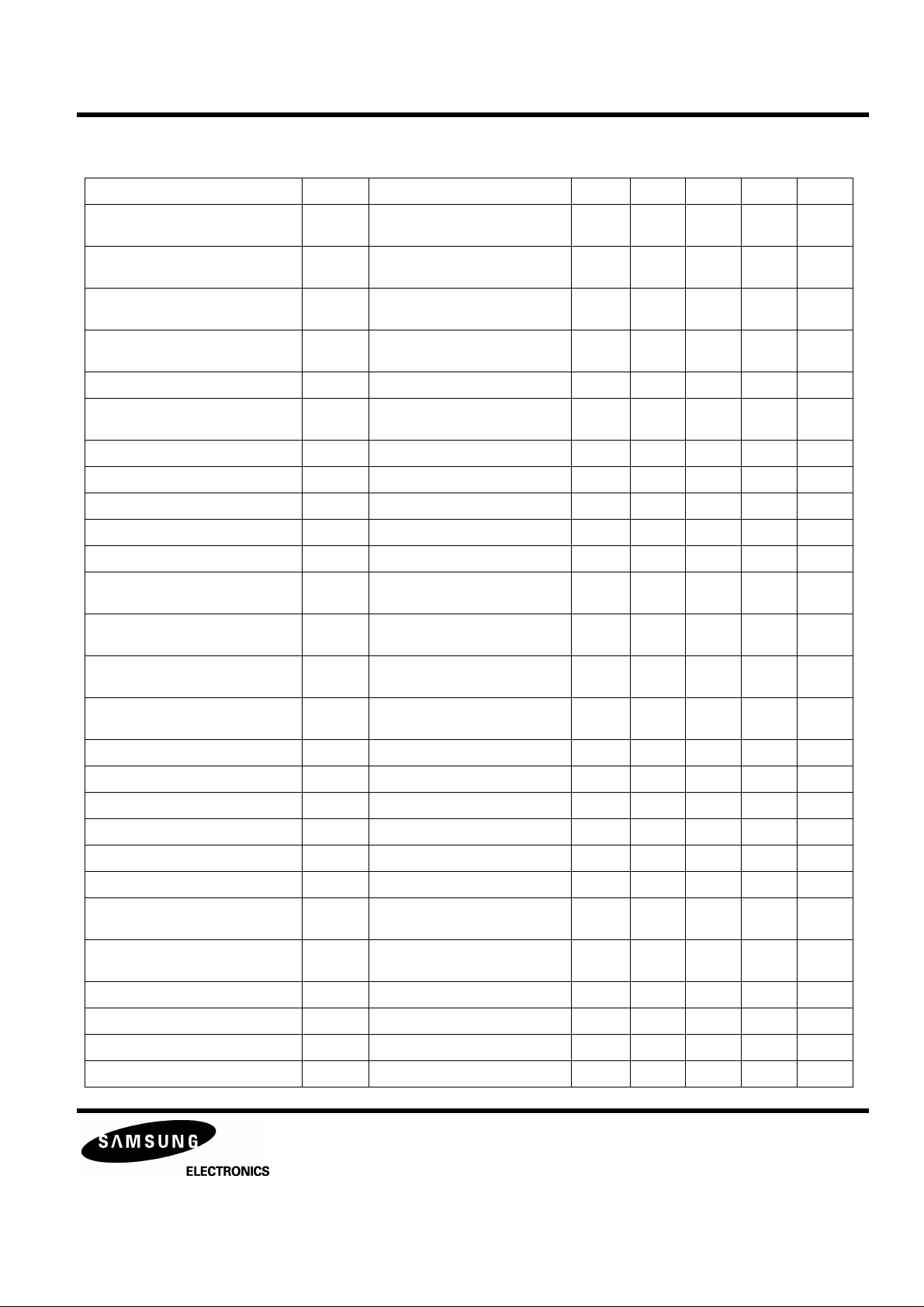

Table 2. Absolute Maximum Ratings

Characteristic Symbol Value Unit

Supply Voltage Vmax 6 V

Power Dissipation PD 200 mW

PRELIMINARY

Operating Temperature

Storage temperature

T

T

OPR

STG

-20 ~ +70

-55 ~ +150

o

C

o

C

ELECTRICAL CHARACTERISTICS

Table 3. Electrical Characteristics

(Ta=25°C, VDD = DVDD = VCC = +5V, VSS = DVSS = GND = VSSP = 0V )

Characteristic Symbol Test Conditions Output Min Typ Max Unit

Supply Current High ICCHI VCC=6V,No load - 20 40 60 mA

Supply Current Typ ICCTY VCC=5V,No Load - 12 30 48 mA

Supply Current Low ICCLO VCC=3.4V,No Load - 10 25 40 mA

RF Amp Offset Voltage Vrfo input open pin 74 -80 0 +80 mV

RF Amp Voltage Gain Grf SG3 f=10KHz,40mVp-p,sine pin 74 25.1 28.1 31.1 dB

RF THD Grfmd SG3 f=1KHz,40mVp-p,sine pin 74 - - 5 %

RF Amp Max. Output Voltage Vrfpp1 SG3 DC 2.7V pin 74 3.8 - - V

RF Amp Min. Output Voltage Vrfpp2 SG3 DC 2.3V pin 74 - - 1.2 V

Focus Error Amp Offset Voltage Vfeo1 input open pin 59 -450 -250 -50 mV

Focus Error Amp Auto Offset

Voltage

Vfeo2 WDCH=88.2KHz Pulse ,$841 pin 59 -35 0 35 mV

Focus Error Amp PD1 Voltage Gain Gfe1 SG3 f=10KHz,32mVp-p,sine pin 59 27 30 33 dB

Focus Error Amp PD2 Voltage Gain Gfe2 SG3 f=10KHz,32mVp-p,sine pin 59 27 30 33 dB

Focus Error Amp Voltage Difference Gfe∆ ∆Gfe1-∆Gfe1 pin 59 -3 0 +3 dB

Focus Error Amp Max. Output

Voltage

Focus Error Amp Min. Output Volt-

age

AGC Max Gain Gagc SG4 f=500KHz,20mVp-p,sine pin 76 16 19 22 dB

AGC EQ Gain Geq Gain Difference of Gagc at

AGC Gain2 Gagc2 SG4 f=500KHz,0.5Vp-p,sine pin 76 3.5 6 9 dB

AGC Cpmpress Ratio Cagc Gain Difference of Gagc2 at

AGC Frequency Fagc Gain Difference

Gfepp1 SG3 DC 2.7V pin 59 4.4 - - V

Gfepp2 SG3 DC2.3V pin 59 - - 0.6 V

pin 76 0 1 2 dB

f=1.5MHz

pin 76 0 2.5 5 dB

0.1Vp-p

pin 76 -1.5 0 2.5 dB

SG4 f=1.5MHz,0.1Vp-p,sine

and f=500KHz,0.1Vp-p,sine

M/M-97-P006

1997. 10. 17

7

PRELIMINARY

KB9223 / KB9223-L

RF AMP & SERVO SIGNAL PROCESSOR

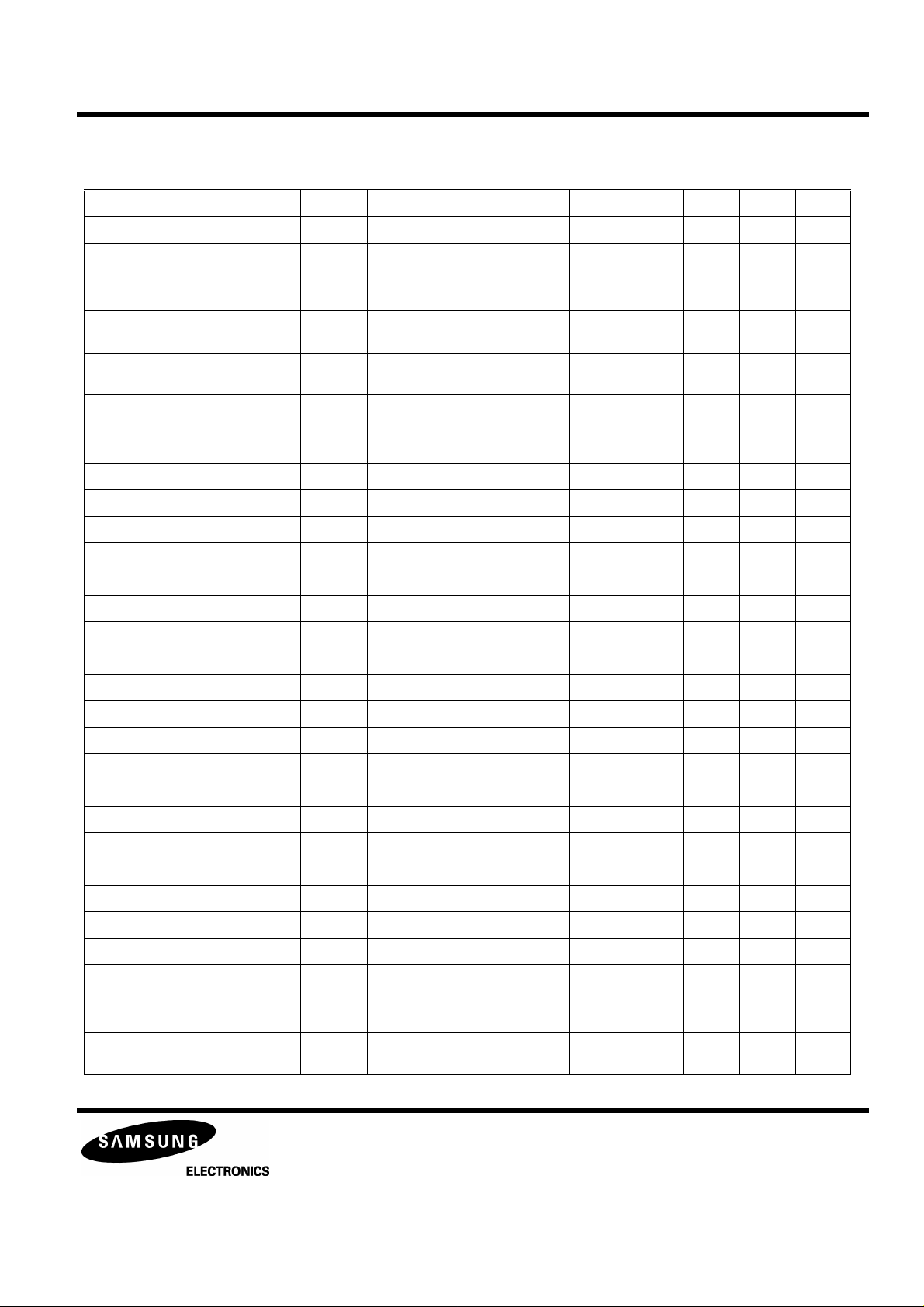

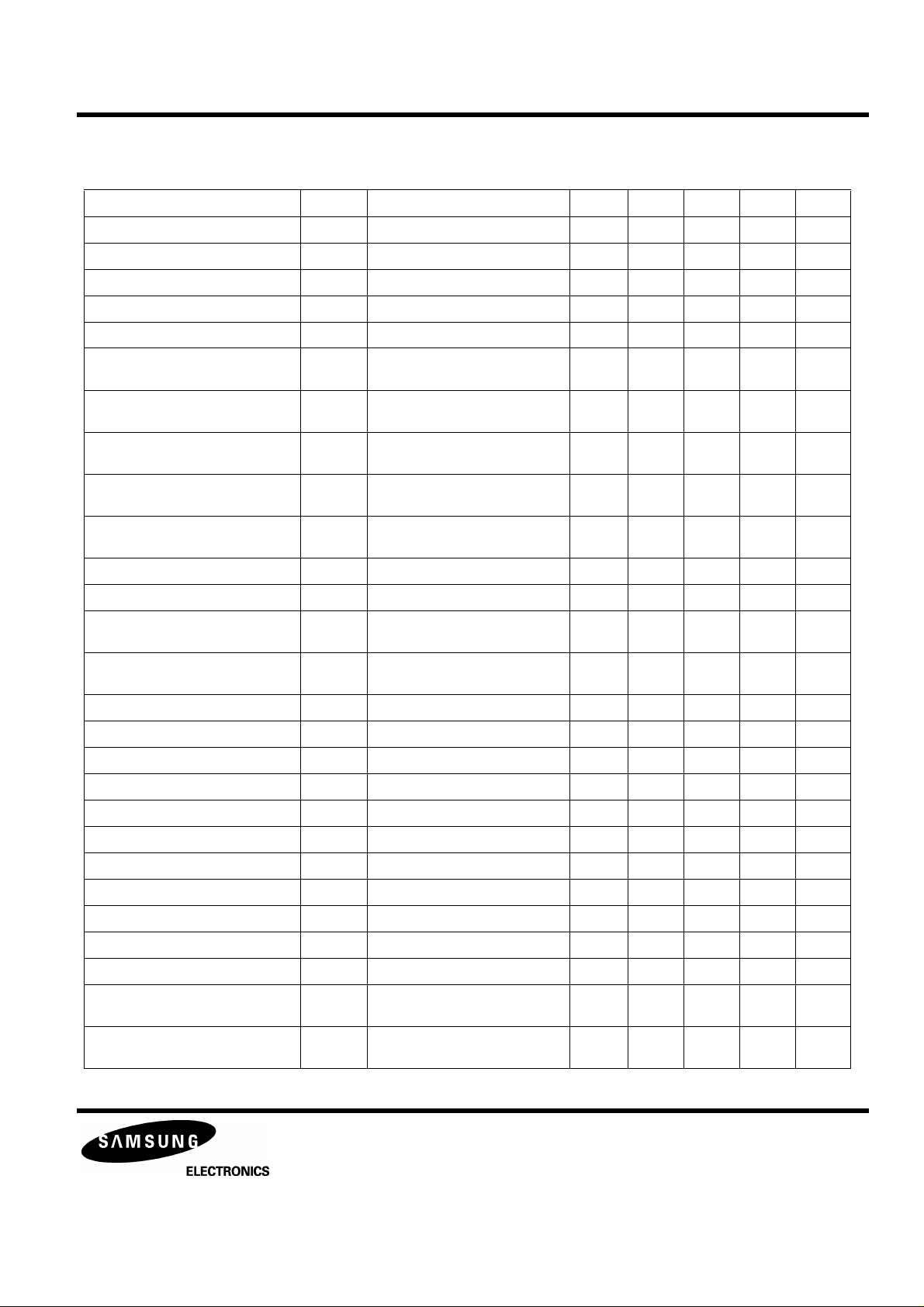

Table 3. Electrical Characteristics (Continued)

(Ta=25°C, VDD = DVDD = VCC = +5V, VSS = DVSS = GND = VSSP = 0V )

Characteristic Symbol Test Conditions Output Min Typ Max Unit

Tracking Error Offset Voltage Vteo $800,$820,input open pin 54 -50 0 +50 mV

Tracking Error Amp Voltage Gain F Gtef $800,$820

SG3 0.3Vp-p,10KHz,sine

Tracking Error AmpVoltage Gain E Gtee SG3 0.3Vp-p,40KHz,sine pin 54 -0.75 2.25 5.25 dB

Tracking Error Amp

Voltage Gain Difference

Tracking Error Amp

Maximum Output Voltage H

Tracking Error Amp

Minimum Output Voltage L

Tracking Error Amp Gain up F Tguf $830 SG3 0.3Vp-p,10KHz,sine pin 54 8.0 11.0 14.0 dB

Tracking Error Amp Gain up E Tgue $830 SG3 0.3Vp-p,10KHz,sine pin 54 5.3 8.3 11.3 dB

Tracking Gain Normal Fgfn SG3 0.3Vp-p,10KHz,sine,$820 pin 54 2.1 5.1 8.1 dB

Tracking F Gain 1 Fgf1 SG3 0.3Vp-p,10KHz,sine,$821 pin 54 0.1 3.1 6.1 dB

Tracking F Gain 2 Fgf2 SG3 0.3Vp-p,10KHz,sine,$822 pin 54 -1.7 1.3 4.3 dB

Tracking F Gain 3 Fgf3 SG3 0.3Vp-p,10KHz,sine,$824 pin 54 -5.0 -2.0 1.0 dB

Tracking F Gain 4 Fgf4 SG3 0.3Vp-p,10KHz,sine,$824 pin 54 -9.2 -6.2 -3.2 dB

Tracking E Balance Normal Tben SG3 0.3Vp-p,10KHz,sine,$800 pin 54 -0.27 2.27 5.27 dB

Tracking E Balance 1 Tbe1 SG3 0.3Vp-p,10KHz,sine,$801 pin 54 -0.51 2.51 5.51 dB

Tracking E Balance 2 Tbe2 SG3 0.3Vp-p,10KHz,sine,$802 pin 54 -0.74 2.74 5.74 dB

Tracking E Balance 3 Tbe3 SG3 0.3Vp-p,10KHz,sine,$804 pin 54 0.17 3.17 6.17 dB

Gte∆ Gtef-Gtee pin 54 -0.25 2.75 5.75 dB

Vtepp1 DG3 DC 4.5V pin 54 3.5 - - V

Vtepp2 SG3 DC 0.5V pin 54 - - 1.5 V

pin 54 2.1 5.1 8.1 dB

Tracking E Balance 4 Tbe4 SG3 0.3Vp-p,10KHz,sine,$808 pin 54 1.03 4.03 7.03 dB

Tracking E Balance 5 Tbe5 SG3 0.3Vp-p,10KHz,sine,$810 pin 54 2.63 5.63 8.63 dB

FGFN-FGF1 ∆FG1 - - 0 1.5 3 dB

FGFN-FGF2 ∆FG2 - - 0.5 2.0 3.5 dB

FGFN-FGF3 ∆FG3 - - 2.0 3.25 4.5 dB

FGFN-FGF4 ∆FG4 - - 3.0 4.25 5.5 dB

TBE5 - TBE4 ∆TB1 - - 0.6 1.6 2.6 dB

TBE4 - TBE3 ∆TB2 - - -0.14 0.86 1.86 dB

TBE3 - TBE2 ∆TB3 - - -0.57 0.43 1.43 dB

TBE2 - TBE1 ∆TB4 - - -0.77 0.23 1.23 dB

APC PSUB Voltage 1 Vapc1 LDON,$853,PN=open,

SG4 GND+85mV

APC PSUB Voltage 2 Vapc2 LDON,$853,PN=open,

SG4 GND+185mV

pin 70 - - 1.2 V

pin 70 3.8 - - V

M/M-97-P006

1997. 10. 17

8

PRELIMINARY

RF AMP & SERVO SIGNAL PROCESSOR

KB9223 / KB9223-L

Table 3. Electrical Characteristics (Continued)

(Ta=25°C, VDD = DVDD = VCC = +5V, VSS = DVSS = GND = VSSP = 0V )

Characteristic Symbol Test Conditions Output Min Typ Max Unit

APC NSUB Voltage 1 Vapc3 LDON,$857,PN=2.5V,

SG4 GND+95mV

pin 70 3.8 - - V

APC NSUB Voltage 2 Vapc4 LDON,$857,PN=2.5V,

SG4 GND+165mV

APC LD Off Voltage 1 Vapc5 LDOFF,$85C,PN=open,SG4

2.5V

APC LD Off Voltage 2 Vapc6 LDOFF,$858,PN=2.5V.SG4 2.5V pin 70 - - 1.0 V

APC Maximum Output Current H Vapc7 LDON,$854,PN=open, SG4 GND

APC Minimum Output Current L Vapc8 LDON,$854,SG4 GND + 85mV pin 70 - - 2.5 V

Mirror Maximum Output Voltage H Vmirh SG4 2.1V+0.8Vp-p,1KHz,sine pin 39 4.3 - - V

Mirror Minimum Output Voltage L Vmirl SG4 2.1V+0.8Vp-p,1KHz,sine pin 39 - - 0.7 V

Mirror Minimum Operating

Frequency

Mirror Maximum Operating

Frequency

Mirror AM Frequency Characteristic Fmir SG4 2.1V+0.8Vp-p

Mirror Minimum Input Voltage Vmir SG4 2.1V+0.2Vp-p,10KHz,sine pin 39 - 0.1 0.2 V

Mirror Maximum Input Voltage Vmih SG4 2.1V+1.8Vp-p,10KHz,sine pin 39 1.8 - - V

FOK Threshold Voltage Vfokt SG4 2.25V~2.0V,DCsweep,

Fmirh SG4 2.1V+0.8Vp-p,900Hz,sine pin 39 - 550 900 Hz

Fmirb SG4 2.1V+0.8Vp-p,30KHz,sine pin 39 30 75 - KHz

+ 185mV

600Hz,fc=500KHz

55% modulation

10mV step

pin 70 - - 1.2 V

pin 70 4.0 - - V

pin 70 2.5 - - V

pin 39 - 400 600 Hz

pin 40 -420 -360 -300 mV

FOK Output Voltage H Vfokh SG4 DC 1.5V pin 40 4.3 - - V

FOK Output Voltage L Vfokl SG4 DC 2.5V pin 40 - - 0.7 V

Defect Output Voltage H Vdfcth $863,SG3 2.520V+0.04Vp-p,

f=1Khz,sine

Output Voltage L Vdfcth $863,SG3 2.520V+0.04Vp-p,

f=1Khz,sine

Focus Loop Mute Fmute SG2 2.5V+0.1Vp-p,1KHz,sine pin 48 -100 0 100 mV

Tracking Loop Mute Tmute SG2 2.5V+0.1Vp-p,1KHz,sine pin 50 -100 0 120 mV

Interruption Imute SG2 2.5V+0.1Vp-p,1KHz,sine pin 50 -100 0 120 mV

Defect Bottom Voltage Fdfct1 SG3 2.520 V+0.04Vp-p,

1KHz,sine

Defect Max Freq. Voltage Fdfct2 SG3 2.520V+0.04Vp-p,

2KHz,sine

Defect Minimum Input Voltage Vdfct1 SG 3 2.510V+0.020Vp-p,

1KHz,sine

pin 41 4.3 - - V

pin 41 - - 0.7 V

pin 41 - 670 1000 Hz

pin 41 2.0 4.7 - KHz

pin 41 - 0.3 0.5 V

M/M-97-P006

ELECTRONICS

1997. 10 .17

14

PRELIMINARY

KB9223 / KB9223-L

RF AMP & SERVO SIGNAL PROCESSOR

Table 3. Electrical Characteristics (Continued)

(Ta=25°C, VDD = DVDD = VCC = +5V, VSS = DVSS = GND = VSSP = 0V )

Characteristic Symbol Test Conditions Output Min Typ Max Unit

Defect Maximum Input Voltage Vdfct2 SG32.535V+0.070Vp-p,

EFM Duty Voltage 1 Defm1 SG4 2.5V+0.75Vp-p,

EFM Duty Voltage 2 Defm2 SG42.75V+0.75Vp-p,

EFM Minimum input Voltage Vefm1 SG4 2.5V+0.12Vp-p,

EFM Maximum input Voltage Vefm2 SG4 2.5V+1.8Vp-p,750KHz,sine pin 33 1.8 - - V

EFM Maximum Operating

Frequency

FZC Threshold Voltage Vfzc DC 2.5V+38mV,100mV pin 31 39 69 100 mV

ATSC Threshold Voltage 1 Vatsc1 $10,SG2 DC 2.5V-6mV,-45mV pin 31 -67 -32 -7 mV

ATSC Threshold Voltage 2 Vatsc2 SG2 DC 2.5V+6mV,+45mV pin 33 7 32 67 mV

TZC Threshold Voltage Vtzc $20,SG2 DC 2.5V-20mV,+20mV pin 31 -30 0 30 mV

SSTOP Threshold Voltage Vsstop $30,SG2 DC 2.5V-71mV,-30mV pin 31 -100 -50 -30 mV

Tracking gain window voltage

Tracking gain window range

Tracking balance window voltage

Fefm SG4 2.5V+0.75Vp-p,4MHz pin 33 4 - - MHz

VtGW $840+$830 SG2 2.5V 2.9V 5mV

VTGW2 $848+$830 SG2 2.5V 5mV DC

VTBW $844+$810 SG2 2.555V ~

1KHz,sine

750KHz,sine

750KHz,sine

750KHz,sine

DC

sweep

2.475V 5mV DC sweep

pin 41 1.8 - - V

pin 32 -50 0 50 mV

pin 32 0 50 100 mV

pin 33 - - 0.12 V

pin 30 200 250 300 mV

pin 30 100 150 200 mV

pin 31 -25 15 55 mV

Tracking balance window range

Vreg Threshold Voltage Vreg - pin 21 3.2 3.4 3.6 V

Center Voltage VCVO 2.5V Reference pin 71 -100 0 100 mV

VREF Current Drive Voltage 1 VCVO1 2.5V Reference pin 71 -100 0 100 mV

VREF Current Drive Voltage 2 VCVO2 2.5V Reference pin 71 -100 0 100 mV

Post CH1 Freq. Characteristic Fpos1 SG1 2.5V+1Vp-p,40KHz,sine pin 13 -4.5 -3.0 -1.5 dB

Post CH2 Freq. Characteristic Fpos2 SG1 2.5V+1Vp-p,40KHz,sine pin 12 -4.5 -3.0 -1.5 dB

Post CH1 Mute Mute1 Mute=5V

Post CH2 Mute Mute2 Mute=5V

Focus Loop DC Gain Gf $08,SG2 DC 2.6V,2.4V average pin 48 19.0 21.5 24.0 dB

Focus Off Offset Vosf1 $00 pin 48 -100 0 100 mV

Focus On Offset Vofs2 $08,DC 2.5V pn 48 0 250 500 mV

Focus Auto Offset Vaof $842,WDCK,after100ms pin 48 -65 0 65 mV

VTBW2 $844+$810 SG2 2.555V ~

2.470V 5mV DC sweep

SG1 2.5V+1Vp-p,1KHz,sine

SG1 2.5V+1Vp-p,1KHz,sine

pin 31 -25 15 55 mV

pin13 - - -35 dB

pin 12 - - -35 dB

M/M-97-P006

1997. 10. 17

10

PRELIMINARY

KB9223 / KB9223-L

RF AMP & SERVO SIGNAL PROCESSOR

Table 3. Electrical Characteristics (Continued)

(Ta=25°C, VDD = DVDD = VCC = +5V, VSS = DVSS = GND = VSSP = 0V )

Characteristic Symbol Test Conditions Output Min Typ Max Unit

Focus Output Voltage H Vfoh1 $08,DC 3.0V pin 48 4.40 - - V

Focus Output Voltage L Vfol1 $08,DC 2.0V pin 48 - - 0.60 V

Focus Output Drive Voltage H Vfoh2 $08,DC 3.0V pin 48 3.68 - - V

Focus Output Drive Voltage L Vfol2 $08,DC 2.0V pin 48 - - 1.32 V

Focus Oscillation Voltage Vosc $08,DC2.5V pin 48 0 100 200 mV

Focus Feed Through Gff Gain Difference at Servo on

and off

Focus AC Gain 1 Gfa1 $08,

SG2 2.5V+0.1Vp-p,1.2KHz,sine

Focus AC Phase 1 Pfa1 $08,

SG2 2.5V+0.1Vp-p,1.2KHz,sine

Focus AC Gain 2 Gfa2 $08,

SG2 2.5V+0.1Vp-p,2.7KHz,sine

Focus AC Phase 2 Pfa2 $08,

SG2 2.5V+0.1Vp-p,2.7KHz,sine

Focus Search Voltage1 Vfs1 $30+$02 pin 48 -0.64 -0.50 -0.36 V

Focus Search Voltage2 Vfs2 $30+$03 pin 48 0.36 0.50 0.64 V

Focus Loop Total Gain Gftg Focus PD gain + Focus loop DC

gain

Tracking DC Gain Gto $25

SG2 DC 2.3V,2.7V average gain

Tracking Off Offset Vost1 $20 pin 50 -100 0 100 mV

Tracking On Offset Vost2 SG2 DC 2.5V,$25 pin 50 -100 0 120 mV

Tracking Oscillation Voltage Vosa1 $25,SG2 DC2.5V pin 50 0 100 200 mV

Tracking gain boost for ATSC Gatsc 2.5V+0.1Vp-p,1KHz,sine pin 50 17.5 20.5 23.5 dB

pin 48 - - -35 dB

pin 48 19.0 23.0 27.0 dB

pin 48 40 65 90 deg

pin 48 14.0 18.5 23.0 dB

pin 48 40 65 90 deg

pin 48 49.5 51.5 53.5 dB

pin 50 13.5 15.5 17.5 dB

Tracking gain boost on LOCK (L) Glock 2.5V+0.1Vp-p,1KHz,sine pin 50 17.5 20.5 23.5 dB

Tracking Output Voltage H Vth1 $25,SG2 DC 1.0V pin 50 4.48 - - V

Tracking Output Voltage L Vtl1 $25SG2 ,DC 4.0V pin 50 - - 0.52 V

Tracking Output Drive Voltage H Vth2 $25,SG2 DC2.0V pin 50 3.68 - - V

Tracking Output Drive Voltage L Vtl2 $25, SG2 DC3.0V pin 50 - - 1.32 V

Tracking Jump Voltage 1 Vtj1 $2C pin 50 -0.64 -0.5 -0.36 V

Tracking Jump Voltage 2 Vtj2 $28 pin 50 0.36 0.5 0.64 V

Tracking Feed Through Gtf Gain Difference at Tracking servo

on and off

Tracking AC Gain 1 Gta1 $10,$25,SG2 2.5V+0.1Vp-p,

1.2KHz,sine

pin 50 - - -39 dB

pin 50 9.0 12.5 16.0 dB

M/M-97-P006

1997. 10. 17

11

Loading...

Loading...