Samsung KB2514 Datasheet

JAN. 2000

Ver 0.1

DATA SHEET

KB2514

Preliminary

Preliminary

OSD PART

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

VIDEO AMP MERGED OSD PROCESSOR

The KB2514 is a very high frequency video amplifier &

wide range OSD processor 1 chip system with I2C Bus

control used in monitors. It contains 3 matched R/G/B video

amplifiers with OSD processor and provides flexible

interfacing to I2C Bus controlled adjustment systems.

FUNCTIONS

• R/G/B video amplifier

• OSD processor

• I2C bus control

• Cut-off brightness control

• R/G/B sub contrast/cut-off control

• Half tone

FEATURES

VIDEO AMP PART

32-DIP-600A

ORDERING INFORMATION

Device Package Operating Temperature

KB2514 32-DIP-600A -20 °C − +75 °C

• 3-channel R/G/B video amplifier, 150MHz @f-3dB

• I2C bus control items

- Contrast control: -38dB

- Sub contrast control for each channel: -12dB

- Brightness control

- OSD contrast control: -38dB

- Cut-off brightness control (AC coupling)

- Cut-off control for each channel (AC coupling)

- Switch registers for SBLK and video half tone and

CLP/BLK polarity selection and INT/EXT CLP selection

• Built in ABL (automatic beam limitation)

• Built in video input clamp, BRT clamp

• Built in video half tone (3mode) function on OSD

pictures

• Capable of 8.0Vp-p output swing

• Improvement of rise & fall time (2.2ns)

• Cut-off brightness control

• Built in blank gate with spot killer

• Clamp pulse generator

• OSD intensity

• BLK, CLP polarity selection

• Clamp gate with anti OSD sagging

• Built in 1K-byte SRAM

• 256 ROM fonts (each font consists of 12 × 18

dots.)

• Full screen memory architecture

• Wide range PLL available (15kHz ~ 90kHz,

Reference 800 X 600)

• Programmable vertical height of character

• Programmable vertical and horizontal

positioning

• Character color selection up to 16 different

colors (in a units of character)

• Programmable background color (up to 16

colors)

• Character blinking and shadowing

• Character scrolling

• 72MHz pixel frequency from on-chip PLL

(Reference 800 X 600)

• Full white pattern generation function

1

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

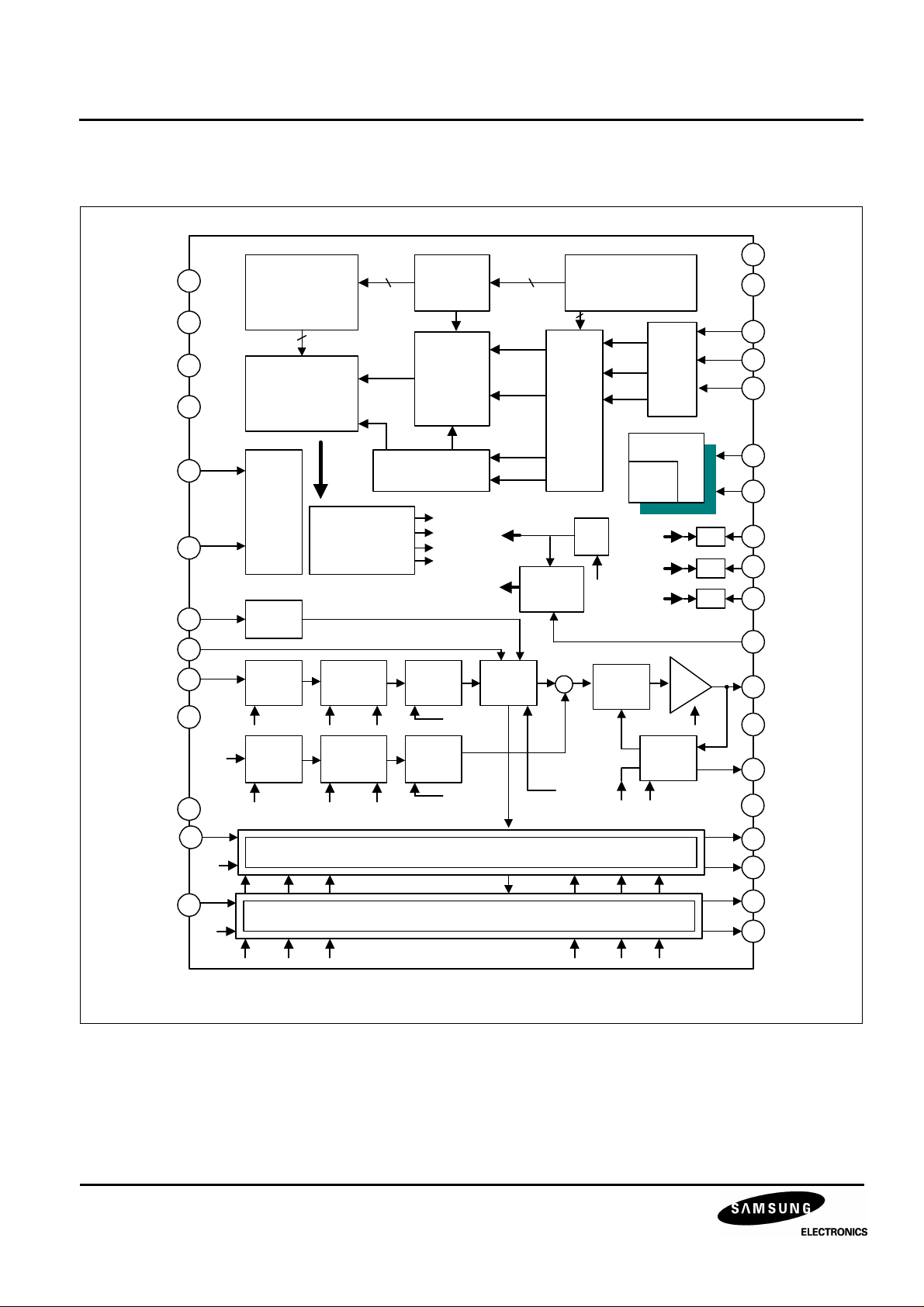

BLOCK DIAGRAM

6

VDDA

VDD

VSS

VCC3

GND3

VREF1

VREF

ABL

CONT_CAP

RIN

GND1

VCC1

31

28

11

12

15

13

9

4

5

8

7

R OSD

ROM

(448 x 18 x 12)

Font Data

Output Stage

Band

Gap.Ref

ABL

Video

Input

Clamp

CLP

OSD

Input

Cilp.

HT DET.

12

R/G/B OSD

FBLK

Intensity

Multi (3 mode)

Half Tone

Video

Half Tone

SW

OSD

Half Tone

SW

FBLK I2C

9 16

ROM

Address

Display Ctrl

H/V/CLK Ctrl

Timing Controller

I2CFBLK

(480 x 16)

Ctrl Font

Controller

Sub

Cont.

Control

OSD

Cont.

Control

ROM

Display

H/V/CLK Ctrl

RGB OSD

FBL

INTE

HT DET.

I2C

I2C

RAM Data

Frame Ctrl

ROM Ctrl

Frame Ctrl

ROM Ctrl

BLK

CLP

Video

Contrast

Control

Register

BLK

Int

Clamp

Pulse

Gen.

+

I2C Cont. Cntl

Data Receiver

16Ctrl Data

CLK

H_Pulse

V_Pulse

Latches

I2C bus

decoder

D/A

R cut off

G cut off

HFLB

B cut off

Sub

Cont.

Control

OSD

PLL

Amp

Out

Birght

Control

CLPI2C

V/I

V/I

V/I

BLK

2

VSSA

32

HFLB

1

VFLB

3

VCO_IN_P

30

SDA

SCL

29

27

RCT

26

GCT

25

BCT

10

CLP_IN

24

R OUT

22

VCC2

23

R CLP

GND2

19

GIN

14

20

G CLP

G-CHANNEL

21

BIN

G OSD

CLP HT DET. FBLK CLP BLKI2C

16

17

G OUT

B CLP

B-CHANNEL

18

B OSD

CLP HT DET. FBLK CLP BLKI2C

B OUT

Figure 1. Functional Block Diagram

2

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

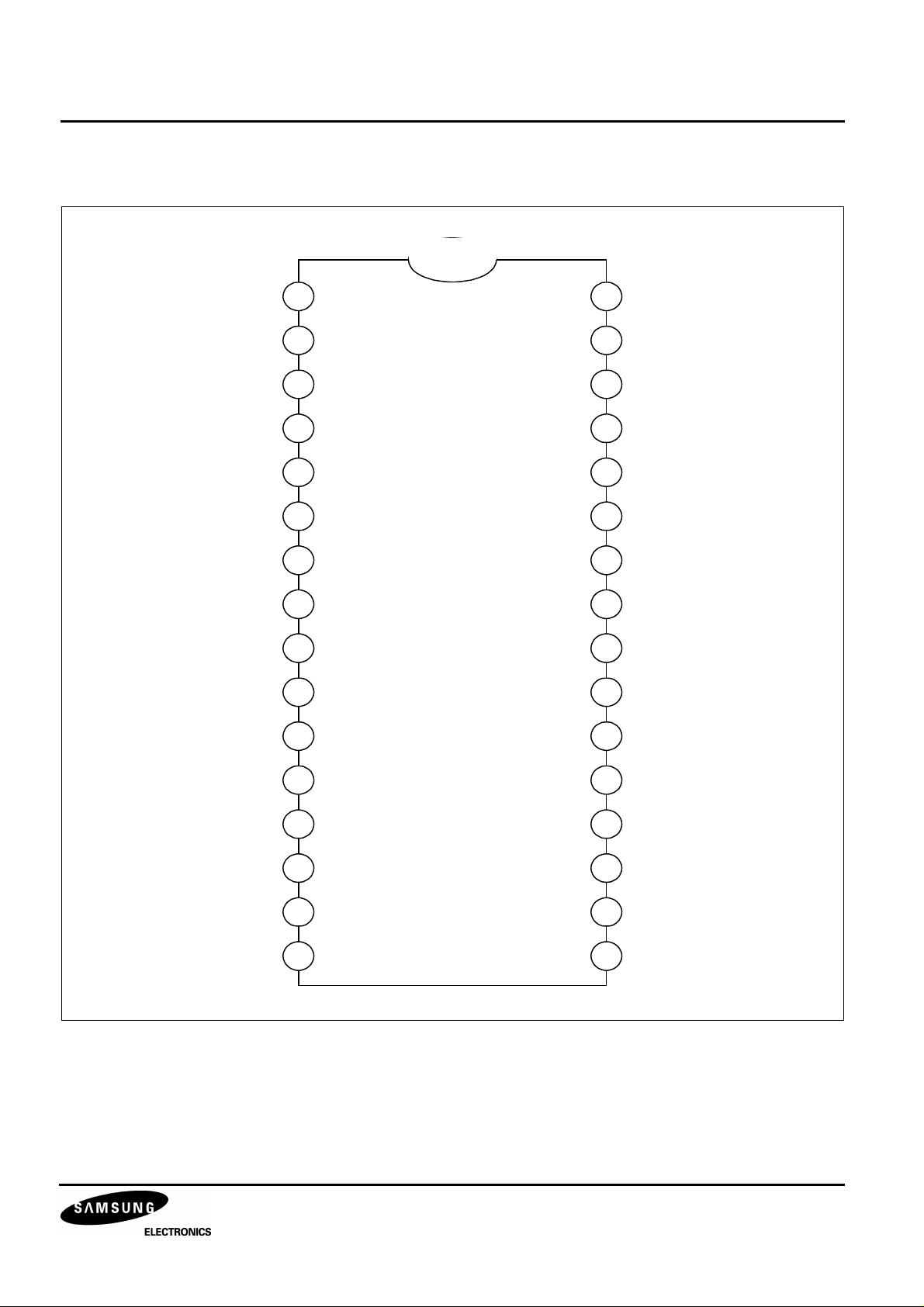

PIN CONFIGURATION

1

VFLB

VSSA

2

VCO_IN_P

3

4

VREF1

5

VREF

6

VDDA

CONT_CAP

7

ABL_IN

8

9

GND3

CLP_IN

10

VCC3

11

KB2514

KB2502

HFLB

VDD

SDA

SCL

VSS

RCT

GCT

BCT

ROUT

RCLP

VCC2

32

31

30

29

28

27

26

25

24

23

22

12

13

14

15

16

RIN

VCC1

GIN

GND1

BIN

Figure 2. Pin Configuration

GOUT

GCLP

GND2

BOUT

BCLP

21

20

19

18

17

3

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

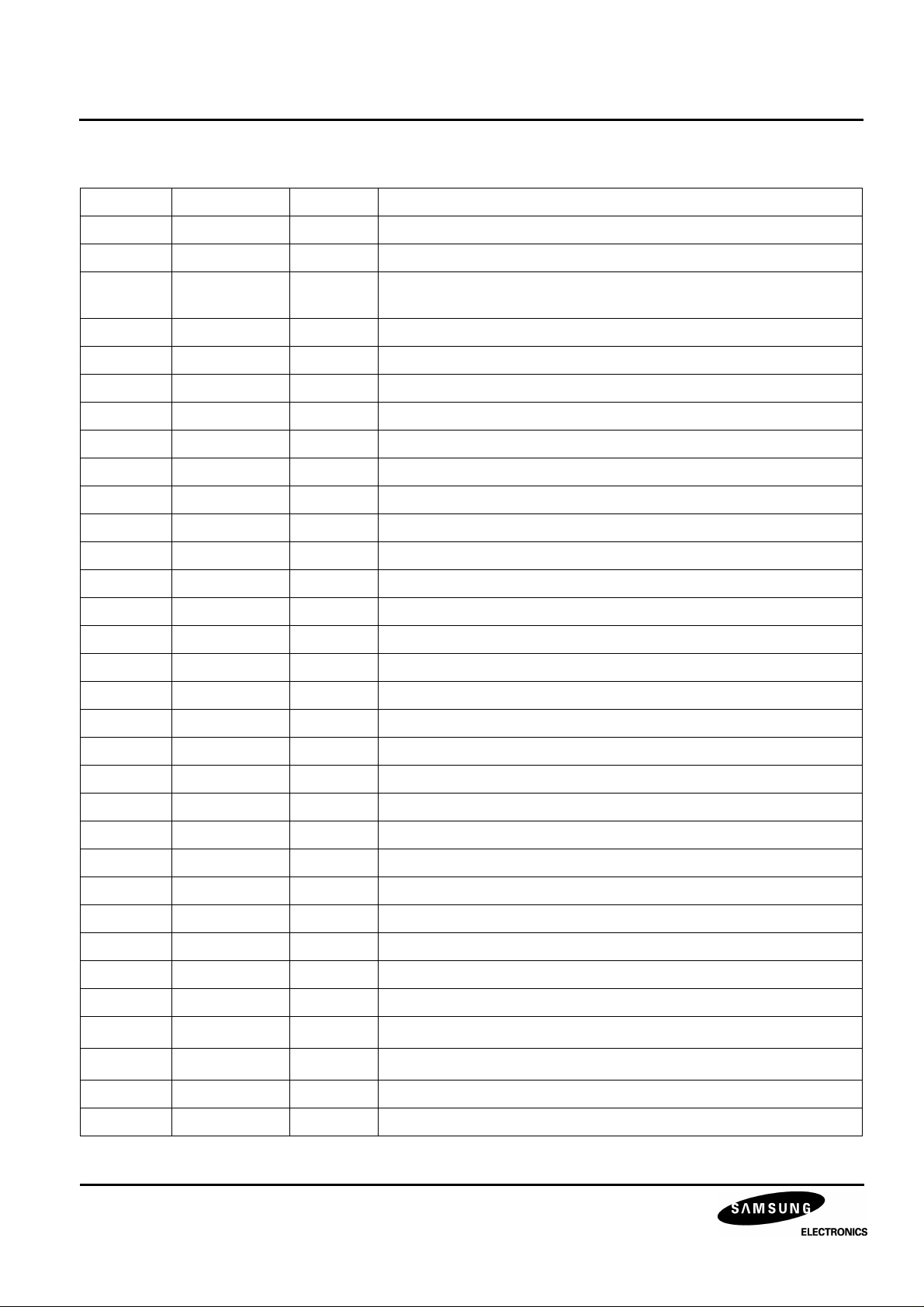

Table 1. Pin Configuration

Pin No. Symbol I/O Configuration

1 VFLB I Vertical flyback signal

2 VSSA - Ground (PLL part)

3 VCO_IN_P I

4 VREF1 O Charge pump output

5 VREF O PLL regulator filter

6 VDDA - +5V supply voltage for PLL part

7 CONT_CAP - Contrast control for AMP part

8 ABL - Auto beam limit.

9 GND3 - Ground for video AMP part(for AMP control)

10 CLP_IN - Video clamp pulse input

11 VCC3 - +12V supply voltage for video AMP part(for AMP control)

12 RIN I Video signal input (red)

13 VCC1 - +12V supply voltage for video AMP(for main video signal process)

14 GIN I Video signal input (green)

15 GND1 - Ground for video AMP part(for main video signal process)

16 BIN I Video signal input (blue)

17 BCLP - B output clamp cap

18 BOUT O Video signal output (blue)

This voltage is generated at the external loop filter and goes into the

input stage of the VCO.

19 GND2 - Ground for video AMP part(for video output drive)

20 GCLP - G output clamp cap

21 GOUT O Video signal output (green)

22 VCC2 - +12V supply voltage for video AMP part(for video output drive)

23 RCLP - R output clamp cap

24 ROUT O Video signal output (red)

25 BCT - B cut-off output

26 GCT - G cut-off output

27 RCT - R cut-off output

28 VSS - Ground for digital part

29 SCL I

30 SDA I/O

31 VDD - +5V supply voltage for digital part

32 HFLB I Horizontal flyback signal

Serial clock (I2C)

Serial data (I2C)

4

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

PIN DESCRIPTION

Table 2. Pin Description

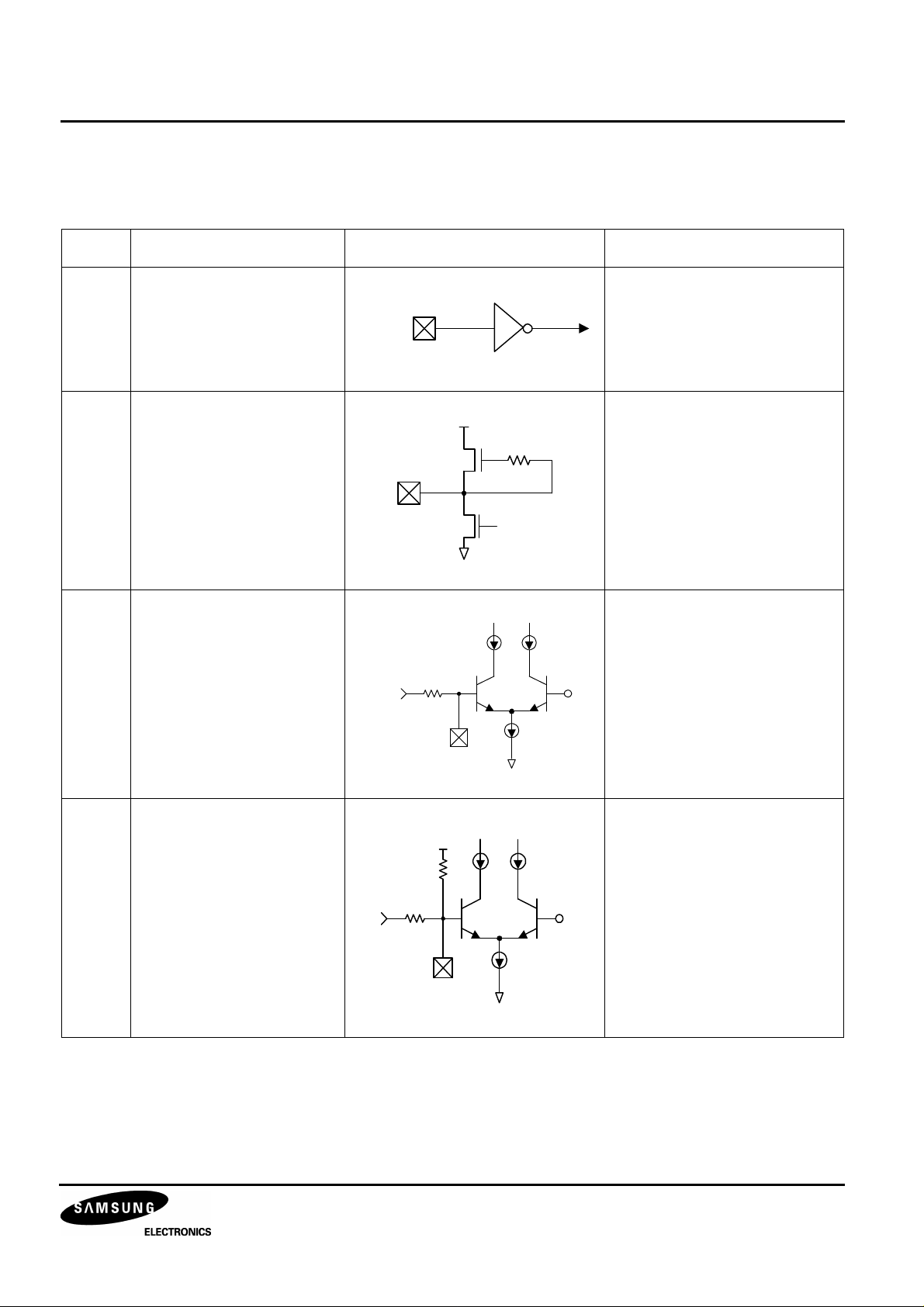

Pin No Pin Name Schematic Description

1

32

3

4

5

VFLB

HFLB

VCO_IN_P

VPEF1

VREF

7 Contrast cap

(CONT_CAP)

VFLB

HFLB

4.0K

FLB signal is in TTL level

Multi polarity input

PLL loop filter output

BandGap ref. output

Contrast cap range

(0.1uF ~ 5uF)

VrefI2C Data

100µA

8 ABL_IN

100K

2K

VCC

ABL input DC range

(1 ~ 4.5V)

VrefVref

250µA

5

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

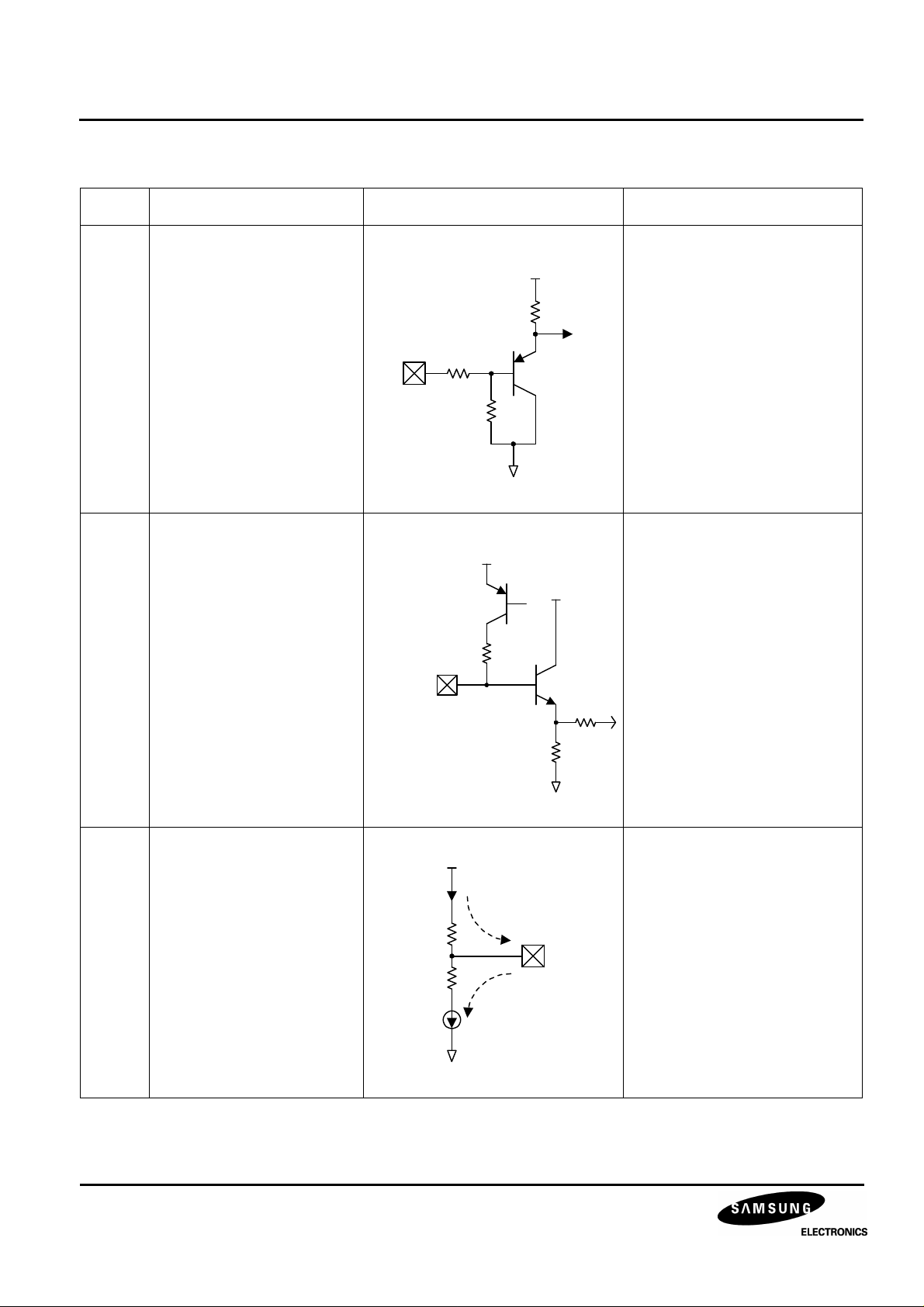

Table 2. Pin Description (Continued)

Pin No Pin Name Schematic Description

10 CLP_IN Multi polarity input

VCC

50K

Clamp gate pulse TTL level

input

10K

12

14

Red video input

(RIN)

Green video input

VCC

Max input video signal is 0.7

Vpp

VCC

(GIN)

16

Blue video input

(BIN)

Video_In

0.2K

17

20

23

Blue (B clamp cap)

Green (G clamp cap)

Red (R clamp)

0.2K

0.2K

12K

Brightness controlling actives by

charging and discharging of the

external cap. (0.1µF)

(During clamp gate)

CLP

Iclamp

6

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

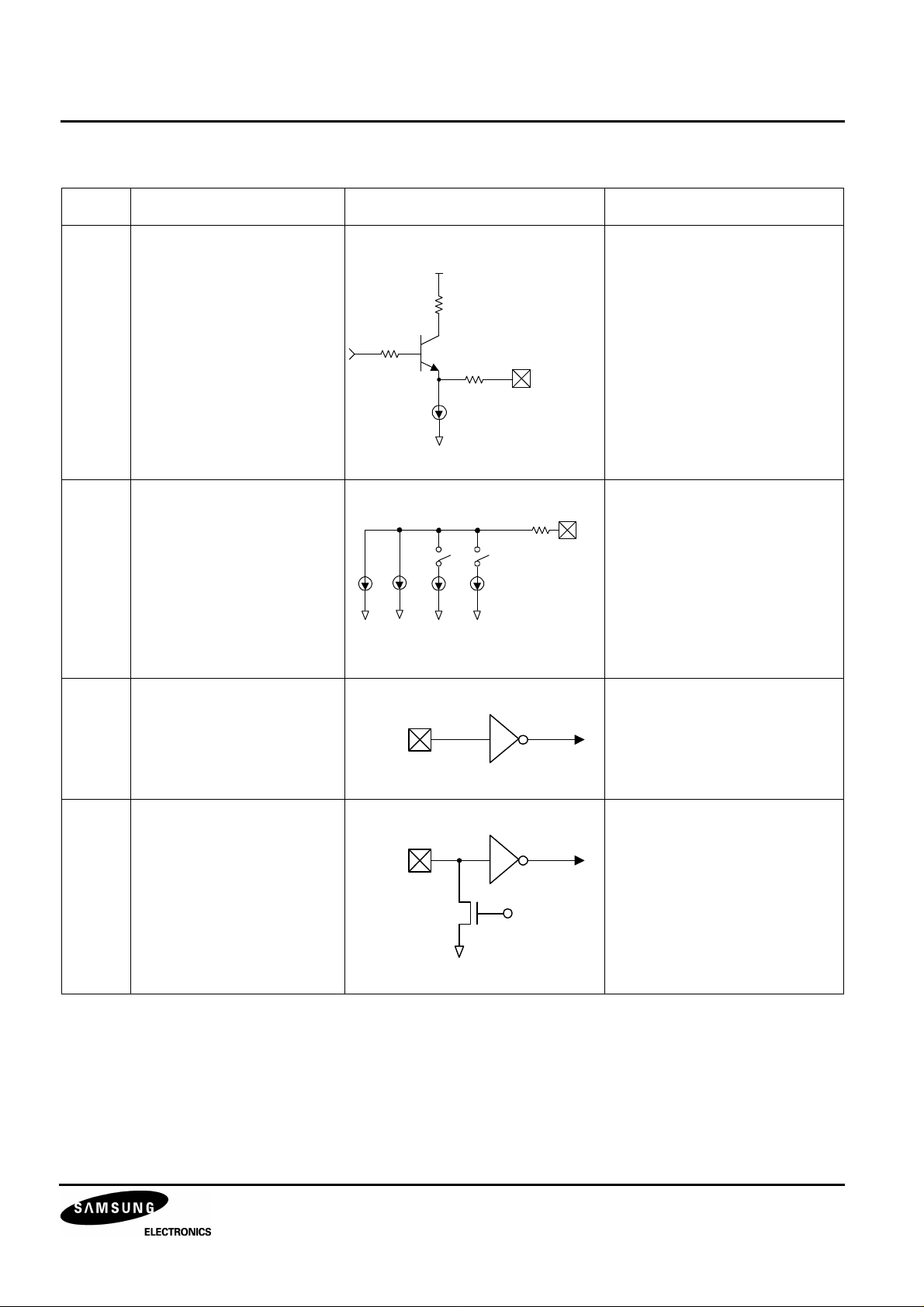

Table 2. Pin Description (Continued)

Pin No Pin Name Schematic Description

18

21

24

27

26

25

Blue video output

(BOUT)

Green video output

(GOUT)

Red video output

(ROUT)

Red cut-off control

(RCT)

Green cut-off control

(GCT)

Blue cut-off control

(BCT)

VCC

0.05K

0.5K

0.04K

Isink

0-600uA 0-200uA 50uA 100uA

Video_Out

0.2K

Video signal output

Cut-off control output

CTX

29 SCL

30 SDA

SCL

SDA

SCL

Serial clock input port of I2C bus

Serial data input port of I2C bus

ACK

7

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

ABSOLUTE MAXIMUM RATINGS

(see 1)

(Ta = 25 °C)

Table 3. Absolute Maximum Ratings

Value

No Item Symbol

Min Typ Max

1 Maximum supply voltage

2

Operating temperature

(see 2)

V

CC

V

DD

Topr -20 - 75 °C

- - 13.2

- - 6.5

3 Storage temperature Tstg -65 150 °C

4 Operating supply voltage

V

V

5 Power dissipation P

CCop

DDop

D

11.4 12.0 12.6

4.75 5.00 5.25

- - W

THERMAL & ESD PARAMETER

Table 4. Thermal & ESD Parameter

Unit

V

V

(see 3)

No Item Symbol

Value

Min Typ Max

Thermal resistance

1

(junction-ambient)

θja - 48 - °C/W

2 Junction temperature Tj - 150 - °C

Human body model

3

(C = 100p, R = 1.5k)

Machine model

4

(C = 200p, R = 0)

HBM 2 - - KV

MM 300 - - V

5 Charge device model CDM 800 - - V

Unit

8

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

ELECTRICAL CHARACTERISTICS

DC ELECTRICAL CHARACTERISTICS

(Tamb = 25 °C, VCC = 12V, VDD = V

= 5V, ABL input voltage = 5V, HFLB input signal = S3, load resistors =

DDA

470Ω, except OSD part current 35mA, unless otherwise stated)

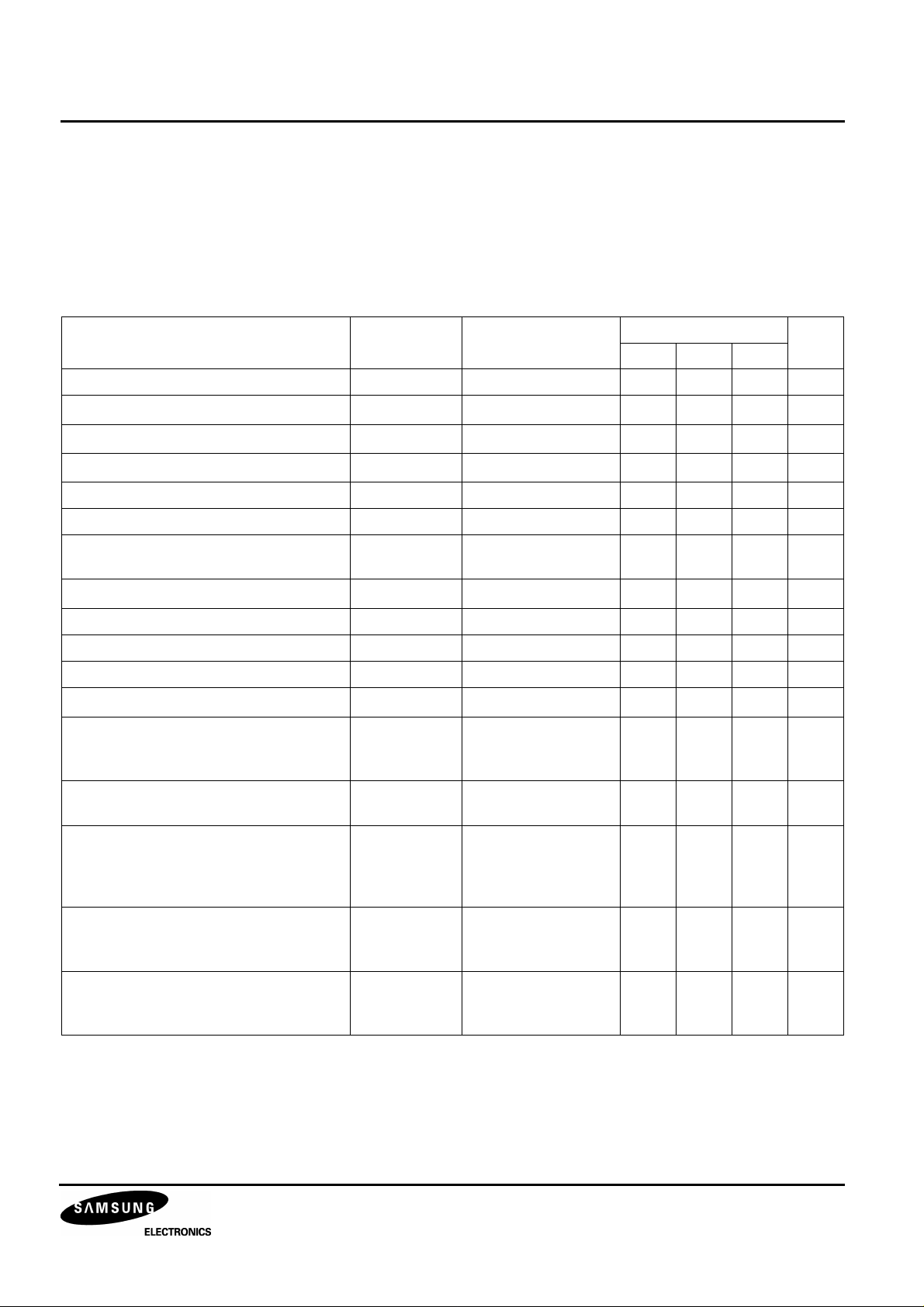

Table 5. DC Electrical Characteristics

Parameter Symbol Conditions

Supply current ICC

Minimum supply current ICC min VCC = 11.4V 95 110 120 mA

Maximum supply current ICC max VCC = 12.6V 105 130 140 mA

ABS supply current ICC abs VCC = 13.2V - - 175 mA

Video input bias voltage V bias 1.8 2.1 2.4 V

Video black level voltage (POR) V blackpor 1.20 1.50 1.80 V

Black level voltage channel difference (POR) ∆ V blackpor

Video black level voltage (FFH) V blackff

Black level voltage channel difference (FFH) ∆ V blackff ∆ 10 - - %

Video black level voltage (00H) V black00 04 = 00H - 0.2 0.5 V

Black level voltage channel difference (00H) ∆ V black00 ∆ 10 - - %

Spot killer voltage Vspot VCC = Var. 9.20 10.4 11.2 V

(see 4)

(see 5)

04 = FFH

(see 13)

Min Typ Max

100 125 130 mA

∆ 10 - - %

Value

2.2 2.7 3.2 V

Unit

Cut-off current (FFH) ICTff Pin25, 26, 27 = 12V

09 ~ 0B: FFH

0C: 00H

Cut-off current (00H) ICT00 Pin25, 26, 27 = 12V

09 ~ 0C: 00H

Cut-off brightness current (FFH) ICTBRTff Pin25, 26, 27 = 12V

09 ~ 0B: 00H

0C: FFH

Cut-off brightness current (80H) ICTBRT80 Pin25, 26, 27 = 12V

09 ~ 0B: 00H

0C: 80H

Cut-off offset current 1 ICS1 Pin25, 26, 27 = 12V

09 ~ 0C: 00H

0E: 11H

500 625 750 µA

- 2.0 5.0 µA

100 180 260 µA

50 90 130 µA

25 50 75 µA

9

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

Table 5. DC Electrical Characteristics (Continued)

Parameter Symbol Conditions

Value

Min Typ Max

Cut-off offset current 2 ICS2 Pin25, 26, 27 = 12V

50 100 130 µA

09 ~ 0C: 00H

0E: 12H

Soft BLK output voltage Vsblk 0D: 80H

- 0.2 0.5 V

0E: 14H

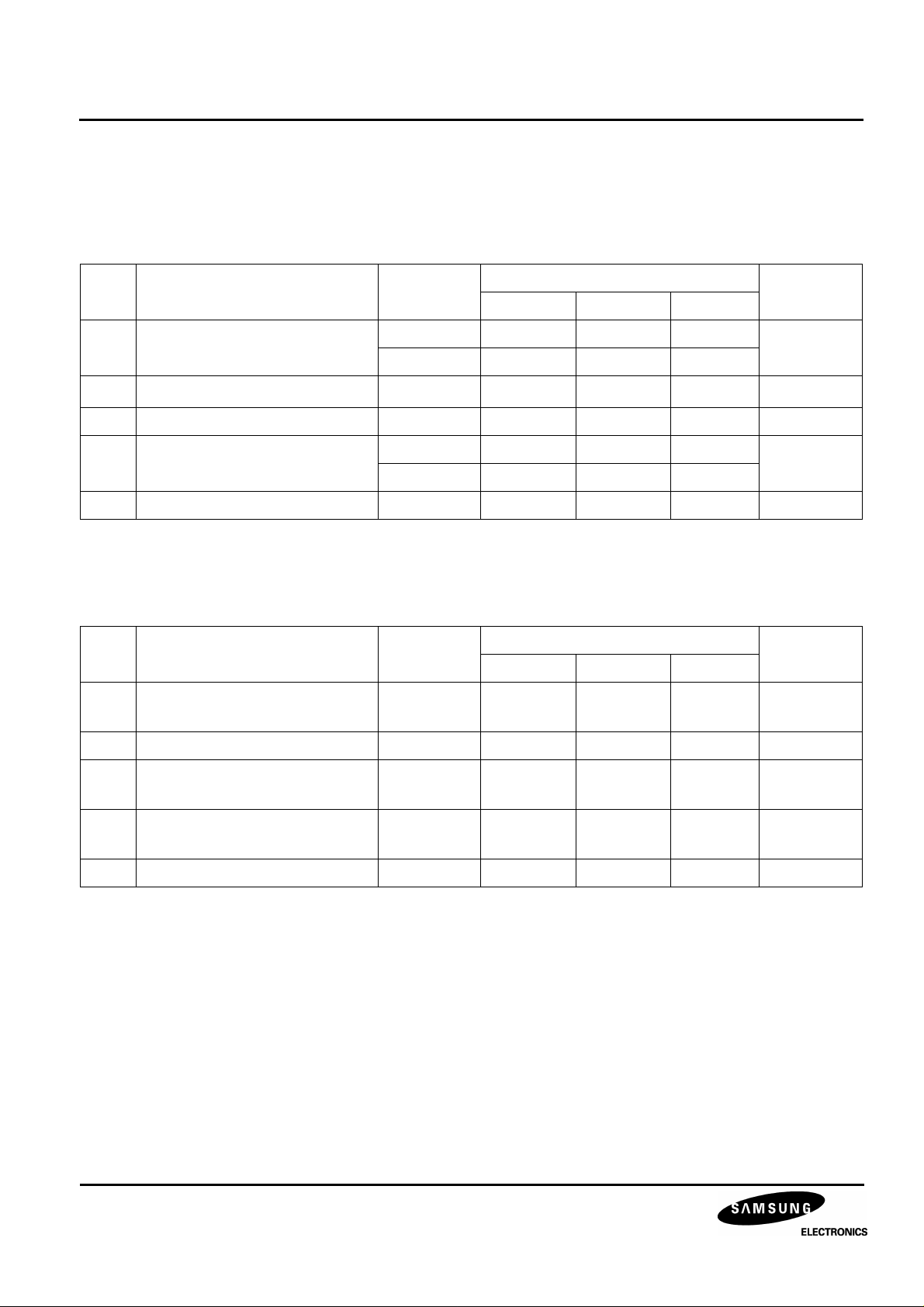

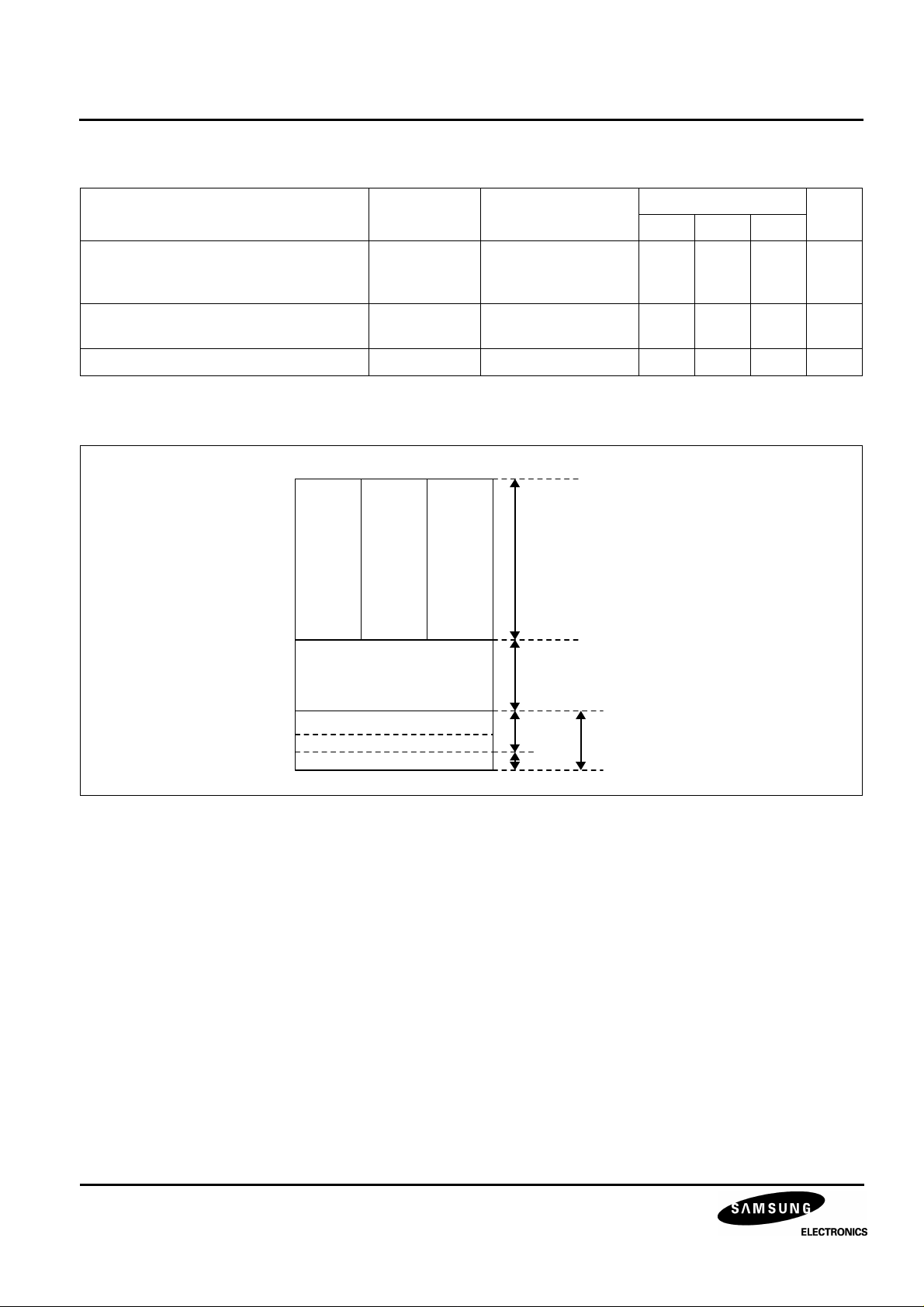

Clamp cap voltage (POR) Vcap 6.0 7.0 8.0 V

Total external cut-off current range

Red

cut-off

Creen

cut-off

Blue

cut-off

600uA

Unit

Cut-Off Brightness

Cut-Off Offset

Switch

CS2

CS1

200uA

100uA

50uA

150uA

10

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

AC ELECTRICAL CHARACTERISTICS

(Tamb = 25 °C, VCC = 12V, VDD = V

470Ω, Vin = 0.7Vpp manually adjust video output pins 18, 21 and 24 to 4V DC for the AC test

otherwise stated

(see 12)

)

= 5V, ABL input voltage = 5V, HFLB input signal = S3, load resistors =

DDA

(see 11)

unless

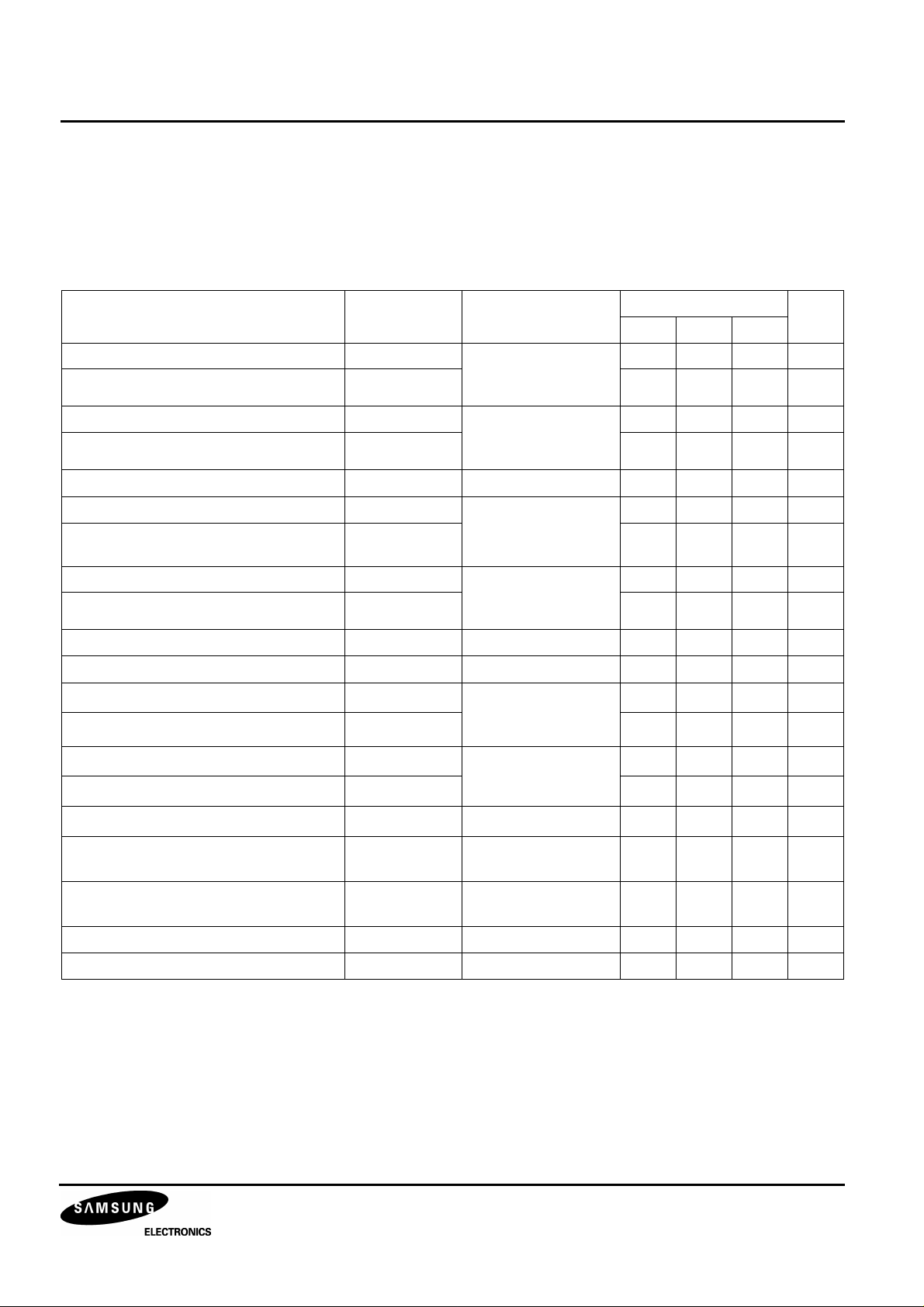

Table 6. AC Electrical Characteristics

Parameter Symbol Conditions

Min Typ Max

Contrast max. output voltage Vcff 03, 05, 06, 07 = FFH

Contrast max. output channel difference ∆ Vcff ∆ 10 - - %

04, 08 ~ 0C = 80H

RGB input = S1

Contrast center output voltage Vc80 03, 04, 08 ~ 0C = 80H

Contrast center output channel difference ∆ Vc80 ∆ 10 - - %

05, 06, 07 = FFH

RGB input = S1

Contrast max. - Center attenuation C C = 20log (Vc80/Vcff) -8 -6 -4 dB

Sub contrast center output voltage Vd80 03 = FFH

Sub contrast center output channel

difference

∆ Vd80 ∆ 10 - - %

04 ~ 0C = 80H

RGB input = S1

Sub contrast min. output voltage Vd00 03 = FFH, 05 ~ 07: 00H

Sub contrast min. output channel difference ∆ Vd00 ∆ 10 - - %

04, 08 ~ 0C = 80H

RGB input = S1

Sub contrast max. - min. attenuation D D = 20log (Vd00/Vcff) -14 -12 -10 dB

ABL control range ABL

R/G/B video rising time

R/G/B video falling time

(see 7)

(see 7)

R/G/B blank output rising time

R/G/B blank output falling time

R/G/B video band width

(see 7, 8)

(see 7)

(see 7)

tr (video) 03, 05 ~ 07: FFH

tf (video) - 2.2 2.8 ns

tr (blank) POR

tf (blank) - 8.0 15.0 ns

f (-3dB)

Video AMP 50MHz cross talk CT_50M

(see7, 9)

(see 15)

04, 08 ~ 0C: 80H

RGB input = S2

HFLB: S4

(see 16)

(see 17)

-12 -10 -8 dB

150 - - MHz

Value

5.0 5.7 6.4 Vpp

2.5 2.85 3.2 Vpp

2.3 2.6 2.9 Vpp

1.3 1.6 1.9 Vpp

- 2.2 2.8 ns

- 6.0 12.0 ns

- -25 -20 dB

Unit

Video AMP 130MHz cross talk CT_130M

(see7, 9)

Absolute gain match Avmatch

Gain change between amplifier Avtrack

(see 6)

(see 7)

(see 18)

- -15 -10 dB

-1 - 1 dB

-1 - 1 dB

11

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

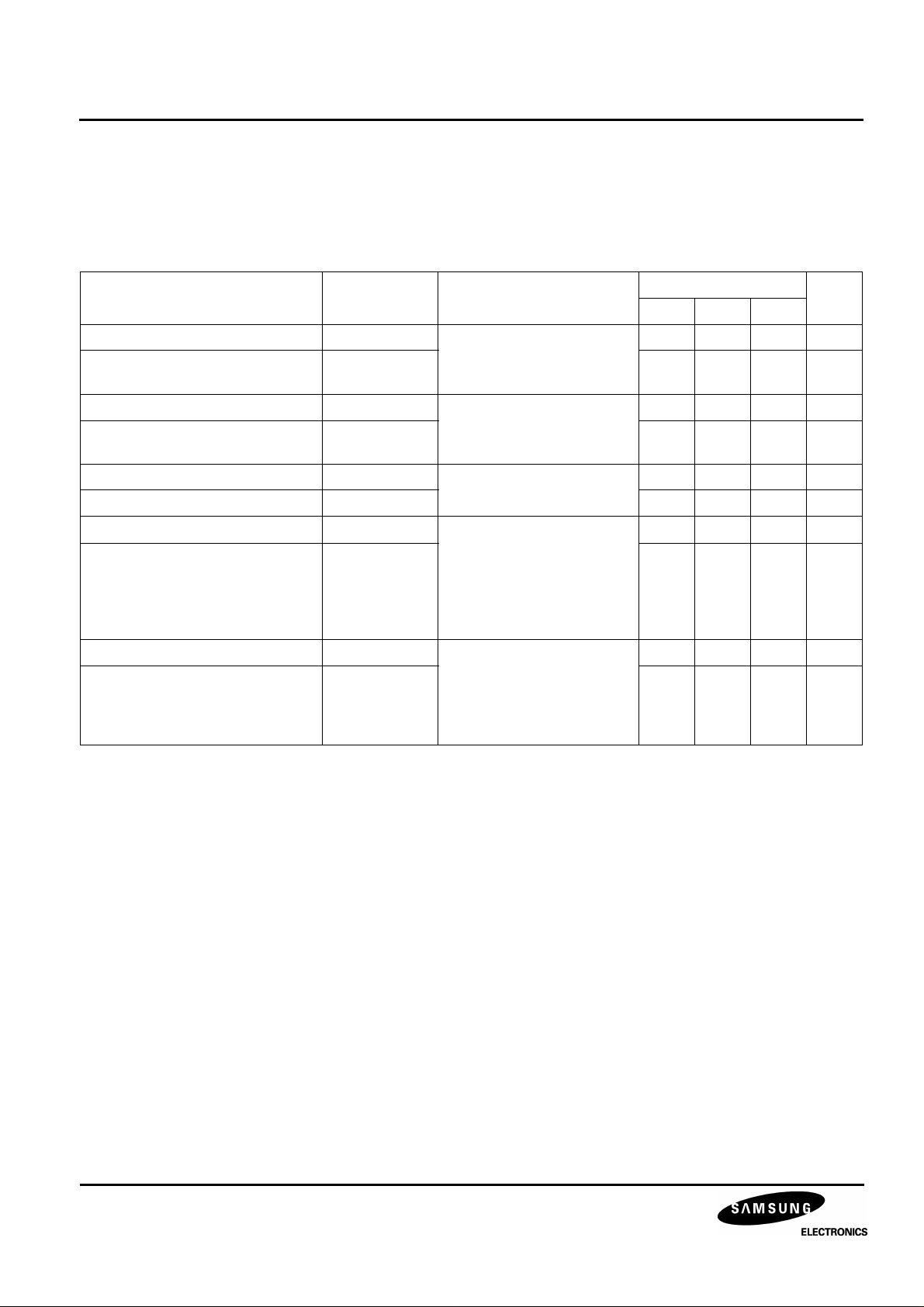

OSD ELECTRICAL CHARCTERISTICS

(Tamb = 25 °C, VCC = 12V, VDD = V

= 5V, HFLB input voltage = S3, load rosistors = 470Ω, V-AMP test

DDA

registor’s FBLK, OSD input conditions unless otherwise stated)

Table 7. OSD Electrical Chaacteristics

Parameter Symbol Conditions

OSD contrast max. output voltage Vocff 08 = FFH

OSD contrast max. output channel

difference

OSD contrast center output voltage Voc80 08 = 80H

OSD contrast center output channel

difference

R/G/B OSD rising time tr (OSD) 08: FFH - 4.0 5.0 ns

R/G/B OSD falling time tf (OSD) - 4.0 5.0 ns

HT video level HTvideo ABL = 6V

HT video output channel difference ∆ HTvideo ∆ 15 - - %

HT OSD level HTosd ABL = 6V

HT OSD output channel difference ∆ HTosd ∆ 15 - - %

∆ Vocff ∆ 10 - - %

∆ Voc80 ∆ 10 - - %

OSD RGB output conditions

OSD RGB output conditions

RGB input = S1

03, 05 ~ 08: FFH

0D: 01H

OSD black conditions input

HTvideo = 20log(V

05 ~ 08: FFH

0D: 0FH

OSD white condition input

HTosd = 20log (V

htvideo/Vcff

htosd/Vocff

Min Typ Max

-6.0 -4.5 -3.0 dB

)

-7.0 -5.5 -4.0 dB

)

Value

5.4 6.4 7.4 Vpp

2.7 3.2 3.7 Vpp

Unit

12

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

OPERATION TIMINGS

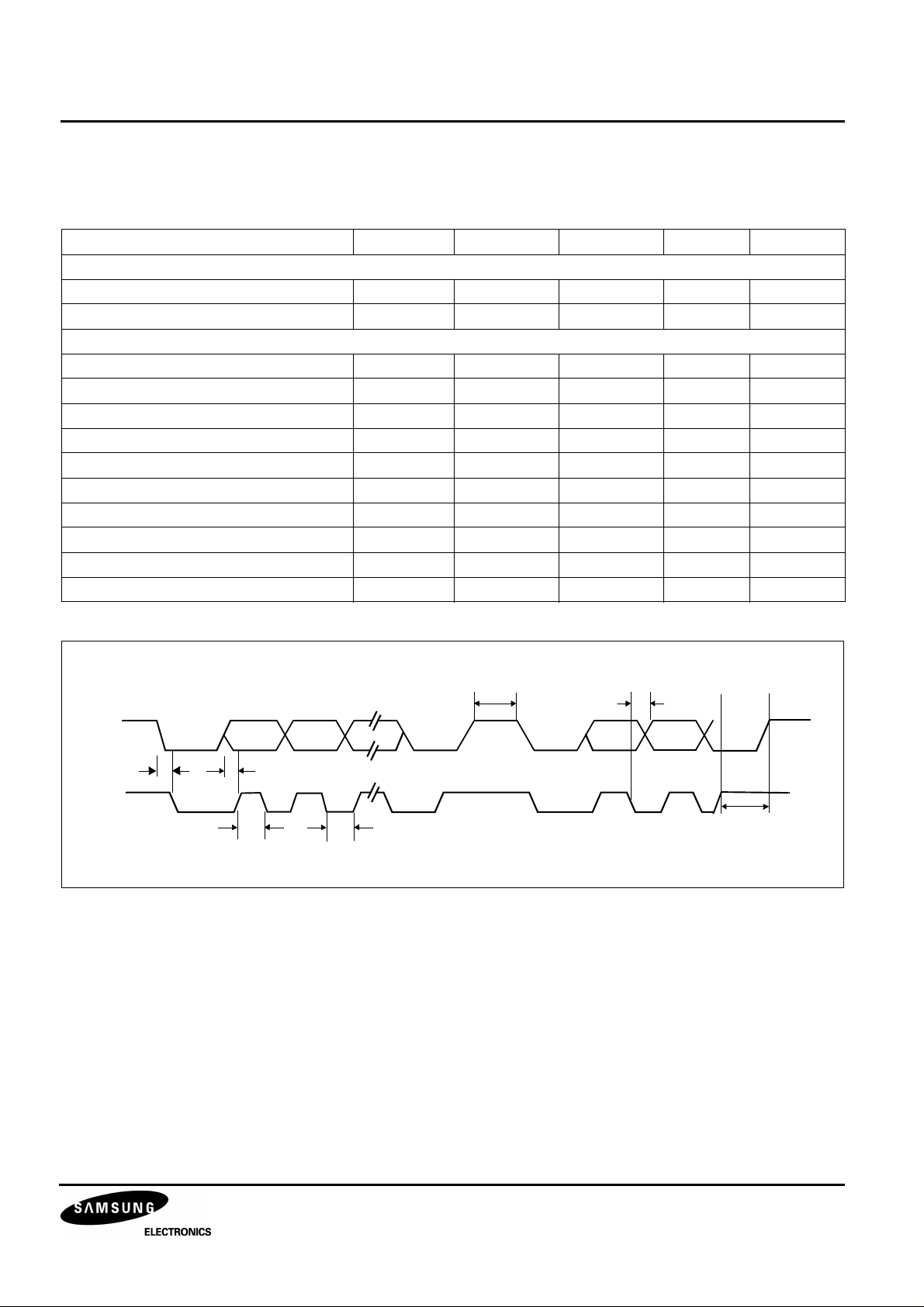

Table 8. Operation Timings

Parameter Symbol Min Typ Max Unit

Input Signal HFLB, VFLB

Horizontal flyback signal frequency f

Vertical flyback signal frequency f

I2C Interface SDA, SCL (Refer to Figure 3)

SCL clock frequency f

Hold time for start condition t

Set up time for stop condition t

Low duration of clock t

High duration of clock t

Hold time for data t

Set up time for data t

Time between 2 access t

Fall time of SDA t

Rise time of both SCL and SDA t

HFLB

VFLB

SCL

hs

sus

low

high

hd

sud

ss

fSDA

rSDA

- - 120 kHz

- - 200 Hz

- - 300 kHz

500 - - ns

500 - - ns

400 - - ns

400 - - ns

0 - - ns

500 - - ns

500 - - ns

- - 20 ns

- - - ns

SDA

SCL

ths

tsud

thigh

tss

tlow

Figure 3. I2C Bus Timing Diagram

thd

tsus

13

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

OSD PART ELECTRICAL CHARACTERISTICS

OSD PART DC ELECTRICAL CHARACTERISTICS

(Ta = 25 °C, V

= VDD = 5V)

DDA

Table 9. OSD Part DC Electrical Characteristics

Parameter Symbol Min Typ Max Unit

Supply voltage V

Supply current

(no load on any output)

Input voltage V

Output voltage

(lout = ±1mA)

Input leakage current I

VCO input voltage V

I

DD

V

V

V

VCO

DD

IH

IL

OH

OL

IL

4.75 5.00 5.25 V

- - 25 mA

0.8V

DD

- - V

- - VSS + 0.4 V

0.8V

DD

- - V

- - VSS + 0.4 V

-10 - 10 µA

2.5 V

14

Preliminary

VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS KB2514

NOTES:

1. Absolute maximum rating indicates the limit beyond which damage to the device may occur.

2. Operating ratings indicate conditions for which the device is functional but do not guarantee specific performance limits.

For guaranteed specifications and test conditions, see the electrical characteristics. The guaranteed specifications apply

only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under

the listed test conditions.

3. VCC supply pins 11, 13, and 22 must be externally wired together to prevent internal damage during VCC power on/off

cycles.

4. The supply current specified is the quiescent current for VCC1/VCC2 and VCC3 with RL = ∞, The supply current

for VCC2 (pin 22) also depends on the output load.

5. Output voltage is dependent on load resistor. Test circuit uses RL = 470Ω

6. Measure gain difference between any two amplifiers Vin = 700mVpp.

7. When measuring video amplifier bandwidth or pulse rise and fall times, a double sided full ground plane printed circuit

board without socket is recommended. Video amplifier 50MHz cross talk test also requires this printed circuit board. The

reason for a double sided full ground plane PCB is that large measurement variations occur in single sided PCBs.

8. Adjust input frequency from 10MHz (AV max reference level) to the -3dB frequency (f -3dB).

9. Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation.

Terminate the undriven amplifier inputs to simulate generator loading. Repeat test at fin = 50MHz for cross talk 50MHz.

10. A minimum pulse width of 200 ns is guaranteed for a horizontal line of 15kHz. This limit is guaranteed by design. if a lower

line rate is used a longer clamp pulse may be required.

11. During the AC test the 4V DC level is the center voltage of the AC output signal. For example. If the output is 4Vpp the

signal will swing between 2V DC and 6V DC.

12. These parameters are not tested on each product which is controlled by an internal qualification procedure.

13. The conditions block’s 03, 04, 05... etc. signify sub address’ 0F03, 0F04, 0F05... etc.

14. Sub address 0F03, 0F05 ~ 0F07: FFH

0F04, 0F08 ~ 0F0C: 80H

RGB input = S1,

When the ABL input voltage is 0V, the R/G/B’s output voltage is VR/VG/VB and uses the formula ABLR = 20log (VR/V

15. OSD TST mode = High, CLP operation off,

RGB input = S5 (frequency sweep),

RGB input clamp cap = 2.1V DC,

RGB clamp cap (pin 23/20/17) = Vcap voltage (7.0V),

S5’s frequency 1MHz → 130MHz sweep, -3dB point = 20log (V

130MHz/V1MHz

)

03, 05 ~ 07: FFH

04, 08 ~ 0C: 80H

0F: 80H

16. OSD TST mode = High, CLP operation off,

RGB input clamp cap = 2.1V DC,

RGB clamp cap (pin 23/20/17) = Vcap voltage (7.0V),

03, 05 ~ 07: FFH

04, 08 ~ 0C: 80H

0F: 80H

R input = S5 (50MHz)

CT_50M = 20log (V

outG/VoutR

) or 20log (V

outB/VoutR

)

17. OSD TST mode = High, CLP operation off,

RGB input clamp cap = 2.1V DC,

RGB clamp cap (pin 23/20/17) = Vcap voltage (7.0V),

03, 05 ~ 07: FFH

04, 08 ~ 0C: 80H

0F: 80H

R input = S5 (130MHz)

CT_150M = 20log (V

outG/VoutR

) or 20log (V

outB/VoutR

)

cffR

)

15

Preliminary

KB2514 VIDEO AMP MERGED OSD PROCESSOR FOR MONITORS

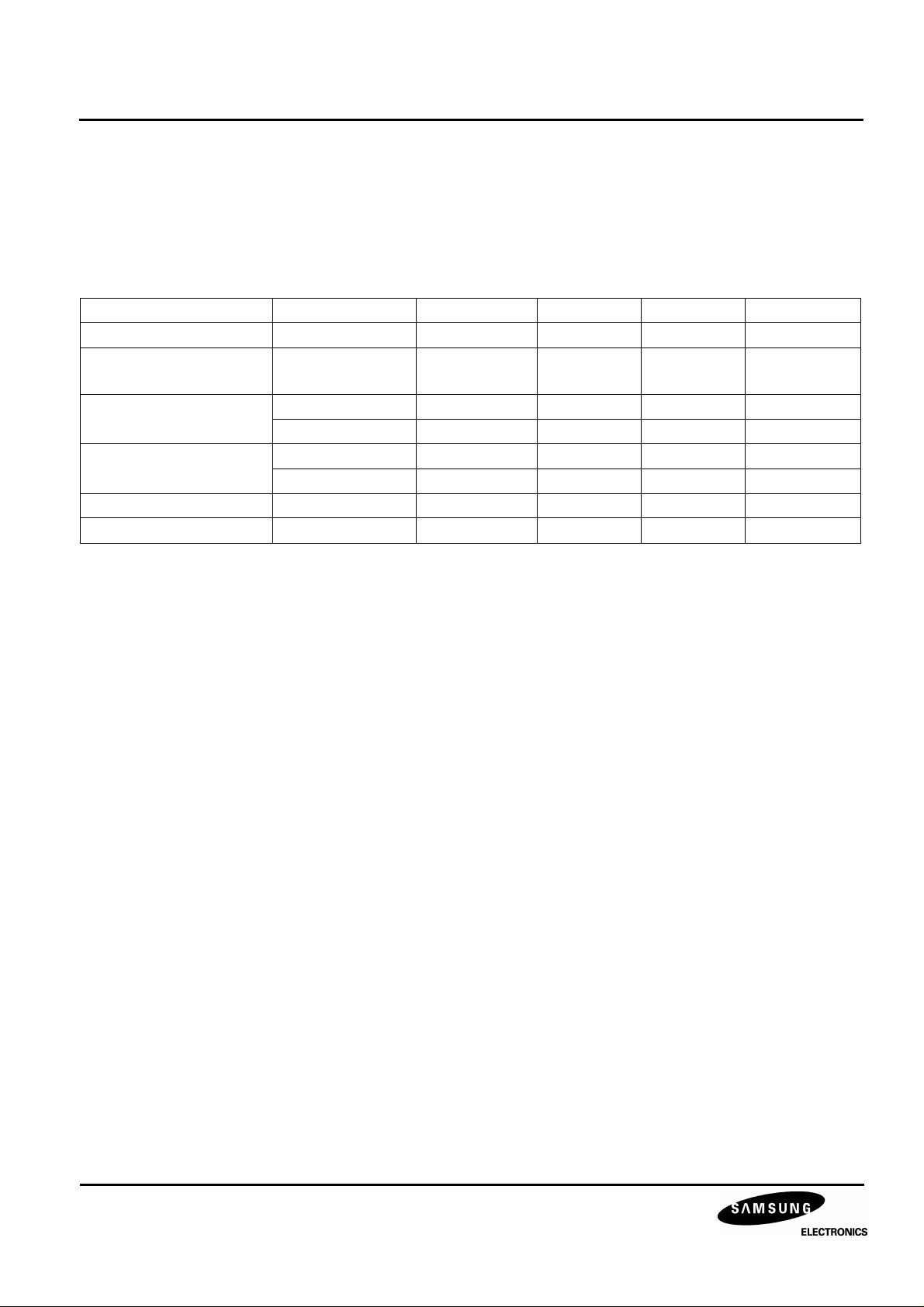

TEST SIGNAL FORMAT

Table 10. Test Signal Format

Signal

Name

S1 Video gain measurement

[V]

S2 Video Tr/Tf measurement

[V]

S3 HFLB (posi & nega.) input

[V]

Video

4uS

f = 200kHz

Input Signal Formal Signal Description

Video = 1MHz/0.7Vpp

Sync = 50kHz

Sync

[t]

f = 200kHz

V = 0.7Vpp

Duty = 50%

Duty = 50%

t = 2uS

0.7

Vpp

[t]

f = 50kHz

t = 2uS

V = 0V/5V

f = 50kHz

S4 OSD level measurement

[V]

[V]

f = 200kHz

S5 Crosstalk test

[V]

Duty = 50%

[t]

5V

0V

[t]

Vi

[t]

Blank Tr/Tf measurement

f = 50kHz

V = 0V/5V

Bandwidth measurement

1MHz/10MHz/50MHz/

Vref

130MHz

Vref = input clamp voltage

Vi = 0.7Vpp

• S1, S2 signal’s low level must be synchronized with the S3 signal’s sync. term.

• The input signal level uses the IC pin as reference.

16

Loading...

Loading...