Samsung KB2512 Datasheet

JUN. 2000

Ver 0.3

DATA SHEET

KB2512

Preliminary

KB2512 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

DEFLECTION PROCESSOR

32-SDIP-400

The KB2512 is a monolithic integrated circuit assembled in 32 pins

shrunk dual in line plastic package. This IC controls all the functions

related to the horizontal and vertical deflection in multi modes or multifrequency computer display monitors.

The internal sync processor, combined with the very powerful geometry

correction block make the KB2512 suitable for very high performance

monitors with very few external components. The horizontal jitter level is

very low. It is particularly well suited for high-end 17” and 19” monitors.

FUNCTIONS

ORDERING INFORMATION

• Deflection processor

• I2C bus control

• B+ regulator

• Vertical parabola generator

• Vertical dynamic focus

FEATURES

Device Package Operating Temperature

KB2512 32-SDIP-400 0 °C ~ 70 °C

• Horizontal dynamic phase (side pin balance &

parallelogram)

• Vertical dynamic focus (Vertical focus amplitude)

(HORIZONTAL)

• Self-adaptive

• Dual PLL concept

• 150kHz maximum frequency

• X-RAY protection input

• I2C controls: Horizontal duty-cycle, H-position, free

running frequency, frequency generator for burn-in

mode.

(VERTICAL)

• Vertical ramp generator

• 50 to 185Hz AGC loop

• Geometry tracking with V-POS & V-AMP

• I2C Controls: V-AMP, V-POS, S-CORR, C-CORR

• DC breathing compensation

(I2C GEOMETRY CORRECTIONS)

• Vertical parabola generator

(pincushion-E/W, keystone, corner)

(GENERAL)

• Sync processor

• 12V supply voltage

• Hor. & Vert. lock/unlock outputs

• Read/Write I2C interface

• Horizontal and vertical moire

• B+ Regulator

- Internal PWM generator for B+ current mode

step-up converter.

- I2C adjustable B+ reference voltage

- Output pulses synchronized on horizontal

frequency

- Internal maximum current limitation.

- Soft start

• Compared with the KB2511B, KB2512 HAS:

- Corner correction

- Horizontal moire

- B+ soft start

- Increased max. Vertical frequency

- No horizontal focus

- No step down option for DC/DC converter.

1

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS KB2512

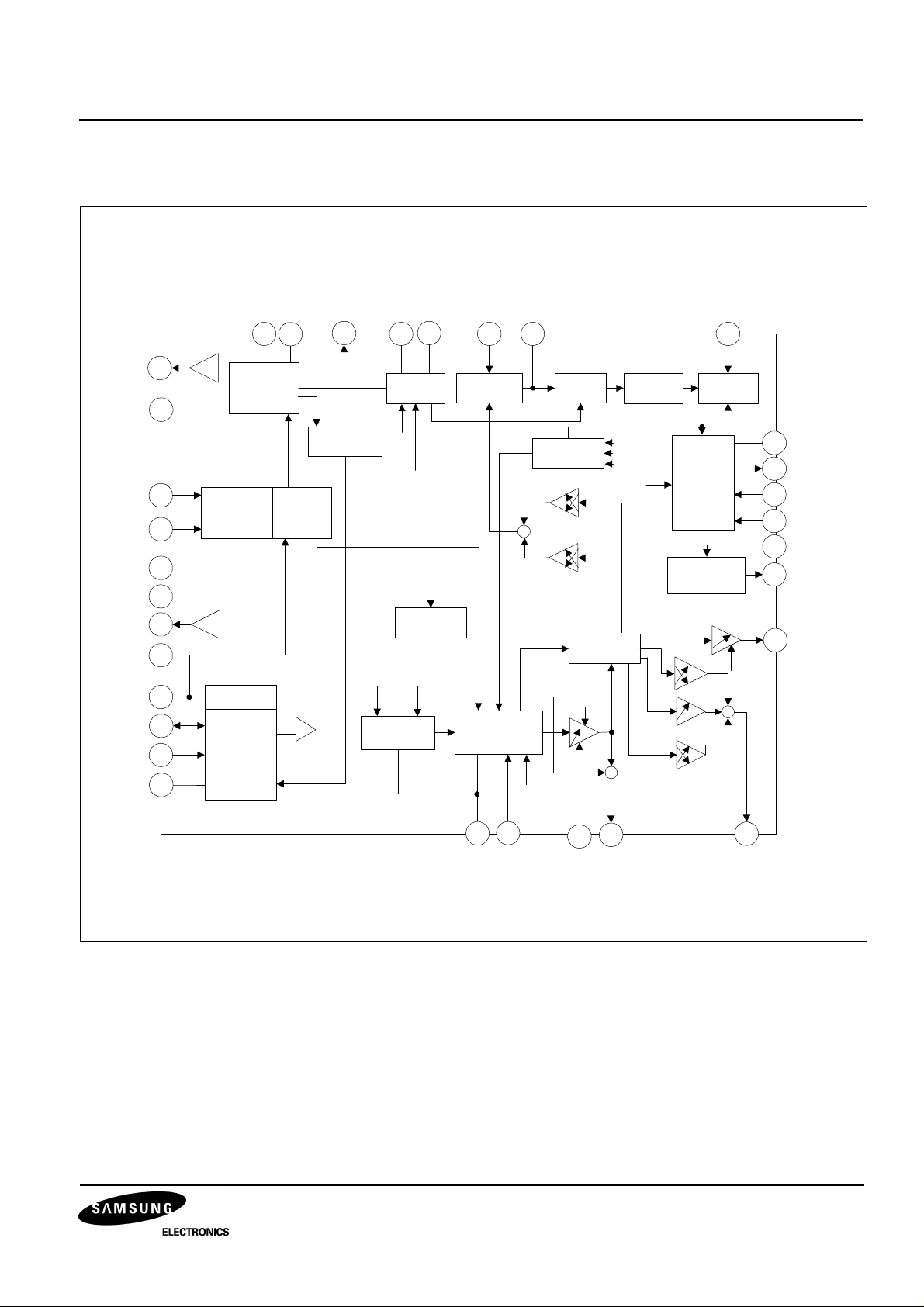

BLOCK DIAGRAM

HREF

HGND

H/HVIN

VSYNCIN

VCC

XRAY

VREF

VGND

SDA

SCL

GND

PLL1F

H POSITION

7

8

13

V

R

PHASE/

EF

FREQUENCY

COMPARATOR

11

1

2

29

25

21

19

5V

32

31

30

27

H-PHASE(7 bits)

SYNC INPUT

SELECT

(1bit)

V

R

EF

RESET

GENERATOR

2

I C INTERFACE

SYNC

PROCESSOR

HLOCKOUT

3

LOCK/UNLOCK

IDENTIFICATION

R0

C0

5

6 12 4

VCO

Forced

Freq.

2 bits

Free running

5 bits

VSYNC

MOIRE

CANCEL

5 BITS+ON/OFF

6 bits 8 bits

S AND C

CORRECTION

HFLY

PHASE

COMPARATOR

VERTICAL

OSCILLATOR

RAMP GENERATOR

+

VPOS

7bits

PLL2C

PHASE

SHIFTER

SAFETY

PROCESSOR

2

X

Spin Bal

6 bits

2

X

Key Bal

6 bits

VAMP

7 bits

B+ ADJUST

GEOMETRY

TRACKING

+

5V

Vcc

XRAY

7 bits

H-DUTY

(5 bits)

CONTROLLER

HSYNC

Moire Cancel

5 bits + on/off

Corner

7 bits

B+

Horizontal

4

X

EW

7 bits

2

X

keyst

6 bits

X

HOUT

26

HOUT

BUFFER

+

AMPVDF

6 bits

14

COMP

B+ OUT

28

REGIN

15

16

ISENSE

17

BGND

9

HMOIRE

10

FOCUS

22 20

VCAP

VACCAP

18

BREATH

23

VOUT

24

EWOUT

2

KB2512 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

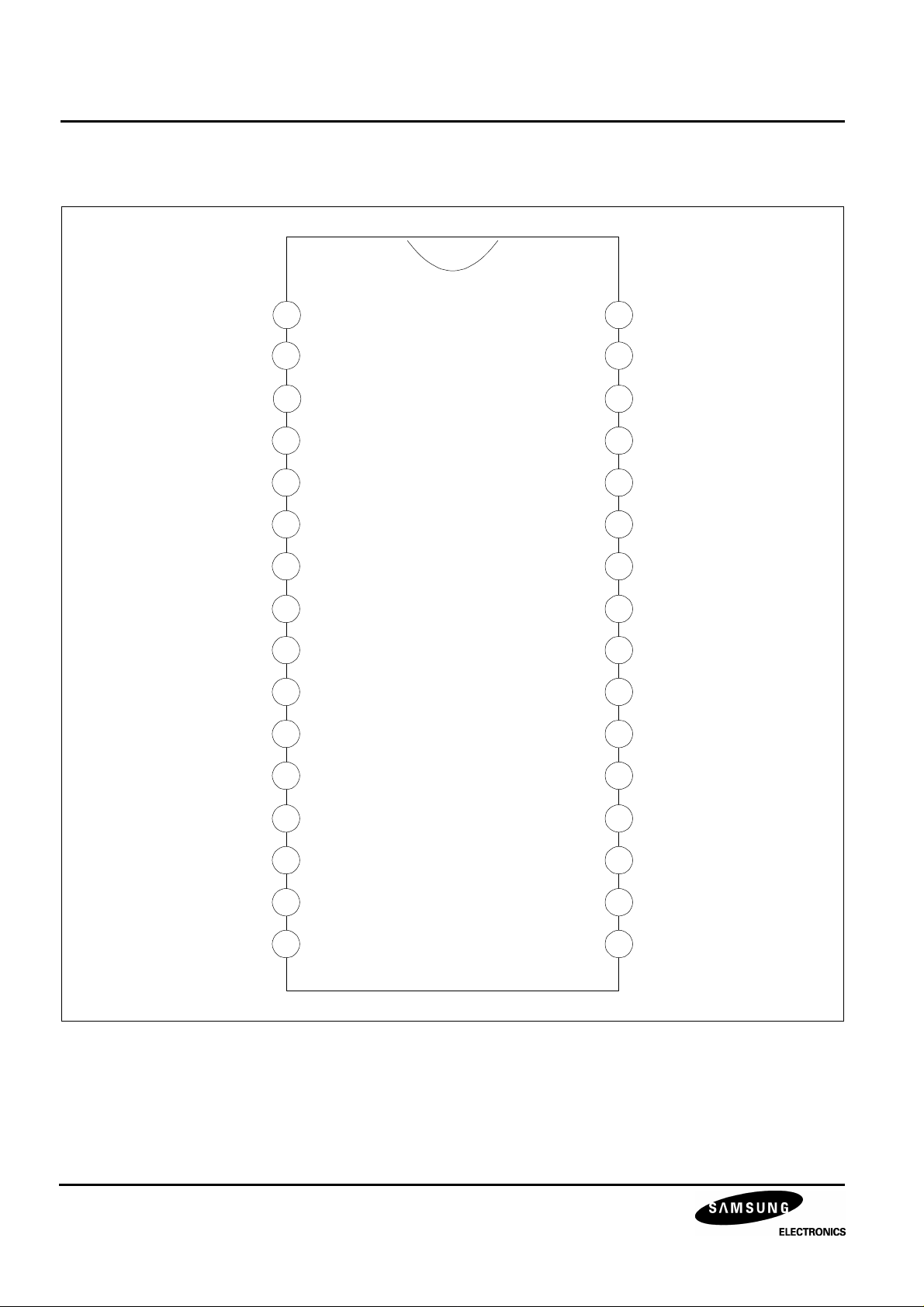

PIN CONFIGURATIONS

1

2

3

4

5

6

7

8

9

10

11

H/HVIN

VSYNCIN

HLOCKOUT

PLL2C

C0

R0

PLL1F

HPOSITION

HMOIRE

FOCUSOUT

HGND

32

5V

31

SDA

30

SCL

29

VCC

GND

28

27

26

25

24

23

22

BOUT

HOUT

XRAY

EWOUT

KB2512

VOUT

VCAP

12

HFLY

13

HREF

14

COMP

15

REGIN

16

ISENSE

3

VREF

VAGCCAP

VGND

BREATH

B+GND

21

20

19

18

17

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS KB2512

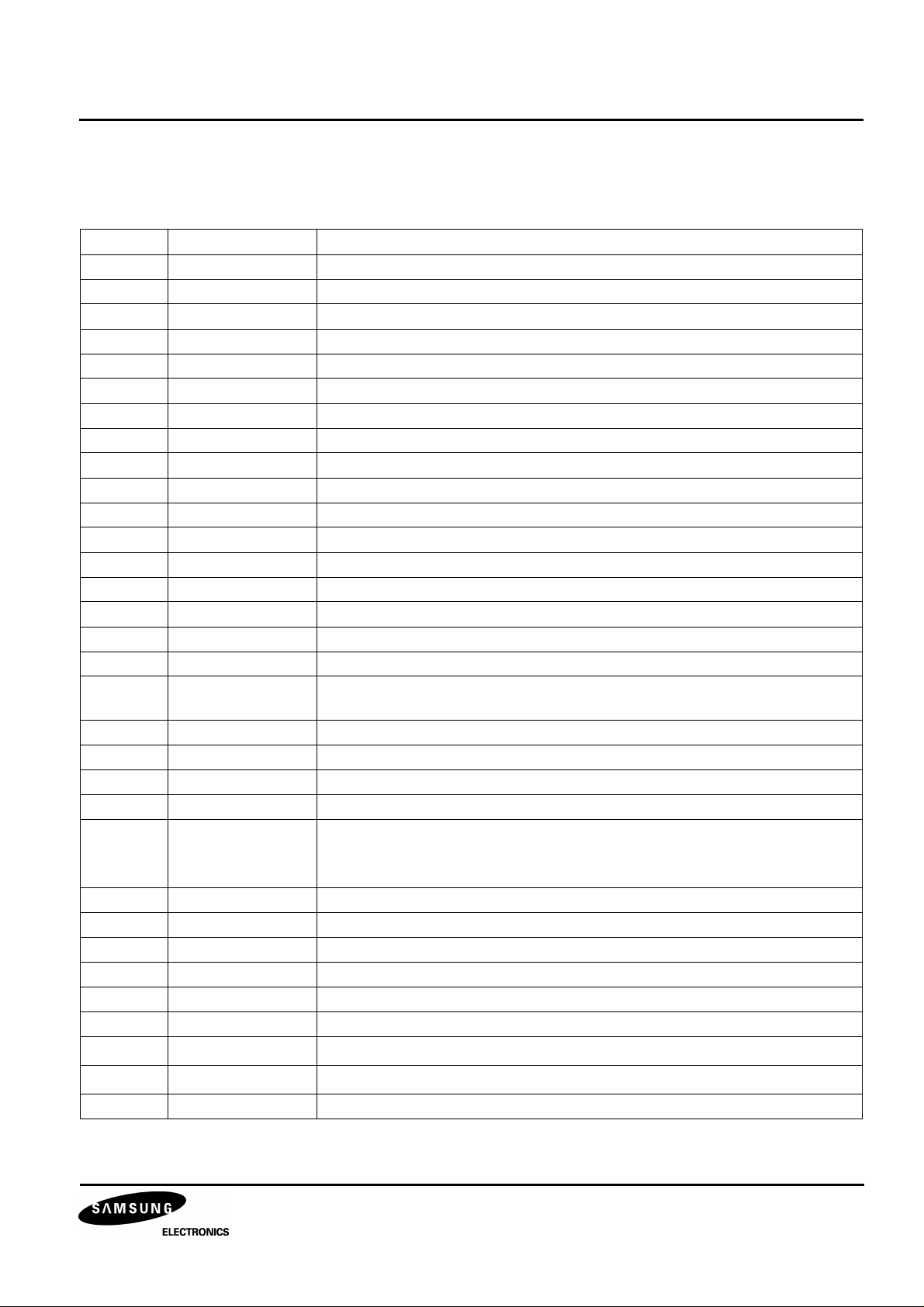

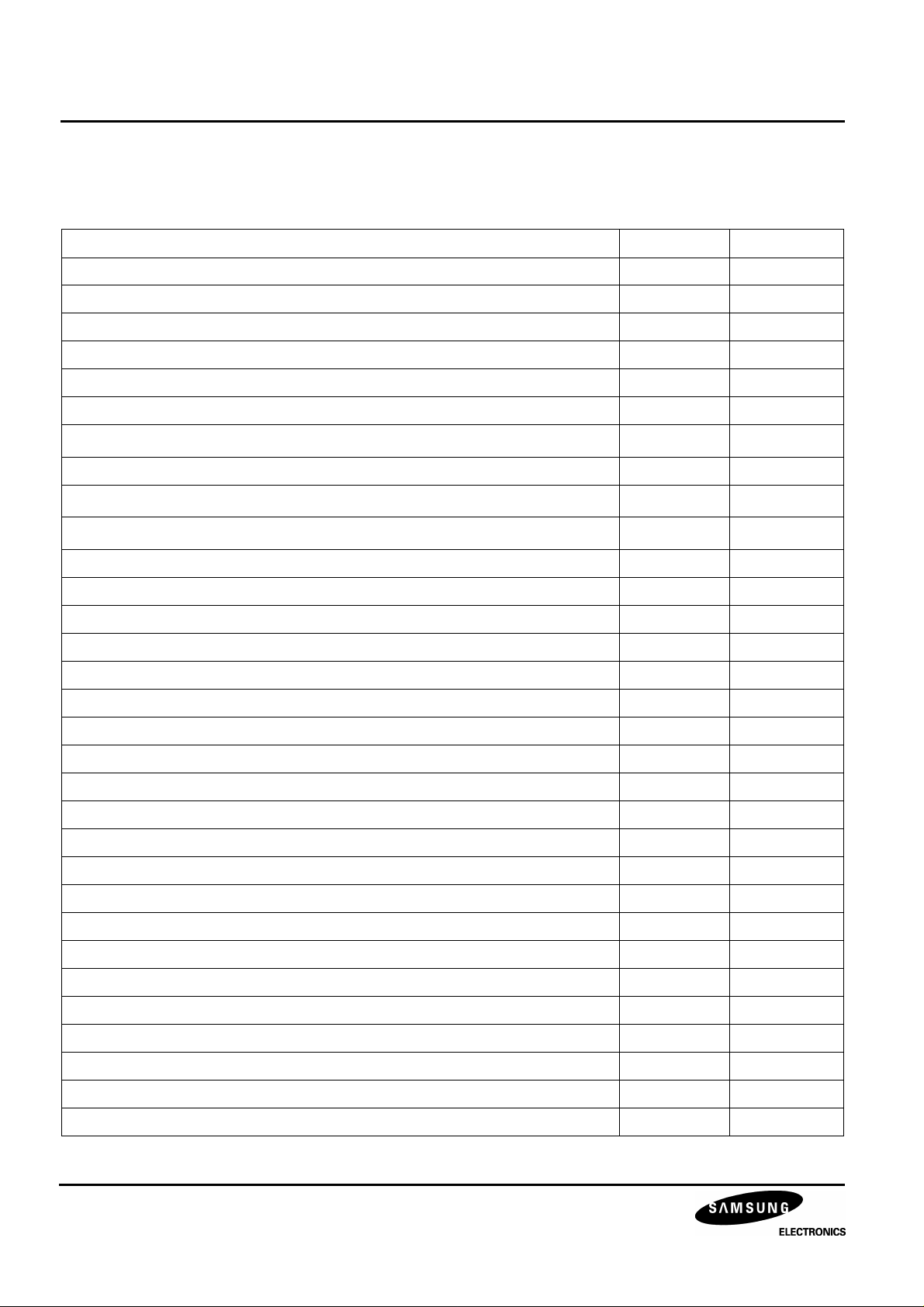

PIN DESCRIPTION

Table 1. Pin Description

No Pin Name Description

1 H/HVIN TTL compatible horizontal sync input (separate or composite)

2 VSYNCIN TTL compatible vertical sync input (for separated H&V)

3 HLOCKOUT First PLL lock/unlock output (0V unlocked - 5V locked)

4 PLL2C Second PLL loop filter

5 C0 Horizontal oscillator capacitor

6 R0 Horizontal oscillator resistor

7 PLL1F First PLL loop filter

8 HPOSITION Horizontal position filter (capacitor to be connected to HGND)

9 HMOIRE Horizontal moire output (to be connected to PLL2 C through a resistor divider)

10 FOCUSOUT Vertical dynamic focus output

11 HGND Horizontal section ground

12 HFLY Horizontal Flyback input (positive polarity)

13 HREF Horizontal section reference voltage (to be filtered)

14 COMP B+ error amplifier output for frequency compensation and gain setting

15 REGIN Regulation input of B+ control loop

16 ISENSE Sensing of external B+ switching transistor current

17 B+GND Ground (related to B+ reference adjustment)

18 BREATH DC breathing input control (compensation of vertical amplitude against EHV

variation)

19 VGND Vertical section ground

20 VAGCCAP Memory capacitor for automatic gain control loop in vertical ramp generator

21 VREF Vertical section reference voltage (to be filtered)

22 VCAP Vertical sawtooth generator capacitor

23 VOUT Vertical ramp output

(with frequency independent amplitude and S or C corrections if any).

It is mixed with vertical position voltage and vertical moire.

24 EWOUT Pincushion-East/West correction parabola output

25 XRAY X-RAY protection input (with internal latch function)

26 HOUT Horizontal drive output (internal transistor, open collector)

27 GND General ground (referenced to Vcc)

28 BOUT B+ PWM regulator output

29 Vcc Supply voltage (12V typ)

30 SCL

31 SDA

32 5V Supply voltage (5V typ)

I2C clock input

I2C data input

4

KB2512 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

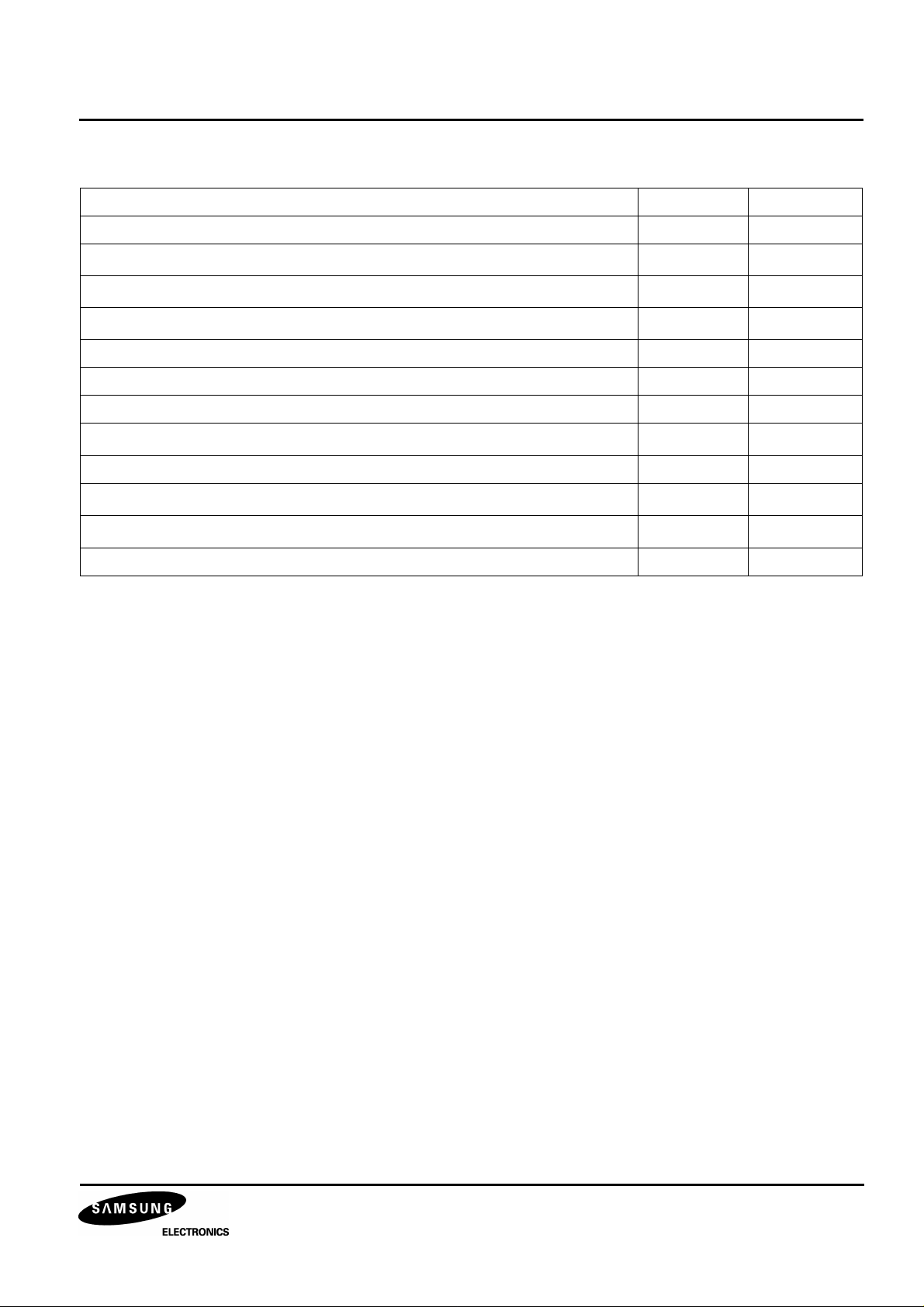

REFERENCE DATA

Table 2. Reference Data

Parameter Value Unit

Horizontal frequency 15 to 150 kHz

Autosynch frequency (for given R0 and C0) 1 to 4.5FO FH

± Horizontal sync polarity input Yes

Polarity detection (on both horizontal and vertical section) Yes

TTL composite sync Yes

Lock/unlock identification (on both horizontal 1st PLL and vertical section) Yes

I2C control for H-position

XRAY protection Yes

I2C horizontal duty cycle adjust

I2C free running frequency adjustment

Stand-by function Yes

Dual polarity H-drive outputs No

Supply voltage monitoring Yes

PLL1 inhibition possibility No

Blanking output No

Vertical frequency 35 to 200 Hz

Vertical Autosync (for 150nf on pin22 and 470nf on pin20) 50 to 185 Hz

Vertical S correction Yes

Vertical C correction Yes

Vertical amplitude adjustment Yes

DC breathing control on vertical amplitude Yes

Corner correction Yes

±10 %

30 to 60 %

0.8 to 1.3FO FH

East/West parabola output (also known as pin cushion output) Yes

East/West correction amplitude adjustment Yes

Keystone adjustment Yes

Vertical position adjustment Yes

Internal dynamic horizontal phase control Yes

Side pin balance amplitude adjustment Yes

Parallelogram adjustment Yes

Tracking of geometric corrections with vertical amplitude and position Yes

Reference voltage (both on horizontal and vertical) Yes

5

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS KB2512

Table 2. Reference Data (Continued)

Parameter Value Unit

Vertical dynamic focus Yes

I2C horizontal dynamic focus amplitude adjustment

I2C horizontal dynamic focus symmetry adjustment

I2C vertical dynamic focus amplitude adjustment

No

No

Yes

Deflection of input sync type Yes

Vertical moire output Yes

Horizontal moire output Yes

I2C controlled moire amplitude

Yes

Frequency generator for burn-in Yes

Fast I2C read/write

B+ regulation adjustable by I2C

400 kHz

Yes

B+ soft start Yes

6

KB2512 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

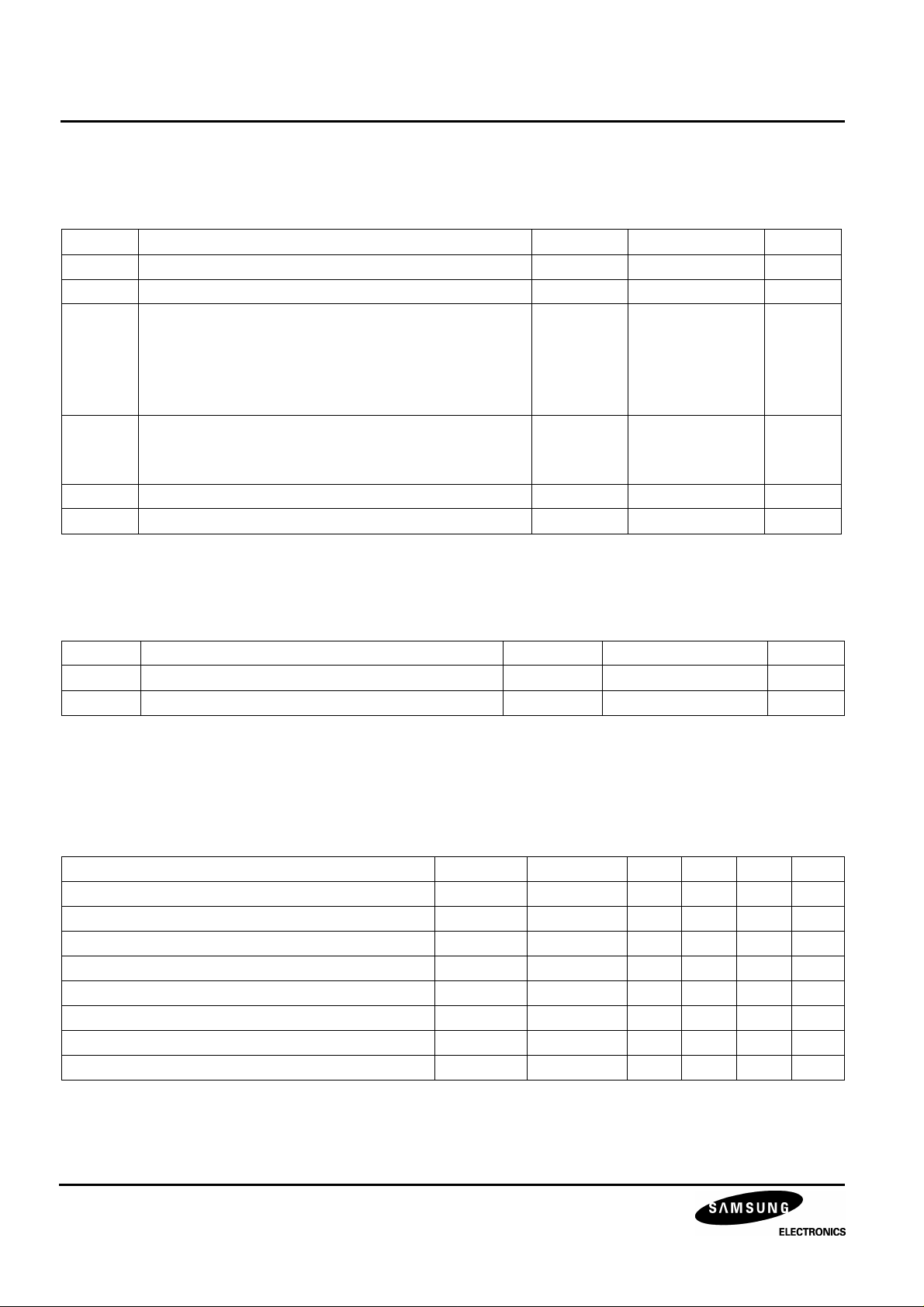

ABSOLUTE MAXIMUM RATINGS

Table 3. Absolute Maximum Ratings

No Item Symbol Value Unit

1 Supply voltage (Pin 29) V

2 Supply voltage (Pin 32) V

3 Maximum voltage on Pin 4

CC

DD

V

IN

Pin 5

Pin 6, 7, 8, 14, 15, 16, 20, 22

Pin 9, 10, 18, 23, 24, 25, 26, 28

Pin 1, 2, 3, 30, 31

4 ESD susceptibility

VESD 2

Human body model, 100pF discharge through 1.5KΩ

EIAJ norm, 200pF discharge through 0Ω

5 Storage temperature Tstg - 40, +150 °C

6 Operating temperature Topr 0, +70 °C

13.5 V

5.7 V

4.0

6.4

8.0

V

CC

V

DD

kV

300

V

V

V

V

V

V

THERMAL CHARACTERISTICS

Table 4. Thermal Characteristics

No Item Symbol Value Unit

1 Junction temperature Tj +150 °C

2 Junction-ambient thermal resistance θja 65 °C/W

SYNC PROCESSOR

OPERATING CODNITIONS(VDD = 5V, Tamb = 25 °C)

Table 5. Sync Processor Operating Conditions

Parameter Symbol Conditions Min Typ Max Unit

Horizontal sync input voltage HsVR Pin 1 0 5 V

Minimum horizontal input pulse duration MinD Pin 1 0.7 µs

Maximum horizontal input signal duty cycle Mduty Pin 1 25 %

Vertical sync input voltage VsVR Pin 2 0 5 V

Minimum vertical sync pulse width VSW Pin 2 5 µs

Maximum vertical sync input duty cycle VSmD Pin 2 15 %

Maximum vertical sync width on TTL H/V composite VextM Pin 1 750 µs

Sink and source current I

HLOCKOUT

Pin 3 250 µA

7

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS KB2512

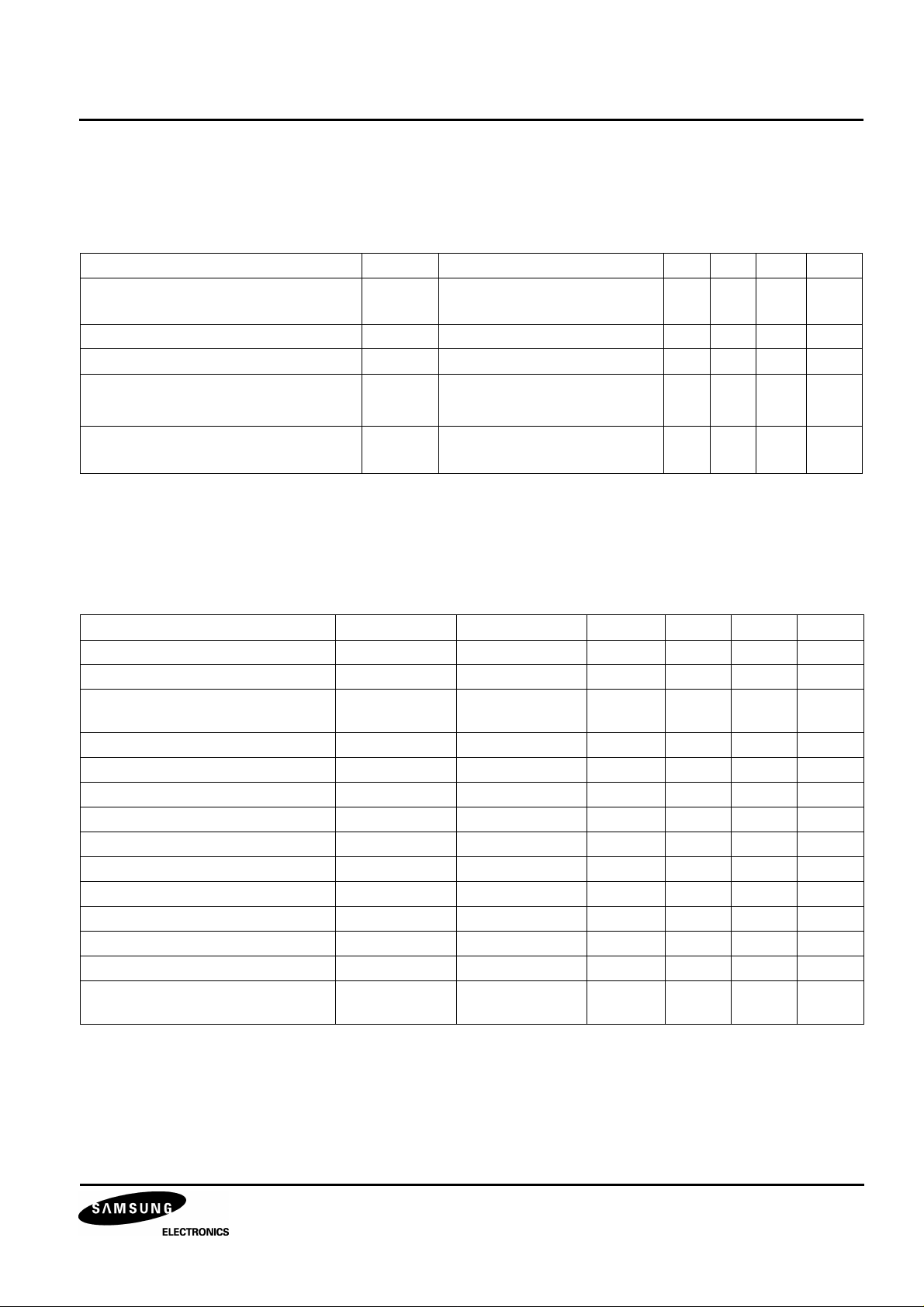

ELECTRICAL CHARACTERISTICS

(VDD = 5V, Tamb = 25 °C)

Table 6. Sync Processor Electrical Characteristics

Parameter Symbol Conditions Min Typ Max Unit

Horizontal and vertical input threshold

voltage (pin 1, 2)

Horizontal and vertical pull-up resister RIN Pins 1,2 200 KΩ

Falling and rising output CMOS buffer TfrOut Pin 3, Cout = 20pF 200 ns

Horizontal 1st PLL lock output status

(pin 3)

Extracted Vsync integration time (% of

(see 9)

TH

) on H/V composite

VINTH Low level

0.8 V

High level 2.2

VHlock Locked, I

Unlocked, I

LOCKOUT

LOCKOUT

= -250µA

= +250µA

4.4

0

5

0.5 V

VoutT C0 = 820pF 26 35 %

V

V

I2C READ/WRITE (See also I

2

C table control and I2C sub address control)

OPERATING CONDITIONS (VDD = 5V, Tamb = 25 °C)

Table 7. I2C Read/Write Operating Conditions

Parameter Symbol Condition Min Typ Max Unit

Input high level voltage VinH 3.0 - 5.0 V

Input low level voltage VinL 0 - 1.5 V

Hold time before a new

tBUF 1.3 - - µs

transmission can start

Hold time for start conditions tHDS 0.6 - - µs

Set-up time for stop conditions tSUP 0.6 - - µs

Hold time data tHDAT 0.3 - - µs

Set-up time data tSUPDAT 0.25 - - µs

Rise time of SCL tR - - 1.0 µs

Fall time of SCL tF - - 3.0 µs

Maximum clock frequency Fscl Pin 30 400 kHz

Low period of the SCL clock Tlow Pin 30 1.3 µs

High period of the SCL clock Thigh Pin 30 0.6 µs

SDA and SCL input threshold Vinth Pin 30, 31 2.2 V

Acknowledge output voltage on

VACK Pin 31 0.4 V

SDA input with 3mA

8

KB2512 DEFLECTION PROCESSOR FOR MULTISYNC MONITORS

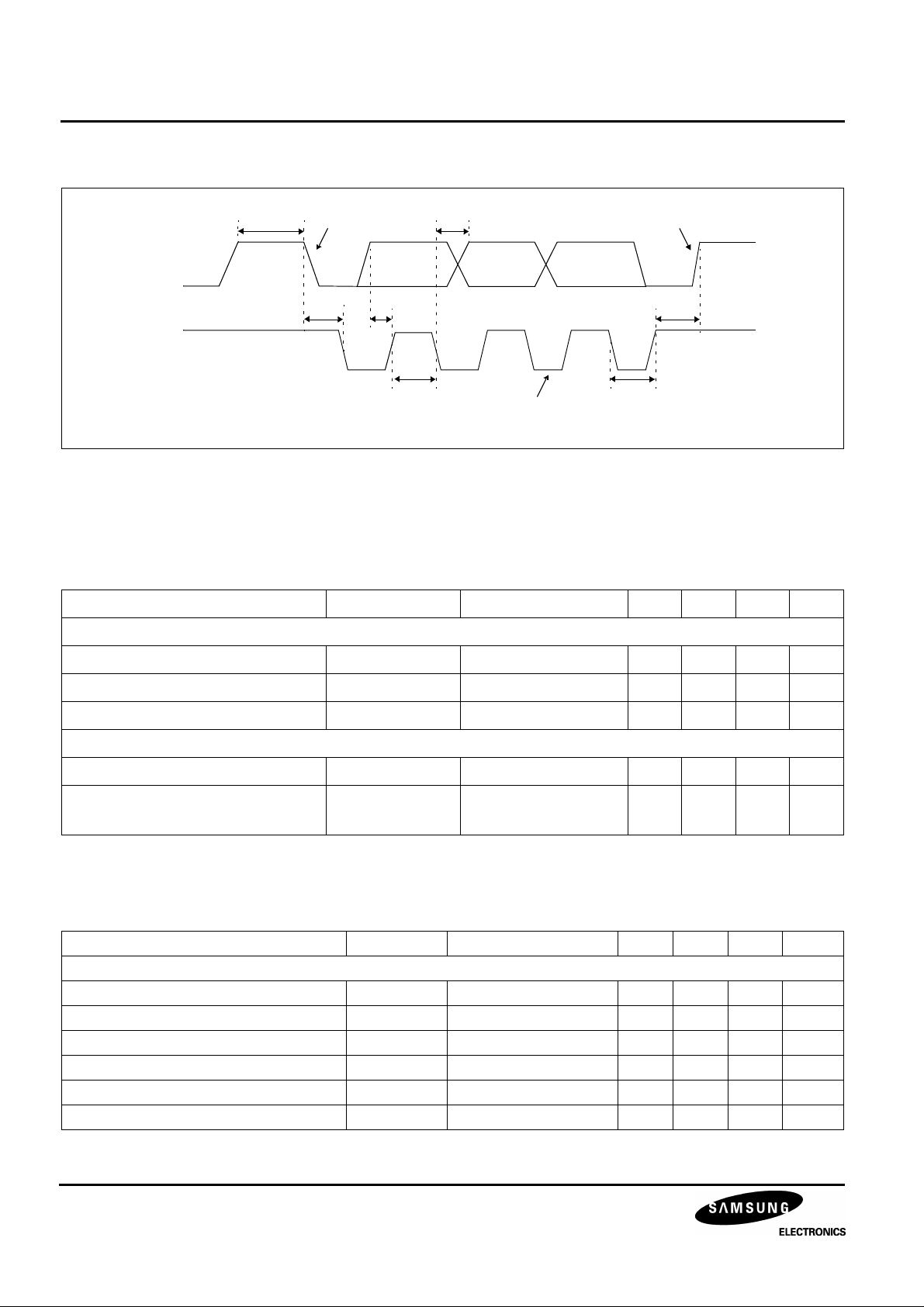

I2C Bus Timing Requirement

SDA

SCL

t

BUF

Start:Clock High

t

HDS

HORIZONTAL SECTION

OPERATING CONDITIONS

Table 8. Horizontal Section Operating Conditions

Parameter Symbol Conditions Min Typ Max Unit

VCO

Minimum oscillator resistor Ro

Minimum oscillator capacitor Co

Maximum oscillator frequency Fo

OUTPUT SECTION

t

HDAT

t

SUPDAT

(Min.)

(Min.)

(Max.)

Stop:Clock High

t

SUP

t

t

HIGH

Data Change:Clock Low

LOW

Pin 6 6 KΩ

Pin 5 390 pF

150 kHz

Maximum input peak current I12m Pin 12 5 mA

Horizontal drive output maximum

HOI Pin 26, sunk current 30 mA

current

ELECTRICAL CHARACTERISTICS (VDD = 5V, Tamb = 25 °C)

Table 9. Horizontal Section Electrical Characteristics

Parameter Symbol Conditions Min Typ Max Unit

SUPPLY AND REFERENCE VOLTAGE

Supply voltage Vcc Pin 29 10.8 12 13.2 V

Supply voltage V

Supply current I

Supply current I

Horizontal reference voltage V

Vertical reference voltage V

DD

CC

DD

REF-H

REF-V

9

Pin 32 4.5 5 5.5 V

Pin 29 50 mA

Pin 32 5 mA

Pin 13, I = -2mA 7.4 8 8.6 V

Pin 21, I = -2mA 7.4 8 8.6 V

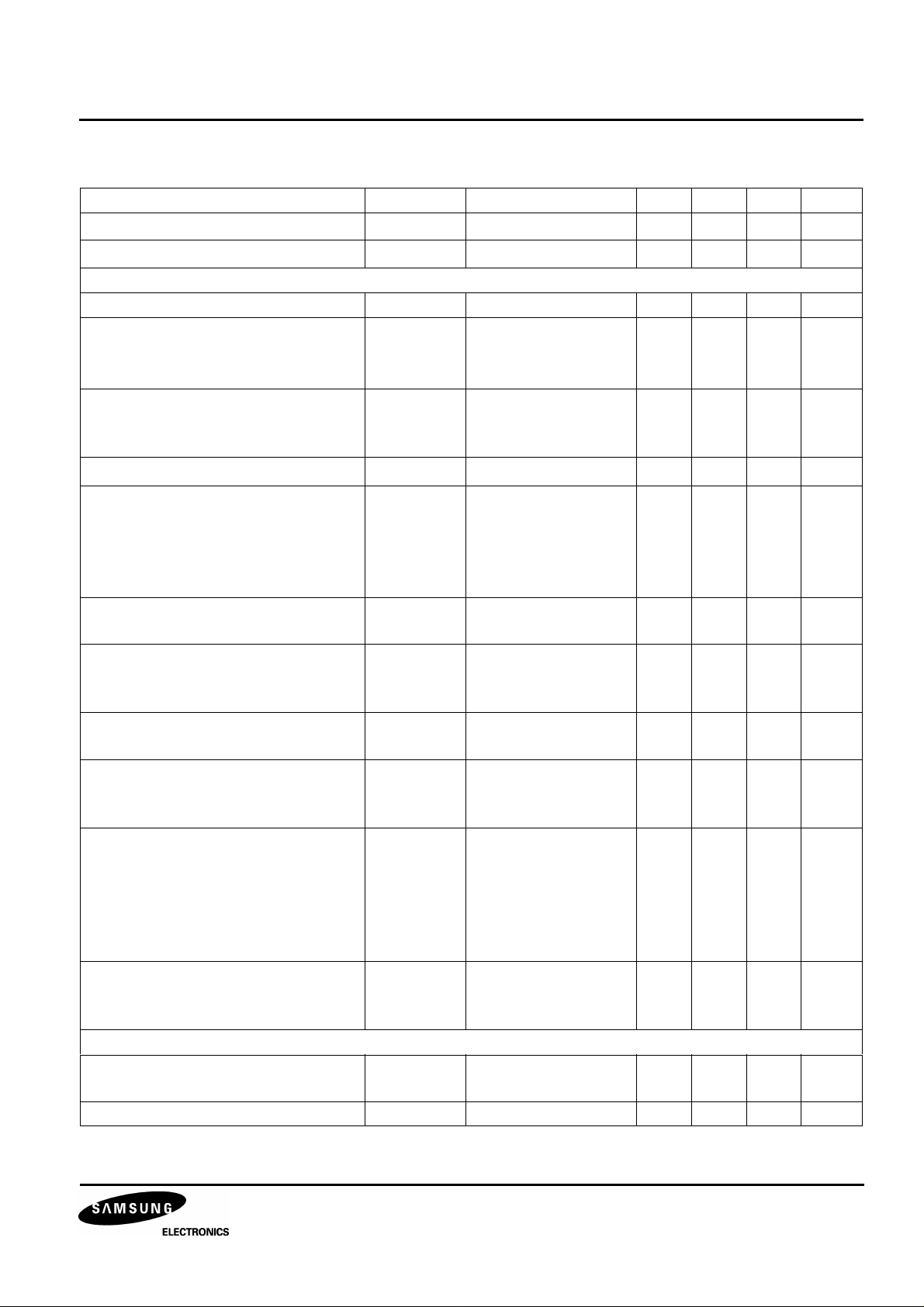

DEFLECTION PROCESSOR FOR MULTISYNC MONITORS KB2512

Table 9. Horizontal Section Electrical Characteristics (Continued)

Parameter Symbol Conditions Min Typ Max Unit

Max. sourced current on V

Max. sourced current on V

REF-H

REF-V

1st PLL SECTION

Polarity integration delay HpoIT Pin 1 0.75 ms

VCO control voltage (pin 7) V

VCO gain (pin 7) V

Horizontal phase adjustment

(see 11)

Horizontal phase setting value (Pin 8)

(see 11)

Minimum current value

Typical value

Maximum value

PLL1 filter current charge IPII1U

Free running frequency fo Ro = 6.49KΩ,

Free running frequency thermal drift (no

drift on external components)

(see 7)

Free running frequency adjustment

Minimum value

Maximum value

PLL1 capture range CR Ro = 6.49KΩ,

Safe forced frequency

SF1 Byte 11 x x x x x x

SF2 Byte 10 x x x x x x

2ND PLL SECTION HORIZONTAL OUTPUT SECTION

Flyback input threshold

voltage (pin12)

Horizontal jitter Hjit At 31.4kHz 70 ppm

I

REF-H

I

REF-V

VCO

COG

Pin 13 5 mA

Pin 21 5 mA

V

fo

fH (Max.)

Ro = 6.49KΩ,

REF-H

= 8V

1.3

6.2

V

V

17 kHz/V

Co = 820pF,

dF/dV = 1/11RoCo

Hph % of horizontal period ±10 %

Sub-address 01

Hphmin

Hphtyp

Hphmax

IPII1L

Byte x 1111111

Byte x 1000000

Byte x 0000000

PLL1 is unlocked

PLL1 is locked

Co = 820pF,

2.8

3.4

4.0

±140

±1

V

V

V

µA

mA

22.8 kHz

fo = 0.97/8RoCo

dF0/dT -150 ppm/c

Sub-address 02

fo(Min.)

fo(Max.)

Byte x x x 11111

Byte x x x 00000

0.8

1.3

Fo

Fo

Co = 820pF,

from fo + 0.5kHz to

4.5Fo (fo:22.8kHz)

fH (min.)

fH (max.)

100

23.5 kHz

kHz

SFF Sub-address 02

2F0

3F0

FBth 0.65 0.75 V

10

Loading...

Loading...