Page 1

PLASMA DISPLAY TV

Chassis : D52A

Model: HPL63H1X/XAA

PLASMA DISPLAY TV CONTENTS

Precautions

Reference Information

Specifications

Exploded View and Parts List

Alignment and Adjustments

Circuit Operation Description

Troubleshooting

Handling Description

Glossary

Schematic Diagrams

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

Page 2

ELECTRONICS

© Samsung Electronics Co., Ltd. JAN. 2003

Printed in Korea

AA82-00355A

Page 3

1. Precautions

1-1 Safety Precautions

1. Be sure that all of the built-in protective

devices are replaced. Restore any missing

protective shields.

2. When reinstalling the chassis and its

assemblies, be sure to restore all protective

devices, including: nonmetallic control knobs

and compartment covers.

3. Make sure that there are no cabinet openings

through which people—particularly

children—might insert fingers and contact

dangerous voltages. Such openings include

the spacing between fornt cabinet and back

cabinet, excessively wide cabinet

ventilation slots, and improperly fitted back

covers.

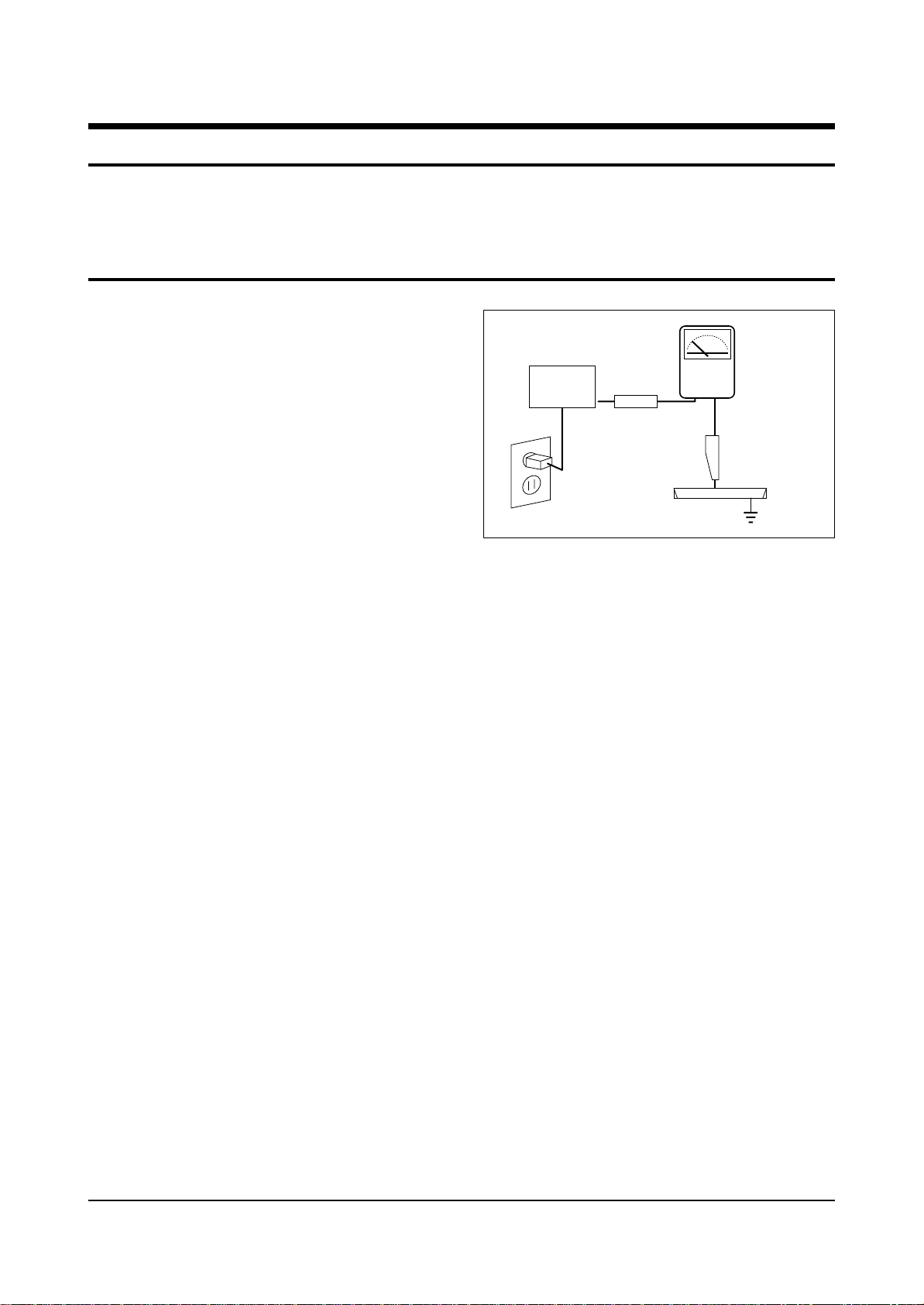

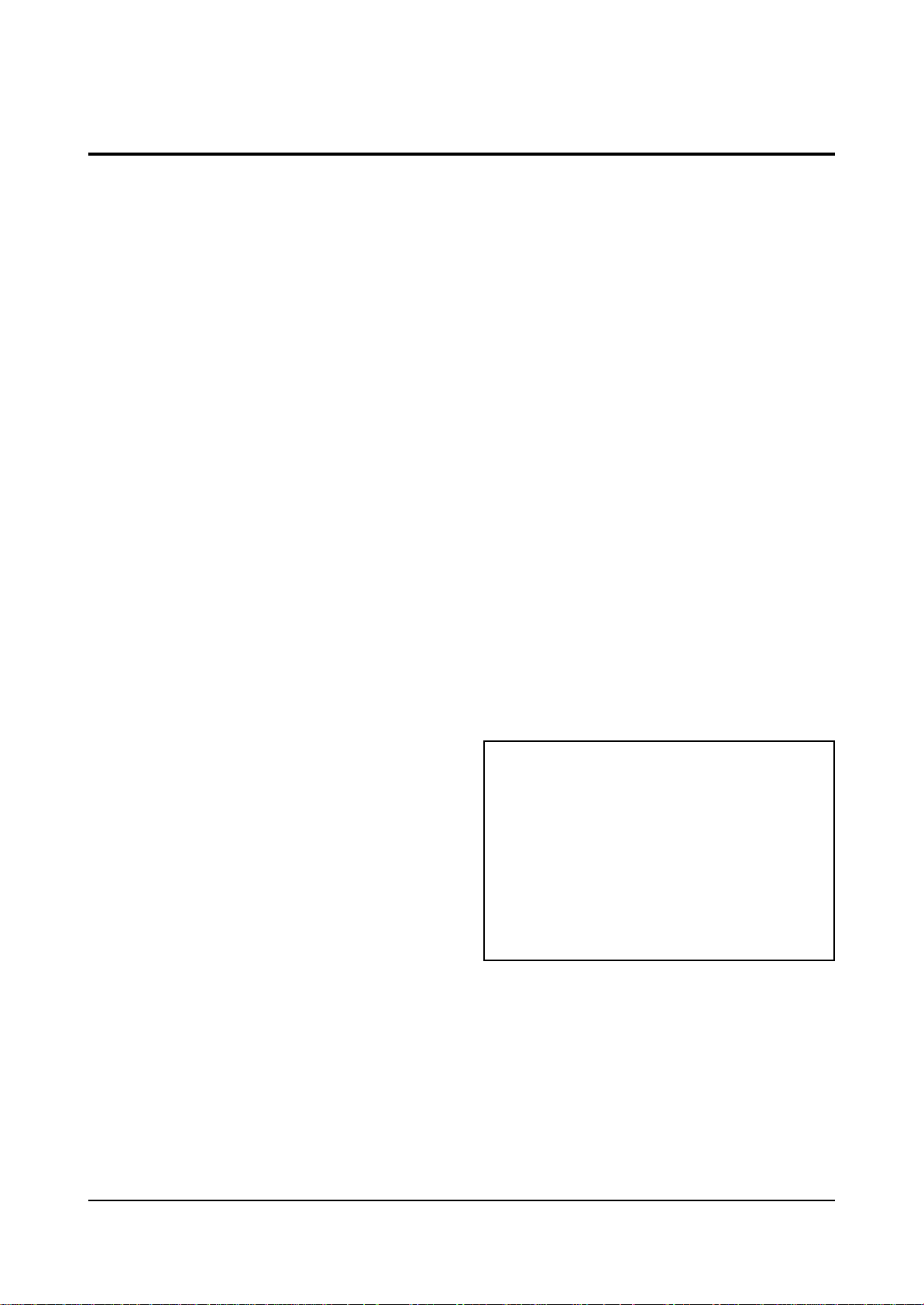

4. Leakage Current Hot Check (Figure 1-1):

Warning: Do not use an isolation

transformer during this test. Use a leakagecurrent tester or a metering system that

complies with American National Standards

Institute (ANSI C101.1, Leakage Current for

Appliances), and Underwriters Laboratories

(UL Publication UL1950.5.2).

5. With the unit completely reassembled, plug

the AC line cord directly into the power

outlet. With the unit’s AC switch first in the

ON position and then OFF, measure the

current between a known earth ground (metal

water pipe, conduit, etc.) and all exposed

metal parts, including: antennas, handle

brackets, metal cabinets, screwheads and

control shafts. The current measured should

not exceed 3.5 milliamp. Reverse the powerplug prongs in the AC outlet and repeat the

test.

Fig. 1-1 AC Leakage Test

6. Antenna Cold Check:

With the unit’s AC plug disconnected from the

AC source, connect an electrical jumper across

the two AC prongs. Connect one lead of the

ohmmeter to an AC prong. Connect the other

lead to the coaxial connector.

Precautions

Samsung Electronics 1-1

LEAKAGE

CURRENT

TESTER

DEVICE

UNDER

TEST

TEST ALL

EXPOSED METAL

SURFACES

3-WIRE CORD

ALSO TEST WITH

PLUG REVERSED

(USING AC ADAPTER

PLUG AS REQUIRED)

EARTH

GROUND

(READING SHOULD

NOT BE ABOVE

3.5mA)

Follow these safety, servicing and ESD precautions to prevent damage and protect against potential

hazards such as electrical shock and X-rays.

Page 4

1-2 Safety Precautions (Continued)

7. High voltage is maintained within specified

limits by close-tolerance, safety-related

components and adjustments. If the high

voltage exceeds the specified limits, check

each of the special components.

8. Design Alteration Warning:

Never alter or add to the mechanical or

electrical design of this unit. Example: Do not

add auxiliary audio or video connectors. Such

alterations might create a safety hazard. Also,

any design changes or additions will void the

manufacturer’s warranty.

9. Hot Chassis Warning:

Some TV receiver chassis are electrically

connected directly to one conductor of the AC

power cord. If an isolation transformer is not

used, these units may be safely serviced only

if the AC power plug is inserted so that the

chassis is connected to the ground side of the

AC source.

To confirm that the AC power plug is inserted

correctly, do the following: Using an AC

voltmeter, measure the voltage between the

chassis and a known earth ground. If the

reading is greater than 1.0V, remove the AC

power plug, reverse its polarity and reinsert.

Re-measure the voltage between the chassis

and ground.

10. Some TV chassis are designed to operate with

85 volts AC between chassis and ground,

regardless of the AC plug polarity. These units

can be safely serviced only if an isolation

transformer inserted between the receiver and

the power source.

11. Some TV chassis have a secondary ground

system in addition to the main chassis ground.

This secondary ground system is not

isolated from the AC power line. The two

ground systems are electrically separated by

insulating material that must not be defeated

or altered.

12. Components, parts and wiring that appear to

have overheated or that are otherwise

damaged should be replaced with parts that

meet the original specifications. Always

determine the cause of damage or overheating, and correct any potential hazards.

13. Observe the original lead dress, especially

near the following areas: Antenna wiring,

sharp edges, and especially the AC and high

voltage power supplies. Always inspect for

pinched, out-of-place, or frayed wiring. Do

not change the spacing between components

and the printed circuit board. Check the AC

power cord for damage. Make sure that leads

and components do not touch thermally hot

parts.

14. Product Safety Notice:

Some electrical and mechanical parts have

special safety-related characteristics which

might not be obvious from visual inspection.

These safety features and the protection they

give might be lost if the replacement component differs from the original—even if the

replacement is rated for higher voltage,

wattage, etc.

Components that are critical for safety are

indicated in the circuit diagram by shading,

( ) or ( ).

Use replacement components that have the

same ratings, especially for flame resistance

and dielectric strength specifications.

A replacement part that does not have the

same safety characteristics as the original

might create shock, fire or other hazards.

15. Littum battery replace warning:

Danger of explosion if battery is incorrectly

replaced, Replace only with the same or

eqivalent type.

Precautions

1-2 Samsung Electronics

“CAUTION, Double-pole/neutral fusing”

CAUTION

Danger of explosion if battery is incorrectly

replaced.

Replace only with the same or equivalent type

recommended by the manufacturer.

Dispose of used batteries according to the manufacturer’s instructions.

Page 5

1-3 Servicing Precautions

1. Servicing precautions are printed on the

cabinet. Follow them.

2. Always unplug the unit’s AC power cord from

the AC power source before attempting to: (a)

Remove or reinstall any component or

assembly, (b) Disconnect an electrical plug or

connector, (c) Connect a test component in

parallel with an electrolytic capacitor.

3. Some components are raised above the printed

circuit board for safety. An insulation tube or

tape is sometimes used. The internal wiring is

sometimes clamped to prevent contact with

thermally hot components. Reinstall all such

elements to their original position.

4. After servicing, always check that the screws,

components and wiring have been correctly

reinstalled. Make sure that the portion around

the serviced part has not been damaged.

5. Check the insulation between the blades of the

AC plug and accessible conductive parts

(examples: metal panels, input terminals and

earphone jacks).

6. Never defeat any of the B+ voltage interlocks.

Do not apply AC power to the unit (or any of

its assemblies) unless all solid-state heat sinks

are correctly installed.

7. Always connect a test instrument’s ground

lead to the instrument chassis ground before

connecting the positive lead; always remove

the instrument’s ground lead last.

8. Plasma display panels have partial afterimages when a same picture continues to be displayed for a certain time. This happens due to

the degradation of brightness caused by a

scale-down effect.

To prevent such afterimages when displaying

a same picture for a certain time, be sure to

reduce the level of brightness and contrast.

ex) Contrast : 50 or 75, Brightness : 25

9. Plasma display is an array of pixels(cells).

Therefore, if at least 99.9% pixels keep normal,

the appropriate panel is judged as ‘approved

product.’ Even though some of pixels keep

luminescent or always light off, do not worry

because the panel is approved.

Precautions

Samsung Electronics 1-3

Warning 1 : First read the “Safety Precautions” section of this manual. If some unforeseen circumstance creates a

conflict between the servicing and safety precautions, always follow the safety precautions.

Warning 2 : An electrolytic capacitor installed with the wrong polarity might explode.

Page 6

1-4 Precautions for Electrostatically Sensitive Devices (ESDs)

1. Some semiconductor (“solid state”) devices

are easily damaged by static electricity. Such

components are called Electrostatically

Sensitive Devices (ESDs); examples include

integrated circuits and some field-effect

transistors. The following techniques will

reduce the occurrence of component damage

caused by static electricity.

2. Immediately before handling any semicon

ductor components or assemblies, drain the

electrostatic charge from your body by

touching a known earth ground. Alternatively,

wear a discharging wrist-strap device. (Be

sure to remove it prior to applying power—

this is an electric shock precaution.)

3. After removing an ESD-equipped assembly,

place it on a conductive surface such as

aluminum foil to prevent accumulation of

electrostatic charge.

4. Do not use freon-propelled chemicals. These

can generate electrical charges that damage

ESDs.

5. Use only a grounded-tip soldering iron when

soldering or unsoldering ESDs.

6. Use only an anti-static solder removal device.

Many solder removal devices are not rated as

“anti-static”; these can accumulate sufficient

electrical charge to damage ESDs.

7. Do not remove a replacement ESD from its

protective package until you are ready to

install it. Most replacement ESDs are

packaged with leads that are electrically

shorted together by conductive foam,

aluminum foil or other conductive materials.

8. Immediately before removing the protective

material from the leads of a replacement ESD,

touch the protective material to the chassis or

circuit assembly into which the device will be

installed.

9. Minimize body motions when handling

unpackaged replacement ESDs. Motions such

as brushing clothes together, or lifting a foot

from a carpeted floor can generate enough

static electricity to damage an ESD.

Precautions

1-4 Samsung Electronics

CAUTION

These servicing instructions are for use by

qualified service personnel only.

To reduce the risk of electric shock do not

perform any servicing other than that contained

in the operating instructions unless you are

qualified to do so.

Page 7

Reference Information

Samsung Electronics 2-1

2. Reference Information

2-1 Tables of Abbreviations and Acronyms

A

Ah

Å

dB

dBm

°C

°F

°K

F

G

GHz

g

H

Hz

h

ips

kWh

kg

kHz

kΩ

km

km/h

kV

kVA

kW

I

MHz

Ampere

Ampere-hour

Angstrom

Decibel

Decibel Referenced to One

Milliwatt

Degree Celsius

Degree Fahrenheit

degree Kelvin

Farad

Gauss

Gigahertz

Gram

Henry

Hertz

Hour

Inches Per Second

Kilowatt-hour

Kilogram

Kilohertz

Kilohm

Kilometer

Kilometer Per Hour

Kilovolt

Kilovolt-ampere

Kilowatt

Liter

Megahertz

MV

MW

MΩ

m

µA

µF

µH

µm

µs

µW

mA

mg

mH

mI

mm

ms

mV

nF

Ω

pF

Ib

rpm

rps

s

V

VA

W

Wh

Megavolt

Megawatt

Megohm

Meter

Microampere

Microfarad

Microhenry

Micrometer

Microsecond

Microwatt

Milliampere

Milligram

Millihenry

Milliliter

Millimeter

Millisecond

Millivolt

Nanofarad

Ohm

Picofarad

Pound

Revolutions Per Minute

Revolutions Per Second

Second (Time)

Volt

Volt-ampere

Watt

Watt-hour

Table 2-1 Abbreviations

Page 8

Reference Information

2-2 Samsung Electronics

Table 2-2 Table of Acronyms

ABL

AC

ACC

AF

AFC

AFT

AGC

AM

ANSI

APC

APC

A/V

AVC

BAL

BPF

B-Y

CATV

CB

CCD

CCTV

Ch

CRT

CW

DC

DVM

EIA

ESD

ESD

FBP

FBT

FF

FM

FS

GND

G-Y

H

HF

HI-FI

IC

IC

IF

Automatic Brightness Limiter

Alternating Current

Automatic Chroma Control

Audio Frequency

Automatic Frequency Control

Automatic Fine Tuning

Automatic Gain Control

Amplitude Modulation

American National Standards Institute

Automatic Phase Control

Automatic Picture Control

Audio-Video

Automatic Volume Control

Balance

Bandpass Filter

Blue-Y

Community Antenna Television (Cable TV)

Citizens Band

Charge Coupled Device

Closed Circuit Television

Channel

Cathode Ray Tube

Continuous Wave

Direct Current

Digital Volt Meter

Electronics Industries Association

Electrostatic Discharge

Electrostatically Sensitive Device

Feedback Pulse

Flyback Transformer

Flip-Flop

Frequency Modulation

Fail Safe

Ground

Green-Y

High

High-Frequency

High Fidelity

Inductance-Capacitance

Integrated Circuit

Intermediate Frequency

I/O

L

L

LED

LF

MOSFET

MTS

NAB

NEC

NTSC

OSD

PCB

PLL

PWM

QIF

R

RC

RF

R-Y

SAP

SAW

SIF

SMPS

S/N

SW

TP

TTL

TV

UHF

UL

UV

VCD

VCO

VCXO

VHF

VIF

VR

VTR

VTVM

TR

Input/output

Left

Low

Light Emitting Diode

Low Frequency

Metal-Oxide-Semiconductor-Field-Effect-Tr

Multi-channel Television Sound

National Association of Broadcasters

National Electric Code

National Television Systems Committee

On Screen Display

Printed Circuit Board

Phase-Locked Loop

Pulse Width Modulation

Quadrature Intermediate Frequency

Right

Resistor & Capacitor

Radio Frequency

Red-Y

Second Audio Program

Surface Acoustic Wave(Filter)

Sound Intermediate Frequency

Switching Mode Power Supply

Signal/Noise

Switch

Test Point

Transistor Transistor Logic

Television

Ultra High Frequency

Underwriters Laboratories

Ultraviolet

Variable-Capacitance Diode

Voltage Controlled Oscillator

Voltage Controlled Crystal Oscillator

Very High Frequency

Video Intermediate Frequency

Variable Resistor

Video Tape Recorder

Vacuum Tube Voltmeter

Transistor

Page 9

Specifications

Samsung Electronics 3-1

3. Specifications

MODEL

SCREEN SIZE

3-1 Display(PDP Monitor)

Display

Remote Control

Display

Remote Control

Power Consumption

Voltage

RGB input

VIDEO input

Dimensions

(mm/inch)

Weight

HPL6315

1393(H) x 783(V)/54.86 x 30.84

1566(W) x 89(D) x 912.5(H) mm/61.65(W) x 3.5(D) x 35.93(H) Inches

54(W) x 31.5(D) x 220(H)mm/2.13(W) x 1.24(D) x 8.66(H) Inches

72Kg/158.73Ibs

150g(including batteries)/0.33Ibs

AC120V 60Hz

725W

RGB1 : MINI D-SUB 15P

RBG2 : BNC (R/G/B H(CS)/V)

VIDEO : ANALOG 0.714VPP/75 Ω(Terminated)

SYNC(H,V)

VIDEO : 1.0VPP/75 Ω (BNC)

S-VIDEO : Y -> 1.0VPP/75 Ω

C -> 0.28V

PP/75 Ω

COMPONENT (Y/Pb/Pr) : Y -> 1.0V

PP/75 Ω

Pb -> 0.7vPP/75 Ω

Pr -> 0.7VPP/75 Ω

Page 10

3-2 Samsung Electronics

MEMO

Page 11

Alignment and Adjustments

Samsung Electronics 5-1

5. Alignment and Adjustments

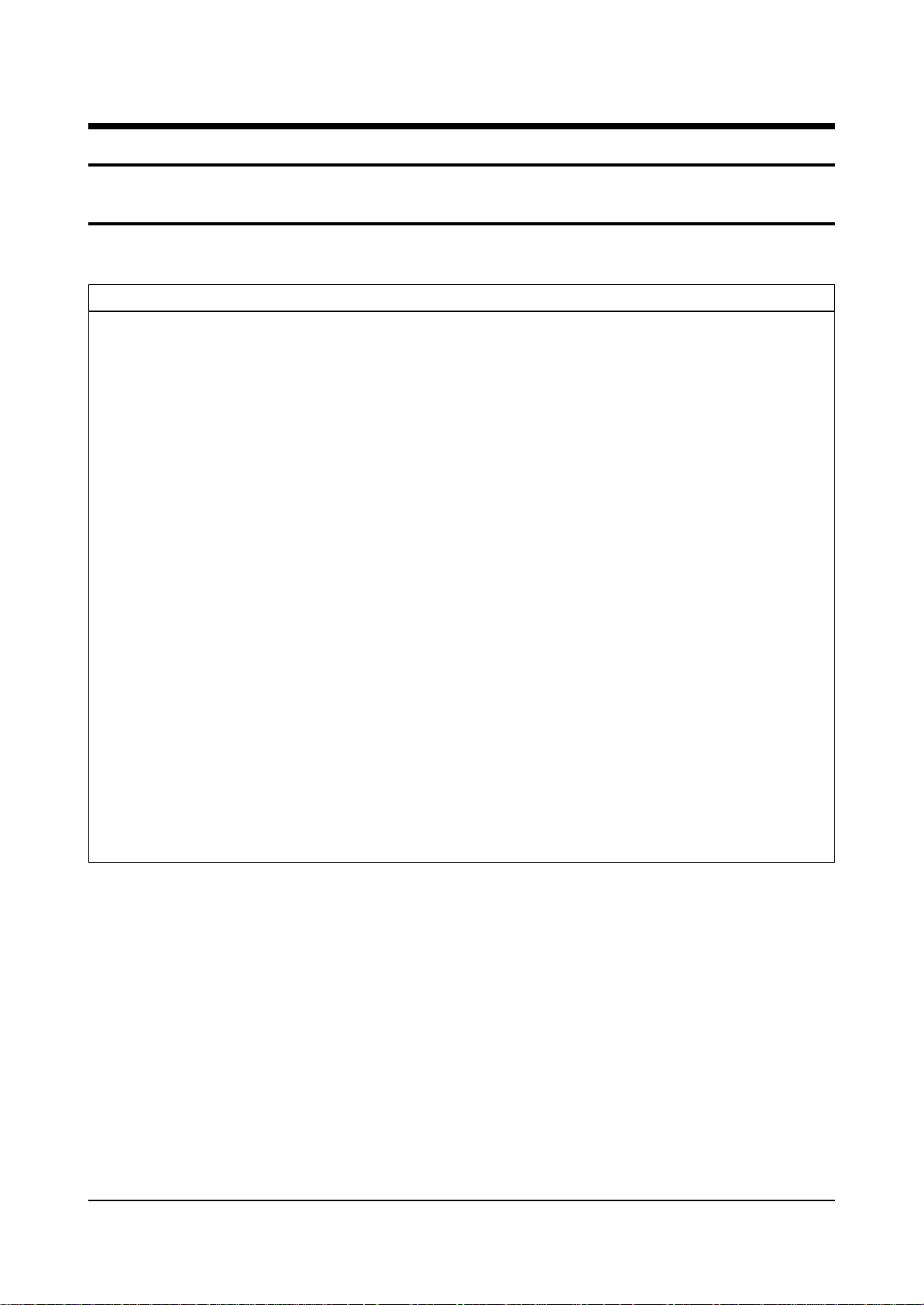

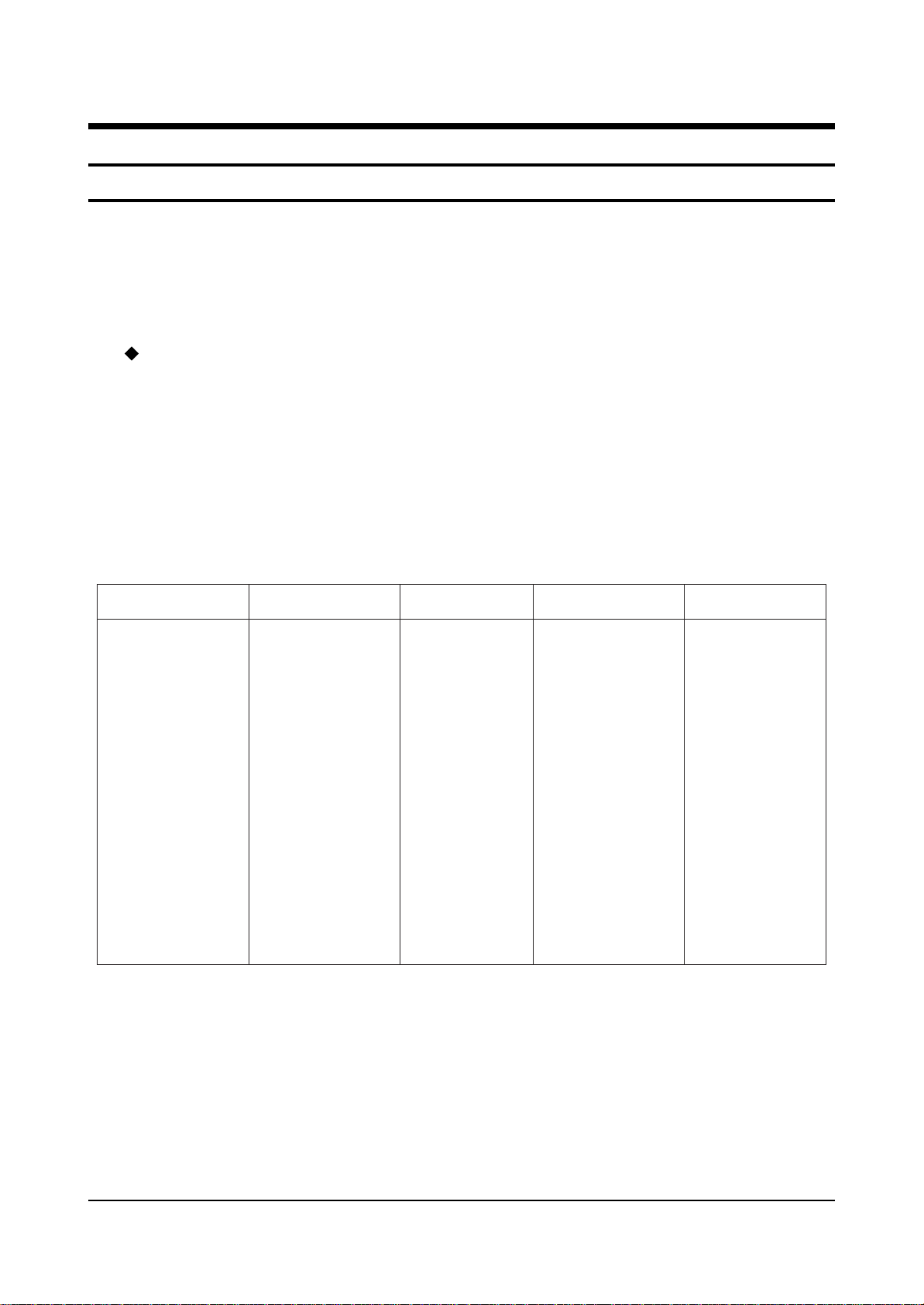

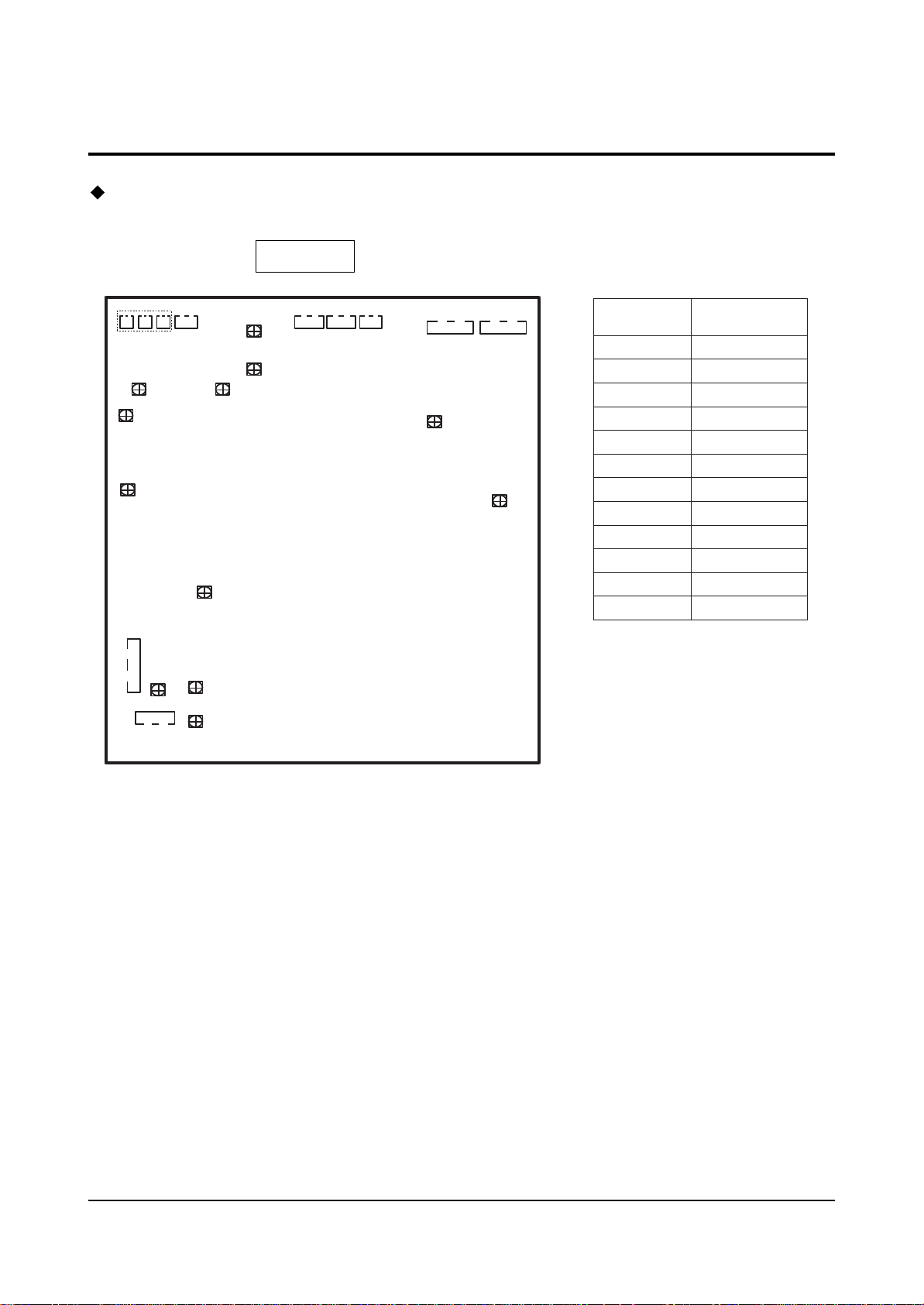

5-1 Service Mode

5-1-1 SERVICE MODE ENTRY METHOD (General Transmitter)

1. Turn off the power to make the SET STAND-BY mode.

2. In order to enter the Service Mode, select MUTE-1-8-2-POWER.

In case entry into SERVICE MODE is unsuccessful, repeat the procedures above.

5-1-2 Initial DISPLAY State in times of SERVICE MODE Switch overs

PW364

INITIAL DISPLAY

SDA92 80 VPC3230 SDA9400

1, PW

364

2, SD

A9280

3, V

PC3230

4, SD

A9400

5, C

XA2101

6, A

D9884

7, O

SD POSITION

8, O

PTION

9, R

ESET

10, A

GING

H

orizonta lSize

V

er tical

Horizontal

Ve r t i ca l

Si

ze

Pos

Pos

CTIT

HRESH

CTIT

RAWID

Y- D

ELAY

L

PF GA IN

B

PF GAIN

H

PF GA IN

PH

ACOM

C

OR

B

RIGHT YUV

C

ONT YUV

I

FCOMP

ChromaB

and

L

uma LPF

H

PLL Speed

L

uma Delay

3230 Bri

ght

3230 C

ontr ast

HL

PF Y/ C

L

PF Chroma

HHPeak Fil

ter

PeakingG

ain

C

oaring off/ on

O

UT DELAY

TNRCLY

CLY

TNRCLC

CLY

ST

OP MODE

Page 12

Alignment and Adjustments

5-2 Samsung Electronics

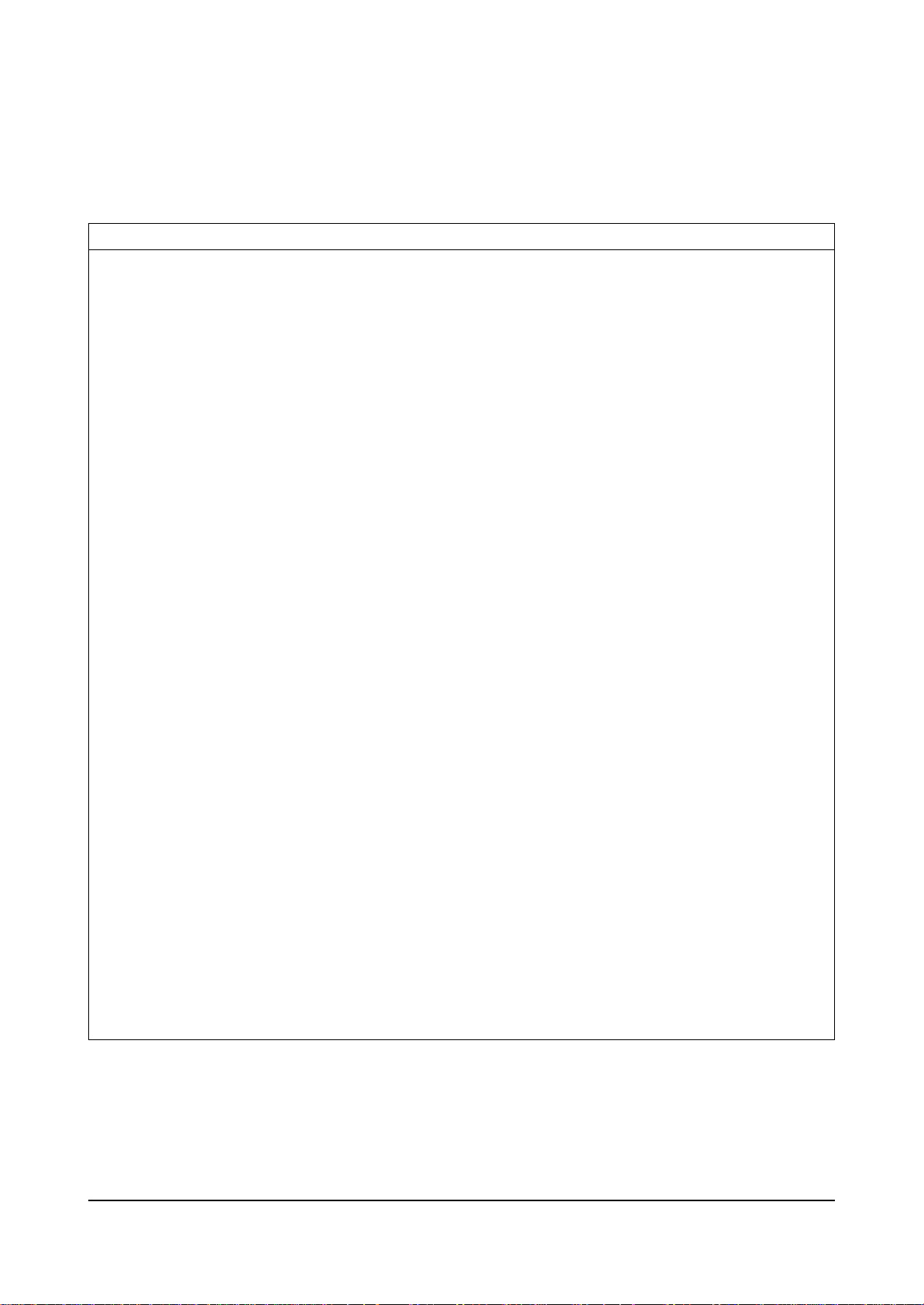

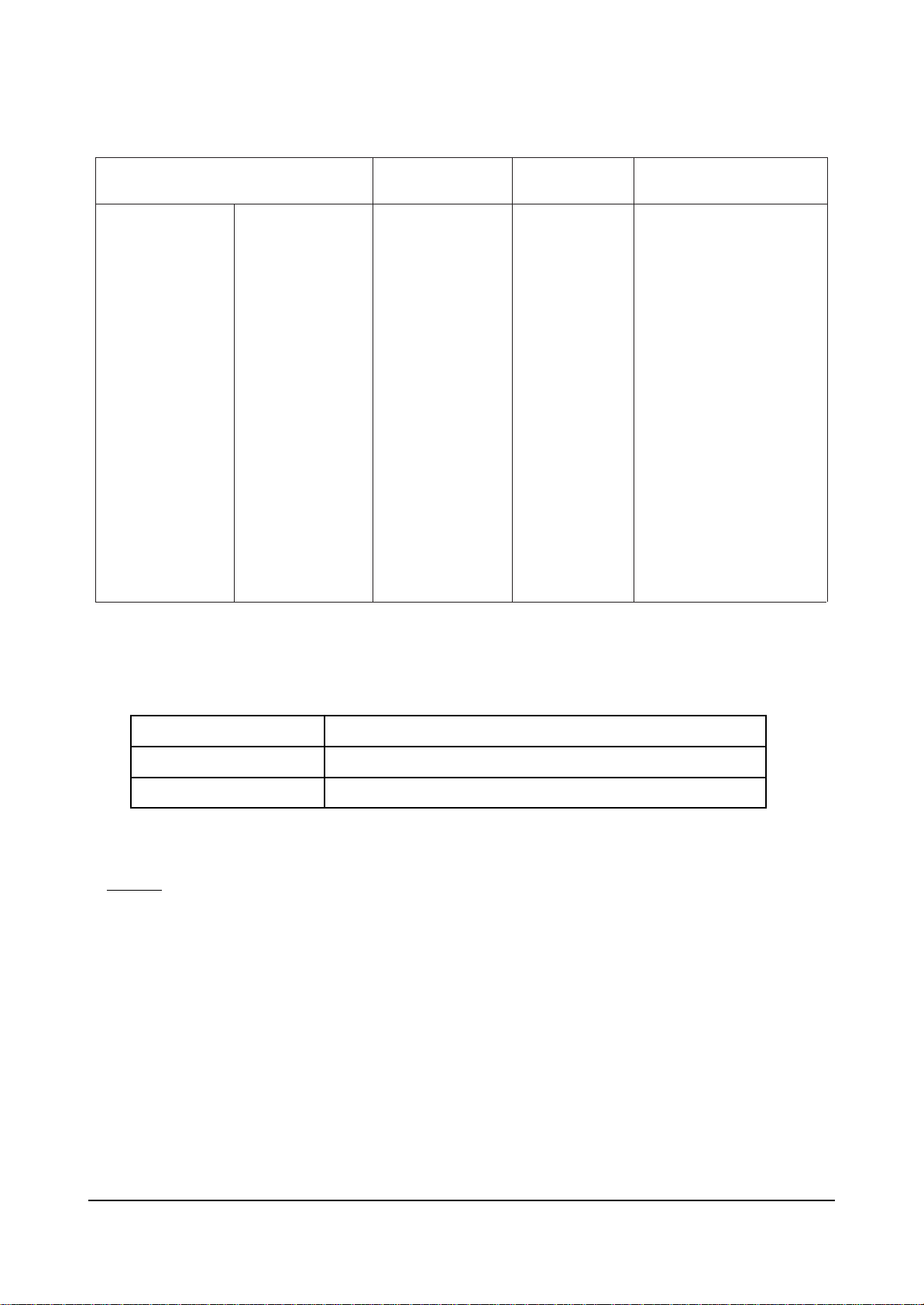

5-1-3 Buttons Operations within SERVICE MODE

#Notice

The existing service data may be deleted after downloading a program. Be sure to make a backup copy of

your data before downloading and then restore the data after completing the download.

Menu

Channel UP/DOWN

Volume UP/DOWN

Entire menu display

Cursor move to select items

Enable to increase and decrease the data of the selected items

Limit Level

Sys tem

D-Color

R-DRIVE

-DRIVE

G

-DRIVE

B

R-Cutoff

G-Cutoff

-Cut off

B

ABL MODE

ABL TH

HSEPSEL

CONT RAST

BRI GHT

CR OFFSET

CB

OFFS ET1

CXA2101 AD9884

DRIVE

SUB BRIGHT

SUB CONT

SUB COLOR

SUB HUE

SUB SHP

R-Y/R

R-Y/B

GG-Y/R

-Y/B

P

ABL LEVEL

SHP FO

PRE/OVER

CTI LEVEL

1

LTI LEVEL

DC - TRAN

D-PIC

RED

Gain

GREEN

BLUE

OFFSET

RED

GREEN

BLUE

GAIN DRIVE

OFFSET DIRVE

V CONTRAST

V BRIGHT

PHASE

CHANGE PUMP

Gain

Gain

OFFSET

OFFSET

OSD

POSITION

HORIZ

VE RT

OP TION

1, BACK GR OUN D COLOR

SHIFT PIXEL

2,

PIXEL SHIFT

3,

PIXEL SHIFT

4,

FAN PROTECT

5,

TEMP

6,

7,

8, BASE LANGUAGE

PROTECT

SHARPNESS

MIN

SEC

Page 13

Alignment and Adjustments

Samsung Electronics 5-3

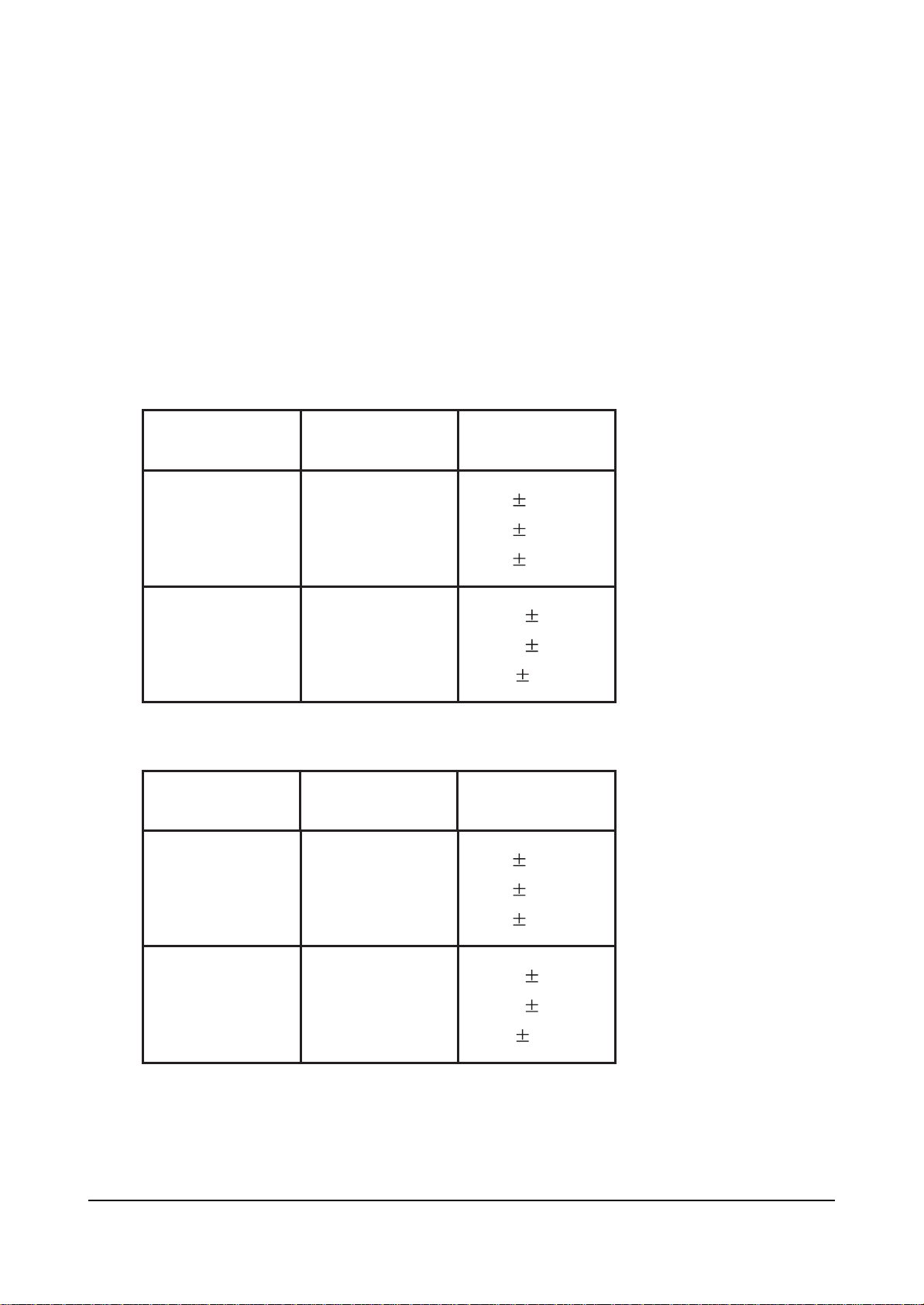

5-1-4 White Balance Adjust Method

1. Press MUTE-1-8-2-POWER to enter the factory mode.

2. Enter AD9884

3. Adjust LOW coordinates as R, B OFFSET and HIGH coordinates as R, B GAIN.(GREEN is fixed.)

4. In AD9884, adjust brightness with V CONTRAST / V BRIGHT for VIDEO / DTV, and adjust with

GAIN DRIVE / OFFSET DRIVE for PC.

1. VIDEO MODE (SPR-3100, input TOSHIBA PATTERN)

2. DTV MODE (SPR-3100, input TOSHIBA PATTERN)

A

dj ustme

nt

Adjustme

nt

Coor dinates

Coor dinates

Value

Deviation

A

dj ustme

nt

Adjustme

nt

Coor dinates

Coor dinates

Value

Deviation

H

-LIGHT

-LIGHT

x:286

y

:

274

Y

:

18.7(fL)

3

3

3

L

H-LIGHT

-LIGHT

L

x:278

y

:

272

Y

:0.53(f L)

(f L)

5

5

0. 1

x:288

y

:

277

Y: 16.1

Y:

3

3

3

x:280

y

:277

0.71

5

5

0. 1

- W/B Adjustment SPEC (Suwom Factory Toshiba PATTERN)

Page 14

Alignment and Adjustments

5-4 Samsung Electronics

2. PC MODE (VG828, input TOSHIBA PATTERN)

A

dj ustme

nt

Adjustme

nt

Coor dinates

Coor dinates

Value

Deviation

H-LIGHT

-LIGHT

L

x:287

y:288

Y: 21.3(fL)

Y:

x:287

y:294

2.17

3

3

3

5

5

0. 1

Page 15

Alignment and Adjustments

Samsung Electronics 5-5

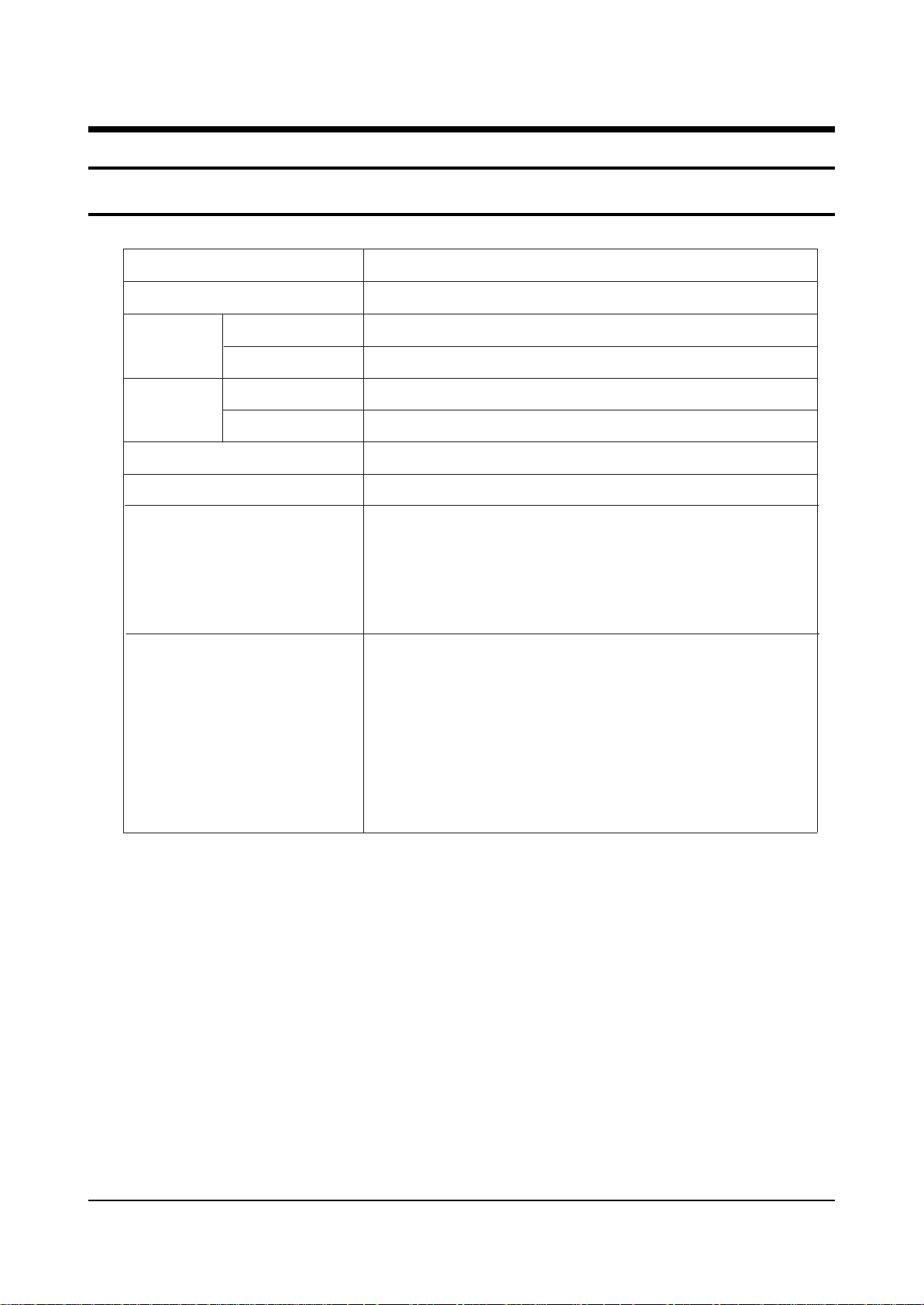

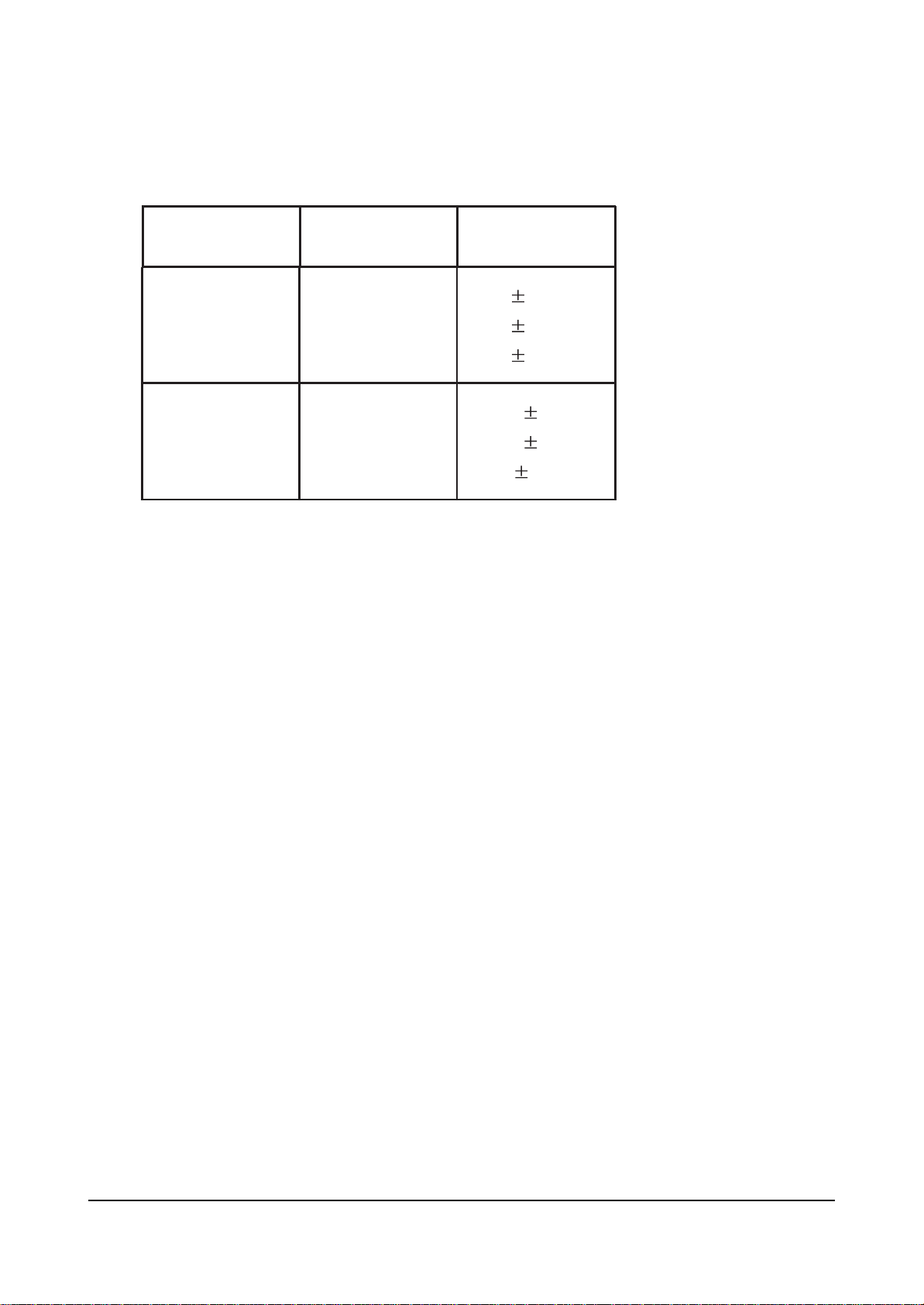

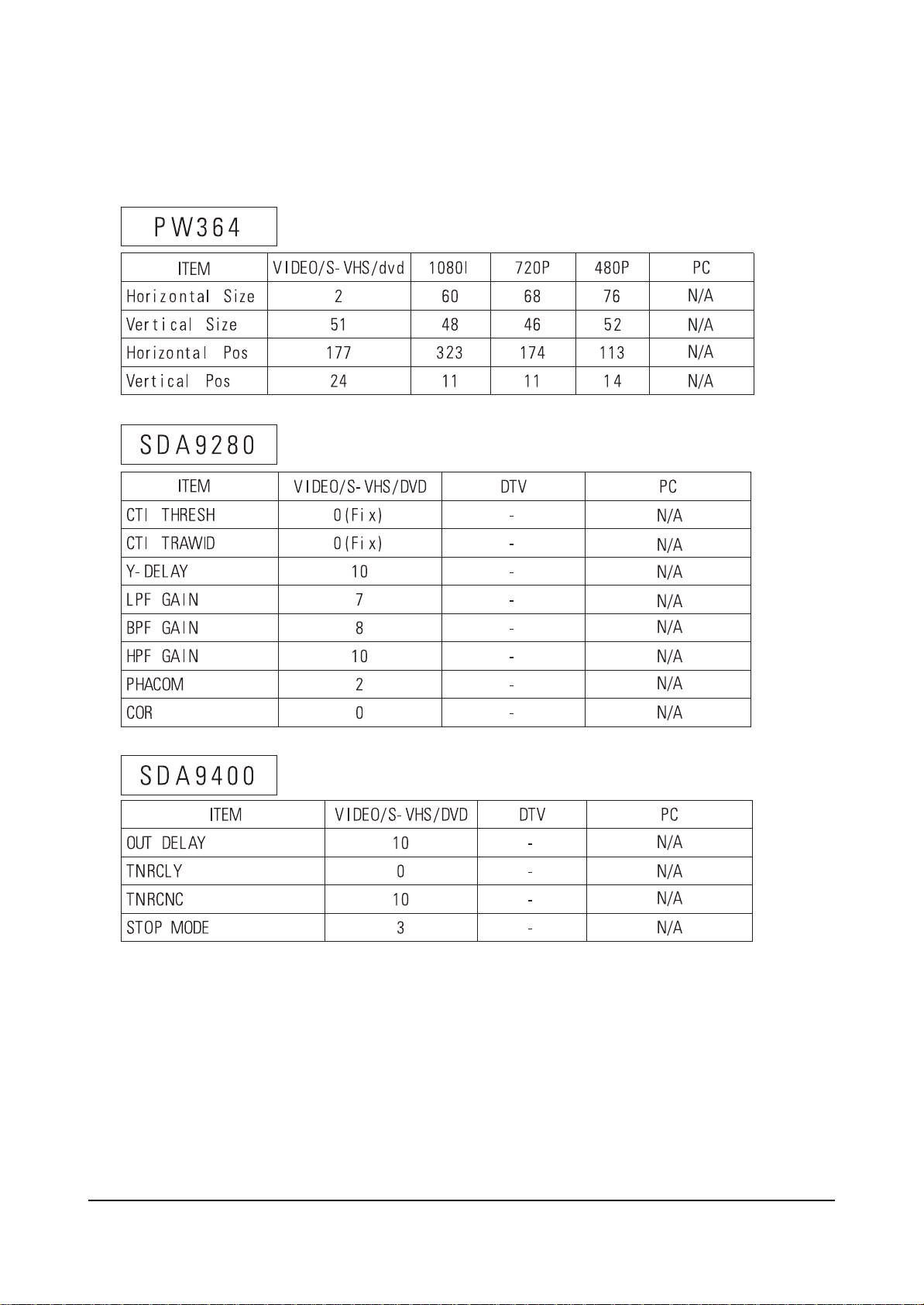

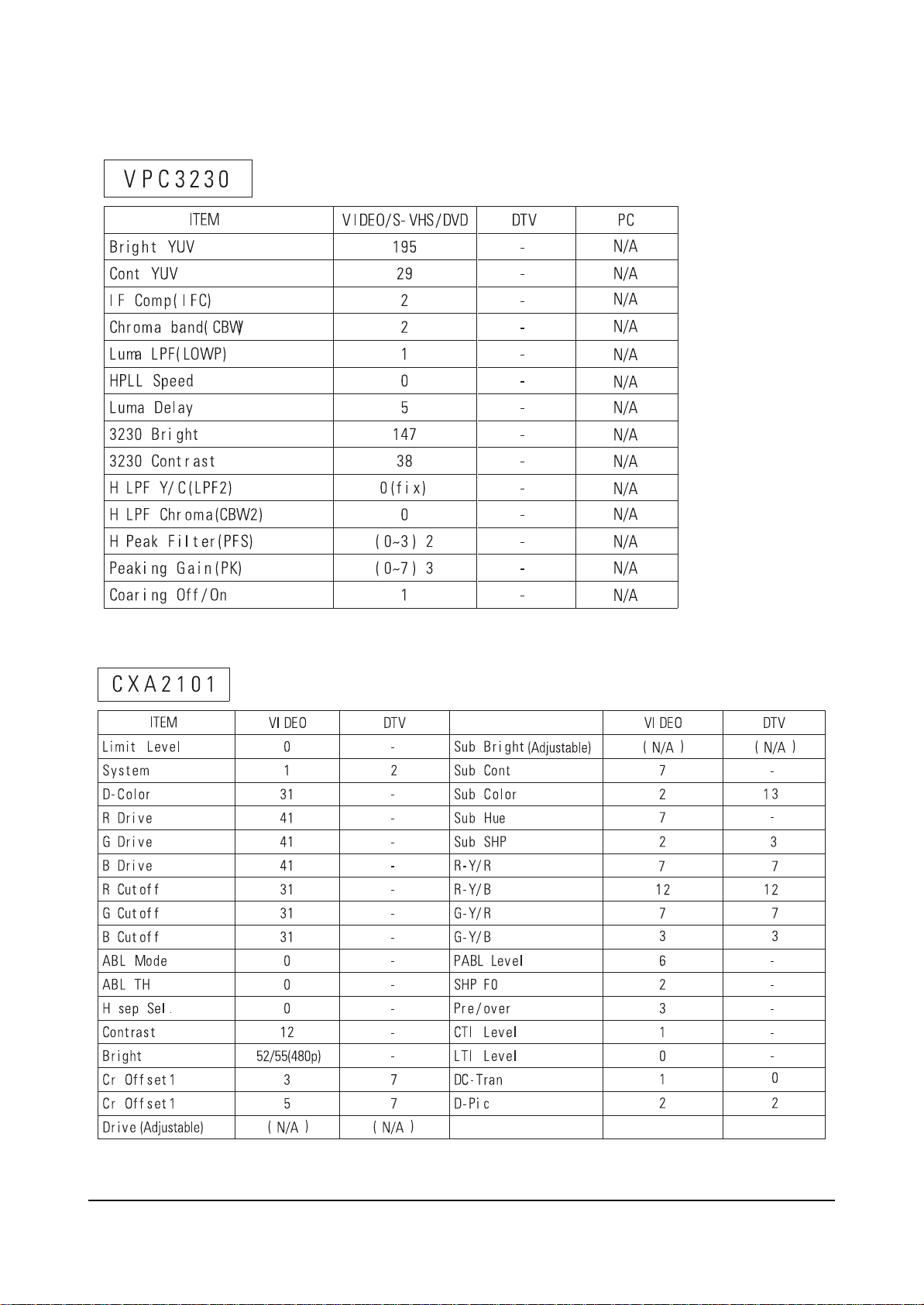

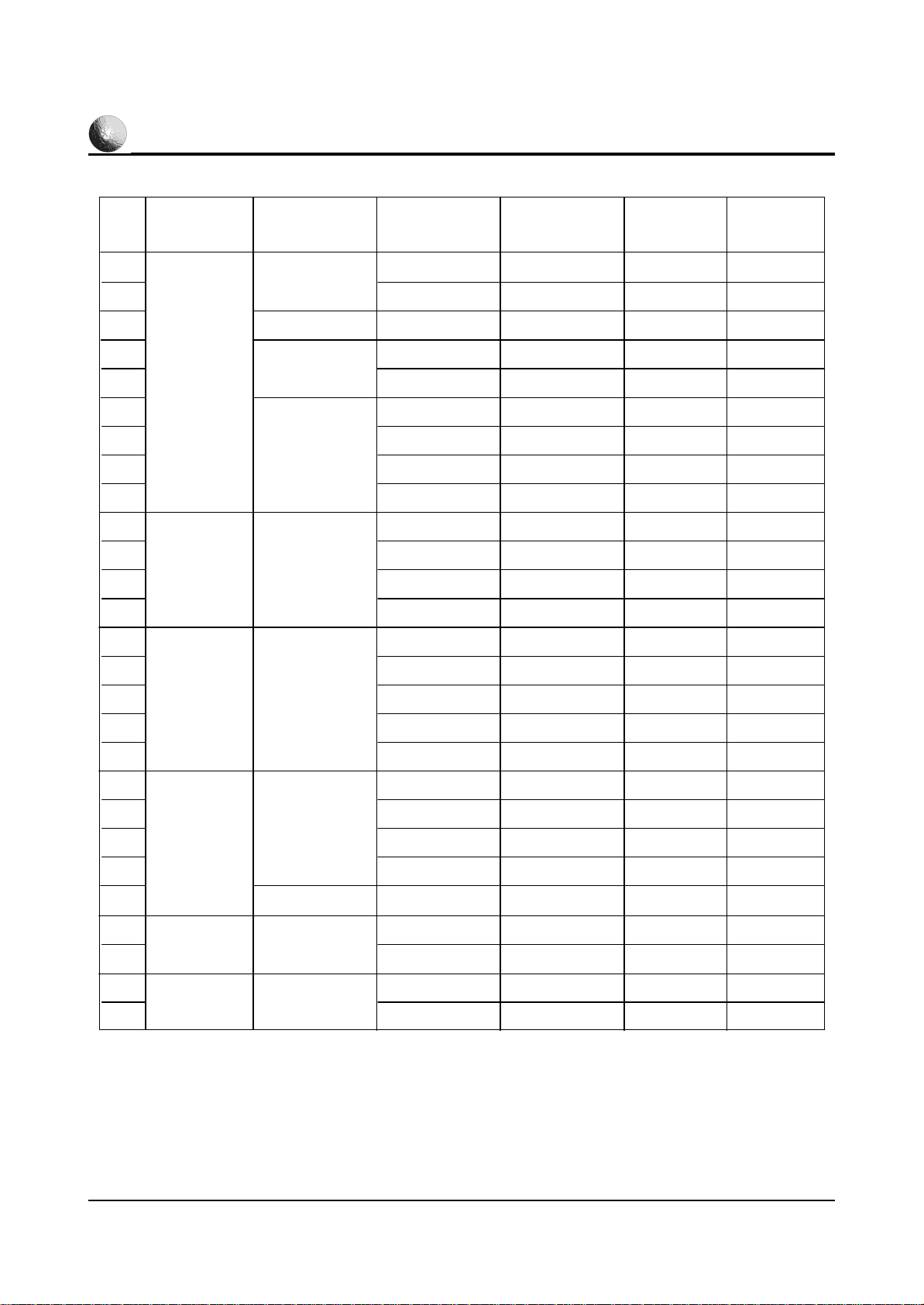

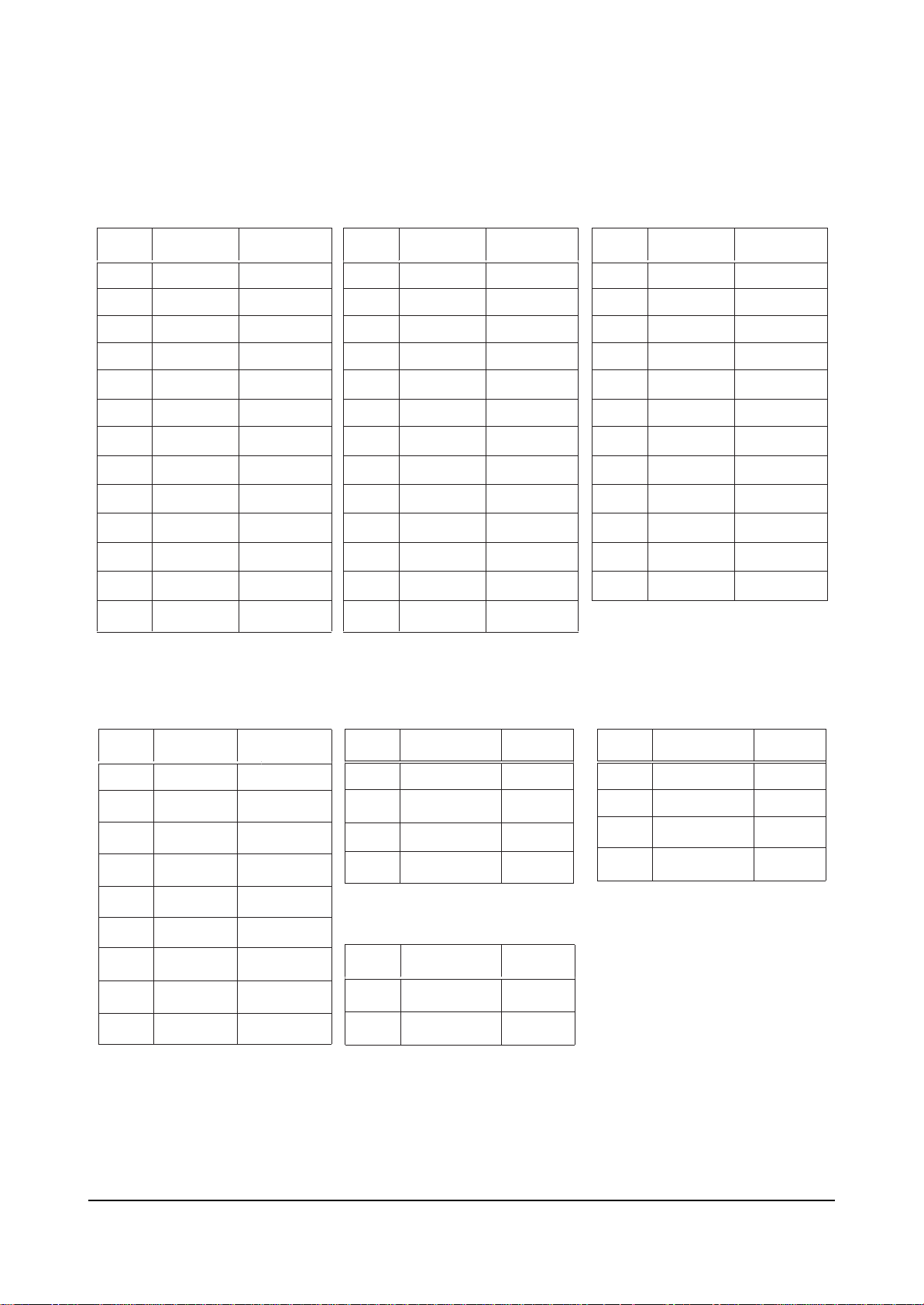

5-1-5 SCALAR FACTORY DATA DEFAULT VALUES

Page 16

Alignment and Adjustments

5-6 Samsung Electronics

Page 17

Alignment and Adjustments

Samsung Electronics 5-7

Page 18

5-8 Samsung Electronics

Alignment and Adjustments

HPL6315

VGA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Video signal Dot X Line

640 X 350

640 X 400

VGA

WVGA

720 X 400

640 X 480

848 X 480

Ve rtical

Frequency (Hz)

70.086

85.080

85.080

70.087

85.039

59.940

72.809

75.000

85.008

60.000

72.000

75.000

85.000

56.250

Horizontal

Frequency (kHz)

31.469

37.861

37.861

31.469

37.927

31.469

37.861

37.500

43.269

29.838

35.156

36.072

37.650

42.925

Ve rtical

polarity

N

N

P

P

P

N

N

N

N

P

P

P

P

N/P

Horizontal

polarity

P

P

N

N

N

N

N

N

N

N

N

N

N

N/P

15

16

17

18

19

20

21

22

23

24

25

26

27

SVGA

XGA

WXGA

SXGA

800 X 600

1024 X 768

1152 X 864

1280 X 768

1280 X 1024

60.317

72.188

75.000

85.061

60.004

70.069

75.029

84.997

75.000

60

75

60.020

75.025

37.879

48.077

46.875

53.674

48.363

56.476

60.023

68.677

67.500

47.700

60.150

63.981

79.976

P

P

P

P

N

N

P

P

P

P

P

P

P

P

P

P

P

N

N

P

P

P

N

N

P

P

Page 19

Alignment and Adjustments

Samsung Electronics 5-9

5-2 Adjusting the Discharge Voltage Of the Main Unit While Replacing ASS'Y (Body Part)

Turning the variable resistor clockwise reduces voltage except VG, V9, and VR(6).

SMPS

OUT PUT Voltage(V)

1. V A

1. V FAN

3. SIGNAL

V5D

VFAN

VAMP

1. V SB

4. V 5A

11. V 12A

12. V 5D1

1. V 5D

3. V 5D

V5D1

VSET

VSCAN

VA

1. V A

2. V A

2. V A

1. V 5D

3. V G

5. V SCAN

7. V E

11. V S

12. V S

13. V S

VE

1. V 5D

3. V G

5. V E

7. V SCAN

10. V S

11. V S

12. V S

VS

VS 168

VE 183

VA 70

VSET 190

VSCAN 80

V5D 5

VFAN 12

VAMP 9

V5D1 5

V5A 5

V12A 12

VSB 5

V12A

V5A

VSB

1. V 5A

3. V 9A

4. V 12A

6. V AMP

7. V AMP

Page 20

Alignment and Adjustments

5-10 Samsung Electronics

Alignment and Adjustments

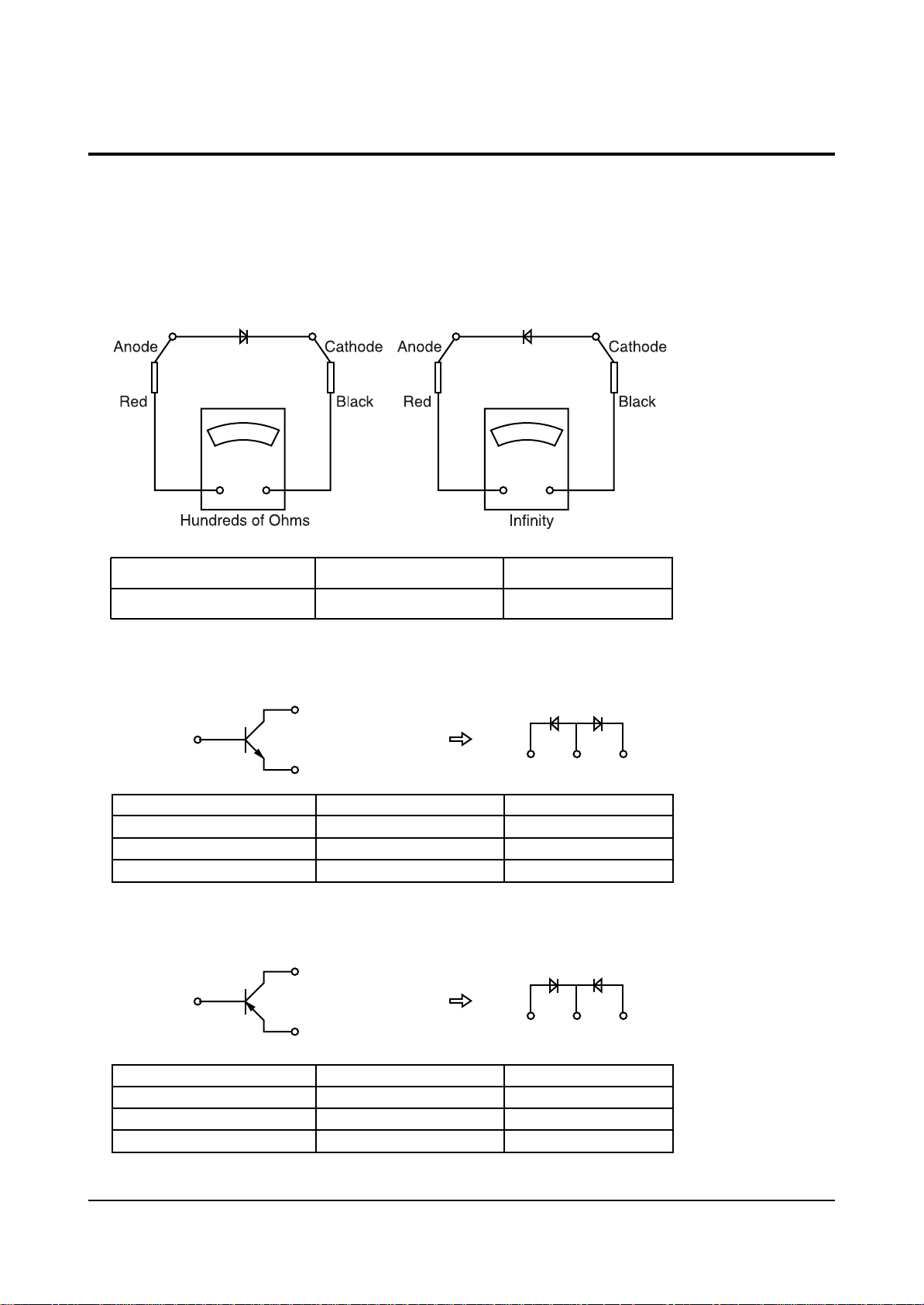

5-3 Fault Finding Using MULTI METER

Parts defects can be found for DIODE TRANSISTOR IC, using MULTI TEST including

Forward/Reverse direction Multi Test. Of course, in case resistance of several ohms and COIL are connected in parallel circuit, the lock out circuit parallel connected to part must be severed.

1.DIODE

2. TRANSISTOR

● For NPN(KSC815-Y, 2SC2068, 2SC2331-Y)

● For PNP(KSA539-Y)

Forward Direction

Hundreds of ohms

Reverse Direction

Infinity

Between Anode and Cathode

C (COLLECTOR)

E

B(BASE)

BC

C (COLLECTOR)

E

B(BASE)

BC

E (EMITTER)

E (EMITTER)

Forward Direction

Hundreds of ohms

Hundreds of ohms

Infinity

Reverse Direction

Infinity

Infinity

Infinity

Between B and E

Between B and C

Between E and C

Forward Direction

Hundreds of ohms

Hundreds of ohms

Infinity

Reverse Direction

Infinity

Infinity

Infinity

Between B and E

Between B and C

Between E and C

+- +-

Page 21

Alignment and Adjustments

Samsung Electronics 5-11

Alignment and Adjustments

3. IC (INTEGRATED CIRCUIT)

IC has built in DIODE against overvoltage in PIN. Generally, except for internal circuit defects, IC defects

can be found, by measuring the DIODE.

✍ Defects have SHORT(0 ohm) for both forward and reverse direction.

Hundreds of ohms

Forward Direction

Reverse Direction

Varying depending on IC but generally normal

Infinity in DIODE TEST MODE

Page 22

5-12 Samsung Electronics

MEMO

Page 23

Circuit Operation Description

Samsung Electronics 6-1

6. Circuit Description

6-1 Power supply

6-1-1 Outline(PDP SMPS)

Considering various related conditions, the switching regulator with good efficiency and allowing for its

small size and light weight was used as the power supply for PDP 50inch, VS requiring high power consumption used forward converter and 12VSAMP used the simple flyback converter and other high voltage

(VSCAN,VSET,VE)used DC/DC converter. To comply with the international harmonics standards and

improve the power factor, active PFC(Power Factor Correction) was used to rectify AC input into +400V

DC output, which in turns used as input to the switching regulator.

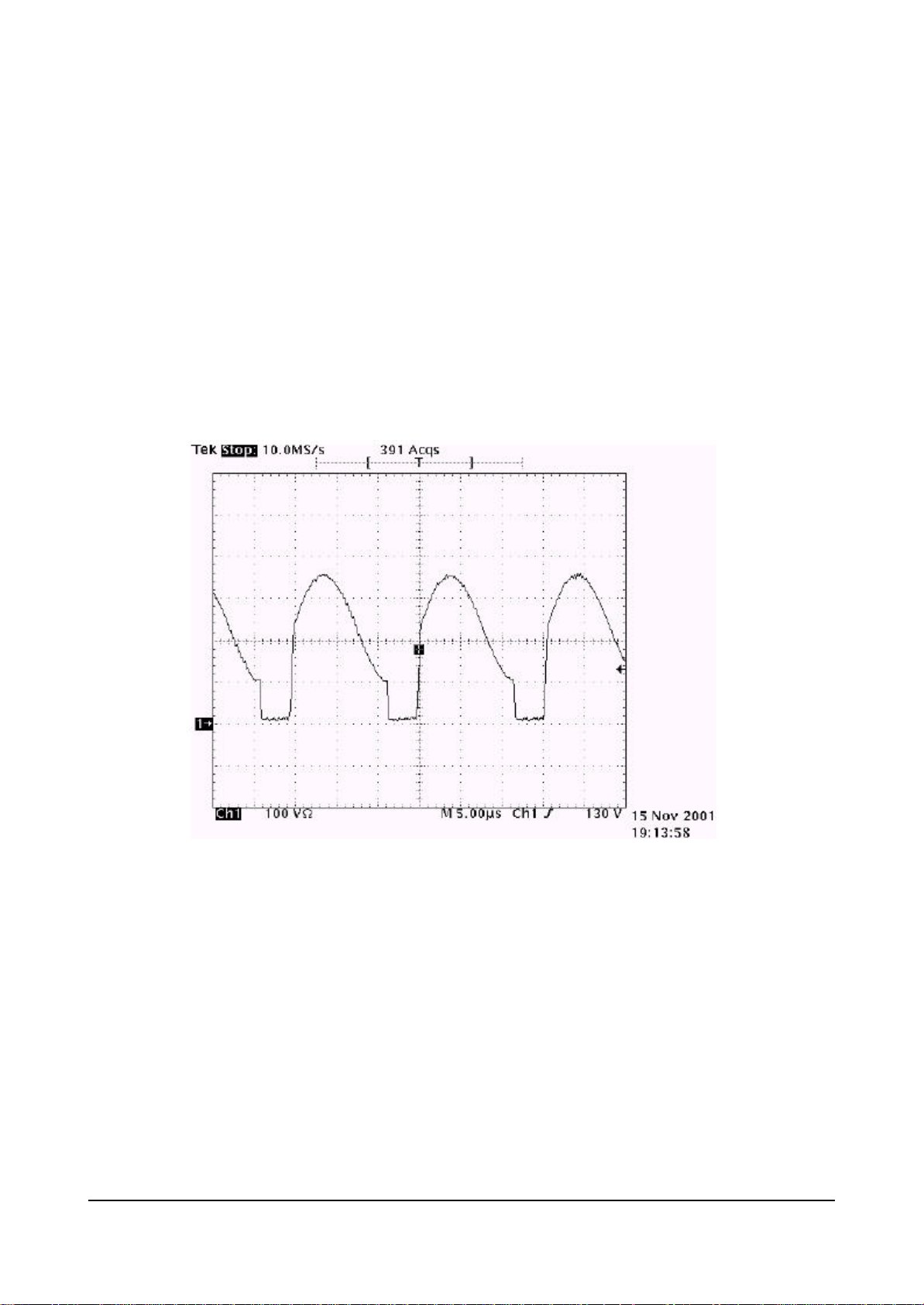

6-1-2 63"HD SMPS Specification

(1) Input

The PDP-PS-421S board should be designed so that the AC power supply within the 100VAC

(common) to 150VAC and the input frequency within 50/60Hz can be applied.

(2) Output

The PDP-PS-421S board converts the AC Voltages (+165Vs1, +75Va, +185Ve, +5Vd, +12Vcc, +6Vsp,

+9Vsp, +9Vcc, +12Vfan, +5Vd1, +5Va, +220Vset, +75Vscan, +18Vg) into the DC Voltages.

The usage and specification of each output is as shown in Table 1.

Table 1 shows the power supplies for PDP SMPS.

Table1. Specifications of Output Power Supplies for PDP SMPS

165Vs

75Va

185Ve

220Vset

75Vscan

5Vd

18Vg

5Vdl

5Va

9Vcc

12Vcc

6Vsp

12Vfan

5Vsb

165V ± 1%

75V ± 1%

185V ± 1%

220V ± 1%

75V ± 1%

5.2V ± 1%

18V ± 5%

5.2V ± 1%

5.2V ± 1%

9.2V ± 5%

12.2V ± 5%

6V ± 5%

11V ~ 14V

5.2V ± 1%

160V ~ 190V

60V ~ 85V

170V ~ 200V

200V ~ 250V

60V ~ 90V

4.5V ~ 5.5V

-

4.5V ~ 5.5V

-

-

-

3V ~ 24V

-

5.0V ~ 5.4V

0.2

0.2

0.01

0.01

0.01

0.3

0.07

0.2

0.1

0.07

0.07

0.25

0.1

0.1

2.0

2.0

0.1

→

→

→

→

→

→

→

→

2.5

→

1.0

0.2

0.2

0.01

0.01

0.01

0.3

0.07

0.2

0.1

0.07

0.07

0.25

0.1

0.1

Output

Voltage

(V)

Voltage

Setting

(Normal Load)

Output

Voltage

Variable Point

Output Current(A)

Min Non Max

Page 24

Circuit Operation Description

6-2 Samsung Electronics

(3) FUNCTION OF BOARD

1) Remote control

Using 120V/10A relay, the board makes remote control available.

2) Voltage

The board designed so that input voltage can be used within 100 VAC to 150VAC.

3) Improvement of power factor

The board is designed using PFC circuit so that PF (Power Factor) can be over 0.95, because

low PF can be a problem in high voltage power.

4) Protection

The OCP (Over Current Protection), the OVP (Over voltage Protection), and the Short Circuit

Protection functions are added against system malfunction.

(4) BLOCK DIAGRAM

This product can be defined as a power supply device (Input power: AC110/220V), consists of

Inrush Current Limit Circuit on Input and Power Factor Correction circuits, VS, VA, and VI Block,

providing the power (current) required for PDP Panel discharges and external circuits. PFC circuit

utilizes Discontinuous Current Mode ( DCM) that produces a high efficiency. And, an input EMI

filter circuit is equipped on the exterior.

1) PFC Block Boost Discontinuous Current Mode (DCM) PFC circuit is used for PFC (Power

Factor Correction), where a common PWM IC gives an easy control, a simple circuit onfiguration,

and a high efficiency. The circuit operates as described as following:RELAY is to be operated by

inputting initial Relay “ON” while the resistance for Inrush Current Limit charges a capacitor of

PFC Output Terminal. If the charged voltage of the capacitor goes over 340V, a comparator of

PFC circuit controller activates VA Block and Relay for Inrush Current Limit. Thereafter, PFC

circuit initiates a normal operation.

PFC circuit has output, voltage, current limit circuits for placing a restriction on switching current,

and protective (safeguard) circuits against output over-voltage. The over-voltage induces input

Terminal Relay to be “OFF” with the set shut down.

2) Vs Block supplies the sustain power closely related to PDP Panel and includes 165Vs and

185Ve employing a Full-bridge circuit as Topology. In order to insulate gate signal, Driver

at the secondary side based on properties of the pulse type of load. 185Ve power utilizes a

variable Regulator for sub-output of 165Vs power, which is supplied to the load being added to

165Vs power. 70kHz is applied for switching frequency that has the Sequence operated after

rising 5Vd power.

Table 2. Security function SPEC required for PDP SMPS

Division

+165Vs

+ 75Va

OCP Current

5 ~ 7A

3 ~ 4A

OVP Voltage

190 ~ 220V

85 ~ 100V

UVP Voltage

135 ~ 145V

50 ~ 65V

Short Circuit

OK

OK

Page 25

Circuit Operation Description

Samsung Electronics 6-3

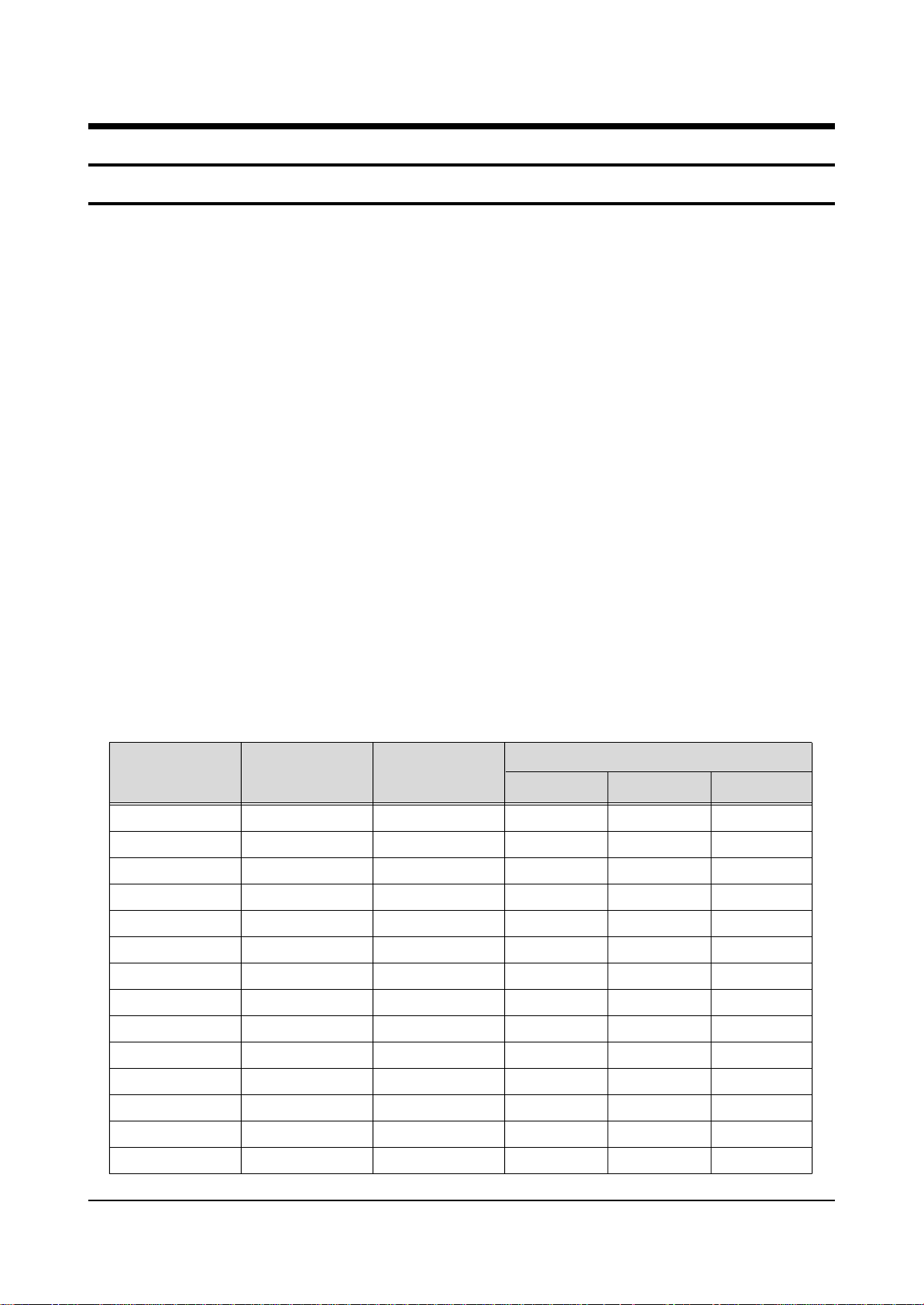

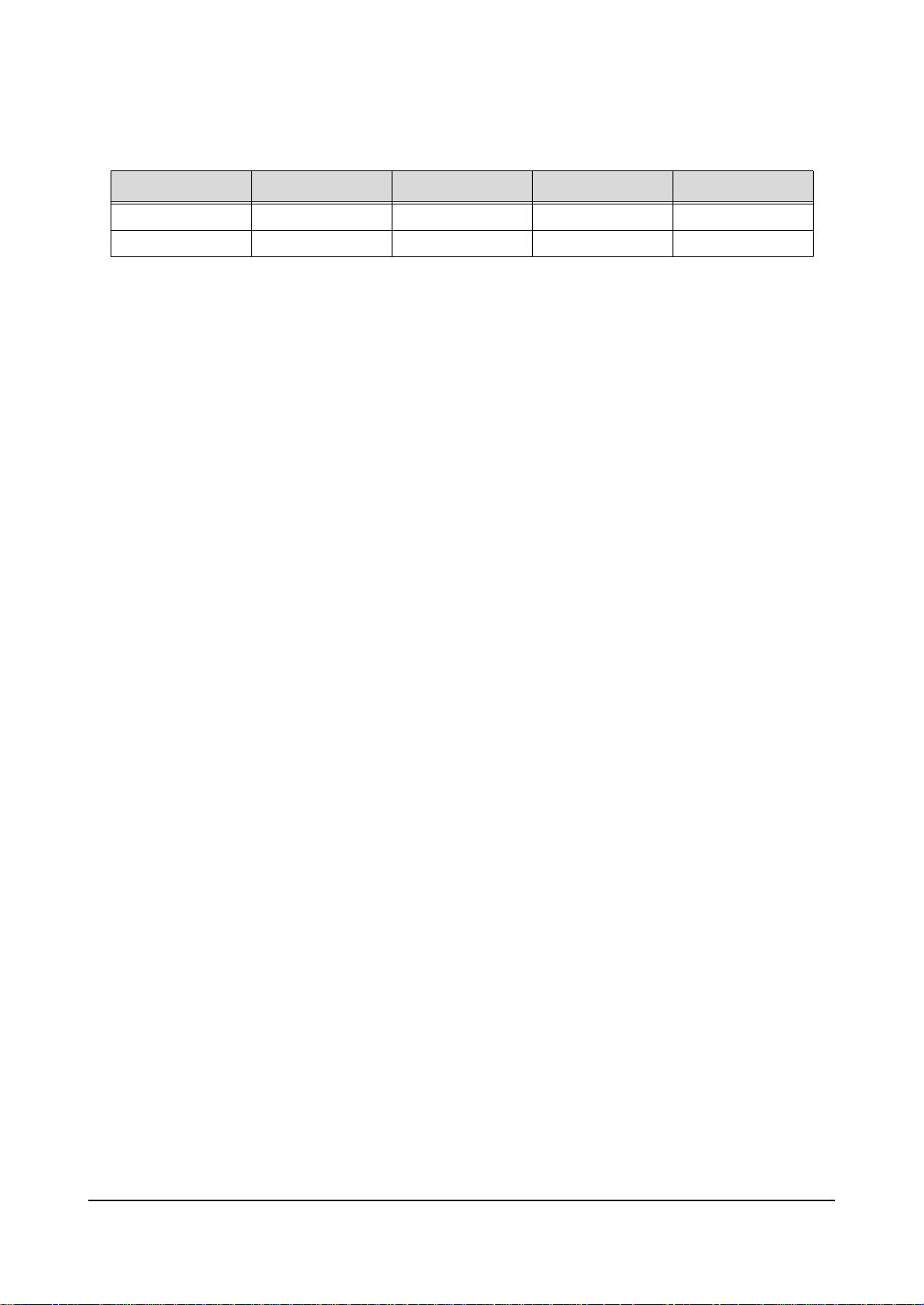

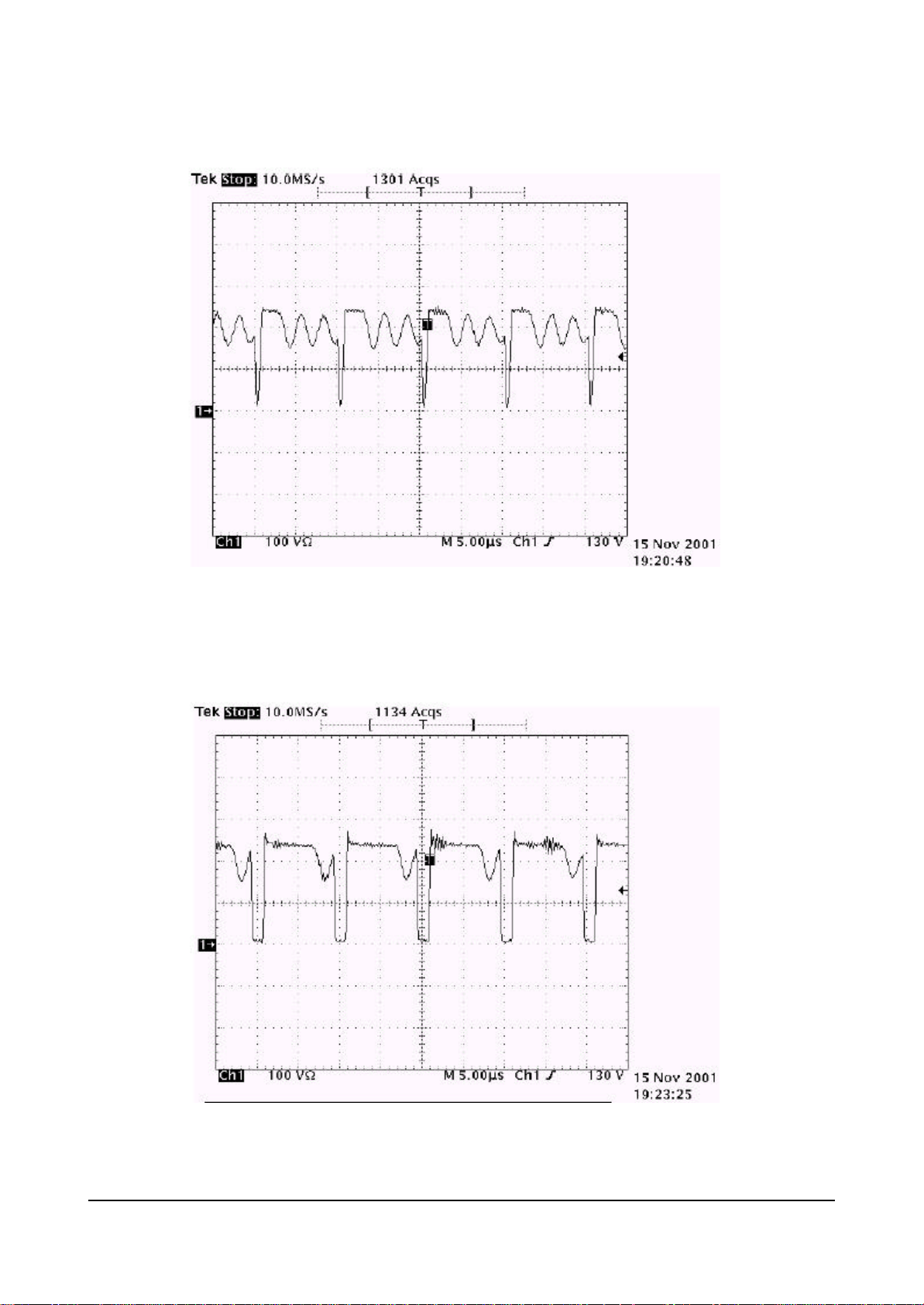

Vs Switching Pulse(Pulse for power board operation only)

Va Switching Pulse(Pulse for Set ON)

Page 26

Circuit Operation Description

6-4 Samsung Electronics

3) Va Block Va Block consists of address voltage suppliers (75Va, 220Vset, and 75Vscan), VCCs

that supply a power to logic circuit, and 12V fan; the power of cooling Fan of 18Vg. PDP Set

that provides Gate voltages of drive circuit. It utilizes a Forward circuit mode as TOpology.

75Vscan uses 75Va power to construct not only stable but, if needed, also variable DC/DC

Converter while 220Vset, also variable if wanted, is applied by adding 165Vs power to the power

generated from Buck Converter with 75Va power. 5Vd and 12Vsp power can be generated by

Buck Converter with the power gained through Coupling in Transformer, and 18Vg by Linear

Regulator. The switching frequency is 70kHz.

Va Switching Pulse(Pulse for Set ON)

4) Block VI Block consists of voltage suppliers for image circuits (5Va, 9Vcc, 12Vcc, and 5Vd1),

and a Flyback circuit mode is applied as Topology. Feedback for voltage stability is designed for

5Vd1, 5Va, 9Vcc, 12Vcc, and 5Vd1 powers anr generated by using each Linear Regulator for the

power gained through Coupling in Transformer. The switching frequency is 100kHz.

Page 27

Circuit Operation Description

Samsung Electronics 6-5

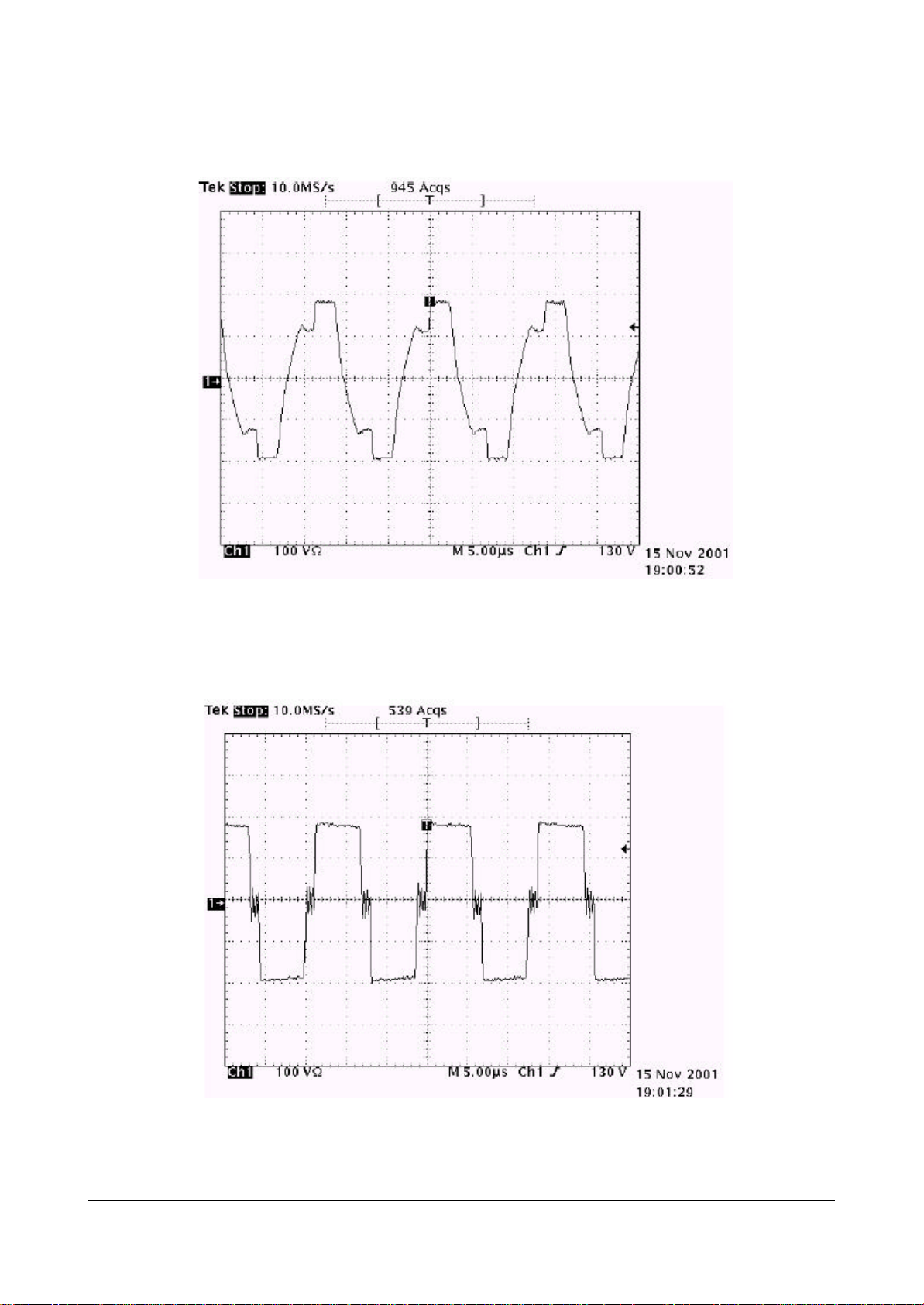

VI Switching Pulse(Pulse for power board operation only)

VI Switching Pulse(Pulse for Set ON)

Page 28

Circuit Operation Description

6-6 Samsung Electronics

6-1-3 Pin Assignment

Image Board

NO OUT PUT

1

2

3

4

5

6

7

8

9

10

11

12

13

+5V

GND(D)

GND(D)

+5V

RELAY

THDET

FAN

GND

GND

N.C

+12V

+5V

N.C

LOC

VSB

V5(D)

V12

V5(D)

SX(X Driver)

OUT PUT

NO

1 +5V

2

3

4

5

6

7

8

9

10

11

12

13

GND

+18V

GND

70V

GND

230V

N.C

GND

GND

165V

165V

165V

LOC

V5(D)

VG

VSCAN

VS

VS

VS

SY (Y Drive)

NO

OUT PUT

1 +5V(D)

2

3

4

5

6

7

8

9

10

11

12

GND(D)

+18V

GND

200V

GND

70V

GND

GND

165V

165V

165V

LOC

V5(D)

VG

VE

VSCAN

VS

VS

VS

Speaker

NO OUT PUT

1

2

3

4 +12V V12

5 GND

6 VSAMP

7 VSAMP

8

9

+5V

GND

+9V

+6V

+6V

GND

GND

LOC LOC

V9

Buffer(2EA) SL(Logic)

NO OUT PUT

1

2

3

4

NO OUTPUT

1 +12V VFAN

2 GND

+70V

+70V

GND

GND

Fan(3EA)

VA

VA

LOC

NO

1

2

3

4

OUT PUT

+70V

+70V

GND

GND

LOC

Page 29

Circuit Operation Description

Samsung Electronics 6-7

6-1-4 SMPS Block diagram

AC

INPUT

PFC

VS

BLOCK

VA

BLOCK

Reg.

DC/DC

DC/DC

Reg.

BUCK

BUCK

GND

GND

GND

GND

GND

GND

GND

GND

GND

185VE

165VS

220VET

75VSCAN

75VA

18VG

5VD

6VSP

12VFAN

AC

INPUT

VI

BLICK

Reg.

Reg.

Reg.

GND

GND

GND

GND

GND

5VD1

5VA

9VCC

12VCC

5VSB

Page 30

Circuit Operation Description

6-8 Samsung Electronics

6-2 Driver circuit

6-2-1 Driver circuit overview

6-2-1(A) WHAT IS THE DRIVER CIRCUIT

It is a circuit generating an appropriate pulse (High voltage pulse) and then driving the panel to implement

images in the external terminals (X electrode group, Y electrode group and address electrode), and this high

voltage switching pulse is generated by a combination of MOSFETs.

6-2-1(B) PANEL DRIVING PRINCIPLES AND TYPES OF DISCHARGE BY DRIVE PULSE

In PDP, images are implemented by impressing voltage on the X electrode, Y electrode and address

electrode, components of each pixel on the panel, under appropriate conditions. Currently, ADS (Address &

Display Separate: Driving is made by separating address and sustaining sections) is most widely used to

generate the drive pulse. Discharges conducted within PDP pixels using this method can largely be

classified into 3 types, as follows:

Address discharge: This functions to generate wall voltage within pixels to be lighted by addressing

information to them (i.e., impressing data voltage)

Sustaining discharge: This means a display section where only pixels with wall voltage by the

address discharge display self-sustaining discharge by the support of such wall voltage. (Optic outputs realizing images are generated.)

Ramp reset discharge: To have address discharge occur selectively in pixels, all pixels in the panel

must have the same conditions (i.e., the same state of wall and space electric discharges). The ramp

reset discharge section, therefore, is important to secure the drive margin, and methods most widely

used to date include wall voltage controlling by ramp pulse.

Page 31

Circuit Operation Description

Samsung Electronics 6-9

6-2-1(C) Discharge of Drive

Sustaining discharge

1(C). Kinds and detailed descriptions of driving discharge

Sustaining discharge means a self-sustaining discharge generated by the total of the sustaining pulse

voltage (usually, 160~180V) alternately given to X and Y electrodes during the sustaining period and

the wall voltage which varies depending upon pixels' previous discharge status. It is operated by the

memory function (through this, the current status is defined by previous operation conditions) AC

PDP basically possesses. That is, when there is existing wall voltage in pixels (in other words, when

pixels remain ON), the total of wall voltage and a sustaining voltage to be impressed subsequently

impresses a voltage equal to or above the discharge start voltage, thereby generating discharge again,

but when there is no existing wall voltage in pixels (in other words, when pixels remain OFF), the

sustaining voltage only does not reach the discharge start voltage, thus causing no discharge. The

sustaining discharge is a section generating actual optic outputs used in displaying images.

Address discharge

This means a discharge type generated by the difference between positive voltage of the address

electrode (usually, 60~70V) and GND of the Y electrode. The address discharge serves to generate

wall voltage in pixels where images are to be displayed (that is, discharge is to be generated) prior to

the sustaining discharge section. Namely, pixels with wall voltage by the address discharge will generate sustaining discharge by the following sustaining pulses.

Weak erasing discharge

The purpose of resetting discharge is to make even wall voltage in all pixels on the panel.

Wall voltage which may vary depending upon the previous sustaining discharge status must be

made even. That is, wall voltage generated by the sustaining discharge must surely be removed, by

making discharges and then supplying ions or electrons. Wall voltage can be removed by making

discharges and then setting a limitation on time for opposite polarity charging of the wall voltage or

generating weak discharge (Low voltage erasing) to supply an appropriate quantity of ions or

electrons and keep polarities from being charged oppositely. The weak discharge (Low voltage erasing) methods which have been known to date can largely be into two types:

1) the log pulse adopted by most companies including F Company, and

2) the ramp pulse adopted by Matsushita.

In both two methods, impression is made with a slow rising slope of the erasing pulse. Because the

total of the existing wall voltage and a voltage on the rising pulse must be at least the drive start

voltage to generate discharges, external impressed voltage is adjusted based on the difference in wall

voltage between pixels.

And, weak discharge is generated because of a small impressed voltage.

Page 32

Circuit Operation Description

6-10 Samsung Electronics

6-2-2 Driver Circuit Block Diagram

(1) Y

(2) X

Fig. Driver Y-Bd

Fig. Driver Y-Bd

LOGIC SIGNAL INPUT

LOGIC SIGNAL BUFFER

FET GA TE DR IV ER

Reco very

Switching

Main

Switching

Reco very circuit

(Recovery Cap)

POWER SUPPLY INPUT

5V

17V

170V

Vs et

Switching

220V

75V

Vs ca n

Switching

LOGIC SIGNAL INPUT

LOGIC SIGNAL BUFFER

FET GATE DRIVER

Reco very

Switching

Reco very circuit

(Recovery Cap)

POWER SUPPLY INPUT

5V

17V

Main

Switching

200V

170V

Ve

Switching

Page 33

(3) Key Requirements of the Driver Circuit Operations

1) Power Supply

- Power is supplied from the power board. The minimum value may differ from the following.

2) Logic Signals

- Logic signals are supplied from the logic board.

- Gate signals of each FET

(4) Diagram and Functional Description of the Driver Circuit

- Functional Description of Each Board

Circuit Operation Description

Samsung Electronics 6-11

X- Bu ffe r

(Upper Part)

X Driver Board

-Sustain waveforms

mp waveforms

a

(Energy Recove ry)

-Rising R

Y- Sub X - Sub

X- Bu ffe r

(Lower Part)

(6 block)

X electrode port

(Energy Recovery)

X Driver Board

- Sustain waveforms

- RisingRamp waveforms

-Vebias

-Vebias

COB

waveforms

(Energy Recover y)

Y Driver Board

- Sustain waveforms

- Rising Ramp waveforms

- Falling Ramp waveforms

- Vscan waveforms

(Energy Recovery)

Y Driver Board

- Sustain waveforms

- RisingRamp waveforms

- Fa lling Ramp

- Vscan waveforms

(6 block)

Y- Buffer

(Upper Part)

Y- Buffer

(Lower Part)

Page 34

1) X Board I, II

X Board I and II are connected to the X port on the panel to:

- Produce sustain voltage waveforms (including ERC)

- Produce X rising ramp waveforms

- Sustain Ve bias during the Scan.

2) Y Board I, II

Y Board I and II are connected to the Y port on the panel to:

- Produce sustain voltage waveforms (including ERC)

- Produce Y rising ramp waveforms

- Sustain V scan bias.

3) X Buffer Board (Upper and Lower)

The X buffer board applies Sustain waveforms to the X port. It consists of an upper and

a lower board.

4) Y Buffer Board (Upper and Lower)

The Y buffer board applies Scan waveforms to the Y port. It consists of an upper and a

lower board. Each board is installed with 6 Scan driver ICs (STMicroelectronics

STV7616: 64 or outputs).

5) X Sub Board

The X sub board distributes and applies logic data to the X board I and II.

6) Y Sub Board

The Y sub board distributes and applies logic data to the Y board I and II.

7) COB

The COB applies Va waveforms to the Address electrodes during the Address stage to

produce Address discharges by using the difference between the injection waveforms

and the voltage applied to the Y electrode. ACOB is installed with 4 data drive ICs

(STMicroelectronics STV7610A: 96 outputs). A total 22 COBs are required.

Circuit Operation Description

6-12 Samsung Electronics

Page 35

Circuit Operation Description

Samsung Electronics 6-13

6-2-3 Driving Waveform Specs

6-2-3(A) Driving Waveform Diagram

Vs

Vscan

Xsustain

pulse

Vs

Ysustain

pulse

Y s can

pulse

Ve

Y falling

Ramp

Va

Addres s

pulse

Vs 160~170V Ve 190V~200V

Vs e t 210~225V Va 70~75V

Vs c a n 70~75V

Vs e t

Ve

Y r is ing

Ramp

X r is ing

Ramp

Y

X

RESET SCAN SUSTAI N

X Co mmon & Sus t a i n El e ct r ode

Ad d r e s s

A1 , 2 . . . . . Address( =Dat a) Elect rode

Y1 , 2 . . . . Scan &Sustain Electrode

Page 36

Circuit Operation Description

6-14 Samsung Electronics

6-2-3(B) Functional Description of Each Waveform

(1) X Rising Ramp Waveform

The last Y electrode Sustain waveform is applied from the sub field before the XZ Rising Ramp

waveforms begin to be applied. The last waveform triggers the Sustain Discharge.

Then, a positive wall charge occurs on the X electrodes and a negative wall chanrge on the Y

electrodes.

The X rising ramp eliminates the wall charge produced by the aforementioned Sustain Discharge

waveform by triggering a low discharge.

(2) Y Rising Ramp Waveform

During the Y Rising Ramp stage, an external voltage of 390-400V is applied to the Y electrodes to

adjust each Gap Voltage to the same initial voltage level before starting a low discharge. As the low

discharge is sustained, a negative wall charge continues on the Y electrodes and a positive wall

charge on the X and Address electrodes across the panel.

(3) Y Falling Ramp Waveform

During the Y Falling Ramp stage, most of the negative wall charges on the Y electrodes,

with approximately 200V X bias, are used to eliminate the positive wall charges on the

X electrodes. Most of the positive wall charges on the (OV) rising ramp section of the

Address electrodes are sustained to form wall charges in preparation for an address discharge.

(4) Y Scan Wavdform

The Y Scan waveform is also calle an injection waveform. It selects Y electrodes one

line at a time. Vscan is referred to as Scan bias voltage. About 70 Volts (V scan)are

applied to the applicable electrode limes with Vscan, and 0 Vots (GND) to the rest.

When Ramp waveforms are applied, however, a negative wall charge occurs on the Y

electrodes, and a positive wall charge on the Address electrodes. Because the voltage

level exceeds the initial discharge level in those cells affected by address waveforms

(70~75V), an address discharge occurs. The PDP Address takes a long time because it

applies injection and data waveforms line by line.

Page 37

Circuit Operation Description

Samsung Electronics 6-15

6-2-3(C) Principles of Fets Operation and High Voltage Switching

1) With signal impressed on the gate(Positive voltage) ,

FET gets short-circuited (a conducting wire of zero

(0) resistance); and

2) With no signal impressed on the gate (GND), FET

gets open-circuited (a non-conducting wire of ∞

resistance).

1) With no signal impressed on G1, FET1 gets open-circuited, and with signal impressed on G2, FET2

gets short-circuited, thereby causing GND to be outputted to output terminals.

2) With signal impressed on G1, FET1 gets short-circuited, and with no signal impressed on G2, FET2

gets open-circuited, thereby causing 180V to be outputted to output terminals.

Page 38

Circuit Operation Description

6-16 Samsung Electronics

6-2-3(D) Driver Circuit Composition Diagram

C_Xerc

VsVe

D_Xs

C_Xsink

Dscan

Xr

Xs

D_Xsink

Xrr

D_Ysink

Ramp

D_Xr

D_YVsC

LX

Cp

3

1

2

Xg

D_Xf

Xf

D_YGC

3 2

1

0 0

0

VscanVset

Vs

Ysc

Rset

Yrr

Ys

Ysp

C_Ysink

Ramp

Dset

D_YVsC

Yr

Yp

Cset

LY

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

floating 5V

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

Page 39

Circuit Operation Description

Samsung Electronics 6-17

6-2-3(E) Driver Board Connector Layout

(1) X I

CN4004

- Power

CN4406

- Panel

CN4005

- Signal

CN4009

CN4008

CN4007

CN4006

CN4402

CN4401

CN4404

CN4403

CN44 05

CN4407

- Panel

CN4408

- Panel

Page 40

Circuit Operation Description

6-18 Samsung Electronics

(2) X II

CN4004

- Power

CN4009

CN4008

CN4505

CN45 01

CN45 03

CN4506

- Panel

CN4005

- Signal

CN4007

CN4006

CN45 02

CN45 04

CN4508

- Panel

CN4507

- Panel

Page 41

Circuit Operation Description

Samsung Electronics 6-19

(3) Y I

CN5401

- Panel

CN5402

- Panel

CN5404

CN5406

CN5405

CN5407

CN5409

CN5008

- Power

CN5007

CN5001

CN5006

CN5005

CN5003

CN5403

- Panel

CN5408

CN5004

CN5002

- Signal

Page 42

Circuit Operation Description

6-20 Samsung Electronics

(4) Y II

CN5503

- Panel

CN5502

- Panel

CN5508

CN5509

CN5507

CN5505

CN5506

CN5007

CN5001

CN5006

CN5005

CN5008

-

Power

CN5501

- Panel

CN5003

CN5504

CN5004

CN5002

- Signal

Page 43

Circuit Operation Description

Samsung Electronics 6-21

Single scan mode PDP action : Rest section, X : 0 -> Ve, Y : 0

C_Xerc

VsVe

VscanVset

D_Xs

C_Xsink

Dscan

D_Xsink

D_Ysink

Ysc

Xr

Xs

Xrr

Ramp

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 44

Circuit Operation Description

6-22 Samsung Electronics

Single scan mode PDP action : Rest section, X : 0 , Y : Vs -> Vs + Vset

C_Xerc

VsVe

VscanVset

C_Xsink

Dscan

D_Xs

D_Xsink

Ysc

Xr

Xs

Xrr

Ramp

D_Ysink

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 45

Circuit Operation Description

Samsung Electronics 6-23

Single scan mode PDP action : Rest section, X : Vs, Y : Vs

C_Xerc

VsVe

VscanVset

D_Xs

C_Xsink

Dscan

D_Xsink

D_Ysink

Ysc

Xr

Xs

Xrr

Ramp

Ysp

C_Ysink

D_Xr

D_YVsC

LX

Cp

3

1

D_Xf

D_YGC

Xg

2

1

floating 5V

Xf

0 0

0

155V

Vs : 155V

3 2

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

Va :78V

Vscan : 65V 65V

Ve :184V

Y fall

155V

V set + V s:355V

Y rise

155V

Y

184V

Vs : 155V

X rise

X

Ad dress

RESET SCAN SUSTA IN

Page 46

Circuit Operation Description

6-24 Samsung Electronics

Single scan mode PDP action : Rest section, X : Ve, Y : Vs

C_Xerc

VsVe

VscanVset

C_Xsink

Dscan

D_Xs

D_Xsink

Ysc

Xr

Xs

Xrr

Ramp

D_Ysink

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 47

Circuit Operation Description

Samsung Electronics 6-25

Single scan mode PDP action : Rest section, X : Ve, Y : Vs -> 0

C_Xerc

VsVe

VscanVset

D_Xs

C_Xsink

Dscan

D_Xsink

D_Ysink

Ysc

Xr

Xs

Xrr

Ramp

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 48

Circuit Operation Description

6-26 Samsung Electronics

Single scan mode PDP action : Rest section, X : Ve, Y : Vscan, idle scan-line

C_Xerc

VsVe

VscanVset

C_Xsink

Dscan

D_Xs

D_Xsink

Ysc

Xr

Xs

Xrr

Ramp

D_Ysink

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Ramp

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 49

Circuit Operation Description

Samsung Electronics 6-27

Single scan mode PDP action : Rest section, X : Ve, Y : Vscan, address scan-line

C_Xerc

VsVe

VscanVset

C_Xsink

Dscan

D_Xs

D_Xsink

Ysc

Xr

Xs

Xrr

Ramp

D_Ysink

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 50

Circuit Operation Description

6-28 Samsung Electronics

Single scan mode PDP action : Rest section, X : Ve, Y : Vscan, idle scan-line

C_Xerc

VsVe

VscanVset

C_Xsink

Dscan

D_Xs

D_Xsink

Ysc

Xr

Xs

Xrr

Ramp

D_Ysink

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Ramp

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 51

Circuit Operation Description

Samsung Electronics 6-29

Single scan mode PDP action : Rest section, X : 0, Y : 0, GND mode

C_Xerc

D_XrXfD_Xf

Xr

VsVe

VscanVset

C_Xsink

Dscan

D_Xs

D_Xsink

Ysc

Rset

Xs

Xrr

Ramp

D_Ysink

C_Ysink

Yrr

Ramp

Dset

Ysp

D_YVsC

1

Yp

Cset

Cp

LX

3

2

+5V

Yfr

D_YGC

Xg

1

D_fVdd

3 2

floating 5V

C_fVdd

0 0

0

155V

Vs :155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

Vs

Ys

Yr

LY

D_YVsC

D_Yr

Ramp

Yg

D_Yf

Yf

0 0 00

V set + V s:355V

Y rise

155V

155V

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

C_Yerc D_YGC

Page 52

Circuit Operation Description

6-30 Samsung Electronics

Single scan mode PDP action : Rest section, X : 0, Y : 0 -> Vs, charging mode

C_Xerc

VsVe

VscanVset

C_Xsink

Dscan

D_Xs

D_Xsink

Ysc

Xr

Xs

Xrr

Ramp

D_Ysink

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Ramp

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 53

Circuit Operation Description

Samsung Electronics 6-31

Single scan mode PDP action : Rest section, X : 0, Y : Vs, Gas discharging mode

C_Xerc

VsVe

VscanVset

D_Xs

C_Xsink

Dscan

D_Xsink

D_Ysink

Ysc

Xr

Xs

Xrr

Ramp

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 54

Circuit Operation Description

6-32 Samsung Electronics

Single scan mode PDP action : Rest section, X : 0, Y : Vs -> 0, discharge mode

C_Xerc

VsVe

VscanVset

D_Xs

C_Xsink

Dscan

D_Xsink

D_Ysink

Ysc

Xr

Xs

Xrr

Ramp

C_Ysink

Ysp

D_Xr

D_YVsC

LX

Cp

1

D_Xf

Xf

D_YGC

0 0

0

Xg

155V

Vs :155V

2

3

3 2

1

floating 5V

Vs

Rset

Ys

Yrr

Ramp

Dset

Yr

Yp

Cset

LY

D_YVsC

D_Yr

+5V

Yfr

Yg

D_Yf

C_Yerc D_YGC

D_fVdd

Ramp

Yf

C_fVdd

0 0 00

V set + V s:355V

Y rise

155V

155V

Va :78V

Vscan :65V 65V

Ve :184V

Yfall

RESET SCAN SUSTA IN

Vs :155V

184V

Y

X rise

X

Address

Page 55

Circuit Operation Description

Samsung Electronics 6-33

6-3 Logic part

6-3-1 Description of Logic Board

The logic board consists of a logic main board and a buffer board. The logic main board is made up

of a data signal processor that processes video signals, and a XY signal generator that runs the XY

drivers. The buffer boar stores address driver output sigals and sends them to the address driver IC

(COF module).

6-3-2 Name and Description of Major COmponents of the Logic Board

Logic Board Function Remarks

(Lo gic M a in)

(Bu ffe r Bo a rd )

E, F, G Buffer oard

H, I, J Buffer board

- Processes video signals. (W/L, Error diffusion, APC)

- Outputs address driver control signals and data

signals to the buffer board.

- Outputs XY driver board control signals

Sends data signals and control signalss to the upper

COF.

Sends data signals and control signals to the lower

COP.

*

!

@

#

(

$

)

^&

%

Page 56

Circuit Operation Description

6-34 Samsung Electronics

Description

NO

An input connector that receives LVDS encoded RGB, H, V, DATAEN, and

DCLK signals from the video board.

Indicates if the logic board properly receives Sync and

clock signal.

A connector to the Key Scan board that check and adjust

24C16 data.

An EEPROM for saving the gamma table, the APC table, the drive signal

timing and other options, etc.

A connector that outputs Y driver board control signals.

A connector that outputs X driver board control signals.

A connector that outputs address data and control signals to the

E,F and G buffer board.

A connector that outputs address data and control signals to the

H,I and J buffer board.

A fuse connected to the power source (5V) of the logic board.

A connector that supplies power (5V) to the logic board.

LVDS Connector

Operation LED

Key Scan Connector

256K

Y Connector

X Connector

Address Buffer

Connector (E,F,G)

Address Buffer

Connector (H,I,J)

Power Fuse

Power Connector

NAME

6-3-3 Waveform in Normal Operation

If the PDP unit and the logic board are operationg properly, the LED LD2010 in Figure 1 will blink

at about a 1 second interval.

If the unit is out of order, check the status of the Operation LED through eye-inspection first.

If the behavior of the Operation LED is different from that of normal operation, you have to replace

the board. To trouble-shoot the board, complete the logic board test procedures attached in the

Appendix.

Page 57

Circuit Operation Description

Samsung Electronics 6-35

6-3-3(A) Layout and Apperance of the Board

(1) Input

Fig. 1 Layout of the Logic Mainboard

LD2010

LD2002

LD2001

KEYSCAN

LG2000

F3

F2

256K

CN2001

256K

F1

TP1

U2002

GND

U2003

LG2003LG2002LG2001

U2005

U2006

U2007

U2008

CN2002

U2009

U2004

U2 010

LY2000

CN2003

LE2001 LE2002 LE2003

Page 58

(2) Appearance of and Markings on the Connector

Basically, it is depicted exactly the same as the real one on the PCB.

6-3-3(B) DIP Switch setting that selects the internal or external clock (CN2001)

(1) External Mode Selection

Circuit Operation Description

6-36 Samsung Electronics

☞ When External Mode is selected;

! Enter PAGE 00.

@ Set Register 2E’s address to 01.

# Adjust the Dip Switch as shown above.

(UP : PIN_NUMBER 6,5,3,2,1 / DOWN : PIN_NUMBER 4)

(2) Internal Mode NTSC Pattern Selection

☞ When Internal Mode Pattern is selected;

! Enter PAGE 00.

@ Set Register 2E’s address to 01.

# Adjust the Dip Switch as shown above.

(UP : PIN_NUMBER 6,5,4,3,2 / DOWN : PIN_NUMBER 1)

MODE PAGE

NTSC 00 2E 01

REGISTER

ADDRESS

EXTERNAL

MODE VALUE

MODE PAGE

REGISTER

ADDRESS

INTERNAL

MODE VALUE

DIP SWITCH STATE

EXTERNAL MODE

6

5

4

3

DIP SWITCH STATE

INTERNAL MODE

2

1

NTSC 00 2E 00

6

5

4

3

2

1

Page 59

Circuit Operation Description

Samsung Electronics 6-37

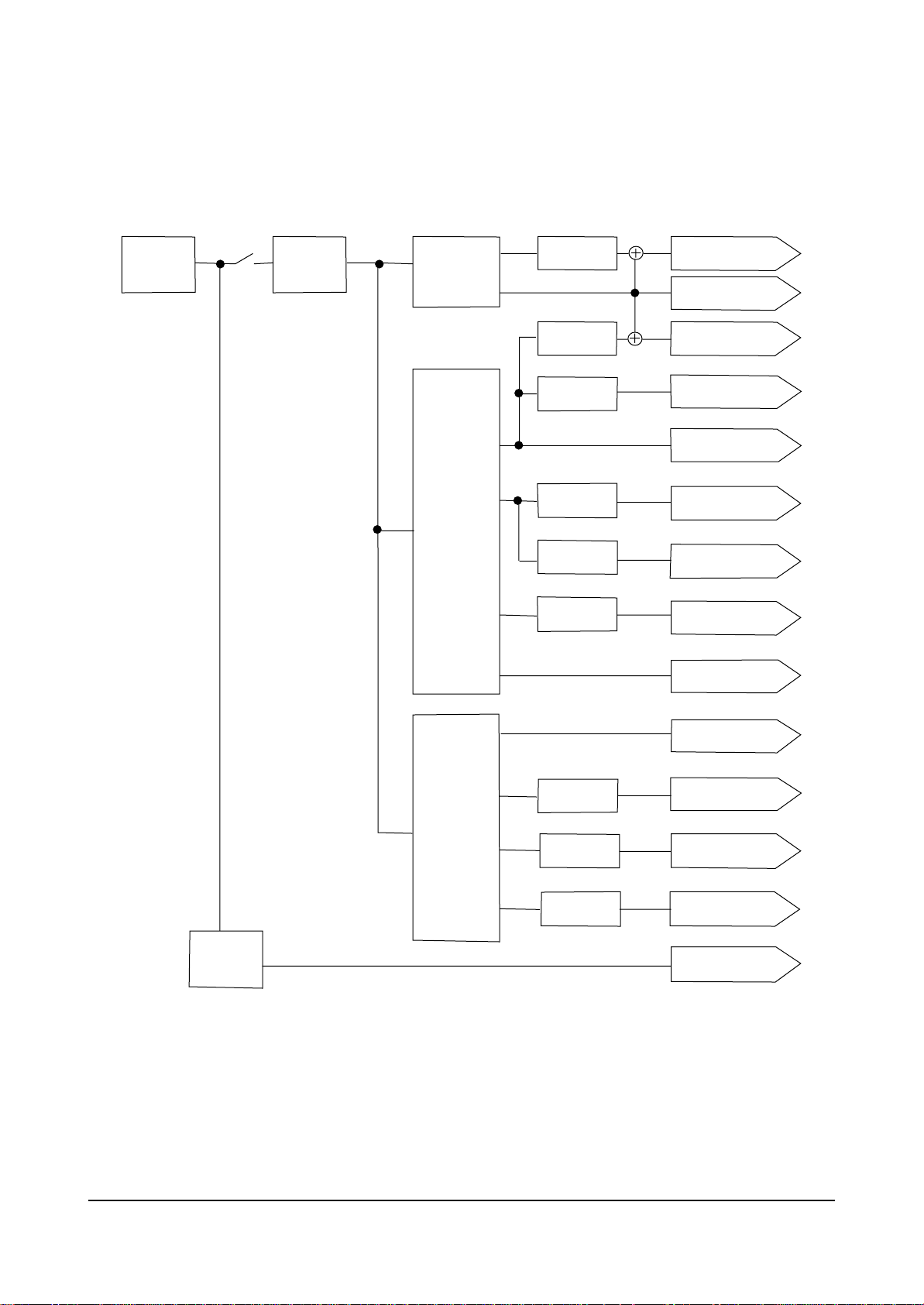

6-4 Scaler Board Block Diagram & Description

6-4-1 General Signal Process B/D

Ke y p a d

Exte r nal

IR

Module

Sub PCB for

Exte rna l Cont rol

MCLK DCLK

LVDS OUT

(63LVDM83A)

RGB,H/V

CLK, DE

2000. 05. 06

designed by K.H.I

PDP

Logic B’d

RGB,H/V

CLK, DE

Flash Mem.

(M29W800T)

(ICS501,502 )

C

2

Progr ammable P LL

OSD Mixe r,

(Imag e S c a ling ,

Image Processor

PW364

with CPU

Frame Rate Conversion)

M

CI

EEPRO

2

(24C16)

I

YUV,

2H/V,

AVO

RGB,

GCLK

Puls e Gen.

YPbP r RGB

(M4A3 32/32)

SCP

(CXA2101)

YPbPr

RGB,H/V

GFBK

DTV(480p,720p,1080i)DVD(480p)

RGB,H/V

Analog Switch

C

2

I

(BA7657)

with PLL

A/D conver ter

RGB

Analog Switch

RGB,H/V

RGB,H/V

C

2

I

(SDA9400)

Interlace to

Progre ss ive

YUV,H/ V

C

Decoder

2

(VPC3230)

Main Vid e o

I

D/A

(SDA9280)

C

2

I

Sand Castle

13.5MHz

27MHz

YPbPr

H/V (480P)

H/V

C

2

I

HD Interface

DVD

3D

COMB

YPbPr(480i)

C

2

I

(AD9884)

(BA7657)

SRAM

(KM616V1000)

RTC

(PCF8563)

CS

(LM1881)

Sync Sepe ra te

H/V

G(SOG)

DDC IC

V

DDC

(24LC21)

SDA/SCL

RXD/T X

D

(MAX232A)

Serial Interface

Aud io Am p.

( TA1101 )

Sub PCB for

Aud io

C

2

I

Aud io

Processor

( TDA7429 )

Video

(CVBS)

(Y/C)

S- Video

Input

(Y,Pb,Pr)

Comp onen t

DTV YPbPr

(480p,720p,1080i)

DVD YPbPr

(480i,480p)

PC RGB HV

(15 pin)

PC Input

VGA to S XGA

Vf: 56 to 75Hz

Hf: 3 1 to 80 kHz

RS232C

OUT

(L/R)

Audio In

RS232C IN

Page 60

Circuit Operation Description

6-38 Samsung Electronics

6-4-2 Description in Signal Process Block

3D COMB FILTER : This 3D Comb Filter is used to improve noise and picture quality by three-dimensionally adjusting the

signal from the Input Video jack. The input signal is received from CVBS and the picture is digitally

improved via A/D Conversion and FIELD MEMORY. And then the signal is output as the ANALOG YC signal.

VPC3230 : This functions as a video decoder, which can receive all of the YC, YUV, CVBS inputs.

In addition, this converts Y/C into YUV after receiving 3D Comb Output Y/C, S-Vido Y/C, and DVD YUV.

VIDEO DOUBLER : Usually, the current video image adopts the INTERLACE Scanning system and it has poor video because of

Flicking on the screen. Using the SDA9400 , INTERLACE is converted into PROGRESSIVE in order to improve

the quality of video.

VIDEO PROCESSOR : Since the HD modes like 1920*1080I have higher video bandwidth than the existing video signals, the

ordinary decoder like VPC3230 can't handle those modes. PC has higher bandwidth of video signal than TV

and the RGB video format.

Therefore, if the HD signal can be converted into the RGB signals, the TV video signal can have the same

processing as the PC VIDEO signal. CXA2101 developed by SONY is used to convert YPbPr into RGB.

CXA2101 converts both DTV signals and all the SD signals processed in the sequence of SDA9400 then

SDA9280 into RGB.

This processor performs some user control functions, such as tint, color, and sharpness.

Also, it controls high light gains low light offsets when doing white balance adjustments.

ANALOG SWITCH : The video decoder like VPC3230 has a built-in video switch that assigns one signal out of various

received inputs, though most of ICs for PC are designed so that they support only one source because of

less necessity of simultaneously processing the multi inputs. To process the input source of MULTI

(PC&HD), therefore, a function of selecting an input should be externally added; as is performed by ROHM's

BA7657F. PW364 transmits a signal determining which input is selected.

ADC : A device that converts the input RGB signals into the 8bit DIGITAL RGB signals.

In case of white balance adjustments, this device sets the color temperature by controlling R/B gains and

R/B offsets.

PW364 : PW364 is a multi-functional scaler which one chip has video signal scaling, 8086 CPU, 4M BYTE VIDEO

MEMORY functions. The PC and Video input signals are received from GRAPHIC PORT and VIDEO PORT,

respectively.Its main functions include UP/DOWN SCALING, PIP, ZOOM, GAMMA CORRECTION,

Compensation of GEOMETRIC DISTORTION, powerful GRAPHIC OSD.

FIRMWARE : Mounted is a software that is used for system control by operating 8086 built in PW364. A 4MBIT FLASH

ROM is mainly used, but one up to 8MBIT can be used according to PROGRAM and capacity of OSD DATA.

The system is easy to maintain because programming can be re-done at any yime using the FLASH ROM.

Page 61

Circuit Operation Description

Samsung Electronics 6-39

6-5 IC Line-Up

6-5-1 IC LINE UP

BA7657

CRYSTAL

ANALOG

DIGITAL

CLOCK

AD9884

CXA2101

TOLOGIC

LVDS OUT

90CF385

67.4MHZ

VIDEO

CLK

16 .25

7

ICS501

130MHZ67. 4MHZ

PW364

27MHZ

20 .25

ICS502

SDA9400

27MHZ

FROMSMPS

29LV16

616V100

MAX232

13.5

MHZ

CONTROL

PWR

RMC/LED

BA7657

RGB1 RGB2

D_SUB

DTV

M4A3

DVD(480I)

K4E

151612D

Pr/RVH

B

SDA9280

20

20.2

5

UPD

64082

COM POSITE

Y/GPb/

VPC3230

Y/C

VIDEO

TO SOUND

Y/C

S_VIDE

O

Page 62

Circuit Operation Description

6-40 Samsung Electronics

6-5-2 PIN Description

Pi n No. Pin Name Pin Na me Pin Name Pin Name Pin Na me Pin Name

1 DGND

2 GND SCL KEY1

3 TxOUT0 - / RxIN0

4+/

5 REL_SW R 1 LED G

6 TEMP DET T2

7FANDETR2

8 GND

9AMPMUTE1

10 12V GND

11 12V

12 A6V

13

14

15 T xCLKOUT-/ RxCLKIN16

TxCLKOUT-/ RxCLKIN

17

18

19

20

21 NC

22 NC

23 NC

24 NC

25 NC

26 NC

27 NC

28 NC

29 NC

30 NC

31 NC

DGND

TxOUT0 RxIN0

DGND

DGND

TxOUT1 - / RxIN1

TxOUT1 RxIN1

TxOUT1 - / RxIN1

TxOUT1 RxIN1

TxOUT3 - / RxIN3

TxOUT3 RxIN3

+/

DGND

DGND

+/

DGND

DGND

DGND

DGND

+/

+

ST5V SDA ST5V

GND

D5V T1 LED R

GND

GND

GND

GND

KEY1

KEY1

KEY4

GND

KEY4

GND GND

KEY4

RMC S IG

Page 63

Circuit Operation Description

Samsung Electronics 6-41

6-6 Main I/O signal pules and voltages

6-6-1 Signal Pulses of Image Board(Input Signal Conditions : 7 Color bar)

* 9C55 VIDEO INPUT *3D COMB P88 VIDEO INPUT

* 3D COMB P84 Y OUTPUT *3D COMB P83 C OUTPUT

* 3U1(VPC3230) PIN75 Y_IN * 3U1(VPC3230) PIN72 C_IN

Page 64

Circuit Operation Description

6-42 Samsung Electronics

* 3U1(VPC3230) PIN40 Yo_OUT * 3U1U(VPC3230) PIN56 HS_OUT

* 3U1(VPC3230) PIN57 VS_OUT * 3U1(VPC3230) PIN27 LLC2_OUT

* 3U1(VPC3230) PIN28 LLC1_OUT

Page 65

Circuit Operation Description

Samsung Electronics 6-43

* 3U2(SDA9280) PIN47 V_Y_OUT * 3U2(SDA9280) PIN51 V_Pr_OUT

* 3U2(SDA9280) PIN54 V_Pb_OUT * 2U2(CXA2101) PIN39 B_OUT

* 2U2(CXA2101) PIN37 G_OUT * 2U2(CXA2101) PIN35 R_OUT

Page 66

Circuit Operation Description

6-44 Samsung Electronics

* 1U1(AD9884) PIN:115 PCLK_OUT * U29(AD9884) PIN7 R_IN

* U29(AD9884) PIN95 ROUT_ODD * U29(AD9884) PIN105 ROUT_EVEN

Page 67

Circuit Operation Description

Samsung Electronics 6-45

* 2U2(CXA2101AQ) PIN5 DTV.Y_IN * 2U2(CXA2101AQ) PIN4DTV.Pb_IN

* 2U2(CXA2101AQ) PIN3 DTV.Pr_IN * 2U2(CXA2101AQ) PIN35 DTV.R_OUT

* 2U2(CXA2101AQ) PIN37 DTV.G_OUT * 2U2(CXA2101AQ) PIN39 DTV.B_OUT a

Page 68

6-46 Samsung Electronics

MEMO

Page 69

Troubleshooting

Samsung Electronics 7-1

7. Troubleshooting

7-1 No Raster(Board Change in PDP Monitor)

ST - BY Mode(LED:RED)

norma l

Power On 8J1 Re place s caler B’d

(LED:GREEN) Output

norma l

SMPS AC

Abnormal

ST 5V

Abnormal

Abnormal Abnor mal

Output Voltage Input

norma l

norma l

Logic Connect Powe r Re place SMPS

LED Lig h t- o n

(Po w e r,Sink)

norma l

Abnormal

Re place Logic B’d

X- B’ d Connect Power

norma l

or Go to P age 7- 2

Cha n g e Fuse

X- B’ d

Output

norma l

Abnormal

Repla ce X- B’d

Y- B’ d Connect Power

Y- B’ d

Abnormal

Repla ce X- B’d

Output

norma l

Repla ce Panel

Page 70

7-2 Samsung Electronics

Alignment and Adjustments

7-2 No Raster in Scaler Board

Chec k Out p ut Da t a of 5J1

Abnormal

Nor mal

Chec k Log ic B’d

Check Input Signal of 5U1 LVDS IC

Pin 2 7(LHS),28(LVS),32(CLK)

Abnormal

Check Output Signal of 1U1 AD9884

Pin 115(CLK), 85 (G7), 1 05(R7),65(B7)

Abnormal

Check Input Signal of 1U1 AD9 884

R,G,B IN AND H,V IN