Samsung DVD-611 Reference Information

Samsung Electronics 2-1

2. Reference Information

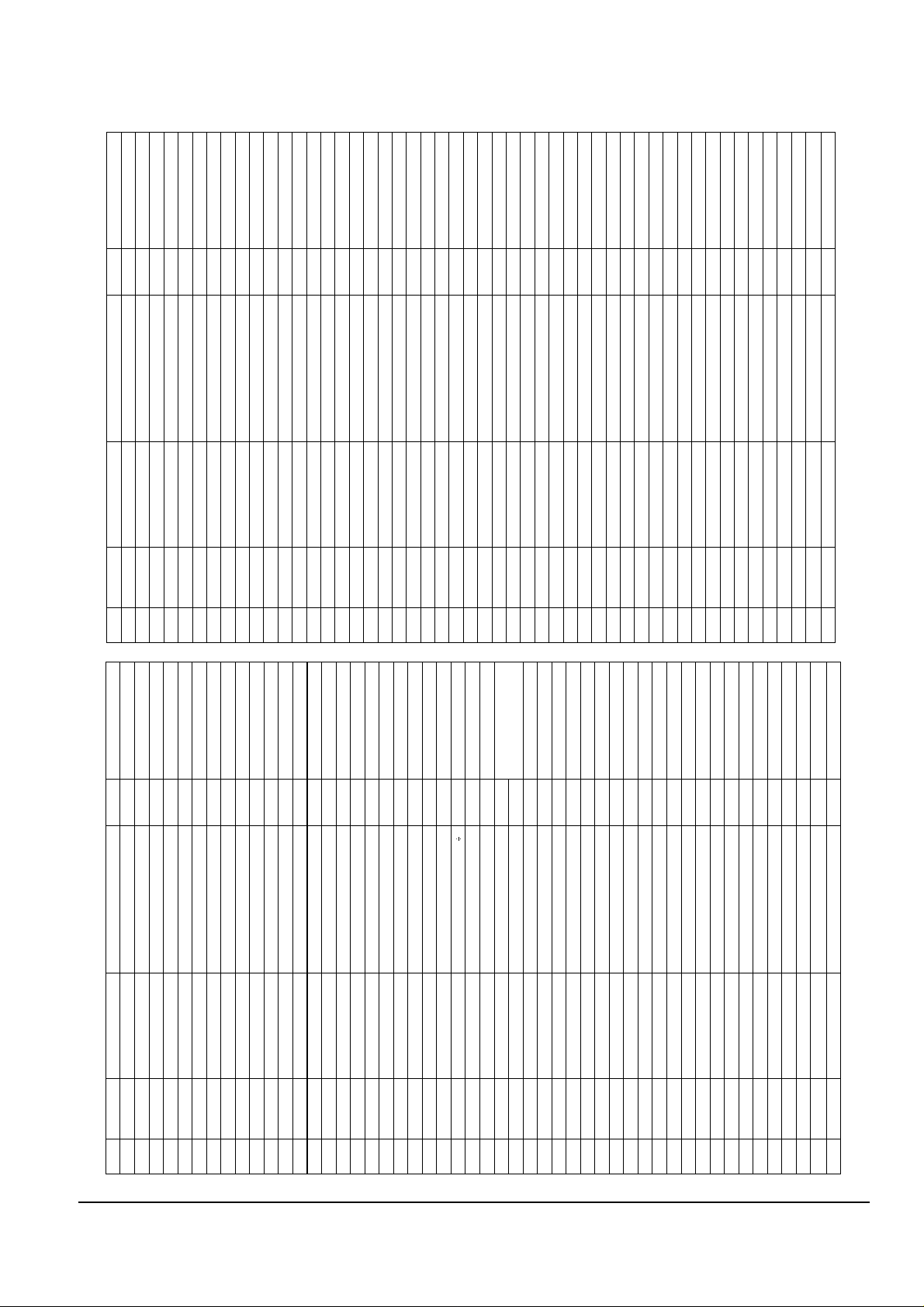

2-1 IC Descriptions

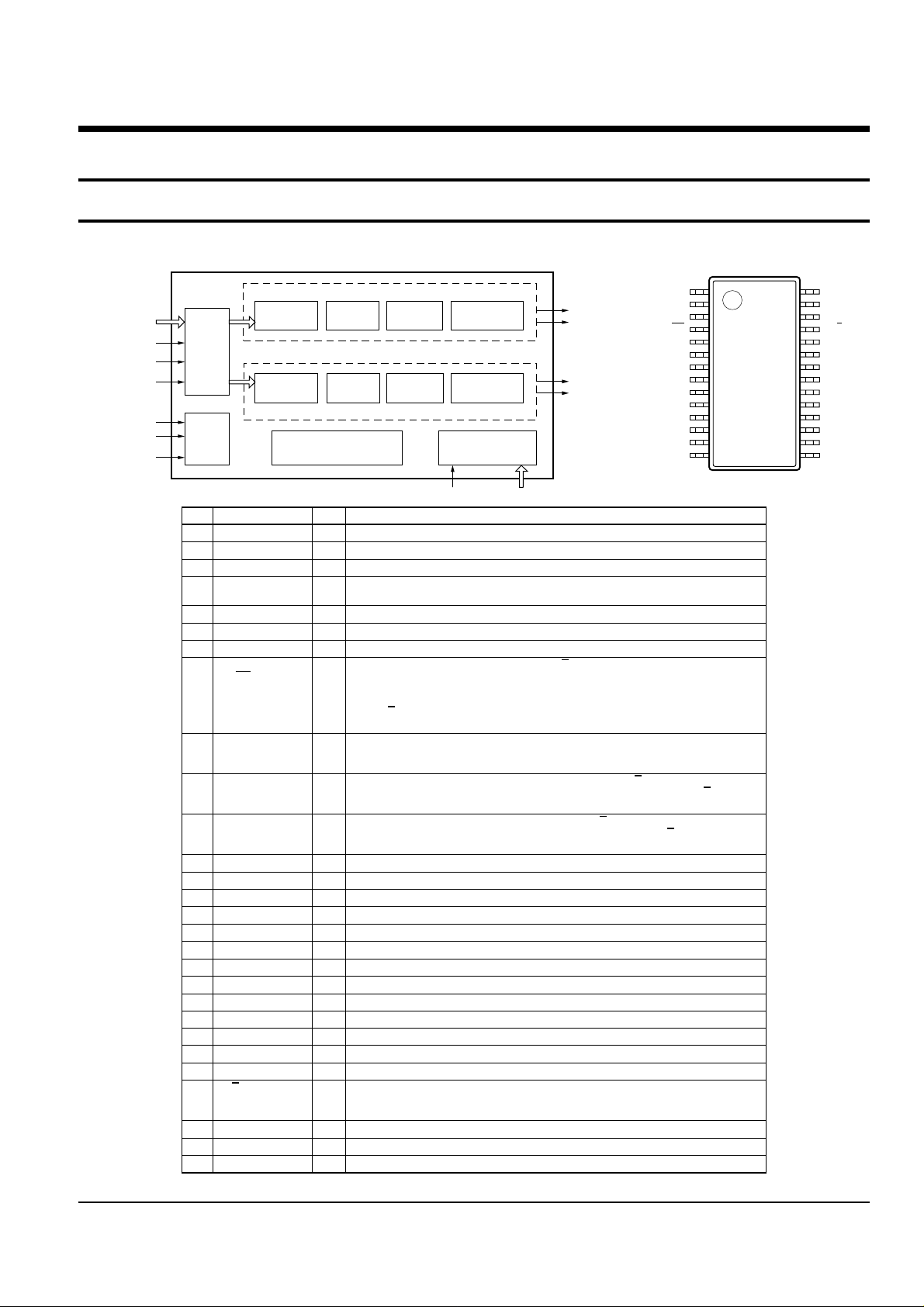

2-1-1 AIC1 (AK4393 ; Digital-to-Analog Converter)

Serial

Input

Interface

De-emphasis

Control

De-emphasis

Soft Mute

De-emphasis

Soft Mute

Left Channel

Right Channel

8X

Interpolator

8X

Interpolator

Multi-bit ˘•

Modulator

Multi-bit ˘•

Modulator

Switched

Capacitor Filter

Switched

Capacitor Filter

Control

Register

Double

Speed Select

Soft Mute

Power Down

Serial Data

Bit Clock

Left/Right Clock

Serial

Input Control

Clock Divider

Master Clock Clock Control

Left Output -

Left Output +

Right Output -

Right Output +

DVSS

DVDD

MCLK

PD

BICK

SDATA

LRCK

SMUTE

DFS

DEM0

DEM1

DIF0

1

2

3

4

5

6

7

8

9

10

11

12

DIF1

13

DIF2

CKS2

CKS1

CKS0

P/S

VCOM

AOUTL+

AOUTLAOUTR+

AOUTRAVSS

AVDD

VREFH

VREFL

BVSS

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

No. Pin Name I/O Pin Function and Description

1 DVSS - Digital Ground. Digital ground is 0V.

2 DVDD - Digital Supply. 3.3V or 5.0V nominal.

3 MCLK I Master Clock Input.

4 PD I Power-down and Reset. When low the AK4393 is in Power-down Mode and held in reset.

The AK4393 should always be reset after power-up.

5 BICK I Audio Serial Data Clock Input. A clock input of 64fs or more is recommended.

6

SDATA I

Serial Data Input.

7 LRCK I Left/Right Clock Input. Defines the sampling rate, F

s

.

8 SMUTE

(or CS

)

I Soft Mute Input or Chip Select Input. If the P/S

pin (pin 25) is high, SMUTE controls the

soft mute function as follows:

- When SMUTE goes high, the soft mute cycle is initiated.

- When SMUTE goes low, the output mute is slowly released.

If the P/S

pin is low, SMUTE is the Chip Select Input for the Serial Control Mode. Chip

select is active when SMUTE is low.

9 DFS I Double Sampling Speed Input. When low, this pin defines the Normal Speed Mode, and

128 x F

s

oversampling is implemented. When high, the DFS pin defines the Double Speed

Mode, implemented with 64 x F

s

oversampling. This pin features an internal pull-down.

10 DEM0

(or CCLK)

I De-emphasis Enable #0 or Control Data Clock Input. If the P/S

pin (pin 25) is high,

DEM0 is used to select the De-emphasis Mode according to Table 3. If the P/S pin os low

DEM0 is the clock input for the Serial Control Mode.

11 DEM1

(or CDTI)

I De-emphasis Enable #1 or Control Data Input. If the P/S

pin (pin 25) is high, DEM1 is

used to select the De-emphasis Mode according to T able 3. If the P/S pin is low, DEM1 is

the control data input for the Serial Control Mode.

12 DIF0 I Digital Input Format Select #0.

13 DIF1 I Digital Input Format Select #1.

14 DIF2 I Digital Input Format Select #2.

15 BVSS - Substrate Ground Pin. Substrate ground is 0V.

16 VREFL I Low Level Voltage Reference Input. Normally connected to analog ground.

17 VREFH I High Level Voltage Reference Input. Normally connected to analog supply.

18 AVDD - Analog Supply. Analog supply is 5V nominal.

19 AVSS - Analog Ground. Analog ground is 0V.

20 AOUTR- O Right Channel Negative Output.

21 AOUTR+ O Right Channel Positive Output.

22 AOUTL- O Left Channel Negative Output.

23 AOUTL+ O Left Channel Positive Output.

24 VCOM O Common Voltage Output. Common voltage output is 2.6V nominal.

25 P/S

I Parallel/Serial Control Mode Select Input. If Low, the Serial Control Mode is

implemented. If High, the Parallel Control Mode is selected. This pin has an internal

pull-up.

26 CKS0 I Master Clock Select #0.

27 CKS1 I Master Clock Select #1.

28 CKS2 I Master Clock Select #2.

Reference Information

2-2 Samsung Electronics

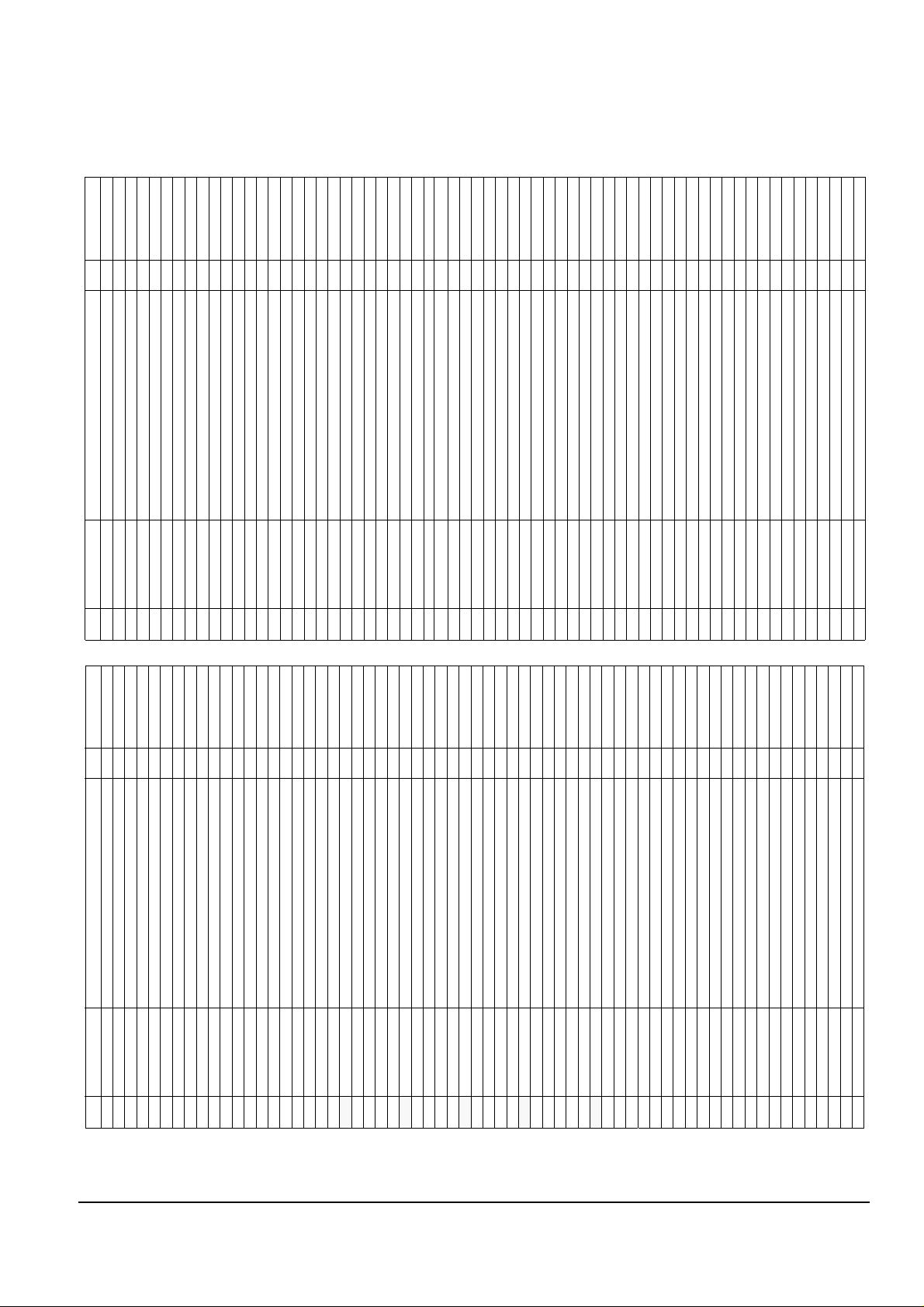

2-1-2 DIC1 (KS1453 ; Data Processor)

DVD CL V/CAV

16-8

DEMO D

32BIT SR

X-tal & Timing

Generator

Frame Sync

DET/PROT /INS

(17.57KHz)

VCO Timing

Generator

MICOM I/F

(208,192,17)

(182,172,11)

ECC

Descrambler

(6,4,3)

efmwr ID ECC

EDC

17.58KHz= 2 6 .1 6M/1 488

RFCK 1 7.58/7.35KHz

26.16MHz

676.08Hz

To MICOM (15)

MDAT[7:0]_BI, MRZA_IN, ZCS_IN, MWR_IN,

MRD_IN, ZIRQZD_OUT, ZWAI T_OUT, ZRST_IN

To DRAM

256K*16

(32)

DD[15:0]_BI

DADR[8:0]_OUT

ZRAS_OUT

ZUCAS_OUT

ZLCAS_ OUT

ZOE[1 :0]_OUT

ZWE[1:0]_OUT

To AV (13)

SDATA[0]_OUT/

CDATA

SDATA[1]_OUT/LRCK

SDATA[2]_OUT/BCLK

SDATA[3]_OUT/C2PO

SDATA[4]_OUT/SQDT

SDATA[5]_OUT/WFSY

SDATA[6]_OUT/S0S1

SDATA[7]_BI /SQCK

DATREQ_IN

CSTROBE _OUT

DTER_OUT

DATACK_OUT

TOS_OUT

Mon i tor (9)

GFS_OUT, FRSYZ_OUT , TX_OU T, EFMO_OUT,

WFCK_OUT, RFCK_ OUT, CK16M_OUT, DEMPHA_OUT

CLVLOCK_OUT

ECSY

CD CL V/CA V

23BIT SR

Frame Sync

DET/PROT /INS

(7.35KHz)

VCO Timing

Generator

M

M

WFCK 17.58/7.35KHz

(32,28,5)

(28,24,5)

CIRC

EFM

DEMO D

SUBCODE I/F

75Hz

M

7.35KHz= 4 .3 218M/588

DVDP ,

SQ-VCD

CD-G

(6,4,3)

trans ID ECC

Deinterleave

&

RAM Control

M

V-C D,CD-D A

To RF (9)

PWMO[ 7:0]_OUT, BCARZ_IN

Pow er (34)=VDD(11)+GND(23)

Test Pin (3

)

TEST0_IN, TEST1_IN, TEST2_IN

Fr om

Servo (3)

EFMI_IN

PLCK_IN

FG_IN

To

Servo (6)

MON_OUT

MDP_OUT

MDS_OUT

FSW_OUT

PLLLOCK_

OUT

SERLOCK_

OUT

X-tal (4)

XTI_IN

XTO_OUT

CK33MI_IN

CK33MO_OUT

Reference Information

Samsung Electronics 2-3

No. Pin Name Description I/O Notes

Notes

1 DVSS Digital GND (0 V)

2 ZCS_IN Chip Select (Active Low) I MICOM

3 MRZA_IN Micom Register Select (L

REGISTER H fi DATA) I MICOM

4 DVSS Digital GND (0 V)

5 MDAT7_BI MICOM Data Bus B MICOM

6 MDAT6_BI MICOM Data Bus B MICOM

7 MDAT5_BI MICOM Data Bus B MICOM

8 MDAT4_BI MICOM Data Bus B MICOM

9 MDAT3_BI MICOM Data Bus B MICOM

10 MDAT2_BI MICOM Data Bus B MICOM

11 MDAT1_BI MICOM Data Bus B MICOM

12 MDAT0_BI MICOM Data Bus B MICOM

13 DVDD Digital Power (+5V)

14 XTI_IN System Clock Input for 26.16 MHz I XTAL

15 XTO_OUT System Clock Output for 26.16 MHz O XTAL

16 DVSS Digital GND (0 V)

17 DD15_BI DRAM Data Bus B DRAM

18 DD0_BI DRAM Data Bus B DRAM

19 DD14_BI DRAM Data Bus B DRAM

20 DD1_BI DRAM Data Bus B DRAM

21 DVSS Digital GND (0 V)

22 DD13_BI DRAM Data Bus B DRAM

23 DD2_BI DRAM Data Bus B DRAM

24 DD12_BI DRAM Data Bus B DRAM

25 DD3_BI DRAM Data Bus B DRAM

26 DVDD Digital Power (+5 V)

27 DD11_BI Digital Data Bus B DRAM

28 DD4_BI Digital Data Bus B DRAM

29 DD10_BI Digital Data Bus B DRAM

30 DD5_BI Digital Data Bus B DRAM

31 DVSS Digital GND (0 V)

32 DD9_BI DRAM Data Bus B DRAM

33 DD6_BI DRAM Data Bus B DRAM

34 DD8_BI DRAM Data Bus B DRAM

35 DD7_BI DRAM Data Bus B DRAM

36 DVSS Digital GND (0 V)

37 ZLCAS_OUT DRAM Low Column Address Strobe O DRAM

38 ZUCAS_OUT DRAM Upper Column Address Strobe O DRAM

39 ZWE1_OUT DRAM Write Enable 1 (8M ONLY) O DRAM

40 ZWE0_OUT DRAM Write Enable 0 (4M, 8M, 16M) O DRAM

41 ZOE1_OUT DRAM Output Enable 1 (16M MODE DADR9) O DRAM

42 DVDD Digital Power (+5 V)

43 ZOE0_OUT DRAM Output Enable 0 O DRAM

44 ZRAS_OUT DRAM Row Address Strobe O DRAM

45 DADR8_OUT

DRAM Address Bus

O DRAM

65 SDATA5_OUT DVD Data/Subcode Frame Sync (WFSY) O AV Decoder

66 SDATA6_OUT DVD Data/Subcode Block Sync (S0S1) O AV Decoder

67 SDATA7_BI DVD Data/Subcode Serial Clock (SQCK) B AV Decoder

68 DVSS Digital GND (0 V)

69 CSTROBE_OUT Data Strobe (Clock) Output O AV Decoder

70 DATREQ_IN Data Request from A/V Decoder or ROM Decoder I AV Decoder

71 DTER_OUT DVD Data Error Output O AV Decoder

72 DVSS Digital GND (0 V)

73 PWMO7_OUT PWM Output Signal O RF

74 PWMO6_OUT PWM Output Signal O RF

75 PWMO5_OUT PWM Output Signal O RF

76 PWMO4_OUT PWM Output Signal O RF

77 DVDD Digital Power (+5 V)

78 PWMO3_OUT PWM Output Signal O RF

79 PWMO2_OUT PWM Output Signal O RF

80 PWMO1_OUT PWM Output Signal O RF

81 PWMO0_OUT PWM Output Signal O RF

82 DVSS Digital GND (0 V)

83 DVSS Digital GND (0 V)

84 DVSS Digital GND (0 V)

85 DVDD DIGITAL Power (+5 V)

86 DVDD DIGITAL Power (+5 V)

87 DVSS Digital GND (0 V)

88 DVSS Digital GND (0 V)

89 DVSS Digital GND (0 V)

90 DVSS Digital GND (0 V)

91 FRSYZ_OUT Frame Sync Out O Monitor

92 TX_OUT Digital Out O Monitor

No. Pin Name Description I/O

46 DADR7_OUT DRAM Address Bus O DRAM

47 DVSS Digital GND (0 V)

48 DADR0_OUT DRAM Address Bus O DRAM

49 DADR6_OUT DRAM Address Bus O DRAM

50 DADR1_OUT DRAM Address Bus O DRAM

51 DADR5_OUT DRAM Address Bus O DRAM

52 DADR2_OUT DRAM Address Bus O DRAM

53 DADR4_OUT DRAM Address Bus O DRAM

54 DADR3_OUT DRAM Address Bus O DRAM

55 DVSS Digital GND (0 V)

56 DVSS Digital GND (0 V)

57 TOS_OUT Top of Sector O AV Decoder

58 DATACK_OUT Data Acknowledge Signal Output O AV Decoder

59 DVDD DIGITAL Power (+5 V)

60 SDATA0_OUT DVD Data/CD Data Bit Stream (CDATA) O AV Decoder

61 SDATA1_OUT DVD Data/CD Data L/R Clock (LRCK) O AV Decoder

62 SDATA2_OUT DVD Data/CD Data Bit Clock (BLCK) O AV Decoder

63 SDATA3_OUT DVD Data/CD Data Error Flag (C2PO) O AV Decoder

64 SDATA4_OUT DVD Data/Subcode Serial Data (SQDT) O AV Decoder

93 GFS_OUT Good Frame Sync Detection State Output (OK at H) O Monitor

94 DVSS Digital GND (0 V)

95 CK33MI_IN System Clock Input for 33.8688 MHz I X-tal

96 CK33MO_OUT System Clock Output for 33.8688 MHz O X-tal

97 DVDD Digital Power (+5 V)

98 TEST0_IN Test Mode Selection Terminal I

99 TEST1_IN Test Mode Selection Terminal I

100 TEST2_IN Test Mode Selection Terminal I

101 EFMO_OUT EFM Out O Monitor

102 WFCK_OUT Write Frame Pulse O Monitor

103 RFCK_OUT Reference Frame Pulse O Monitor

104 PLCK_IN Phase Locked Clock I Servo

105 DVSS Digital GND (0 V)

106 PLLLOCK_OUT Lock Signal for PLL O Servo

107 CLVLOCK_OUT Lock Signal for CLV O Monitor

108 SERLOCK_OUT Lock Signal for SERVO O Servo

109 MDP_OUT Spindle Motor Phase Control Signal (3-STATE) O Servo

110 MDS_OUT Spindle Motor Speed Control Signal (3-STATE) O Servo

111 DVSS Digital GND (0 V)

11 2 DVSS Digital GND (0 V)

11 3 MON_OUT Spindle Motor Output Filter Switching Output O Servo

114 FG_IN Reference Signal for CAV I Servo

11 5 FSW_OUT Spindle Motor Output Filter Switching Output (3-STATE) O Servo

11 6 EFMI_IN EFM/EFM+ Signal Input I Servo

117 DVDD Digital Power (+5 V)

118 DVDD Digital Power (+5 V)

119 DVDD Digital Power (+5 V)

120 CK16M_OUT CK33Ms 2 Division Clock / 16.9344 MHz O Monitor

121 DEMPHA_OUT HIGH, when on Deemphasis O Monitor

122 BCARZ_IN BCA Input Signal I RF

123 DVSS Digital GND (0 V)

124 ZRST_IN Hardware Reset (Active Low) I MICOM

125 ZWAIT_OUT Micom Read / Write Access Wait (Wait at L) O MICOM

126 ZIRQZD_OUT Interrupt Request to Micom O MICOM

127 MRD_IN Micom Read Strobe (Active Low) I MICOM

128 MWR_IN Micom Write Strobe (Active Low) I MICOM

Notes

Reference Information

2-4 Samsung Electronics

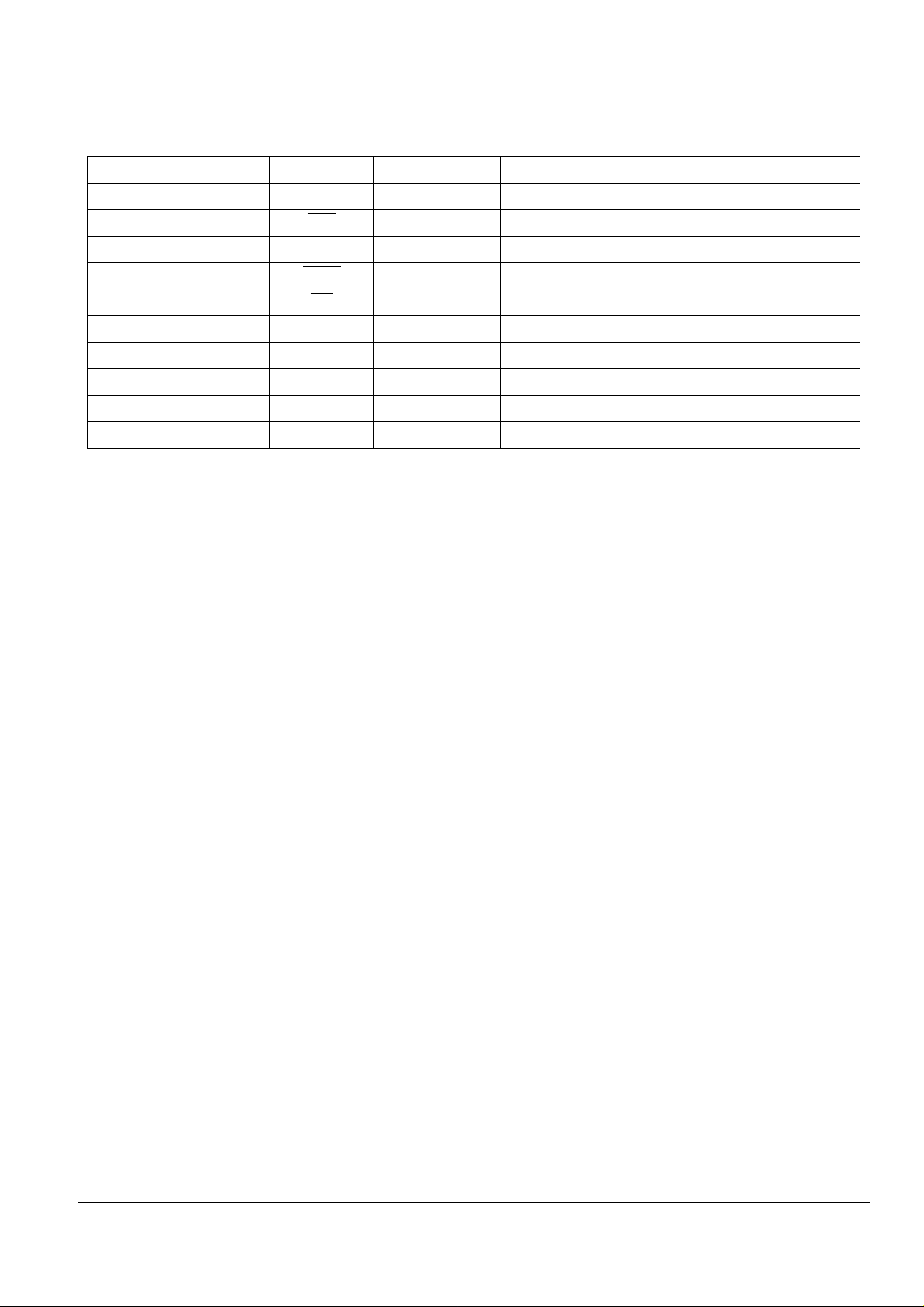

2-1-3 DIC2 (KM416C254D ; CMOS 4M DRAM)

WE

CASL CAS

CASH

D0

D1

D2

D3

D4

D5

D6

D7

D8

RAS

NO.2 CLOCK

GENERATOR

CONTROL

LOGIC

COLUMN

DECODER

SENSE AMPLIFIERS

VO GATING

ROW

DECODER

512x512x16

MEMORY

ARRAY

512

512

DATA-IN BUFFER

DATA-OUT

BUFFER

REFRESH

CONTROLLER

REFRESH

COUNTER

NO.1CLOCK

GENERATOR

ROW.

ADDRESS

BUFFERS(9)

COLUMN

ADDRESS

BUFFER

OE

Vcc

Vss

IO0

IO15

16

9

88

99

9

9

16

512x16

Reference Information

Samsung Electronics 2-5

PIN NO. SYM. TYPE DESCRITION

16~19, 22~26 A0~A8 Input Address Input

14 RAS Input Row Address Strobe

28 CASH Input Column Address Strobe/Upper Byte Control

29 CASL Input Column Address Strobe/Lower Byte Control

13 WE Input Write Enable

27 OE Input Output Enable

2~5, 7~10, 31~34, 36~39 I/O0~I/O15 Input/Output Data Input/Output

1, 6, 20 Vcc Supply Power, 5V

21, 35, 40 Vss Ground Ground

11, 12, 15, 30 NC - No Connect

Reference Information

2-6 Samsung Electronics

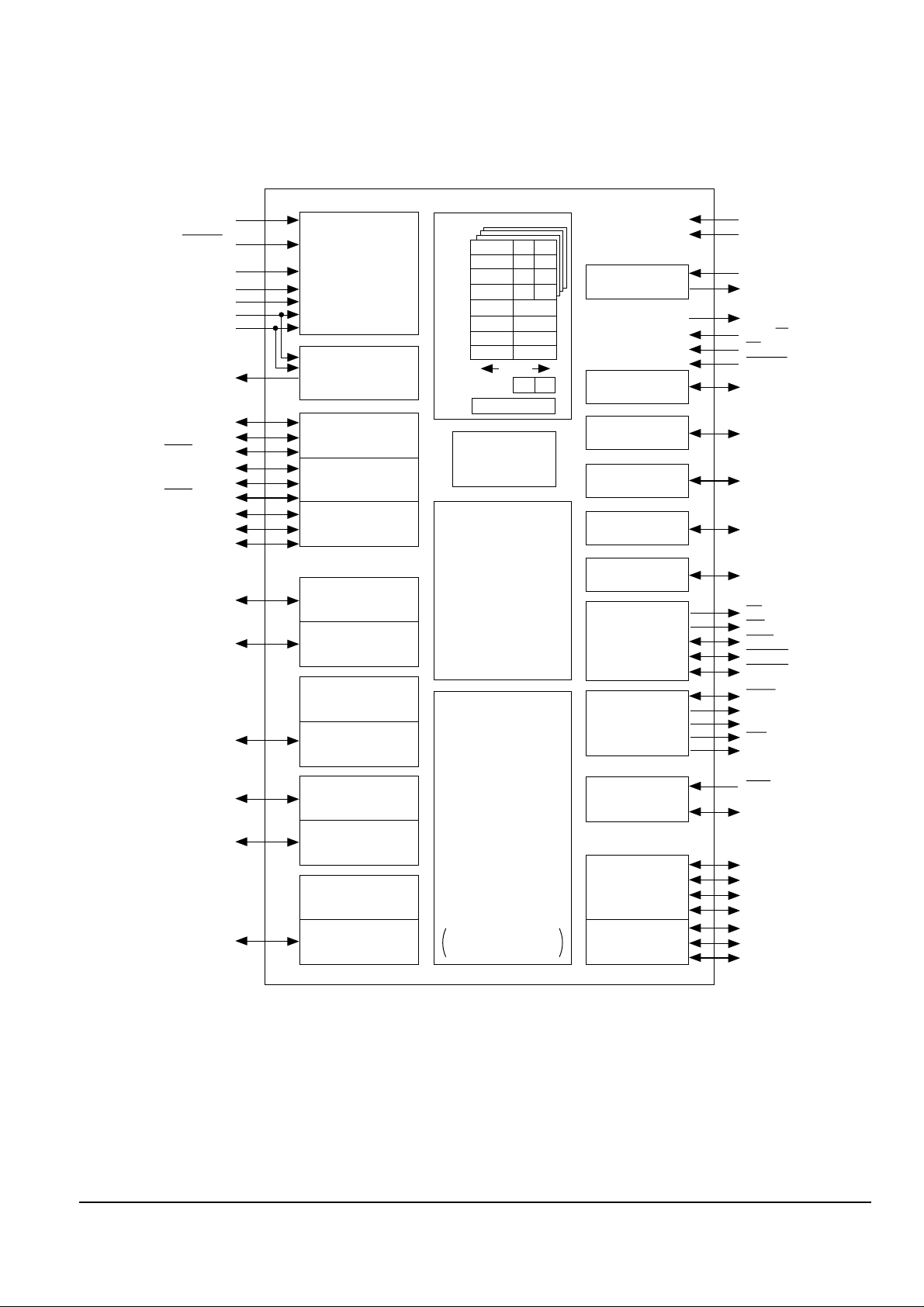

2-1-4 MIC1 (TMP95C265 ; Main Micom)

AND~AN2

(PA0~PA2)

AN3/ADTRG

(PA3)

AN4~AN7

(PA4~PA7)

VREFH

VREFL

AVCC

AV55

TxD0(P80)

RxD0(P81)

SCLK0/CT50(P82)

TxD1(P83)

RxD1(P84)

SCLK1/CT51(P85)

TxD2(P86)

RxD2(P87)

SCLK2/CT52(P57)

DAOUT0,1

10BIT 8CH

A/D

CONVERTER

8BIT 2CH

A/D

CONVERTER

SERIAL I/O

(CH. 1)

SERIAL I/O

(CH. 0)

SERIAL I/O

(CH. 2)

8BIT TIMER

(TIMER 0)

8BIT TIMER

(TIMER 1)

8BIT TIMER

(TIMER 2)

8BIT TIMER

(TIMER 3)

8BIT TIMER

(TIMER 4)

8BIT TIMER

(TIMER 5)

8BIT TIMER

(TIMER 6)

8BIT TIMER

(TIMER 7)

Not included in

TMP95C265

64KB ROM

2KB ROM

WATCHDOG

TIMER

PC

SR

XWA

XBC

XDE

XHL

XIX

XIY

XIZ

XSP

W

900/H CPU

A

BC

DE

H

IX

OSC

PORT0

PORT1

PORT2

PORT3

PORT4

PORT5

CS/WAIT

CONTROLLER

(4-BLOCK)

INTERRUPT

CONTROLLER

16BIT TIMER

(TIMER 8)

16BIT TIMER

(TIMER 9)

IY

IZ

SP

L

32bit

F

VCC [3]

VSS[3]

X1

X2

(P00~P07)

D0~D7 *

(P10~P17)

D8~D15

(P20~P27)

A15~A23 *

(P30~P37)

A8~A15 *

(P40~P47)

A0~A7 *

WAIT(P55)

C50(P60)

C51(P61)

C52(P62)

C53(P63)

T18/INT5(P90)

T19/INT6(P91)

TO8(P92)

TO9(P93)

TIA/INT7(P94)

TIB/INT8(P95)

TOA/TOB(P96)

NIMI

INTO(P56)

RD(P50)*

WR(P51)*

HWR(P52)

BUSRQ(P53)

BUSAK(P54)

CLK

AM8/16

EA

RESET

T10/INT(P70)

TO3/INT2(P72)

T14/INT3(P73)

TO7/INT4(P75)

TO1(P71)

TO5(P74)

Reference Information

Samsung Electronics 2-7

NO PORT NAME ASSIGNED NAME DESCRIPTION TYPE REMARK

51 D6 HAD6 Data6 I/0

52 D7 HAD7 Data7 I/0

53 P10 CLSW Close Switch I DECK

54 P11 OPSW Open Swithc I DECK

55 P12 MTP8 Reserved I/0 0 NC

56 P13 MTP9 Reserved I/0 0 NC

57 P14 MTP10 Reserved I/0 0 NC

58 P15 MTP11 Reserved I/0 0 NC

59 P16 MTP12 Reserved I/0 0 NC

60 P17 MTP13 Reserved I/0 0 NC

61 AM8/16 AM8 Address Mode(H:8 BIT MODE) I VCC

62 Vss DGND - GND

63 Vcc 5D - VCC

64 A23 HA23

SERVO /RD Strobe Mask Signal

0 74HCOO(5)

65 P26/A22 MRP14 Reserved Address Port 0 NC

66 P25/A21 MRP15 Reserved Address Port 0 NC

67 P24/A20 MRP16 Reserved Address Port 0 NC

68 A19 HA19 Address 19 0

EPROM, SRAM ADDRESS

69 A18 HA18 Address 18 0

EPROM, SRAM ADDRESS

70 A17 HA17 Address 17 0

EPROM, SRAM ADDRESS

71 A16 HA16 Address 16 0

EPROM, SRAM ADDRESS

72 A15 HA15 Address 15 0

EPROM, SRAM ADDRESS

73 A14 HA14 Address 14 0

EPROM, SRAM ADDRESS

74 A13 HA13 Address 13 0

EPROM, SRAM ADDRESS

75 A12 HA12 Address 12 0

EPROM, SRAM ADDRESS

76 A11 HA11 Address 11 0

EPROM, SRAM ADDRESS

77 A10 HA10 Address 10 0

EPROM, SRAM, Zlva Adrs

78 A9 HA9 Address 9 0

EPROM, SRAM, Zlva Adrs

79 A8 HA8 Address 8 0

EPROM, SRAM, Zlva Adrs

80 A7 HA7 Address 7 0

EPROM, SRAM ADDRESS

81 A6 HA6 Address 6 0

EPROM, SRAM ADDRESS

82 A5 HA5 Address 5 0

EPROM, SRAM ADDRESS

83 A4 HA4 Address 4 0

EPROM, SRAM ADDRESS

84 A3 HA3 Address 3 0

EPROM, SRAM ADDRESS

85 A2 HA2 Address 2 0

EPROM, SRAM ADDRESS

86 A1 HA1 Address 1(SERVO DAB) 0

EPROM, SRAM ADDRESS

87 A0 HA0 Address 0(DSP DAB) 0

EPROM, SRAM ADDRESS

88 /RD /RD /Read Strobe 0 /Read

89 /WR /WR /Write Strobe 0 /Write

90 P52 RSTB RF&Servo IC Reset 0 KS1461 (73), KS1452 (9)

91 Vss DGND - DGND

92 PA0 RFRP

Tracking Lock monitir from SERVO

I KS1452 (7)

93 PA1 TILTO Monitor signal I KS1452 (69)

94 PA2 MTP17 Reserved I I NC

95 PA3 SENSE SENSE monitor from SERVO I KS1452 (22)

96 PA4 FR

Spindle direcrion from SP Driver

I BA6849FP (20)

97 PA5 SLOCK LOCK monitor from DSP I KS1453 (108)

98 PA6 FOKB Focus lock monitor from RF I KS1461 (48)

99 PA7 RFO RF sum signal (Analog Lnput) I RFO

100 VREFH 5D A/D Ref Input (H) I 5D

NO PORT NAME ASSIGNED NAME DESCRIPTION TYPE REMARK

1 VREFL DGND A/D Ref Input(L) I DGND

2 AVss DGND A/D Ref Input - DGND

3 AVcc 5D A/D VCC Input - 5D

4 DAOUT0 MTP1 0 NC

5 DAOUT1 MPT2 0 NC

6 /NMI - PULL-UP I

7 P53 CSB D. Servo IC Chip Select 0 KS1452(10)

8 P54/BUSAK MTP3 0

9 /WAIT /MWAIT /Wait(ZiVA, DSP) I /MWait

10 P56 DVD/CD DVD/CD RF AGC Gain Select 0 RF(KS1461)

11 SCLK2 SCLK Serial Data Clock I FRONT

12 P80/TXD0 MD RF Contrl Data 0 KS1461(69)

13 P81/RXD0 STB RF Data Latch I/0 KS1461(71)

14 P82/SCLKO MC RF Control Clock 0 KS1461(70)

15 P83/TXD1 MTP5 0 NC

16 P84/RXD1 MTP6 0 NC

17 P85/SCLK1 MTP4 0 NC

18 TXD2 RXD Serial Data Output 0 FRONT

19 RXD2 TXD Serial Data Input I FRONT

20 CSO /CSO EPROM(M27C801) Select 0 EPROM(M27C801)

21 CS1 /CS1 SRAM(KM681000) Select 0 SRAM(KM681000)

22 CS2 /DVD1CS AVDecoder(ZiVA4) Select 0 AVDecoder(ZiVA4)

23 CS3 /DSPCS

Data Processor(KS1453) Select

0 Data Processor(KS1453)

24 CLK CLK

CLOCK OUTPUT (System Clock 2)

0 fc/2

25 Vcc 5D - VCC

26 Vss GDND GND - GND

27 X1 X1 High Frequency OSC in I

28 X2 X2 High frequency OSC out 0

29 /EA /EA Internal ROM Less Mode I GND

30 /REST /MRST Master reset from FRONT I FRONT, IC

31 INT1 SRQ Interrupt from Front Micom I FRONT

32 P71 RRQ Request to Front Micom 0 FRONT

33 P72 SCL EEPROM CLOCK 0 KS24C020(6)

34 P73 SDA EEPROM DATA I/O 0 KS24C020(5)

35 P74 OPEN Tray Out Motor Control Output 0 DRIVER(0PIN-, 16)

36 P75 CLOSE Tray In Motor Control Output 0 DRIVER(0PIN-, 17)

37 INT5 FGINT

Interrupt from Spindle Motor FG

I DRIVER(FG, 2)

38 P91 ACT MUTE Driver IC MUTE(Actuator) 0 DRIVER(MUTE4, 37)

39 P92 M/D MUTE Driver IC MUTE(Spindle) 0 DRIVER(MUTE3, 38)

40 P93 ZRST DSP H/W reset 0 KS1453(124)

41 INT7 /DVDINT Interrupt from AV-DEC I INV(ZiVA-4(51))

42 INT8 /DSPINT Interrupt from DSP I INV(KS1453(126))

43 P96 ZIVA_RST

AV Decoder Reset(Active H:4.0, L:4.1)

0 ZiVA-4(52)

44 Vcc 5D

45 D0 HAD0 Data 0 I/0

46 D1 HAD1 Data 1 I/0

47 D2 HAD2 Data 2 I/0

48 D3 HAD3 Data 3 I/0

49 D4 HAD4 Data 4 I/0

50 D5 HAD5 Data 5 I/0

20MHz

Loading...

Loading...