SAMSUNG CT-727 Diagram

14. Schematic Diagrams

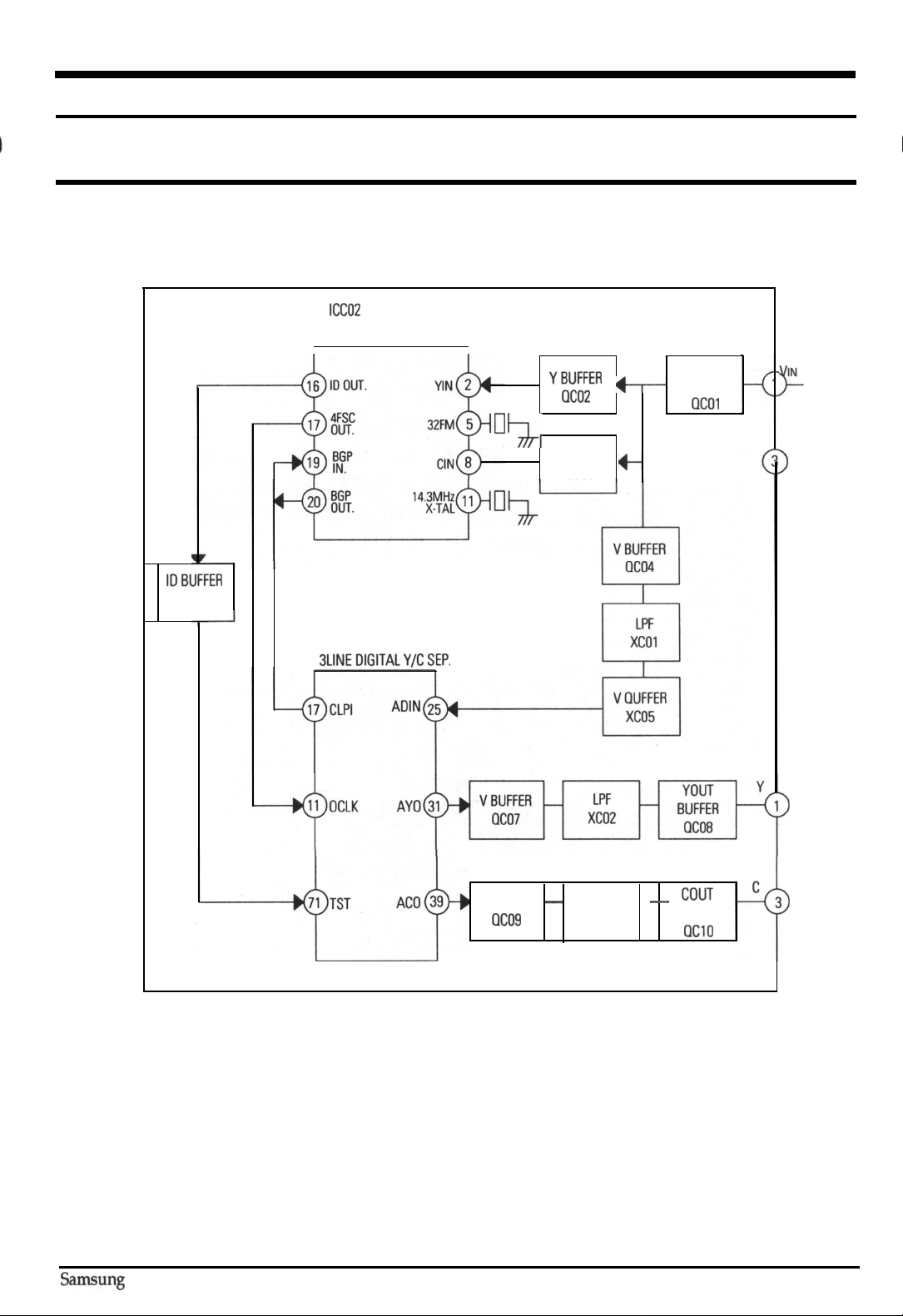

14-1 Digital Comb Filter and Clock Generator

14-1-1 Block Diagram

ICC02

CLOCKGENERATOR

IDBUFFER

0C06

ICC01

JLlNEDlGlTALY/CSEP.

YBUFFER +______

oc02

t;h-.

. CBUFFER

QC03

+_

VIDEO

BUFFER

OCOl

IN

J>

Samsung

Electronics

CBUFFER

QC09

Fig.

.

14-1

-

LPF -

xc03

'OUT

BUFFER

QClO

14-1

Schematic Diagrams

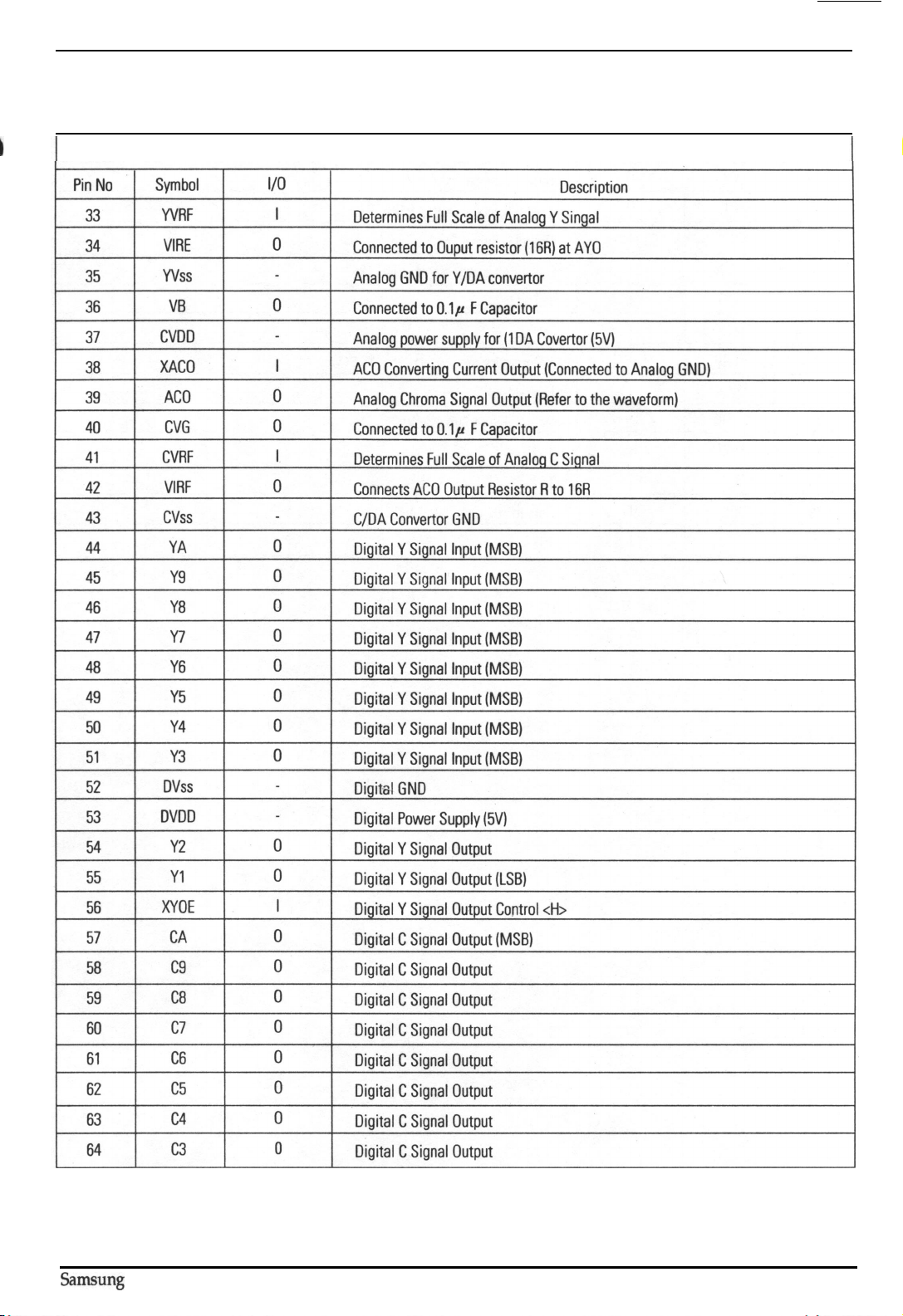

14-1-2 Digital Comb Filter Pin Descriptions

18

19

20

29

30

31

32

XCPDN

ADVS

ICP

YVDD

XAYO

AYO

YVG

AD Convertor Clock Pulse Input

Connected to GND, clamping On

AD Convertor Digital GND

Integrates Clamp Control Voltage, connected to 0.01 mF Capacitor

AD

Convertor Digital

Y/DA Convertor Power Supply (5V)

AYO Convert Current Output (connected to Analog

Analog Y Signal Output (refer to the waveform)

Connected to 0.1 mF Capacitor

Power

(BGP)

Supply(5V)

Clamping the Low Clamp Pulse Signal

Wss)

14-2

Samsung

Electronics

Table 14-1 (Continued)

Schematic Diagrams

!hnsung Electronics

14-3

Schematic

Diaerams

71

72

73

74-

78

79

80

TEST

DVSS

DVDD

TEST

TEST

BPF

TEST

Y Output Mode Convert

Digital GND

Digital Power Supply

TST

tb

TST

<b

Sets to

tb,

Standard Mode

TST

tb

(5V)

tH> :

TST On

14-4

Samsung

Electronics

Schematic Diagrams

14-1-3 Clock Generator (CXA

14-1-3 (a) Clock Generator, Block Diagram

1666M)

Samsung

Electronics

145

Schematic Diagrams

14-l-3 (b) Digital Clock Generator, Pin Description

Connected to 32fH VCO Ceramic Oscillator

Table

14-Z

14-6

Samsung

Electronics

14-1-4 Digital Comb Filter and Clock Generator, Waveforms

100% Multiburst

Fig.

14-3

VIN

Fig. 14-4 Y-OUT

Schematic

Diaerams

7-Step Color Bar

Fig. 14-5

V

IN

V

~6.~$$_._.__._____ _

I 1

I .

_:_..___ - .__. --..-.-

Fig. 14-6 Y-OUT

Samsung

Electronics

.

Fig. 14-7 C-OUT

147

Schematic Diaerams

14-1-5 Digital

I I

I

S-line

Y/C Separator (ICCOl)

I I

Fig. 14-8 Pin 25

t

I

ADIN

I

I

I I

u

I

I

f

I

I

Fig. 14-9 Pin 17

CLPI

IU

I

-_.

14-8

Fig. 14-10 Pin H, OCLK

.-- --

-

bLYID!b

Fig. 14-12 Pin31 AYO

Fig. 14-11 Pin 14CLK0

Fig. 14-13 Pin 39

AC0

Samsung

Electronics

Loading...

Loading...