㆔合微科股份㈲限公司

S

AMHOP

GENERAL DESCRIPTION FEATURES

Microelectronics Corp.

SM6B595

8-BIT LED DRIVER

The SM6B595 is specifically designed for

USE in LED DISPLAY.

This device contains an 8-bit shift register,

8 bit D-type storage register an d open-drain

NMOS output drivers.

The serial output allows for cascading of the

data from the shift register to additional

devices.

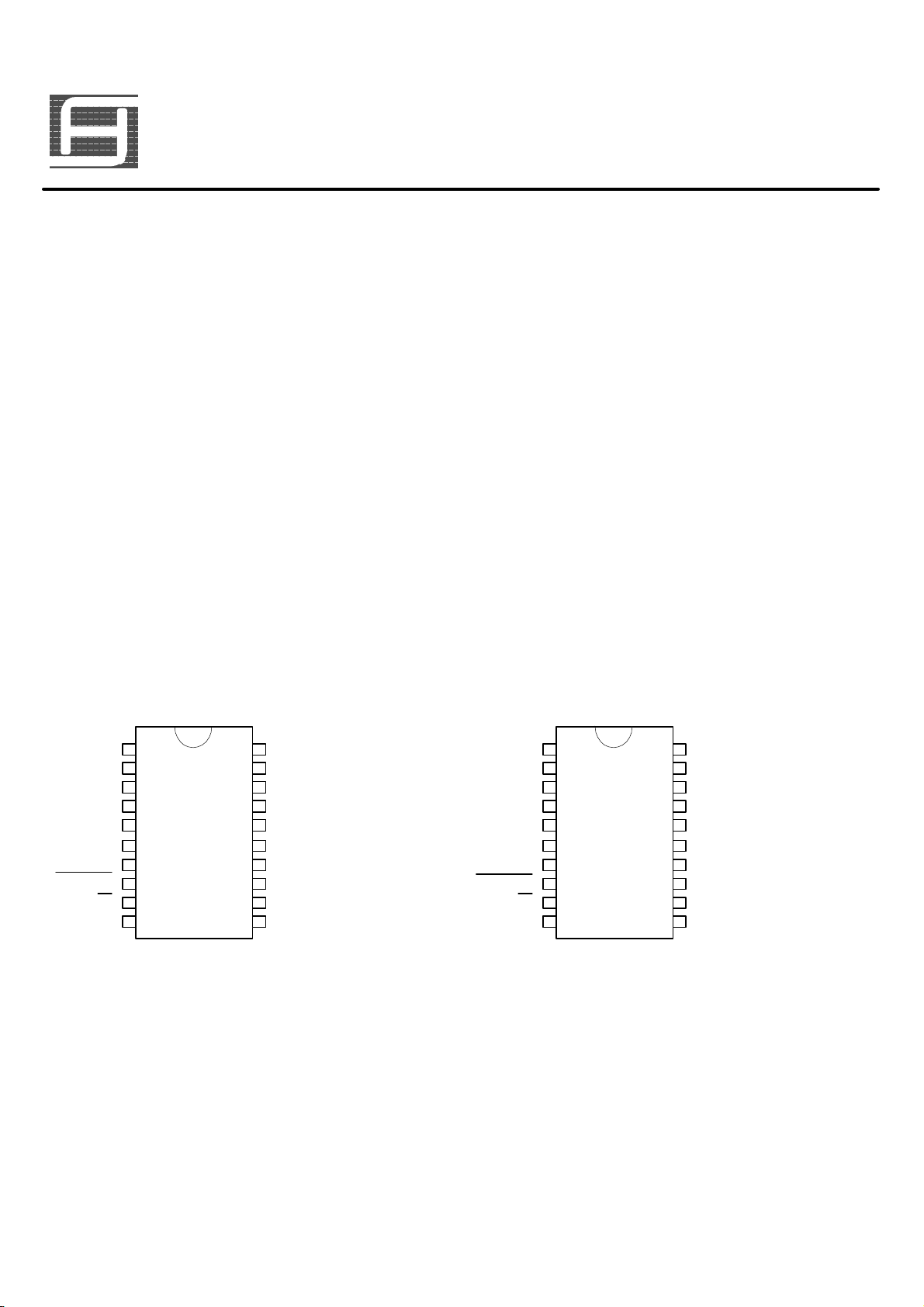

PIN ASSIGNMENTS

* Maximum output terminal voltage: 30V.

* Maximum continuous drain current:100mA.

* Typical R

DS(ON) :

5 Ω

* Devices are cascadable

* Low power consumption

* Serial data transfer rate: 25 MHz.

NC

VCC

SERIN

OUT0

OUT1

OUT2

OUT3

SRCLR

G

GND

1

2

3

4

5

6

7

8

9

10

SM6B595P

20 PIN DIP

20

19

18

17

16

15

14

13

12

11

NC

GND

SEROUT

OUT7

OUT6

OUT5

OUT4

SRCK

RCK

GND

NC

VCC

SERIN

OUT0

OUT1

OUT2

OUT3

SRCLR

G

GND

1

2

3

4

5

6

7

8

9

10

SM6B595F

20 PIN SOP

20

19

18

17

16

15

14

13

12

11

NC

GND

SEROUT

OUT7

OUT6

OUT5

OUT4

SRCK

RCK

GND

Page 1

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

PIN DESCRIPTION

Microelectronics Corp.

SM6B595

8-BIT LED DRIVER

Pin NO.

1

2

3

4-7

8

9 G

10-11 GND Ground terminal.

Pin Name

NC

Vcc

SER IN

OUT0~3

SRCLR

No connection

5V supply voltage terminal.

Input terminal of a serial-data for shift-register.

Output terminals.

Input terminal of clear signal for shift-register. When SRCLR is

low, the input shift-register is cleared.

Input terminal of output enable. All outputs (OUT0~7) do off

with "H" level of G-terminal, and do on with "L" level input.

Function Description

12 RCK

13

14-17

18

19

20

SRCK

OUT4~7

SER OUT

GND

NC

Input terminal of a clock for storage-register. Data transfer

through storage-register on the rising edge of the storageregister clock.

Input terminal of a clock for shift-register. Data transfer through

shift-register on the rising edge of the shift-register clock.

Output terminals.

Output terminal of serial-data for next SER IN terminal.

Ground terminal.

No connection.

Page 2

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

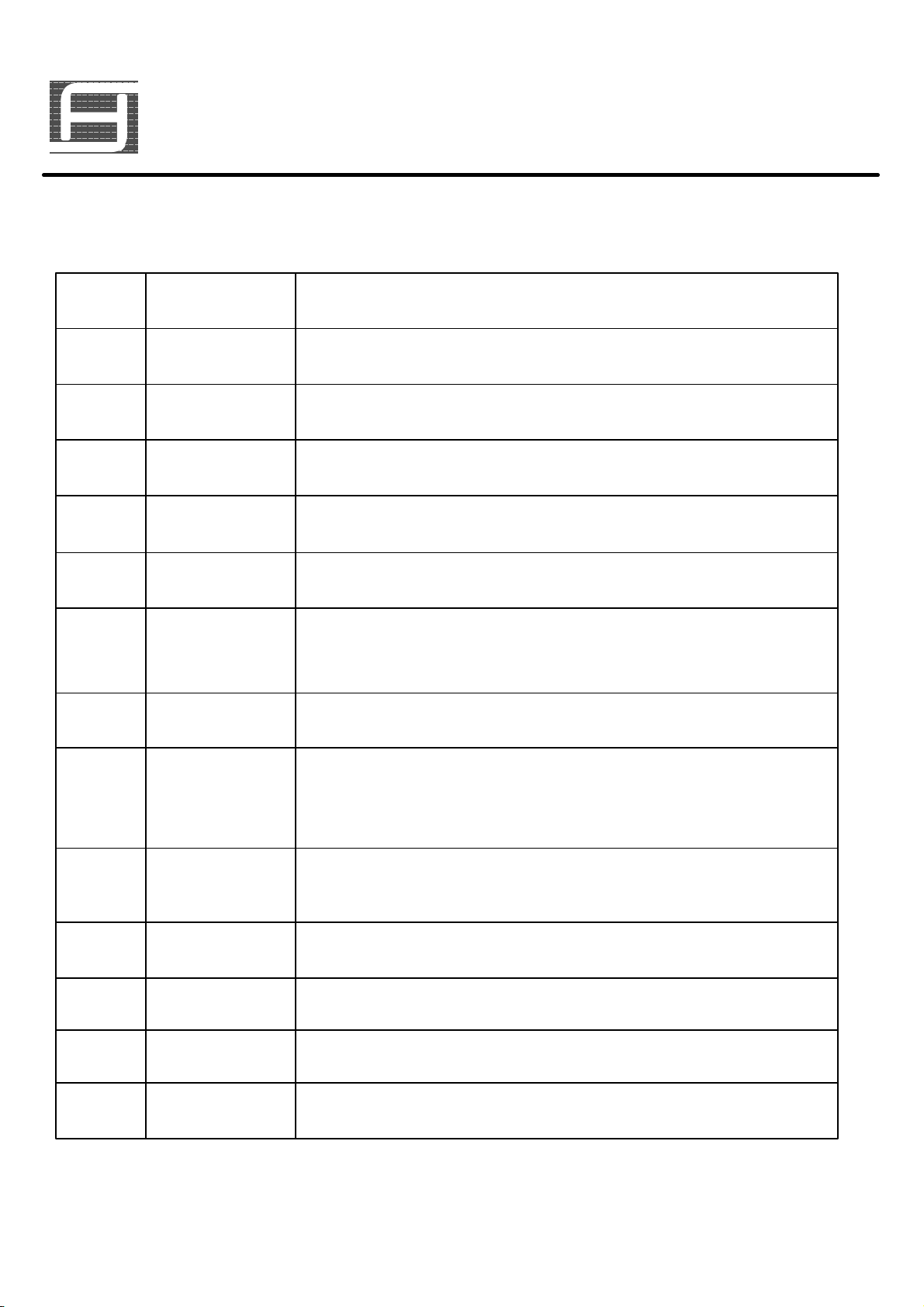

BLOCK DIAGRAM

G

RCK

SERIN

SRCK

Microelectronics Corp.

OUT0 OUT1 OUT7

Q D

CK

D Q

CK

CLR

D Q

CK

CLR

Q D

CK

D Q

CK

CLR

SM6B595

8-BIT LED DRIVER

Q D

CK

SERIAL-OUT

SRCLR

TIMING DIAGRAM

SRCK

SER IN

SRCLR

RCK

G

Out0

Out1

Out2

Out7

Serial-out

5V

0V

5V

0V

5V

0V

5V

0V

5V

0V

Off

On

Off

Off

On

Off

5V

0V

Page 3

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

TRUTH TABLE

Microelectronics Corp.

SM6B595

8-BIT LED DRIVER

SERIN

H

L

X

X

SRCLR

H

H

H

L L L L … L L LX

Shift-register

H R0 R1… R5 R

L R0 R1… R5 R

R0 R1 R2… R6 R

X X X … X X X

P0 P1 P2 … P6 P

SEROUT

6

6

7

7

R

R

R

P

RCK GSRCK

6

6

7

Storage-register

R0 R1 R2 …R6 R7

7

P0 P1 P2 … P6 P7

X X X … X X

P : Present state. R : Previous state.

MAXIMUM RATINGS (Ta = 25oC unless otherwise noted)

Characteristic

Logic Supply Voltage

Logic Input Voltage

Output Current

Output Voltage

Operating Termerature

Symbol

VCC

VIN

IOUT

VOUT

Topr

TstgStorage Temperature

- 0.3 ~ 7V

-40 ~ 125 oC

-55 ~ 150 oC

Rating

7 V

100 mA

30 V

H

OUT0 OUT1…OUT7

L

P0 P1 … P7

H H … H

Page 4

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

RECOMMENDED OPERATING CONDITIONS

Microelectronics Corp.

SM6B595

8-BIT LED DRIVER

Characteristic UnitTyp. Max.Symbol

Supply Voltage

Output Voltage

Output Current

Input Voltage

Set-up Time for SER IN

Hold Time for SER IN

Pulse duration for SER IN

Operating Temperature

V

CC

V

OUT

I

O

V

IH

V

IL

tsetup

t

hold

tw

Topr

Condition

-

OUTn

OUTn

-

-

-

-

-

-

Min.

4.5

-

-

0.85Vcc

-

20

20

40

-40

5.0

-

-

-

-

-

-

-

-

5.5

30

100

-

0.15Vcc

-

-

-

85

V

V

mA

V

V

ns

ns

ns

o

C

Page 5

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

Microelectronics Corp.

SM6B595

8-BIT LED DRIVER

ELECTRICAL CHARACTERISTICS (V

Characteristic

Output breakdownvoltage

Off-state leakage current

Static drain-source

on-state resistance

Nominal Current

Logic input current

Symbol

V

(BR)DSX

I

DSX

R

DS(ON)

I

N

I

IH

I

IL

DD

= 5.0V, Ta = 25oC unless otherwise noted)

Condition

I0=ImA

V0 =24V, Vcc= 5.5V

V0 =24V, Vcc=5.5V, Tc=125oC

V0 =12V, Vcc= 5.5V

V0 =12V, Vcc=5.5V, Tc=125oC

I0= 100mA, Vcc= 4.5V

V

DS(on)

=0.5V, Ta=85oC

VI = V

VI = 0, Vcc=5.5V

cc

=5.5V

Min. Typ. Max. Unit

30

-

-

-

-

-

-

- -

- -

- -

0.5

10

0.1

1

5

90

5

30

1

3

-

-

1

-1

V

µA

Ω

mA

µA

µA

Logic Supply Current

SER OUT output voltage

Propagation delay

(G-OUTn)

Output rise time

Output fall time

I

V

V

t

PLH

t

PLH

CC

OH

OL

t

r

t

f

VCC=5.5V

IOH = -20µA, Vcc= 4.5V

IOH = -4mA, Vcc= 4.5V

IOL =20µA, Vcc = 4.5V

IOL = 4mA, Vcc = 4.5V

Io = 100mA, CL=30

Io = 100mA, CL=30

Io = 100mA, CL=30

Io = 100mA, CL=30

PF

PF

PF

PF

-

4.4 4.49

4.0 4.2

-

-

-

-

-

-

20

0.005

0.3

150

90

200

200

100

-

-

0.1

0.5

-

-

-

-

µA

V

V

V

V

ns

ns

ns

ns

Page 6

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

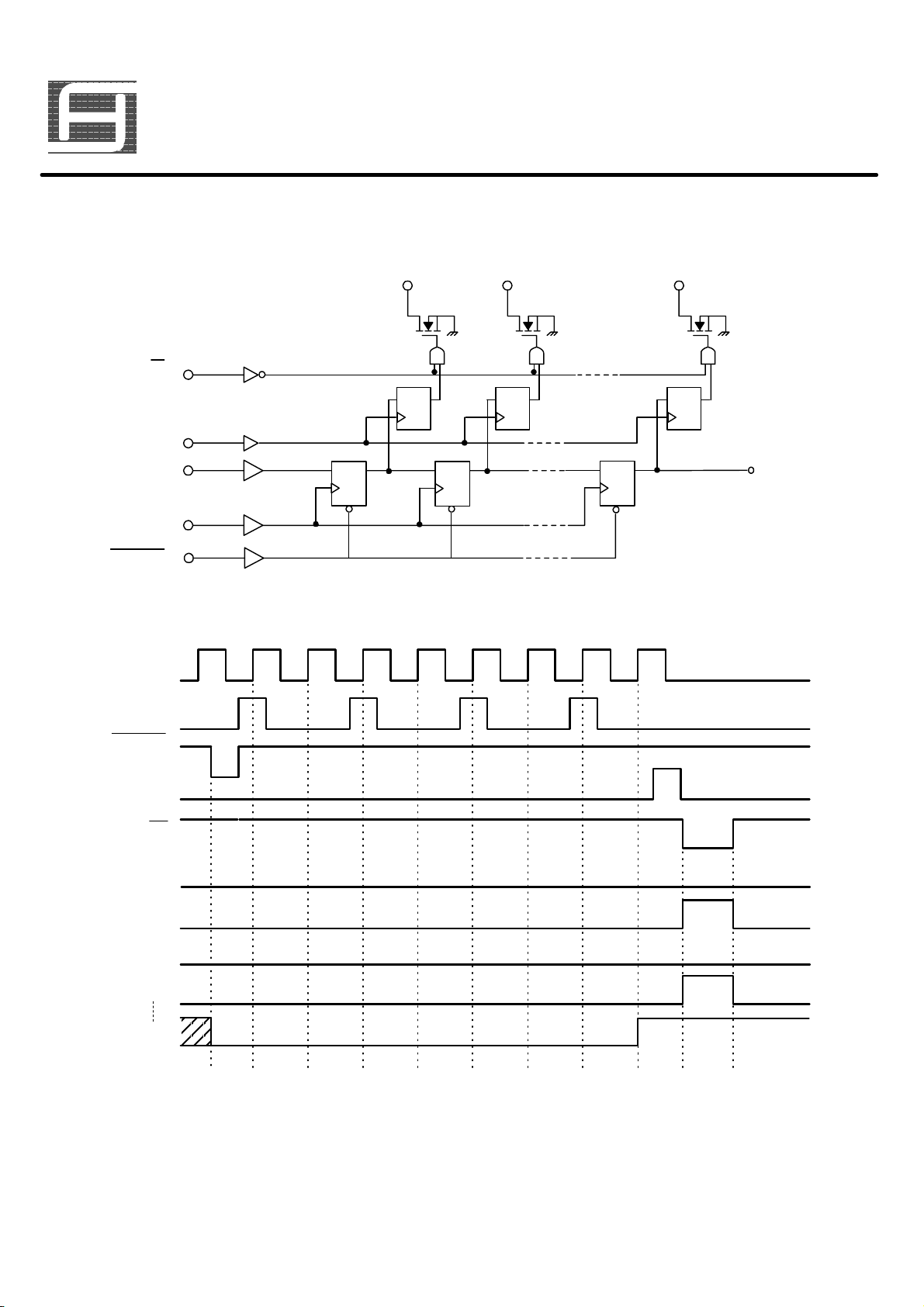

TIMING WAVEFORM

Microelectronics Corp.

t

W

(SRCK)

SM6B595

8-BIT LED DRIVER

SRCK

SER IN

SER OUT

RCK

G

OUTn

G

OUTn

t

setup

50%

t

hold

tp

50%

50%

tsetup

t

W(G)

50%

t

W(RCK)

50%

Low

tp

50%

t

PLH

t

PHL

90%

t

f

10%

t

r

Page 7

0

0

0

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

PACKAGE OUTLIN

20 PINS DIP

110

Microelectronics Corp.

0.975 (24.77)

0.940 (23.88)

1120

0.070 (1.78) MAX

SM6B595

8-BIT LED DRIVER

0.260 (6.60)

0.240 (6.10)

0.035 (0.89) MAX 0.020 (0.51) MIN

0.100 (2.54)

0.021 (0.53)

0.015 (0.38)

0.010 (0.25)

M

0.200 (5.08) MAX

Seating Plane

0.125 (3.18) MIN

0.325 (8.26)

0.300 (7.62)

0.015 (0.38)

Gauge Plane

0.010 (0.25) NOM

0.430 (10.92) MAX

UNIT : inches (millimeters)

Page 8

SEP, 2002

㆔合微科股份㈲限公司

S

AMHOP

PACKAGE OUTLIN

20 PINS SOP

Microelectronics Corp.

SM6B595

8-BIT LED DRIVER

0.050 (1.27)

110

0.510 (12.95)

0.500 (12.70)

0.020 (0.51)

0.014 (0.35)

1120

0.010 (0.25)

0.419 (10.65)

0.400 (10.15)

0.299 (7.59)

0.291 (7.39)

M

0.010 (0.25) NOM

Gage Plane

o

o

0

- 8

0.010 (0.25)

0.050 (1.27)

0.016 (0.40)

0.104 (2.65) MAX

0.012 (0.30)

0.004 (0.10)

Page 9

Seating Plane

0.004 (0.10)

UNIT : inches (millimeters)

SEP, 2002

Loading...

Loading...