SAMES SA9401 Datasheet

sames

UNIVERSAL PABX TONE GENERATOR

FEATURES

■ Generates PBX supervisory tones in

PCM format

SA9401

■ Each of these tone streams selectable

from 16 tone blocks

■ Integrated time slot allocation circuitry

■ No noticeable level changes in tones

■ Frame synch. signal source (internal/

external) selectable

■ Eight tone programs

■ Eight independent PCM tone streams

■ Seperate Intrude Tone for each pro-

gram

■ Choice of clock frequencies

■ Watchdog facility

■ Low power CMOS technology

within each program

PROGRAMMABLE FEATURES

■ Tone samples

■ Tone Cadence timing

■ Tone to time-slot mapping

■ Size of tone blocks

■ Intrude tone frequency

■ Intrude tone cadence

■ "silence sample" value

DESCRIPTION

The SA9401 operates in conjunction with a standard EPROM to generate the system

tone plans for the PABX systems of most major countries.

The high level of programmability allows the SA9401 to satisfy a wide variety of tone

plans. Furthermore by providing three inputs to select between one of eight tone

programs during initialisation, the device effectively facilitates the design of a universally

programmable "PABX Processor Card". Because the tone program inputs are latched

at the start of each PCM frame the SA9401 minimises the possibility of glitches.

The SA9401 can also generate the PCM Frame synchronising reference signal if

required.

4092 PDS039-SA9401-001 REV. C 07-05-96

SA9401

C

A6A5P

A4GNDA3A2A1A0C

LK_SEL

CMFSC

LKIN

CC

D2

D1

MRST

D0

A7

40

41

42

43

44

1

2

3

4

5

6

V

363739 38

35 34 33 32

SA9401

D3

D4

D5

D7

D6

31

30 29

28

TEST

27

FS1

26

A8

25

A9

24

A11

23

GND

22

A10

21

A12

20

A13

19

PS2

18

WD_INT

DR-00603

87910

CLKDIV2

PS0

2MCLK

8KFS

11 141312

INTRFRQ

CC

INTRCAD

V

15

16 17

PCM_OUT

PS1

WD_RST

WD_EN

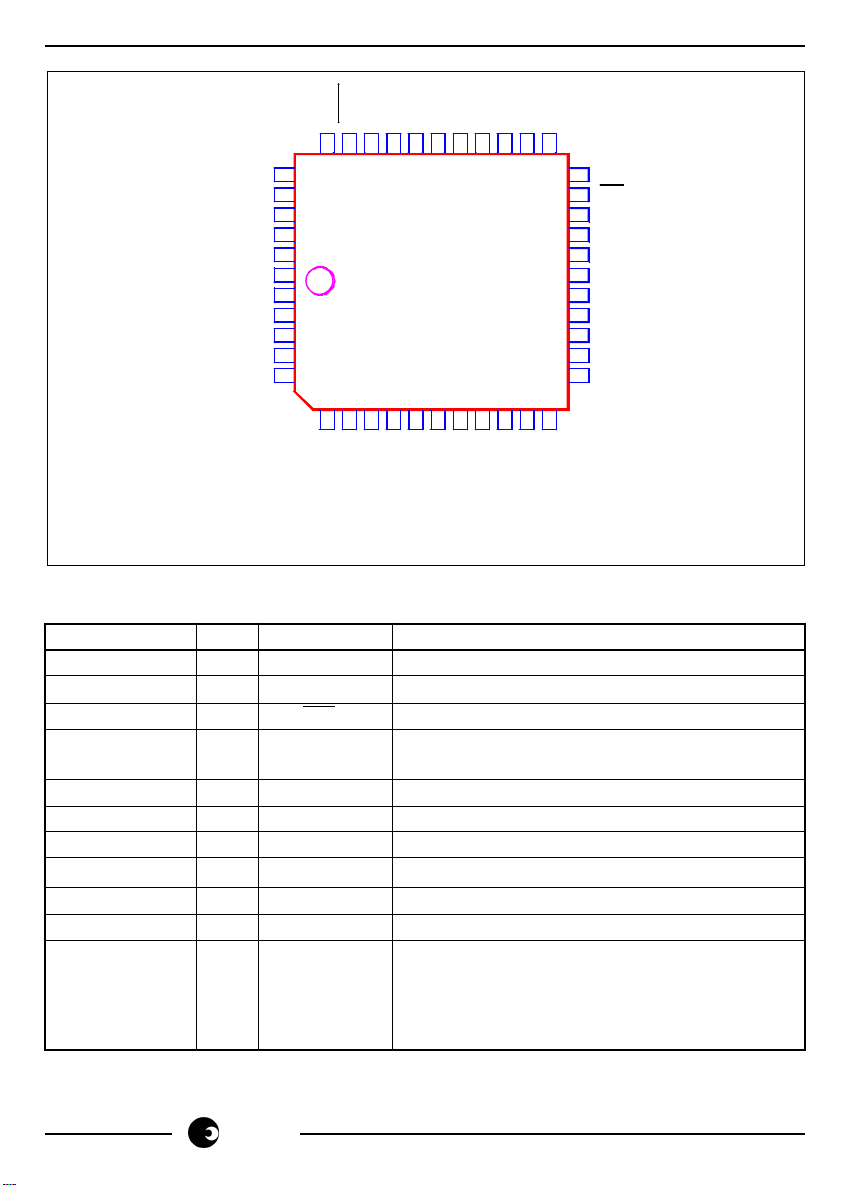

Package : PLCC - 44

PIN DESCRIPTION

Pin No I /0 Designation Description

1, 23 I GND Supply Ground

12, 34 I VCC +5V Power Supply

27 I FS1 Frame Synchronisation (active low)

6 I CLKIN Master clock input (either 8192kHz or 2048 Khz

dependent on logic level of "CLK _SEL")

8 O 2MCLK 2048 kHz clock derived internally from CLKIN

10 O 8KFS 8 kHz Frame Synchronisation output.

5 O PCMFSC 8 kHz Auxilliary Frame Synchronisation Output

11 O INTRFRQ Square Wave Intrude Tone

13 O INTRCAD Intrude Tone Cadence Signal

15 O PCM_OUT Tri-state PCM Highway tone output

41, 42, 43, 44, O A0..A13 EPROM Address Lines

2, 3, 4, 39, 26,

25, 22, 24,

21, 20

2

sames

PIN DESCRIPTION (Continued)

DR-01085

T

P

/

D

C

/

C

Pin No I/0 Designation Description

37, 36, 35, 33, I D0..D7 EPROM Data Lines

32, 31, 30, 29

9, 14, 19 I PS0, PS1, Program Select Inputs for Selecting

PS2 between 1 of 8 tone plans

7 O CLKDIV2 CLKIN divided by 2 output (i.e. 4096 kHz or 1024

kHz depending on CLK_SEL input)

40 I CLK_SEL Selects between CKLIN of 8192 or 2048 kHz and

Synchronisation source.

0 = 8192kHz/Internal

1 = 2048kHz/External

28 I TEST Used for IC testing purpose. Tied Low during

normal operation.

38 I MRST Asynchronous Reset Pin. Resets all Internal Flip

Flops (active low)

16 I WD_RST Watchdog reset input (Rising-edge triggered) Tied

high if unused

17 I WD_EN Watchdog enable input (active low) Tied high if

unused

18 O WD_INT Watchdog output (active low, tri-state)

SA9401

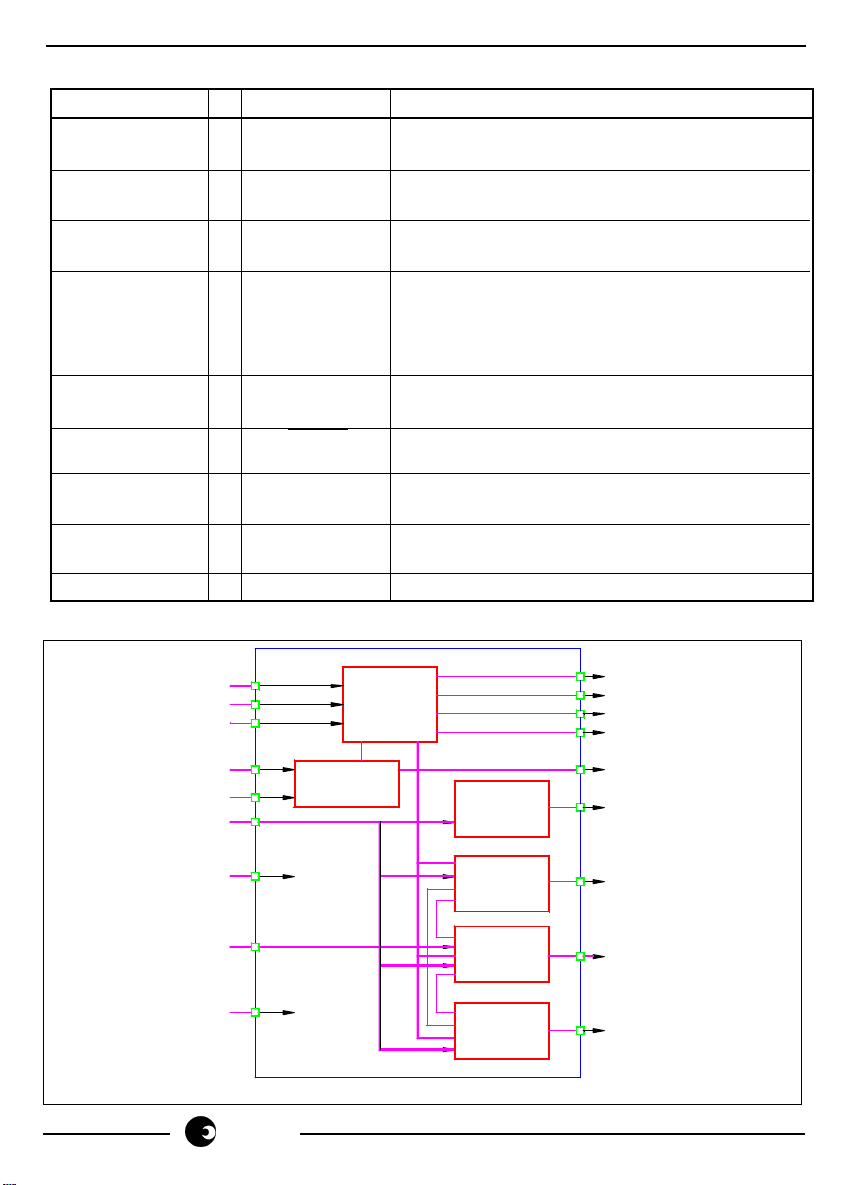

BLOCK DIAGRAM

MRST

LK_SEL

LKIN

WD_RST

WDENB

[7 : 0]

FS1

S[2 : 0]

EST

sames

SA9401

CLOCK

GENERATOR

WATCHDOG

TIMER

INTRUDE

TONE

GENERATOR

CADENCE

TIMER

EPROM

INTERFACE

PCM

INTERFACE

CLKDIV2

2MCLK

8KFS

PCMFSC

WD_INT

INTRFRQ

INTRCAD

A[13 : 0]

PCM_OU

3

SA9401

FUNCTIONAL DESCRIPTION

The design of the SA9401 has been based on the assumption that any supervisory tone

used in a PABX (e.g. Dial tone or Busy Tone etc) can be described by a small set of

simple parameters and that the tones will be injected into a standard PCM 30 (2048kHz)

backplane in either A-law or µ-law format.

In the SA9401 a tone is created by repeating a fundamental waveform (or one of two

waveforms) which would typically be one cycle of a sinewave or alternatively may be

several cycles of a higher frequency signal (say 400 to 1000Hz) modulated by a lower

frequency signal. This Tone may then be interrupted (“Cadenced”) so that the tone is

effectively switched on and off.

The waveform shape, number of samples per cycle and the cadence can all be set by

the system designer in accordance with the related National Standards.

Once a set of tones have been described they may then be injected into the PCM

backplane. The time slot associated with each tone can be set by the system designer.

The SA9401 accommodates up to 9 different Tones to form a Tone Plan making ample

allowance for Ring, Dial, Busy, Intrude and other Tones. The set of data describing one

Tone Plan (waveforms, cadence timings, timeslots etc) is referred to as a Program and

is stored in an external EPROM which is addressed directly by the SA9401.

Up to eight T one Plans may be stored and selected at will to accommodate products for

multi-national markets.

ARCHITECTURE

The architecture of the SA9401 consists of 6 functional blocks each of which is described in detail in the following sections. Refer also to the block diagram.

Clock Generator

The clock generator circuit derives all the timing for the ic from either a 2048kHz or a

8192kHz clock. The desired Clock is selected by the state of the CLK_SEL pin (1 for

2048kHz and 0 for 8192kHz).

The CLK_SEL pin also determines the function of the Frame Sync pin. If CLK_SEL is

low then Internal synchronisation is assumed and FS1 should be tied high. If CLK_SEL

is high then an external Frame Synchronisation source must be connected to /FS1.

The Clock Generator comprises 5 functional blocks.

A divide-by-4 counter is enabled only if a 8192kHz clock is selected so that all internal

timing is based on 2048kHz. The Time Slot Counter keeps track of the Time Slots (0

to 31) in the PCM Frame while the bit position (0 to 7) in each time-slot is tracked by the

Bit Position Counter. PCM frame synchronisation signals are controlled by the Frame

Generator. Long cadence intervals are accommodated by the Five-ms-Timebase

which delivers a 200Hz signal which clocks the Cadence Timers.

4

sames

SA9401

D

Intrude Tone Generator

This module generates a square wave output based on the master clock of 2048kHz.

The Intrude Tone frequency is determined by the contents of the 16-bit Intrude Tone

Register (INTR_LO and INTR_HI) according to the formula:-

f

= 2048kHz/(2*(n+1))

int

where n is the content of the INTR register.

The range of values in the register (from 0 to 65535) give Intrude tones in the range

15.625Hz to 1024kHz.

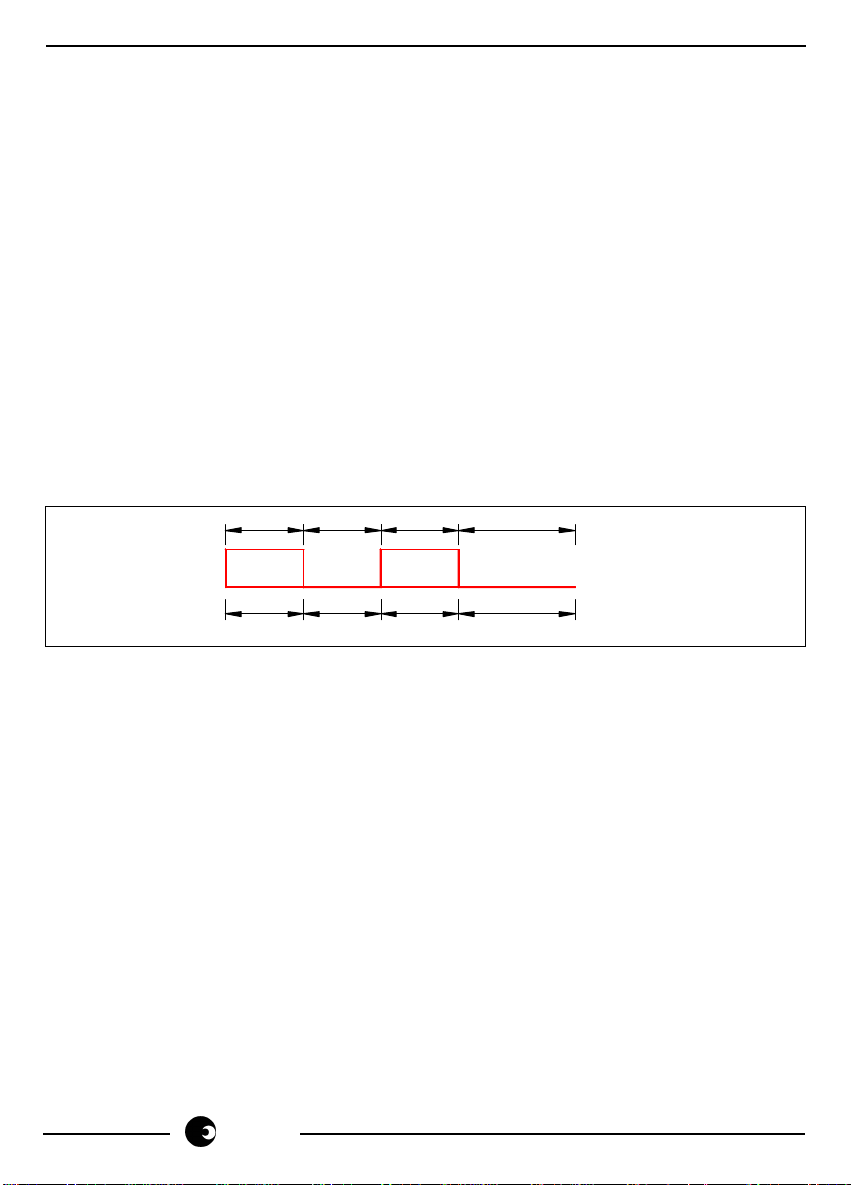

Cadence Timer

In any given Tone Plan the SA9401 assumes that any or all of the 9 (8 PCM tone

streams and one squarewave Intrude Tone) tones are required to have their own independently defined cadence. A typical cadence is illustrated in FIGURE 1 above. Each

tone is assumed to comprise up to 4 cadence periods which repeat cyclically. The

duration of each period is controlled by the Cadence Timers which in turn comprise 10-

bit Counters. These timers are clocked by the five_ms_timebase generated by the

Clock Generator so that intervals of up to 5.12 seconds can be defined with a resolution

of 5ms. (10 bits => 1023: 1023*5ms = 5115ms)

ON

OFF

OFF

TONE_n_A

CADO_n

R-01086

CAD1_nONCAD2_n

TONE_n_B

CAD3_n

FIGURE 1: TONE CADENCING

The Cadence Controller controls the loading of the 10-bit counter and the sequencing

of the Cadence Position Counter. The duration of each period of the tone is denoted by

the parameter:-

CADm_n_LO = Period m, Tone stream n low-order 8 bits and

CADm_n_HI = Period m, Tone stream n high-order 2 bits

where0 ≤ m ≤ 3 and 0 ≤ n ≤ 8 (8 = Intrude Tone)

The Cadence Position Counter keeps track of the period being generated and during

period 0 the SA9401 generates a tone based on one Tone Block (A) while during the

period 2 (if used) the samples from another Block (B) are used. During periods 1 and 3

the silence sample is transmitted. This feature allows the sound of the tone to be

altered along with the cadence.

A continuous tone is created by loading values of 1(or any non-zero value),0,0,0 into

the registers CAD0_n to CAD3_n respectively. The zero value is interpreted by the

SA9401 as an instruction to ignore the period and to process the next one. With the

register contents shown the Cadence Controller continuously processes the first (ON)

period.

sames

5

Loading...

Loading...