SAMES SA2531 Datasheet

SA2531 A/B/C/E/G/U

sames

VERSATILE SINGLE CHIP TELEPHONE

WITH 14 NUMBER REPERTORY DIALLER

FEATURES

■ Speech circuit, LD/MF Repertory Dialler

and Tone Ringer on one 28 pin CMOS

chip

■ Net 4 compatible

■ Soft clip to avoid harsh distortion

■ Line Loss Compensation selectable by

pin option

■ Power down mode

■ Versatile applications for different PTT

demands

■ 31 digit last number redial

■ Sliding Cursor protocol with comparison

■ 2 Flash keys, 100 ms and 280 ms (option

600 ms)

■ Ring frequency discrimination

SA2531 A/B/C/D/E/F/G/J/U

■ Operating range from 13 to 100 mA

(down to 5 mA with reduced performance)

■ Volume control of receive signalExcept

"D")

■ Low noise (max. -72dBmp)

■ Real or Complex impedance on chip pro-

grammable

■ LD/MF switchable dialling

■ 14 memories, 4 direct/10 indirect or 10

direct

■ Pause key for 2, 3 or 6 sec Auto Pause or

Wait function

■ On chip MF filter (CEPT CS 203 compat-

ible)

■ 3-tone melody generator

GENERAL DESCRIPTION

The SA2531 is a CMOS integrated circuit that contains all the functions needed to form a high

performance electronic telephone.

The device incorporates LD/MF repertory dialling, melody generation, ring frequency

discrimination and a high quality speech circuit.

A RAM is on chip for a 31 digit last number redial and 14 memories each containing up to 21

digits. The sliding cursor procedure makes Last Number Redial easy behind a PABX.

The SA2531 (exept the SA2531D) incorporates a volume control for the earpiece. The receive

volume can be controlled by the VOL key (+4dB) or by the +/- keys (+6dB/-4dB in 5 steps).

The versatility of the circuit is provided by on chip programmability and a few external

components. This allows easy adaption to different PTT requirements without changing the

PCB of the telephone.

sames

M82-2013 PDS039-SA2531-001 Rev.D 15-05-97

1/24

SA2531 A/B/C/E/G/U

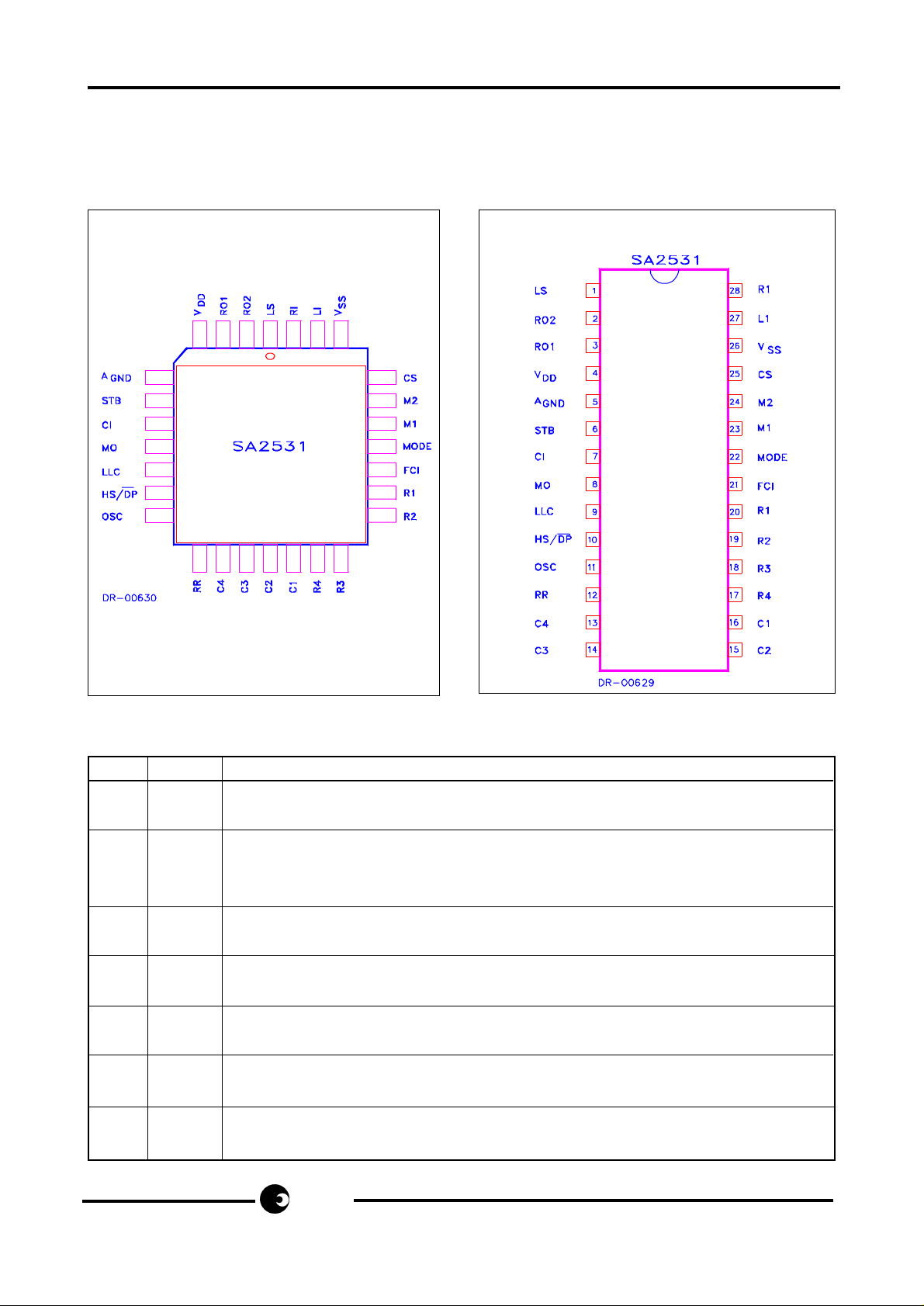

PACKAGE

Available in 28 pin DIP and PLCC

PIN CONFIGURATIONS

28 Pin PLCC

28 Pin DIP

PIN DESCRIPTION

Pin# Symbol Function

23 M1 Microphone Inputs

24 M2 Differential inputs for the microphone (electret).

3 RO1 Receiver Outputs

2 RO2 These are the outputs for driving a dynamic earpiece with an impedance

of 150 to 300Ω

5A

GND

Analogue Ground

This is the analog ground for the amplifiers.

28 RI Receive Input

This is the input for the receive signal.

6 STB Side Tone Balance Input

This is the input for side tone cancellation.

1LS Line Current Sense Input

This is the input for sensing the line current.

27 LI Line Input

This input is used for power extraction and line current sensing.

2/24

sames

Pin# Symbol Function

25 CS Current Shunt Control Output

This N-channel open drain output controls the external high power shunt

transistor for the modulation of the line voltage and for shorting the line

during make period of pulse dialling.

4V

DD

Positive Voltage Supply

This is the supply pin for the circuit.

26 V

SS

Negative Power Supply

8MOMelody Output

Pulse Density Modulated output of the melody generator for tone ringer. At

high impedance when not active.

21 FCI Frequency Comparator Input

This is a Schmitt trigger input for ring frequency discrimination. Disabled

during off-hook.

10 HS/DP Hook Switch Input and Dial Pulse Output

This is an I/O that is pulled high by the hook switch when off- hook. An open

drain pulls it low during break periods of pulse dialling and flash.

11 OSC Oscillator Input

Oscillator pin for Xtal or ceramic resonator (3.58 MHz). Recommended part

is the Murata CSA3.5MG312AM.

9 LLC Line Loss Compensation

Select pin for the loss compensation.

OPEN = None V

= 45-75mA VDD = 20-50mA

DD

12 RR Repetition Rate

Select pin for repetition rate of melody for the Tone rinser.

22 MODE Signalling Mode Select Input

Mode pin Function

High LD mode, 10pps, M:B = 33:66 (J:20pps)

Open MFonly

Low LD mode, 10pps, M:B = 40:60 (J:20pps, M:B = 33:66)

SA2531 A/B/C/E/G/U

20 R1 Keyboard Rows

19 R2

18 R3

17 R4

16 C1 Keyboard Columns

15 C2

14 C3

13 C4

7CI Complex Impedance Input

Input pin for the capacitor in the complex impedance

sames

3/24

SA2531 A/B/C/E/G/U

FUNCTIONAL DESCRIPTION

Power On Reset

The on chip power on reset circuit monitors the supply voltage (VDD). When VDD rises above

approx. 1.2V, a power on reset occurs to assure correct start-up and the RAM is cleared.

DC Conditions

The normal operating range is from 13mA to 100 mA. Operating range with reduced

performance is from 5mA to 13mA. In the operating range all functions are operational.

At line currents below 13mA the SA2531 provided an additional scope below 4.5V to allow

parallel operation. (See Figure 12).

The dc characteristic (excluding diode bridge and Pulsing transistors) is determined by the

voltage at LI and the resistor R1 as follows:

VLS = VLI + I

Line

.R1

The voltage at LI is 4.5V.

During pulse dialling the speech circuit and other parts of the device not required are in a

power down mode to save current. The CS pin is pulled to V

in order to turn the external

SS

shunt transistor on to keep a low voltage drop at the LS pin during make periods.

AC Impedance

The Characteristic or Output impedance of the SA2531 is set within the IC and adjusted by

Mask Options. Available options are for 600Ω and 1000Ω. When the 1000Ω option is selected

then a capacitor may be added to the circuit at pin CI to add a reactive element and make the

output impedance complex.

Oscillator

All the Timing Functions of the SA2531 are based on a Clock Frequency of 3.58MHz. A crystal

or ceramic resonator of this frequency should be connected to the OSC pin. In practise minor

deviations from the nominal frequency may occur due to the characteristics of the frequency

reference device used and so it is recommended that care is taken in the selection of

components.

Typically a small value capacitor ( ≤47pF) should be connected in parallel with the Frequency

Reference to ensure start-up and/or operation at the nominal frequency.

Speech Circuit

The speech circuit consists of a transmit and a receive path born with soft clip, mute, line loss

compensation and side tone cancellation.

Transmit

The gain of the transmit from M1/M2 to LS is 35dB for 600Ω versions and 37dB for 1000Ω

versions (see test circuit figure 5). The microphone input is differential with an input

impedance of 25 kΩ.

The soft clip circuit limits the output voltage at LI to 2.0V

(see figures 8 & 9). The attack

PEAK

time is 30µs/6dB and the decay time is 20 ms/6 dB. When mute is active, during dialling

4/24

sames

SA2531 A/B/C/E/G/U

or after pressing the MUTE key, the gain is reduced by > 60 dB.

Receive

The receive input is the differential signal of RI and STB. The gain of the receive path

is 2 dB (test circuit figure 5) with differential outputs, RO1/RO2 (0dB on 1000Ω versions).

When mute is active during dialling the gain is reduced by > 60dB. During DTMF dialling

a MF comfort tone is applied to the receiver. The comfort tone is the DTMF signal with

a level that is -30dB relative to the line signal.

The receive gain can be adjusted under user control by using the volume control keys (not

on SA2531D). The VOL key gives a 4dB increase or returns the gain to normal in a Toggle

Function. Alternatively the + and - keys may be used. The + key increases the gain to

a maximum of +6dB while the - key reduces the gain to a minimum of -4dB. Each press

of the keys changes the gain by approximately 2dB.

The gain is reset by the next on-hook.

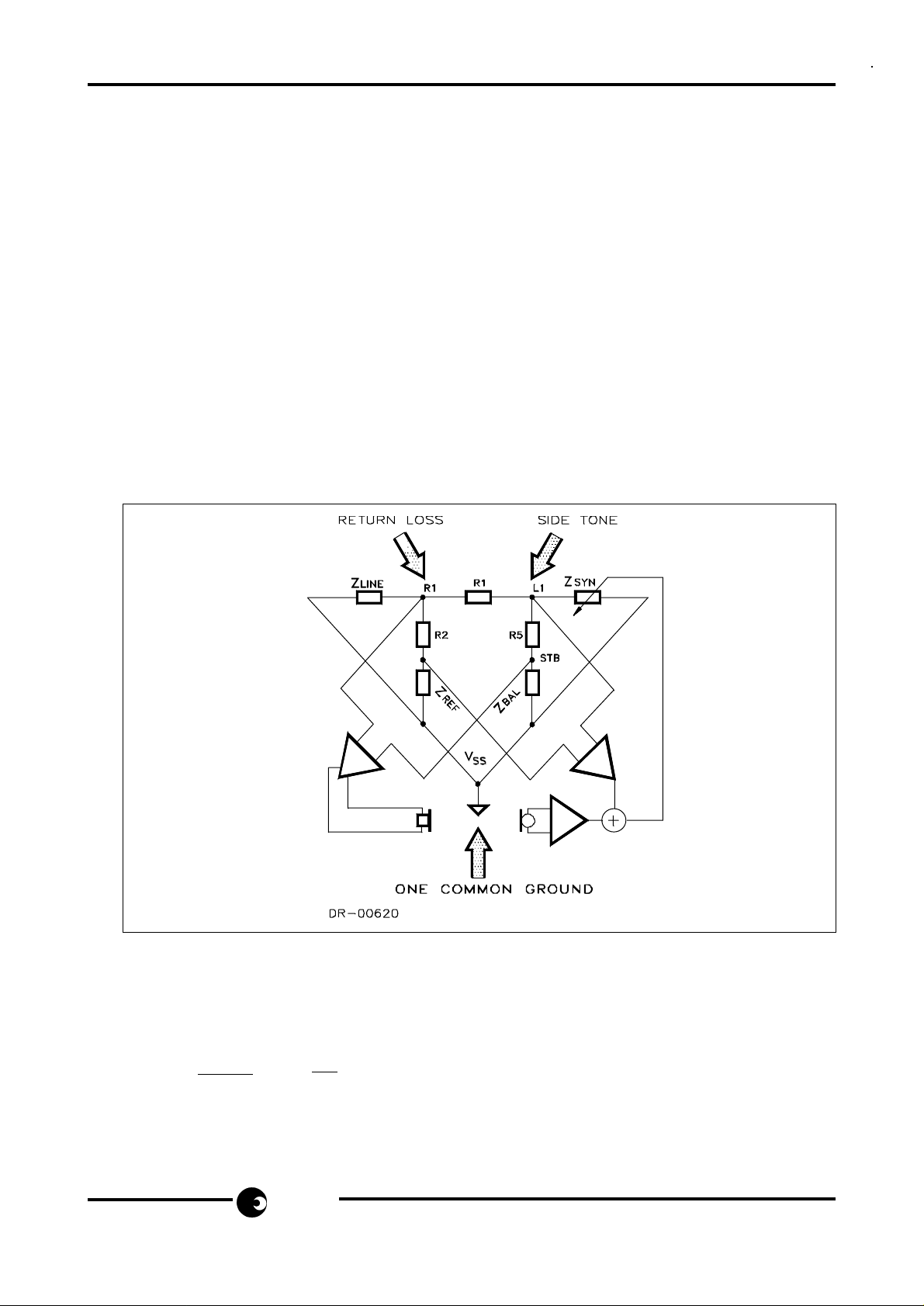

Side Tone

Side Tone is controlled along with Return Loss by a Double Balance Bridge as shown in

Fig. 1.

Figure 1

Double balance bridge (return loss and side tone) with one common ground

A good side tone cancellation is achieved by using the following equation:

ZBAL = R5

ZLINE R1

sames

5/24

SA2531 A/B/C/E/G/U

The side tone cancellation signal is applied to the STB input.

Line Loss Compensation

When Line Loss Compensation is active the gain of the Transmit and Receive amplifiers

are changed by 6dB in accordance with the DC conditions as measured at Pins LI and

LS. When the LLC Pin is Low this adjustment in gain occurs over the range I

50 mA. When LLC is High the range is 45 to 75mA. Note that these figures apply for R1

= R30Ω.

When the LLC Pin is open the amplifier gains remain fixed regardless of the Line Current

(see figures 6 & 7).

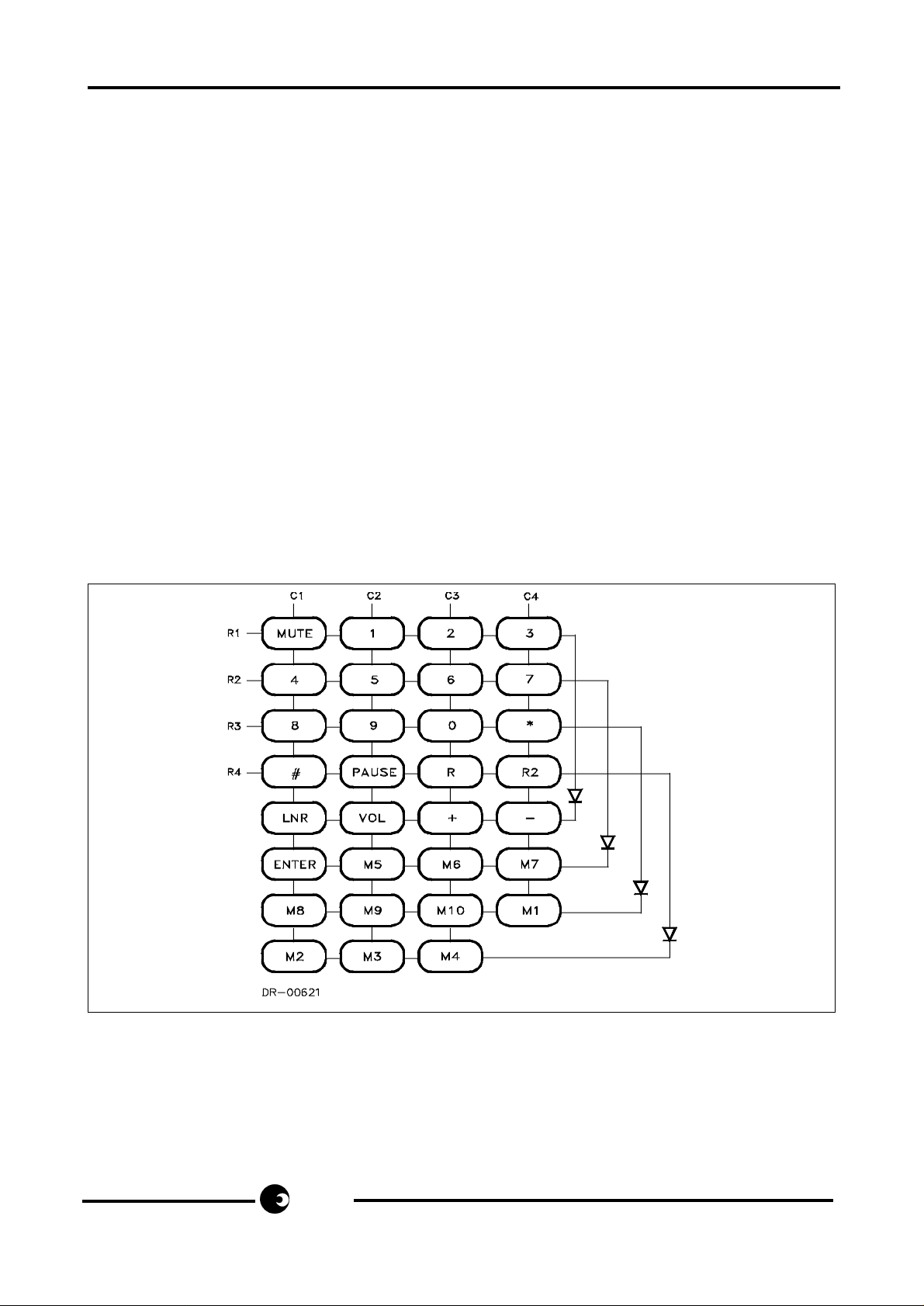

Dialling Functions

Valid Keys

The keypad of the SA2531 comprises a maximum of 32 keys some of which are provided

to cater for options (such as the two Recall/Flash periods). A Bi-polar scan technique is

used so that the 32 keys are scanned in a 4 x 8 matrix using only 8 pins. Two explanatory

keypad arrangements are illustrated in Figures 2 & 3.

= 20 to

LINE

A valid key is detected when one and only one contact closure is detected between a Row

and Column Pin. Key contacts are debounced to avoid incorrect detection.

It is also possible to drive the keypad inputs with a micro controller.

Dial Mode Selection

The default mode (LD or MF) can be selected by the Mode pin. When default LD mode

is selected, a temporary change to MF can be invoked by pressing the * key. The circuit

will revert to LD by pressing the R (or R2) key or by next on-hook.

When MF mode is selected by the mode pin, the circuit can not be changed temporary

to LD but will remain in MF.

Last Number Redial

LNR is a facility that allows resignalling of the last manually dialled number without keying

in all the digits again. The LNR is repeatable.

The current contents of the RAM are overwritten by new entries.

A manually entered number is automatically stored in the LNR RAM. The capacity of the

RAM is 31 digits. If a number greater than 31 digits is entered, the LNR facility will be

inhibited (Until new entries < 32 digits) and further entries will be buffered in a First In First

Out Memory (FIFO).

6/24

sames

SA2531 A/B/C/E/G/U

Post dialled digits, i.e. digits manually entered after LNR has been invoked, are not stored

in RAM but buffered in FIFO.

Pauses can be inserted by pressing the PAUSE key. (Further details of the Pause

Function are included in the Memory Keys section.)

Recall Function

A Recall (R key or R2 key) activation will invoke a Flash (Timed Loop Break).

If Recall is the first entry in a digit string, it will be stored in LNR RAM when digit(s) are

entered after the Recall.

If the recall key is depressed after a digit string has been entered or dialled out, the recall

will not be stored but buffered in the FIFO together with subsequently entered digits.

If pressing the recall key is not followed by digit entries, the LNR RAM remains intact.

After a recall a pause of 27ums or 3 seconds will automatically be executed.

On versions C/C/E/G a recall cannot be executed in LD mode.

Memory Keys

The keys M1 to M10 are direct memory access keys and the MEM key is used for indirect

or abbreviated dialling.

In the on chip RAM, 14 numbers can be stored. Each number can contain up to 21 digits

(including pauses).

During programming multiple pauses can be inserted by pressing the PAUSE key or the

LNR key. Each pause is 3 seconds (optionally 6 or 2 seconds) when inserted within the

first 5 digits otherwise a wait function that will halt dialling until the PAUSE key or the LNR

key is depressed.

Memory dialling is cascadable. However, the content of one memory must be dialled out

before a new one can be invoked.

Mute Function

The MUTE key is enabled in speech mode only. Depressing the MUTE key mutes the

microphone amplifier. Repressing the MUTE key deactivates the mute (toggle function).

Any key entry overwrites a mute activated by the MUTE key and mute will be deactivated.

When privacy mute is activated a reminder tone is applied to the earpiece.

Sliding Cursor Procedure

To accommodate easy and uncomplicated redialling (LNR) behind a PABX, a sliding

cursor protocol is implemented. If new entries match the previous RAM contents, pressing

the LNR key will dial out the remaining digits.

If there is an error in matching, the LNR will be inhibited until next on-hook, and the RAM

will contain the new number.

sames

7/24

SA2531 A/B/C/E/G/U

Tone Generator

The tone generator incorporates the DTMF tones and 3 basic frequencies for the tone

ringer.

DTMF Tones

The DTMF Tone Generator creates 12 Tones in compliance with CCITT Recommendation Q23. Signal levels are altered by Mask Option. High group frequencies have a level

2.6dB higher than those of the Low Group.

Details of the DTMF Tones are:

Low group

Digit 1-2-3 697Hz (Error = -.074%)

Digit 4-5-6 770Hz (Error = -.679%

Digit 7-8-9 852Hz (Error = -.621%)

Digit *-0-# 941Hz (Error = +.139%)

High group

Digit 1-4-7-* 1209Hz (Error = +.533%)

KEYBORD ARRANGEMENT 1

10 Direct memories (either VOL or +/- keys)

8/24

Figure 2

sames

Loading...

Loading...