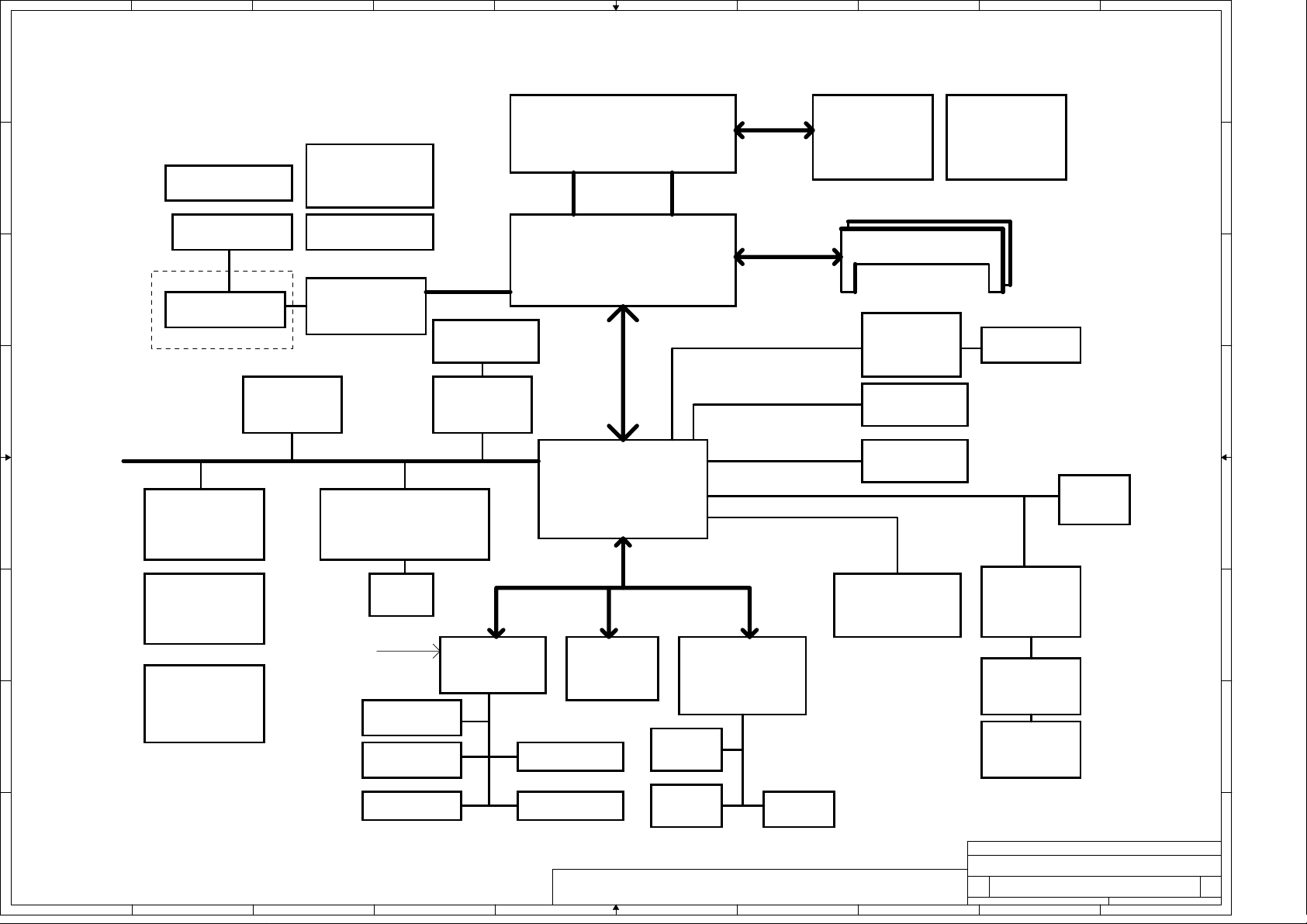

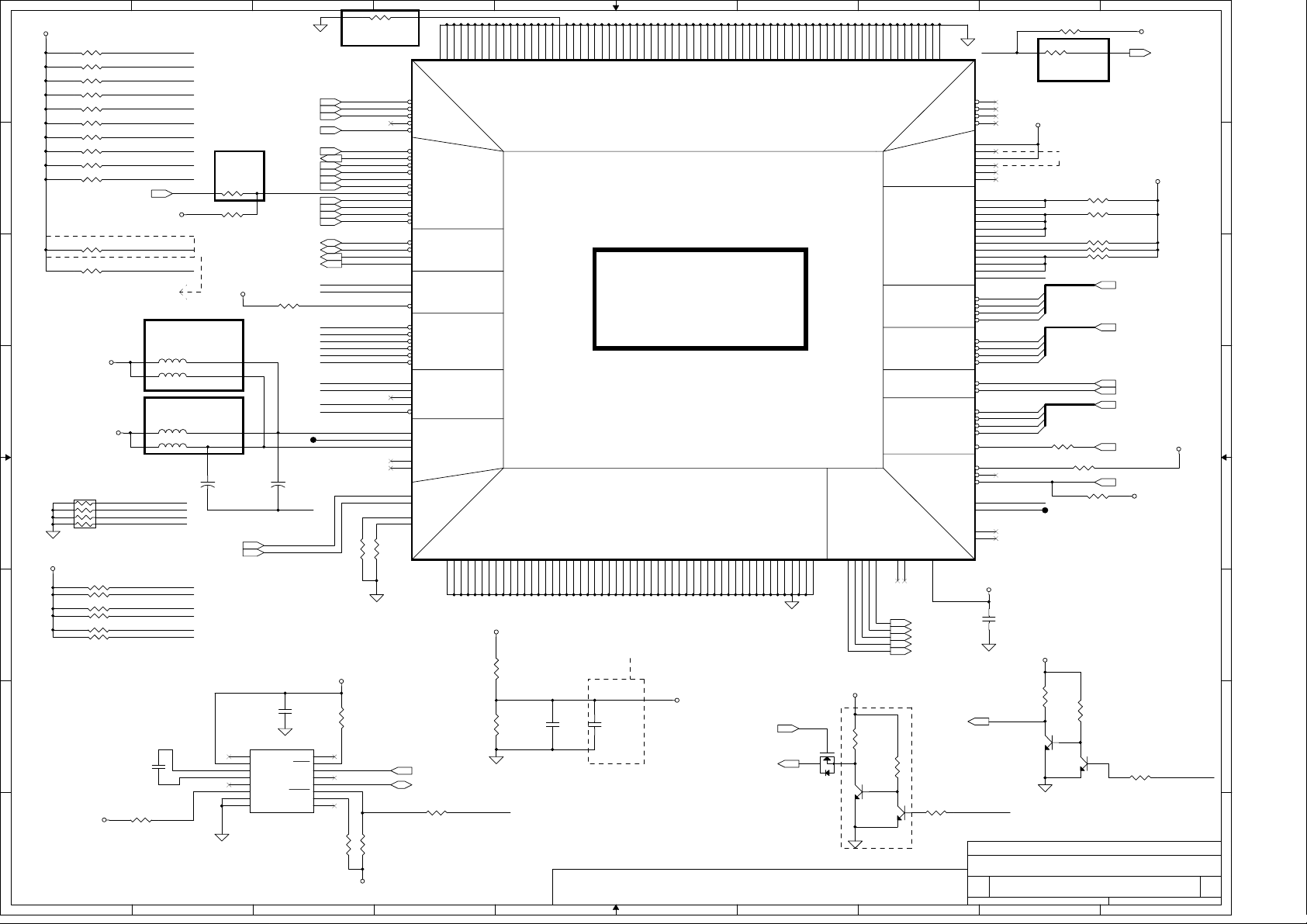

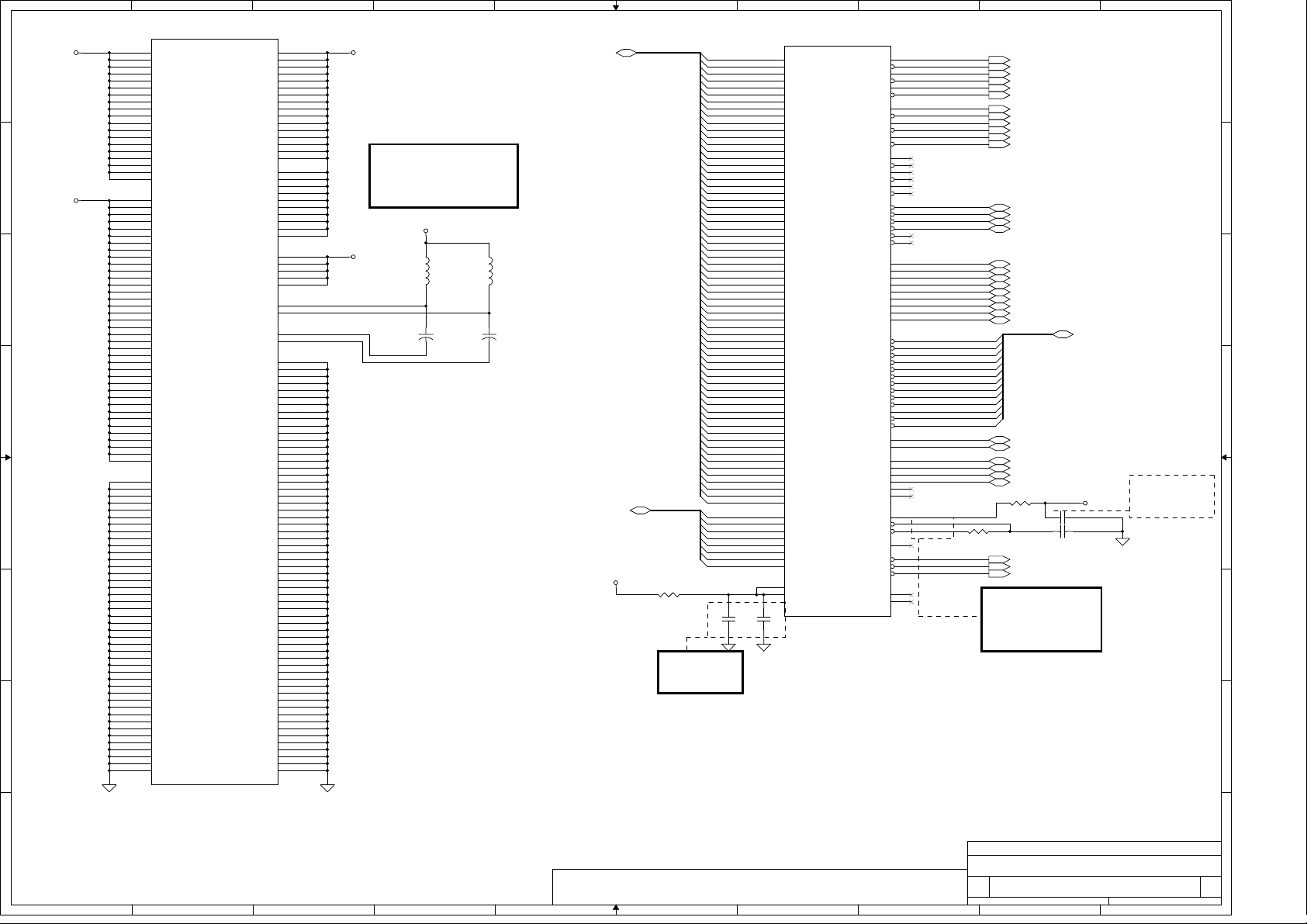

RoverBook LA-1381 APL11, Voyager H570L, PL11 Schematic

A

1 1

2 2

3 3

B

C

D

E

F

G

H

I

J

4 4

LA-1381 REV0.5 Schematics Document

uFCBGA/uFCPGA Northwood with

5 5

6 6

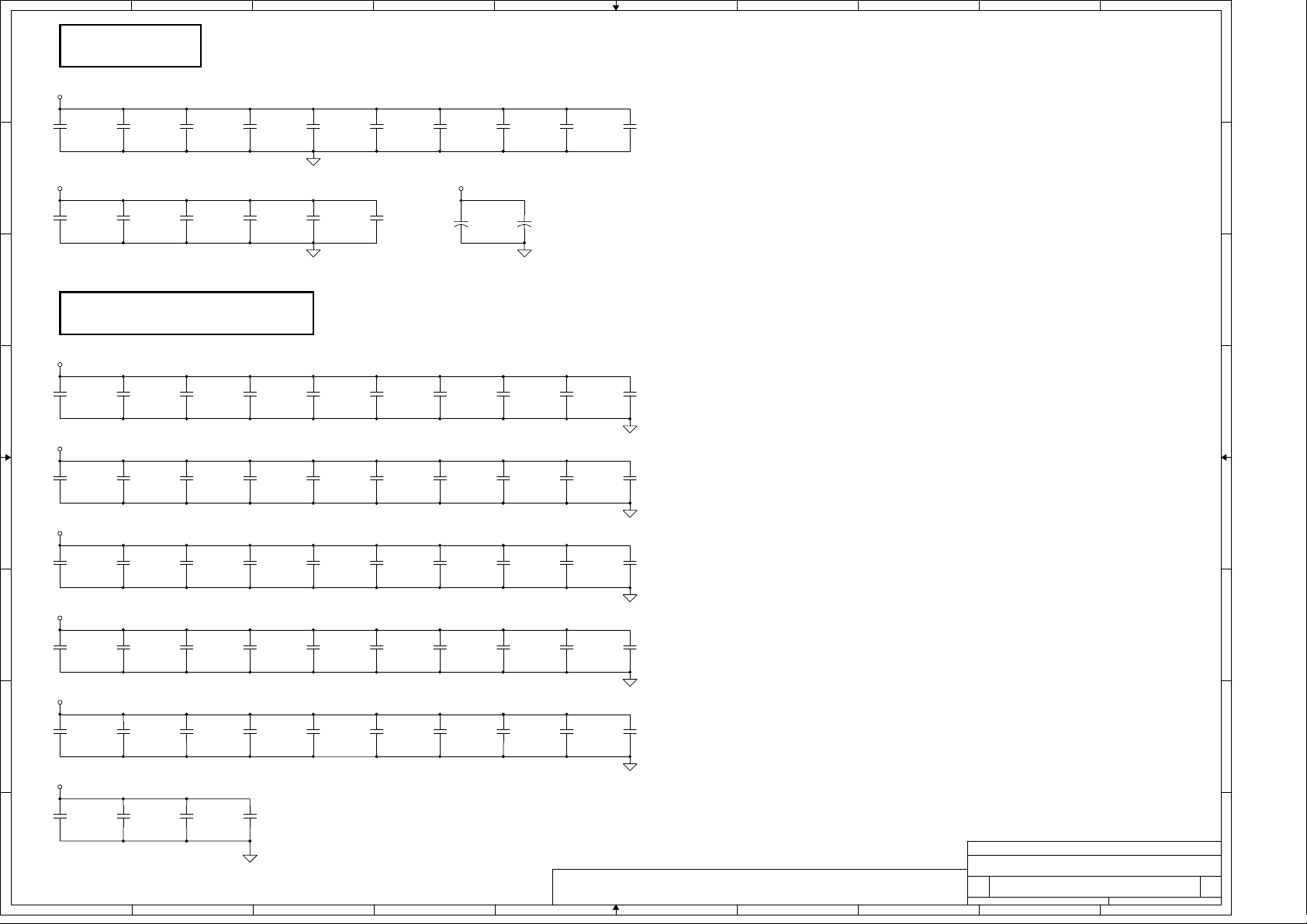

BOM 記號

DT@ SKU W/Desktop CPU 要打

M@ SKU W/Mobile CPU 要打

7 7

LAN@ SKU W/LAN 要打

1394@ SKU W/1394 controller 要打

S@ SKU W/TVOUT 要打

FIR@ SKU W/FIR module 要打

MDC@ SKU W/MODEM module 要打

DK@ SKU W/DOCKING 要打

SD@ SKU W/SD CARD 要打

8 8

BT@ SKU W/Bluetooth module 要打

MLED@ SKU Media LED supper 要打

SUB@ SKU W/SUBWOOFER要打

A

Brookdale chipset(845MP/MZ+ICH3-M)

PCB Layer

Structure:

TOP

GND1

IN1

IN2

VCC

IN3

GND2

BOT

B

C

D

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

F

G

H

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

Date: Sheet

?30, 2002

I

of

146,

J

2B

A

B

C

D

E

F

G

H

I

J

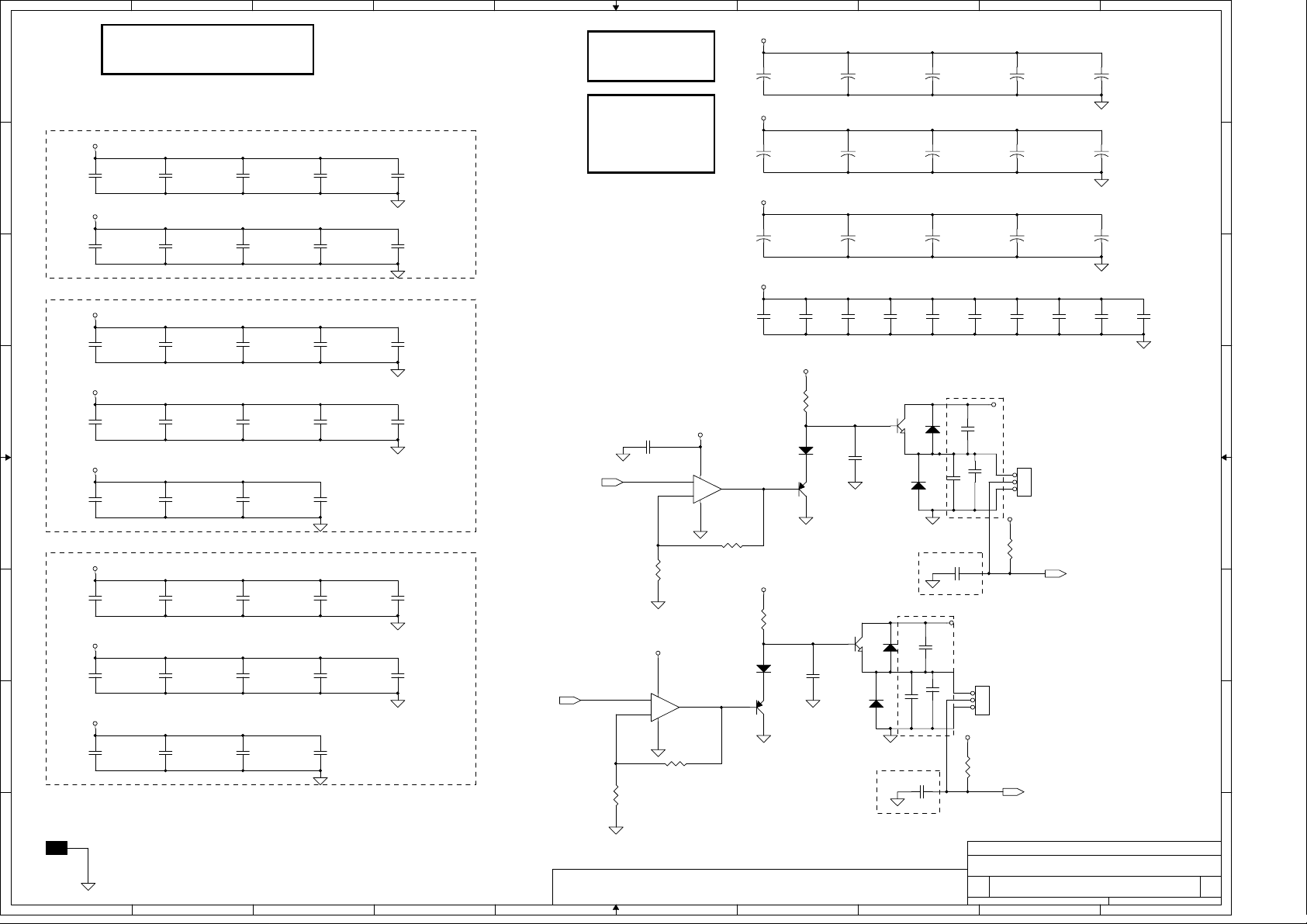

Compal confidential

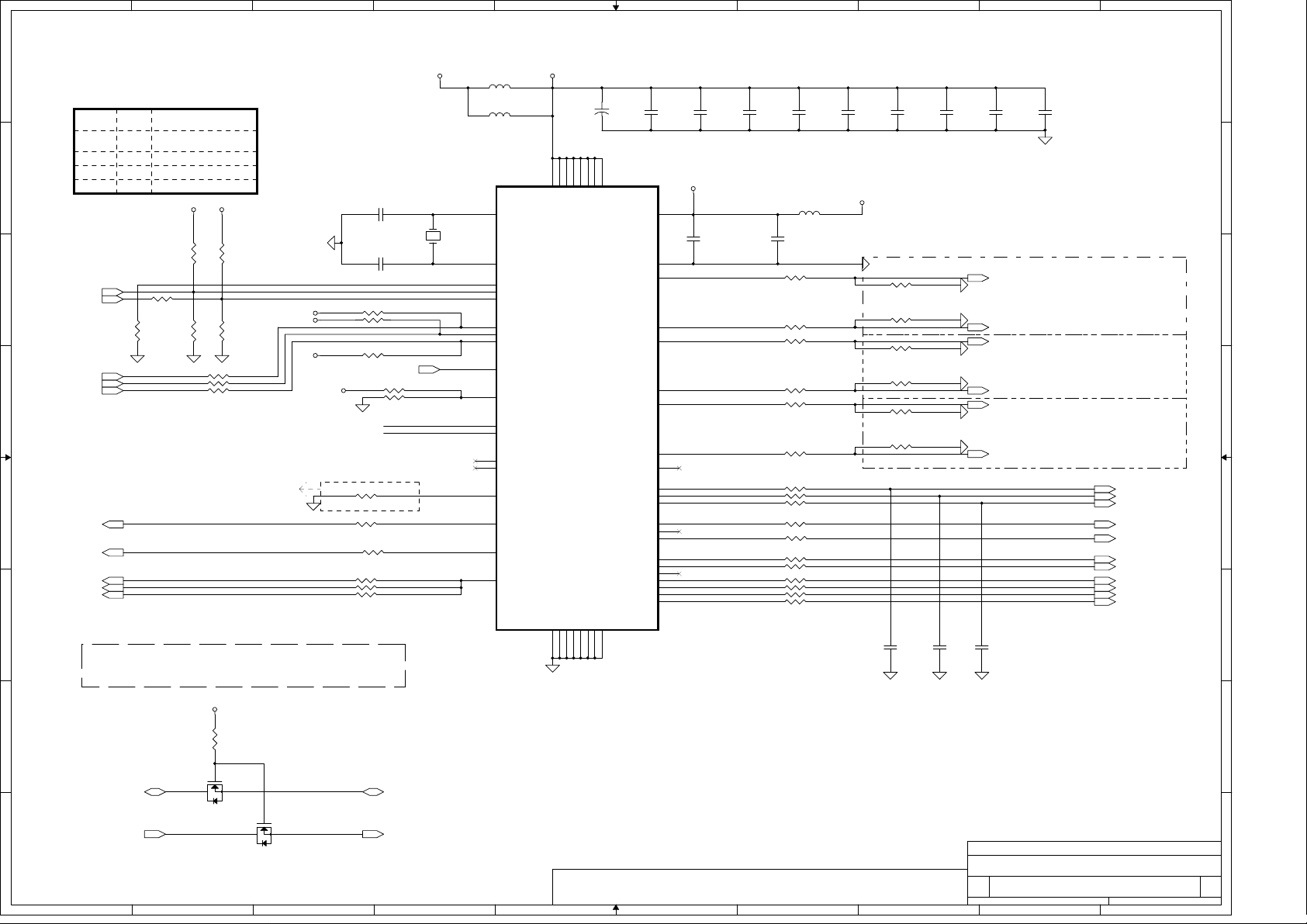

Model Name :APL11

File Name : LA-1381

1 1

Mobil e Nort hwood

uFCBGA/ uFC PGA CPU

2 2

3 3

Fan Cont rol

CRT Connector

page 6

page 15

VGA

Board

& CPUVID

LM75 thermal

sensor

AGP Conn

page 15

page 6

AGP4X(1.5V)

System Bus

400MHz

Brookdale-M

MCH-M

625 BGA

USB2.0 conn X 2

page 32

HUB Link

CPU B ypass

4 4

Mini PCI

Conn.

page 36

VIA_ VT 6202

USB2.0

page 26

PCI BUS

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

5 5

TI TSB43AB22

1394

page 25

DC/DC Interface

Suspend

6 6

page 37

CardBus Controller

PCI 1410

Slot 0

page 24

14M_5V

Power Circuit

DC/DC

page

38,39,40,41,42,43,44,45

7 7

Touch Pad

EC Ext. I/O

3.3V 33MHz

page 23

EC 87591

page 30

page 29

page 31

1.8V 266MHz

LPC BUS

3.3V 33MHz

Int.KBD

ICH3-M

421 BGA

SD/MS CARD

page 27

page 33

page 4,5

HD#(0..63)HA#( 3..31)

page 8,9

page 16,17

LPT

Port.

page 29

Memory

BUS(DDR)

2.5V 200MHz

LAN interface

USB interface

3.3V 48MHz

3.3V 24.57 6MHz

3.3V ATA100

SMsC

LPC47N227

page 28

Therm al Sensor

MAX6654 W320-04

page 5

SO-DIMM X2

BANK 0, 1, 2, 3

LAN

Kinnereth

Blu etooth

USB conn X1

IDE Connector

(HDD/CR-ROM)

page 19

Clock Generator

page 11,12

page 20

page 32

page 32

page 14

RJ45

page 20

AC-LINK

AC97

Codec

ALC202

page 21

AMP& Phone

Jack

page 22

SUB WOOFER

page 37

MDC

page 32

BIOS

page 31 page 29

8 8

A

B

C

D

PS/2 conn

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

FIR

page 29

F

FDD

page 19

G

Compal Electronics, Inc.

Title

SCHEM AT IC , M/ B LA- 1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

H

Date: Sheet

?30, 2002

I

246,

2B

of

J

10

9

8

7

6

5

4

3

2

1

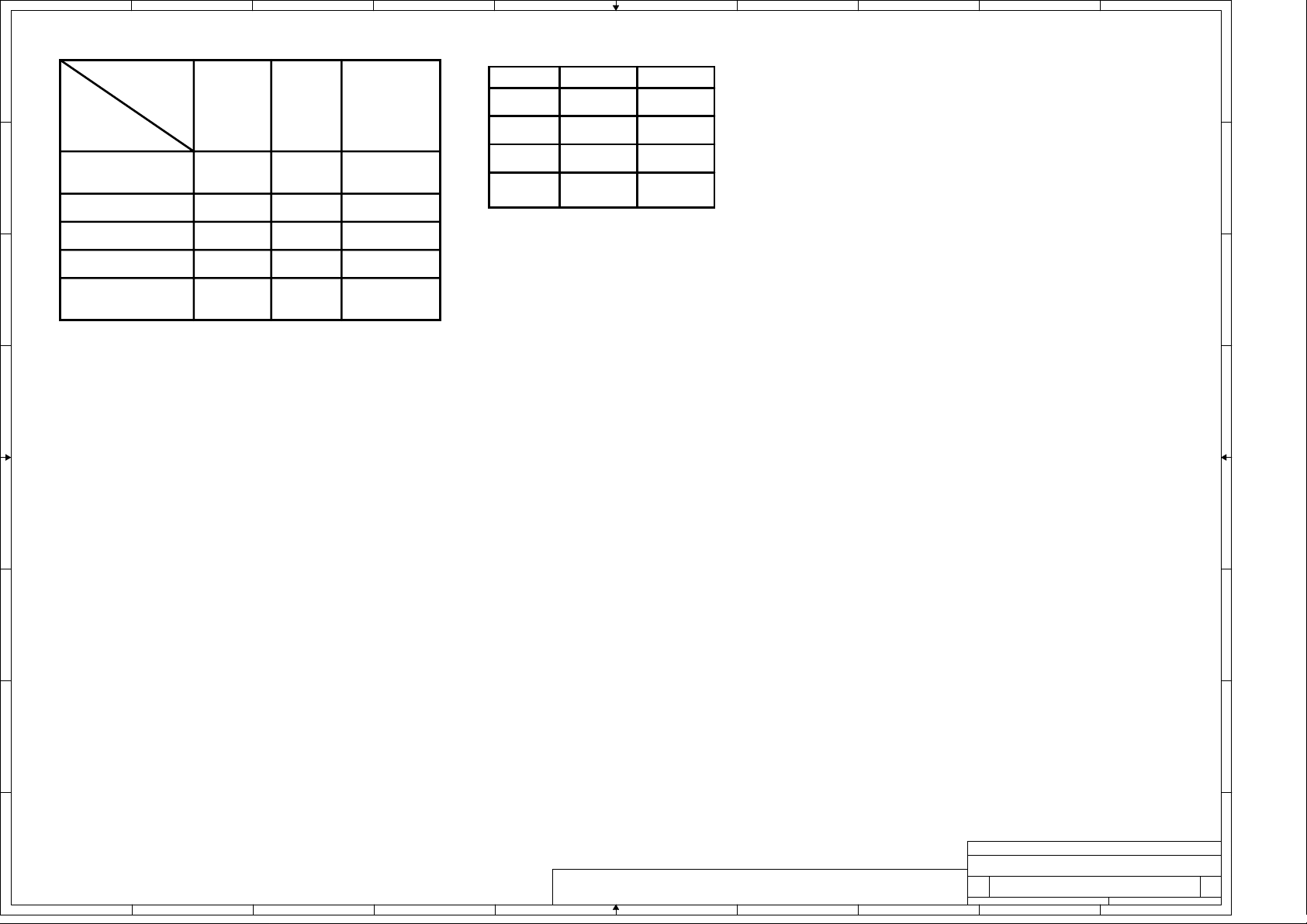

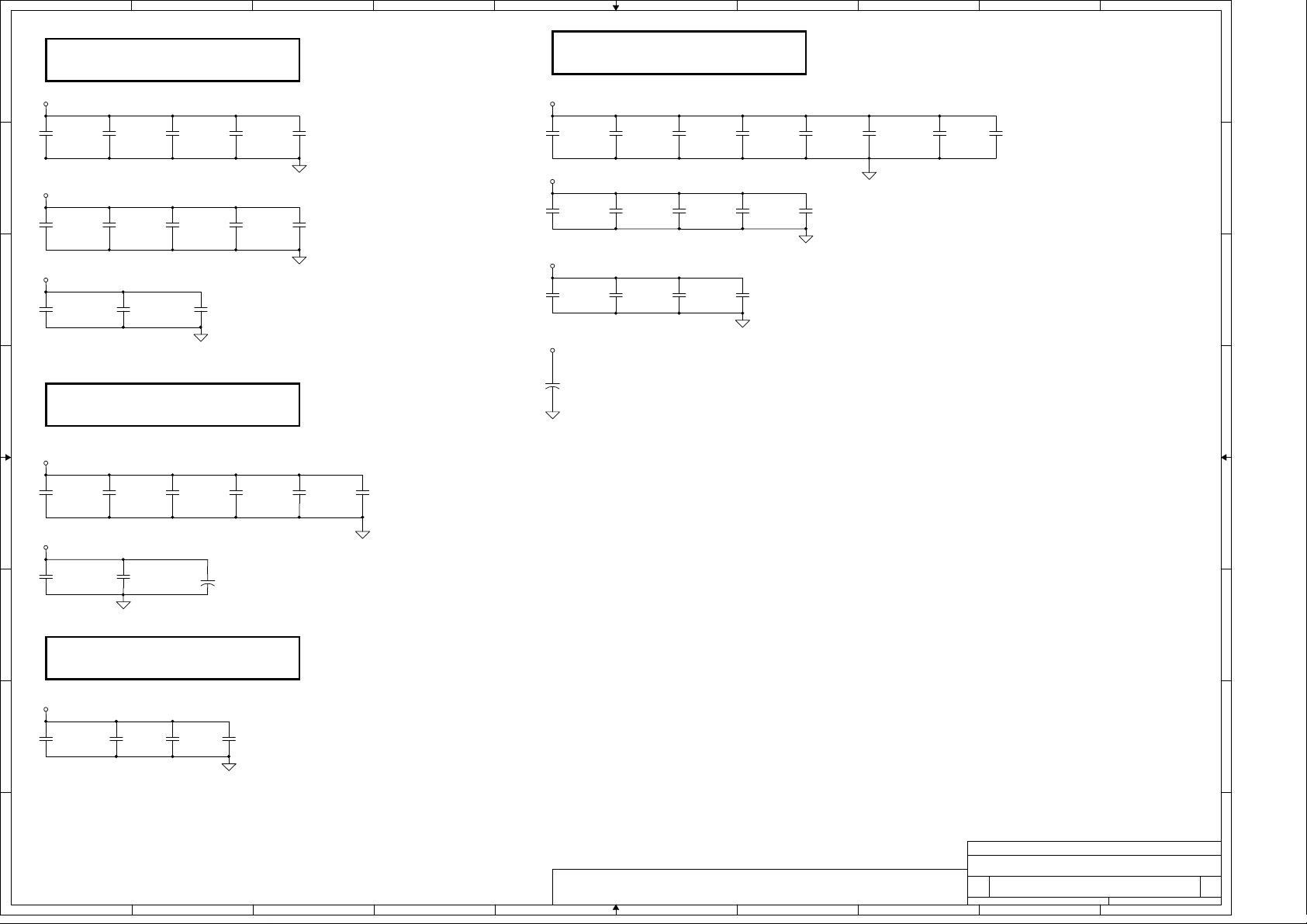

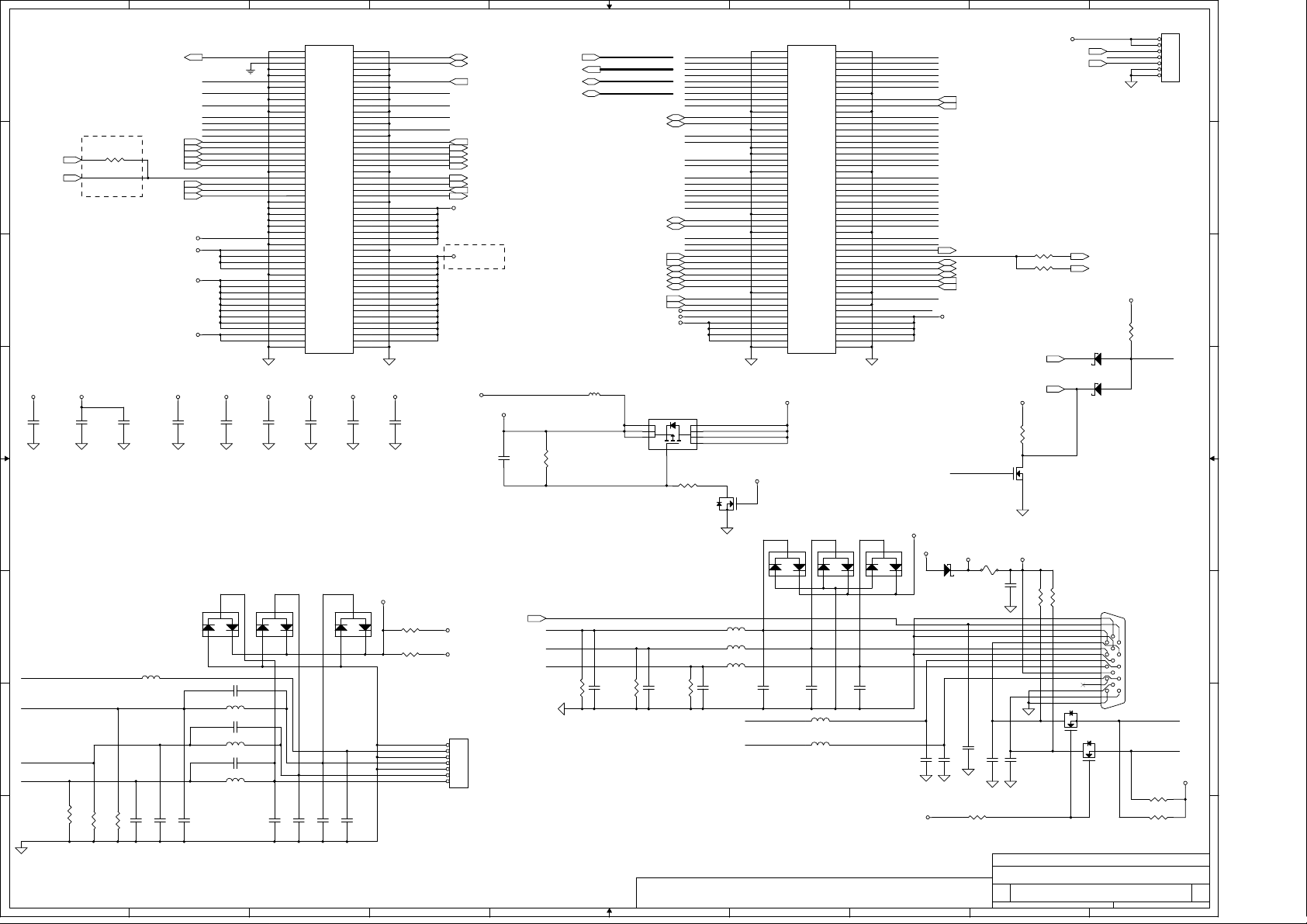

Power Managment table

H H

State

Signal

+3VALW

+5VALW

+1.8VALW

+3V

+5V

+2.5V

+12VALW

G G

S0

S1

ON

ON ON ON

ON ON

+3VS

+5VS

+1.8VS

+1.5VS

+1.2VP

+CPU_CORE

+1.25V

NB Chip Rev SB Chip Rev

S3

S5 S4/AC

F F

E E

D D

C C

S5 S4/AC don't exist

ON ON

ON OFF

OFF OFF OFF

OFF

OFF

B B

A A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

10

9

8

7

6

5

4

3

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

Date: Sheet

?30, 2002

2

of

346,

1

2B

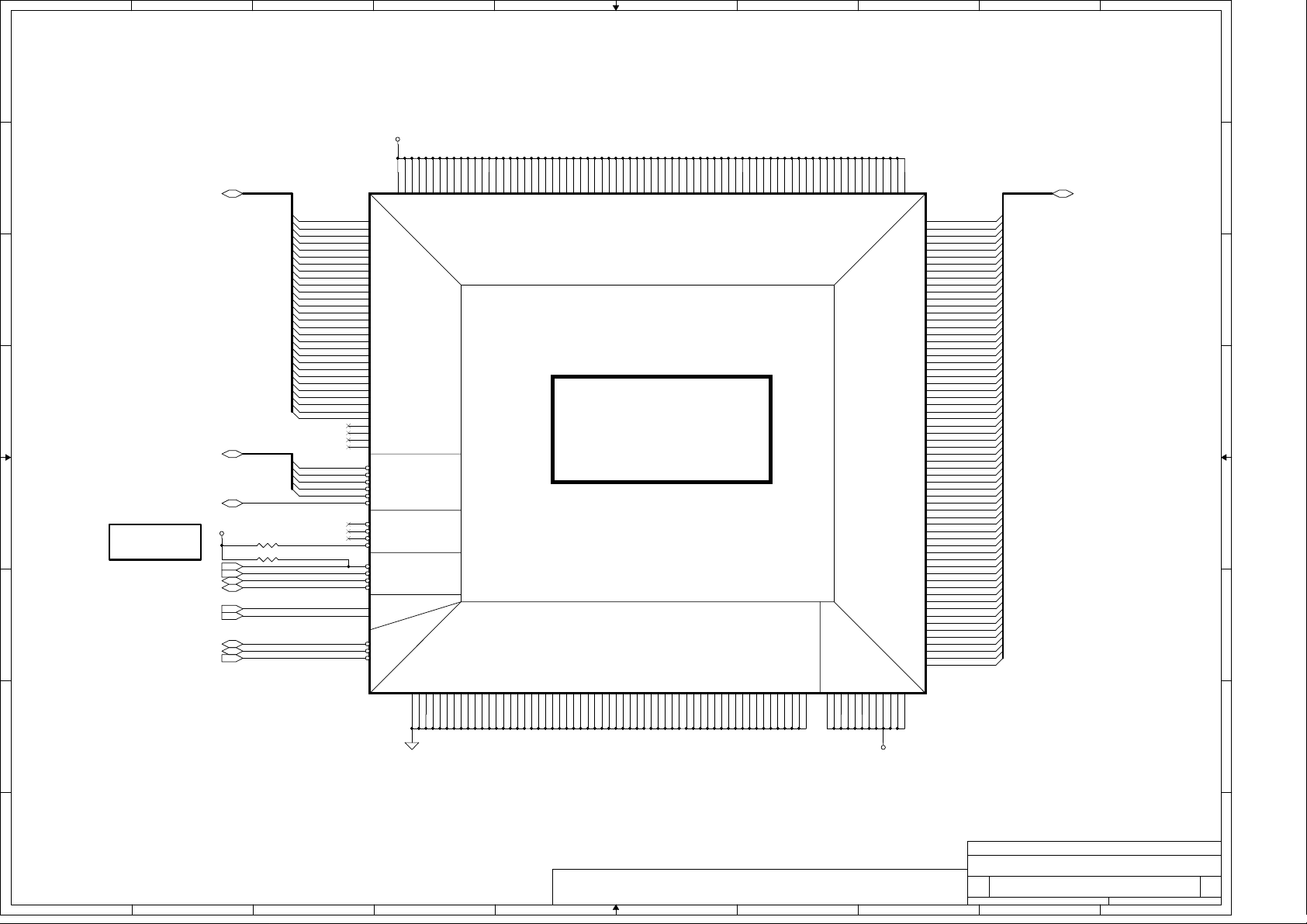

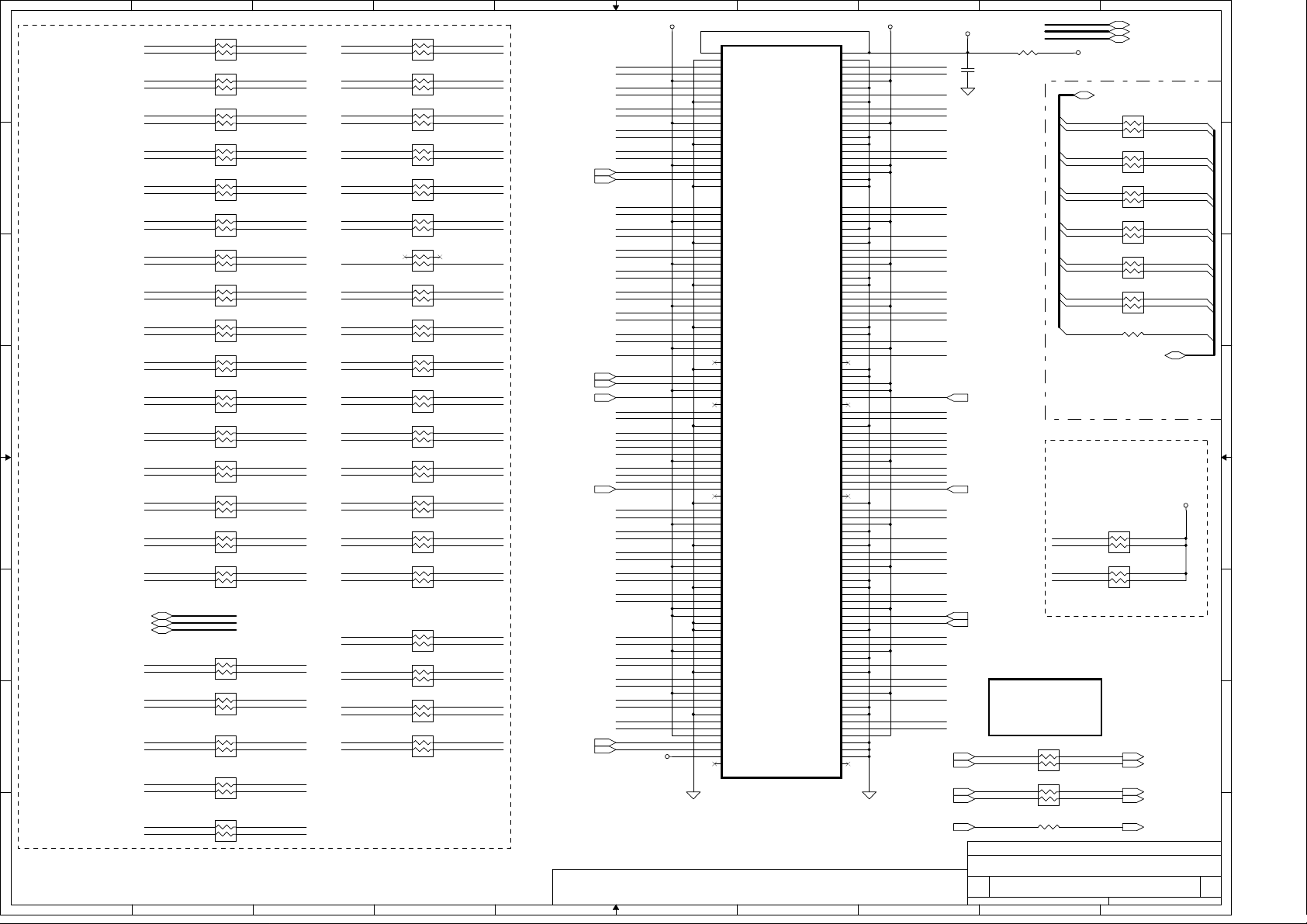

A

B

C

D

E

F

G

H

I

J

1 1

+CPU_CORE

2 2

HA#[3..31]<8>

3 3

4 4

HREQ#[0 ..4 ]<8>

HADS#<8>

5 5

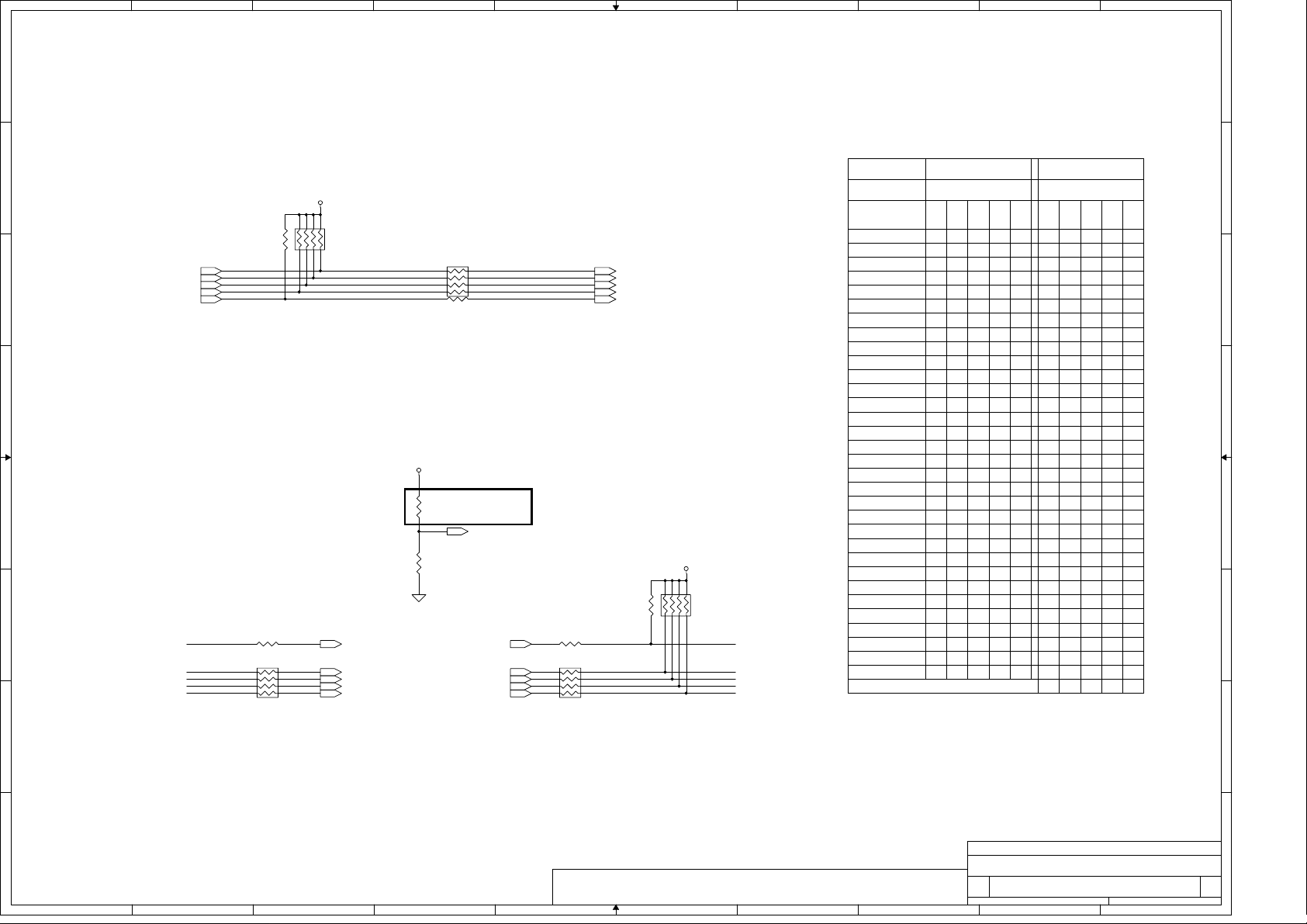

R148 not plant

for DT CPU.

HBR0#<8>

HBPRI#<8>

HBNR#<8>

HLOCK#<8>

CLK_HCLK<14>

CLK_HCLK#<14>

+CPU_CORE

HA#[3..31]

HREQ#[0..4]

R148 M@10K_0402

1 2

R96 200_0402

1 2

CLK_HCLK

CLK_HCLK#

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

AF22

AF23

6 6

HIT#<8>

HITM#<8>

HDEFER#<8>

A10

A12

A14

A16

U41A

VCC_0

VCC_1

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

BCLK0

BCLK1

HIT#

HITM#

DEFER#

VCC_2

VSS_0H1VSS_1H4VSS_2

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

W1

T5

U4

V3

W2

Y1

AB1

J1

K5

J4

J3

H3

G1

AC1

V5

AA3

AC3

H6

D2

G2

G4

F3

E3

E2

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

D9

A18

A20

AA10

AA12

AA14

VCC_3

VCC_4

VCC_5

VCC_6A8VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56B7VCC_57B9VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65C8VCC_66

Mobile

NorthWood

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12A3VSS_13A9VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VCC_81

VCC_82

VCC_83

VCC_84

F9

F13

F15

F17

A11

A13

A15

A17

A19

A21

A24

H23

H26

A26

AA1

AA11

AA4

AA7

AA13

AA15

AA9

AA17

AA19

AA23

AA26

AB10

AB12

AB3

AB6

AB8

AC2

AC5

AC7

AC9

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AD1

AC22

AC25

AD10

AD4

AD12

AD14

AD16

AD18

AD21

AD23

AD8

F19

E10

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71D7VCC_72

VCC_73

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79E8VCC_80

VCC_85

F11

NorthWood

E12

E14

E16

E18

E20

B21

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

HD#[0 ..6 3 ] <8>

7 7

8 8

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

D

E

F

G

+CPU_CORE

Compal Electronics, Inc.

Title

SCHEM AT IC , M/ B LA- 1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

H

Date: Sheet

?30, 2002

I

446,

2B

of

J

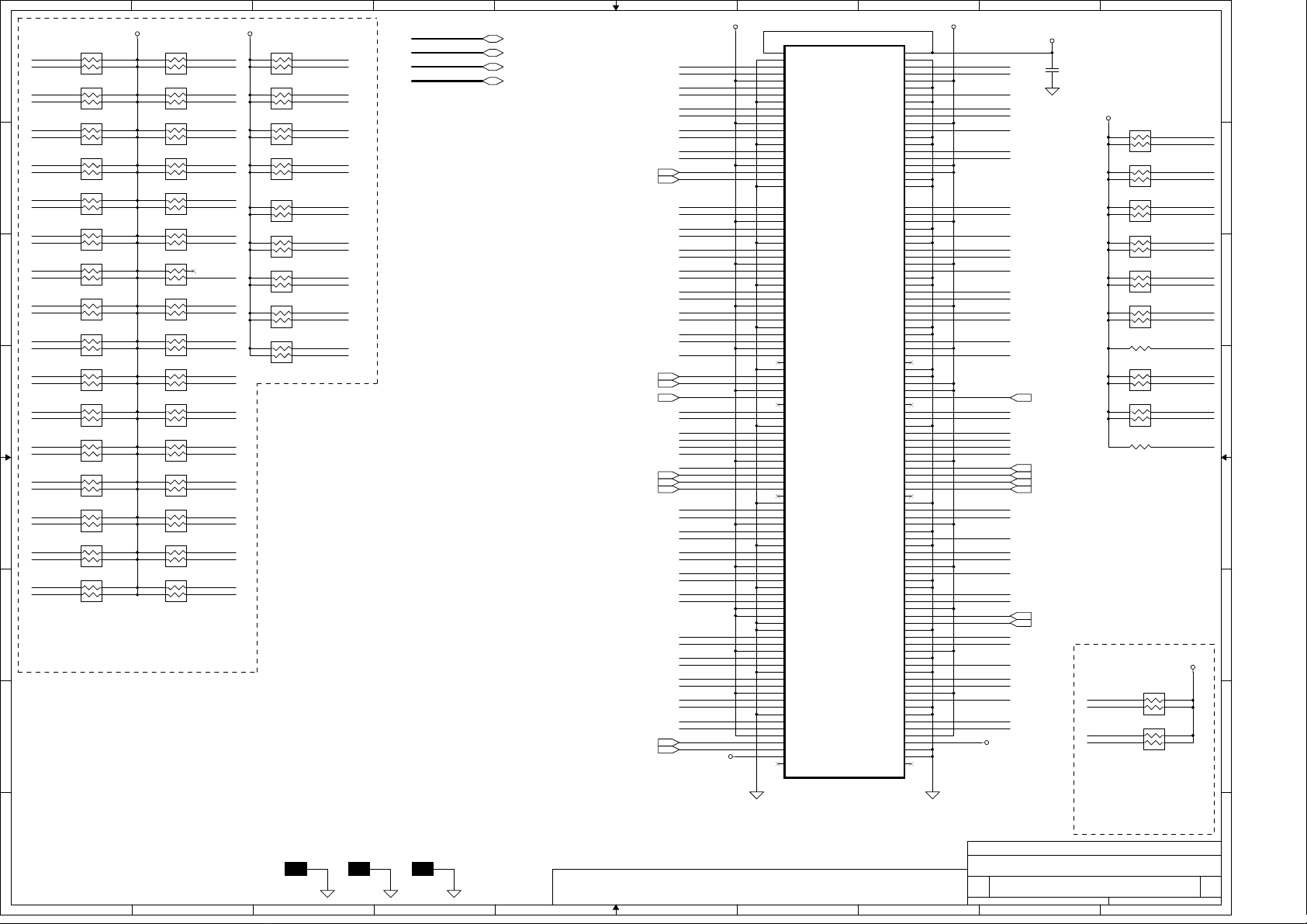

A

+CPU_CORE

R116

1 1

2 2

3 3

R119

R120

R100

R26

R99

R101

R146

R115

R28 300_0402

R30

R114

Place resistor <100mils from

CPU pin

+CPU_CORE

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

200_0402

12

56_0402

12

12

H_DPSLP#<16>

51.1_1%

12

200_0402

12

+CPU_CORE

PM_CPUPERF#

4 4

+1.2VP

Murata LQG21F4R7N00

If used ITP port must depop

RP6 8P4R_1.5K

1 8

2 7

5 5

6 6

3 6

4 5

+CPU_CORE

R147 51.1_1%

R87

R88

R89 51.1_1%

R158 51.1_1%

R159 51.1_1%

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

12

12

51.1_1%

51.1_1%

12

12

12

12

7 7

C155

2200PF

+5VALW

R197 1K_0402

8 8

Address:1001_110X

A

H_A20M#

H_SMI#

H_IGNNE#

H_STPCLK#

H_DPSLPR#

H_NMI

H_INIT#

H_INTR

H_F_FERR#

H_PWRGD

H_RESET#

DT : INSTALL

L50

DT@4.7UH_80mA

1 2

DT@4.7UH_80mA

L19

1 2

DT : REMOVE

L51

M@4.7UH_80mA

1 2

M@4.7UH_80mA

L12

1 2

ITP_PREQ#

ITP_PRDY#

ITP_BPM0

ITP_BPM1

ITP_BPM2

ITP_BPM3

12

H_THERMDA

H_THERMDC

12

B

DT : REMOVE

M@0_0402

R20

R19

DT@56_0402

12

C67

+

22U_1206_10V4Z

CLK_ITPP<14>

CLK_ITPP#<14>

B

H_TRDY#<8>

H_F_FERR#<16>

H_IGNNE#<16>

H_PWRGD<16>

H_STPCLK#<16>

12

12

H_RESET#<8>

H_DBSY#<8>

H_DRDY#<8>

+1.2VP

1 2

R124 56_0402

12

+

H_VSSA

Thermal Sensor

MAX6654MEE

W=15mil

1 2

U11

1

NC

2

VCC

3

DXP

SMBCLK

4

DXN

5

NC

SMBDATA

6

ADD1

GND

GND

MAX6654MEE

ALERT

7

8

C

H_RS#0<8>

H_RS#1<8>

H_RS#2<8>

H_A20M#<16>

H_SMI#<16>

H_INTR<16>

H_NMI<16>

H_INIT#<16>

H_BSEL0<14>

H_BSEL1<14>

H_THERMTRIP#

TP1

1

C94

22U_1206_10V4Z

+5VALW

C198

.1UF_0402

16

NC

15

STBY

14

13

NC

12

11

10

ADD0

9

NC

R199

1K_0402

C

12

R34 M@0_0402

DT : REMOVE

F1

G5

F4

AB2

J6

H_A20M#

H_F_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_DPSLPR#

H_INTR

H_NMI

H_INIT#

H_RESET#

H_THERMDA

H_THERMDC

ITP_BPM0

ITP_BPM1

ITP_BPM2

ITP_BPM3

ITP_PRDY#

ITP_PREQ#

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

H_VCCA

H_VCCIOPLL

R56

51.1_1%

R190

1 2

1 2

+5VALW

C6

B6

B2

B5

AB23

Y4

AD25

D1

E5

W5

AB25

H5

H2

AD6

AD5

B3

C4

A2

AC6

AB5

AC4

Y6

AA5

AB4

D4

C1

D5

F7

E6

AD20

A5

AE23

AF25

AF3

AC26

AD26

L24

P1

R142

51.1_1%

1 2

1 2

10K_0402

CPU_THRM# PROCHOT#

R195

10K_0402

1 2

D

AE11

AE13

AE15

U41B

VSS_57

VSS_58

VSS_59

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCA

VCCSENSE

VCCIOPLL

NC7

NC8

ITP_CLK0

ITP_CLK1

COMP0

COMP1

VSS_129F8VSS_130

G21

EC_SMC2 <30,39>

EC_SMD2 <30,39>

12

R172

@0_0402

D

AE17

AE19

VSS_60

VSS_61

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

G24

H_SKTOCC#

AE22

AE24

AE26

AE7

VSS_62

VSS_63

VSS_64

VSS_65

VSS_136

J22

J25

+CPU_CORE

12

R_A

12

R_B

E

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

AF26

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

SKTOCC#

B26

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85B4VSS_86B8VSS_87

NorthWood

VSS_137J5VSS_138

VSS_139

VSS_140K3VSS_141K6VSS_142L1VSS_143

VSS_144

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

L23

L26

K21

K24

GTL Reference Vol tage

Layout note :

1. Place R_A and R_B near CPU.

2. Place decoupling cap 220PF near CPU.(Within

500mils )

R57

49.9_1%

Trace width>=7mila

R58

100_1%

M22

M25

C443

1UF

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

P22

P25

N21

N24

C442

220PF

F

C11

C13

C15

C17

C19

C22

C25

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92C2VSS_93

VSS_94

VSS_95C5VSS_96C7VSS_97C9VSS_98

Mobile

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

T21

T24

R23

R26

+H_GTLREF1

F

G

D10

D12

D14

D16

D18

D20

D21

D24

E11

E13

E15

E17

E19

E23

E26

H

F10

F12

F14

F16

F18

F22

F25

F5

I

R125 DT@56_0402

1 2

PM_CPUPERF#H_GHI#

1 2

R123 M@0_0402

J

+CPU_CORE

PM_CPUPERF# <16>

DT : REMOVE

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125F2VSS_126

VSS_127

VSS_128

J26

DP#0

K25

DP#1

K26

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

NC1

NC2

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

ITPCLKOUT0

ITPCLKOUT1

TESTHI8

TESTHI9

TESTHI10

GHI#

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

VSSA

VSSSENSE

NC3

VID0

VID1

VID2

VID3

G

S

AE5

AE4

AE3

AE2

+5VS

R632

@301_1%_0402

1 2

Q13

2

@3904

3 1

VID4

NC5

AE1

AE21

@470_0402

1 2

Q76

@3904

3 1

4/29 update

Johnny

NC6

AF24

R153

VSS_168

VSS_169U5VSS_170V1VSS_171

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

VSS_180

VSS_181

V23

V26

U22

U25

W21

PCIRST#<8,15,16,19,23,25,26,28,34>

MAINPWON<37,40,41>

Y5

Y22

Y25

W24

2

1 3

D

Q15

@2N7002

G

NC4

VCCVID

NorthWood

AF4

CPU_VR_VID4 <7>

CPU_VR_VID3 <7>

CPU_VR_VID2 <7>

CPU_VR_VID1 <7>

CPU_VR_VID0 <7>

PROCHOT#<30>

R144

2

1 2

@470_0402

H

H_THERMTRIP#

+H_GTLREF1

L25

AA21

AA6

F20

F6

A22

A7

TESTTHI0_1

AD24

AA2

TESTTHI2_7

AC21

AC20

AC24

AC23

ITPCLKOUT0

AA20

ITPCLKOUT1

AB22

TESTTHI8_10

U6

W4

Y3

H_GHI#

A6

H_DSTBN#0

E22

H_DSTBN#1

K22

H_DSTBN#2

R22

H_DSTBN#3

W22

H_DSTBP#0

F21

H_DSTBP#1

J23

H_DSTBP#2

P23

H_DSTBP#3

W23

L5

R5

H_DBI#0

E21

H_DBI#1

G25

H_DBI#2

P26

H_DBI#3

V21

H_DBR#

AE25

H_PROCHOT#

C3

V6

H_SLP#

AB26

H_VSSA

AD22

A4

AD2

AD3

+1.2VP

C145

.1UF_0402

R171

1K_0402

PROCHOT#

Q14

3904

Compal Electronics, Inc.

Title

SCHEM AT IC , M/ B LA- 1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

Date: Sheet

All of these pin

connected inside

R25 56_0402

1 2

R27 56_0402

1 2

R49 56_0402

1 2

R50 56_0402

1 2

R102 56_0402

1 2

H_DSTBN#[0..3]

H_DSTBP#[0..3]

H_DBI#[0..3]

1 2

R210 @0_0402

1 2

R145 56_0402

TP2

1 2

3 1

?30, 2002

I

R29 200_0402

1 2

2

Q12

3 1

1

+3VALW

R176

470_0402

2

3904

+CPU_CORE

H_DSTBN#[0..3] <8>

H_DSTBP#[0..3] <8>

H_ADSTB#0 <8>

H_ADSTB#1 <8>

H_DBI#[0..3] <8>

+CPU_CORE

ITP_DBR# <33>

H_SLP# <16>

12

+CPU_CORE

R143

1 2

470_0402

546,

J

H_PROCHOT#

of

2B

A

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

1 1

Use 2~3 vias per PAD.

B

C

D

E

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

F

+CPU_CORE

G

12

C462

+

DT@470UF_D4_2.5V_10m

12

C449

+

DT@470UF_D4_2.5V_10m

H

12

C441

+

DT@470UF_D4_2.5V_10m

I

12

C492

+

DT@470UF_D4_2.5V_10m

12

C419

+

DT@470UF_D4_2.5V_10m

J

Please place these cap in the socket cavity area

+CPU_CORE

12

2 2

3 3

4 4

5 5

C95

10UF_6.3V_1206_X5R

+CPU_CORE

12

C107

10UF_6.3V_1206_X5R

Please place these cap on the socket north side

+CPU_CORE

12

C80

10UF_6.3V_1206_X5R

+CPU_CORE

12

C128

10UF_6.3V_1206_X5R

+CPU_CORE

12

C429

10UF_6.3V_1206_X5R

12

C122

10UF_6.3V_1206_X5R

12

C106

10UF_6.3V_1206_X5R

12

C92

10UF_6.3V_1206_X5R

12

C61

10UF_6.3V_1206_X5R

12

C430

10UF_6.3V_1206_X5R

12

C89

10UF_6.3V_1206_X5R

12

C465

10UF_6.3V_1206_X5R

12

C104

10UF_6.3V_1206_X5R

12

C59

10UF_6.3V_1206_X5R

12

C423

10UF_6.3V_1206_X5R

12

C113

10UF_6.3V_1206_X5R

12

C461

10UF_6.3V_1206_X5R

12

C428

10UF_6.3V_1206_X5R

12

C57

10UF_6.3V_1206_X5R

12

C53

10UF_6.3V_1206_X5R

12

C98

10UF_6.3V_1206_X5R

12

C445

10UF_6.3V_1206_X5R

12

C118

10UF_6.3V_1206_X5R

12

C56

10UF_6.3V_1206_X5R

Please place these cap on the socket south side

+CPU_CORE

12

C123

10UF_6.3V_1206_X5R

6 6

7 7

+CPU_CORE

12

C447

10UF_6.3V_1206_X5R

+CPU_CORE

12

C176

10UF_6.3V_1206_X5R

12

C115

10UF_6.3V_1206_X5R

12

C83

10UF_6.3V_1206_X5R

12

C426

10UF_6.3V_1206_X5R

12

C159

10UF_6.3V_1206_X5R

12

C495

10UF_6.3V_1206_X5R

12

C427

10UF_6.3V_1206_X5R

12

C116

10UF_6.3V_1206_X5R

12

C174

10UF_6.3V_1206_X5R

12

C55

10UF_6.3V_1206_X5R

12

C448

10UF_6.3V_1206_X5R

12

C175

10UF_6.3V_1206_X5R

EN_FAN2<30>

EMI Clip PAD for CPU

PAD1

PAD-2.5X3

1

A

B

C

D

8 8

For Desktop's CPU:

ESR total=0.75m ohm

C total=6350uF

For Mo b i l e 's CPU:

ESR total=1.875m ohm

C total=2590uF

.1UF_0402

12

R295

13K_1%

+12VS

84

U27A

+

-

R293

7.32K_1%

+12VS

5

6

1

LM358

12

F

C190

EN_FAN1<30>

3

2

12

R296

13K_1%

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

+CPU_CORE

12

C485

+

470UF_D4_2.5V_10m

+CPU_CORE

12

C149

+

330UF_D2_2.5V_15m

+CPU_CORE

12

C456

.22UF_X7R

+12VS

R292

3.48K_1%

84

U27B

+

7

-

LM358

R294

7.32K_1%

3.48K_1%

2

R434

2

12

+12VS

1 2

21

D40

1N4148

31

Q51

2SA1036K

G

12

C455

.22UF_X7R

1 2

21

D27

1N4148

31

Q32

2SA1036K

Q24

FMMT619

C225

2.2UF_16V_0805

1 2

12

C420

+

470UF_D4_2.5V_10m

12

C99

+

330UF_D2_2.5V_15m

12

C480

.22UF_X7R

Q23

FMMT619

C367

2.2UF_16V_0805

1 2

2

3 1

D12

1N4148

2 1

12

C479

.22UF_X7R

2

3 1

D15

1N4148

2 1

New add

5/15 Johnny

D13

1SS355

2 1

C754

33PF_0402

New add

5/15 Johnny

C747

220PF_0402

H

12

C474

+

DT@470UF_D4_2.5V_10m

12

C50

+

330UF_D2_2.5V_15m

12

C478

.22UF_X7R

12

C477

.22UF_X7R

12

C421

+

DT@470UF_D4_2.5V_10m

12

C49

+

330UF_D2_2.5V_15m

12

12

C476

.22UF_X7R

C475

.22UF_X7R

12

C434

+

DT@470UF_D4_2.5V_10m

12

C48

+

330UF_D2_2.5V_15m

12

C450

.22UF_X7R

Fan1 Control circuit

New add

5/15 Johnny

+5VS

D16

C234

1SS355

1000PF_0402

2 1

+5VFAN1

C752

33PF_0402

New add

5/15 Johnny

C746

220PF_0402

+5VS

C222

1000PF_0402

+5VFAN2

C753

.1uF_0402

+3VS

12

Title

Size Docu ment Number Re v

Custom

Date: Sheet

JP22

C751

1

.1uF_0402

2

3

53398-0310

+3VS

12

R433

10K_0402

FAN_SPEED <30>

Fan2 Control circuit

JP23

1

2

3

53398-0310

R220

10K_0402

FAN_SPEED2 <30>

Compal Electronics, Inc.

SCHEM AT IC , M/ B LA- 1381

401212

星期一 十二

?30, 2002

I

12

C451

.22UF_X7R

646,

2B

of

J

10

H H

9

8

7

6

5

4

3

2

1

For Mobile CPU

G G

1K_0402

CPU_VR_VID0<5>

CPU_VR_VID1<5>

CPU_VR_VID2<5>

F F

E E

CPU_VR_VID3<5>

CPU_VR_VID4<5>

CPU_VR_VID0

CPU_VR_VID1

CPU_VR_VID2

CPU_VR_VID3

CPU_VR_VID4

For Desktop CPU

D D

C C

CPU_VR_VID0

CPU_VR_VID1

CPU_VR_VID2

CPU_VR_VID3

CPU_VR_VID4 CPU_VID4

1 2

R399 DT@0_0402

RP89

4 5

3 6

2 7

1 8

DT@8P4R_0

R173

+3VS

12

182736

45

RP8

8P4R_1K

CPU_ECVID0 <31>

CPU_ECVID1 <31>

CPU_ECVID2 <31>

CPU_ECVID3 <31>

CPU_ECVID4 <31>

RP90 M@8P4R_0

4 5

3 6

2 7

1 8

R178 M@0_0402

1 2

+3VALW

R390

DT : REMOVE

M@100K_0402

1 2

1 2

R389

DT@100K_0402

NB/DT#_CPU <31,43>

EC_CPUVID0<31>

EC_CPUVID1<31>

EC_CPUVID2<31>

EC_CPUVID3<31>

EC_CPUVID4<31>

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

1 2

R403 DT@0_0402

RP87

4 5

3 6

2 7

1 8

DT@8P4R_0

CPU_VID0 <43>

CPU_VID1 <43>

CPU_VID2 <43>

CPU_VID3 <43>

CPU_VID4 <43>

@10K_0402

R404

+5VS

12

182736

45

RP86

@8P4R_10K

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

NB/DT_CPU

VID

VCC

1.750V

1.700V

1.650V

1.600V

1.550V

1.500V

1.450V

1.400V

1.350V

1.300V

1.250V

1.200V

1.150V

1.100V

1.050V

1.000V

0.975V

0.950V

0.925V

0.900V

0.875V

0.850V

0.825V

0.800V

0.775V

0.750V

0.725V

0.700V

0.675V

0.650V

0.625V

0.600V

Mobil CPU Destop CPU

10

00 01

00000

1

0000

1

000

00 0

00

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0000

1

1

1

1

1

1

0000

1

00

1

1

0

1

1

0

1

1

1

1

0

1

1

1

1

1

1

000

0

000

1

1

00

1

1

00

1

1

0

1

00

1

1

1

00

1

1

00

1

1

0

1

1

1

1

0

1

1

1

00011

1

0000

1

1

000

1

1

0

1

00

1

0

0

0

0

0

11

0

1

11

1

0

0

1

0

0

1

1

0

1

1

0

1

1

0

1

1

0

1

1

1

1

1

1

XXXXX

1

X

1

XXX

000

1

XXXXX

000

1

0

1

XXXXX

00

1

XXXXX

1

XXXXX

00

1

XXXXX

0

11111

VRM output off 1 1 1 1

0412134023

0

0

0

0

0

11

0

0

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

XXXXX

X

XXXXXXX

X

XX

X

XXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

1

B B

A A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

10

9

8

7

6

5

4

3

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

Date: Sheet

?30, 2002

2

of

746,

1

2B

A

B

C

D

E

F

G

H

I

J

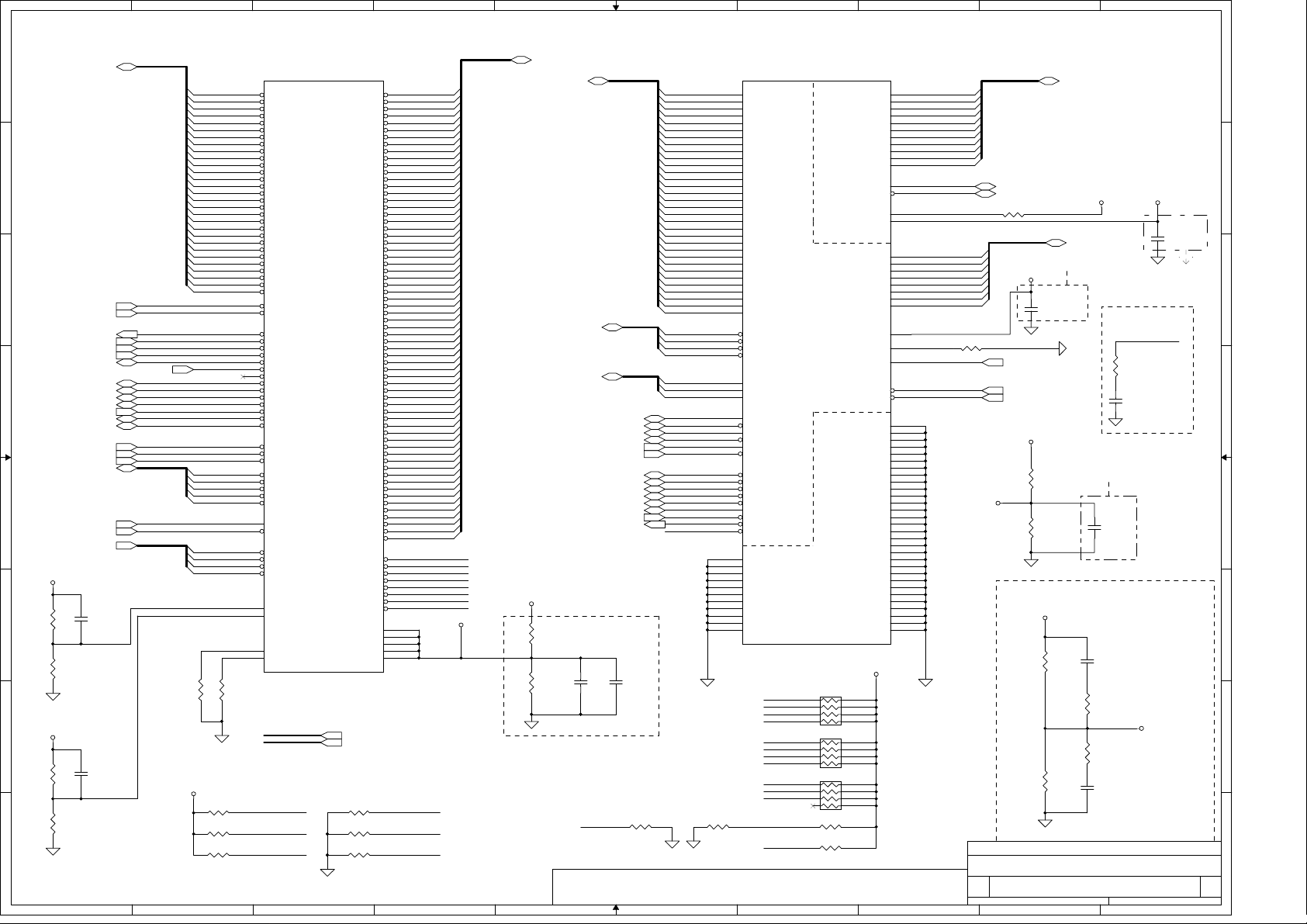

1 1

HA#[3..31]<4>

2 2

3 3

H_ADSTB#0<5>

H_ADSTB#1<5>

H_RESET#<5>

H_TRDY#<5>

HDEFER#<4>

HBPRI#<4>

HLOCK#<4>

H_DBSY#<5>

H_DRDY#<5>

HIT#<4>

4 4

5 5

+CPU_CORE

R68

301_1%

6 6

R72

150_1%

+CPU_CORE

7 7

R63

301_1%

R64

150_1%

HITM#<4>

HBR0#<4>

HADS#<4>

HBNR#<4>

H_RS#0<5>

H_RS#1<5>

H_RS#2<5>

HREQ#[0 ..4 ]<4>

CLK_GHT<14>

CLK_GHT#<14>

H_DBI#[0..3]<5>

12

12

C88

.01UF_0402

12

12

12

C90

.01UF_0402

12

8 8

A

HA#[3..31]

PCIRST#<5,15,16,19,23,25,26,28,34>

HREQ#[0..4]

H_DBI#[0..3]

24.9_0603_1%

CLK_GHT

CLK_GHT#

12

R48

+1.5VS

R90 8.2K_0402

R45 8.2K_0402

R41 8.2K_0402

B

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_SWNG0

H_SWNG1

12

T4

T5

T3

U3

R3

P7

R2

P4

R6

P5

P3

N2

N7

N3

K4

M4

M3

L3

L5

K3

J2

M5

J3

L2

H4

N5

G2

M6

L7

R5

N6

AE17

U7

Y4

Y7

W5

J27

H26

V5

V4

Y5

Y3

V7

V3

W3

W2

W7

W6

U6

T7

R7

U5

U2

J8

K8

AD5

AG4

AH9

AD15

AA7

AD13

AC2

AC13

R75

24.9_0603_1%

AGP_ADSTB0

12

AGP_ADSTB1

12

AGP_SBSTB

12

U43A

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HADSTB#0

HADSTB#1

CPURST#

HTRDY#

DEFER#

BPRI#

HLOCK#

RSTIN#

TESTIN#

DBSY#

DRDY#

HIT#

HITM#

BREQ#0

ADS#

BNR#

RS#0

RS#1

RS#2

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

BCLK

BCLK#

DBI#0

DBI#1

DBI#2

DBI#3

HSWNG0

HSWNG1

HRCOMP0

HRCOMP1

H_DSTBN#[0..3]

H_DSTBP#[0..3]

HOST

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

BROOKDALE(MCH-M)

H_DSTBN#[0..3] <5>

H_DSTBP#[0..3] <5>

R83 @8.2K_0402

R44 @8.2K_0402

R40 @8.2K_0402

C

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

AA2

AB5

AA5

AB3

AB4

AC5

AA3

AA6

AE3

AB7

AD7

AC7

AC6

AC3

AC8

AE2

AG5

AG2

AE8

AF6

AH2

AF3

AG3

AE5

AH7

AH3

AF4

AG8

AG7

AG6

AF8

AH5

AC11

AC12

AE9

AC9

AE10

AD9

AG9

AC10

AE12

AF10

AG11

AG10

AH11

AG12

AE13

AF12

AG13

AH13

AC14

AF14

AG14

AE14

AG15

AG16

AG17

AH15

AC17

AF16

AE15

AH17

AD17

AE16

AD4

AE6

AE11

AC15

AD3

AE7

AD11

AC16

M7

R8

Y8

AB11

AB17

12

12

12

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

AGP_ADSTB0#

AGP_ADSTB1#

AGP_SBSTB#

HD#[0..63]

+V_MCH_GTLREF

AGP_ST0

0=System memory is DDR

1=System memory is SDR

D

HD#[0..63] <4>

AGP_AD[0..31]<15>

AGP_C/BE#[0..3]<15>

AGP_ST[0..2]<15>

+CPU_CORE

12

R66

R_E

49.9_1%

12

R65

R_F

100_1%

GTL Reference Vol tage

Layout note :

1. Place R_E and R_F near MCH

2. Place decoupling cap 220PF near MCH pin.(Within

500mils )

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

AGP_AD[0..31] HUB_PD[0..10]

AGP_ADSTB0<15>

AGP_ADSTB0#<15>

AGP_ADSTB1<15>

AGP_ADSTB1#<15>

AGP_SBSTB<15>

AGP_SBSTB#<15>

AGP_FRAME#<15>

AGP_DEVSEL#<15>

AGP_IRDY#<15>

AGP_TRDY#<15>

AGP_STOP#<15>

AGP_PAR<15>

AGP_REQ#<15>

AGP_GNT#<15>

Trace

width>=7mila

C103

C102

220PF

1UF

R337 2K_0402

AGP_ST0 AGP_ST1

12

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_ST0

AGP_ST1

AGP_ST2

AGP_ADSTB0

AGP_ADSTB0#

AGP_ADSTB1

AGP_ADSTB1#

AGP_SBSTB

AGP_SBSTB#

AGP_FRAME#

AGP_DEVSEL#

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_PAR

AGP_REQ#

AGP_GNT#

AGP_PIPE#

F

U43B

R27

G_AD0

R28

G_AD1

T25

G_AD2

R25

G_AD3

T26

G_AD4

T27

G_AD5

U27

G_AD6

U28

G_AD7

V26

G_AD8

V27

G_AD9

T23

G_AD10

U23

G_AD11

T24

G_AD12

U24

G_AD13

U25

G_AD14

V24

G_AD15

Y27

G_AD16

Y26

G_AD17

AA28

G_AD18

AB25

G_AD19

AB27

G_AD20

AA27

G_AD21

AB26

G_AD22

Y23

G_AD23

AB23

G_AD24

AA24

G_AD25

AA25

G_AD26

AB24

G_AD27

AC25

G_AD28

AC24

G_AD29

AC22

G_AD30

AD24

G_AD31

V25

G_C/BE#0

V23

G_C/BE#1

Y25

G_C/BE#2

AA23

G_C/BE#3

AG25

ST0

AF24

ST1

AG26

ST2

R24

AD_STB0

R23

AD_STB#0

AC27

AD_STB1

AC28

AD_STB#1

AF27

SB_STB

AF26

SB_STB#

Y24

G_FRAME#

W28

G_DEVSEL#

W27

G_IRDY#

W24

G_TRDY#

W23

G_STOP#

W25

G_PAR

AG24

G_REQ#

AH25

G_GNT#

AF22

PIPE#

N22

VSS0

K27

VSS1

K5

VSS2

L24

VSS3

M23

VSS4

K7

VSS5

J26

VSS6

A3

VSS7

A7

VSS8

A11

VSS9

A15

VSS10

R336 @1K_0402

12

AGP_FRAME#

AGP_TRDY#

AGP_PAR

AGP_STOP#

AGP_GNT#

AGP_REQ#

AGP_IRDY#

AGP_DEVSEL#

AGP_WBF#

AGP_PIPE#

AGP_RBF#

AGP_ST2

G

HUB

HI_STB#

HLRCOMP

AGP

AGPREF

GRCOMP

BROOKDALE(MCH-M)

+1.5VS

RP4 @8P4R_8.2K

1 8

2 7

3 6

4 5

RP83 @8P4R_8.2K

1 8

2 7

3 6

4 5

RP3 @8P4R_8.2K

1 8

2 7

3 6

4 5

R62 6.2K_0402

12

6.2K_0402

R39

12

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HI_7

HI_8

HI_9

HI_10

HI_STB

HI_REF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

66IN

RBF#

WBF#

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

P25

P24

N27

P23

M26

M25

L28

L27

M27

N28

M24

N25

N24

P27

P26

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AA21

AD25

P22

AE22

AE23

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J29

AGP_ST1

0=533Mhz

1=400Mhz

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HLRCOMP

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

CLK_AGP_MCH

AGP_RBF#

AGP_WBF#

H

HUB_PD[0..10] <16>

HUB_PSTRB <16>

HUB_PSTRB# <16>

R85

1 2

AGP_SBA[0..7]

36.5_1%

AGP_SBA[0..7] <15>

Place this cap near MCH

+AGPREF

12

C84

.1UF_0402

R53

36.5_1%

12

CLK_AGP_MCH <14>

AGP_RBF# <15>

AGP_WBF# <15>

+1.5VS

12

Place this cap near AGP

R22

1K_1%

AGP_NBREF

Title

Size Docu ment Number Re v

Custom

Date: Sheet

12

R23

1K_1%

HUB Interface Reference

Layout note :

+1.8VS

1. Pla c e R_C and R_D in middle of Bus.

2. Place capacitors near MCH.

12

12

R69

301_1%

12

12

12

12

R78

301_1%

R_C

R_D

Compal Electronics, Inc.

SCHEM AT IC , M/ B LA- 1381

401212

星期一 十二

?30, 2002

I

+VS_HUBREF

+1.8VS

Place closely

ball P26

Place closely pin P22

CLK_AGP_MCH

R94

@33_0402

1 2

C121

@10PF_0402

12

C47

.1UF_0402

C108

@470PF

R84

@56.2_1%

+VS_HUBREF

R71

0_0402

C100

.01UF_0402

846,

12

C120

.01UF_0402

of

J

2B

A

B

C

D

E

F

G

H

I

J

U43D

M8

+CPU_CORE

1 1

2 2

+2.5V

3 3

4 4

5 5

6 6

7 7

VTT_0

U8

VTT_1

AA9

VTT_2

AB8

VTT_3

AB18

VTT_4

AB20

VTT_5

AC19

VTT_6

AD18

VTT_7

AD20

VTT_8

AE19

VTT_9

AE21

VTT_10

AF18

VTT_11

AF20

VTT_12

AG19

VTT_13

AG21

VTT_14

AG23

VTT_15

AJ19

VTT_16

AJ21

VTT_17

AJ23

VTT_18

A5

VCCSM1

A9

VCCSM2

A13

VCCSM3

A17

VCCSM4

A21

VCCSM5

A25

VCCSM6

C1

VCCSM7

C29

VCCSM8

D7

VCCSM9

D11

VCCSM10

D15

VCCSM11

D19

VCCSM12

D23

VCCSM13

D25

VCCSM14

F6

VCCSM15

F10

VCCSM16

F14

VCCSM17

F18

VCCSM18

F22

VCCSM19

G1

VCCSM20

G4

VCCSM21

G29

VCCSM22

H8

VCCSM23

H10

VCCSM24

H12

VCCSM25

H14

VCCSM26

H16

VCCSM27

H18

VCCSM28

H20

VCCSM29

H22

VCCSM30

H24

VCCSM31

K22

VCCSM32

K24

VCCSM33

K26

VCCSM34

L23

VCCSM35

K6

VCCSM36

J5

VCCSM37

J7

VCCSM38

L1

VSS41

L4

VSS42

L6

VSS43

L8

VSS44

L22

VSS45

L26

VSS46

N1

VSS47

N4

VSS48

N8

VSS49

N13

VSS50

N15

VSS51

N17

VSS52

N29

VSS53

P6

VSS54

P8

VSS55

P14

VSS56

P16

VSS57

R1

VSS58

R4

VSS59

R13

VSS60

R15

VSS61

R17

VSS62

R26

VSS63

T6

VSS64

T8

VSS65

T14

VSS66

T16

VSS67

T22

VSS68

U1

VSS69

U4

VSS70

U15

VSS71

U29

VSS72

V6

VSS73

V8

VSS74

V22

VSS75

W1

VSS76

W4

VSS77

W8

VSS78

W26

VSS79

Y6

VSS80

Y22

VSS81

AA1

VSS82

BROOKDALE(MCH-M)

POWER/GND

VCC1_5_0

VCC1_5_1

VCC1_5_2

VCC1_5_3

VCC1_5_4

VCC1_5_5

VCC1_5_6

VCC1_5_7

VCC1_5_8

VCC1_5_9

VCC1_5_10

VCC1_5_11

VCC1_5_12

VCC1_5_13

VCC1_5_14

VCC1_5_15

VCC1_5_16

VCC1_5_17

VCC1_5_18

VCC1_5_19

VCC1_5_20

VCC1_5_21

VCC1_5_22

VCC1_5_23

VCC1_5_24

VCC1_5_25

VCC1_8_0

VCC1_8_1

VCC1_8_2

VCC1_8_3

VCC1_8_4

VCCGA1

VCCHA1

VSSGA2

VSSHA2

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

R22

R29

U22

U26

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

L29

N26

L25

M22

N23

T17

T13

U17

U13

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ3

AJ5

AJ7

AJ9

AJ11

AJ13

AJ15

AJ17

AJ27

VCC_MCH_PLL1

VCC_MCH_PLL0

VSS_MCH_PLL1

VSS_MCH_PLL0

+1.5VS

Layout note :

Trace width 5mil ; Spacing

10mil

Trace A to ball U13/T13 or

U17/T7 =1.5" Max

+1.5VS

+1.8VS

12

"Trace A"

12

+

"Trace A"

"Trace A"

L22

4.7UH_30mA

"Trace A"

C169

33UF_D2_16V

Murata LQG21N4R7K10

12

L21

4.7UH_30mA

12

C168

+

33UF_D2_16V

DDR_SDQ[0..63]<11>

DDR_CB[0..7]<11>

SDREF

DDR_SDQ[0..63]

DDR_CB[0..7]

12

0_0402

R108

.1UF_0402_X5R

Layout note

Please closely

pin J21 and J9

DDR_SDQ0

DDR_SDQ1

DDR_SDQ2

DDR_SDQ3

DDR_SDQ4

DDR_SDQ5

DDR_SDQ6

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ10

DDR_SDQ11

DDR_SDQ12

DDR_SDQ13

DDR_SDQ14

DDR_SDQ15

DDR_SDQ16

DDR_SDQ17

DDR_SDQ18

DDR_SDQ19

DDR_SDQ20

DDR_SDQ21

DDR_SDQ22

DDR_SDQ23

DDR_SDQ24

DDR_SDQ25

DDR_SDQ26

DDR_SDQ27

DDR_SDQ28

DDR_SDQ29

DDR_SDQ30

DDR_SDQ31

DDR_SDQ32

DDR_SDQ33

DDR_SDQ34

DDR_SDQ35

DDR_SDQ36

DDR_SDQ37

DDR_SDQ38

DDR_SDQ39

DDR_SDQ40

DDR_SDQ41

DDR_SDQ42

DDR_SDQ43

DDR_SDQ44

DDR_SDQ45

DDR_SDQ46

DDR_SDQ47

DDR_SDQ48

DDR_SDQ49

DDR_SDQ50

DDR_SDQ51

DDR_SDQ52

DDR_SDQ53

DDR_SDQ54

DDR_SDQ55

DDR_SDQ56

DDR_SDQ57

DDR_SDQ58

DDR_SDQ59

DDR_SDQ60

DDR_SDQ61

DDR_SDQ62

DDR_SDQ63

DDR_CB0

DDR_CB1

DDR_CB2

DDR_CB3

DDR_CB4

DDR_CB5

DDR_CB6

DDR_CB7

SDREF_M

12

C141

U43C

G28

SDQ0

F27

SDQ1

C28

SDQ2

E28

SDQ3

H25

SDQ4

G27

SDQ5

F25

SDQ6

B28

SDQ7

E27

SDQ8

C27

SDQ9

B25

SDQ10

C25

SDQ11

B27

SDQ12

D27

SDQ13

D26

SDQ14

E25

SDQ15

D24

SDQ16

E23

SDQ17

C22

SDQ18

E21

SDQ19

C24

SDQ20

B23

SDQ21

D22

SDQ22

B21

SDQ23

C21

SDQ24

D20

SDQ25

C19

SDQ26

D18

SDQ27

C20

SDQ28

E19

SDQ29

C18

SDQ30

E17

SDQ31

E13

SDQ32

C12

SDQ33

B11

SDQ34

C10

SDQ35

B13

SDQ36

C13

SDQ37

C11

SDQ38

D10

SDQ39

E10

SDQ40

C9

SDQ41

D8

SDQ42

E8

SDQ43

E11

SDQ44

B9

SDQ45

B7

SDQ46

C7

SDQ47

C6

SDQ48

D6

SDQ49

D4

SDQ50

B3

SDQ51

E6

SDQ52

B5

SDQ53

C4

SDQ54

E5

SDQ55

C3

SDQ56

D3

SDQ57

F4

SDQ58

F3

SDQ59

B2

SDQ60

C2

SDQ61

E2

SDQ62

G5

SDQ63

C16

SDQ64/CB0

D16

SDQ65/CB1

B15

SDQ66/CB2

C14

SDQ67/CB3

B17

SDQ68/CB4

C17

SDQ69/CB5

C15

SDQ70/CB6

D14

SDQ71/CB7

J21

SDREF0

J9

SDREF1

12

C134

.1UF_0402_X5R

SCK0

SCK#0

SCK1

SCK#1

SCK2

SCK#2

SCK3

SCK#3

SCK4

SCK#4

SCK5

SCK#5

SCK6

SCK#6

SCK7

SCK#7

SCK8

SCK#8

SCS#0

SCS#1

SCS#2

SCS#3

SCS#4

MEMORY

SCS#5

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SMA0/CS#11

SMA1/CS#10

SMA2/CS#6

SMA3/CS#9

SMA4/CS#5

SMA5/CS#8

SMA6/CS#7

SMA7/CS#4

SMA8/CS#3

SMA9/CS#0

SMA10

SMA11/CS#2

SMA12/CS#1

SBS0

SBS1

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SMRCOMP

RCVENIN#

RCVENOUT#

SSI_ST

SRAS#

SWE#

SCAS#

NC0

NC1

BROOKDALE(MCH-M)

E14

F15

J24

G25

G6

G7

G15

G14

E24

G24

H5

F5

K25

J25

G17

G16

H7

H6

E9

F7

F9

E7

G9

G10

F26

C26

C23

B19

D12

C8

C5

E3

E15

E12

F17

E16

G18

G19

E18

F19

G21

G20

F21

F13

E20

G22

G12

G13

G23

E22

H23

F23

J23

K23

J28

G3

H3

H27

F11

G11

G8

AD26

AD27

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

DDR_SDQS8

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SBS0

DDR_SBS1

DDR_CKE0

DDR_CKE1

DDR_CKE2

DDR_CKE3

SM_RCOMP

RCVIN#

RCVOUT#

DDR_SRAS#

DDR_SWE#

DDR_SCAS#

DDR_CLK0 <11>

DDR_CLK0# <11>

DDR_CLK1 <11>

DDR_CLK1# <11>

DDR_CLK2 <11>

DDR_CLK2# <11>

DDR_CLK3 <12>

DDR_CLK3# <12>

DDR_CLK4 <12>

DDR_CLK4# <12>

DDR_CLK5 <12>

DDR_CLK5# <12>

DDR_SCS#0 <11>

DDR_SCS#1 <11>

DDR_SCS#2 <12>

DDR_SCS#3 <12>

DDR_SDQS0 <11>

DDR_SDQS1 <11>

DDR_SDQS2 <11>

DDR_SDQS3 <11>

DDR_SDQS4 <11>

DDR_SDQS5 <11>

DDR_SDQS6 <11>

DDR_SDQS7 <11>

DDR_SDQS8 <11>

DDR_SMA[0..12]

DDR_SBS0 <11>

DDR_SBS1 <11>

DDR_CKE0 <11>

DDR_CKE1 <11>

DDR_CKE2 <12>

DDR_CKE3 <12>

R113 27.4_1%

12

0_0402

R112

R_J

DDR_SRAS# <11>

DDR_SWE# <11>

DDR_SCAS# <11>

Layout note

Place R_J closely Ball

H3<40mil,Ball H3 to G3

trace must

routing 1"

DDR_SMA[0..12] <11>

12

C142 .1UF_0402_X5R

C143 @47PF_0402

+1.25VS

Layout note

Place R113

closely ball

J28

8 8

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

D

E

F

G

H

Compal Electronics, Inc.

Title

SCHEM AT IC , M/ B LA- 1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

Date: Sheet

?30, 2002

I

of

946,

J

2B

10

9

8

7

6

5

4

3

2

1

Layout note :

Distribute as close as possible

H H

G G

F F

to MCH Processor Quadrant.(between VTTFSB and VSS pin)

+CPU_CORE

12

C63

.1UF_0402_X5R

+CPU_CORE

12

C109

.1UF_0402_X5R

+CPU_CORE

12

C52

10UF_6.3V_1206_X5R

Layout note :

E E

Distribute as close as possible

to MCH Processor Quadrant.(between VCCAGP/VCCCORE

and VSS pin)

+1.5VS

12

C114

.1UF_0402_X5R

Processor system bus

12

C62

.1UF_0402_X5R

12

C82

.1UF_0402_X5R

12

10UF_6.3V_1206_X5R

12

C66

.1UF_0402_X5R

12

C70

.1UF_0402_X5R

C54

AGP/CORE

12

C96

.1UF_0402_X5R

12

C105

.1UF_0402_X5R

12

C78

.1UF_0402_X5R

12

C69

.1UF_0402_X5R

12

C425

10UF_6.3V_1206_X5R

12

C85

.1UF_0402_X5R

12

C125

.1UF_0402_X5R

12

C81

.1UF_0402_X5R

12

C97

.1UF_0402_X5R

12

C119

.1UF_0402_X5R

Layout note :

Distribute as close as possible

to MCH P rocessor Quadrant.(bet ween VCCSM and VSS pin)

+2.5V

12

C136

.1UF_0402_X5R

+2.5V

12

C146

.1UF_0402_X5R

+2.5V

12

C163

.1UF_0402_X5R

+2.5V

12

C167

+

220UF_D2_4V

DDR Memory interface

12

C137

.1UF_0402_X5R

12

C160

.1UF_0402_X5R

12

C157

.1UF_0402_X5R

12

C139

.1UF_0402_X5R

12

C164

.1UF_0402_X5R

12

C158

.1UF_0402_X5R

12

C140

.1UF_0402_X5R

12

C165

.1UF_0402_X5R

12

C152

.1UF_0402_X5R

12

C135

.1UF_0402_X5R

12

C162

.1UF_0402_X5R

12

C144

.1UF_0402_X5R

12

C150

22UF_10V_1206

12

C166

22UF_10V_1206

D D

+1.5VS

12

C126

10UF_6.3V_1206_X5R

12

C86

10UF_6.3V_1206_X5R

12

C75

+

100UF_D_16V

C C

Layout note :

Distribute as close as possible

to MCH Processor Quadr ant.(between VCCHL and VSS pin)

+1.8VS

12

B B

C130

10UF_6.3V_1206_X5R

A A

Hub-Link

12

C127

.1UF_0402_X5R

10

12

C132

.1UF_0402_X5R

9

12

C133

.1UF_0402_X5R

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

8

7

6

5

4

3

SCHEMATIC, M/B LA-1381

Size Docu ment Number Re v

401212

Custom

星期一 十二

Date: Sheet

?30, 2002

2

of

10 46,

1

2B

A

Layout note

Place these resistor

closely DIMM0,

all trace length<750mil

1 1

2 2

3 3

4 4

5 5

DDR_SDQ[0..63]<9>

6 6

DDR_CB[0..7]<9>

DDR_SD QS [0 ..8 ]<9>

7 7

8 8

A

B

DDR_SDQ0

DDR_SDQ4

DDR_SDQ1

DDR_SDQ5

DDR_SDQ6

DDR_SDQS0

DDR_SDQ2

DDR_SDQ3

DDR_SDQ8

DDR_SDQ7

DDR_SDQ9

DDR_SDQ12

DDR_SDQS1

DDR_SDQ13

DDR_SDQ10

DDR_SDQ14

DDR_SDQ15

DDR_SDQ11

DDR_SDQ16

DDR_SDQ20

DDR_SDQ21

DDR_SDQ17

DDR_SDQ18

DDR_SDQS2

DDR_SDQ19

DDR_SDQ22

DDR_SDQ24

DDR_SDQ23

DDR_SDQ25

DDR_SDQ28

DDR_SDQS3

DDR_SDQ29

DDR_SDQ56

DDR_SDQ51

DDR_SDQ60

DDR_SDQ57

DDR_SDQS7

DDR_SDQ61

DDR_SDQ62

DDR_SDQ58

DDR_SDQ63 DDR_DQ63

DDR_SDQ59 DDR_DQ59

RP109 4P2R_22

1 4

2 3

RP130 4P2R_22

1 4

2 3

RP131 4P2R_22

1 4

2 3

RP110 4P2R_22

1 4

2 3

RP132 4P2R_22

1 4

2 3

RP92 4P2R_22

1 4

2 3

RP111 4P2R_22

1 4

2 3

RP93 4P2R_22

1 4

2 3

RP112 4P2R_22

1 4

2 3

RP94 4P2R_22

1 4

2 3

RP113 4P2R_22

1 4

2 3

RP95 4P2R_22

1 4

2 3

RP120 4P2R_22

1 4

2 3

RP96 4P2R_22

1 4

2 3

RP114 4P2R_22

1 4

2 3

RP97 4P2R_22

1 4

2 3

DDR_SDQ[0..63]

DDR_CB[0..7]

DDR _ S DQS[0..8]

RP127 4P2R_22

1 4

2 3

RP106 4P2R_22

1 4

2 3

RP128 4P2R_22

1 4

2 3

RP108 4P2R_22

1 4

2 3

RP129 4P2R_22

1 4

2 3

DDR_DQ0

DDR_DQ4

DDR_DQ1

DDR_DQ5

DDR_DQ6

DDR_DQS0

DDR_DQ2

DDR_DQ3

DDR_DQ8

DDR_DQ7

DDR_DQ9

DDR_DQ12

DDR_DQS1

DDR_DQ13

DDR_DQ10

DDR_DQ14

DDR_DQ15

DDR_DQ11

DDR_DQ16

DDR_DQ20

DDR_DQ21

DDR_DQ17

DDR_DQ18

DDR_DQS2

DDR_DQ19

DDR_DQ22

DDR_DQ24

DDR_DQ23

DDR_DQ25

DDR_DQ28

DDR_DQS3

DDR_DQ29

DDR_DQ56

DDR_DQ51

DDR_DQ60

DDR_DQ57

DDR_DQS7

DDR_DQ61

DDR_DQ62

DDR_DQ58

B

C

DDR_SDQ30

DDR_SDQ26

DDR_SDQ31

DDR_SDQ27

DDR_CB5

DDR_CB4

DDR_CB1

DDR_CB0

DDR_CB2

DDR_SDQS8

DDR_CB3

DDR_CB6

DDR_CB7

DDR_SDQ36

DDR_SDQ32

DDR_SDQ33

DDR_SDQ37

DDR_SDQ38

DDR_SDQS4

DDR_SDQ39

DDR_SDQ34

DDR_SDQ44

DDR_SDQ35

DDR_SDQ45

DDR_SDQ40

DDR_SDQS5

DDR_SDQ41

DDR_SDQ43

DDR_SDQ42

DDR_SDQ47

DDR_SDQ46

DDR_SDQ49

DDR_SDQ48

DDR_SDQ53

DDR_SDQ52

DDR_SDQ54

DDR_SDQS6

DDR_SDQ55

DDR_SDQ50

C

D

RP115 4P2R_22

1 4

2 3

RP98 4P2R_22

1 4

2 3

RP116 4P2R_22

1 4

2 3

RP99 4P2R_22

1 4

2 3

RP121 4P2R_22

1 4

2 3

RP100 4P2R_22

1 4

2 3

RP117 4P2R_22

1 4

2 3

RP122 4P2R_22

1 4

2 3

RP102 4P2R_22

1 4

2 3

RP123 4P2R_22

1 4

2 3

RP103 4P2R_22

1 4

2 3

RP118 4P2R_22

1 4

2 3

RP119 4P2R_22

1 4

2 3

RP101 4P2R_22

1 4

2 3

RP104 4P2R_22

1 4

2 3

RP124 4P2R_22

1 4

2 3

RP125 4P2R_22

1 4

2 3

RP105 4P2R_22

1 4

2 3

RP126 4P2R_22

1 4

2 3

RP107 4P2R_22

1 4

2 3

D

DDR_DQ30

DDR_DQ26

DDR_DQ31

DDR_DQ27

DDR_F_CB5

DDR_F_CB4

DDR_F_CB1

DDR_F_CB0

DDR_F_CB2

DDR_DQS8

DDR_F_CB3

DDR_F_CB6

DDR_F_CB7

DDR_DQ36

DDR_DQ32

DDR_DQ33

DDR_DQ37

DDR_DQ38

DDR_DQS4

DDR_DQ39

DDR_DQ34

DDR_DQ44

DDR_DQ35

DDR_DQ45

DDR_DQ40

DDR_DQS5

DDR_DQ41

DDR_DQ43

DDR_DQ42

DDR_DQ47

DDR_DQ46

DDR_DQ49

DDR_DQ48

DDR_DQ53

DDR_DQ52

DDR_DQ54

DDR_DQS6

DDR_DQ55

DDR_DQ50

E

DDR_DQ4

DDR_DQ5

DDR_DQS0

DDR_DQ3

DDR_DQ7

DDR_DQ12

DDR_DQ13

DDR_DQS1

DDR_DQ14

DDR_DQ11

DDR_CLK1<9>

DDR_CLK1#<9>

DDR_DQ20

DDR_DQ17

DDR_DQS2

DDR_DQ22

DDR_DQ23

DDR_DQ28

DDR_DQ29

DDR_DQS3

DDR_DQ26

DDR_DQ27

DDR_F_CB4

DDR_F_CB0 DDR_F_CB1

DDR_DQS8

DDR_F_CB6

DDR_F_CB7

DDR_CLK0<9>

DDR_CLK0#<9>

DDR_CKE1<9>

DDR_SCS#0<9>

DIMM_SMDATA<12,14>

DIMM_SMCLK<12,14>

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF

R&D DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DDR_CKE1 DDR_CKE0

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SBS0

DDR_SWE#

DDR_SCS#0 DDR_SCS#1

DDR_DQ36

DDR_DQ33

DDR_DQS4

DDR_DQ38

DDR_DQ39

DDR_DQ44

DDR_DQ45

DDR_DQS5

DDR_DQ43

DDR_DQ47

DDR_DQ49

DDR_DQ53

DDR_DQS6

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ60

DDR_DQS7

DDR_DQ62

DDR_DQ63

E

F

+2.5V +2.5V

JP25

1

VREF

3

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

+3VS

VDD_SPD

199

VDD_ID

DDR-SODIMM_200_Normal

Front side / H=5.2mm

F

DIMM0

G

DU/RESET#

DU/BA2

G

VREF

VDD

DM0

DQ12

VDD

DQ13

DM1

DQ14

DQ15

VDD

VDD

DQ20

DQ21

VDD

DM2

DQ22

DQ23

DQ28

VDD

DQ29

DM3

DQ30

DQ31

VDD

DM8

VDD

VDD

VDD

CKE0

VDD

RAS#

CAS#

DQ36

DQ37

VDD

DM4

DQ38

DQ39

DQ44

VDD

DQ45

DM5

DQ46

DQ47

VDD

CK1#

DQ52

DQ53

VDD

DM6

DQ54

DQ55

DQ60

VDD

DQ61

DM7

DQ62

DQ63

VDD

VSS

DQ4

DQ5

DQ6

VSS

DQ7

VSS

VSS

VSS

VSS

VSS

CB4

CB5

VSS

CB6

CB7

VSS

VSS

VSS

BA1

VSS

VSS

VSS

CK1

VSS

VSS

VSS

SA0

SA1

SA2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

A11

102

A8

104

106

A6

108

A4

110

A2

112

A0

114

116

118

120

122

S1#

124

DU

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DU

H

DDR_DQ0

DDR_DQ1

DDR_DQ6

DDR_DQ2

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ15

DDR_DQ16

DDR_DQ21

DDR_DQ18

DDR_DQ19

DDR_DQ24

DDR_DQ25

DDR_DQ30

DDR_DQ31

DDR_F_CB5

DDR_F_CB2

DDR_F_CB3

DDR_SMA11

DDR_SMA8

DDR_SMA6

DDR_SMA4

DDR_SMA2

DDR_SMA0

DDR_SBS1

DDR_SRAS#

DDR_SCAS#

DDR_DQ32

DDR_DQ37

DDR_DQ34

DDR_DQ35

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ46

DDR_DQ48

DDR_DQ52

DDR_DQ50

DDR_DQ51

DDR_DQ57

DDR_DQ61

DDR_DQ58

DDR_DQ59

DDR_SBS0<9>

DDR_SWE#<9>

DDR_SCAS#<9>

DDR_SRAS#<9>

DDR_SBS1<9>

H

SDREF_DIMM

12

C254

.1UF_0402

R229

I

DDR_DQ[0..63]

DDR_F_CB [0..7]

DDR_DQS[0..8]

12

SDREF

0_0402

DDR_SMA[0..12] <9>

DDR_SMA12

1 4

DDR_SMA9

2 3

DDR_SMA8

1 4