1

Standard ICs

LCD driver for segment-type LCDs

BU9728AKV

The BU9728AKV is a segment-type LCD system driver which can accommodate microcomputer control and a serial

interface. An internal 4-bit common output and LCD drive power supply circuit enable configuration of a display system at low cost.

•

Applications

Movie projectors, car audio systems, telephones

•

Features

1) Serial interface. (8-bit length)

2) Display RAM: Internal, 128 bits. (up to 128 segments can be displayed)

3) Internal power supply circuit for LCD drive.

4) Display duty: 1 / 4

5) Can be driven with low voltage and low current dissipation.

•

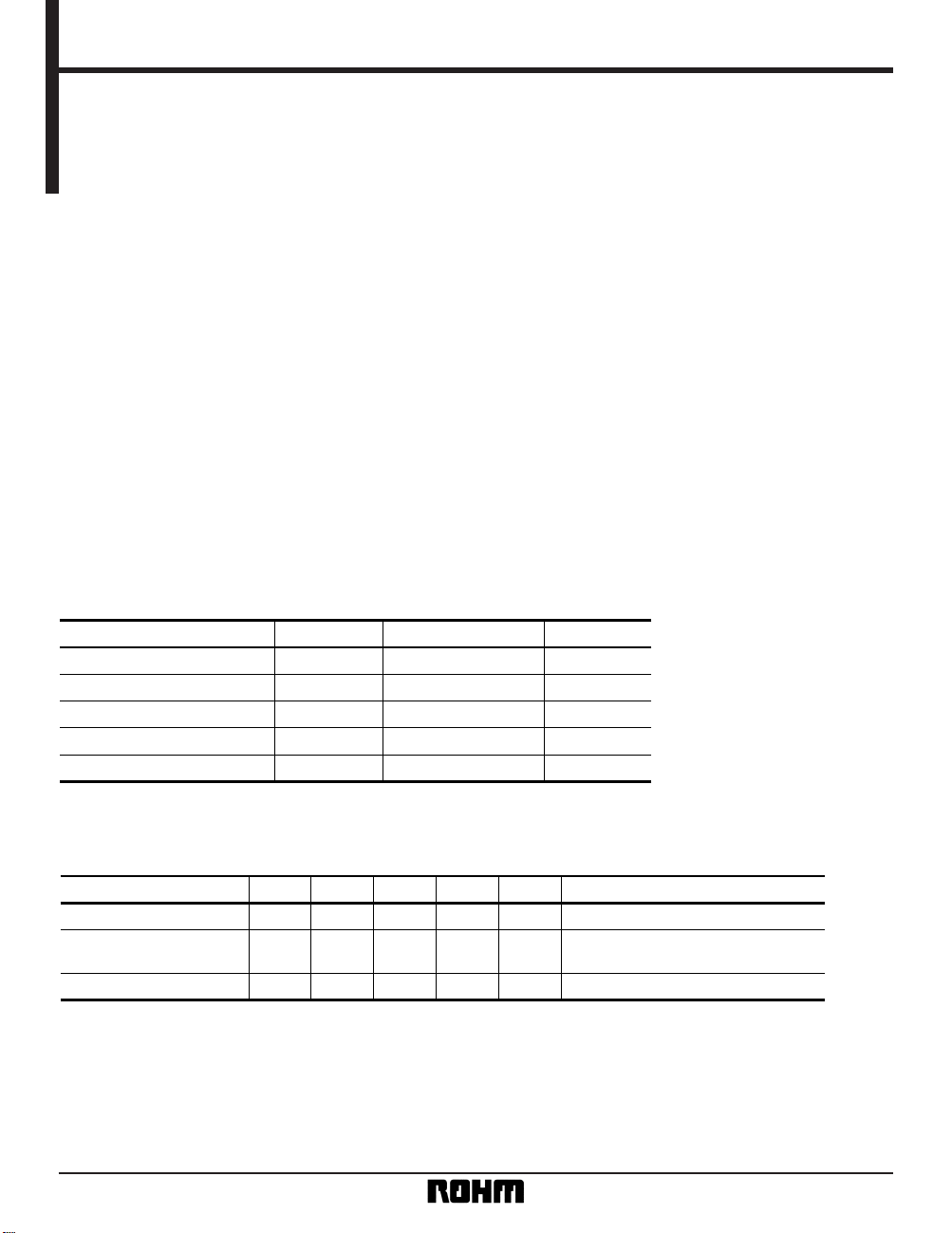

Absolute maximum ratings (Ta = 25°C, VSS = 0V)

Parameter Symbol Limits Unit

V

DD

– 0.3 ~ + 7.0 V

V

LCD

– 0.3 ~ + VDD

V

Pd 400

∗

mW

Tstg – 55 ~ + 125 °C

Topr – 20 ~ + 75 °C

Power supply voltage 1

Power supply voltage 2

Power dissipation

Operating temperature

Storage temperature

∗

Reduced by 4.0mW for each increase in Ta of 1°C over 25°C .

•

Recommended operating conditions (Ta = 25°C, VSS = 0V)

Parameter

V

DD 2.5 5.5 V—

—

V

LCD 0VDD V

The following relationship should

be maintained: V

DD

⭌ V1 ⭌ V2 ⭌ V3 ⭌ VSS.

Rf = 470kΩ

—

f

OSC — — kHz36

Symbol Min. Typ. Max. Unit

Conditions

Power supply voltage 1

Power supply voltage 2

(V

DD - V3)

Oscillation frequency

2

Standard ICs BU9728AKV

•

Block diagram

Serial

Interface

Display Data RAM

(DD RAM)

LCD Driver

Bias Circuit

LCD

Segment

Driver

32bits

LCD

Common

Driver

4bits

SD

SCK

C / D

CS

RESET

V

DD

V1

V2

V3

VSS

COM0

COM1

COM2

COM3

SEG0

SEG1

SEG31

OSC1

OSC2

Timing

Generator

Address

Counter

Common

Counter

Command

Decoder

Command / Data

Register

•

Pin assignments

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

37

38

39

40

41

42

43

44

45

46

47

48

24

23

22

21

20

19

18

17

16

15

14

13

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

OSC1

OSC2

V1V2V3

VSS

VDD

SCK

SD

CS

C / D

COM

0

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

RESET

COM

3

COM2

COM1

252627282930313233343536

121110987654321

BU9728AKV

3

Standard ICs BU9728AKV

•

Pin descriptions

OSC1

OSC2

1

2

I

O

SD 9 I

CS 10 I

I

—

—

—

SCK 8

V

1 ~ V3 3 ~ 5

V

SS 6

V

DD 7

C / D 11 I

COM

0

COM3

12 ~ 15 O

RESET 16 I

SEG

0

SEG31

17 ~ 48 O

Pin NO. I / OPin name Function

Input / output pins for the internal oscillator. Resistance is connected between

these pins when the internal clock is running. When an external clock is

running, the clock is input from OSC

1 and OSC2 is left open.

This is the reset input pin. When this pin is LOW, the BU9728AKV is initialized.

It resets the address counter and turns the display off.

This is the serial data input pin, used to input display data and commands.

Display data is displayed when this is "1" and not displayed when it is "0".

This is the chip select signal input pin. When this pin is LOW, SD input can be

received. The SCK counter is reset when the CS pin goes from HIGH to LOW.

This signal detects whether the SD input is command or display data. If the pin

is LOW at the rising edge of the 8th SCK pulse, the input is recognized as

display data, and if HIGH, the input is recognized as command data.

These are power supply pins for LCD drive.

The following relationship must be satisfied: V

DD ⭌ V1 ⭌ V2 ⭌ V3 ⭌ VSS (Low) .

These are the segment output pins for LCD drive. They are connected to the

LCD panel segments.

These are the common output pins for LCD drive. They are connected to the

LCD panel commons.

This is the shift clock input pin for serial data. The contents of the SD pin are

read one bit at a time at the rising edge of SCK.

This is the V

SS power supply pin.

This is the V

DD power supply pin.

•

Input / output equivalent circuits

VDD

GND

GND

VDD

V

DD

GND

GND

OUT

V

LCD

VLCD

IN

OSC1

IN

OSC

2

I / O

SD

SCK

C / D

CS

I

—

OSC

1

OSC2

RESET I

I / O

SEG

0

SEG31

COM0

COM3

O

~ ~

Pin name

Equivalent Circuit

Pin name

Equivalent Circuit

4

Standard ICs BU9728AKV

•

Electrical characteristics

DC characteristics (unless otherwise noted, V

DD = 2.5 ~ 5.5V, VSS = 0V, Ta = 25°C)

Parameter Symbol Min. Typ. Max. Unit Conditions Pin

Input low level current 1

I

IL1

——

100

µ

AV

IN

=

0V

Input low level current 2

I

IL2

——

2

µ

AV

IN

=

0V

Input high level voltage

V

IH1

0.8

—

V

DD

V

Input low level voltage

V

IL1

0

—

—

—

0.2

V

LCD driver ON resistance

∗

1

R

ON

——

30 k

Ω

∆V

ON

=

0.1V

Input high level current

I

IH

–

2

——µ

AV

IN

=

V

DD

Input capacitance

C

IN

—

5

—

pF

RESET

RESET

OSC

1

, SD, SCK, C / D, CS

OSC

1

, SD, SCK, C / D, CS

RESET

SEG

0 ~ 31

, COM

0 ~ 3

OSC1, SD, SCK, C / D, CS,

SD, SCK, C / D, CS

—

0.05 1

µ

A

In wait state

∗

2

When display is operating

∗

3

During access operation

∗

4

Current dissipation

I

DD

—

40 80

µ

AV

DD

—

100 250

µ

A

∗

1 Internal power supply impedance is not included in the LCD driver ON resistance.

∗

2 All inputs, including V3 = 0V and OSC1, are fixed at either VDD or VSS.

∗

3 Except for V3 = 0V, Rf = 470kΩ , and OSC1, all inputs are fixed at either VDD or VSS.

∗

4 V3 = 0V, Rf = 470kΩ , f

SCK

= 200kHz

—

×

V

DD

×

V

DD

AC characteristics (unless otherwise noted, VDD = 2.5 ~ 5.5V, VSS = 0V, Ta = 25°C)

Parameter Symbol Min. Typ. Max. Unit Conditions

t

CYC 800 — — ns

t

WAIT 800 — — ns

t

WH1 300 — — ns

t

TLH — — 100 ns

t

THL — — 100 ns

t

WL1 300 — — ns

t

SU1 100 — — ns

t

H1 100 — — ns

t

WH2 300 — — ns

t

WL2 6400 — — ns

∗

5 Only one (either one) of the conditions needs to be satisfied.

tSU3 100 — — ns

t

H3 100 — — ns

t

CCH 100 — — ns

t

SCH 100 — — ns

t

SU2 100 — — ns

t

H2 100 —

—

—

—

—

—

—

—

—

—

—

—

—

——ns

Use rise for 8th CK of SCK as standard

Use CS riss as standard

Use rise for 8th CK of SCK as standard

SCK rise time

SCK fall time

SCK cycle time

Command wait time

SCK pulse width

"H"

SCK pulse width

"L"

Data setup time

Data hold time

CS pulse width

"H"

CS pulse width

"L"

CS set-up time

CS hold time

C / D set-up time

C / D hold time

C / D - CS time

∗

5

C / D - SCK time

∗

5

5

Standard ICs BU9728AKV

•

Timing charts

tWL2

tSU2

CS

SCK

SD

C / D

t

H2

tWH2

tCCH

tCYC

tWH1

tWL1

tSU1

tSCH

tH1

tTLH tTHL

tSU3 tH3

Fig.1 Interface timing

SCK

SD

tWAITtCYC

D7 D6 D0 D7

Fig.2 Command cycle

•

Data format

Serial data is 4-line data transmitted in synchronization with the clock. Serial data with a bit length of 8 bits is input in

synchronization with SCK. If C / D is HIGH at the rising edge of the 8 × nth SCK clock pulse, the serial data is recognized as command data, and if C / D is LOW, the serial data is recognized as display data. Serial data is input in

sequential order, starting from the MSB.

6

Standard ICs BU9728AKV

•

A detailed look at commands

The BU9728AKV has the following commands (C / D is HIGH at 8 × nth clock pulse of SCK).

(1) Address Set

AAAAA and the address data displayed in binary format are set in the address counter. Each time input of the

display data (8 bits) has been completed, the address is incremented by + 2.

(2) Display On

All display segments light, regardless of the contents of the Display Data RAM (DDRAM). The contents of the

DDRAM do not change.

(3) Display Off

All display segments go out, regardless of the contents of the DDRAM. The contents of the DDRAM do not

change.

(4) Display Start

Display begins, in accordance with the contents of the DDRAM.

(5) Rewrite Display Data RAM (DDRAM)

The binary bit data DDDD is written to the DDRAM. The data is written to the address specified by the Address

Set command, and after this command is executed, the address is automatically incremented by + 1.

(6) Reset

This command should be executed before any other command, immediately after the power supply is turned on.

This command resets the BU9728AKV to the following status:

• Display is off

• Address counter is reset

0

MSB LSB

0 0 A A A A A

0

MSB LSB

0 1

∗ ∗ ∗ ∗ ∗

∗

Irrelevant

0

MSB LSB

1 0

∗ ∗ ∗ ∗ ∗

∗

Irrelevant

0

MSB LSB

1 1

∗ ∗ ∗ ∗ ∗

∗

Irrelevant

1

MSB LSB

0 0

∗

D D D D

∗

Irrelevant

1

MSB LSB

1 0

∗∗∗∗∗

∗

Irrelevant

•

Description of functions

(1) Register

The BU9728AKV has a command / data register configured of eight bits. Serial data is read in 8-pulse units of the

SCK clock.

If the data read to the register is display data (C / D is LOW at the 8th clock pulse of SCK), it is written to the

DDRAM, and if the data is command data (C / D is HIGH at the 8th clock pulse of SCK), it is output to a command

decoder and used to control the BU9728AKV.

(2) Address counter

The address counter indicates the DDRAM address. When the set address is written to the command / data register,

the address data is automatically sent to the address counter.

After the data is written to the DDRAM, the address counter is automatically incremented by either + 1 or + 2. The

amount by which the counter is incremented is determined automatically, based on the following statuses:

8 bits written to DDRAM (C / D LOW at 8th clock pulse of SCK) → + 2

4 bits written to DDRAM (C / D HIGH at 8th clock pulse of SCK) → + 1

When the address counter reaches 1FH, it will be reset back to 00H the next time it is incremented.

(3) Display Data RAM (DDRAM)

The Display Data RAM (DDRAM) is where displays are stored. The capacity of the DDRAM is 32 addresses × 4 bits.

The illustration below shows the relationship between the DDRAM and the display positions.

DDRAM addresses set in the address counter are in hexadecimal format and are indicated as follows.

(Example) For a DDRAM address of “14” (display position: SEG

20)

7

Standard ICs BU9728AKV

00

0

1

2

bit

DDRAM address

3

COM

0

COM1

COM2

COM3

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG29

SEG30

SEG31

01 02 03 04 05 06 07 1D 1E 1F

AC4

MSB LSB

AC3 AC2 AC1 AC0

1

MSB LSB

0 1 0 0

1

4

8

Standard ICs BU9728AKV

The display data input to the command / data register (when C / D is LOW) is written to the DDRAM address and the

address consisting of the specified address + 1, which are indicated by the upper four and lower four bits of the data,

respectively. The four bits of the display data are written sequentially, starting from the MSB, to the MSB of the

DDRAM bits.

If the Rewrite DDRAM command is input (C / D is HIGH), the four bits of the display data in the Rewrite DDRAM

command are written to the specified DDRAM address.

The four bits of the display data are written sequentially, starting from the MSB, to the MSB of the DDRAM bits.

(4) Timing generator

Connecting Rf between OSC

1 and OSC2 causes the internal oscillator circuit to start oscillating, and generates a dis-

play timing signal. The oscillator can also be started by inputting an external clock.

(5) LCD drive power supply

The LCD drive power supply is generated by the BU9728AKV. The LCD drive voltage (V

LCD) is supplied by VDD - V3,

and the power supply is generated by V

1 = 2 • VLCD / 3, V2 = VLCD / 3.

If an external bleeder resistance is used to supply the LCD drive voltage externally, the following relationship must

be observed:

V

DD = V1 ⭌ V2 ⭌ V3 ⭌ VSS

(6) LCD drive circuit

The LCD drive circuit is configured of four common drivers and 32 segment drivers. When oscillation begins, selected waveforms are output automatically for valid common outputs by the common counter, and de-selected waveforms are output for other outputs.

For segment outputs, drive waveforms are output automatically by the display data and common counter.

The following page shows examples of common / segment output waveforms.

(bit3 bit0) (bit3 bit0)

D7

MSB LSB

D6 D5 D4 D3 D2 D1 D0

Specified address Specified address + 1

(bit3 bit0)

1

MSB LSB

0 0

∗

D3 D2 D1 D0

Rewrite DDRAM command Display data

Fig. 3 Rf oscillator circuit

OSC1

OSC2

Rf

Fig. 5 Example of connection when

using internal power supply

VDD

V1

V2

V3

VSS

Fig. 6 Example of connection when

using external power supply

VDD

V1

V2

V3

VSS

Fig. 4 External clock input

OSC1

OSC2 OPEN

EXIT CLOCK INPUT

9

Standard ICs BU9728AKV

•

LCD drive waveforms

Frame cycle

V

DD

COM0

COM1

COM2

COM3

V1

V2

V3

VDD

V1

V2

V3

VDD

V1

V2

V3

VDD

V1

V2

V3

VDD

V1

V2

V3

VDD

COM0 COM1 COM2 COM3

0 0 0 0

Display none of the segments COM

0 to 3.

1 0 0 0

Display segment which

applies to COM

0.

0 1 0 0

Display segment which

applies to COM

1.

0 1 0 1

Display segments which

apply to COM

1 and COM3.

1 1 1 1

Display segments which

apply to COM

0 to COM3.

V

1

V2

V3

VDD

V1

SEG0

SEG31

V2

V3

VDD

V1

V2

V3

VDD

V1

V2

V3

~

10

Standard ICs BU9728AKV

•

External dimensions (Units: mm)

VQFP48

0.5

0.125 ± 0.1

0.10

0.2 ± 0.1

9.0 ± 0.3

7.0

±

0.2

9.0 ± 0.3

7.0

±

0.2

48

37

1

12

13

24

2536

0.5

1.425

±

0.1

0.10

Loading...

Loading...