A

USB Audio Decoder ICs

AAC/WMA/MP3

+SD Memory Card+iPod

BU94604BKV

●Description

BU94604BKV is AAC+WMA+MP3 decoder IC which contains USB host and SD card I/F,

audio DAC, system controller, regulator for internal CORE power supply.

For using of this LSI, it is necessary to become a licensee of Apple Inc. regarding "Made for iPod/iPhone/iPad License".

●Features

1) USB2.0 Full Speed host I/F function contained.

2) Protocol conversion from I2C to USB HID or from USB HID to I2C.

3) SD card I/F function contained.

2

4) I

C I/F function contained.

5) FAT analysis function contained.

6) MP3 decode function contained. (available for MPEG1, 2 and 2.5, Layer 1, 2 and 3)

7) WMA decode function contained. (available for WMA9 standard and not available for DRM)

8) AAC decode function contained. (available for MPEG4 AAC-LC and not available for DRM)

9) Sample Rate Converter contained.

10) System Controller contained.

11) LED Controller contained.

12) KEY matrix Controller contained.

13) Stand Alone mode contained.

14) External processor can control. (Slave mode)

15) Audio DAC contained.

16) Sound Effect function contained.

17) Digital Audio Out(I

18) File Name, Folder Name Sorting.

19) ID3TAG and WMATAG and AACTAG Analysis.

20) Reading a specified file data is possible from USB memory.

21) LUN is selectable.

22) Regulator for internal CORE power supply contained.

23) VQFP64pin(0.5mm pitch)

●Applications

Audio products, etc.

2

S, S/PDIF) function contained.

No.12080EAT03

www.rohm.com

1/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

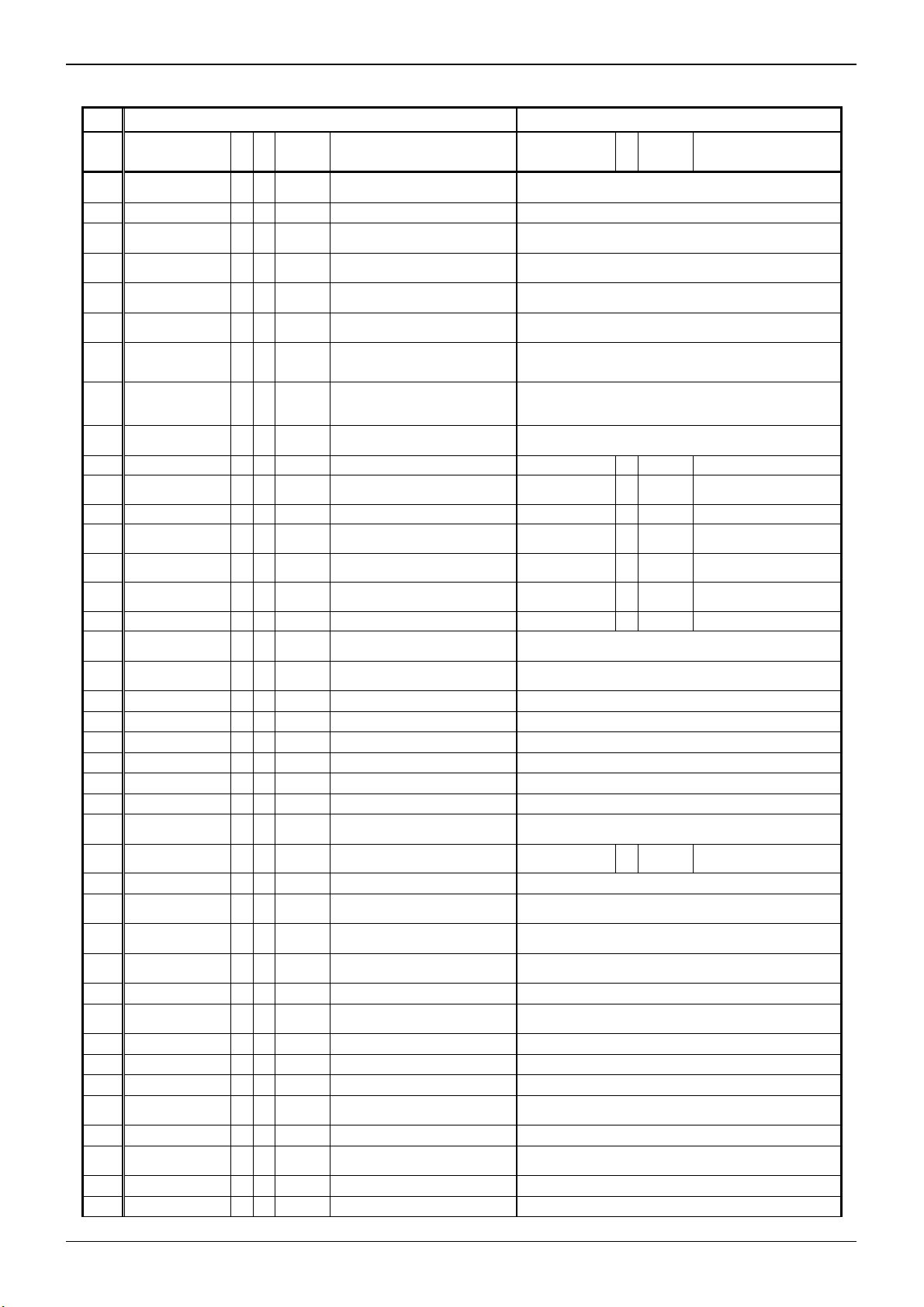

●Absolute maximum ratings (Ta = 25℃)

Parameter Symbol Limits Unit Comment

Supply voltage(Analog, I/O) VDD1MAX

Input voltage VIN

Storage temperature range TSTG

Operating temperature range TOPR

Power dissipation *1 PD 750 mW

*1:In the case of use at Ta=25℃ or more, 7.5mW should be reduced per 1℃.

Radiation resistance design is not arranged.

●Operating conditions (Ta = 25℃)

Parameter Symbol Limits Unit Comment

Supply voltage(Analog, I/O) VDD1

-0.3~4.5

-0.3 ~ VDD1 + 0.3

-55~125 ℃

-40~85 ℃

3.0~3.6 V DVDDIO,VDD_PLL,

V DVDDIO, VDD_PLL,

V

Technical Note

DAVDD, AVDDC

DAVDD, AVDDC

www.rohm.com

2/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

Technical Note

Ⅰ .Electrical characteristics

(Unless specified, Ta=25℃、VDD1=3.3V, DVSS=AVSSC=VSS_PLL=DAVSS=0V, XIN_PLL=16.9344MHz)

Parameter Symbol

MIN. TYP. MAX.

Limits

Unit Condition

<Total >

Circuit current (VDD1 USB1) IDD1USB1

- 65 80

mA *1 When USB memory is

played.

Circuit current (VDD1 SD1) IDD1SD1 - 35 50 mA *1 When SD card is played.

<Digital block>

H-Level input voltage VIH VDD1*0.7 - VDD1 V *3

L-Level input voltage

H-Level output voltage1

L-Level output voltage1

H-Level output voltage2

L-Level output voltage2

H-Level output voltage3

L-Level output voltage3

H-Level output voltage4

L-Level output voltage4

VIL DVSS - VDD1*0.3 V *3

VOH1 VDD1-0.4 - VDD1 V IOH=-1.6mA, *4

VOL1 0 - 0.4 V IOL=1.6mA. *4

VOH2 VDD1-0.4 - VDD1 V IOH=-3.6mA, *5

VOL2 0 - 0.4 V IOL=3.6mA, *5

VOH3 VDD1-0.4 - VDD1 V IOH=-0.6mA, *6

VOL3 0 - 0.4 V IOL=0.6mA, *6

VOH4 VDD1-1.0 - VDD1 V IOH=-0.6mA, *7

VOL4 0 - 1.0 V IOL=0.6mA, *7

<USB-HOST >

H-Level input

VIHUSB VDD1*0.6 - VDD1 V *8

voltage

L-Level input voltage

VILUSB AVSSC - VDD1*0.3 V *8

Output impedance(H) ZOH 22.0 45.0 60.0 Ω *8

Output impedance(L) ZOL 22.0 45.0 60.0 Ω *8

H-Level output

VOHUSB VDD1-0.5 - VDD1 V *8

voltage

L-Level output voltage

VOLUSB 0 - 0.3 V *8

Rise/Fall time Tr/Tf - 11 - ns *8, Output capacity 50pF

Voltage of crossing point VCRS - VDD1/2 - V *8, Output capacity 50pF

Range of differential input VDIFF 0.8 - 2.5 V *8

Differential input sensitivity VSENS 0.2 - - V *8

Pull-down resistance RPD 14.25 15.0 24.8 kΩ *8

<Audio DAC>

Distortion rate THD - 0.02 - % 1kHz, 0dB, sine, *9

Dynamic range DR - 88 - dB 1kHz, -60dB, sine, *9

S/N ratio S/N - 96 - dB *9

Max output level VSMAX - 0.92 - Vrms 1kHz, 0dB, sine, *9

*1 3.3V system I/O, Analog Power supply(VDD1), 1kHz, 0dB, sine-wave playing

*3 1-7, 9-17, 19-20, 25-26, 28-30, 40, 49-52, 56, 58-61, 63 pin

*4 8, 10-11, 14-16, 48-55 pin

*5 13 pin

*6 21-23, 26 pin

*7 41 pin

*8 33, 34 pin

*9 44, 46 pin

www.rohm.com

3/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

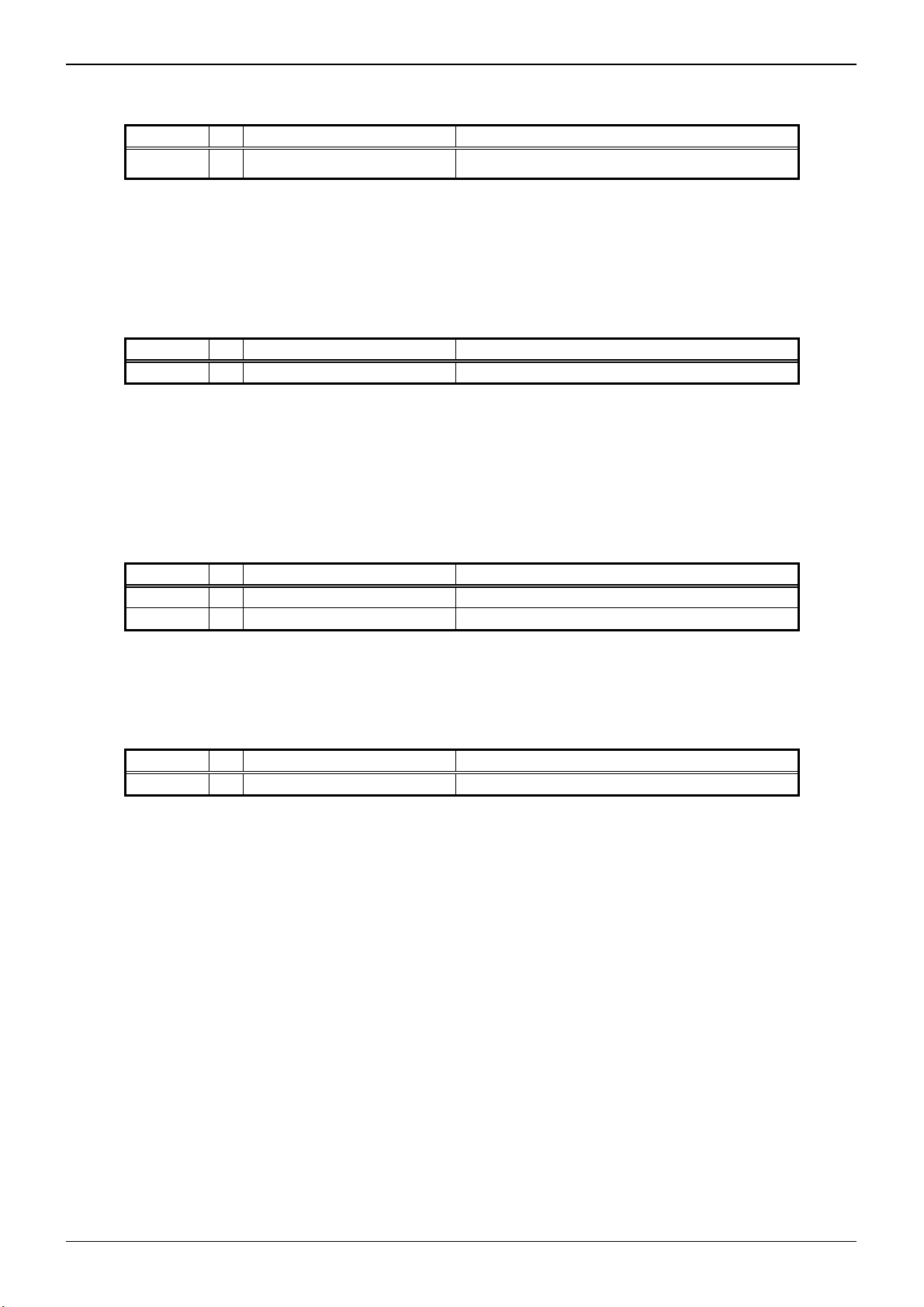

Ⅱ . Block diagram

LED_ERROR/TEST9

LED_PLAY/TEST10

LED_PSD/TEST11

LED_PUSB/TEST12

LED_ACCESS/LRCK

/SPDIF

LED_RANDOM/BCK

LED_REPEAT/DATA

TEST13

DVDD_M1

TEST14

TEST15

TEST16

TEST17

DVSS

TMODE

DVDDIO

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

USB_DP

AVSSC

43 42 41 4047 46 45 4448

DAVSS

VSS_PLL

XOUT_PLL

XIN_PLL

TEST_PLL

39 38 37 36 35 34 33

VDD_PLL

VOREFI

PLL

REXTI

USB

PHY

DAVDD

LDACO

VCDACO

RDACO

AMUTE

Audio DAC

USB

Sound Effecter

Controller

FAT

File system

AAC / WMA /

LDO

MP3

Decoder

SD I/F

Controller

System

Controller

12345678910111213141516

IRPTO

TEST2

RESETX

SEL_SLAVE

SEL_MP3

SEL_DOUT

SEL_VOL

SEL_APLAY

SEL_UTPKT

Block diagram

MCHNG

KEY_ROW1/

BUSY

KEY_ROW2/

I2C I/F

Controller

KEY_ROW3/SCL

KEY_ROW4/SDA

KEY_COL1/A0

KEY_COL2/A1

Technical Note

USB_DM

32

AVDDC

31

ATEST1

30

TEST8

29

TEST7

28

TEST6

27

DVDD_M2

26

TEST5/CLKOUT12

25

TEST4

DVSS

24

SD_CS

23

22

SD_DI

21

SD_CLK

SD_DO

20

SD_CON

19

DVDDIO

18

17

TEST3

SEL_SMAN

KEY_COL3/

www.rohm.com

4/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

y

)

g

)

y

)

)

)

)

)

y

y

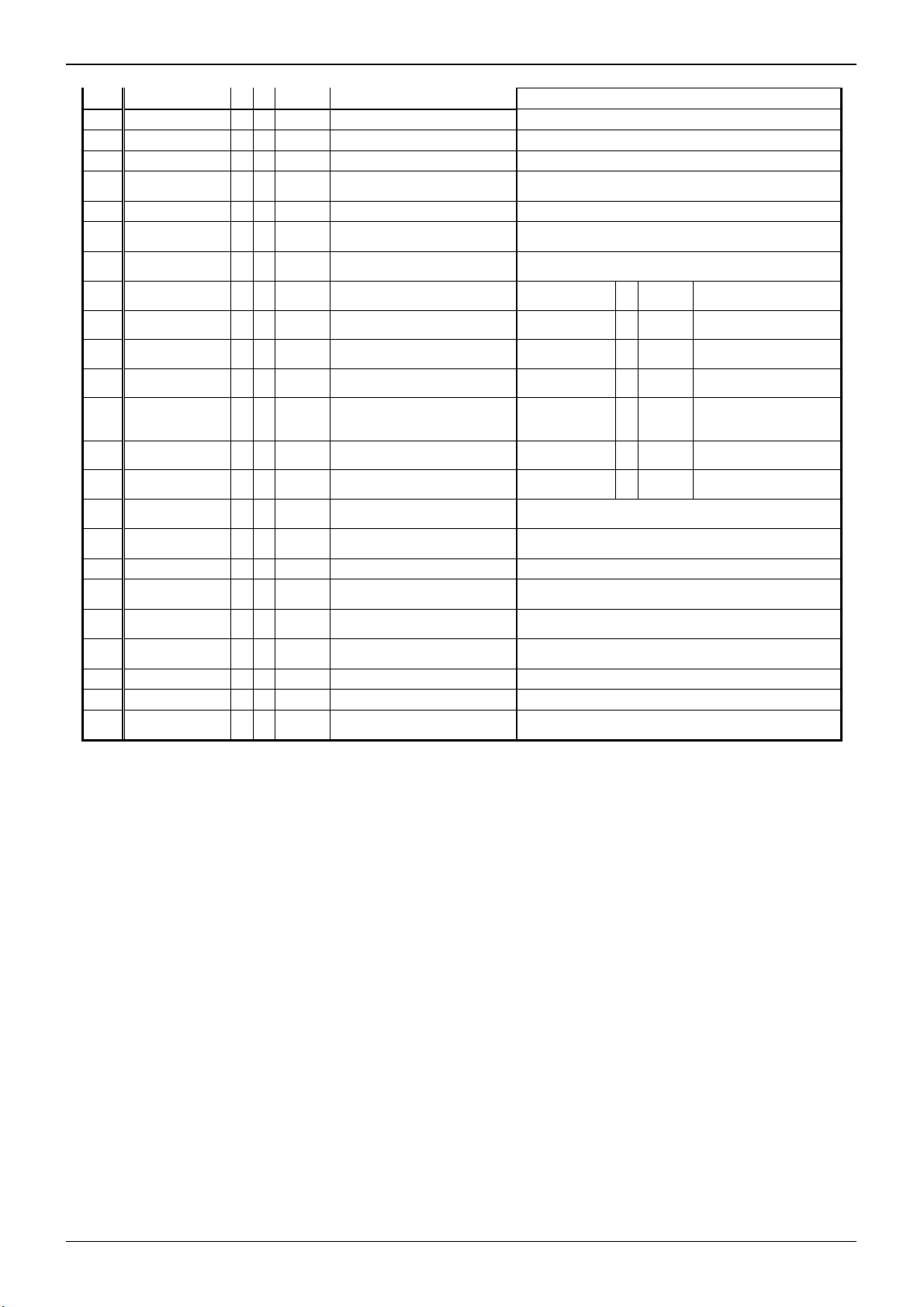

Ⅲ . Description of Terminals

STAND ALONE MODE(MODE1) SLAVE MODE(MODE2,MODE3)

Pin

Signal Name

No.

1 RESETX A I PU

2 SEL_SLAVE B I PU(*1) H: STAND ALONE, L:SLAVE ←

3 SEL_MP3 B I PU(*1)

4 SEL_DOUT B I PU(*1)

5 SEL_VOL B I PU(*1)

6 SEL_APLAY B I PU(*1)

7 SEL_UTPKT B I PU(*1)

8 IRPTO B O -

9 TEST2 - I PU

10 KEY_ROW1 B I PU KEY Input ROW1 MCHNG O - Music change Output

11 KEY_ROW2 B I PU KEY Input ROW2 BUSY O -

12 KEY_ROW3 B I PU KEY Input ROW3 SCL I - I2C I/F Clock Input

13 KEY_ROW4 B I PU KEY Input ROW4 SDA I/O -

14 KEY_COL1 B O - KEY Input COLUMN1 A0 I -

15 KEY_COL2 B O - KEY Input COLUMN2 A1 I -

16 KEY_COL3 B O - KEY Input COLUMN3 SEL_SMAN I PU(*1) H: MODE2, L: MODE3

17 TEST3 B I PU

18 DVDDIO - - -

19 SD_CON B I - SD I/F (*2) ←

20 SD_DO B I - SD I/F (*2) ←

21 SD_CLK B O - SD I/F ←

22 SD_DI B O - SD I/F ←

23 SD_CS B O - SD I/F ←

24 DVSS - - - Connect to GND ←

25 TEST4 - I PU

26 TEST5 - I PU

27 DVDD_M2 - - - Connect to 57PIN ←

28 TEST6 - I -

29 TEST7 - I -

30 TEST8 - I -

31 ATEST1 - O - OPEN (for TEST) ←

32 AVDDC - - -

33 USB_DM C I/O - USB DATA- ←

34 USB_DP C I/O - USB DATA+ ←

35 AVSSC - - - Connect to GND ←

36 REXTI D O -

37 VOREFI - O - OPEN (for TEST) ←

38 VDD_PLL - - -

39 TEST_PLL - I - OPEN (for TEST) ←

40 XIN_PLL E I - X'tal Input 16.9344MHz ←

I/O

Cir

I/O

Pull-Up/

Down

Function Signal Name I/O

H: Release RESET,

L: RESET

H: PLAY MP3 ONLY,

L: PLAY MP1,MP2 and MP3

H: ANALOG DAC Output,

L: Digital Output

H: Volume control valid,

L: Volume control invalid

H: Auto Play OFF ,

L: Auto Pla

H: Normal Operation

L: USB Test Packet Output

Device (Have 2 configuration

or more) connection’s

interruption output terminal

Pull-up to 3.3V system power

supply (for TEST

Pull-up to 3.3V system power

supply (for TEST

Connect to 3.3V

System Power Suppl

Pull-up to 3.3V system power

supply (for TEST

Pull-up to 3.3V system power

supply (for TEST

Pull-up to 3.3V system power

supply (for TEST

Pull-up to 3.3V system power

supply (for TEST

Pull-up to 3.3V system power

supply (for TEST

Connect to 3.3V

System Power Suppl

Connect Bias Resistor

to GND

Connect to 3.3V

System Power Suppl

CLKOUT12(*3)

Pull-Up/

Down

←

←

←

←

←

←

←

←

←

←

←

I/O

PU(*3) 12MHz CLK Output.

(*3)

←

←

←

←

←

←

Technical Note

Function

Command

Operation Busy Fla

I2C I/F Data

Input/Output

I2C I/F Slave

Address Set0

I2C I/F Slave

Address Set1

www.rohm.com

5/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

y

(

)

y

y

y

y

)

r

)

)

)

y

41 XOUT_PLL E O - Connect to X'tal 16.9344MHz ←

42 VSS_PLL - - - Connect to GND ←

43 DAVSS - - - Connect to GND ←

44 RDACO F O - Audio DAC Line Output Rch ←

45 VCDACO F O -

Audio DAC

Reference Voltage Output

46 LDACO F O - Audio DAC Line Output Lch ←

47 DAVDD - - -

48 AMUTE G O -

Connect to 3.3V

System Power Suppl

Audio Mute Output

H:Mute Cancel, L:Mute

49 LED_ERROR B O - Error LED Output TEST9 I PU

50 LED_PLAY B O - Play LED Output TEST10 I PU

51 LED_PSD B O - Play SD Card LED Output TEST11 I PU

52 LED_PUSB B O - Play USB LED Output TEST12 I PU

53(*3) LED_ACCESS B O - Memory Access LED Output

LRCK

/SPDIF(*4)

54(*3) LED_RANDOM B O - Random Play LED Output BCK(*4)

55(*3) LED_REPEAT B O - Repeat Play LED Output DATA(*4)

56 TEST13 - I PU

57 DVDD_M1 - - -

Pull-up to 3.3V system power

supply (for TEST

Connect to

Bypass Condense

I/O

(*4)

I/O

(*4)

I/O

(*4)

58 TEST14 F I - Connect to GND ←

59 TEST15 - I -

60 TEST16 - I -

61 TEST17 - I -

Pull-up to 3.3V system power

supply (for TEST

Pull-up to 3.3V system power

supply (for TEST

Pull-up to 3.3V system power

supply (for TEST

62 DVSS - - - Connect to GND ←

63 TMODE H I - Connect to GND ←

64 DVDDIO - - -

Connect to 3.3V

System Power Suppl

*1 When L is input, Pull-UP turns OFF.

*2 When SD I/F is disused, pull-up to 3.3V system power supply.

*3 Enabled/Disabled can be selected using commands.

This pin becomes output and pull-up is OFF, only when 12MHz clock output is enable.

*4 In STAND ALONE MODE (MODE1),

When ANALOG DAC output is selected (SEL_DOUT=H), LED output is enabled.

When the Digital output is selected (SEL_DOUT=L), the I2S format audio output is enabled.

In SLAVE MODE (MODE2, MODE3),

When the ANALOG DAC output is selected (SEL_DOUT=H), these pins are TEST terminals.

When the Digital output is selected (SEL_DOUT=L), you can select I2S format audio output or digital audio

interface output (SPDIF).

See Chapter Ⅴ.4 for further information.

Technical Note

←

←

←

Pull-up to 3.3V system

power suppl

Pull-up to 3.3V system

power suppl

Pull-up to 3.3V system

power suppl

Pull-up to 3.3V system

power suppl

PU(*4)

PU(*4) I2S Output Bit Clock

PU(*4) I2S Output LR DATA

I2S Output

LR Clock /

SPDIF Output

←

←

←

←

←

←

www.rohm.com

6/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

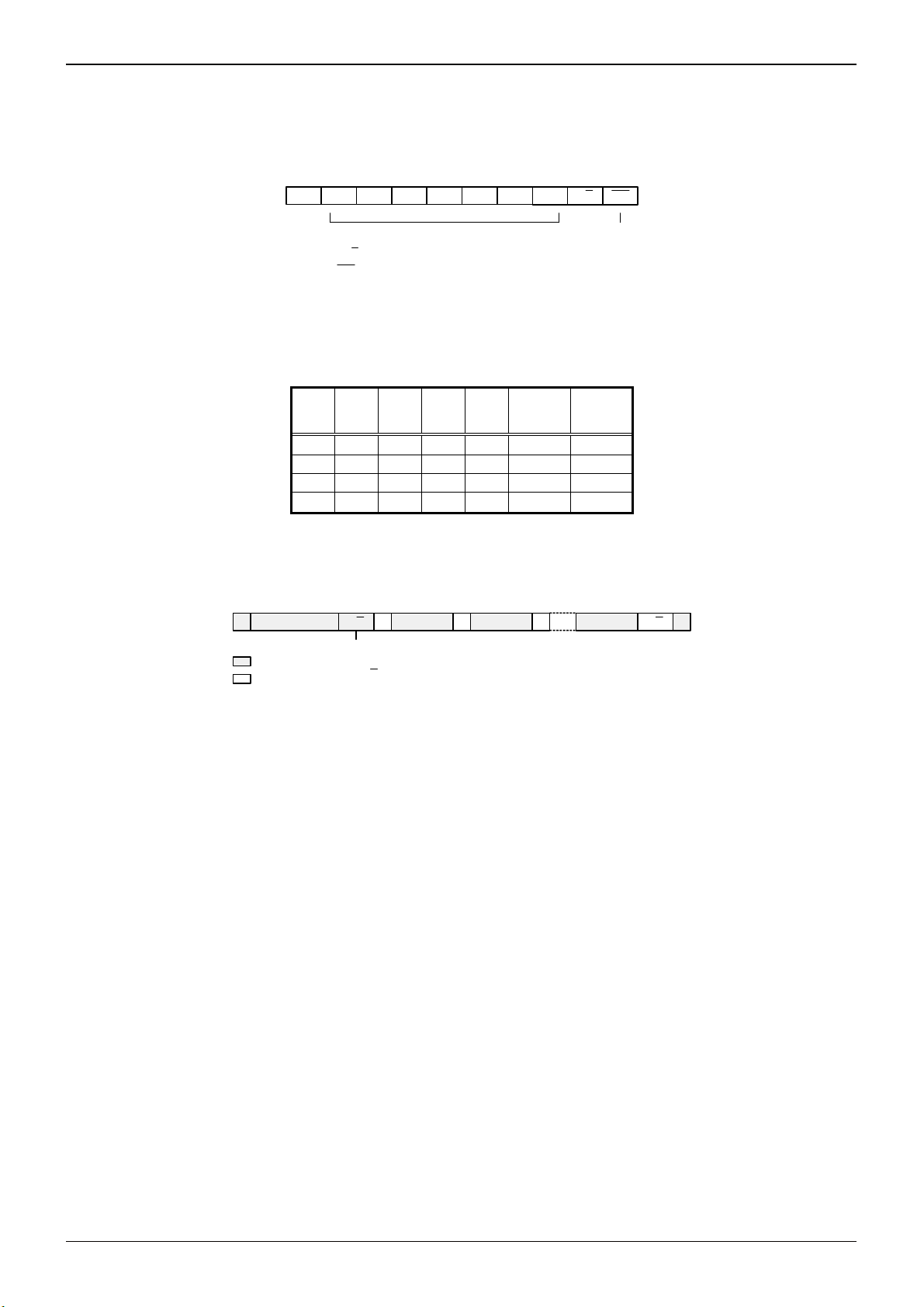

Ⅳ. Terminal equivalent circuit diagram

A B C D

DVDDIO

DVDDIO

DVDDIO

DVDDIO

Technical Note

D

P

D

M

AVDDC

AVDDC

15KΩ

DVSSIO

DVSSIO

15KΩ

AVSSCAVSSC

AVSSC

E F G H

VDD_PLL

XIN

VSS_PLL

VDD_PLL

XOUT

VSS_PLL

DAVDD

DAVSS

DVDDIO

DVSSIO

DVDDIO

DVSSIO

I/O terminal equivalent circuit diagram

www.rohm.com

7/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

X

X

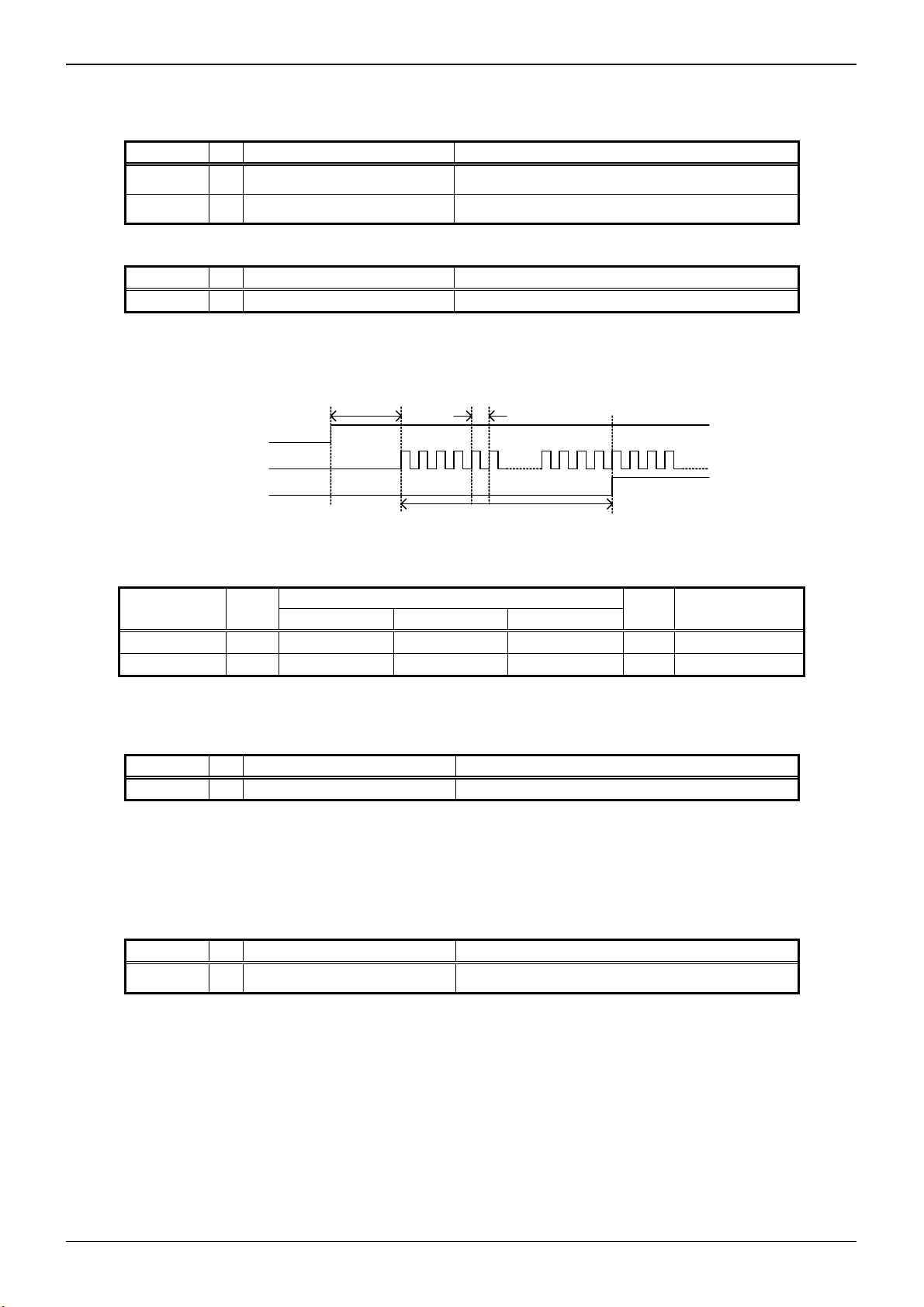

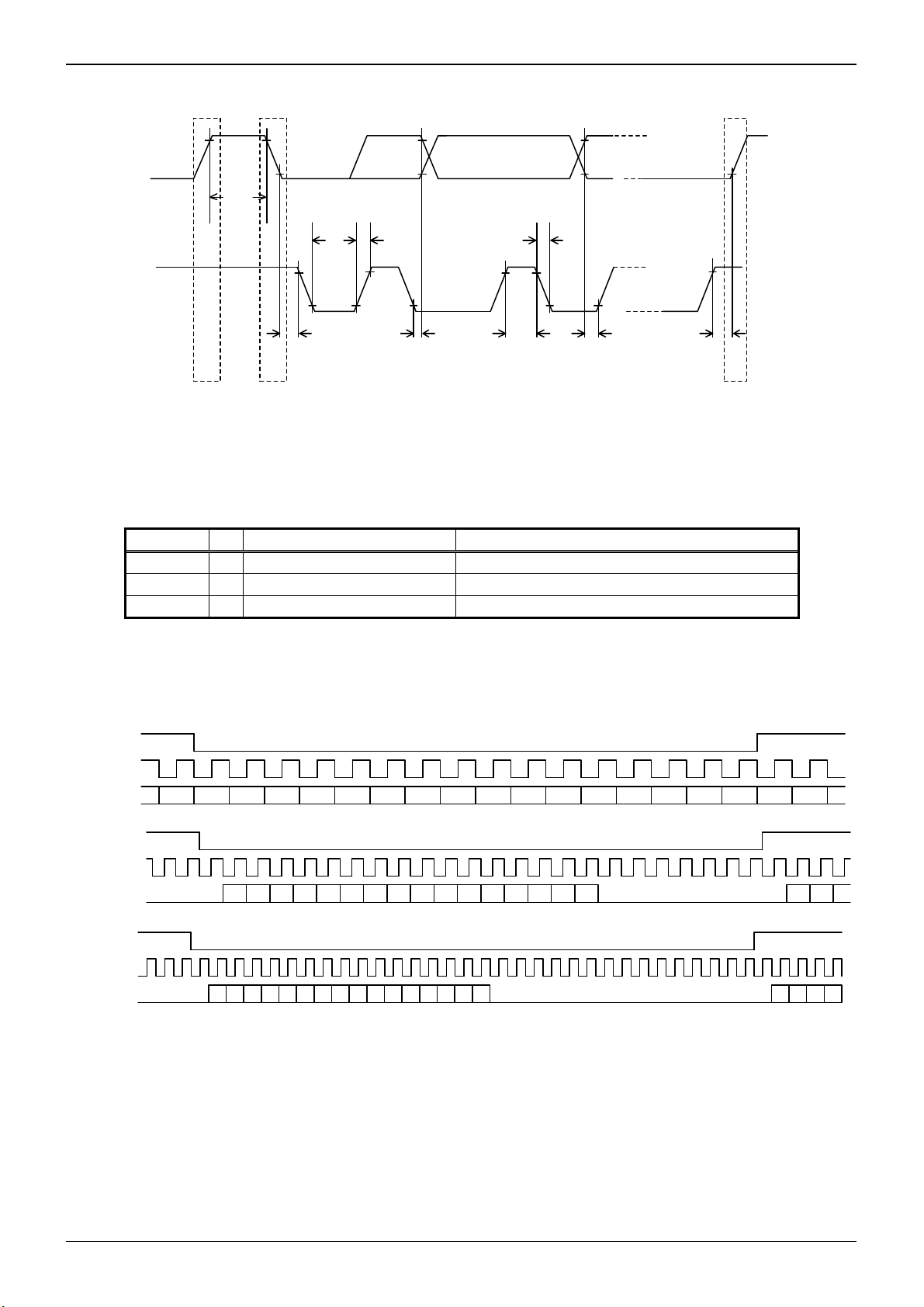

V. I/O Signal Specifications

V.1 Clock and reset

Clock

Signal name I/O Function Remarks

XIN_PLL I

XOUT_PLL O

Reset

Signal name I/O Function Remarks

RESETX I System reset input terminal

To disable a reset signal, continue L input for more than 5 us after all of the supply voltage reach the specified value and

clock input from the oscillation I/O terminal becomes stable. (See Figure V.1.)

Power

supply

XIN_PLL

RESETX

’tal (16.9344 MHz) connection

input terminal

’tal (16.9344 MHz) connection

terminal

Oscillation stabilization

standby time

Technical Note

clk

f

Clock frequency

Reset L interval

V.2 SEL_SLAVE

MODE1/MODE2, 3 selection input signal

Signal name I/O Function Remarks

SEL_SLAVE I Selects MODE1 or MODE2, 3. H: MODE1, L: MODE2, 3

V.3 SEL_MP3

Signal name I/O Function Remarks

SEL_MP3 I MPEG Audio Layer selection

tRSTX

Figure V.1 Reset Timing

Specification

Item Symbol

f

CLK

t

RSTX

min typ max

16.9302 16.9344 16.9386 MHz

5 - - us

Unit Remarks

SEL_SLAVE selects MODE1 (STAND ALONE MODE) or MODE 2/3 (SLAVE MODE).

By selecting SEL_SLAVE, SLAVE mode terminal setting shown in Table II.2 is enabled.

SEL_SLAVE is set only at power ON. Note that change of selection after power ON is ignored.

MPEG Audio Layer 1, 2, 3 play selection signal

H: Can play MP3 only. L: Can play MP1, MP2 and

MP3.

SEL_MP3 allows you to select the layer of the MPEG audio to be played. When enabling all the files having mp1,

mp2 or mp3 as the file extension to be played, enter L. When enabling mp3 only, enter H.

SEL_MP3 is set only at power ON. Note that change of election after power ON is ignored.

www.rohm.com

8/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

F

F

F

F

F

p

V.4 SEL_DOUT

Audio output selection signal

Signal name I/O Function Remarks

SEL_DOUT I Audio output selection H: Line output, L: I2S 3 lines serial output/SPDIF

This SEL_DOUT selects audio output signal.

Table V4.1 “Audio output” shows the audio outputs for each MODE.

Also table V4.2 ”I2S_fs” shows the I2S output formats for each MODE.

For command, see Chapter VI.

"TEST terminal" needs to be pull-up to 3.3V power supply.

Technical Note

TableV.4.1 Audio output

Pin No.

44 Line Out Rch O OF

46 Line Out Lch O OF

53 LED_ACCESS O OF

54 LED_RANDOM O OF

55 LED_REPEAT O OF

V.5 SEL_VOL

MODE1 MODE2,3

SEL_DOUT=H SEL_DOUT=L SEL_DOUT=H

function I/O PU function I/O PU function I/O PU function I/O PU function I/O PU

HiZ O OFFLine Out Rch O OFF HiZ O OFF HiZ O OFF

HiZ O OFFLine Out Lch O OFF HiZ O OFF HiZ O OFF

I2S LR CLOCK O OFFTEST terminal I ON I2S LR CLOCK O OFF SPDIF O OFF

I2S BIT CLOCK O OFFTEST terminal I ON I2S BIT CLOCK O OFF TEST terminal I OFF

I2S LRDATA O OFFTEST terminal I ON I2S LRDATA O OFF TEST terminal I OFF

SEL_DOUT=L

I2S SPDIF ON

Table V.4.2 I2S_fs

MODE1 32fs

MODE2/3 Can select 32fs, 48fs, 64fs by command.

SEL_DOUT is set only at power ON. Note that change of selection after power ON is ignored.

Sound volume operation selection signal

Signal name I/O Function Remarks

SEL_VOL I Sound volume operation

H: Sound volume operation enabled, L: Sound volume

operation disabled

SEL_VOL selects whether sound volume operation is to be enabled or disabled.

Sound volume operation is enabled when SEL_VOL=H.

Initial value of audio output is -24.1dB at power ON.

Sound volume operation is disabled when SEL_VOL=L. Audio output is fixed to 0dB.

Figure V.5 shows the relationship between audio output and sound volume step.

SEL_VOL is set only at power ON. Note that change of selection after power ON is ignored.

0

*PU・・・Pull-Up

-10

-20

-30

-40

-50

-

Audio output (dB)

-60

Initial value: -24.1 dB

(when SEL_VOL=H)

02468101214161820222426283032

Volume ste

Figure V.5 Volume Step Function

www.rohm.com

9/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

V.6 SEL_APLAY

Auto play selection signal at power ON/device recognition

Signal name I/O Function Remarks

SEL_APLAY I

SEL_APLAY selects whether the audio data in the memory is to be automatically played when a memory device

(USB memory or SD card) is inserted at power ON or when the system recognizes the memory device inserted.

SEL_APLAY can be selected only in MODE1. Since selection of SEL_APLAY is ignored in MODE2/3, select it

from Pull-up. When MODE2/3 is selected, audio data is halted after the system recognizes a device.

V.7 SEL_UTPKT

USB test packet

Signal name I/O Function Remarks

SEL_UTPKT I USB test packet send H: Disabled, L: USB test packet send

A test packet signal is output from USB_DP terminal or USB_DM terminal when L is set to SEL_UTPKT at power

ON.

Once enabled, SEL_UTPK keeps that state regardless of operation modes and sends out a test packet.

A test packet signal is continuously output until power turns OFF. Use SEL_UTPKT when evaluating the USB

terminal. In other cases, use it from Pull-up.

V.8 Audio output

Audio output

Signal name I/O Function Remarks

LDACO O Lch audio line output -

RDACO O Rch audio line output -

These signals are decoded MP3 music audio data line outputs.

They turn ON when the line output is selected by SEL_DOUT terminal.

V.9 MUTE control output

Audio MUTE

Signal name I/O Function Remarks

AMUTE O Audio mute control terminal H: At audio output, L: At mute

This is a control terminal to mute audio output at power ON or FF/FB (silence).

This terminal outputs H at audio output and L at mute.

Figure Ⅴ.9 shows the operation waveform.

Auto play selection signal at

device recognition

Technical Note

H: Stop after recognizing device, H: Play after

recognizing device

Figure V.9 Waveform at Audio Mute

www.rohm.com

10/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

V.10 KEY input format

3x4 matrix command input

Signal name I/O Function Remarks

KEY_ROW1 I

KEY_ROW2 I -

KEY_ROW3 I -

KEY_ROW4 I -

KEY_COL1 O -

KEY_COL2 O -

KEY_COL3 O -

Configure a circuit for the matrix signals terminals for KEY commands as shown in the applied circuit diagram

V.10.

The operation corresponding to the key pressed over the circuit is performed.

Details of each operation are explained in Chapter VI.2.

Technical Note

-

KEY matrix I/O signal

REPEAT RANDOM CHG_DEV+10

VOL+ FOL- FOL+VOL-

V.11 I2C interface format

I2C serial interface

Signal name I/O Function Remarks

SCL I I2C interface clock input -

SDA I/O I2C interface data I/O -

A0 I Slave address selection terminal Slave address [0] bit setting terminal

A1 I Slave address selection terminal Slave address [1] bit setting terminal

This is an I2C serial interface terminal. By inputting L to SEL_SLAVE terminal, the interface terminal becomes

enabled.

The terminal supports slave I2C operation.

V.11.1 I2C protocol

When I2C bus is in IDLE, SDA and SCL are set to H by the external Pull-up resistance. When starting

communications, the master sets SDA to L while SCL is set to H (Start condition). When ending communications,

the master sets SDA to H while SCL is set to H (Stop condition). During transfer, SDA is changed only when SCL

is set to L. Figure V.11.1 shows Start condition, Stop condition of I2C.

KEY_

ROW1

KEY_

ROW2

PLAY/

PAUSE

STOP

KEY_

ROW3

KEY_

ROW4

FFFB

KEY_

COL1

Figure V.10 KEY Matrix Applied Circuit Diagram

KEY_

COL2

KEY_

COL3

SCL

SDA

Start or

Repeated start

condition

12

MSB

8

LSB ACK

9 1

ACK

9

Stop or

Repeated start

condition

Figure V.11.1 I2C start, stop condition

www.rohm.com

11/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

V.11.2 Slave address

An I2C bus slave address corresponds to the 7-bit addressing mode. As shown in Table V.11.2, you can select

the slave address using input of A0 terminal and A1 terminal. Figure V.11.2 shows the slave address transfer

format.

S A6 A5 A4 A3 A2 A1 A0 R/W ACK

Start

condition

R / W = Read / Write Pulse

ACK = Acknowledge

Slave Address

Figure V.11.2 Slave Address Transfer Format

Table V.11.2 Settable Slave Addresses

sent by

slave

Technical Note

MSB

A6

A5 A4 A3 A2

A1

terminal

LSB

A0

terminal

1 0 0 0 0 0 0

1 0 0 0 0 0 1

1 0 0 0 0 1 0

1 0 0 0 0 1 1

V.11.3 Write protocol from master

To send a master command using an I2C bus, follow the transfer protocol shown in Figure V.11.3. For details on

each command, see Chapter VI.

S Slave Address A Data(8bit)R/W A Data(8bit) A Data(8bit) PA/A

"0"(write)

From Master to Slave

From Slave to Master

A = Acknowledge(SDA low)

A = No Acknowledge(SDA high)

S = Start Condition

P = Stop condition

Figure V.11.3 Command send protocol

V.11.4 Read protocol to master

To send reception data using an I2C bus from the slave to the master, follow the transfer protocol shown in Figure

V.11.4.1. First, transfer the status read command (step1). Then, input SCL clock of required bytes in step 2 to

read the status.

When the device is BUSY at reception of device status or memory data, the I2C bus may possibly be occupied by

the device during BUSY. This LSI transfers the bus to the master so as not to generate such bus occupation.

However, as a BUSY state still exists inside of the system, appropriate data may not be transferred during BUSY.

Therefore, the first byte of transfer data (Step2) is used to judge the transfer data is enabled/disabled. When

specifying addresses from the master to the slave and the first byte of the transfer data immediately after data

transfer is required is 0x00, transfer data from the slave is enabled. If the first byte is 0xFF, it shows the BUSY

state. Therefore, the transfer data should be disabled. If this happens, retry command transfer at Step 1 to read

out the status.

Figure V.11.4.2 shows the relationship between the transfer data and BUSY.

* For further information on BUSY, see Chapter V.17.

www.rohm.com

12/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

I2C

Step1

S Slave Address A Data(8bit)R/W A Data(8bit) PA/A

Step2

S Slave Address A Data(8bit)R/W A Data(8bit) PA/A

From Master to Slave

From Slave to Master

"0"(write)

"1"(read)

A = Acknowledge(SDA low)

A = No Acknowledge(SDA high)

S = Start Condition

P = Stop condition

Figure V.11.4.1 Status Reception Protocol

Step1 command S Slave Address A 0xFF A Data(8bit) PA/AData(8bit) AR

Technical Note

Data(8bit) A

BUSY

Step1 command S Slave Address A 0x00 A Data(8bit) PA/AData(8bit) AR

Dummy byte for Busy

Dummy byte for Busy

Figure V.11.4.2 Relationship between Transfer Data and BUSY

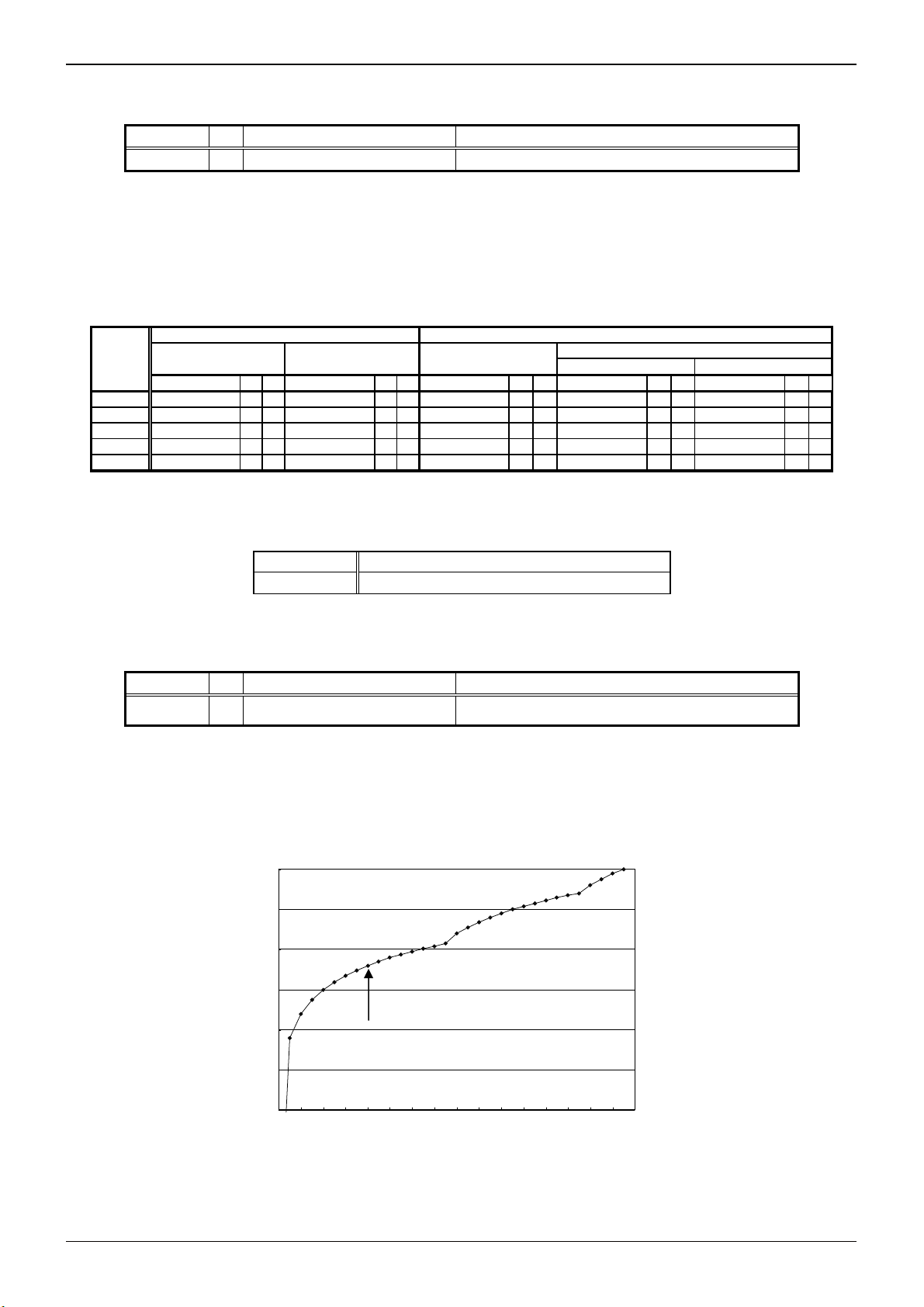

V.11.5 I2C Bus line electrical specification and timing

SDA and SCL bus-line characteristic (Unless specified, Ta=25℃, Vcc=3.3V)

Parameter Code Min. Max. Unit

1 SDA, SCL H input voltage VIH VDD*0.7 VDD V

2 SDA, SCL L input voltage VIL DVSS VDD*0.3 V

3 SDA H output voltage VOH VDD-0.4 VDD V

4 SDA L output voltage VOL 0 0.4 V

5 SCL clock frequency fSCL 0 400 kHz

Bus-free-time between "Stop" condition and

6

"Start" condition

Hold time for "Start" condition

7

After this, the first clock pulse is generated.

tBUF 1.3 - us

tHD;STA 0.6 - us

8 LOW status hold-time of SCL clock tLOW 1.3 - us

9 HIGH status hold-time of SCL clock tHIGH 0.6 - us

10 Data-hold-time tHD;DAT 0* - us

11 Date-setup-time tSU;DAT 100 - ns

12 Rising time of SDA and SCL signal tR 20+0.1*Cb 300 ns

13 Fall time of SDA and SCL signal tF 20+0.1*Cb 300 ns

14 Setup time of "Stop" condition tSU;STO 0.6 - us

15 Capacitive load of each bus-line Cb - 400 pF

The above-mentioned numerical values are all the values corresponding to V

*To exceed an undefined area on falling edged of SCL, transmission device should internally offer the hold-time of 300ns or more for SDA signal (V

signal).

Because the "Repeated Start" condition to send "Start" condition without sending "Stop" condition doesn't correspond, after sending "Start" condition, always

send "Stop" condition.

Neither terminal SCL nor terminal SDA correspond to 5V tolerant.

IH min

and V

IL max

level.

IH min

of SCL

www.rohm.com

13/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

SDA

t

BUF

SCL

t

LOW

t

R

t

HD;STA

SP

t

HD;DAT

t

HIGH

Figure V.11.5 Timing chart

V.12 I2S format

I2S serial audio interface

Signal name I/O Function Remarks

LRCK O I2S Bit clock output (fs=44.1kHz) -

BCK O I2S Bit clock output -

DATA O I2S data output -

This is a serial audio interface terminal. By inputting L to SEL_DOUT terminal, the interface terminal becomes

enabled. When selecting the I2S serial audio output, the output format varies depending on MODE. *See

Chapter Ⅴ.4. MODE2 allows you to select 32fs, 48fs or 64fs. *See Chapter V.4.

Figures V.12.1. V12.2 and V.12.3 show the I2S format to be output.

t

F

t

SU;DAT

t

SU;STO

Technical Note

P

LRCK

BCK(32fs)

DATA

Left Channel

0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 11 0

Right Channel

15

Figure V.12.1 I2S Output Timing (32fs)

LRCK Left Channel Right Channel

BCK(48fs)

DATA

15 14 12 11 10 9 8 7 6 5 4 3 2 1 0 15 1413

Figure V.12.2 I2S Output Timing (48fs)

LRCK

BCK(64fs)

DATA

13 1215 14 11 8 710 9 6 3 25 4 1 0 13 1215 14

Left Channel Right Channel

Figure V.12.3 I2S Output Timing (64fs)

www.rohm.com

14/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

V.13 SPDIF format

Digital audio interface

Signal name I/O Function Remarks

SPDIF O Digital audio output -

SPDIF output becomes enabled by setting SEL_DOUT terminal to L and setting this condition using the I2C

command. *See Chapter V.4.

Figure V.13 shows the digital audio signal output format.

Source code

Synchronous

preamble

Source code(4-31)

SPDIF output

Technical Note

034 1112 2728293031

Synchronous

preamble

Synchronous

preamble

0 0 0 0 0 0 0 0 1 0 1 1 0 1

all 0 Audio data(16bit)

(B pattern)

(M pattern)

(W pattern)

LSB MSB

Figure V.13 SPDIF Output Format

V U C P

A sub-frame of SPDIF is composed of synchronous preamble, 16-bit audio data, V bit (validity flag), U bit (user

data), C bit (channel status) and P bit (parity bit).

Output rate is fixed to 1X speed.

SPDIF outputs synchronous preamble (source code 0-3) as it is and others (source code 4-31) as bi-phase output.

It outputs L while the operation is stopped.

Synchronous preamble and C bit use 32 frames (≈4.4ms) as one cycle. Table V.13.1 and Table V.13.2 show

these formats. V bit is fixed to L. U bit uses 98 frames (≈13.3ms) as one cycle.

Table V.13.1 Synchronous Preamble Pattern

L0 R0 L1 R1 L2 R2 L3 R3 L4 R4 L5 R5

0 B W M W M W M W M W M W

1 M W M W M W M W M W M W

: : : : : : : : : : : : :

31 M W M W M W M W M W M W

Table V.13.2 C Bit Format

L0 R0 L1 R1 L2 R2 L3 R3 L4 R4 L5 R5

0 0 0 0 0 0 0

1 0 0 1 0 0 0

2 0 0 0 0 0 0

3 0 0 1 0 0 1 0 0

4 0 0 0 0 0 0

5 0 0 0 0 0 0

: : : : : : :

31 0 0 0 0 0 0

www.rohm.com

15/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

P bit is set to 1 if the number of “1s” of source codes 4-30 is odd, and set to 0 if the number is even. Therefore,

the number of source codes which turn to 1 for one data must be an odd value, SPDIF ends with L output and

preamble output always starts in the same direction.

V.14 USB I/F

USB I/O I/F

Signal name I/O Function Remarks

USB_DP I/O USB D+I/O terminal -

USB_DM I/O USB D-I/O terminal -

REXTI O

Differential signals of USB_DP and USB_DM enable communications with USB devices.

REXTI terminals become bias resistance connection terminals of the USB-PHY block.

V.15 SD I/F

SPI interface for SD memory card I/F

Signal name I/O Function Remarks

SD_CS O SPI chip select -

SD_CLK O SPI clock -

SD_DI O SPI data input -

SD_DO I SPI data output -

SD_CON I

These I/F enable communication with SD memory cards through SD memory card slots.

Since SD memory card slot requires detecting insertion of SD memory card, use of slot equipped with SD memory

card detecting terminal and connection to SD_CON terminal are required.

SD_CON terminal is pulled up within the device and detects SD memory card connection by L input.

V.16 MCHNG

Playing sound tune number detection output

Signal name I/O Function Remarks

MCHNG O

This signal outputs change of file to be played during playing MP3 file in the memory device.

MCHNG correctly outputs "H" during MP3 decode sequence, outputs "L" during "STOP" status.

V.17 BUSY

BUSY state detection output

Signal name I/O Function Remarks

BUSY O

This signal outputs to indicate that this LSI is in BUSY.

BUSY signal analyzes commands from the master and outputs H until the operation is executed.

This LSI ignores command input during BUSY. However, only the ABORT and STOP commands can be

accepted even during BUSY, which can be executed. *See Chapter V.11.

Technical Note

Table V.13.3 U Bit Format

L0 R0 L1 R1 L2 R2 L3 R3 L4 R4 L5 R5

0 0 0 0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0 0 0 0

2 1 0 0 0 0 0 0 0 0 0 0 0

3 1 0 0 0 0 0 0 0 0 0 0 0

: : : : : : : : : : : : :

97 1 0 0 0 0 0 0 0 0 0 0 0

USB bias resistance connection

terminal

SD card connect detection

terminal

Music tune number change

detection output signal

BUSY state detection output

signal

Connect resistance of 12kΩ 1% to GND.

H: Not detecting SD card connection.

L: Detecting SD card connection.

H: Playing, L: Tune completed/stopped

H: Busy, L: Not Busy

www.rohm.com

16/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

V.18 IRPTO

CONFIG outputs it for two more device connection state detection.

Signal name I/O Function Remarks

IRPTO O

When the USB device is chosen, output it to show that the USB device that two USB CONFIGURATION

DESCRIPTOR or more has in this LSI is connected. The timing of an output is dependent on the connected USB

device.

V.19 TEST terminal

By the terminal setting of TEST15, TEST16 and TEST17, It is possible to following function.

TEST15 TEST16 TEST17 Function

H H H Full function effective

L L L Only WMA and MP3 can play-back. The AAC file is disregarded.

H L L The IRPTO function is invalidated.

USB CONFIG outputs it for two

more device connection state

detection.

H: Detection , L: Undetection.

Technical Note

www.rohm.com

17/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

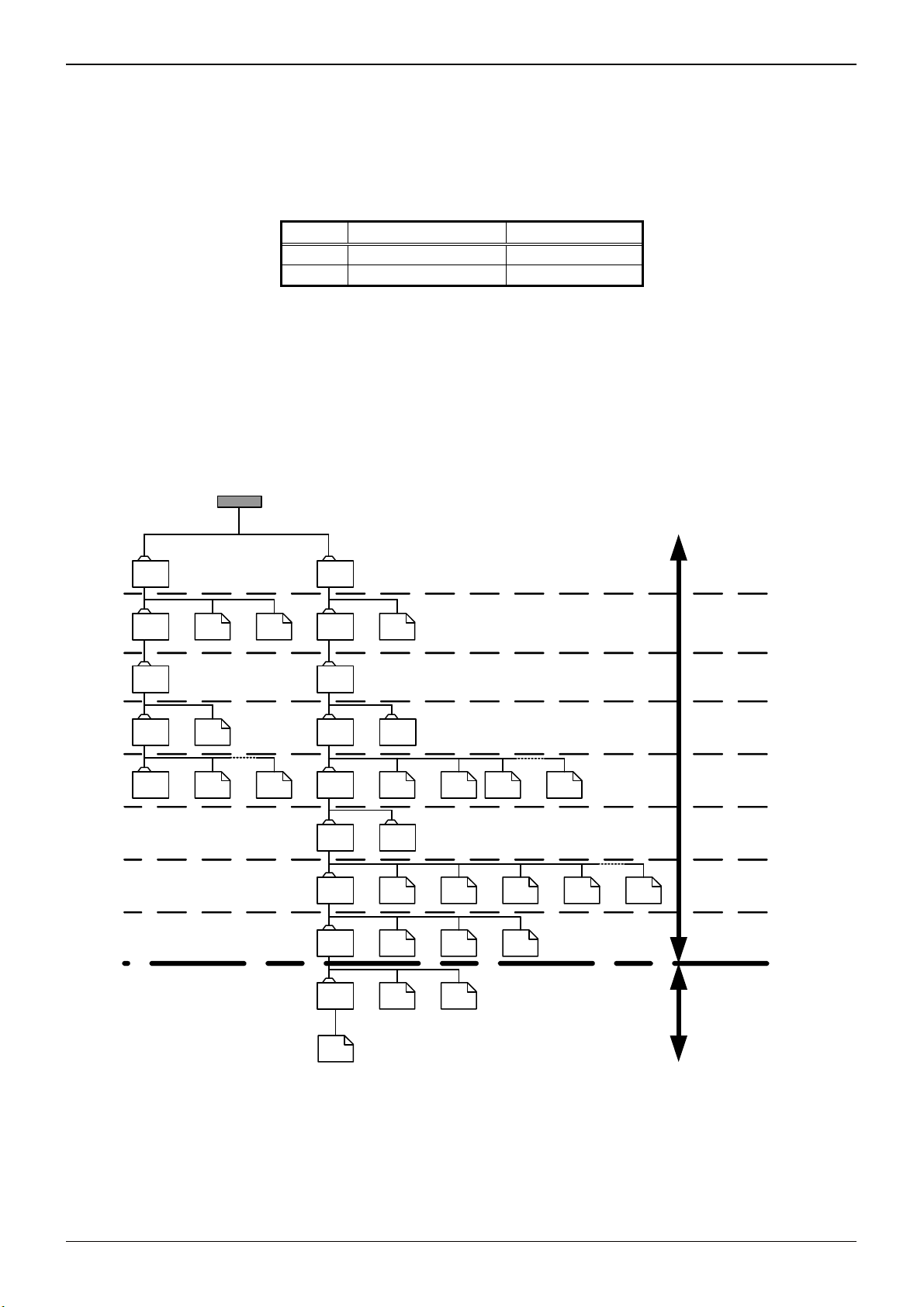

VI. Function/Operation Explanation

VI.1 File detection

VI.1.1 Function

· This function supports FAT16 and FAT32 file systems. (It does not support NTFS and FAT12.)

· The maximum number of playable files per folder

The number of files described above contains files other than AAC/WMA/MP3 and folders. If those nonAAC/WMA/MP3 files and folders exit within the folder and exceed the maximum number, all the AAC/WMA/MP3

files may not be played.

· Files less than 100 can be sorted by UNICODE in the FAT order within the folder. Files over 100 are sorted

in the FAT order. Also, the folders can be sorted in the same manner and those over 100 are sorted in the

FAT order.

· The searchable folder hierarchy is of 8 layers containing the root folder. Figure VI.1.1 shows an example of

memory layers.

Memory

Technical Note

Table VI.1.1 Maximum Number of Playable Files

Root folder Sub folder

FAT16 512 65534

FAT32 65536 65534

USB

Folder

Folder

Folder

Folder

File File

File

File File

Playable layers

FolderFolder

Folder

Folder

Folder Folder

Folder

Folder Folder

Folder File File File File File

Folder File File File

Folder

File

File File File File

File File

Unplayable layers

File

Figure VI.1.1 Example of Memory Layers

www.rohm.com

18/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

VI.1.2 Playable file

The playable file extensions are *.M4A, *.3GP and *.MP4 for AAC files, *.WMA and *.ASF for WMA files, *.MP3,

*.MP2 and *.MP1 for MP3 files. (Upper case letters and lower case letters are not distinguished.) Note that

the file operation differs in the following cases:

(1) SEL_MP3: See SEL_MP3 for details.

(2) Attribute: A AAC/WMA/MP3 file whose attribute is masked can be played. A file with system attributes

(3) Data destroyed file: When the data section of AAC/WMA/MP3 file is destroyed, the music data of the file

(4) File name: A file name and its size do not depend on playing.

(5) Extension: When file data is configured in the non-AAC format and its file extension is *.M4A, *.3GP and

(6) File size: When file size is “0”, the file do not recognize at AAC/WMA/MP3 files.

(7) This LSI corresponds to the AAC file encoded by iTunes. The versions of iTunes checked operation are 4.*,

(8) When the extension of WMA file is *.ASF, this LSI corresponds to the ASF file of only an audio stream.

VI.1.3 Playing sequence

The playing sequence of AAC/WMA/MP3 files is determined based on the following rules. See Figure VI.1.3.

(1) Folders are sorted in the order written in FAT (in the order of FAT), and files 1 to 100 are sorted in the order

(2) When AAC/WMA/MP3 file exists in the root folder (the highest layer), the AAC/WMA/MP3 file is played first.

(3) When all the AAC/WMA/MP3 files in the root folder have been played, those in the folder under the root

(4) When a folder is layered under that, AAC/WMA/MP3 files in the folder are played. When not, the master

(5) After playing all the files, the master returns to the root folder as described in (2) and start playing with the

VI.1.4 Folder/file sort

Folders and files are sorted in the following sequence using this LSI.

(1) Obtain up to 100 files and 100 folders in the order written to FAT.

(2) Compare the obtained folder/file names up to 14 characters (including filename extensions) and sort them

(3) When the same strings are generated, follow the order written to FAT. When the same strings are

(4) For 101 or more folders and files, follow the order written to FAT.

* The processing of the file name and the folder name is shown in the following.

2-a) When character-code that appears first is ≧0x80 ,It’s treated as the first byte of two byte character.

Technical Note

cannot be played.

can be played as much as possible rather than disabling to play the entire file. The section which cannot

be played is muted. However, AMUTE terminal remains the H output level. When the header section of

WMA and AAC file is destroyed, it plays next.

*.MP4 the state is play next. When file data is configured in the non-WMA format and its file extension is

*.WMA, or *.ASF, the state is play next. When file data is configured in the non-MP3 format and its file

extension is *.MP3, *.MP2 or *.MP1, the state is silent playing basically. If playable data can be read, only a

part of the file can be played. The information on time required to output serial status also becomes

uncertain. Then, partial output is done but the correct time information is not output.

5.*, 6.*, and 7.0 to 7.5. The AAC file encoded with other software may cause fault, such as being in the

middle of reproduction and skipping to next.

of UNICODE. (*See Chapter VI. 1.4.) Files over 100 are sorted in the order of FAT. Folders over 100

are sorted in the same manner.

AAC/WMA/MP3 files are sorted by AAC/WMA/MP3 following SEL_MP3. Folders are sorted including null

folders and those in which AAC/WMA/MP3 files are not written. Within each folder, AAC/WMA/MP3 files

over 100 and folders over 100 are played in the order written to the FAT directory entry.

Since how to write to the directory entry depends on the OS (Operating System) processing to write to the

memory, you cannot understand the file playing sequence.

folder, if any, are played.

searches any other folders at the same layer and plays the one, if any.

first sorted file.

in the ascending order.*

generated and the extension is different, MP3 file is first, WMA file is second, and AAC file is last.

1)When the LFN(long file name) entry exists, folder/filename is processed as one character in two bytes.

2)When the LFN entry doesn't exist, the SFN(short file name) entry is processed as follows.

Byte data afterwards is treated as the second byte of two byte character-code, and treated by two

bytes as one character.

2-b) When the case that doesn't apply to 2-a) ,that is, the character-code appears first is installed within the

range of 0x00-0x7F(US-ASCII) One byte is treated as one character. '0x00' is added and enhanced to

Unicode.

Please confirm the specification of the FAT filesystem about details of LFN and SFN.

www.rohm.com

19/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

y

Technical Note

[Root

Folder]

E.mp3

F.mp3

G.mp3

H.mp3

J.mp3

L.mp3

M.mp3

N.mp3

O.doc

P.xls

Q.mp3

S.txt

T.txt

V.mp3

W.mp3

X.mp3

Y.mp3

Z.mp3

A.mp3

B.mp3

C.mp3

D.mp3

A_FOLDER

B_FODER

C_FOLDER

R.txt

D_FOLDER

E_FOLDER

I.mp3

K.mp3

U.mp3

Figure VI.1.3 Configurations of Folders and Files within Memory Device

Table VI.1.3 MP3 File Playing Sequence for Folder/File Configuration as in Figure VI.1.3

Playing

sequence

1 A.mp3

2 B.mp3

3 C.mp3

4 D.mp3

5 E.mp3

6 F.mp3

7 G.mp3

8 H.mp3

9 I.mp3

10 J.mp3

11 K.mp3

12 L.mp3

13 M.mp3

14 N.mp3

15 Q.mp3 · Non-MP3 files are ignored.

16 U.mp3

17 V.mp3

18 W.mp3

19 X.mp3

20 Y.mp3

21 Z.mp3

File to be

pla

ed

Remarks

· If MP3 files exist in the root folder,

those files are played first.

· Files are played in the ascending order

of UNICODE by file name.

· After all MP3 files in the root folder are

played, the master searches folders

under that layer.

· The master searches folders in the

ascending order of UNICODE by folder

name.

· After the master plays all MP3 files

including those in the lower layers

within A_FOLDER, it moves to a folder

in the same layer as A_FOLDER to

search MP3 files.

· Since there is no MP3 file in

D_FOLDER, the layers same as

A_FOLDER, the master plays MP3

files in E_FOLDER under that.

www.rohm.com

20/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

VI.1.5 Search within multi-drive and multi-partition

If a device is a multi-drive type or multi partition type, the LSI can recognize the drive by selecting LUN (Logical Unit

Number) for the supporting FAT. (MODE2 and MODE3)

If particular LUN isn’t selected, the LSI mounts the device whose LUN detected first. (default)

When the multi-card reader is connected, the LSI can recognize device which connected to the card-reader by

selecting LUN. But after the device is mounted, it’s impossible to recognize states whether the device connected to

the card-reader is inserted or removed.

VI.1.6 External HUB search

When the USB connector is connected to a HUB, and a FAT-supported drive is connected ahead of the HUB at

mounting the USB for this LSI, only one drive is recognized.

The LSI does not support external HUBs, it cannot detect plugging/unplugging of the drive ahead of the HUB after

the USB is mounted.

VI.2 MODE1

VI.2.1 KEY command operation

VI.2.1.1 KEY SCAN (Single Mode)

Technical Note

KEY SCAN operates in the following sequence on the circuit configuration as shown in Figure V.10 .

(1) KEY_COL1 to 3 output waveforms at timing as shown in Figure VI.2.1.

(2) By pressing KEY switch, KEY_ROW 1 to 4 are set to L at timing when KEY_COL 1 to 3 are L.

(3) When detecting L input from KEY_ROW 1 to 4 three times, the master judges that KEY has been

pressed. Then, the master starts the KEY operation.

figure VI.2.1 KEY SCAN Waveform.

KEY_COL1

KEY_COL2

KEY_COL3

PLAY

KEY_ROW1

KEY_ROW2

KEY_ROW3

KEY_ROW4

KEY_COL1

420ns

420ns

420ns

20ms

Figure VI.2.2 Operating Waveforms when KEY is Pressed

20ms 20ms 20ms 20ms 20ms 20ms

Determine that KEY is pressed

Start the operation of the pressed KEY.

www.rohm.com

21/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

VI.2.1.2 KEY SCAN (Hold Mode)

KEY SCAN operates in the following sequence on the circuit configuration as shown in Figure V.10 .

(1) KEY_COL1 to 3 output waveforms at timing as shown in Figure VI.2.1.

(2) By pressing KEY switch, KEY_ROW 1 to 4 are set to L at timing when KEY_COL 1 to 3 are L.

(3) When detecting L input from KEY_ROW 1 to 4 three times, the master judges that KEY has been

pressed. Then, the master starts judging status of held KEY.

(4) When pressed KEY’s decision (L input from KEY_ROW 1 to 4 three times) is detected consecutive 15

times, the master judges that KEY Mode is Hold Mode.

(5) When KEY release is detected in judging status of hold KEY, the master judges that KEY Mode is

Single Mode. Then, the master starts the KEY operation.

(6) When Hold Mode is detected, the master starts the KEY operation in Hold Mode. When KEY release is

detected in Hold Mode, the master finish the KEY operation.

The keys corresponding to Hold Mode are FF, FB, VOL+, and VOL-.

Figure VI.2.3 KEY SCAN Waveform.

Note 1: Based on the above sequence, the master determines that KEY is pressed and starts the operation of the pressed

KEY, pressing multiple KEYs at the same time will produce different operations depending on the KEY

combinations. Therefore, you cannot regulate the operation sequence correctly even simultaneously pressing

multiple KEYs will not cause any problems. In Hold Mode, Other pressed KEY is disregarded.

Note 2: Because the KEY input does not have a buffering function, KEY inputs other than those described below are

ignored.

Technical Note

www.rohm.com

22/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

VI.2.1.3 KEY operation

Table VI.2.1.2.1 shows the types and operations of KEYs.

Table VI.2.1.2.2 shows enabled/disabled states of KEY operations.

Table VI.2.1.2.1 KEY Commands and Operation Description

KEY COMMAND OPERATION DESCRIPTION

· When receiving “PLAY/PAUSE” key during stop, the master starts playing the first MP3 file

sorted to the recognized device.

PLAY/PAUSE

STOP

FF

FB

FOL+

FOL-

+10

VOL+/VOL-

· When receiving “PLAY/PAUSE” key during play, the master stops playing the MP3 file

temporarily. When receiving PLAY/PAUSE key again, the master restarts playing the file.

· When receiving “STOP” key during play, pause or file search, the master stops playing,

pausing or searching the MP3 file.

· When receiving “FF” KEY (Single Mode) during play or pause, the master searches the next

AAC/WMA/MP3 file in the order of sort of files being played or paused. Upon completion of

searching, the master starts playing the file.

· During play of the last file, the master returns to the first file in the order of sort and plays the

file.

· When receiving “FF” KEY (Hold Mode) during play or pause, the master starts fast forward

playing the file. When "FF" KEY release is detected, the master return to normal playing.

· When music finishes into "FF" KEY (Hold Mode), the master starts fast forward playing from

top of the next file. However, when selecting “REPEAT” or “RANDOM”, master search next

file by setup.

· When receiving “FB” KEY (Single Mode) during play or pause, the master searches the

previous AAC/WMA/MP3 file in the order of sort of files being played or paused. Upon

completion of searching, the master starts playing the file.

· During play of the first file, the master plays the last file in the order of sort.

· When receiving "FB" KEY within 1sec from top of file playing, the master searches the

previous AAC/WMA/MP3 file in the order of sort of files being played. Upon completion of

searching, the master starts playing the file. When receiving "FB" KEY over 1sec from top of

file playing, the master starts playing from top of this AAC/WMA/MP3 file.

· When receiving “FB” KEY (Hold Mode) during play or pause, the master starts fast backward

playing the file. When "FB" KEY release is detected, the master return to normal playing.

· When music finishes into "FB" KEY (Hold Mode), the master starts fast backward playing

from end of the previous file. However, when selecting “REPEAT” or “RANDOM”, master

search previous file by setup.

· When receiving “FOL+” KEY during play or pause, the master searches the AAC/WMA/MP3

files in the next folder in the order of sort of the folder in which the file being played or paused

exists. Upon completion of search, the master plays the file.

· During play of the file in the last folder in the order of sort, the master plays the first file in the

order of sort.

· When receiving “FOL-“ KEY during play or pause, the master searches the AAC/WMA/MP3

files in the next folder in the order of sort of the folder in which the file being played or paused

exists. Upon completion of search, the master plays the file.

· During play of the file in the first folder in the order of sort, the master plays the first file in the

order of sort in the last folder.

· When receiving “+10” KEY during play or pause, the master searches AAC/WMA/MP3 files

10 files next to the current one in the order of sort of the file being played or paused. Upon

completion of search, the master starts playing the file.

· When the remaining files are less than 10 during play of the current file, the master plays the

first file.

· When receiving “VOL+/VOL-“ KEY while SEL_VOL terminal is set to H, the master controls

sound volume.

· Sound volume can be controlled at 32 steps from -∞ (minimum volume) to 0dB (maximum

volume).

· Since VOL+/VOL- KEY does not judge release of KEY, the master turns up or down volume

step by step when determining press of the KEY. Therefore, VOL KEY can be held down.

Technical Note

www.rohm.com

23/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

(

CHNG_DEV

REPEAT

RANDOM

Technical Note

· The master selects the device between USB memory and SD memory card. To do this,

both devices should be connected or one device should correspond to the other (USB to SD

or SD to USB). Otherwise, this key operation is ignored.

· Stop after selecting the device at the top tune of the device.

· REPEAT and RANDOM settings return to the initial values.

· When inserting both USB Memory and SD Memory card, or neither USB Memory nor SD

Memory card, the master precedes USB Memory.

· This key changes the mode of repeat.

· Press of “REPEAT” KEY toggles like: “repeat all tunes in memory” “repeat one tune”

“repeat within folder”.

· When selecting “repeat within folder”, the master repeats AAC/WMA/MP3 files within the

folder being played. The initial setting is “repeat all tunes in memory”.

· This key plays the range of 128 files from the current one being played in the order of sort

at random.

· “RANDOM” KEY is enabled to change mode only during play, pause or stop.

Table VI.2.1.2.2 KEY Operation Enabled/Disabled

After recognizing device

PLAY/

PAUSE

STOP

FF

FB

FOLDER+

FOLDER-

VOL+

VOL-

+10

CHNG_DEV

REPEAT

RANDOM

= Enabled = Disabled

VI.2.2 LED operation

Seven types of LEDs used to display the LSI operation states are controlled. Table VI.2.2 shows the types and

states of LEDs.

Search or pause)

Recognize

either USB

or SD

Recognize

both USB

and SD

Table VI.2.2 Types of LEDs and operation description

During play of device

Recognize

either USB

or SD

Recognize

both USB

and SD

Searching

Recognize

either USB

or SD

Error

Recognize

both USB

and SD

Types of LEDs Operation description

Lights when an error occurs. This happens in the following cases:

LED_ERROR

LED_PLAY Lights during play. Blinks during pause.

LED_PSD

LED_PUSB

LED_ACCESS Lights during access to USB memory or SD memory card.

LED_RANDOM Lights during random play.

LED_REPEAT

www.rohm.com

24/57

© 2012 ROHM Co., Ltd. All rights reserved.

(1) Neither USB memory nor SD memory card is connected. No AAC/WMA/MP3 file

exists even if these devices are connected.

(2) Communication error or disconnection occurs in the memory being played.

Lights when SD memory card is connected and played.

Blinks when SD memory card is connected but SD memory card is not selected.

Goes off when SD memory card is not connected.

Lights when USB memory is connected and played.

Blinks when USB memory is connected but USB memory card is not selected.

Goes off when USB memory is not connected.

Lights during folder repeat. Blinks during repeat of one tune. Goes off during repeat

all tunes in memory

2012.04 - Rev.

BU94604BKV

A

VI.3 MODE2

VI.3.1 Command operation

You can operate commands via the I2C serial interface. When using the LSI in MODE2, it can be operated by setting

SEL_SLAVE to L. The length of command to be sent varies depending on which command is selected.

Table VI.3.1.1 shows the command specifications.

Table VI.3.1.2 shows enabled/disabled state of each command.

Technical Note

Table VI.3.1.1 Command Operation Description

Command name

PLAY

PAUSE 0x02 - -

STOP 0x03 - -

VOL+ 0x04 - -

VOL- 0x05 - -

REPEAT 0x06 - -

RANDOM 0x07 - -

CHNG_DEV 0x08 - -

ABORT 0x0C - -

Command

byte length

2 0x50

1st 2nd 3rd 4th~

Command Operation description

· When receiving “PLAY” command during stop, the master starts playing

the AAC/WMA/MP3 file currently selected. The order sorted from the

root folder is initially set.

· When receiving “PLAY” command during pause, the master restarts

0x01 - -

playing the file from that point.

· When a state which disables MP3 decoding for more than 5 seconds

during play, status “DECO_ERR” is set to H. MP3 decoding is continued.

· When receiving “PLAY” command during fast forward (or backward)

playing, the master restarts normal playing the file from current point.

· When receiving “PAUSE” command during play, the master stops playing

the AAC/WMA/MP3 files temporarily.

· When receiving “STOP” command during play, pause or file search, the

master stops playing the AAC/WMA/MP3 file.

· When receiving “STOP” command during fast forward (or backward)

playing, the master stops playing the file.

· “STOP” command can be received even during BUSY.

· When SEL_VOL is set to H, “VOL+” command is enabled.

· When receiving “VOL+” command, the master controls sound volume.

· Sound volume can be controlled at 32 steps from -∞ (minimum volume)

to 0dB (maximum volume).

· When SEL_VOL is set to H, “VOL-“command is enabled.

· When receiving “VOL-“command, the master controls sound volume.

· Sound volume can be controlled at 32 steps from -∞ (minimum volume)

to 0dB (maximum volume).

· This command selects the mode during repeat.

· REPEAT command toggles like: “repeat all tunes in memory” “repeat

one tune” “repeat within folder”.

· When STATUS RPT_OFF is set as ON by "REPRAND" command,

REPEAT command toggles like: “all play in memory” “one file play”

“play within folder”. In this mode, it stops upon completion of playing.

· When selecting “repeat within folder”, the master repeats AAC/WMA/MP3

files within the folder being played.

· The initial setting is “repeat all tunes in memory”.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command is as same as the “REPEAT” command in MODE1.

· This key plays the range of 128 files from the current one being played

in the order of sort at random.

· When STATUS RPT_OFF is set as ON by "REPRAND" command,

REPEAT command toggles like: “one random file play” “all play with

random in memory”. In this mode, it stops upon completion of playing.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command is as same as the “RANDOM” command in MODE1.

· The command selects the device between USB memory and SD memory

card. To do this, both devices should be connected or one device

should correspond to the other (USB to SD or SD to USB). Otherwise,

this key operation is ignored.

· Stop after selecting the device at the top tune of the device.

· REPEAT and RANDOM settings return to the initial values.

· This command interrupts Tag analysis.

· It interrupts Tag analysis only the file is being played.

www.rohm.com

25/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

Technical Note

SET_RESUME_

INFO1

SET_RESUME_

INFO2

SET_RESUME_

INFO3

SET_RESUME_

INFO4

SET_RESUME_

INFO5

SET_RESUME_

INFO6

SET_RESUME_

INFO7

SET_RESUME_

INFO8

FF

FF&PLAY 0x01

FFP_ON 0x02

8 0x51

4 0x55

0x41

0x42

0x43

0x44

0x45

0x46

0x47

0x48

0x01

RESUME INFO

1byte-6byte

RESUME INFO

7byte-12byte

RESUME INFO

13byte-18byte

RESUME INFO

19byte-24byte

RESUME INFO

25byte-30byte

RESUME INFO

31byte-36byte

RESUME INFO

37byte-42byte

RESUME INFO

37byte-42byte

0x00

0x00

· This command sets byte 1 to 6 of 42-byte data obtained by

“READ_RESUME_INFO”.

· This command sets byte 7 to 12 of 42-byte data obtained by

“READ_RESUME_INFO”.

· This command sets byte 13 to 18 of 42-byte data obtained by

“READ_RESUME_INFO”.

· This command sets byte 19 to 24 of 42-byte data obtained by

“READ_RESUME_INFO”.

· This command sets byte 25 to 30 of 42-byte data obtained by

“READ_RESUME_INFO”.

· This command sets byte 31 to 36 of 42-byte data obtained by

“READ_RESUME_INFO”.

· This command sets byte 37 to 42 of 42-byte data obtained by

“READ_RESUME_INFO”. When RESUME reproduction is possible, play

started that music. When RESUME is impossible, play the head music of

media is started.

· About some kind of setting of Resume Play, see “Application Note – V.2.9

Resume Play Method”.

· This command sets byte 37 to 42 of 42-byte data obtained by

“READ_RESUME_INFO”. When RESUME reproduction is possible, it

stops in the music. When RESUME is impossible, it stops at the head of

media.

· About some kind of setting of Resume Play, see “Application Note – V.2.9

Resume Play Method”.

· When receiving FF command during play, pause or stop, the master

searches the next AAC/WMA/MP3 file in the order of sort of the file being

played or paused.

· During play of the last file, the master returns to the first file in the order

of sort.

· Operation stops upon completion of search.

· When ID3 or WMA-TAG analysis is set by SEL_ID3 command, operation

stops upon completion of TAG analysis.

· When receiving ”FF&PLAY” command during play, pause or stop, the

master searches the next AAC/WMA/MP3 file in the order of sort of the

file being played or paused.

· During play of the last file, the master returns to the first file in the order

of sort.

· Operation starts playing, after completion of search.

· When TAG analysis is set by SEL_ID3 command, the master plays the

file upon completion of TAG analysis.

· When receiving FFP_ON command during play, pause or stop, the

master starts fast forward playing from current point.

When music finishes into that FFP_ON command is ON, the master

·

starts fast forward playing from top of the next file. When setting

“REPEAT” or “RANDOM”, master search next file by setup.

FFP_OFF 0x03

FB 0x02 0x00 0x00

www.rohm.com

26/57

© 2012 ROHM Co., Ltd. All rights reserved.

· When receiving FFP_OFF command during fast forward playing, the

master restarts normal playing from current point.

· When receiving “FB” command during play, pause or stop within 1sec

from top of file playing, the master searches the previous AAC/WMA/MP3

file in the order of sort of files being played or paused. When receiving

“FB” command during play or pause over 1sec from top of file playing,

the master searches top of present AAC/WMA/MP3 file.

· The master returns to the last file during play of the first file within 1sec

from top of file playing.

· Upon completion of search, the operation stops.

· When TAG analysis is set by SEL_ID3 command, operation stops upon

completion of TAG analysis.

2012.04 - Rev.

BU94604BKV

A

·· When receiving “FB&PLAY” command during play, pause or stop within

1sec from top of file playing, the master searches the previous

AAC/WMA/MP3 file in the order of sort of files being played or paused.

When receiving “FB&PLAY” command during play or pause over 1sec

from top of file playing, the master searches top of present

FB&PLAY 0x01

FBP_ON 0x02

AAC/WMA/MP3 file.

· The master returns to the last file during play of the first file within 1sec

from top of file playing.

· Operation starts playing, after completion of search.

· When TAG analysis is set by SEL_ID3 command, the master plays the

file upon completion of TAG analysis.

· When receiving FBP_ON command during play, pause or stop, the

master starts fast backward playing from current point.

·

When music finishes into that FBP_ON command is ON, the master

starts fast backward playing from end of previous file. When

setting “REPEAT” or “RANDOM”, master search previous file by

setup.

FBP_OFF 0x03

FOL+

0x03

FOL+&PLAY 0x01

FOL-

0x04

FOL-&PLAY 0x01

+10 0x05 0x00 0x00

0x00

0x00

· When receiving FBP_OFF command during fast backward playing, the

master restarts normal playing from current point.

· When receiving “FOL+” command during play, pause or stop, the master

searches the next folder in the order of sort of the folder in which the file

being played or paused exists.

· The master returns to the first folder in the order of sort during play of the

last folder.

· The operation stops upon completion of search.

· When TAG analysis is set by SEL_ID3 command, operation stops upon

completion of TAG analysis.

· When receiving “FOL+&PLAY” command during play, pause or stop, the

master searches the next folder in the order of sort of the folder in which

the file being played or paused exists.

· The master returns to the first folder in the order of sort during play of the

last folder.

· Operation starts playing, after completion of search.

· When TAG analysis is set by SEL_ID3 command, the master plays the

0x00

file upon completion of TAG analysis.

· When receiving “FOL-“ command during play, pause or stop, the master

search the next folder in the sort of the folder in which the file being

played or paused exists.

· During play of the first folder, the master returns to the last folder in the

order of sort.

· The operation stops upon completion of search.

· When TAG analysis is set by SEL_ID3 command, operation stops upon

completion of TAG analysis.

· When receiving “FOL-&PLAY“ command during play, pause or stop, the

master searches the next folder in the order of sort of the folder in which

the file being played or paused exists.

· During play of the top folder, the master returns to the first folder in the

order of sort.

· Operation starts playing, after completion of search.

· When TAG analysis is set by SEL_ID3 command, the master plays the

file upon completion of TAG analysis.

· When receiving “+10” command during play, pause or stop, the master

searches the AAC/WMA/MP3 file of the 10

the file being played or paused.

· When the remaining files to be played are less than 10 in the order of

sort, the master returns to the first file.

· The operation stops upon completion of search.

· When TAG analysis is set by SEL_ID3 command, operation stops upon

completion of TAG analysis.

Technical Note

th

tune in the order of sort of

www.rohm.com

27/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

Technical Note

· When receiving “+10&PLAY” command during play, pause or stop, the

master searches the AAC/WMA/MP3 file of the 10

sort of the file being played or paused.

+10&PLAY 0x01

-10

0x06

-10&PLAY 0x01

USB_MNT_R

EADY

4 0x5D 0x0B 0x01 0x00

0x00

· When the remaining files to be played are less than 10 in the order of

sort, the master returns to the first file.

· Operation starts playing, after completion of search.

· When TAG analysis is set by SEL_ID3 command, the master plays the

file upon completion of TAG analysis.

· When receiving “-10” command during play, pause or stop, the master

searches the AAC/WMA/MP3 file of the previous 10

sort of the file being played or paused.

· When playing the top 10 or less files in the order of sort, the master

returns to the first file.

· The operation stops upon completion of search.

· When ID3 or WMA-TAG analysis is set by SEL_ID3 command, operation

stops upon completion of TAG analysis.

· When receiving “-10&PLAY” command during play, pause or stop, the

master searches the AAC/WMA/MP3 file of the previous 10

order of sort of the file being played, paused or stopped.

· When playing the top 10 or less files in the order of sort, the master

returns to the first file.

· Operation starts playing, after completion of search.

· When TAG analysis is set by SEL_ID3 command, the master plays the

file upon completion of TAG analysis.

· This command prepares for USB memory mount.

· Be sure to send this command when STATUS turns to USB_INS=H and

BUSY=L..

th

tune in the order of

th

tune in the order of

th

tune in the

0x00

SET_DOUT 4 0x51 0x20

0x01 0x01

0xFF 0x00

0x00 - -

0x01 - -

0x02 - -

0x03 - -

0x04 - -

SET_EQ

* See Chapter

VI.3.3.

SET_VOL 2 0x53

2 0x52

0x05 - -

0x07 - -

0x08 - -

0x09 - -

0x0A - -

0x0B - -

0x0C - -

0x0D - -

0x0F - -

Setting

value

· This command outputs the audio data in the I2S (32fs) format.

0x58

· When SET_DOUT command is sent, SEL_DOUT terminal setting is

· This command outputs the audio data in the I2S (48fs) format.

0x59

· When SET_DOUT command is sent, SEL_DOUT terminal setting is

· This command outputs the audio data in the I2S (64fs) format.

0x5B

· When SET_DOUT command is sent, SEL_DOUT terminal setting is

· This command performs serial audio interface (SPDIF) output.

· When SET_DOUT command is sent, SEL_DOUT terminal setting is

· This command stops serial audio interface (I2S, SPDIF) output.

· When SET_DOUT command is sent, SEL_DOUT terminal setting is

This command turns OFF the EQ setting.

POPS

JAZZ

ROCK

CLASSIC

R&B

This command turns OFF the EQ setting.

BASS BOOST1

POPS+BASS BOOST1

JAZZ+BASS BOOST1

ROCK+BASS BOOST1

CLASSIC+BASS BOOST1

R&B+BASS BOOST1

BASS BOOST2

· This command sets the sound volume to the 2nd byte value of the

- -

ignored

ignored

ignored

ignored

ignored

command. The setting value ranges 32 steps from 0x00 to 0x1F.

Any value outside of the above range is ignored.

www.rohm.com

28/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

REPRAND 2 0x54

SEL_ID3 2 0x56

SEL_TOC 2 0x57

SEL_12MOUT 2 0x58

0x00 - -

0x01 - -

0x02 - -

0x03 - -

0x04 - -

0x05 - -

0x06 - -

0x07 - -

0x00 - -

0x01 - -

0x00 - -

0x01 - -

0x00 - -

0x01 - -

Technical Note

· This command repeats all the tunes within the memory. This is initially

set.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· The command repeats playing the AAC/WMA/MP3 file within the folder

being played.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command repeats playing the MP3 file being played.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command plays through the range of 128 files in the order of the

sort from the current one being played at random.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command plays all the tunes within the memory. STATUS RPT_OFF

is set as ON.

· It stops after the last file playing.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command plays all the tunes within the folder being played. STATUS

RPT_OFF is set as ON.

· It stops after the last file playing within the folder.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command plays one tunes. STATUS RPT_OFF is set as ON.

· It stops after the file playing.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command plays through the range of 128 files in the order of the

sort from the current one being played at random. STATUS RPT_OFF is

set as ON.

· It stops after the file playing.

· The last setting to “REPRAND”, “REPEAT” and “RANDOM” commands

will be enabled.

· This command does not perform ID3Tag analysis written to the MP3 file.

· This command does not perform WMATag analysis written to the WMA

file.

· This command does not perform AACTag analysis written to the AAC file.

· The file played immediately after set will be enabled first.

· This command analysis ID3Tag written to the MP3 file.

· This command analysis WMATag written to the WMA file.

· This command analysis AACTag written to the AAC file.

· The file played immediately after set will be enabled first.

· Upon completion of Tag analysis, the data is written to the status register.

· This command does not perform TOC analysis.

· TOC analysis is not performed at initial setting.

· When receiving the command, inserting into the device or changing the

device, the master analyzes the total folders (including root directory) and

total AAC/WMA/MP3 files within the device.

· The number of total AAC/WMA/MP3 files conforms to SEL_MP3 terminal.

· When receiving the command, only change from OFF to ON is executed.

· Upon completion of TOC analysis, the master returns to the top tune of

the device and stops.

· After TOC analysis, the data is written to the status register.

· This command stops 12MHz clock output from CLKOUT12 terminal.

· This command enables 12 MHz clock output from CLKOUT12 terminal.

0x00 - -

SEL_WDT 2 0x5A

0x01 - -

www.rohm.com

29/57

© 2012 ROHM Co., Ltd. All rights reserved.

· This command stops WDT.

· This command writes “1” to

STATUS WDT_RFLG.

2012.04 - Rev.

BU94604BKV

A

A

A

A

A

SET_RPM 6 0x5B

SET_RPM_ATT 4 0x5B

SET_UPLOAD

_FILE1

SET_UPLOAD_

FILE2

UPLOAD_END 2 0x51 0x53 - -

SET_TOUT_M 4 0x5D 0x07 0xYY 0xXX

SET_TOUT_C 4 0x5D 0x08 0xYY 0xXX

SET_USB_R_W

AIT

GET_ VENDOR

FORCE_DISC

ON_USB

FORCE_CON

_USB

8 0x51 0x51

8 0x51 0x52

4 0x5D 0x09 0xXX 0x00

2 0x5F 0x16 - -

2 0x5D 0x02 - -

2 0x5D 0x0A - -

0x00 setting

0x01 setting 0x00

NAME[0:5]

NAME[6:7]

EXT[0:2]

Technical Note

· This command set up playtime and skiptime for fast forward playing and

fast backward playing. Fast forward and fast backward playing repeat

this cycle by making {playtime(M) + skiptime(N) +error(O)} into 1 cycle.

With an error, it depends on the cajoled error between the minimum

decoding unit and playtime, and the real time which searches skiptime.

Errors differ by every file and every composition in memory.

· This command set up that playtime is M[15:0]=[4th byte, 3rd byte] and

skiptime are N[15:0]=[6th byte and 5th byte]. Initial value set playtime is

300 mili second=M[15:0]=[4 th byte=x01, 3rd byte=x2C] and skiptime is

2100 mili second=N[15:0]=[6 th byte=x08, 5 th byte=x34].

When command set up to 0x0, setting value is initial value.

The playtime should set up 300ms or more, and skiptime should set up

below (playtime x16).

· This command set up the attenuation level under fast forward and

backward playing.

An attenuation level serves as (-6dB X [3rd byte]).

A setup can be specified from 0x00 to 0x10.As for an initial value,

0x02=-12dB is set up. It becomes equivalent to MUTE by setup of 0x10.

Specify the part of the first half of the file name of the file for File Read

Function.

*Bury it by 0x20 when the file name(NAME) doesn't come up to eight bytes.

Specify the part of the latter half of the file name of the file for File Read

Function.

*Bury it by 0x20 when the file name(NAME) doesn't come up to eight bytes.

Bury it by 0x00 when the file extension doesn't come up to three bytes.

It targets neither the file name comparison since 0x00 of the end in the

comparison.

The File Read function is ended.

Transmit after completing the file reading.

The ACK timeout of the command under memory mount is set up.

The set point x100 (msec) is timeout. At the time, XX is upper byte and YY is

lower byte.

n initial value is 30 sec (YY=0x2C, XX=0x01), and maximum value is 60

sec (YY=0x58, XX=0x02).If set point is over the maximum value, this

command is ignored.

Mount ERROR will be carried out if a timeout occur.

The ACK timeout of the commands at the time of PLAY or STOP or PAUSE

(except during mount) is set up.

The set point x100 (msec) is timeout. At the time, XX is upper byte and YY is

lower byte.

n initial value is 5 sec (YY=0x32, XX=0x00), and maximum value is 60 sec

(YY=0x58, XX=0x02). If set point is over the maximum value, this command

is ignored.

Communication ERROR will be carried out if a timeout occur.

The wait time after bus reset is set up at the time of USB memory

recognition.

The set point (XX) x200 (msec) is wait time.

n initial value is 600 msec (XX=0x03), and maximum value is 51.2 sec

(XX=0xFF).

vendor code and Product ID are stored in COMAREA.

Please read COMAREA after GET_VENDOR command transmission and

acquire code data.

Offset 0x20:Vendor code Lower byte

0x21:Vendor code Upper byte

0x22:Product code Lower byte

0x23:Product code Upper byte

Force mounted USB memory to be disconnected.

Mounts USB memory again, which Mount ERROR occurred.

www.rohm.com

30/57

© 2012 ROHM Co., Ltd. All rights reserved.

2012.04 - Rev.

BU94604BKV

A

Technical Note

FORCE_DISC

ON_SD

FORCE_CON

_SD

SET_LUN

RESET_LUN

4 0x5D 0x0C 0x01 0x00