Page 1

A

Operational Amplifiers / Comparators

Ground Sense Low Voltage

Operation CMOS Operational Amplifiers

BU7461G, BU7461SG, BU7441G, BU7441SG, BU7462F/FVM/NUX, BU7462SF/FVM/NUX,

BU7442F/FVM/NUX, BU7442SF/FVM/NUX, BU7464F, BU7464SF, BU7444F, BU7444SF,

BU7465HFV, BU7465SHFV, BU7445HFV, BU7445SHFV

●Description

Low Voltage CMOS Op-Amp integrates one or two independent outputs full swing Op-Amps and phase compensation

capacitors on a single chip. Especially, this series is operable with low voltage, low supply current and low input bias current.

Ground Sense : BU7461 (BU7461S) family, BU7441 (BU7441S) family, BU7462 (BU7462S) family,

BU7442 (BU7442S) family, BU7464 (BU7464S) family, BU7444 (BU7444S) family,

BU7465 (BU7465S) family, BU7445 (BU7445S) family,

●Features

1) Operable with low voltage

+1.7[V] ~ +5.5[V] (Single supply) :

BU7461/BU7441 family, BU7462/BU7442 family

BU7464/BU7444 family, BU7465/BU7445 family

2) Input Ground Sense, Output Full Swing

3) High speed operation (BU7461 family, BU7462 family)

4) Internal phase compensation

5) Wide temperature range

-40[℃] ~ +85[℃]

(BU7461G, BU7462 family, BU7464F, BU7465HFV)

(BU7441G, BU7442 family, BU7444F, BU7445HFV)

-40[℃] ~ +105[℃]

(BU7461SG, BU7462S family, BU7464SF, BU7465SHFV)

(BU7441SG, BU7442S family, BU7444SF, BU7445SHFV)

Ground Sense

High speed Single

Low power

Dual

Quad

Single

Dual

Quad

6) High open loop voltage gain

7) Low supply current

(BU7441 family, BU7442 family)

(BU7445 family, BU7444 family)

8) Low input bias current 1[pA](Typ.)

9) ESD protection circuit

Human body mode (HBM)±4000[V](Typ.)

BU7461G

(BU7461SG:Operation guaranteed up to +105℃)

BU7465HFV

(BU7465SHFV::Operation guaranteed up to +105℃)

BU7462F/FVM/NUX

(BU7462S F/FVM/NUX:Operation guaranteed up to +105℃)

BU7464F

(BU7464SF:Operation guaranteed up to +105℃)

BU7441G

(BU7441SG:Operation guaranteed up to +105℃)

BU7445HFV

(BU7445SHFV:Operation guaranteed up to +105℃)

BU7442F/FVM/NUX

(BU7442S F/FVM/NUX:Operation guaranteed up to +105℃)

BU7444F

(BU7444SF:Operation guaranteed up to +105℃)

No.10049JET21

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

1/36

2010.12 - Rev.

Page 2

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

●Pin Assignments

IN+

VSS

+

2

-

VDD

51

3 4

IN-

OUT

OUT1

IN1IN1+

VSS

1

CH1

++--

2

3

4

CH2

8

7

6

5

VDD

OUT2

IN2IN2+

1

CH1

2

IN1IN1+

VDD

IN2+

IN2-

OUT2

+-

3

4

5

+-

CH2

6

78

SSOP5 HVSOF5 SOP8 MSOP8 VSON008X2030 SOP14

Package

Input type

SSOP5 HVSOF5 SOP8 VSON008X2030 MSOP8 SOP14

Technical Note

14OUT1

OUT4

CH4

+

+

CH3

-

-

13

12

11

10

9

IN4IN4+

VSS

IN3+

IN3-

OUT3

Ground Sense

BU7461G

BU7461SG

BU7441G

BU7441SG

BU7465HFV

BU7465SHFV

BU7445HFV

BU7445SHFV

BU7462F

BU7462SF

BU7442F

BU7442SF

BU7462NUX

BU7462SNUX

BU7442NUX

BU7442SNUX

BU7462FVM

BU7462SFVM

BU7442FVM

BU7442SFVM

BU7464F

BU7464SF

BU7444F

BU7444SF

●Absolute maximum rating (T a=25[℃])

Rating

Parameter Symbol

BU7441G, BU7442F/FVM/NUX

BU7464F, BU7444F

BU7445HFV, BU7465HFV

BU7461G, BU7462F/FVM/NUX

BU7461SG, BU7462S F/FVM/NUX

BU7441SG, BU7442S F/FVM/NUX

BU7464SF, BU7444SF

BU7445SHFV, BU7465SHFV

Supply Voltage VDD-VSS +7 V

Differential Input Voltage

Input Common-mode

Voltage Range

(*1)

Vid VDD-VSS V

Vicm (VSS-0.3) ~ (VDD+0.3) V

Operating Temperature Topr -40 ~ +85 -40 ~ +105 ℃

Unit

Storage Temperature Tstg -55 ~ +125 ℃

Maximum

Junction Temperature

Note: Absolute maximum rating item indicates the condition which must not be exceeded.

Application of voltage in excess of absolute maximum rating or use out absolute maximum rated temperature environment

may cause deterioration of characteristics.

(*1) The voltage difference between inverting input and non-inverting input is the differential input voltage.

Then input terminal voltage is set to more than VSS.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

Tjmax +125 ℃

2/36

2010.12 - Rev.

Page 3

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

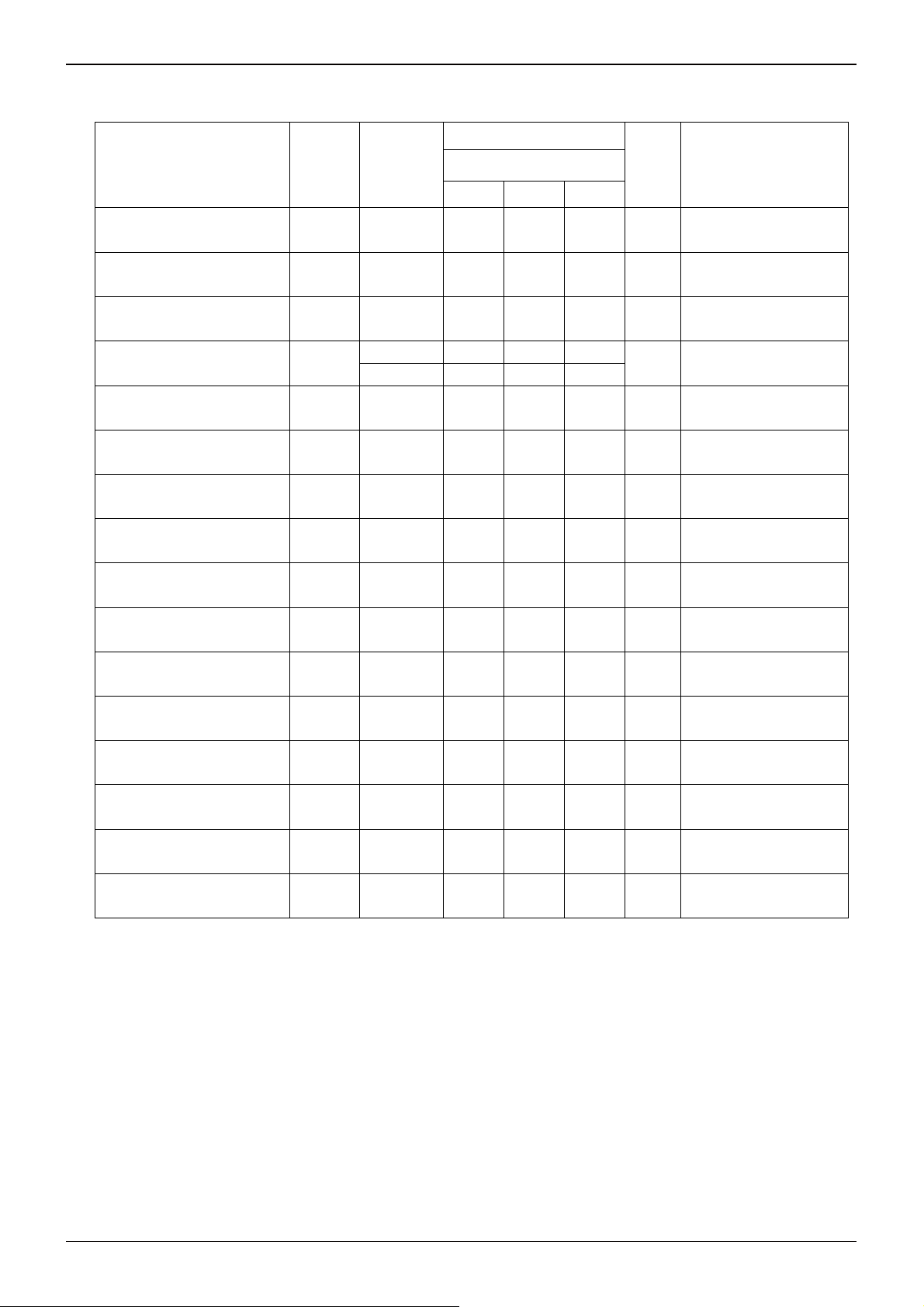

●Electrical characteristics

○BU7461 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

Unit Condition BU7461G, BU7461SG

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*2)

Vio 25℃ - 1 6 mV -

(*2)

Iio 25℃ - 1 - pA -

(*2)

Ib 25℃ - 1 - pA -

(*3)

IDD

25℃ - 150 350

Full range - - 450

RL=∞ All Op-Amps

μA

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 70 95 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*4)

IOH 25℃ 4 8 - mA VDD-0.4[V]

Vicm 25℃ 0 - 1.8 V VSS ~ VDD-1.2[V]

CMRR 25℃ 45 60 - dB -

PSRR 25℃ 60 80 - dB -

Output Sink Current

(*4)

IOL 25℃ 6 12 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 1.0 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 1 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 50 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - %

(*2) Absolute value

(*3) Full range: BU7461: Ta=-40[℃] to +85[℃] BU7461S: Ta=-40[℃] to +105[℃]

(*4) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

VOUT=1[Vp-p]

f=1[kHz]

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

3/36

2010.12 - Rev.

Page 4

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

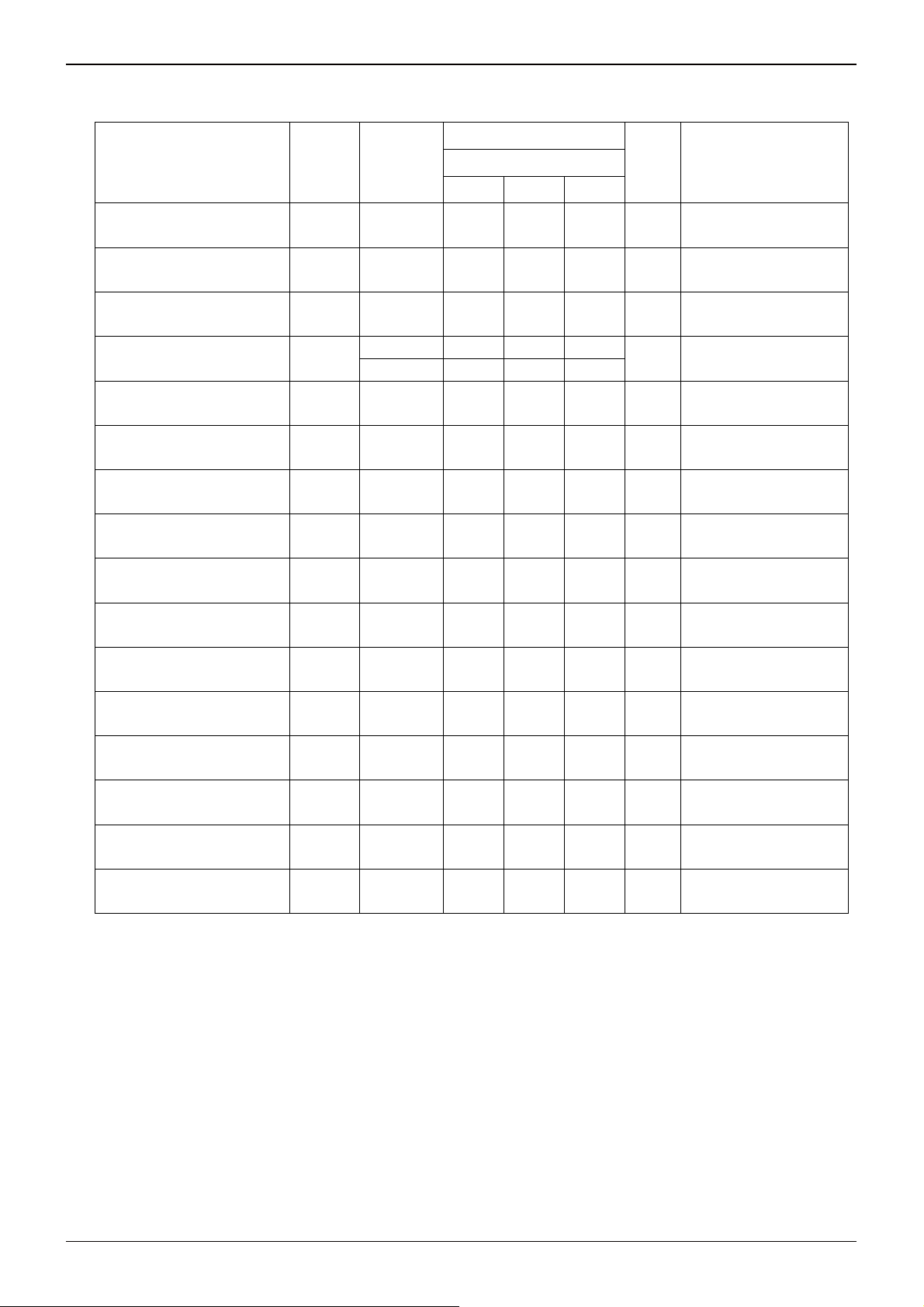

○BU7462 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

BU7462F/FVM/NUX

BU7462S F/FVM/NUX

Unit Condition

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*5)

Vio 25℃ - 1 6 mV -

(*5)

Iio 25℃ - 1 - pA -

(*5)

Ib 25℃ - 1 - pA -

(*6)

IDD

25℃ - 300 700

Full range - - 900

RL=∞ All Op-Amps

μA

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 70 95 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*7)

IOH 25℃ 4 8 - mA VDD-0.4[V]

Vicm 25℃ 0 - 1.8 V VSS ~ VDD-1.2[V]

CMRR 25℃ 45 60 - dB -

PSRR 25℃ 60 80 - dB -

Output Sink Current

(*7)

IOL 25℃ 6 12 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 1.0 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 1 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 50 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - %

VOUT=1[Vp-p] ,

f=1[kHz]

Channel Separation CS 25℃ - 100 - dB AV=40[dB]

(*5) Absolute value

(*6) Full range: BU7261, BU7262: Ta=-40[℃] to +85[℃] BU7462S: Ta=-40[℃] to +105[℃]

(*7) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

4/36

2010.12 - Rev.

Page 5

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

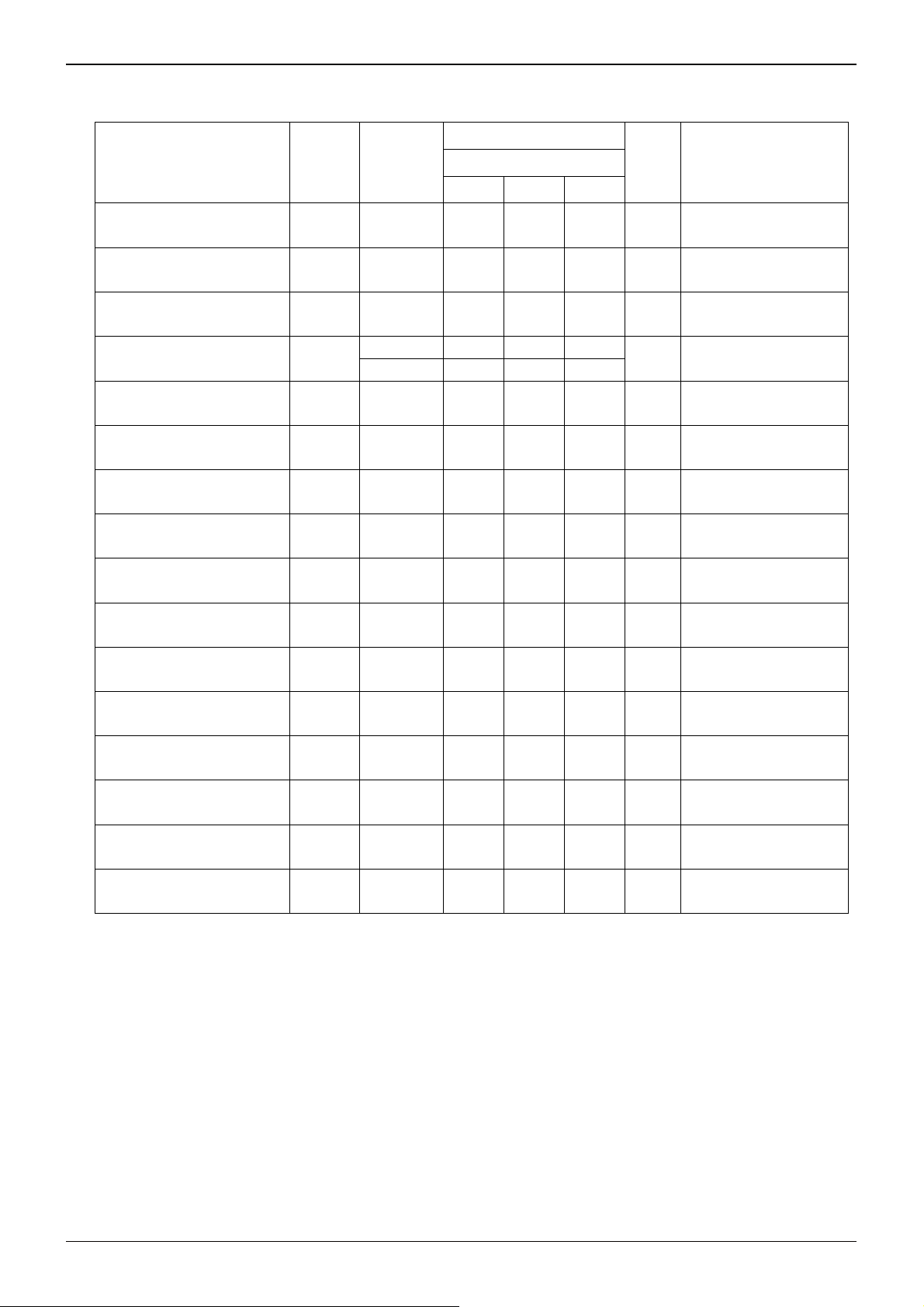

○BU7464 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

BU7464F

BU7464SF

Unit Condition

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*5)

Vio 25℃ - 1 6 mV -

(*5)

Iio 25℃ - 1 - pA -

(*5)

Ib 25℃ - 1 - pA -

(*6)

IDD

25℃ - 600 1400

Full range - - 1800

RL=∞ All Op-Amps

μA

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 70 95 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*7)

IOH 25℃ 4 8 - mA VDD-0.4[V]

Vicm 25℃ 0 - 1.8 V VSS ~ VDD-1.2[V]

CMRR 25℃ 45 60 - dB -

PSRR 25℃ 60 80 - dB -

Output Sink Current

(*7)

IOL 25℃ 6 12 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 1.0 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 1 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 50 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - %

VOUT=0.8[Vp-p],

f=1[kHz]

Channel Separation CS 25℃ - 100 - dB AV=40[dB]

(*8) Absolute value

(*9) Full range: BU7464: Ta=-40[℃] to +85[℃] BU7464S: Ta=-40[℃] to +105[℃]

(*10) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

5/36

2010.12 - Rev.

Page 6

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

○BU7465 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

BU7465HFV

BU7465SHFV

Unit Condition

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*5)

Vio 25℃ - 1 6 mV -

(*5)

Iio 25℃ - 1 - pA -

(*5)

Ib 25℃ - 1 - pA -

(*6)

IDD

25℃ - 120 300

Full range - - 400

RL=∞ All Op-Amps

μA

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 60 100 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*7)

IOH 25℃ 4 8 - mA VDD-0.4[V]

Vicm 25℃ 0 - 1.8 V VSS ~ VDD-1.2[V]

CMRR 25℃ 45 60 - dB -

PSRR 25℃ 60 80 - dB -

Output Sink Current

(*7)

IOL 25℃ 9 18 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 1.0 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 1.2 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 60 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - %

(*11) Absolute value

(*12) Full range: BU7465: Ta=-40[℃] to +85[℃] BU7465S: Ta=-40[℃] to +105[℃]

(*13) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

VOUT=0.8[Vp-p],

f=1[kHz]

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

6/36

2010.12 - Rev.

Page 7

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

○BU7441 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

Unit Condition BU7441G, BU7441SG

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*14)

Vio 25℃ - 1 6 mV -

(*14)

Iio 25℃ - 1 - pA -

(*14)

Ib 25℃ - 1 - pA -

(*15)

IDD

25℃ - 50 120

Full range - - 240

μA

RL=∞ All Op-Amps

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 70 95 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*16)

Vicm 25℃ 0 - 1.8

CMRR 25℃ 45 60 -

V VSS ~ VDD-1.2[V]

dB -

PSRR 25℃ 60 80 - dB -

IOH 25℃ 3 6 - mA VDD-0.4[V]

Output Sink Current

(*16)

IOL 25℃ 5 10 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 0.3 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 0.6 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 50 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - % VOUT=1[Vp-p], f=1[kHz]

(*14) Absolute value

(*15) Full range: BU7441: Ta=-40[℃] to +85[℃] BU7441S: Ta=-40[℃] to +105[℃]

(*16) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

7/36

2010.12 - Rev.

Page 8

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

○BU7442 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

BU7442F/FVM/NUX

BU7442S F/FVM/NUX

Unit Condition

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*17)

Vio 25℃ - 1 6 mV -

(*17)

Iio 25℃ - 1 - pA -

(*17)

Ib 25℃ - 1 - pA -

(*18)

IDD

25℃ - 100 240

Full range - - 480

μA

RL=∞ All Op-Amps

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 70 95 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*19)

Vicm 25℃ 0 - 1.8

CMRR 25℃ 45 60 -

V VSS ~ VDD-1.2[V]

dB -

PSRR 25℃ 60 80 - dB -

IOH 25℃ 3 6 - mA VDD-0.4[V]

Output Sink Current

(*19)

IOL 25℃ 5 10 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 0.3 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 0.6 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 50 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - % VOUT=1[Vp-p], f=1[kHz]

Channel Separation CS 25℃ - 100 - dB AV=40[dB]

(*17) Absolute value

(*18) Full range: BU7442: Ta=-40[℃] to +85[℃] BU7442S: Ta=-40[℃] to +105[℃]

(*19) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

8/36

2010.12 - Rev.

Page 9

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

○BU7444 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

Unit Condition BU7444F, BU7444SF

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*20)

Vio 25℃ - 1 6 mV -

(*20)

Iio 25℃ - 1 - pA -

(*20)

Ib 25℃ - 1 - pA -

(*21)

IDD

25℃ - 200 480

Full range - - 960

μA

RL=∞ All Op-Amps

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 70 95 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*22)

Vicm 25℃ 0 - 1.8

CMRR 25℃ 45 60 -

V VSS ~ VDD-1.2[V]

dB -

PSRR 25℃ 60 80 - dB -

IOH 25℃ 3 6 - mA VDD-0.4[V]

Output Sink Current

(*22)

IOL 25℃ 5 10 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 0.3 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 0.6 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 50 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - %

VOUT=0.8[Vp-p],

f=1[kHz]

Channel Separation CS 25℃ - 100 - dB AV=40[dB]

(*20) Absolute value

(*21) Full range: BU7444: Ta=-40[℃] to +85[℃] BU7444S: Ta=-40[℃] to +105[℃]

(*22) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

9/36

2010.12 - Rev.

Page 10

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

○BU7445 family (Unless otherwise specified VDD=+3[V], VSS=0[V], Ta=25[℃])

Limits

Parameter Symbol

Temperature

Range

Unit Condition BU7445HFV, BU7445SHFV

Min. Typ. Max.

Technical Note

Input Offset Voltage

Input Offset Current

Input Bias Current

Supply Current

(*23)

Vio 25℃ - 1 6 mV -

(*23)

Iio 25℃ - 1 - pA -

(*23)

Ib 25℃ - 1 - pA -

(*24)

IDD

25℃ - 40 90

Full range - - 120

μA

RL=∞ All Op-Amps

AV=0[dB], VIN=0.9[V]

High Level Output Voltage VOH 25℃ VDD-0.1 - - V RL=10[kΩ]

Low Level Output Voltage VOL 25℃ - - VSS+0.1 V RL=10[kΩ]

Large Signal Voltage Gain AV 25℃ 60 100 - dB RL=10[kΩ]

Input Common-mode

Voltage Range

Common-mode

Rejection Ratio

Power Supply

Rejection Ratio

Output Source Current

(*25)

Vicm 25℃ 0 - 1.8

CMRR 25℃ 45 60 -

V VSS ~ VDD-1.2[V]

dB -

PSRR 25℃ 60 80 - dB -

IOH 25℃ 4 8 - mA VDD-0.4[V]

Output Sink Current

(*25)

IOL 25℃ 9 18 - mA VSS+0.4[V]

Slew Rate SR 25℃ - 0.25 - V/μs CL=25[pF]

Gain Band width FT 25℃ - 0.4 - MHz CL=25[pF], AV=40[dB]

Phase Margin θ 25℃ - 60 - ° CL=25[pF], AV=40[dB]

Total Harmonic Distortion THD 25℃ - 0.05 - %

(*23) Absolute value

(*24) Full range: BU7445: Ta=-40[℃] to +85[℃] BU7445S: Ta=-40[℃] to +105[℃]

(*25) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

VOUT=0.8[Vp-p],

f=1[kHz]

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

10/36

2010.12 - Rev.

Page 11

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

y

05

y

g

g

g

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

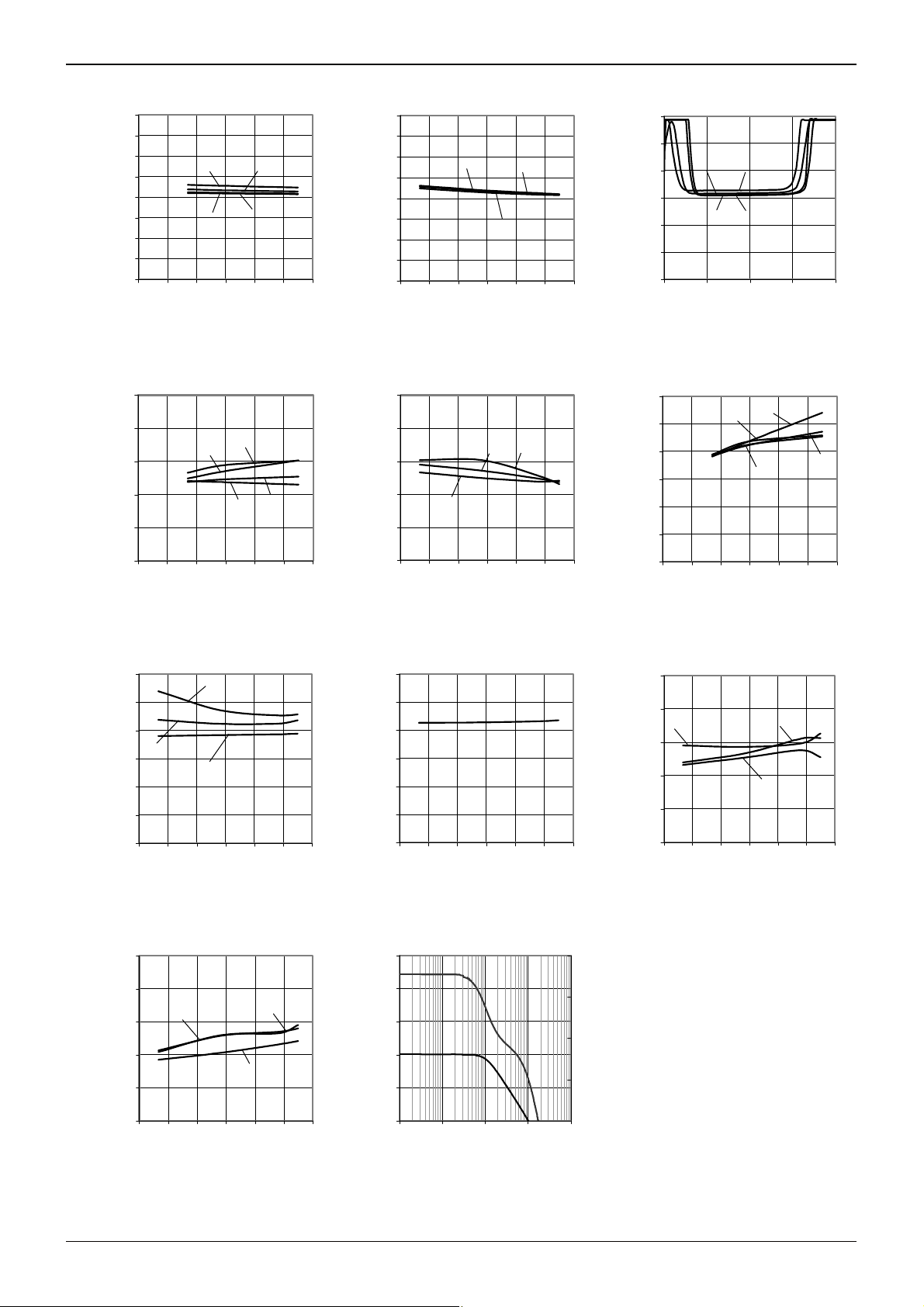

●Reference data (BU7461 family)

800

BU7461 famil

800

BU7461 famil

300

600

400

BU7461G

200

POWER DISSIPATION [mW]

0

050100150

AMBIENT TEMPERATURE [°C]

85

Fig.1 Fig.2 Fig.3

Derating curve Derating curve

600

BU7461SG

400

200

POWER DISSIPATION [mW]

0

0 50 100 150

AMBIENT TEMPERATURE [°C]

105

200

100

SUPPLY CURRENT [μA]

0

0246

SUPPLY VOLTAGE [V]

Supply Current – Supply Voltage

800

600

400

200

SUPPLY CURRENT [uA]

0

-60 -30 0 30 60 90 120

Fi

Supply Current – Ambient Temperature

3.0V

AMBIENT TEMPERATURE [°C]

12

5.5V

BU7461 famil

1.7V

6

4

2

OUTPUT VOLTAGE HIGH [V]

0

0246

85℃

SUPPLY VOLTAGE [V]

-40℃

1

℃

BU7461 famil

25℃

6

4

2

OUTPUT VOLTAGE HIGH [V]

0

-60-300 306090120

AMBIENT TEMPERATURE [°C]

.4 Fig.5 Fig.6

BU7461 famil

Output Voltage High – Supply Voltage

(RL=10[kΩ])

8

BU7461 famil

Output Voltage High – Ambient Temperature

40

9

6

3

OUTPUT VOLTAGE LOW [mV]

0

0246

SUPPLY VOLTAGE [V]

Fi

85℃

105℃

25℃

-40℃

.7 Fig.8 Fig.9

Output Voltage Low – Supply Voltage

(RL=10[kΩ])

20

15

10

5

BU7461 famil

5.5V

3.0V

1.7V

OUTPUT SOURCE CURRENT [mA]

0

-60-300 306090120

Fi

AMBIENT TEMPERATURE [°C]

.10 Fig.11 Fig.12

Output Source Current – Ambient Temperature

(VOUT=VDD-0.4[V])

(*)The above data is ability value of sample, it is not guaranteed. BU7461G: -40[℃] ~ +85[℃] BU7461SG: -40[℃] ~ +105[℃]

6

5.5V

4

1.7V

2

OUTPUT VOLTAGE LOW [mV]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

3.0V

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

85℃

BU7461 famil

-40℃

105℃

80

60

40

20

OUTPUT SINK CURRENT [mA]

0

0123

25℃

OUTPUT VOLTAGE [V]

Output Sink Current – Output Voltage

(VDD=3[V])

30

20

105℃

10

OUTPUT SINK CURRENT [mA]

0

0123

OUTPUT VOLTAGE [V]

Output Source Current – Output Voltage

60

40

20

OUTPUT SINK CURRENT [mA]

0

-60-300 306090120

AMBIENT TEMPERATURE [°C]

Output Sink Current – Ambient Temperature

(VOUT=VSS+0.4[V])

Technical Note

BU7461 family

25℃

5.5V

5.5V

85℃

-40℃

BU7461 family

BU7461 famil

25℃

BU7461 famil

105℃

3.0V

1.7V

(RL=10[kΩ])

-40℃

85℃

(VDD=3.0[V])

3.0V

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

11/36

2010.12 - Rev.

Page 12

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

–

–

–

y

–

–

–

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7461 family)

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

-7.5

INPUT OFFS ET VOLTAGE [mV]

-10.0

0123456

-40℃

85℃

SUPPLY VOLTAGE [V]

Fig.13 Fig.14 Fig.15

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

25℃

100

80

60

LARGE SIGNAL VOLTAGE GAIN [dB]

0123456

SUPPLY VOLTAGE [V]

Fig.16 Fig.17 Fig.18

Large Signal Voltage Gain

Supply Voltage

120

100

5.5V

80

3.0V

60

40

1.7V

20

0

-60-300 306090120

COMMON MODE REJECTION RATIO [dB]

AMBIENT TEMPERATURE [°C]

Fig.19 Fig.20 Fig.21

Common Mode Rejection Ratio

Ambient Temperature

2.0

1.6

1.2

0.8

0.4

SLEW RATE H-L [V/μs]

5.5V

BU7461 famil

25℃

105℃

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

-7.5

INPUT OFFSET VOLTAGE [mV]

-10.0

-60 -30 0 30 60 90 120

3.0V

AMBIENT TEMPERATURE [°C]

Input Offset Voltage – Ambient Temperature

(Vicm= VDD-1.2[V], VOUT= VDD/2)

-40℃

105℃

BU7461 family

85℃

160

140

120

100

80

LARGE SIGNAL VOLTAGE GAIN [dB]

60

1.7V

-60-300 306090120

AMBIENT TEMPERATURE [°C]

Power Supply Rejection Ratio

3.0V

1.7V

BU7461 family

5.5V

BU7461 family

5.5V

15

10

5

0

-5

-10

INPUT OFFSET VOLTAGE [mV]

-15

-1 0 1 2 3

Input Offset Voltage – Input Voltage

120

100

80

60

40

20

0

0123456

COMMON MODE R EJECTION RATIO [dB]

Common Mode Rejection Ratio

Ambient Temperature

BU7461 famil

120

100

80

60

40

20

0

-60 -30 0 30 60 90 120

POWER SUPPLY REJECTION RATIO [dB]

AMBIENT TEMPERATURE [°C]

Large Signal Voltage Gain

BU7461 family

2.0

1.6

3.0V

1.2

0.8

0.4

SLEW RATE L-H [V/μs]

0.0

-60 -30 0 30 60 90 120

Slew Rate L-H

Ambient Temperature

BU7461 famil

200

150

100

PHASE [deg]

50

1.7V

BU7461 family

3.0V

100

80

60

40

GAIN [dB]

20

Phase

Gain

0.0

-60-300 306090120

AMBIENT TEMPERATURE [°C]

Fig.22 Fig.23

Slew Rate H-L

(*)The above data is ability value of sample, it is not guaranteed. BU7461G: -40[℃] ~ +85[℃] BU7461SG: -40[℃] ~ +105[℃]

Ambient Temperature

0

1.E+00 1.E+02 1.E+04 1.E+06 1.E+08

FREQUENCY [Hz]

Gain –Frequency

0

BU7461 famil

25℃

-40℃

85℃ 105℃

INPUT VOLTAGE [V]

(VDD=3[V])

BU7461 family

-40℃

105℃

85℃

SUPPLY VOLTAGE [V]

– Supply Voltage

BU7461 famil

5.5V

1.7V

AMBIENT TEMPERATURE [°C]

Ambient Temperature

25℃

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

12/36

2010.12 - Rev.

Page 13

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7462 family)

800

1000

800

600

600

400

400

200

200

PO WE R DISSIPA TION [mW]

POWER DISSIPATION [mW]

0

0

0 50 100 150

0 50 100 150

AMBIENT TEMPERATURE[℃]

AMBIENT TEMPERATURE [°C]

BU7462F

AMBIENT TEMPERATURE[℃]

Fig.24 Fig.25 Fig.26

Derating curve

BU7462FVM

BU7462NUX

85

BU7462 famil

800

1000

800

600

600

400

400

200

200

POWER DISSIPATION [mW]

POWER DISSIPATIO N [m W ]

0

0

0 50 100 150

0 50 100 150

AMBIENT TEMPERATURE[℃]

AMBIENT TEMPERATURE[℃]

AMBIENT TEMPERATURE [°C]

Derating curve

800

BU7462 famil

6

600

400

200

SUPPLY CURRENT [μA]

3.0V

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

5.5V

1.7V

4

2

OUTPUT VOLTAGE HIGH [V]

0

0246

85℃

SUPPLY VOLTAGE [V]

Fig.27 Fig.28 Fig.29

Supply Current – Ambient Temperature

-40℃

BU7462 family

105℃

25℃

12

9

6

3

OUTPUT VOLTAGE LOW [mV]

0

0246

85℃

SUPPLY VOLTAGE [V]

Output Voltage High – Supply Voltage

(RL=10[kΩ])

8

6

4

2

OUTPUT VOLTAGE LOW [mV]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

1.7V

Fig.30 Fig.31 Fig.32

Output Voltage Low – Supply Voltage

(RL=10[kΩ])

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

20

15

3.0V

10

5

BU7462 family

5.5V

1.7V

OUTPUT SOURCE CURRENT [mA]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Fig.33 Fig.34 Fig.35

Output Source Current – Ambient Temperature

(VOUT=VDD-0.4[V])

(*)The above data is ability value of sample, it is not guaranteed. BU7462F/FVM/NUX: -40[℃] ~ +85[℃] BU7462S F/FVM/NUX: -40[℃] ~ +105[℃]

80

60

40

20

OUTPUT SINK CURRENT [mA]

25℃

0

0123

OUTPUT VOLTAGE [V]

Output Sink Current – Output Voltage

(VDD=3[V])

BU7462SF

BU7462SFVM

BU7462SNUX

105

-40℃

25℃

105℃

5.5V

3.0V

-40℃

105℃

BU7462 famil

BU7462 family

BU7462 famil

BU7462 family

85℃

500

400

300

200

100

SUPPLY CURRENT [μA]

0

0246

85℃

-40℃

SUPPLY VOLTAGE [V]

Supply Current – Supply Voltage

8

6

4

2

OUTPUT VO L T AGE HIGH [V]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Output Voltage High – Ambient Temperature

40

30

20

10

OUTPUT SINK CURRENT [mA]

0

0123

Output Source Current – Output Voltage

60

40

20

OUTPUT SINK CURRENT [mA]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Output Sink Current – Ambient Temperature

5.5V

3.0V

1.7V

(RL=10[kΩ])

85℃

105℃

OUTPUT VOLTAGE [V]

(VDD=3.0[V])

3.0V

1.7V

(VOUT=VSS+0.4[V])

BU7462 famil

105℃

25℃

BU7462 family

BU7462 famil

-40℃

25℃

BU7462 family

5.5V

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

13/36

2010.12 - Rev.

Page 14

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

–

–

–

–

–

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7462 family)

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

-7.5

INPUT OFFSET VOLTAGE [mV]

-10.0

0123456

Fig.36 Fig.37 Fig.38

-40℃

85℃

SUPPLY VOLTAGE [V]

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

BU7462 famil

25℃

105℃

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

-7.5

INPUT OFFSET VOLTAGE [mV]

-10.0

-60 -30 0 30 60 90 120

3.0V

1.7V

AMBIENT TEMPERATURE [°C]

Input Offset Voltage – Ambient Temperature

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

25℃

120

100

80

60

LARGE SIGNAL VOLTAGE GAIN [dB]

0123456

SUPPLY VOLTAGE [V]

Fig.39 Fig.40 Fig.41

Large Signal Voltage Gain

Supply Voltage

-40℃

BU7462 famil

105℃

85℃

160

140

120

100

80

LARGE SIGNAL VOLTAGE GAIN [dB]

60

1.7V

3.0V

-60-300 306090120

AMBIENT TEMPERATURE [°C]

Large Signal Voltage Gain

Ambient Temperature

BU7462 family

5.5V

15

10

5

0

-5

-10

INPUT OFFSET VOLTAGE [mV]

-15

-1 0 1 2 3

25℃

85℃ 105℃

INPUT VOLTAGE [V]

Input Offset Voltage – Input Voltage

(VDD=3[V])

BU7462 famil

5.5V

120

100

80

60

40

20

0

COMMON MODE REJECTION RATIO [dB]

0123456

105℃

SUPPLY VOLTAGE [V]

Common Mode Rejection Ratio

– Supply Voltage

120

100

80

60

40

20

0

COMMON MODE REJECTION RATIO [dB]

3.0V

-60-300 306090120

AMBIENT TEMPERATURE [°C]

Fig.42 Fig.43 Fig.44

Common Mode Rejection Ratio

Ambient Temperature

5.5V

1.7V

BU7462 famil

200

160

120

80

40

0

POWER SUPPLY REJECTION RATIO [dB]

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Power Supply Rejection Ratio

– Ambient Temperature

BU7462 famil

2.0

1.6

1.2

0.8

SLEW RATE L-H [V/μs]

0.4

0.0

-60 -30 0 30 60 90 120

Slew Rate L-H

3.0V

1.7V

AMBIENT TEMPERATURE [°C]

Ambient Temperature

5.5V

BU7462 family

3.0V

100

80

60

40

GAIN [dB]

20

Phase

Gain

2.0

1.6

1.2

0.8

0.4

SLEW RATE H-L [V/μs]

1.7V

BU7462 famil

200

150

100

PHASE [deg]

50

0.0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Fig.45 Fig.46

Slew Rate H-L

Ambient Temperature

(*)The above data is ability value of sample, it is not guaranteed. BU7462F/FVM/NUX: -40[℃] ~ +85[℃] BU7462S F/FVM/NUX: -40[℃] ~ +105[℃]

0

1.E+00 1.E+02 1.E+04 1.E+06 1.E+08

FREQUENCY [Hz]

Gain –Frequency

0

-40℃

-40℃

85℃

BU7462 famil

BU7462 family

25℃

BU7462 family

5.5V

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

14/36

2010.12 - Rev.

Page 15

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7464 family)

800

600

400

200

POWER DISSIPATIO N [mW] .

0

0 50 100 150

AMBIENT TEMPERATURE [℃]

Fig.47 Fig.48 Fig.49

1000

750

500

250

SUPPLY CURRENT [μA]

0

-60-300 306090120

AMBIENT TEMPERATURE [℃]

Fig.50 Fig.51 Fig.52

Supply Current – Ambient Temperature

12

9

6

3

OU TPUT VOLTAGE LOW [mV]

0

123456

Fig.53 Fig.54 Fig.55

Output Voltage Low – Supply Voltage

20

15

10

5

OUTPUT SOURCE CURRENT [mA]

0

-60 -30 0 30 6 0 90 120

AMBIENT TEMPERATURE [℃]

Fig.56 Fig.57 Fig.58

Output Source Current – Ambient Temperature

BU7464F

Derating curve

3.0V

85℃

-40℃

SUPPLY VOLTAGE [V]

(RL=10[kΩ])

(VOUT=VDD-0.4[V])

(*)The above data is ability value of sample, it is not guaranteed. BU7464F: -40[℃] ~ +85[℃] BU7464SF: -40[℃] ~ +105[℃]

85

1.7V

5.5V

3.0V

5.5V

105℃

1.7V

BU7464 famil

BU7464 famil

BU7464 famil

25℃

BU7464 famil

800

600

400

200

POWER DISSIPATION [mW] .

0

050100150

A MBIEN T TEMPE RAT URE [℃]

BU7464SF

BU7464 famil

105

Derating curve

6

5

4

3

2

1

OUTPUT VOLTAGE HIGH [ V]

0

123456

105℃

85℃

-40℃

SUPPLY VOLTAGE [V]

BU7464 famil

25℃

Output Voltage High – Supply Voltage

(RL=10[kΩ])

8

6

4

2

OUTPUT VOLTAGE LOW [mV]

0

-60-30 0 306090120

AMBIENT TEMPERATURE [℃]

5.5V

BU7464 famil

3.0V

1.7V

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

80

60

40

20

OUTPUT SINK CURRENT [mA]

0

25℃

0.0 0. 5 1.0 1.5 2.0 2.5 3.0

OUTPUT VOLTAGE [ V]

-40℃

85℃

BU7464 famil

105℃

Output Sink Current – Output Voltage

(VDD=3[V])

1000

750

500

250

SUPPLY CURRENT [μA]

0

123456

85℃

-40℃

SUPPLY VOLTAGE [V]

BU7464 famil

105℃

25℃

Supply Current – Supply Voltage

8

6

4

2

OUT PUT VOLTAG E HIGH [V]

0

-60 -30 0 30 60 90 1 20

5.5V

3.0V

1.7V

AMBIENT TEMPERATURE [℃]

BU7464 famil

Output Voltage High – Ambient Temperature

(RL=10[kΩ])

40

30

20

10

OUTPU T SOURCE CURRENT [mA]

-40℃

105℃

0

0 0.5 1 1.5 2 2.5 3

85℃

OUT PUT VOLTAG E [V]

BU7464 family

25℃

Output Source Current – Output Voltage

(VDD=3.0[V])

60

50

40

30

20

10

OUTPU T SINK CURRENT [mA]

1.7V

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERAT URE[℃]

5.5V

3.0V

Output Sink Current – Ambient Temperature

(VOUT=VSS+0.4[V])

BU7464 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

15/36

2010.12 - Rev.

Page 16

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

–

–

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7464 family)

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

INPUT OFFSET VOLTAG E [mV]

-7.5

-10.0

123456

105℃

INPUT VOLTAGE [V]

Fig.59 Fig.60 Fig.61

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

LARGE SIG NAL VOLTAGE GAIN [dB]

60

123456

105℃

-40℃

SUPPLY VOLTAGE [V]

Fig.62 Fig.63 Fig.64

Large Signal Voltage Gain

– Supply Voltage

120

100

80

60

40

20

COMMON MO DE REJE CTION R ATI O [dB]

0

1.7V

-60-300 306090120

AMBIE NT TEMPERATURE [℃]

Fig.65 Fig.66 Fig.67

Common Mode Rejection Ratio

– Ambient Temperature

2.0

1.6

3.0V

1.2

0.8

SLEW RA TE H-L [V/μs]

0.4

0.0

-60 -30 0 30 60 90 120

1.7V

A MBIEN T TEMP ERAT URE [℃]

Fig.68 Fig.69

Slew Rate H-L – Ambient Temperature

BU7464 famil

85℃

-40℃ 25℃

BU7464 family

85℃

25℃

BU7464 famil

5.5V

BU7464 famil

5.5V

3.0V

10.0

7.5

INPUT OFFSET VOLTAGE [mV]

5.0

2.5

0.0

-2.5

-5.0

-7.5

-10.0

5.5V

3.0V

-60-300 306090120

A MB I EN T TE MP E RA T UR E [℃]

Input Offset Voltage – Ambient Temperature

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

LARGE SIGNAL VOLTAGE GAIN [dB]

60

-60-30 0 30 60 90120

3.0V

1.7V

AMBIE NT TEMPERATURE [℃]

Large Signal Voltage Gain

Ambient Temperature

140

120

100

80

60

40

20

POWE R S UPPLY RE JECTI ON RA TIO [d B]

0

-60 -30 0 30 60 90 120

AMBIE NT TEMPERATURE [℃]

Power Supply Rejection Ratio

– Ambient Temperature

100

80

60

GAIN [dB]

40

20

0

Phase

Gain

1.E+00 1.E+01 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 1.E+07 1.E+08

FREQUENCY [Hz]

Gain –Frequency

5.5V

BU7464 famil

BU7464 famil

1.7V

BU7464 family

BU7464 famil

200

150

100

50

0

15

10

5

0

-5

-10

INPUT OFFSET VOLTAGE [mV]

-15

-1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0

-40℃

25℃

105℃

INPUT VOLTAGE [V ]

Input Offset Voltage – Input Voltage

(VDD=3[V])

120

100

-40℃

80

60

40

20

COMM ON MODE REJE CT ION RA T I O [dB]

0

85℃

123456

25℃

105℃

SUPPLY VOLTAGE [V]

Common Mode Rejection Ratio

Supply Voltage

2

1.5

5.5V

1

0.5

POWE R S UPPLY RE JECTI ON RA TIO [d B]

0

-60-30 0 306090120

1.7V

AMBIENT TEMPERATURE [℃]

Slew Rate L-H – Ambient Temperature

PHASE [deg]

(*)The above data is ability value of sample, it is not guaranteed. BU7464F: -40[℃] ~ +85[℃] BU7464SF: -40[℃] ~ +105[℃]

BU7464 famil

85℃

BU7464 family

BU7464 famil

3.0V

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

16/36

2010.12 - Rev.

Page 17

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7465 family)

1000

800

600

400

200

POWER DISSIPATIO N [mW] .

0

050100150

Fig.70 Fig.71 Fig.72

300

250

200

150

100

SUPPLY CURRENT [μA]

50

0

-60-30 0 30 60 90120

Fig.73 Fig.74 Fig.75

Supply Current – Ambient Temperature

15

10

5

OUTPUT VOLTAGE LOW [mV]

0

123456

Fig.76 Fig.77 Fig.78

Output Voltage Low – Supply Voltage

20

15

10

5

OUTPUT SOURCE CURRENT [mA]

0

-60 -30 0 30 60 90 120

Fig.79 Fig.80 Fig.81

Output Source Current – Ambient Temperature

BU7465HFV

AMBIENT TEMPERATURE [

Derating curve

3.0V

AMBIENT TEMPERATURE [℃]

-40℃

85℃

SUPPLY VOLTAGE [V]

(RL=10[kΩ])

5.5V

1.7V

AMBIENT TEMPERATURE [

(VOUT=VDD-0.4[V])

3.0V

85

BU7465 famil

℃

BU7465 famil

5.5V

1.7V

BU7465 famil

105℃

25℃

BU7465 famil

BU7465 famil

105℃

-40℃

BU7465 famil

BU7465 family

25℃

-40℃

BU7465 famil

105

BU7465 famil

BU7465 famil

BU7465 famil

300

250

200

150

100

SUP PL Y CURREN T [μA]

50

0

123456

85℃

25℃

S UPPLY VOLTAGE [V]

Supply Current – Supply Voltage

8

6

4

2

OUT PUT VOLTAG E HIGH [V]

0

-60 -30 0 30 60 90 1 20

5.5V

3.0V

1.7V

AMBIENT TEMPERATURE [℃]

Output Voltage High – Ambient Temperature

(RL=10[kΩ])

50

40

30

20

10

OUTPU T SOURCE CURRENT [mA]

0

00.511.522.53

25℃

-40℃

85℃ 105℃

OUT PUT VOLTA G E [V]

Output Source Current – Output Voltage

(VDD=3[V])

50

40

30

20

10

OUTPUT SINK CURRENT [ mA]

0

-60 -30 0 30 60 90 120

5.5V

3.0V

1.7V

AMBIENT TEMPERATURE[℃]

Output Sink Current – Ambient Temperature

(VOUT=VSS+0.4[V])

1000

800

600

400

200

POWER DISSIPATIO N [mW] .

0

]

050100150

A MBI ENT TEMP ERA TURE [℃]

BU7465SHFV

Derating curve

6

5

4

3

2

1

OUTPUT VOLTAGE HIGH [V]

0

123456

105℃

85℃

-40℃

SUPPLY VOLTAGE [V]

Output Voltage High – Supply Voltage

(RL=10[kΩ])

15

10

1.7V

5

OUT PUT VOLTAG E LOW [mV]

0

-60 -30 0 3 0 60 90 120

AMBIENT TEMPERATURE [℃]

5.5V 3.0V

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

80

60

40

20

OUTPUT SINK CURRENT [mA]

0

℃

]

25℃

85℃ 105℃

0.0 0. 5 1.0 1.5 2.0 2.5 3.0

OUTPUT VOLTAGE [ V]

Output Sink Current – Output Voltage

(VDD=3[V])

(*)The above data is ability value of sample, it is not guaranteed. BU7465HFV: -40[℃] ~ +85[℃] BU7465SHFV: -40[℃] ~ +105[℃]

BU7465 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

17/36

2010.12 - Rev.

Page 18

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

–

–

y

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7465 family)

1.7V

5.5V

BU7465 famil

℃

]

BU7465 family

BU7465 famil

℃

]

BU7465 famil

10

8

6

4

2

0

-2

-4

-6

INPUT OFFSET VOLTAGE [mV]

-8

-10

-1.0 -0.5 0.0 0.5 1.0 1. 5 2. 0 2.5 3.0

INPU T VOLTA GE [V]

Input Offset Voltage – Input Voltage

(VDD=3[V])

140

120

100

80

60

40

20

COMM ON MODE REJE CT ION RA T I O [dB]

0

123456

-40℃

SUPPLY VOLTAGE [V]

Common Mode Rejection Ratio

Supply Voltage

3.0

2.5

2.0

1.5

1.0

SL E W RA T E L- H [ V /μ s]

0.5

0.0

-60-300306090120

1.7V

AMBIENT TEMPERATURE [℃]

Slew Rate L-H – Ambient Temperature

200

150

100

PHASE [deg]

50

0

85℃

-40℃

5.5V

BU7465 famil

85℃

BU7465 family

25℃

BU7465 famil

3.0V

℃

]

BU7465 famil

10.0

7.5

INPUT OFFSET VOLTAGE [mV]

5.0

2.5

0.0

-2.5

-5.0

-7.5

-10.0

5.5V

3.0V

1.7V

-60-30 0 30 60 90120

A MB I EN T TE MP E R A T UR E [

Input Offset Voltage – Ambient Temperature

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

LARGE SIGNAL VOLTAGE GAIN [dB]

60

-60-30 0 30 60 90120

3.0V

AMBIE NT TEMPERATURE [℃]

Large Signal Voltage Gain

– Ambient Temperature

140

120

100

80

60

40

20

POWER S UPPLY RE JECTI ON RA TIO [d B]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [

Power Supply Rejection Ratio

– Ambient Temperature

100

80

60

GAIN [dB]

40

20

0

Phase

Gain

1.E+00 1.E+01 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 1. E+07 1.E+08

FREQUENCY [Hz]

Gain –Frequency

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

INPUT OFFSET VOLTAG E [mV]

-7.5

-10.0

123456

Fig.82 Fig.83 Fig.84

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

LARGE SIG NAL VOLTAGE GAIN [d B]

60

123456

Fig.85 Fig.86 Fig.87

140

120

100

80

60

40

20

COMM ON MO DE RE JECTI ON RA TIO [d B]

0

-60 -30 0 30 60 90 120

Fig.88 Fig.89 Fig.90

Common Mode Rejection Ratio

3.0

2.5

2.0

1.5

1.0

SLEW RATE H-L [V/μs]

0.5

0.0

-60 -30 0 30 60 90 1 20

Fig.91 Fig.92

Slew Rate H-L – Ambient Temperature

-40℃ 25℃

105℃

INPUT VO LTAGE [V]

105℃

SUPPLY VOLTAGE [V]

Large Signal Voltage Gain

– Supply Voltage

5.5V

1.7V

A MBIEN T TEMP ERAT URE [

Ambient Temperature

3.0V

1.7V

AMBIENT TEMPERATURE [℃]

(*)The above data is ability value of sample, it is not guaranteed. BU7465HFV: -40[℃] ~ +85[℃] BU7465SHFV: -40[℃] ~ +105[℃]

25℃

85℃

3.0V

85℃

105℃

BU7465 famil

25℃

5.5V

-40℃

BU7465 family

105℃

BU7465 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

18/36

2010.12 - Rev.

Page 19

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

●Reference data (BU7441 family)

800

BU7441 family

800

BU7441 famil

160

Technical Note

BU7441 famil

600

400

BU7441G

600

400

BU7441SG

120

105℃

80

200

POWER DISSIPATION [mW]

0

0 50 100 150

AMBIENT TEMPERATURE [°C]

85

Fig.93 Fig.94 Fig.95

Derating curve

800

BU7441 famil

600

400

3.0V

5.5V

200

SUPPLY CURRENT [μA]

1.7V

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Fig.96 Fig.97 Fig.98

Supply Current – Ambient Temperature

12

BU7441 family

200

POWER DISSIPATION [mW]

0

050100150

AMBIENT TEMPERATURE [°C]

105

Derating curve

6

4

2

OUTPUT VOLTAGE HIGH [V]

0

0246

85℃

SUPPLY VOLTAGE [V]

BU7441 famil

-40℃

25℃

105℃

Output Voltage High – Supply Voltage

(RL=10[kΩ])

8

BU7441 famil

40

SUPPLY CURRENT [μA]

0

0246

25℃

SUPPLY VOLTAGE [V]

Supply Current – Supply Voltage

6

4

2

OUTPUT VOLTAGE HIGH [V]

0

-60 -30 0 30 60 90 120

3.0V

1.7V

AMBIENT TEMPERATURE [°C]

Output Voltage High – Ambient Temperature

(RL=10[kΩ])

30

Fig.102 Fig.103 Fig.104

9

6

3

OUTPUT VOLTAGE LOW [mV]

0

0246

SUPPLY VOLTAGE [V]

105℃

85℃

25℃

-40℃

6

4

2

OUTPUT VOLTAGE LOW [mV]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

5.5V

1.7V

3.0V

Fig.99 Fig.100 Fig.101

Output Voltage Low – Supply Voltage

(RL=10[kΩ])

20

15

10

5

OUTPUT SOURCE CURRENT [mA]

0

-60-300 306090120

AMBIENT TEMPERATURE [°C]

BU7441 famil

5.5V

3.0V

1.7V

Output Source Current – Ambient Temperature

(VOUT=VDD-0.4[V])

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

105℃

BU7441 famil

-40℃

85℃

80

60

40

20

OUTPUT SINK CURRENT [mA]

0

0123

25℃

OUTPUT VOLTAGE [V]

Output Sink Current – Output Voltage

(VDD=3[V])

(*)The above data is ability value of sample, it is not guaranteed. BU7441G: -40[℃] ~ +85[℃] BU7441SG: -40[℃] ~ +105[℃]

23

15

8

OUTPUT SOURCE CURRENT [mA]

0

85℃

105℃

0123

OUTPUT VOLTAGE [V]

Output Source Current – Output Voltage

(VDD=3[V])

60

40

5.5V

20

3.0V

OUTPUT SINK CURRENT [mA]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

1.7V

Output Sink Current – Ambient Temperature

(VOUT=VSS+0.4[V])

85℃

-40℃

BU7441 famil

5.5V

BU7441 famil

-40℃

25℃

BU7441 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

19/36

2010.12 - Rev.

Page 20

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

●Reference data (BU7441 family)

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

-7.5

INPUT OFFSET VO LT AGE [mV]

-10.0

0123456

-40℃

85℃

SUPPLY VOLTAGE [V]

Fig.105 Fig.106 Fig.107

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

25℃

85℃

0123456

SUPPLY VOLTAGE [V]

Fig.108 Fig.109 Fig.110

Large Signal Voltage Gain

– Supply Voltage

120

100

80

60

40

20

0

COMMON MODE REJECTION RATIO [dB]

3.0V

-60-300 306090120

AMBIENT TEMPERATURE [°C]

Fig.111 Fig.112 Fig.113

Common Mode Rejection Ratio

– Ambient Temperature

1.0

0.8

60

LARGE SIGNAL VOLT AG E GAIN [d B]

0.6

0.4

0.2

SLEW RATE H-L [V/μs]

0.0

-60-300 306090120

1.7V

AMBIENT TEMPERATURE [°C]

Fig.114 Fig.115

Slew Rate H-L – Ambient Temperature

(*)The above data is ability value of sample, it is not guaranteed. BU7441G: -40[℃] ~ +85[℃] BU7441SG: -40[℃] ~ +105[℃]

BU7441 family

25℃

105℃

10.0

7.5

5.0

2.5

INPUT OFFSET VO LT AGE [mV]

0.0

-2.5

-5.0

-7.5

-10.0

3.0V

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Input Offset Voltage – Ambient Temperature

(Vicm= VDD-1.2[V], VOUT= VDD/2)

BU7441 famil

-40℃

105℃

160

140

120

100

80

60

LARGE SIGNAL VOLT AGE G AIN [dB]

1.7V

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Large Signal Voltage Gain

– Ambient Temperature

BU7441 famil

5.5V

1.7V

120

100

80

60

40

20

0

POWER SUPPLY REJECT IO N RATIO [dB]

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

5.5V

5.5V

3.0V

1.7V

BU7441 family

BU7441 family

BU7441 famil

15

10

5

0

-5

-10

INPUT OFFSET VO LT AG E [m V]

-15

105℃

25℃

-10123

INPUT VOLTAGE [V]

Input Offset Voltage – Input Voltage

(VDD=3[V])

120

100

80

60

40

20

0

COMMON MO DE R EJECT ION R ATIO [dB]

0123456

SUPPLY VOLTAGE [V]

Common Mode Rejection Ratio

– Supply Voltage

1.0

0.8

0.6

0.4

SLEW RATE L-H [V/μs]

0.2

0.0

-60 -30 0 30 60 90 120

3.0V

AMBIENT TEMPERATURE [°C]

BU7441 famil

3.0V

5.5V

Power Supply Rejection Ratio

– Ambient Temperature

100

80

60

40

GAIN [dB]

20

0

1.E+00 1.E+02 1.E+04 1.E+06 1.E+08

Phase

Gain

FREQUENCY [Hz]

BU7441 famil

200

150

100

50

0

Slew Rate L-H – Ambient Temperature

PHASE [deg]

Gain – Frequency

Technical Note

BU7441 famil

-40℃

85℃

BU7441 family

25℃

-40℃

105℃

1.7V

5.5V

85℃

BU7441 family

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

20/36

2010.12 - Rev.

Page 21

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7442 family)

800

1000

800

600

600

400

400

200

200

POWER DISSIPATION [mW]

POWER DISSIPATION [mW]

0

0

050100150

0 50 100 150

AMBIENT TEMPERATURE[℃]

AMBIENT TEMPERATUR E [ °C]

Fig.116 Fig.117 Fig.118

Derating curve

800

600

400

200

SUPPLY CURRENT [uA]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Fig.119 Fig.120 Fig.121

Supply Current – Ambient Temperature

12

BU7442F

BU7442FVM

BU7442NUX

85

3.0V 1.7V

BU7442 family

BU7442 famil

5.5V

BU7442 family

800

1000

800

600

600

400

400

200

200

POWER DISSIPATION [mW]

POWER DISSIPATION [mW]

0

0

0 50 100 150

0 50 100 150

AMBIENT TEMPERATURE [°C]

AMBIENT TEMPERATURE[℃]

Derating curve

6

4

2

OUTPUT VOLTAGE HIGH [V]

0

0246

85℃

SUPPLY VOLTAGE [V]

Output Voltage High – Supply Voltage

(RL=10[kΩ])

8

BU7442 family

BU7442SF

BU7442SFVM

BU7442SNUX

105

-40℃

25℃

105℃

BU7442 famil

BU7442 famil

300

200

105℃

100

SUPPLY CURRENT [μA]

0

0246

25℃

SUPPLY VOLTAGE [V]

SUPPLY VOLTAGE [V]

Supply Current – Supply Voltage

6

4

2

OUTPUT VOLTAGE HIGH [V]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

3.0V

1.7V

Output Voltage High – Ambient Temperature

(RL=10[kΩ])

30

9

6

3

OUTPUT VOLTA G E LOW [mV]

0

0246

85℃

SUPPLY VOLTAGE [V]

Fig.122 Fig.123 Fig.124

Output Voltage Low – Supply Voltage

(RL=10[kΩ])

20

15

105℃

25℃

-40℃

BU7442 famil

5.5V

6

4

2

OUTPUT VOLTAGE LOW [mV]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

5.5V

1.7V

3.0V

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

80

60

25℃

BU7442 family

-40℃

23

15

8

OUTPUT SOURCE CURRENT [mA]

0

0123

85℃

OUTPUT VOLTAGE [V]

Output Source Current – Output Voltage

(VDD=3.0[V])

60

40

10

OUTPUT SOURCE CURRENT [mA]

Fig.125 Fig.126 Fig.127

Output Source Current – Ambient Temperature

1.7V

5

0

-60-300 306090120

3.0V

AMBIENT TEMPERATURE [°C]

(VOUT=VDD-0.4[V])

40

85℃

20

OUTPUT SINK CURRENT [mA]

0

0123

OUTPUT VOLTAGE [V]

105℃

Output Sink Current – Output Voltage

(VDD=3[V])

20

OUTPUT SINK CURRENT [mA]

0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Output Sink Current – Ambient Temperature

(*)The above data is ability value of sample, it is not guaranteed. BU7442F/FVM/NUX: -40[℃] ~ +85[℃] BU7442S F/FVM/NUX: -40[℃] ~ +105[℃]

5.5V

3.0V

1.7V

(VOUT=VSS+0.4[V])

BU7442 famil

85℃

-40℃

BU7442 family

5.5V

BU7442 famil

-40℃

25℃

105℃

BU7442 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

21/36

2010.12 - Rev.

Page 22

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

–

–

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7442 family)

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

-7.5

INPUT OFFSET VO LTAGE [mV]

-10.0

0123456

Fig.128 Fig.129 Fig.130

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

60

LARGE SIGNAL VOLT AGE GAIN [dB]

0123456

Fig.131 Fig.132 Fig.133

Large Signal Voltage Gain

120

100

80

60

40

20

0

-60 -30 0 30 60 90 120

COMMON MODE REJECTION RATIO [dB]

Fig.134 Fig.135 Fig.136

SLEW RATE H-L [V/μs]

Fig.137 Fig.138

AMBIENT TEMPERATU R E [°C]

Common Mode Rejection Ratio

– Ambient Temperature

1.0

0.8

0.6

0.4

0.2

0.0

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Slew Rate H-L – Ambient Temperature

-40℃

85℃

SUPPLY VOLTAGE [V]

-40℃

25℃

SUPPLY VOLTAGE [V]

Supply Voltage

1.7V

BU7442 famil

25℃

105℃

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

-7.5

INPUT OFFSET VO LTAGE [mV]

-10.0

-60 -30 0 30 60 90 120

AMBIENT TEMPERAT URE [°C]

3.0V

Input Offset Voltage – Ambient Temperature

(Vicm= VDD-1.2[V], VOUT= VDD/2)

BU7442 famil

105℃

85℃

160

140

120

100

80

60

LARGE SIGNAL VOLTAGE GAIN [dB]

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

1.7V

Large Signal Voltage Gain

Ambient Temperature

BU7442 famil

5.5V

1.7V 3.0V

120

100

80

60

40

20

0

POWER SUPPLY REJECTION RATIO [dB]

-60 -30 0 30 60 90 120

AMBIENT TEMPERATURE [°C]

Power Supply Rejection Ratio

– Ambient Temperature

BU7442 famil

3.0V

5.5V

100

80

60

40

GAIN [dB]

20

0

1.E+00 1.E+02 1.E+04 1.E+06 1.E+08

Phase

Gain

FREQUENCY [Hz]

Gain – Frequency

(*)The above data is ability value of sample, it is not guaranteed. BU7442F/FVM/NUX: -40[℃] ~ +85[℃] BU7442S F/FVM/NUX: -40[℃] ~ +105[℃]

5.5V

3.0V

1.7V

BU7442 famil

BU7442 famil

5.5V

BU7442 family

BU7442 family

200

150

100

50

0

15

10

5

0

-5

-10

INPUT OFFSET VO LTAGE [mV]

-15

-1 0 1 2 3

-40℃

25℃

85℃

105℃

INPUT VOLTAGE [V]

Input Offset Voltage – Input Voltage

(VDD=3[V])

120

100

80

60

40

20

0

0123456

COMMON MODE REJECTION RATIO [dB]

85℃

-40℃

SUPPLY VOLTAGE [V]

Common Mode Rejection Ratio

– Supply Voltage

1.0

0.8

0.6

0.4

0.2

SLEW RATE L-H [V/μs]

0.0

-60 -30 0 30 60 90 120

3.0V

AMBIENT TEMPERATURE [°C]

Slew Rate L-H – Ambient Temperature

PHASE [deg]

105℃

1.7V

5.5V

BU7442 family

BU7442 famil

25℃

BU7442 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

22/36

2010.12 - Rev.

Page 23

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7444 family)

1000

800

600

400

200

POWER DISSIPATION [mW] .

0

0 50 100 150

Fig.139 Fig.140 Fig.141

400

350

300

250

200

150

100

SUPPLY CURRENT [μA]

50

0

-60-30 0 30 60 90120

Fig.142 Fig.143 Fig.144

Supply Current – Ambient Temperature

12

9

6

3

OUT PU T VOLTAG E LOW [mV]

0

123456

Fig.145 Fig.146 Fig.147

Output Voltage Low – Supply Voltage

20

15

10

5

OUTPUT SOURCE CURRENT [mA ]

0

-60 -30 0 30 60 90 120

Fig.148 Fig.149 Fig.150

Output Source Current – Ambient Temperature

BU7444F

AMBIENT TEM PERATURE [℃]

Derating curve

3.0V

AMBIENT TEMPERATURE [

85℃

-40℃

SUPPLY VOLTAGE [V]

(RL=10[kΩ])

5.5V

1.7V

AMBIENT TEMPERATURE [℃]

(VOUT=VDD-0.4[V])

85

BU7444 famil

BU7444 family

5.5V

1.7V

BU7444 famil

105℃

25℃

3.0V

℃

]

BU7444 famil

1000

800

600

400

200

POWER DISSIPATIO N [mW] .

0

050100150

AMBIENT TEMPERATURE [℃]

BU7444SF

Derating curve

6.00

5.00

105℃

4.00

3.00

2.00

1.00

OUTPUT VOLTAGE HIGH [V]

0.00

123456

85℃

-40℃

SUPPLY VOLTAGE [V]

Output Voltage High – Supply Voltage

(RL=10[kΩ])

8

6

4

2

OUT PUT VOLT AG E LOW [mV]

0

-60-300 306090120

AMBI ENT TEMPERATURE [℃]

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

80

25℃

60

40

20

OUTPUT SINK CURRENT [mA]

-40℃

0

0.0 0. 5 1.0 1.5 2 .0 2.5 3.0

OUTPUT VOLTAGE [ V]

Output Sink Current – Output Voltage

(VDD=3[V])

5.5V

3.0V

25℃

105℃

BU7444 famil

105

BU7444 famil

BU7444 famil

BU7444 famil

1.7V

85℃

400

350

300

250

200

150

100

SUPPLY CURRENT [μA]

50

0

123456

85℃

SUPPLY VOLTAGE [ V]

Supply Current – Supply Voltage

8

6

4

2

OUT PUT VOLTAG E HIGH [V]

0

-60 -30 0 30 60 90 1 20

5.5V

3.0V

1.7V

AMBIENT TEMPERATURE [℃]

Output Voltage High – Ambient Temperature

(RL=10[kΩ])

40

35

30

25

20

15

10

OUTPUT SOURCE CURRENT [mA]

-40℃

25℃

105℃

85℃

5

0

00.511.522.53

OUT PUT VOLTAG E [V]

Output Source Current – Output Voltage

(VDD=3.0[V])

60

50

40

30

20

10

OUTPUT SINK CURRENT [mA]

0

-60-30 0 30 60 90120

5.5V

1.7V

AMBIENT TEMPERATURE[℃]

Output Sink Current – Ambient Temperature

(VOUT=VSS+0.4[V])

BU7444 famil

105℃

25℃

BU7444 famil

BU7444 family

3.0V

(*)The above data is ability value of sample, it is not guaranteed. BU7444F/FVM/NUX: -40[℃] ~ +85[℃] BU7444S F/FVM/NUX: -40[℃] ~ +105[℃]

-40℃

BU7444 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

23/36

2010.12 - Rev.

Page 24

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

–

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

●Reference data (BU7444 family)

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

INPUT OFFSET VOLTAG E [mV]

-7.5

-10.0

123456

105℃

-40℃

INPUT VOLTAGE [V]

Fig.151 Fig.152 Fig.153

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

60

40

20

LARGE SIG NAL VOLTAGE GAIN [d B]

0

123456

105℃

25℃

85℃

SUPPLY VOLTAGE [V]

-40℃

Fig.154 Fig.155 Fig.156

Large Signal Voltage Gain

– Supply Voltage

120

100

80

60

40

20

COMM ON MO DE RE JECTI ON RA TIO [d B]

0

-60-30 0 306090120

5.5V

1.7V

AMBIENT TEMPERATURE [℃]

Fig.157 Fig.158 Fig.159

Common Mode Rejection Ratio

Ambient Temperature

1.0

0.8

0.6

0.4

SL EW RATE H-L [V/μs]

0.2

0.0

-60-30 0 306090120

5.5V

AMBIENT TEMPERATURE [℃]

Fig.160 Fig.161

Slew Rate H-L – Ambient Temperature

25℃

85℃

3.0V

1.7V

BU7444 famil

BU7444 family

BU7444 famil

BU7444 famil

3.0V

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

INPUT OFFSET VOLTAGE [mV]

-7.5

-10.0

-60-300 306090120

5.5V

1.8V

A MB I EN T TE MP E R A T UR E [℃]

Input Offset Voltage – Ambient Temperature

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

LARGE SIGNAL VOLTAGE GAIN [dB]

60

-60-300306090120

3.0V

AMBIE NT TEMPERATURE [℃]

Large Signal Voltage Gain

– Ambient Temperature

140

120

100

80

60

40

20

POWE R S UPPLY RE JECTI ON RA TIO [d B]

0

-60 -30 0 30 60 90 120

AMBIE NT TEMPERATURE [℃]

Power Supply Rejection Ratio

– Ambient Temperature

100

GAIN [dB]

Phase

80

60

40

20

Gain

0

1.E+00 1. E+01 1.E+02 1.E+03 1. E+04 1.E+05 1.E+06 1.E+07 1.E+08

F REQUENCY [ Hz]

Gain – Frequency

1.7V

BU7444 famil

3.0V

BU7444 family

5.5V

BU7444 famil

BU7444 family

200

150

100

50

0

15

10

5

0

-5

-10

INPU T OFFSET VOLTAGE [mV ]

-15

-1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0

Input Offset Voltage – Input Voltage

120

100

80

60

40

20

COMMON MODE RE JECTION RATIO [dB]

0

123456

Common Mode Rejection Ratio

1.0

0.8

s]

μ

0.6

5.5V

0.4

SLEW RATE L-H [V/

0.2

0.0

-60-30 0 3060 90120

A MBI EN T TEMPE RA TUR E [℃]

Slew Rate L-H – Ambient Temperature

PHASE [deg ]

(*)The above data is ability value of sample, it is not guaranteed. BU7444F/FVM/NUX: -40[℃] ~ +85[℃] BU7444S F/FVM/NUX: -40[℃] ~ +105[℃]

Technical Note

25℃

INPUT VOLTAGE [V]

(VDD=3[V])

85℃ 105℃

SUPPLY VOLTAGE [V]

– Supply Voltage

3.0V

1.7V

-40℃

25℃

BU7444 famil

105℃

85℃

BU7444 family

-40℃

BU7444 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

24/36

2010.12 - Rev.

Page 25

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

y

y

y

y

y

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

Technical Note

●Reference data (BU7445 family)

1000

800

600

400

200

POWER DISSIPATION [mW] .

0

050100150

Fig.162 Fig.163 Fig.164

100

75

50

25

SUPPLY CURRENT [μA]

0

-60-30 0 30 60 90120

Fig.165 Fig.166 Fig.167

Supply Current – Ambient Temperature

15

10

5

OUTPUT VOLTAGE LOW [mV]

0

123456

Fig.168 Fig.169 Fig.170

Output Voltage Low – Supply Voltage

30

25

20

15

10

5

OUTPUT SOURCE CURRENT [mA]

0

-60-30 0 306090120

Fig.171 Fig.172 Fig.173

Output Source Current – Ambient Temperature

BU7445HFV

AMBI EN T TEMPERA TUR E [℃]

Derating curve

3.0V

AMBIENT TEMPERATURE [℃]

-40℃

SUPPLY VOLTAGE [V]

(RL=10[kΩ])

3.0V

1.7V

AMBIENT TEMPERATURE [℃]

(VOUT=VDD-0.4[V])

85℃

85

5.5V

BU7445 famil

BU7445 famil

5.5V

1.7V

BU7445 famil

105℃

25℃

BU7245 famil

1000

800

600

400

200

POWER DISSIPATIO N [mW] .

0

050100150

A MBI ENT TEMP ERA TURE [℃]

BU7445SHFV

Derating curve

6.00

5.00

4.00

3.00

2.00

1.00

OUTPUT VOLTAGE HIGH [V]

0.00

123456

105℃

85℃

-40℃

SUPPLY VOLTAGE [V]

Output Voltage High – Supply Voltage

(RL=10[kΩ])

15

10

5

OUTPUT VOLTAGE LOW [mV]

0

-60-300 306090120

1.7V

A MBI EN T TEMPE RAT URE [℃]

Output Voltage Low – Ambient Temperature

(RL=10[kΩ])

80

-40℃

60

25℃

40

20

OUTPUT SINK CURRENT [mA]

0

0.0 0. 5 1.0 1.5 2.0 2.5 3.0

OUTPUT VOLTAGE [ V]

Output Sink Current – Output Voltage

(VDD=3[V])

BU7445 famil

105

BU7445 famil

25℃

BU7445 famil

5.5V 3.0V

BU7445 famil

85℃ 105℃

100

75

50

25

SUPPLY CURRENT [μA]

0

123456

85℃

25℃

SUPPLY VOLTAGE [ V]

-40℃

Supply Current – Supply Voltage

8

6

4

2

OUT PUT VOLTAG E HIGH [V]

0

-60 -30 0 30 60 90 1 20

5.5V

3.0V

1.7V

AMBIENT TEMPERATURE [℃]

Output Voltage High – Ambient Temperature

(RL=10[kΩ])

50

40

30

20

10

OUTPU T SOURCE CURRENT [mA]

0

-40℃

105℃

85℃

00.511.522.53

OUT PUT VOLTA G E [V]

Output Source Current – Output Voltage

(VDD=3.0[V])

50

40

30

20

10

OUTPUT SINK CURRENT [mA]

0

-60-30 0 30 60 90120

5.5V

1.7V

AMBIENT TEMPERATURE[℃]

Output Sink Current – Ambient Temperature

(VOUT=VSS+0.4[V])

BU7445 famil

105℃

BU7445 famil

BU7445 family

25℃

3.0V

(*)The above data is ability value of sample, it is not guaranteed. BU7445HFV: -40[℃] ~ +85[℃] BU7445S HFV: -40[℃] ~ +105[℃]

BU7445 famil

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

25/36

2010.12 - Rev.

Page 26

A

BU7461/BU7461S family, BU7441/BU7441S family, BU7462/BU7462S family, BU7442/BU7442S family

y

y

–

–

y

–

y

y

y

y

BU7464/BU7464S family, BU7444/BU7444S family, BU7465/BU7465S family, BU7445/BU7445S family

●Reference data (BU7445 family)

10.0

7.5

5.0

2.5

0.0

-2.5

-5.0

INPUT OFFSET VOLTAG E [mV]

-7.5

-10.0

123456

-40℃ 25℃

85℃

INPU T VOLTA GE [V]

Fig.174 Fig.175 Fig.176

Input Offset Voltage – Supply Voltage

(Vicm= VDD-1.2[V], VOUT= VDD/2)

160

140

120

100

80

LARGE SIG NAL VOLTAGE GAIN [dB]

60

123456

85℃

-40℃