High-performance Regulator IC Series for PCs

Switching Regulators

for DDR-SDRAM Cores

BD9533EKN

●Description

BD9533EKN is a switching regulator controller with high output current which can achieve low output voltage (0.7V to 2.0V)

TECHNICAL NOTE

from a wide input voltage range (4.5V to 28V). High efficiency for the switching regulator can be realized by utilizing an

external N-MOSFET power transistor. A new technology called H

ultra high transient response against load change. SLLM (Simple Light Load Mode) technology is also integrated to improve

efficiency in light load mode, providing high efficiency over a wide load range. For protection and ease of use, the soft start

function, variable frequency function, short circuit protection function with timer latch, over voltage protection function and

REF synchronous function are all built in. This switching regulator is specially designed for the DDR-SDRAM core.

●Features

●Applications

3

1) H

2) Light Load Mode and Continuous Mode Changeable

3) Thermal Shut Down (TSD), Under Voltage LockOut (UVLO), Over Current Protection (OCP),

Over Voltage Protection (OVP), Short Circuit Protection (SCP) built-in

4) Soft start function to minimize rush current during startup

5) Switching Frequency Variable (f=200KHz~600KHz)

6) HQFN20V Package

Laptop PC, Desktop PC, LCD-TV, Digital Components

RegTM Switching Regulator Controller

3

RegTM is a Rohm proprietary control method to realize

Sep. 2008

●Maximum Absolute Ratings (Ta=25℃)

*

1

*

1

*

1

*

1

*

1

*

1

*

1

*

2

*

3

*

4

*

5

r

r

Parameter Symbol Limit Unit

Input Voltage 1 VCC 7

Input Voltage 2 VDD 7

Input Voltage 3 VIN 30

BOOT Voltage BOOT 35

BOOT-SW Voltage BOOT-SW 7

HG-SW Voltage HG-SW 7

V

V

V

V

V

V

LG Voltage LG VDD V

REF Voltage REF VCC V

Output Voltage VOUT/Is+/Is- VCC V

ILIM/SCP/SS/FS/SLLM Voltage ILIM/SCP/SS/FS/SLLM VCC V

VREG Voltage VREG VCC V

EN Input Voltage EN 7

Power Dissipation 1 Pd1 0.5

Power Dissipation 2 Pd2 0.75

Power Dissipation 3 Pd3 1.75

Power Dissipation 4 Pd4 2.00

Operating Temperature Range Top

-10~+100 ℃

V

W

W

W

W

Storage Temperature Range Tstg -55~+150 ℃

Maximum Junction Temperature Tjmax +150 ℃

*1 Not to exceed Pd.

*2 Reduced by 4mW for each increase in Ta of 1℃ over 25℃ (when don’t mounted on a heat radiation board )

*3 Reduced by 6mW for increase in Ta of 1℃ over 25℃. (when mounted on a board 70.0mm×70mm×1.6mm Glass-epoxy PCB.)

*4 Reduced by 14mW for increase in Ta of 1℃ over 25℃. (when mounted on a board 70.0mm×70mm×1.6mm Glass-epoxy PCB.)

*5 Reduced by 16mW for increase in Ta of 1℃ over 25℃. (when mounted on a board 70.0mm×70mm×1.6mm Glass-epoxy PCB.)

●Operating Conditions (Ta=25℃)

Paramete

Symbol MIN MAX Unit

Input Voltage 1 VCC 4.5 5.5 V

Input Voltage 2 VDD 4.5 5.5 V

Input Voltage 3 VIN 4.5 28 V

BOOT Voltage BOOT 4.5 33 V

SW Voltage SW -0.7 28 V

BOOT-SW Voltage BOOT-SW 4.5 5.5 V

SLLM Input Voltage SLLM 0 5.5 V

EN Input Voltage EN 0 5.5 V

Output setting voltage REF 0.7 2.0 V

Is Input Voltage Is+/Is- 0.7 2.7 V

MIN ON Time Tonmin - 200 nsec

★ This product should not be used in a radioactive environment.

2/20

●ELECTRICAL CHARACTERISTICS

(unless otherwise noted, Ta=25℃ VCC=5V,VDD=5V,EN/SLLM=5V,VIN=12V,REF=1.8V,R

Parameter Symbol

Standard Value

MIN TYP MAX

=68kΩ)

FS

Unit Condition

[Whole Device]

VCC Bias Current Icc - 700 900 μA

VIN Bias Current Iin - 100 200 μA

VCC Standby Current Iccstb - 0 10 μA EN=0V

VIN Standby Current Iinstb - 100 200 μA EN=0V

EN Low Voltage Enlow GND - 0.8 V

EN HighVoltage Enhigh 2.3 - 5.5 V

EN Bias Current Ien - 7 10 μA

VREG Voltage Vreg 2.475 2.500 2.525 V

Ireg=100μA

Ta =- 10 ℃ to 100℃*

[Under Voltage Locked Out ]

VCC threshold voltage Vcc_UVLO 4.1 4.3 4.5 V VCC:Sweep up

VCC hysteresis voltage dVcc_UVLO 100 160 220 mV VCC:Sweep down

VIN threshold voltage Vin_UVLO 4.1 4.3 4.5 V VIN:Sweep up

VIN hysteresis voltage dVin_UVLO 100 160 220 mV VIN:Sweep down

VREG threshold voltage Vreg_UVLO 2.0 2.2 2.4 V VREG:Sweep up

VREG hysteresis voltage dVreg_UVLO 100 160 220 mV VREG:Sweep down

[H3RegTM]

Frequency Fosc - 300 - kHz

ON Time Ton 400 500 600 nsec

MAX ON Time Tonmax - 3 - μsec

MIN OFF Time Toffmin - 450 550 nsec

[FET Driver]

HG Higher side ON resistor HGhon - 3.0 6.0 Ω

HG Lower side ON resistor HGlon - 2.0 4.0 Ω

LG Higher side ON resistor LGhon - 2.0 4.0 Ω

LG Lower side ON resistor LGlon - 0.5 1.0 Ω

[Dead Time]

HG rising HGdead - 50 - nsec

LG rising LGdead - 50 - nsec

[SCP]

SCP Detect Voltage Vscp

REF×0.65 REF×0.7 REF×0.75

V

SCP threshold voltage Vscpth 1.2 1.25 1.3 V

Charge current Iscp 1.5 2 2.5 μA

Standby voltage Vscp_stb - - 50 mV

[OVP]

OVP Detect Voltage VOVP

REF×1.16 REF×1.2 REF×1.24

V

[Soft start]

Charge current Iss 1.5 2 2.5 μA

Standby voltage Vss_stb - - 50 mV

[Over Current Protection Block]

Current limit threshold1 Ilim1 43 50 57 mV

ILIM=0.5V

Ta =- 10 ℃ to 100℃*

Current limit threshold2 Ilim2 160 200 240 mV ILIM=2.0V

Reverse current limit threshold1 ReIlim1 - -50 - mV ILIM=0.5V

Reverse current limit threshold2 ReIlim2 - -200 - mV ILIM=2.0V

[VOUT setting ]

VOUT offset voltage1 Voutoff1 REF-7m REF REF+7m V Ta=-10℃ to 100℃*

VOUT bias current Ivout -100 0 100 nA

REF bias current Iref -100 0 100 nA

Is+ Input current IIs+ -1 0 1 μA Is+=1.8V

Is- Input current IIs- -1 0 1 μA Is-=1.8V

[SLLM ]

Continuous mode threshold Vthcon VCC-0.5 - VCC V

SLLM threshold VthSLLM GND - 0.5 V

* Design Guarantee

3/20

●Reference Data

]

600

590

580

Icc(uA)

570

560

550

-1010 30507090

Ta(℃)

Fig.1 Ta vs Icc Fig.3 Ta vs UVLO (VCC)

2.500

2.498

2.496

2.494

VREG[V

2.492

2.490

-101030507090

Ta(℃)

Fig.2 Ta vs VREG

4.30

4.25

4.20

4.15

VCC[V]

4.10

4.05

4.00

-101030507090

Ta(℃)

4.30

4.25

4.20

4.15

VIN[V]

4.10

4.05

Sweep up

Sweep down

4.00

-1010 30507090

Fig.4 Ta vs UVLO (VIN) Fig.5 Ta vs UVLO (VREG) Fig.6 Ta vs EN Threshold

Ta(℃)

2.20

2.15

2.10

2.05

VREG[V]

2.00

1.95

1.90

-101030507090

Sweep up

Sweep down

Ta(℃)

1.7

1.6

1.5

EN[V]

1.4

1.3

1.2

-10103050 7090

Ta(

2.8

2.4

2.0

1.6

1.2

VREG(V)

0.8

0.4

0.0

0 1.5 3 4.5 6

CC vs VREG (Start up)

Fig.7 V

Right: -10℃

Middle: 25℃

Vcc(V)

400

350

300

250

200

TON [nsec]

150

100

50

0

0.6 0.8 1 1.2 1.4 1.6 1.8 2

Fig.10 REF-ON TIME

(V

Bottom: 100℃

REF [V]

IN=25V)

Left: 100℃

Top: -10℃

Middle: 25℃

1000

900

800

700

600

500

400

TON [nsec]

300

200

100

0

0.6 0.8 1 1.2 1.4 1.6 1.8 2

Top: -10℃

Middle: 25℃

Bottom: 100℃

REF [V]

Fig.8 REF vs ON TIME

IN=7V)

(V

1200

1000

800

600

TON [nsec]

400

200

0

5 10152025

Top: -10℃

Middle: 25℃

Bottom: 100℃

VIN [V]

Fig.11 VIN-ON TIME

(REF=1.8V)

600

500

400

300

TON [nsec]

200

100

0

0.6 0.8 1 1.2 1.4 1.6 1.8 2

REF [V]

Fig.9 REF vs ON TIME

IN=12V)

(V

3

2

1

0

-1

VOUT-REF [mV]

-2

-3

-101030507090

Ta [℃]

Fig.12 Ta vs VOUT offset

Sweep up

Sweep down

Sweep up

Sweep down

)

℃

Top: -10℃

Middle: 25℃

Bottom: 100℃

4/20

●Reference Data

54

52

50

Is [mV]

⊿

48

46

-101030507090

Fig.13 Ta vs current limit

threshould

Te [

]

℃

ILIM=0.5V

100

SLLM

80

60

[%]

η

40

Continuous

mode

20

0

1 10 100 1000 10000

Fig.16 Io vs Efficiency

Io(mA)

(V

IN=7V)

VOUT

HG/LG

IOUT

Fig.19 Load Transient

Response (V

IN=7V)

VOUT

HG/LG

IOUT

Fig.22 Load Transient

Response (V

IN=7V)

350

330

310

290

frequency[kHz]

270

250

-10 10 30 50 70 90

Ta(℃)

400

360

320

280

frequency[kHz]

240

200

0 5 10 15 20 25

Io=2A

Io=0A

VIN(V)

Fig.14 Ta vs Frequency Fig.15 VIN vs Frequency

100

SLLM

80

60

[%]

η

40

20

0

1 10 100 1000 10000

Continuous

mode

Io(mA)

Fig.17 Io vs Efficiency

(V

IN=12V)

VOUT

HG/LG

IOUT

Fig.20 Load Transient Response

(VIN=12V)

VOUT

HG/LG

IOUT

Fig.23 Load Transient Response

IN=12V)

(V

100

[%]

η

80

60

40

20

SLLM

Continuous

mode

0

1 10 100 1000 10000

Io(mA)

Fig.18 Io vs Efficiency

(V

IN=20V)

VOUT

HG/LG

IOUT

Fig.21 Load Transient

Response (V

VOUT

HG/LG

IOUT

IN=19V)

Fig.24 Load Transient

Response (V

IN=19V)

5/20

●Reference Data

HG/LG

IL

HG/LG/SW

VIN

HG/LG

VOUT

1.82

1.81

1.8

VOUT [V]

1.79

1.78

VOUT

IL

Fig.25 SLLM

(I

OUT=0A)

Fig.28 Continuous MODE

(Io=0A)

Fig.31 VIN change

(5→19V)

Continuous

mode

SLLM

1 10 100 1000 10000

Iout [mA]

Fig.34 I

OUT-VOUT Fig.35 IOUT-Frequency Fig.36 FS resistance- Frequency

IL

HG/LG/SW

VIN

HG/LG

VOUT

VOUT

IL

HG/LG

Fig.26 SLLM

(I

OUT=0.4A)

Fig.29 Continuous MODE

(Io=4A)

Fig.32 VIN change

(19→5V)

400

Continuous

350

300

250

200

150

Frequency [kHz]

100

50

0

mode

SLLM

1 10 100 1000 10000

Iout [mA]

IL

HG/LG/SW

EN

SS

VOUT

VOUT

IL

HG/LG

Fig.27 SLLM

(I

OUT=1A)

Fig.30 Continuous MODE

(Io=5A)

Fig.33 FS VIN wake up

700

600

500

400

300

Frequency [kHz]

200

100

From upper side VIN=5V

30 40 50 60 70 80 90 100 110 120 130

RFS [kΩ]

7V

12V

16V

19V

6/20

●Block Diagram

2

VIN VCC

5

VREG

19 16

SS

VOUT

EN

SCP

REF

4

7

20

18

Reference

Block

REF×0.7

SS×0.7

VOUT

Thermal

Protection

SS

TSD

VREG

VIN

SCP

UVLO

ILIM

SCP

TSD

+

+

UVLO

SCP

H3RegTM

Controller

Block

2.5VReg

REF×1.2

VOUT

R

S

ILIM

2.5V

Q

Current Limit

Soft Start Block

OVP

SLLM

SLLM

-

+

Driver

Circuit

SS

BOOT

HG

SW

VDD

LG

PGND

EN/UVLO

15

14

13

12

11

10

VDD

1

GND FS

17

6

SLLM

3 9

ILIM

Is+

8

Is-

●PHYSICAL DIMENSIONS ●Pin Number・Pin Name

BD9533

1PIN MARK

Lot No.

※ Mounting is not recommended to the dotted line part.

(UNIT:mm)

HQFN20V

Pin

No.

Pin Name

1 GND

2 VCC

3 ILIM

4 EN

5 VIN

6 SLLM

7 SCP

8 IS-

9 IS+

10 PGND

11 LG

12 VDD

13 SW

14 HG

15 BOOT

16 SS

17 FS

18 VOUT

19 VREG

20 REF

- FIN

Please short FIN to the 1PIN

VIN

VOUT

7/20

●Pin Descriptions

・GND(1pin)

This is the ground pin for IC internal circuits. It is equivalent to FIN voltage.

・VCC(2pin)

This is the power supply pin for IC internal circuits, except the FET driver. The maximum circuit current is 900uA. The input

supply voltage range is 4.5V to 5.5V. It is recommended that a 0.1uF bypass capacitor be put in this pin.

・ILIM(3pin)

BD9533EKN detects the voltage between Is+ pin and Is- pin and limits the output current (OCP). Voltage equivalent to 1/10

of the ILIM voltage is the voltage drop of external current sense resistor. A very low current sense resistor or inductor DCR

can also be used for this platform.

・EN(4pin)

When EN pin voltage is at least 2.3V, the status of this switching regulator becomes active. Conversely, the status switches

off when EN pin voltage goes lower than 0.8V and circuit current becomes 10uA.

・VIN(5pin)

The duty cycle is determined by input voltage and output voltage. In other words, the output voltage is affected by input

voltage. Therefore, when VIN voltage fluctuates, the output voltage becomes also unstable. Since the VIN line is also the

input voltage of the switching regulator, stability depends on the impedance of the voltage supply. It is recommended to

establish a bypass capacitor or CR filter suitable for the actual application.

・SLLM(6pin)

This is the switch shift pin for Simple Light Load Mode. The efficiency in SLLM is improved when SLLM pin voltage goes

lower than 0.5V.

・SCP(7pin)

This is the pin to adjust the timer latch time for short circuit protection. The timer circuit is active when the pin voltage

becomes 70% of REF, and the output switches OFF and latched after the specified time. When the UVLO circuit is active or

EN is low, this latch function is cancelled.

・Is-(8pin) ,Is+(9pin)

These pins are connected to both sides of the current sense resistor to detect output current. The voltage drop between Is+

and Is- is compared with the voltage equivalent to 1/10 of ILIM voltage. When this voltage drop reaches the specified

voltage level, the output voltage goes OFF.

・PGND(10pin)

This is the power ground pin connected to the source of the low side FET.

・LG(11pin)

This is the voltage supply to drive the Gate of the low side FET. This voltage swings between VDD and PGND. High-speed

Gate driving for the low side FET is achieved due to the low on-resistance (2 ohm when LG is high, 0.5 ohm when LG is low)

of the driver.

・VDD(12pin)

This is the power supply pin to drive the LOW side FET. It is recommended that a 1uF bypass capacitor be established to

compensate for rush current during the FET ON/OFF transition.

・SW(13pin)

This is the source pin for the high side FET. The maximum absolute ratings are 30V (from GND). SW voltage swings

between VIN and GND.

・HG(14pin)

This is the voltage supply to drive the Gate of the high side FET. This voltage swings between BOOT and SW. High-speed

Gate driving for the high side FET is achieved due to the low on-resistance (3 ohm when HG is high, 2 ohm when HG is low)

of the driver.

・BOOT(15pin)

This is the voltage supply to drive the high side FET. The maximum absolute ratings are 35V (from GND) and 7V (from SW).

BOOT voltage swings between VIN+Vcc and Vcc during active operation.

・SS(16pin)

This is the adjustment pin to set the soft start time. SS voltage is low during standby status. When EN is ON, the soft start

time can be determined by the SS charge current and capacitor between SS-GND. Until SS reaches REF voltage, the

output voltage is equivalent to SS voltage.

FS(17pin)

・

This is the pin to adjust the switching frequency based on the resistor value. The frequency range is f=200KHz - 600KHz.

・VOUT(18pin)

This is the output voltage sense pin. It is also possible to adjust the output voltage using external resistor divider based on

the equation, REF≒VOUT.

・VREG(19pin)

This is the reference voltage output pin. The voltage is 2.5V, with 100uA current ability. It is recommended that a 1uF

capacitor (X5R or X7R) be established between VREG and GND. When REF is not adjusted from the external voltage

supply, the REF voltage can be adjusted using the external resistor divider of VREF.

・REF(20pin)

This is the output voltage adjustment pin. It is very convenient for synchronizing external voltage supply. The IC controls the

output voltage (REF≒VOUT).

8/20

●Explanation of Operation

A

A

3

The BD9533EKN is a synchronous buck regulator controller incorporating ROHM’s proprietary H

system. When V

OUT drops due to a rapid load change, the system quickly restores VOUT by extending the TON time interval.

RegTM CONTROLLA control

Thus, it serves to improve the regulator’s transient response. Activating the Light Load Mode will also exercise Simple Light

Load Mode (SLLM) control when the load is light, to further increase efficiency.

3

RegTM control

H

(Normal operation)

VOUT

REF

HG

LG

When V

detected, activating the H

OUT falls to a threshold voltage (REF), the drop is

REF

T

ON=

×

V

IN

3

RegTM CONTROLLA system.

1

[sec]・・・(1)

f

HG output is determined with the formula above.

LG outputs until the status of VOUT is lower than REF

after the status of HG is off.

OUT drops due to a rapid load change)

(V

VOUT

REF

Io

ON+α

T

When VOUT drops due to a rapid load change, and

the voltage remains below REF after the

programmed T

system quickly restores V

ON time interval has elapsed, the

OUT by extending the TON

time, improving the transient response.

HG

LG

(SLLM )

VOUT

REF

HG

In SLLM (SLLM=0V), SLLM function is operated when

LG pin is OFF and the coil current is lower than 0

(the current goes from VOUT to SW). And it stops to

output next HG.

When V

OUT goes lower than REF voltage again, the

status of HG is ON.

LG

0

9/20

●Timing Chart

T

w

• Soft Start Function

EN

TSS

SS

OU

V

Soft start is exercised with the EN pin set high. Current

control takes effect at startup, enabling a moderate

output voltage “ramping start.” Soft start timing and

incoming current are calculated with formulas (2) and

(3) below.

Soft start time

Tss=

REF×Css

[sec]

・・・(2)

2μA(typ)

IIN

Incoming current

OUT

Co×V

IIN=

Ts s

[A]

・・・(3)

(Css: Soft start capacitor; Co: Output capacitor)

・Timer Latch Type Short Circuit Protection

VOUT

SCP

REF×0.7

TSCP

Short protection kicks in when output falls to or belo

REF X 0.7. When the programmed time period elapses,

output is latched OFF to prevent destruction of the IC.

Output voltage can be restored either by reconnecting

the EN pin or disabling UVLO. Short circuit protection

time is programmed using formula (4) below.

EN/UVLO

Short protection time setting

Tscp=

1.25(V)×C

SCP

2μA(typ)

[sec]

・・・(4)

・Over Voltage Protection

VOUT

REF×1.2

HG

LG

Switching

10/20

●External Component Selection

r

[A]

p

[H]

(

)

[A]

1. Inductor (L) selection

VIN

ΔIL

IL

V

OUT

L

Co

The inductor value is a major influence on the output ripple

current. As formula (5) below indicates, the greater the inductor o

the switching frequency, the lower the ripple current.

(V

ΔIL=

IN-VOUT)×VOUT

ΔI

L×VIN×f

・・・(5)

The proper output ripple current setting is about 30% of maximum

out

ut current.

ΔI

L=0.3×IOUTmax. [A]・・・(6)

(V

IN-VOUT)×VOUT

L=

(ΔI

ΔI

L×VIN×f

L: output ripple current; f: switch frequency)

・・・(7)

Output ripple current

※Passing a current larger than the inductor’s rated current will cause magnetic saturation in the inductor and decrease

system efficiency. In selecting the inductor, be sure to allow enough margin to assure that peak current does not exceed the

inductor rated current value.

※To minimize possible inductor damage and maximize efficiency, choose a inductor with a low (DCR, ACR) resistance.

2.Output Capacitor (C

VIN

L

Output capacitor

O) Selection

OUT

V

ESR

ESL

Co

When determining the proper output capacitor, be sure to factor in the equivalent

series resistance required to smooth out ripple volume and maintain a stable

output voltage range.

Output ripple voltage is determined as in formula (8) below.

ΔV

OUT=ΔIL×ESR+ESL×ΔIL/TON [V]・・・(8)

(ΔI

L: Output ripple current; ESR: CO equivalent series resistance,

ESR:equivalent series inductance)

※ In selecting a capacitor, make sure the capacitor rating allows sufficient

margin relative to output voltage. Note that a lower ESR can minimize output

ripple voltage.

Please give due consideration to the conditions in formula (9) below for output capacity, bearing in mind that output rise time

must be established within the soft start time frame.

Co≦

Ts s×(Limit-I

V

OUT

OUT)

・・・(9)

Tss: Soft start time

Limit: Over current detection

Note: Improper capacitor may cause startup malfunctions.

3. Input Capacitor (Cin) Selection

VIN

Cin

The input capacitor selected must have low enough ESR resistance to fully

support large ripple output, in order to prevent extreme over current. The formula

for ripple current IRMS is given in (10) below.

OUT

L

Co

V

I

RMS=IOUT×

Where VCC=2×VOUT,IRMS=

√

V

OUT

VIN-VOUT

VIN

・・・(10)

IOUT

2

Input Capacitor

A low ESR capacitor is recommended to reduce ESR loss and maximize efficiency.

11/ 20

4. MOSFET Selection

5. Setting Detection Resistance

VIN

main switch

L

VIN

L

IL

Current limit

VIN

IL

L

r

Current limit

Co

synchronous switch

R

RL

C

Co

V

Co

OUT

V

V

OUT

OUT

Loss on the main MOSFET

Pmain=P

V

= ・・・(11)

VIN

RON+PGATE+PTRAN

OUT

×RON×IOUT2+Ciss×f×VDD+

2

IN

×Crss×IOUT×f

V

I

DRIVE

(Ron: On-resistance of FET; Ciss: FET gate capacity;

f: Switching frequency Crss: FET inverse transfer function;

I

: Gate peak current)

DRIVE

Loss on the synchronous MOSFET

Psyn=PRON+PGATE

VIN-VOUT

=

VIN

×RON×IOUT2+Ciss×f×VDD

・・・(12)

The over current protection function detects the output ripple

current peak value. This parameter (setting value) is

determined as in formula (13) below.

V

ILMIT=

ILIM×0.1

[A]・・・(13)

R

(VILIM: ILIM voltage; R: Detection resistance)

When the over current protection is detected by DCR of coil L, this

parameter (setting value) is determined as in formula (14) below.

(Application circuit:P20)

ILMIT=VILIM×0.1×

L

(RL=

r×C

r×C

[A]・・・(14)

L

)

(VILIM:ILIM voltage RL: the DCR value of coil)

12/20

V

y

y

6.Setting frequency

3000

2500

2000

1500

TON [nsec]

1000

500

0

VIN=5V

7V

12V

16V

19V

0 50 100 150 200

RFS [kΩ]

REF=1.8

Calculated frequency

using TON above

Frequency [kHz]

1200

1000

800

600

400

200

VIN=5V

7V

12V

16V

19V

On Time (TON) at steady state is determined b

resistance value connected to FS pin as shown in the

figure. The frequency can be calculated with TON,

input voltage VIN, the reference voltage REF as

follows.

F=

・・・(15)

However, the actual frequency becomes lower than

the formula due to expanded TON time caused by the

rise/fall time of the MOSFET (This rise/fall time is

affected by the switching speed). TON is also

influenced by Dead Time under light load in

continuous mode. In this case the frequency

becomes lower than setting frequency.

The setting frequency noted above is under heav

load (when the inductor current does not go back to

VIN through the body diodes of the external

MOSFET’s).

0

0 50 100 150 200

Resistance [kΩ]

7. Setting standard voltage (REF)

VIN

REF

Outside

voltage

H3RegTM

CONTROLLA

RQ

S

It is available to synchronize setting the reference

voltage (REF) with outside supply voltage [V] by using

outside power supply voltage.

VOUT

VREG

VIN

R1

R2

REF

H3RegTM

CONTROLLA

RQ

S

It is available to set the reference voltage (REF) by the

resistance division value from VREG in case it is not

set REF from an external power supply.

REF= ×VREG [V]・・・(16)

VOUT

13/20

REF

IN×TON

V

R1+R2

R2

8. Setting output voltage

This IC is operated that output voltage is REF≒VOUT.

And it is operated that output voltage is feed back to FB pin in case the output voltage is 0.7V to 2.0V.

REF

REF

R1

R2

VOUT

It is operated that the resistance division value of the output voltage is feed back to V

more than 2.0V.

VOUT

VIN

H3RegTM

CONTROLLA

In case the output voltage range is 0.7V to 2.0V.

output voltage≒ ×REF [V]・・・(17)

VIN

H3RegTM

CONTROLLA

In case the output voltage is more than 2.0V.

RQ

S

R1+R2

R2

RQ

S

SLLM

Driver

SLLM

SLLM

SLLM

Circuit

OUT pin in case the output voltage is

Driver

Circuit

VIN

VIN

Output

voltage

Output

voltage

14/20

●I/O Equivalent Circuit

3pin (ILIM) 4pin (EN) 5pin (VIN)

VCC

6pin (SLLM) 7pin (SCP) 8pin (Is-)

VCC

VCC VCC

9pin (Is+) 11pin (LG) 13pin (SW)

VCC

VCC

VDD

14pin(HG) 15pin (BOOT) 16pin (SS)

BOOT BOOT

HG SW

17pin (FS) 18pin (VOUT) 19pin (VREG)

VCC VCC

20pin (REF)

VCC

15/20

VCC

VCC

BOOT

HG

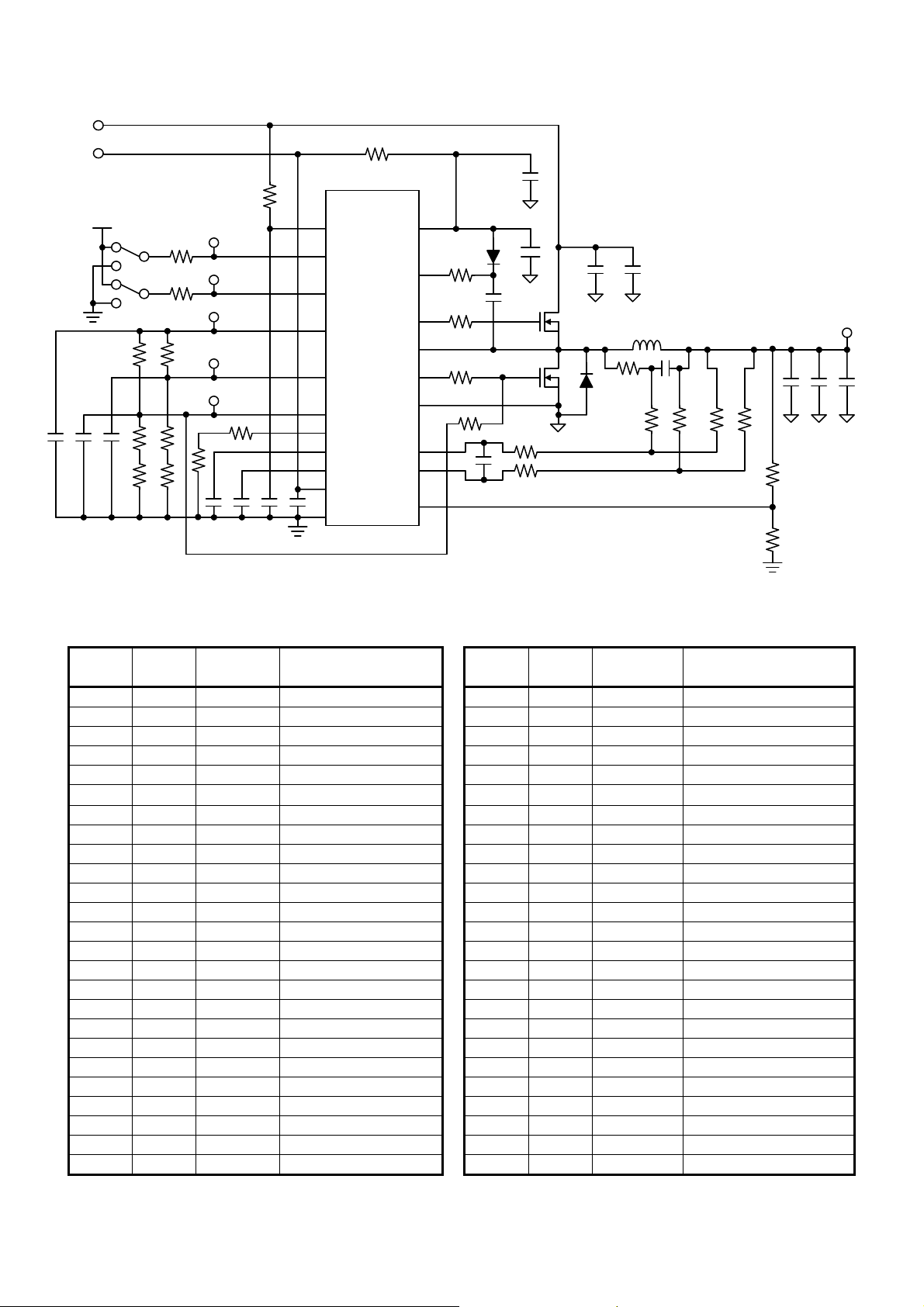

●Evaluation Board Circuit (Frequency=300kHz application circuit in Continuous mode/SLLM)

4.5V~25V

VIN

VCC

C13

VCC

C14

5V

R16

EN

R18

SLLM

R19

VREG

2.5V

R14

C3

R15

R17

ILIM

R12

R13

R20

REF

R9

0.5V

1.8V

R1

C12

C11

5

4

6

19

3

20

17

7

16

2

C1

C2

1

R2

BD9533EKN

VIN

EN

SLLM

VREG

ILIM

REF

FS

SCP

SS

VCC

GND

VDD

BOOT

HG

SW

LG

PGND

Is+

VOUT

C6

12

R11

15

R10

14

13

R8

11

10

R4

9

8

Is-

18

PGND

D1

C15

C9

PGND

C8

Q1

Q2

R3

C16

R5

PGND

PGND PGND

R6

D2

GND

L1

C10

C4

PGNDPGND

R25 R26

VOUT

C5

C17

R7

R23

R22

R21

1.8V/10A

R24

PGND

Part

No

Value Company Part name

Part

No

Value Company Part name

U1 ROHM BD9533EKN R4

Q1 ROHM RSS100N03 R5 0Ω ROHM MCR03

Q2 ROHM RSS100N03 R6

D1 ROHM RB521S-30 R7 5mΩ ROHM PMR100

D2 ROHM RB051L-40 R8 0Ω ROHM MCR03

C1 1uF KYOCERA CM105B105K06A R9 0Ω ROHM MCR03

C2 10nF MURATA GRM39X7R103K50 R10 0Ω ROHM MCR03

C3 100pF MURATA GRM39C0G101J50 R11 0Ω ROHM MCR03

C4 R12 200kΩ ROHM MCR03

C5 R13 51kΩ ROHM MCR03

C6 10uF KYOCERA CM21B106K06 R14 68kΩ ROHM MCR03

C7 R15 180kΩ ROHM MCR03

C8 0.1uF KYOCERA CM05B104K25A R16 1kΩ ROHM MCR03

C9 10uF KYOCERA CM316B106M16A R17 0Ω ROHM MCR03

C10 10uF KYOCERA CM316B106M16A R18 10kΩ ROHM MCR03

C11 1000pF MURATA GRM39X7R102K50 R19 10kΩ ROHM MCR03

C12 1500pF MURATA GRM39X7R152K50 R20 0Ω ROHM MCR03

C13 1uF KYOCERA CM105B105K06A R21

C14 R22

C15 10uF KYOCERA CM21B106M06A R23 0Ω ROHM MCR03

C16 R24 0Ω ROHM MCR03

C17 470uF SANYO 2R5TPE470ML R25 0Ω ROHM MCR03

R1 68KΩ ROHM MCR03 R26

R2 0Ω ROHM MCR03 L1 1.8uH SUMIDA CDEP104-1R8ML

R3 0Ω ROHM MCR03

16/20

●Evaluation Board Circuit (Frequency=300kHz application circuit for detecting DCR current in Continuous mode/SLLM)

4.5V~25V

VIN

VCC

5V

R16

VCC

R14

C3

C14

C13

R15

R17

R18

R19

EN

SLLM

VREG

ILIM

R12

REF

R1

R13

R9

R20

C11

C12

C2

GND

5

4

6

19

3

20

17

7

16

2

C1

1

R2

BD9533EKN

VIN

EN

SLLM

VREG

ILIM

REF

FS

SCP

SS

VCC

GND

VDD

BOOT

HG

SW

PGND

VOUT

LG

Is+

C6

12

R11

15

R10

14

13

R8

11

10

R4

9

8

Is-

18

PGND

D1

C15

C9

PGND

C8

Q1

Q2

R3

C16

R5

PGND PGND

D2

PGND

C10

L1

R6

C7

R21

R23

R22

R24

PGND

R25 R26

●Evaluation Board Parts List

VOUT

C5

C4

PGNDPGND

C17

Part

No

Value Company Part name

Part

No

Value Company Part name

U1 ROHM BD9533EKN R4

Q1 ROHM RSS100N03 R5 0Ω ROHM MCR03

Q2 ROHM RSS100N03 R6 1kΩ ROHM MCR03

D1 ROHM RB521S-30 R7

D2 ROHM RB051L-40 R8 0Ω ROHM MCR03

C1 1uF KYOCERA CM105B105K06A R9 0Ω ROHM MCR03

C2 10nF MURATA GRM39X7R103K50 R10 0Ω ROHM MCR03

C3 100pF MURATA GRM39C0G101J50 R11 0Ω ROHM MCR03

C4 R12 51kΩ ROHM MCR03

C5 R13 200kΩ ROHM MCR03

C6 10uF KYOCERA CM21B106K06 R14 68kΩ ROHM MCR03

C7 0.1uF KYOCERA CM05B104K25A R15 180kΩ ROHM MCR03

C8 0.1uF KYOCERA CM05B104K25A R16 1kΩ ROHM MCR03

C9 10uF KYOCERA CM316B106M16A R17 0Ω ROHM MCR03

C10 10uF KYOCERA CM316B106M16A R18 10kΩ ROHM MCR03

C11 1000pF MURATA GRM39X7R102K50 R19 10kΩ ROHM MCR03

C12 1500pF MURATA GRM39X7R152K50 R20 0Ω ROHM MCR03

C13 1uF KYOCERA CM105B105K06A R21 0Ω ROHM MCR03

C14 R22 0Ω ROHM MCR03

C15 10uF KYOCERA CM21B106M06A R23

C16 R24

C17 330uF SANYO 6TPB330M R25 0Ω ROHM MCR03

R1 68KΩ ROHM MCR03 R26

R2 0Ω ROHM MCR03 L1 3.3uH NEC/TOKIN MPLC0730L3R3

R3 0Ω ROHM MCR03

17/20

●Operation Notes

1. Absolute maximum ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can

break down the devices, thus making impossible to identify breaking mode, such as a short circuit or an open circuit. If any

over rated values will expect to exceed the absolute maximum ratings, consider adding circuit protection devices, such as

fuses.

2. Connecting the power supply connector backward

Connecting of the power supply in reverse polarity can damage IC. Take precautions when connecting the power supply

lines. An external direction diode can be added.

3. Power supply lines

Design PCB layout pattern to provide low impedance GND and supply lines. To obtain a low noise ground and supply line,

separate the ground section and supply lines of the digital and analog blocks. Furthermore, for all power supply terminals to

ICs, connect a capacitor between the power supply and the GND terminal. When applying electrolytic capacitors in the

circuit, not that capacitance characteristic values are reduced at low temperatures.

4. GND voltage

The potential of GND pin must be minimum potential in all operating conditions.

5. Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

6. Inter-pin shorts and mounting errors

Use caution when positioning the IC for mounting on printed circuit boards. The IC may be damaged if there is any

connection error or if pins are shorted together.

7. Actions in strong electromagnetic field

Use caution when using the IC in the presence of a strong electromagnetic field as doing so may cause the IC to

malfunction.

8. ASO

When using the IC, set the output transistor so that it does not exceed absolute maximum ratings or ASO.

9. Thermal shutdown circuit

The IC incorporates a built-in thermal shutdown circuit (TSD circuit). The thermal shutdown circuit (TSD circuit) is designed

only to shut the IC off to prevent thermal runaway. It is not designed to protect the IC or guarantee its operation. Do not

continue to use the IC after operating this circuit or use the IC in an environment where the operation of this circuit is

assumed.

TSD on temperature [°C] (typ.) Hysteresis temperature [°C] (typ.)

BD9533EKN 175 15

10. Testing on application boards

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress.

Always discharge capacitors after each process or step. Always turn the IC's power supply off before connecting it to or

removing it from a jig or fixture during the inspection process. Ground the IC during assembly steps as an antistatic

measure. Use similar precaution when transporting or storing the IC.

18/20

P

iti

P

iti

11. Regarding input pin of the IC

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated.

P-N junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode

or transistor. For example, the relation between each potential is as follows:

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode.

When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes can occur inevitable in the structure of the IC. The operation of parasitic diodes can result in mutual

interference among circuits, operational faults, or physical damage. Accordingly, methods by which parasitic diodes

operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin, should not be used.

Pin A

Parasitic element

N

+

P

P

GND

Resistor Transistor (NPN)

B

C

E

N

P

P+

P substrate

GND

+

P

N N

P substrate

Pin A

aras

element

Pin B

N

+

c

P

Parasitic element

N

GND

Pin B

B C

E

aras

element

GND

Other adjacent elements

Fig. 37 Example of IC structure

12. Ground Wiring Pattern

When using both small signal and large current GND patterns, it is recommended to isolate the two ground patterns,

placing a single ground point at the ground potential of application so that the pattern wiring resistance and voltage

variations caused by large currents do not cause variations in the small signal ground voltage. Be careful not to change the

GND wiring pattern of any external components, either.

c

19/20

●Type Designations (Selections) for Ordering

B D 9 5 3 3 K

Product name

・BD9533

HQFN20V

<Dimension>

(1.1)

0.1

0.1

±

±

4.0

4.2

0.22±0.05

0.05

±

0.22

4.2±0.1

4.0±0.1

15 11

16

10

20

6

5

1

0.05

0.03

0.02

+

−

0.02

0.95MAX

0.05

(0.22)

3−(0.35)

0.5

(2.1)

(0.5)

(Unit:mm)

0.6

(2.1)

+

0.1

−

0.3

Package type

・EKN : HQFN20V

<Tape and Reel information>

Tape

Quantity

Direction

Embossed carrier tape(with dry pack)

2500pcs

E2

(The direction is the 1pin of product is at the upper left when you hold

reel on the left hand and you pull out the tape on the right hand)

1234

1234

Reel

※When you order , please order in times the amount of package quantity.

N

―

E 2 E

Taping type name

E2= Embossed carrier tape

1234

1pin

1234

1234

Direction of feed

1234

20/20

Catalog No.08T441A '08.9 ROHM ©

Appendix

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM

CO.,LTD.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you

wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM

upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the

standard usage and operations of the Products. The peripheral conditions must be taken into account

when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should

you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no re-

sponsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples

of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to

use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no re-

sponsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment

or devices (such as audio visual equipment, office-automation equipment, communication devices, elec-

tronic appliances and amusement devices).

The Products are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or

malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the

possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as

derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your

use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system

which requires an extremely high level of reliability the failure or malfunction of which may result in a direct

threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment,

aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear

no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intend-

ed to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under

the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Notes

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact your nearest sales office.

ROHM Customer Support System

www.rohm.com

Copyright © 2009 ROHM CO.,LTD.

21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan

THE AMERICAS / EUROPE / ASIA / JAPAN

Contact us : webmaster@ rohm.co. jp

TEL : +81-75-311-2121

FAX : +81-75-315-0172

Appendix-Rev4.0

Loading...

Loading...