System Lens Driver Series for Digital Still Cameras / Single-lens Reflex Cameras

6ch System Lens Drivers

for Digital Still Cameras /

Single-lens Reflex Cameras

BD6373GW,BD6873KN,BD6753KV

No.09014EAT02

●Description

The BD6373GW motor driver provides 6 Full-ON Drive H-bridge channels. The BD6873KN motor driver provides 5 Full-ON

Drive H-bridge channels and 1 Linear Constant-Current Drive H-bridge channel, while the BD6753KV provides 4 Full-ON

Drive channels and 2 PWM Constant-Current Drive H-bridge channels.

Stepping motors can be used for auto focus, and either zoom or iris. A new drive type (lens barrier) is also available. Three types of drivers

for shutter are offered: a simple Full-ON type, a high-precision linear constant current type, or a high-efficiency PWM constant current type,

enabling selection of the ideal solution based on the application.

●Features

1) Subminiature 31PIN Wafer-level CSP (Chip Size Package): 2.6 x 2.6 x 0.85mm3 (BD6373GW)

2) DMOS output allowing a range power supply: 4.5V to 10.5V (BD6753KV; VM1), 2.0V to 10.5V (BD6753KV; VM2 to VM4)

3) Low ON-Resistance Power MOS output:

Full-ON Drive block with 1.2Ω Typ. (BD6373GW)

Full-ON Drive block with 1.2Ω Typ. and Linear Constant-Current Drive block with 1.0Ω Typ. (BD6873KN)

Full-ON Drive block with 1.2Ω Typ. and PWM Constant-Current Drive block with 1.2Ω Typ. (BD6753KV)

4) Serial interface 3-line bus control input (BD6753KV)

5) Built-in two-step output current setting switch for the Linear Constant-Current Drive block (BD6873KN)

6) Drive mode switching function

7) 1.2V±3% high-precision reference voltage output (BD6873KN)

8) Constant-Current Drive block features phase compensation capacitor-free design (BD6873KN)

9) Built-in ±3% high-precision Linear Constant-Current Driver (BD6873KN)

10) Built-in peak current control PWM Constant-Current Driver (BD6753KV)

11) Built-in charge pump circuit for the DMOS gate voltage drive (BD6753KV)

12) UVLO (Under Voltage Lockout Protection) function

13) Built-in TSD (Thermal Shut Down) circuit

14) Standby current consumption: 0μA Typ.

●Absolute Maximum Ratings

Parameter Symbol

BD6373GW BD6873KN BD6753KV

Limit

Unit

Power supply voltage VCC -0.5 to +6.5 0 to +7.0 -0.5 to +7.0 V

Motor power supply voltage VM -0.5 to +6.5 0 to +7.0 -0.5 to +12.5 V

Charge pump voltage VG - - 18.0 V

Control input voltage VIN -0.5 to VCC+0.5 0 to VCC -0.5 to VCC+0.5 V

Power dissipation Pd 940

1

※

950

2

※

112 5

3

※

mW

Operating temperature range Topr -25 to +85 -25 to +85 -25 to +75 °C

Junction temperature Tjmax +150 +150 +150 °C

Storage temperature range Tstg -55 to +150 -55 to +150 -55 to +150 °C

H-bridge output current Iout -800 to +800

※1 Reduced by 7.52mW/°C over 25°C, when mounted on a glass epoxy board (50mm x 58mm x 1.75mm; 8layers).

※2 Reduced by 7.6mW/°C over 25°C, when mounted on a glass epoxy board (70mm x 70mm x 1.6mm).

※3 Reduced by 9.0mW/°C over 25°C, when mounted on a glass epoxy board (70mm x 70mm x 1.6mm).

※4 Must not exceed Pd, ASO, or Tjmax of 150°C.

4

※

-800 to +800

4

※

-800 to +800

4

※

mA/ch

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

1/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

Technical Note

●Operating Conditions (Ta=-25 to +85°C(BD6373GW, BD6873KN), -25 to +75°C(BD6753KV))

Parameter Symbol

BD6373GW BD6873KN BD6753KV

Limit

Power supply voltage VCC 2.5 to 5.5 2.5 to 5.5 2.7 to 5.5 V

Motor power supply voltage VM 2.5 to 5.5 2.5 to 5.5

4.5 to 10.5 (VM1)

2.0 to 10.5 (VM2 to VM4)

Control input voltage VIN 0 to VCC 0 to VCC 0 to VCC V

Output current control input

voltage range

PWM signal input frequency FPWM - - 0 to 0.1 MHz

H-bridge output current Iout -500 to +500

※5 Must not exceed Pd or ASO.

VLIM - 0 to VCC 0 to 0.5 V

5

※

-500 to +500

5

※

-500 to +500

5

※

mA/ch

●Electrical Characteristics

1) BD6373GW Electrical Characteristics (Unless otherwise specified, Ta=25°C, VCC=3.0V, VM=5.0V)

Parameter Symbol

Min. Typ. Max.

Limit

Unit Conditions

Overall

Circuit current ICC - 1.0 1.9 mA no signal and no load

Control input (IN=ENABLExx, INPUTx, and BRAKEx)

High level input voltage VINH 2.0 - VCC V

Low level input voltage VINL 0 - 0.7 V

High level input current IINH 15 30 60 μA VINH=3V

Low level input current IINL -1 0 - μA VINL=0V

UVLO

UVLO voltage VUVLO 1.6 - 2.4 V

Full-ON Drive block (ch1 to ch6)

Output ON-Resistance 1 RON1 - 1.2 1.5 Ω

Output ON-Resistance 2 RON2 - 1.5 2.0 Ω

Io=±400mA on high and low sides In total

(VM=5V)

Io=±400mA on high and low sides In total

(VM=3V)

Turn on time ton - 0.55 1.95 μs RL=20Ω

Turn off time toff - 0.08 0.5 μs RL=20Ω

Rise time tr 0.1 0.15 1.0 μs RL=20Ω

Fall time tf - 0.03 0.2 μs RL=20Ω

2) BD6873KN Electrical Characteristics (Unless otherwise specified, Ta=25°C, VCC=3.0V, VM=5.0V)

Parameter Symbol

Min. Typ. Max.

Limit

Unit Conditions

Overall

Circuit current

during standby operation

ICCST - 0 10 μA PS=0V

Circuit current ICC - 1.2 2.3 mA PS=VCC with no signal and no load

Power-saving (PS)

High level input voltage VPSH 2.0 - - V

Low level input voltage VPSL - - 0.7 V

High level input current IPSH 15 30 60 μA VPS=3V

Low level input current IPSL -1 0 - μA VPS=0V

Control input (IN=IN1A to IN5B, SEL1 to 3, BRK1, EN1, IN6, and VLIMS)

High level input voltage VINH 2.0 - - V

Low level input voltage VINL - - 0.7 V

High level input current IINH 15 30 60 μA VINH=3V

Low level input current IINL -1 0 - μA VINL=0V

Pull-down resistance RIN 50 100 200 kΩ

UVLO

UVLO voltage VUVLO 1.6 - 2.4 V

Full-ON Drive block (ch1 to ch5)

Output ON-Resistance RON - 1.2 1.5 Ω Io=±400mA on high and low sides In total

Linear Constant-Current Drive block (ch6)

Output ON-Resistance RON - 1.0 1.25 Ω Io=±400mA on high and low sides in total

VREF output voltage VREF 1.16 1.20 1.24 V Iout=0~1mA

Output limit voltage VOL 194 200 206 mV RNF=0.5Ω, VLIM=0.2V

Unit

V

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

2/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

3) BD6753KV Electrical Characteristics (Unless otherwise specified, Ta=25°C, VCC=3.3V, VM=10.5V)

Parameter Symbol

Overall

Circuit current

during standby operation

Circuit current ICC - 2.2 3.0 mA PS=VCC with no signal; CRx open

Power-saving (PS)

High-level input voltage VPSH 2.0 - - V

Low-level input voltage VPSL - - 0.7 V

High-level input current IPSH 25 50 100 μA VPSH=3.3V

Low-level input current IPSL -1 0 - μA VPSL=0V

Control input (IN=STROBE, CLK, DATA, and PWM1 to 6)

High-level input voltage VINH 2.0 - - V

Low-level input voltage VINL - - 0.7 V

High-level input current IINH 16.5 33 66 μA VINH=3.3V

Low-level input current IINL -1 0 - μA VINL=0V

Pull-down resistance RIN 50 100 200 kΩ

Charge pump

Charge pump voltage VCP 16 16.5 - V

UVLO

UVLO voltage VUVLO 1.6 - 2.5 V

Full-ON Drive block (ch1 to ch4)

Output ON-Resistance RON - 1.2 1.5 Ω

PWM Linear Constant-Current Drive block (ch5 and ch6)

Output ON-Resistance RON - 1.2 1.5 Ω

VLIM pin input current IVLIM -1 -0.2 - μA VLIMx=0V, SENSEx=0.5V

SENSE pin input current ISENSE -1 -0.2 - μA VLIMx=0.5V, SENSEx=0V

Output limit voltage VOL 485 500 515 mV VLIMx=500mV

CR clamp voltage VCR 0.8 0.9 1.0 V R=10kΩ

CR switching high voltage VCRH 0.72 0.80 0.88 V

CR switching low voltage VCRL 0.36 0.40 0.44 V

Minimum ON time TMINON 0.1 0.5 1.0 μs C=470pF, R=10kΩ

Constant voltage power supply

VREF output voltage VREF 0.81 0.90 0.99 V Iout=0~1mA

ICCST - 0 10 μA PS=0V

Min. Typ. Max.

Limit

Unit Conditions

Io=±400mA, VG=16.5V

on high and low sides in total

Io=±400mA, VG=16.5V

on high and low sides in total

Technical Note

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

3/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

]

]

Technical Note

●Electrical Characteristic Diagrams

1250

1000

940mW

750

489mW

500

250

Power dissipation : Pd [mW]

0

0 25 50 75 100 125 150

Ambient t emperatur e : Ta [° C]

85°C

Fig.1 Power Dissipation Reduction

BD6373GW

1250

950mW

1000

750

494mW

500

250

Power dissipation : Pd [mW]

0

0 25 50 75 100 125 150

Ambient t emperatur e : Ta [° C]

Fig.2 Power Dissipation Reduction

85°C

BD6873KN

1250

112 5mW

1000

675mW

750

500

250

Power dissipation : Pd [mW]

0

0 25 50 75 100 125 150

Ambient t emperatur e : Ta [° C]

BD6753KV

75°C

Fig.3 Power Dissipation Reduction

Op. range

BD6373GW

Top 8 5 ° C

Mid 25°C

Low -25°C

5.0

4.0

3.0

2.0

Circuit current : ICC [mA

1.0

(2.5V to 5.5V)

5.0

4.0

3.0

2.0

Circuit current : ICC [mA

1.0

(2.5V to 5.5V)

0.0

0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0

Supply voltag e : VCC [V]

Fig.4 Circuit current

0.0

0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0

Supply voltag e : VCC [V]

Fig.5 Circuit current

Op. range

BD6373GW

Top 8 5 ° C

Mid 25°C

Low -25°C

5.0

4.0

3.0

2.0

1.0

Output ON resistance : RON [Ω]

0.0

0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0

(2.5V to 5.5V)

Supply voltage : VM [V]

Fig.8 Output ON-Resistance

-

5.0

4.0

3.0

2.0

1.0

Output ON resistance : RON [Ω]

0.0

0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0

Fig.7 Output ON-Resistance

(2.5V to 5.5V)

Supply voltag e : VM [V]

-

5.0

4.0

BD6753KV

Top 7 5 ° C

Mid 25°C

Low -25°C

250

200

3.0

2.0

1.0

Output ON resistance : RON [Ω]

0.0

13.0 14.0 15.0 16.0 17.0 18.0

Supply voltag e : VG [V]

Fig.10 Output ON-Resistance

=

150

100

50

RNF voltage : VRNF [mV]

0

0 50 100 150 200 250

VLIM voltage : VLIM [mV]

Fig.11 Output limit voltage

Op. range

Op. range

=

BD6873KN

Top 8 5 ° C

Mid 25°C

Low -25°C

BD6873KN

Top 8 5 ° C

Mid 25°C

Low -25°C

BD6873KN

Top 8 5 ° C

Mid 25°C

Low -25°C

Op. range

BD6753KV

Top 7 5 ° C

Mid 25°C

Low -25°C

5.0

4.0

3.0

2.0

1.0

Circuit current : ICC [mA]

0.0

0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0

(2.7V to 5.5V)

Supply voltag e : VCC [V]

Fig.6 Circuit current

Op. range

BD6873KN

Top 8 5 ° C

Mid 25°C

Low -25°C

5.0

4.0

3.0

2.0

1.0

Output ON resistance : RON [Ω]

0.0

0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0

(2.5V to 5.5V)

Supply voltag e : VM [V]

Fig.9 Output ON-Resistance

-

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

4/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

L

A

A3A

A

L

L

A

A

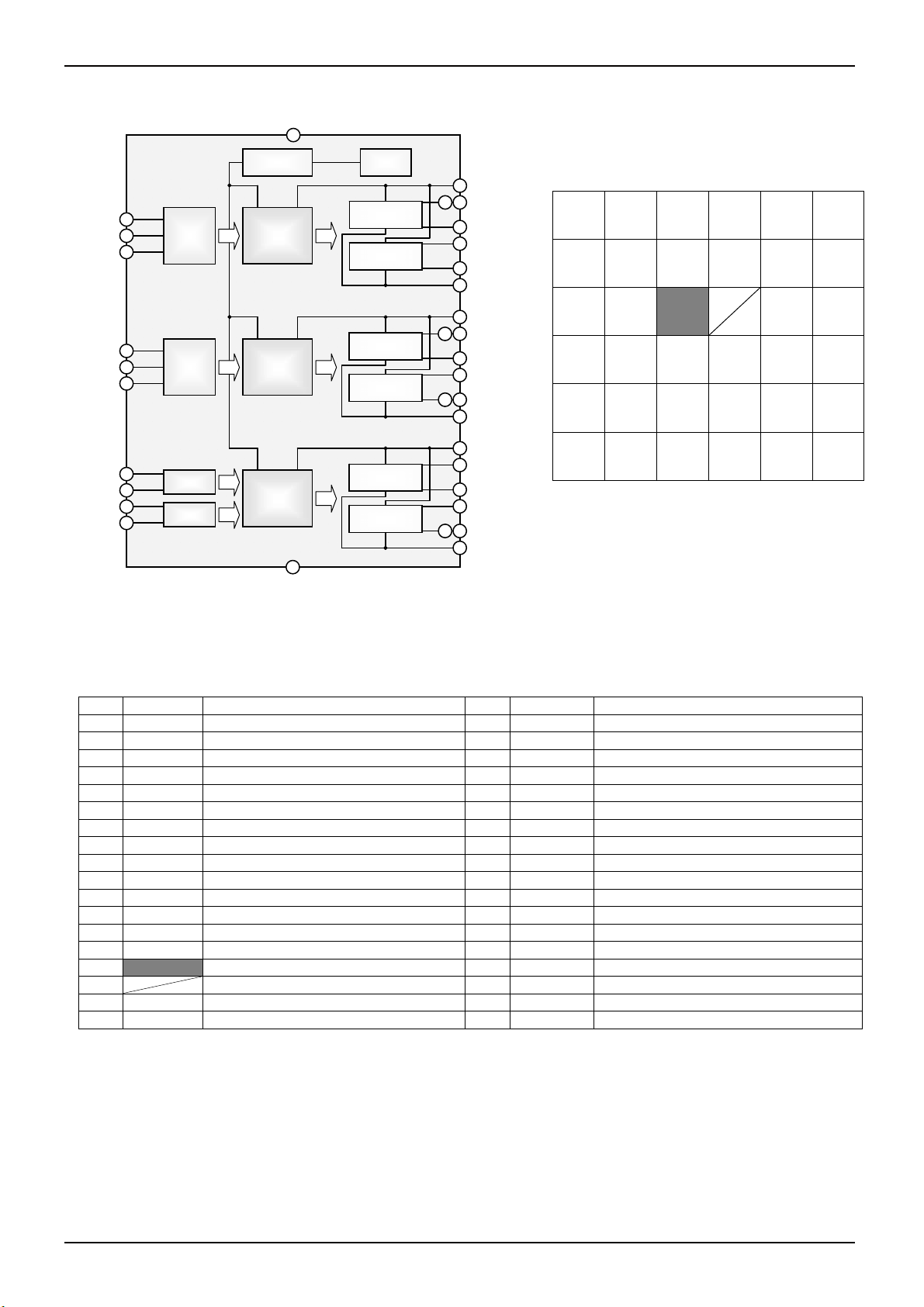

●Block Diagram, Pin Arrangement, and Pin Function

VCC

F3

Technical Note

ENABLE12

ENABLE34

INPUT1

INPUT2

INPUT3

INPUT4

INPUT5

BRAKE5

INPUT6

BRAKE6

TSD & UVLO

C2

D2

E3

D3

B3

B4

C5

D4

E4

D5

Logic12

Logic34

F4

GND

BandGap

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

F2

VM12

F1

E2

OUT1A

OUT1B

E1

D1

OUT2A

OUT2B

C1

PGND12

B1

VM34

2

B2

1

OUT3A

OUT3B

4

OUT4A

6

B5

OUT4B

5

PGND34

F5

VM56

OUT5A

C6

D6

OUT5B

E6

OUT6A

E5

F6

OUT6B

B6

PGND56

1 2 3 4 5 6

A OUT3A VM34 OUT3B OUT4A PGND34 OUT4B

B PGND12 OUT3A INPUT3 INPUT4 OUT4B PGND56

C OUT2B ENABLE12

D OUT2A INPUT1 ENABLE34 BRAKE5 BRAKE6 OUT5B

E OUT1B OUT1A INPUT2 INPUT6 OUT6B OUT6A

F OUT1A VM12 VCC GND VM56 OUT6B

INDEX

POST

INPUT5 OUT5A

OUT3A, OUT4B, OUT1A, and OUT6B, which are 2

function pins, are shorted on printed circuit boards.

Fig.12 BD6373GW Block Diagram

Fig.13 BD6373GW Pin Arrangement (Top View)

UCSP75M2 Package

BD6373GW Pin Function Table

No. Pin Name Function No. Pin Name Function

A1 OUT3A H-bridge output pin ch3 A D1 OUT2A H-bridge output pin ch2 A

A2 VM34 Motor power supply pin ch3 and ch4 D2 INPUT1 Control input pin ch1 INPUT

A3 OUT3B H-bridge output pin ch3 B D3 ENABLE34 Control input pin ch3 and ch4 ENABLE

A4 OUT4A H-bridge output pin ch4 A D4 BRAKE5 Control input pin ch5 BRAKE

A5 PGND34 Motor ground pin ch3 and ch4 D5 BRAKE6 Control input pin ch6 BRAKE

A6 OUT4B H-bridge output pin ch4 B D6 OUT5B H-bridge output pin ch5 B

B1 PGND12 Motor ground pin ch1 and ch2 E1 OUT1B H-bridge output pin ch1 B

B2 OUT3A H-bridge output pin ch3 A E2 OUT1A H-bridge output pin ch1 A

B3 INPUT3 Control input pin ch3 INPUT E3 INPUT2 Control input pin ch2 INPUT

B4 INPUT4 Control input pin ch4 INPUT E4 INPUT6 Control input pin ch6 INPUT

B5 OUT4B H-bridge output pin ch4 B E5 OUT6B H-bridge output pin ch6 B

B6 PGND56 Motor ground pin ch5 and ch6 E6 OUT6A H-bridge output pin ch6 A

C1 OUT2B H-bridge output pin ch2 B F1 OUT1A H-bridge output pin ch1 A

C2 ENABLE12 Control input pin ch1 and ch2 ENABLE F2 VM12 Motor power supply pin ch1 and ch2

C3 INDEX POST - F3 VCC Power supply pin

C4 - F4 GND Ground pin

C5 INPUT5 Control input pin ch5 F5 VM56 Motor power supply pin ch5 and ch6

C6 OUT5A H-bridge output pin ch5 A F6 OUT6B H-bridge output pin ch6 B

OUT3A, OUT4B, OUT1A, and OUT6B, which are 2 function pins, are shorted on printed circuit boards.

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

5/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

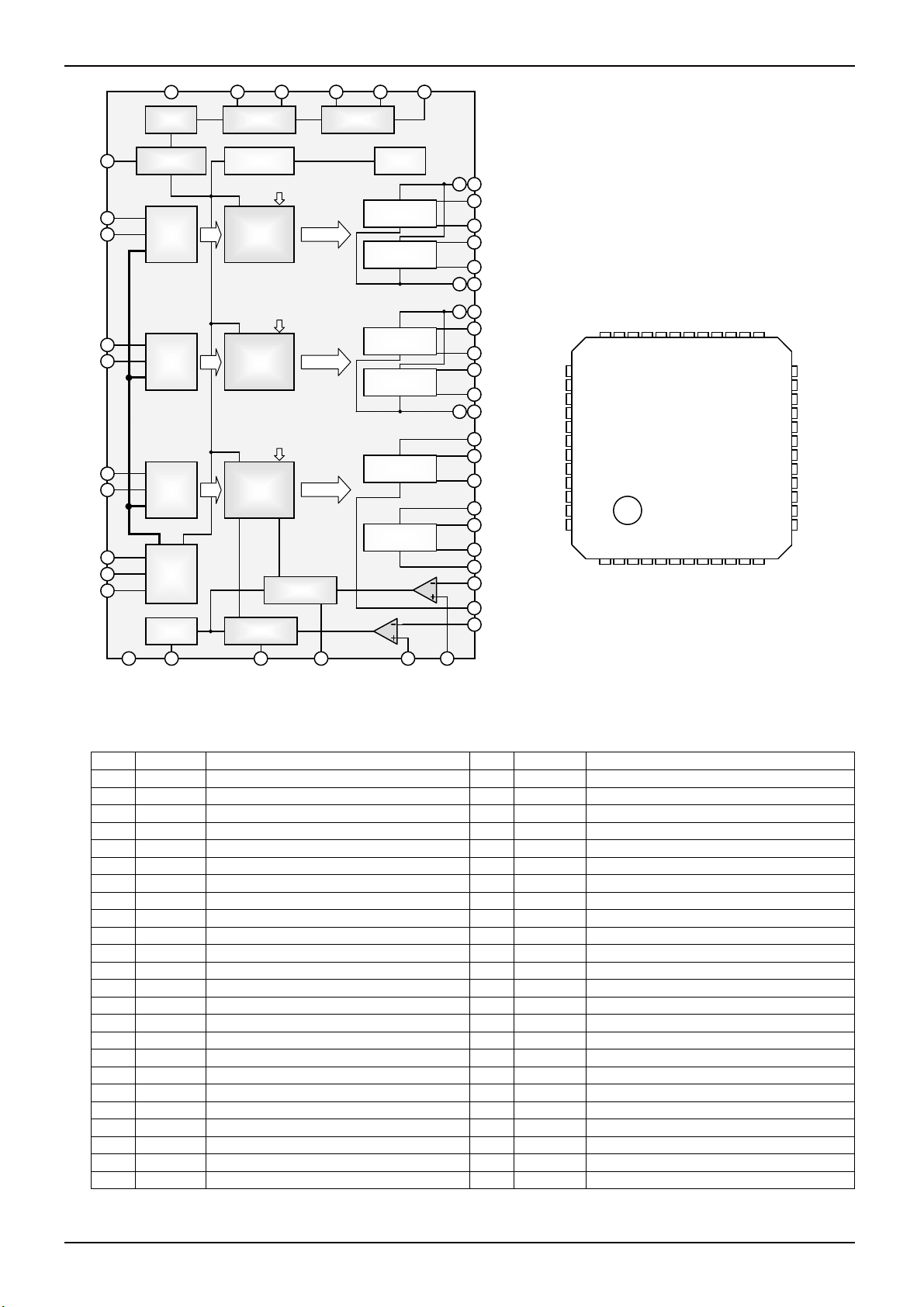

Technical Note

PS

38

Power Save

TSD & UVLO

IN1A

47

IN1B

48

IN2A

1

IN2B

2

SEL1

3

Logic12

Logic12

Level Shift

Pre Driver

IN3A

4

IN3B

5

IN4A

8

IN4B

9

SEL2

10

Logic34

Level Shift

Pre Driver

IN5A

11

IN5B

12

SEL3

13

BRK1

14

Logic5

Level Shift

Pre Driver

EN1

36

IN6

37

Logic6

Level Shift

Pre Driver

23 24 25 26

VREF VLIMS VLIMH VLIML

SelectorVREF

VCC

6

BandGap

VM1 41

39

40

45

46

44

17

15

16

21

22

20

34

32

35

33

28

27

31

29

30

OUT1A

OUT1B

OUT2A

OUT2B

PGND1

VM2

OUT3A

OUT3B

OUT4A

OUT4B

PGND2

VM3

OUT5A

OUT5B

PGND3

VM4

OUT6A

OUT6B

RNF

SENSE

36

EN1

VM3

OUT5B

IN6

PS

OUT1A

OUT1B

VM1

N.C.

N.C.

PGND1

OUT2A

OUT2B

IN1A

IN1B

48

PGND3

BD6873KN

IN2A

IN2B

SEL1

IN3A

RNF

OUT5A

IN3B

VM4

OUT6B

VCC

SENSE

GND

OUT6A

IN4A

IN4B

SEL2

H bridge

&

&

&

&

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Const. Current

7

GND

Fig.14 BD6873KN Block Diagram Fig.15 BD6873KN Pin Arrangement (Top View)

UQFN48 Package

BD6873KN Pin Function Table

No. Pin name Function No. Pin name Function

1 IN2A Control input pin ch2 A 25 VLIML Output current setting pin 2 ch6

2 IN2B Control input pin ch2 B 26 VLIMS Output current selection pin ch6

3 SEL1 Input mode selection pin ch1 and ch2 27 OUT6A H-bridge output pin ch6 A

4 IN3A Control input pin ch3 A 28 VM4 Motor power supply pin ch6

5 IN3B Control input pin ch3 B 29 RNF Resistance connection pin for output current detection ch6

6 VCC Power supply pin 30 SENSE Output current detection pin ch6

7 GND Ground pin 31 OUT6B H-bridge output pin ch6 B

8 IN4A Control input pin ch4 A 32 OUT5A H-bridge output pin ch5 A

9 IN4B Control input pin ch4 B 33 PGND3 Motor ground pin ch5

10 SEL2 Input mode selection pin ch3 and ch4 34 VM3 Motor power supply pin ch5

11 IN5A Control input pin ch5 A 35 OUT5B H-bridge output pin ch5 B

12 IN5B Control input pin ch5 B 36 EN1 Control input pin ch6 ENABLE

13 SEL3 Input mode selection pin ch5 37 IN6 Control input pin ch6 INPUT

14 BRK1 Control input pin ch5 BRAKE 38 PS Power-saving pin

15 OUT3A H-bridge output pin ch3 A 39 OUT1A H-bridge output pin ch1 A

16 OUT3B H-bridge output pin ch3 B 40 OUT1B H-bridge output pin ch1 B

17 VM2 Motor power supply pin ch3 and ch4 41 VM1 Motor power supply pin ch1 and ch2

18 N.C. - 42 N.C. 19 N.C. - 43 N.C. 20 PGND2 Motor ground pin ch3 and ch4 44 PGND1 Motor ground pin ch1 and ch2

21 OUT4A H-bridge output pin ch4 A 45 OUT2A H-bridge output pin ch2 A

22 OUT4B H-bridge output pin ch4 B 46 OUT2B H-bridge output pin ch2 B

23 VREF Reference voltage output pin 47 IN1A Control input pin ch1 A

24 VLIMH Output current setting pin 1 ch6 48 IN1B Control input pin ch1 B

VLIMS

IN5A

VLIML

VLIMH

VREF

OUT4B

OUT4A

PGND2

N.C.

N.C.

VM2

OUT3B

OUT3A

BRK1

SEL3

IN5B

12

24

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

6/17

2009.06 - Rev.A

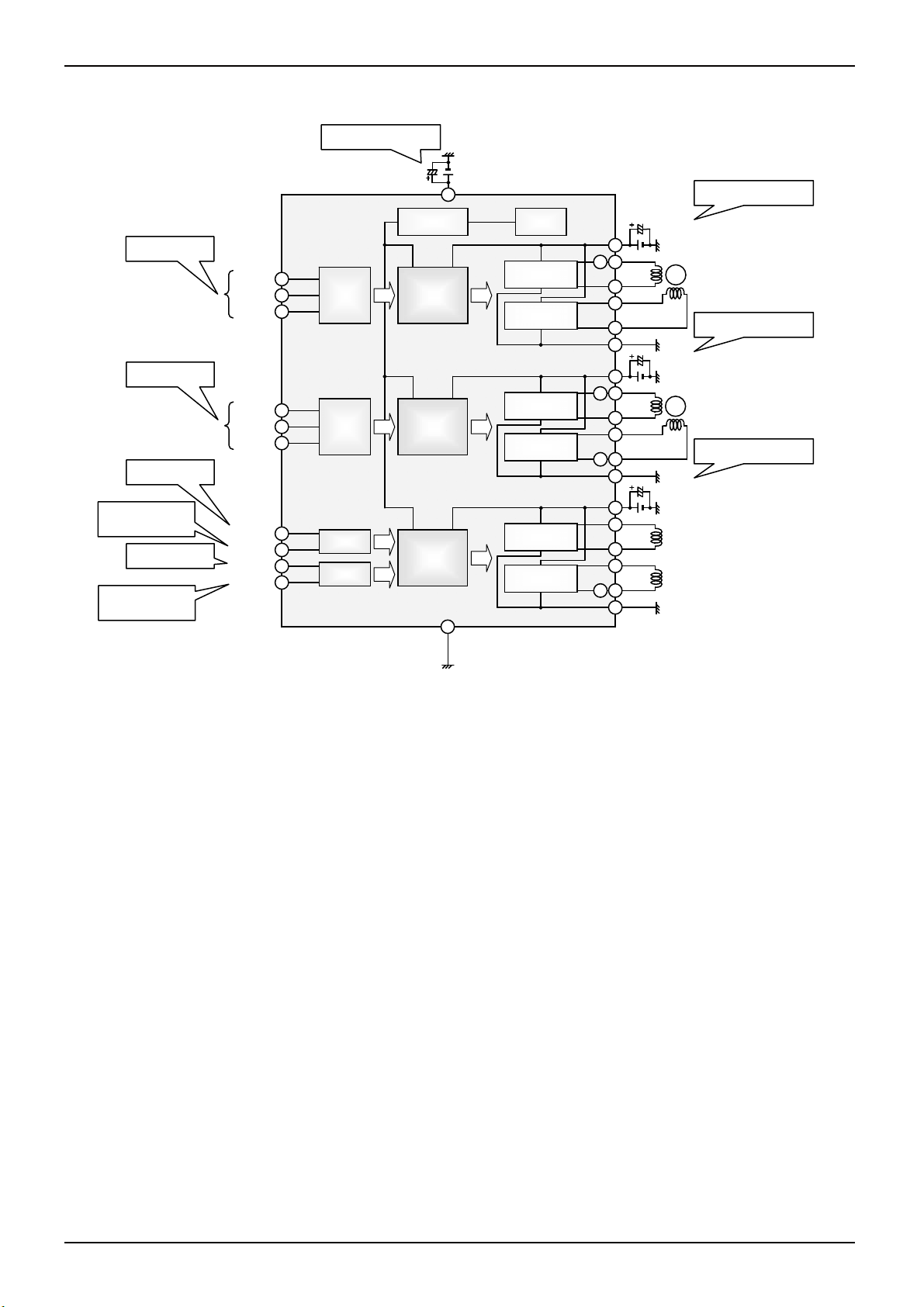

BD6373GW, BD6873KN, BD6753KV

A

A

A

A

K

9

OSC

VCC

CP1 4 CP2

5

Charge Pump Charge Pump

CP3 6 CP4 7VG

8

Technical Note

PS

PWM1

PWM2

PWM3

PWM4

PWM5

PWM6

STROBE

CLK

DATA

28

Power Save

2

3

10

11

12

1

31

32

33

30 29 34

Logic12

Logic34

Logic45

Logic56

Serial

Interface

VREF

TSD & UVLO

VG

Level Shift

&

Pre Driver

VG

Level Shift

&

Pre Driver

VG

Level Shift

&

Pre Driver

PWM LATCH

PWM LATCH

BandGap

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

PWM C. Current

H bridge

PWM C. Current

26 3527

VREF CR2 CR1 GND VREF

VLIM5 VLIM6

VM1 45

44

OUT1A

41

OUT1B

43

OUT2A

46

OUT2B

48

RNF1 47

42

17

VM2

16

OUT3A

13

OUT3B

15

OUT4A

18

OUT4B

20

RNF2 19

14

25

VM3

OUT5A

21

OUT5B

24

36

VM4

37

40

39

22

23

OUT6A

OUT6B

RNF4

SENSE4 38

RNF3

SENSE3

48

36

VM4

VLIM6

OUT6A

SENSE4

RNF4

OUT6B

OUT1A

RNF1

OUT1B

BD6753KV

VM1

VM1

OUT2A

RNF1

OUT2B

PWM6

PWM1

CR2

PWM2

CL

DAT

CP1

CP2

PS

CR1

GND

VREF

STROBE

CP3

CP4

VG

VCC

PWM3

Fig.16 BD6753KV Block Diagram Fig.17 BD6753KV Pin Arrangement (Top View)

VQFP8C Package

BD6753KV Pin Function Table

No. Pin name Function No. Pin name Function

1 PWM6 PWM control input pin ch6 25 VM3 Motor power supply pin ch5

2 PWM1 PWM control input pin ch1 26 VLIM5 Output current setting pin ch5

3 PWM2 PWM control input pin ch2 27 CR1 CR timer setting element connection pin ch5

4 CP1 Charge pump capacitor connection pin 1 28 PS Power-saving pin

5 CP2 Charge pump capacitor connection pin 2 29 VREF Reference voltage output pin

6 CP3 Charge pump capacitor connection pin 3 30 GND Ground pin

7 CP4 Charge pump capacitor connection pin 4 31 STROBE Serial enable input pin

8 VG Charge pump output pin 32 CLK Serial clock input pin

9 VCC Power supply pin 33 DATA Serial data input pin

10 PWM3 PWM control input pin ch3 34 CR2 CR timer setting element connection pin ch6

11 PWM4 PWM control input pin ch4 35 VLIM6 Output current setting pin ch6

12 PWM5 PWM control input pin ch5 36 VM4 Motor power supply pin ch6

13 OUT3A H-bridge output pin ch3 A 37 OUT6A H-bridge output pin ch6 A

14 RNF2 Motor ground pin ch3 and ch4 38 SENSE4 Output current detection pin ch6

15 OUT3B H-bridge output pin ch3 B 39 RNF4 Resistance connection pin for output current detection ch6

16 VM2 Motor power supply pin ch3 and ch4 40 OUT6B H-bridge output pin ch6 B

17 VM2 Motor power supply pin ch3 and ch4 41 OUT1A H-bridge output pin ch1 A

18 OUT4A H-bridge output pin ch4 A 42 RNF1 Motor ground pin ch1 and ch2

19 RNF2 Motor ground pin ch3 and 4 43 OUT1B H-bridge output pin ch1 B

20 OUT4B H-bridge output pin ch4 B 44 VM1 Motor power supply pin ch1 and ch2

21 OUT5A H-bridge output pin ch5 A 45 VM1 Motor power supply pin ch1 and ch2

22 RNF3 Resistance connection pin for output current detection ch5 46 OUT2A H-bridge output pin ch2 A

23 SENSE3 Output current detection pin ch5 47 RNF1 Motor ground pin ch1 and ch2

24 OUT5B H-bridge output pin ch5 B 48 OUT2B H-bridge output pin ch2 B

VLIM5

SENSE3

PWM4

12

VM3

OUT5B

RNF3

OUT5

OUT4B

RNF2

OUT4

VM2

VM2

OUT3B

RNF2

OUT3

PWM5

24

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

7/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

A

A

A

A

A

A

●Application Circuit Diagram and Function Explanation

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

Motor control input

(p.8/16)

TSD & UVLO

C2

ENABLE12

INPUT1

INPUT2

D2

E3

Logic12

Level Shift

&

Pre Driver

Motor control input

(p.8/16)

D3

Motor control input

(p.8/16)

ENABLE34

INPUT3

INPUT4

B3

B4

Logic34

Level Shift

&

Pre Driver

Motor control input

brake function (p.8/16)

H : Brake

Motor control input

(p.8/16)

Motor control input

brake function (p.8/16)

H : Brake

INPUT5

BRAKE5

INPUT6

BRAKE6

C5

D4

E4

D5

Logic5

Logic6

Level Shift

&

Pre Driver

Fig.18 BD6373GW Application Circuit Diagram

1) Power-saving function

When Low-level voltage is applied to PS pin, the IC will be turned off internally and the circuit current will be 0μA (Typ.).

During operating mode, PS pin should be High-level. (See the Electrical Characteristics; p.2/16)

2) Motor Control input

(1) ENABLExx and INPUTx pins (BD6373GW), INxA, INxB, EN1 and IN6 pins (BD6873KN), and PWMx pins (BD6753KV)

These pins are used to program and control the motor drive modes. (See the Electrical Characteristics; p.2/16 and

p.3/16 and I/O Truth Table; p.12/16 and p.13/16)

(2) SELx pins (BD6873KN)

When the Low-level voltage is applied to the SELx pins, the I/O logic can be set to EN/IN mode. However, when the

High-level voltage is applied, the I/O logic can be set to IN/IN mode. The same selection made with the BD6873KN's

SELx pin can be made for the BD6753KV, using serial control. (See the Electrical Characteristics; p.2/16 and p.3/16

and I/O Truth Table)

(3) BRAKEx pins (BD6373GW) and BRK1 pin (BD6873KN)

Applying the High-level voltage pin will set the brake mode. The same selection made with the brake mode can be

made for the BD6753KV, using serial control. (See the Electrical Characteristics; p.2/16 and p.3/16 and I/O Truth

Table; p.12/16 and p.13/16)

Technical Note

VCC

F3

BandGap

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

F4

GND

E2

1

6

E5

F2

F1

E1

D1

C1

B1

2

B2

3

4

B5

5

F5

C6

D6

E6

F6

B6

1~100uF

VM12

OUT1A

OUT1B

OUT2A

OUT2B

PGND12

1~100uF

VM34

OUT3A

OUT3B

OUT4A

OUT4B

PGND34

1~100uF

VM56

OUT5A

OUT5B

OUT6A

OUT6B

PGND56

Bypass filter Capacitor for

power supply input. (p.14/16)

M

Bypass filter Capacitor for

power supply input. (p.14/16)

M

Bypass filter Capacitor for

power supply input. (p.14/16)

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

8/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

Bypass filter Capacitor for

power supply input. (p.14/16)

Power-saving (p.8/16)

H : Active

L : Standby

Motor control input

(p.8/16)

Drive mode selection

(p.8/16)

H : EN/IN

L : IN/IN

Motor control input

(p.8/16)

Drive mode selection

(p.8/16)

H : EN/IN

L : IN/IN

Motor control input

(p.8/16)

Drive mode selection

(p.8/16)

H : EN/IN

L : IN/IN

Motor control input

brake function (p.8/16)

H : Brake

IN1A

IN1B

IN2A

IN2B

SEL1

IN3A

IN3B

IN4A

IN4B

SEL2

IN5A

IN5B

SEL3

BRK1

Motor control input

(p.8/16)

When using the VREF voltage (1.2V) resistance divi sion

value as VLIMH and VLIML input value, select R

values such that,

2kΩ≦R

1+R2+R3

≦20kΩ (p.9/16)

PS

38

47

48

1

2

3

4

5

8

9

10

11

12

13

14

EN1

36

IN6

37

, R2, and R3

1

Power Save

Logic12

Logic12

Logic34

Logic5

Logic6

23 24 2526

VREF VLIMS VLIMH VLIML

R1

Output current selection

(p.10/16)

H : VLIML

L : VLIMH

Fig.19 BD6873KN Application Circuit Diagram

1~100uF

TSD & UVLO

Level Shift

&

Pre Driver

Level Shift

&

Pre Driver

Level Shift

&

Pre Driver

Level Shift

&

Pre Driver

SelectorVREF

R2 R3

VCC

6

3) H-bridge

The 6-channel H-bridges of can be controlled independently. For this reason, it is possible to drive the H-bridges

simultaneously, as long as the package thermal tolerances are not exceeded.

The H-bridge output transistors of the BD6373GW, BD6873KN and BD6753KV consist of Power CMOS, with the motor

power supply VM, and Power DMOS, with the charge pump step-up power supply VG, respectively. The total H-bridge

ON-Resistance on the high and low sides varies with the VM and VG voltages, respectively. The system must be

designed so that the maximum H-bridge current for each channel is 800mA or below.

4) Drive system of Linear Constant-Current H-bridge (BD6873KN: ch6)

BD6873KN (ch6) enables Linear Constant-Current Driving.

(1) Reference voltage output (with a tolerance of ±3%)

The VREF pin outputs 1.2V, based on the internal reference voltage. The output current of the Constant-Current Drive

block is controllable by connecting external resistance to the VREF pin of the IC and applying a voltage divided by the

resistor to the output current setting pins (VLIMH and VLIML pins). It is recommended to set the external resistance to

2kΩ or above in consideration of the current capacity of the VREF pin, and 20kΩ or below in order to minimize the

fluctuation of the set value caused by the base current of the internal transistor of the IC.

BandGap

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Full ON

H bridge

Const. Current

7

GND

Technical Note

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

41

VM1

39

40

45

46

44

17

15

16

21

22

20

34

32

35

33

28

27

31

29

30

OUT1A

OUT1B

OUT2A

OUT2B

PGND1

VM2

OUT3A

OUT3B

OUT4A

OUT4B

PGND2

VM3

OUT5A

OUT5B

PGND3

VM4

OUT6A

OUT6B

RNF

SENSE

M

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

M

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

0.1Ω~5.0Ω

The output current is converted to a voltage with

the RNF external resistor and transmitted to the

SENSE pin. (p.10/16)

Iout[A] = (VLIMH or VLIML[V])÷RNF[Ω]

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

9/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

(p

)

L

L

L

Bypass filter Capacitor for

power supply input. (p.14/16)

Power-saving (p.8/16)

H : Active

L : Standby

1~100uF

9

OSC

VCC

PS

28

Motor control input

(p.8/16)

Power Save

PWM1

PWM2

2

3

Logic12

Motor control input

(p.8/16)

PWM3

PWM4

10

11

Logic34

Motor control input

(p.8/16)

Serial control input

(p.12/16)

PWM5

PWM6

STROBE

CLK

DATA

12

1

31

32

33

Logic45

Logic56

Serial

Interface

VREF

30 29 34

This CR timer determines the

off time for the PWM drive.

5kΩ≦R

10pF≦C

(p.11/16)

Fig.20 BD6753KV Application Circuit Diagram

(2) Output current settings and setting changes

When the Low-level control voltage is applied to the VLIMS pin, the value on the VLIMH pin will be used as an output current

set value to control the output current. When the High-level control voltage is applied to the VLIMS pin, the value on the VLIML

pin will be used as an output current set value to control the output current. (See the Electrical Characteristics; P.2/16)

(3) Output current detection and current settings

By connecting external resistor (0.1Ω to 5.0Ω) to the RNF pin of the IC, the motor drive current will be converted into voltage in

order to be detected. The output current is kept constant by shorting the RNF and SENSE pins and comparing the voltage with

the VLIMH or VLIML voltage. To perform output current settings more precisely, trim the external RNF resistance if needed, and

supply a precise voltage externally to the VLIMH or VLIML pin of the IC. In that case, open the VREF pin.

Output current value Iout[A] =

The output current is 400mA3% if 0.2V is applied to the VLIMH or VLIML pin and a 0.5Ω resistor is connected externally to

the RNF pin.

VLIMH[V] or VLIML[V]

If the VLIMH and VLIML pins are shorted to the VCC pin (or the same voltage level as the VCC is applied) and the SENSE and

RNF pins are shorted to the ground, this channel can be used as a Full-ON Drive H-bridge like the other five channels.

Connecting 0.01μF to 0.1μF capacitors between the CP1 and CP2, CP3

and CP4, and VG and GND pins generate a VG vo ltage of approximately

VM1 + (VCC 2). Use caution to ens ure that the voltage differential between

VG and VM is 4.5V or higher, and that the VG voltage does not exceed the

absolute maximum rating of 18 V, especially BST voltage direct input.

.12/16

0.1μF 0.1μF

CP1 4CP2

5

Charge Pump Charge Pump

TSD & UVLO

VG

VG

VG

PWM LATCH

PWM LATCH

C

≦50kΩ

CR1

≦2200pF

CR1

CR1

0.1μF

CP3 6CP4 7VG

R

C

CR2

CR2RCR1

This CR timer determines the

off time for the PWM drive.

5kΩ≦R

CR2

10pF≦C

(p.11/16)

CR2

RNF[Ω]

Technical Note

8

Bypass filter Capacitor for

power supply input. (p.14/16)

BandGap

44

H bridge

Full ON

H bridge

Full ON

42

16

H bridge

Full ON

H bridge

Full ON

14

H bridge

PWM C. Current

H bridge

PWM C. Current

26 3527

VLIM5 VLIM6

VREF CR2 CR1 GND VREF

R2 R3

R1

When using the VREF voltage (0.9V) resistance divi sion

≦50kΩ

≦2200pF

value as VLIM5 and VLIM6 input value, s elect R

values such that,

Select VLIMH when VLIMS is Low-level

Select VLIML when VLIMS is High-level

45

41

43

46

48

47

17

13

15

18

20

19

25

21

24

36

37

40

39

38

22

23

VM1

OUT1A

OUT1B

OUT2A

OUT2B

RNF1

VM2

OUT3A

OUT3B

OUT4A

OUT4B

RNF2

VM3

OUT5A

OUT5B

VM4

OUT6A

OUT6B

RNF4

0.1Ω~5.0Ω

SENSE4

RNF3

0.1Ω~5.0Ω

SENSE3

1~100uF

M

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

M

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

Bypass filter Capacitor for

power supply input. (p.14/16)

1~100uF

The output current is converted

to a voltage with the RNF4

external resistor and transmitted

to the SENSE4 pin. (p.11/16)

Iout[A] = VLIM6[V]÷RNF4[Ω]

The output current is converted

to a voltage with the RNF3

external resistor and transmitted

to the SENSE3 pin. (p.11/16)

Iout[A] = VLIM5[V]÷RNF3[Ω]

1+R2+R3

≦20kΩ (p.11/16)

1kΩ≦R

, R2, and R3

1

・・・・・・(1)

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

10/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

5) Drive system of PWM Constant-Current H-bridge (BD6753KV: ch5 and ch6)

BD6753KV (ch5 and ch6) enable peak current control PWM Constant-Current Driving.

(1) Output current detection and current settings

By connecting external resistance (0.1Ω to 5.0Ω) to the RNF3 and RNF4 pins of the IC, the motor drive current will be

converted into voltage in order to be detected. The output current is kept constant by shorting the RNF3 and RNF4 pins with

the SENSE3 and SENSE4 pins, respectively, and comparing the voltage to the set voltage input from outside the IC to the

VLIM5 and VLIM6 pins. As with the BD6873KN, the reference voltage generated inside the IC (VREF pin: 0.9V±10%) can

be divided using external resistors (from 1kΩ to 20kΩ). The resulting value can be input as the set voltage.

It is also necessary to connect a resistor and capacitor to the CR1 and CR2 pins, to determine the PWM drive off time.

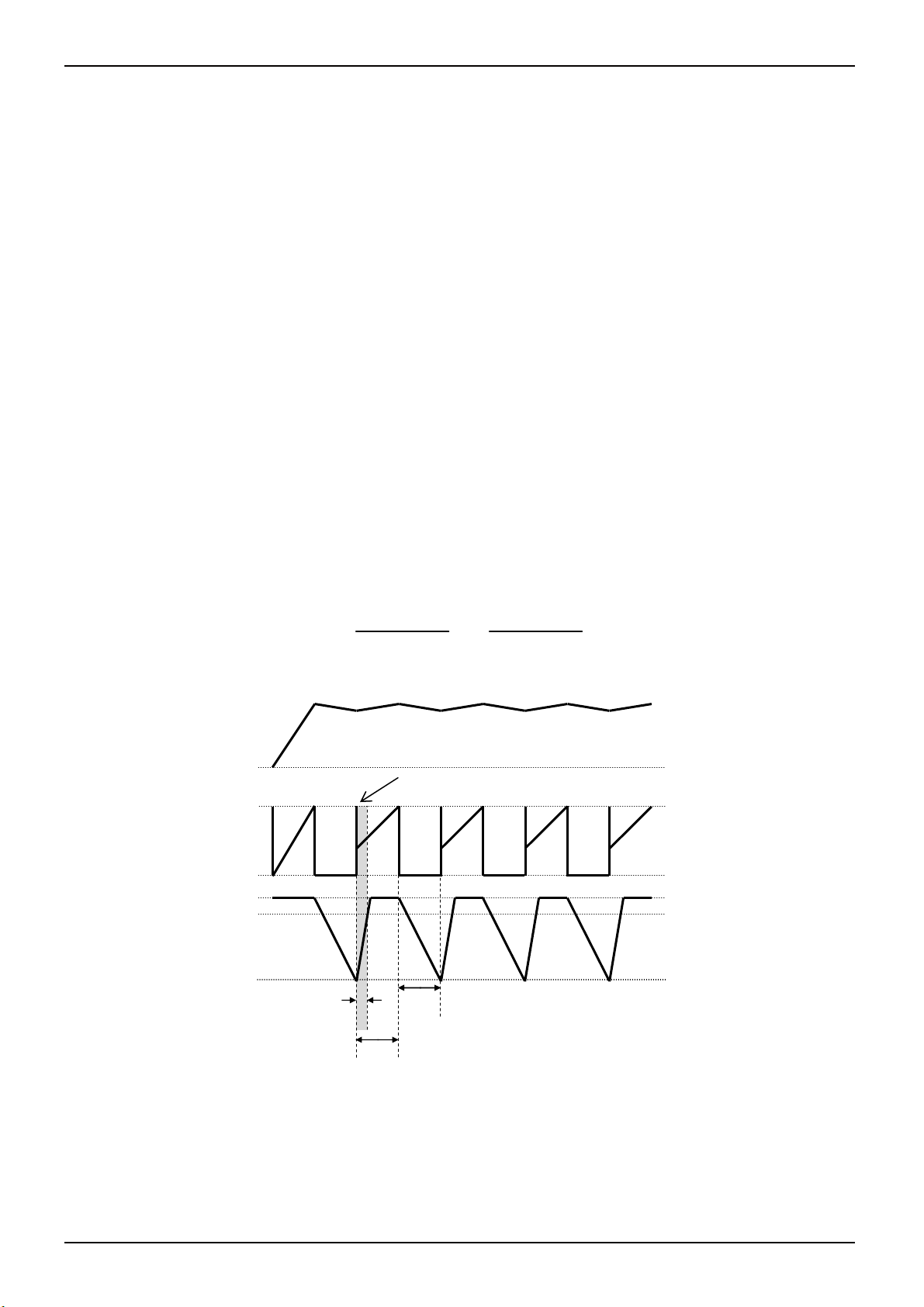

(2) PWM Constant-Current control operation

When the output current in output ON mode increases, and the RNF3 or RNF4 voltage reaches the value set with the

VLIM5 or VLIM6 voltage, the internal current limiting comparator operates to set the IC to short mode. This caused the

current to be attenuated so that the H-bridge's low-side DMOS is ON. Once the off time (Toff) ends, as measured by

the CR timer, the IC returns to output ON mode. By repeating this cycle, the IC maintains a fixed current due to the

motor's inductance characteristics.

(3) Noise cancellation function

In order to avoid false detections by the current limiting comparator (caused by spike noise generated when output is

turned on), the IC uses the noise cancellation time (Tn) to disable current detection. This begins from the time output

turns on, until the noise cancellation time elapses. The noise cancellation time represents the minimum on time, and is

determined by the CR pin's internal resistor, external resistor, and capacitor.

(4) CR timer

When output turns on, the CR pin is clamped at approximately 0.9V. When the mode changes to short mode, it

discharges to approximately 0.4V. The interval over which this 0.5V voltage differential is discharged, is determined by

the off time (Toff). Once the CR pin voltage reaches 0.4V, the pin begins to charge as the output turns on, until it

reaches 0.9V. The interval over which the pin charges from 0.4V to approximately 0.8V is given by the noise

cancellation time (Tn). Toff and Tn are determined by the external resistor and capacitor connected to the CR pin.

A low resistance value to the CR pin will prevent it from reaching the clamp voltage. Therefore a resistor from 5 kΩ to

50kΩ should be used. Capacitors should be from 10pF to 2200pF. The use of a capacitance in excess of 2200pF will

lengthen the noise cancellation time and may cause the output current to exceed the set current. Setting a longer off

time may increase the output current ripple, reducing both the average current and the motor's rotational efficiency.

Output current value Iout[A] =

VLIM5[V]

RNF3[Ω]

or

VLIM6[V]

RNF4[Ω]

Output current: Iout[A]

Spike noise

RNF voltage: VRNF[V]

CR voltage: VCR[V]

Noise cancellation time: Tn[sec]

Charge period

Discharge period

Off time: Toff[sec]

Fig.21 BD6753KV Peak Current Control PWM Constant-Current Drive Using the CR Timer

If the VLIM5 or VLIM6 is shorted to the VCC pin (or the same voltage level as the VCC is applied) and the SENSE3 or

SENSE4 and RNF3 or RNF4 pins are shorted to the ground, this channel can be used as a Full-ON Drive H-bridge

like the other four channels.

Technical Note

・・・・・・(2)

PWM Constant-Current

setting value

0A

VLIM pin setting voltage

0V

0.9V

0.8V

0.4V

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

11/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

6) Charge pump (BD6753KV)

Each output H-bridge of the BD6753KV on the high and low sides consists of Nch DMOS. Therefore, the gate voltage VG

should be higher than the VM voltage to drive the Nch DMOS on the high side.The BD6753KV has a built-in charge

pump circuit that generates VG voltage by connecting an external capacitor (0.01μF to 0.1μF).

If a 0.1μF capacitor is connected between: CP1 and CP2, CP3 and CP4, VG and GND

Then, VG pin output voltage will be: VM1 + (VCC 2)

If a 0.1μF capacitor is connected between: CP1 and CP2, VG and GND

CP4 and VG pins are shorted, and CP3 pin is open

Then, VG pin output voltage will be: VM1 + VCC

The VM1 to VM4 respectively can be set to voltages different to one another. In order to ensure better performance, the

voltage differential between VG and VM must be 4.5V or higher, and the VG voltage must not exceed the absolute

maximum rating of 18V.

7) Serial interface (BD6753KV)

The BD6753KV provides an 8-bit, 3-line serial interface for setting output modes. DATA is sent to the internal shift register

during the STROBE low interval at the CLK rising edge. Shift register data is written to the IC's internal 6-bit memory at

the STROBE rising edge, according to the addresses stored in Bit[7] and Bit[6]. The serial data input order is Bit[0] to

Bit[7]. Serial settings are reset when the PS pin changes to Low-level control voltage, triggering standby mode. Serial

settings are also reset when the UVLO circuit operates.

BD6753KV Serial Resistor Bit Map

No.

ADDRESS BIT DATA BIT

Bit[7] Bit[6] Bit[5] Bit[4] Bit[3] Bit[2] Bit[1] Bit[0]

00H 0 0 mod2 mod1 p2a p2b p1a p1b

01H 0 1 mod4 mod3 p4a p4b p3a p3b

02H 1 0 mod6 mod5 p6a p6b p5a p5b

STROBE

CLK

DATA

Timing of input serial data

writing to internal register

Bit[0] Bit[1] Bit[2] Bit[3] Bit[4] Bit[5] Bit[6] Bit[7] Bit[0] Bit[1] Bit[5] Bit[6] Bit[7]

DATA BITS

Fig.22 BD6753KV Sequence of Serial Control Input

●I/O Truth Table

BD6373GW Full-ON Driver ch1 to ch2 I/O Truth Table

Drive mode

ENABLE12 INPUTx OUTxA OUTxB

INPUT OUTPUT

H X Z Z Standby

EN/IN

L L H L CW

L H L H CCW

BD6373GW Full-ON Driver ch3 to ch4 I/O Truth Table

Drive mode

ENABLE34 INPUTx OUTxA OUTxB

INPUT OUTPUT

H X Z Z Standby

EN/IN

L L H L CW

L H L H CCW

BD6373GW Full-ON Driver ch5 to ch6 I/O Truth Table

Drive mode

INPUT OUTPUT

INPUTx BRAKEx OUTxA OUTxB

L L H L CW

IN/IN

H L L H CCW

X H L L Brake

L: Low, H: High, X: Don't care, Z: High impedance

At CW, current flows from OUTA to OUTB. At CCW, current flows from OUTB to OUTA.

ADDRESS BITS

Output mode

Output mode

Output mode

Technical Note

Timing of register data writing to

internal memory

DATA BITS

ADDRESS BITS

100%

0%

100%

0%

100%

0%

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

12/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

BD6873KN Full-ON Driver ch1 to ch4 I/O Truth Table

Drive mode

SELx INxA INxB OUTxA OUTxB

INPUT OUTPUT

H X Z Z Standby

EN/IN L

L L H L CW

L H L H CCW

L L Z Z Standby

IN/IN H

H L H L CW

L H L H CCW

H H L L Brake

L: Low, H: High, X: Don't care, Z: High impedance

At CW, current flows from OUTA to OUTB. At CCW, current flows from OUTB to OUTA.

BD6873KN Full-ON Driver ch5 I/O Truth Table

Drive mode

SEL3 IN5A IN5B BRK1 OUT5A OUT5B

INPUT OUTPUT

H X X Z Z Standby

EN/IN L

L L L H L CW

L H L L H CCW

L X H L L Brake

L L X Z Z Standby

IN/IN H

H L X H L CW

L H X L H CCW

H H X L L Brake

L: Low, H: High, X: Don't care, Z: High impedance

At CW, current flows from OUTA to OUTB. At CCW, current flows from OUTB to OUTA.

BD6873KN Linear Constant-Current Driver ch6 I/O Truth Table

Drive mode

EN1 IN6 OUT6A OUT6B

INPUT OUTPUT

H X Z Z Standby

EN/IN

L L H L CW

L H L H CCW

L: Low, H: High, X: Don't care, Z: High impedance

At CW, current flows from OUTA to OUTB. At CCW, current flows from OUTB to OUTA.

BD6753KV ch1 to ch6 I/O Truth Table

INPUT

Drive mode

Serial data Terminal

modx pxa pxa PWMx OUTxA OUTxB

L L X Z Z Standby

L H L L H CCW

IN/IN L

L H H L L Brake

H L L H L CW

H L H L L Brake

H H X L L Brake

L X X Z Z Standby

EN/IN H

H L L H L CW

H L H L H CCW

H H X L L Brake

L: Low, H: High, X: Don't care, Z: High impedance

At CW, current flows from OUTA to OUTB. At CCW, current flows from OUTB to OUTA.

OUTPUT

Technical Note

Output mode

Output mode

Output mode

Output mode

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

13/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

Technical Note

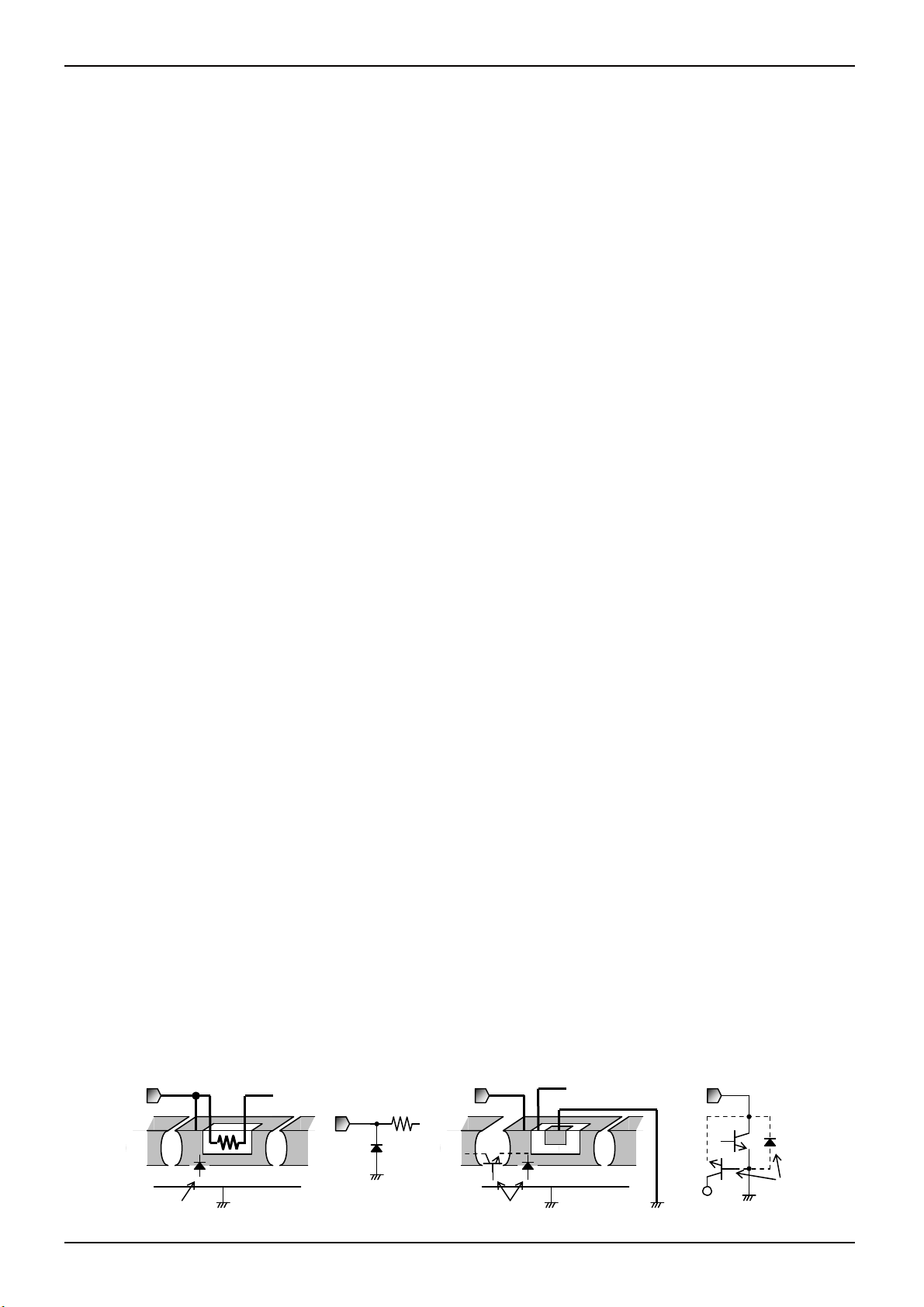

●I/O Circuit Diagram

PS, INxA, INxB, EN1, IN6, VLIMS

ENABLExx, INPUTx, BRAKEx VMx, OUTxA, OUTxB, PGNDx

VCC

VCC

140kΩ

10kΩ

100kΩ

VMx

OUTxA

OUTxB

PGNDx

Fig.23 BD6373GW I/O Circuit Diagram (Resistance values are typical ones)

VMx, OUTxA, OUTxB, PGNDx, RNF VLIMH, VLIML, SENSE

VREF

VCC

VCC

VMx

VCC VCC

VCC

10kΩ

100kΩ

OUTxA

OUTxB

PGNDx

RNF

10kΩ

200kΩ

PS

VCC

Fig.24 BD6873KN I/O Circuit Diagram (Resistance values are typical ones)

STROBE, CLK, DATA, PWMx CPH1, CPL1

VCC

VCC

VMx, OUTxA, OUTxB, RNFx

VMx

VLIMx, SENSEx

40kΩ

70kΩ

CP3, CP1 VG, CP4, CP2 CR1, CR2

10kΩ

100kΩ

OUTxA

OUTxB

VCC

RNFx

100kΩ

VCC

1kΩ

VCC

VCC

VG

5kΩ

CP4

CP2

Fig.25 BD6753KV I/O Circuit Diagram (Resistance values are typical ones)

VM1

●Operation Notes

1) Absolute maximum ratings

Use of the IC in excess of absolute maximum ratings such as the applied voltage or operating temperature range may result in

IC damage. Assumptions should not be made regarding the state of the IC (short mode or open mode) when such damage is

suffered. The implementation of a physical safety measure such as a fuse should be considered when use of the IC in a

special mode where the absolute maximum ratings may be exceeded is anticipated.

2) Storage temperature range

As long as the IC is kept within this range, there should be no problems in the IC’s performance. Conversely, extreme

temperature changes may result in poor IC performance, even if the changes are within the above range.

VCC VCC

VCC VCC

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

14/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

Technical Note

3) Power supply pins and lines

None of the VM line for the H-bridges is internally connected to the VCC power supply line, which is only for the control

logic or analog circuit. Therefore, the VM and VCC lines can be driven at different voltages. Although these lines can be

connected to a common power supply, do not open the power supply pin but connect it to the power supply externally.

Regenerated current may flow as a result of the motor's back electromotive force. Insert capacitors between the power

supply and ground pins to serve as a route for regenerated current. Determine the capacitance in full consideration of all

the characteristics of the electrolytic capacitor, because the electrolytic capacitor may loose some capacitance at low

temperatures. If the connected power supply does not have sufficient current absorption capacity, regenerative current will

cause the voltage on the power supply line to rise, which combined with the product and its peripheral circuitry may exceed

the absolute maximum ratings. It is recommended to implement a physical safety measure such as the insertion of a

voltage clamp diode between the power supply and ground pins.

For this IC with several power supplies and a part consists of the CMOS block, it is possible that rush current may flow

instantaneously due to the internal powering sequence and delays, and to the unstable internal logic, respectively. Therefore,

give special consideration to power coupling capacitance, width of power and ground wirings, and routing of wiring.

4) Ground pins and lines

Ensure a minimum GND pin potential in all operating conditions. Make sure that no pins are at a voltage below the GND at

any time, regardless of whether it is a transient signal or not.

When using both small signal GND and large current MGND patterns, it is recommended to isolate the two ground patterns,

placing a single ground point at the application's reference point so that the pattern wiring resistance and voltage variations

caused by large currents do not cause variations in the small signal ground voltage. Be careful not to change the GND

wiring pattern of any external components, either.

The power supply and ground lines must be as short and thick as possible to reduce line impedance.

5) Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

6) Pin short and wrong direction assembly of the device

Use caution when positioning the IC for mounting on printed circuit boards. The IC may be damaged if there is any

connection error or if positive and ground power supply terminals are reversed. The IC may also be damaged if pins are

shorted together or are shorted to other circuit’s power lines.

7) Actions in strong magnetic field

Use caution when using the IC in the presence of a strong magnetic field as doing so may cause the IC to malfunction.

8) ASO

When using the IC, set the output transistor for the motor so that it does not exceed absolute maximum ratings or ASO.

9) Thermal shutdown circuit

If the junction temperature (Tjmax) reaches 175°C, the TSD circuit will operate, and the coil output circuit of the motor will

open. There is a temperature hysteresis of approximately 25°C (BD6373GW and BD6873KN Typ.) and 25°C (BD6753KV

Typ.). The TSD circuit is designed only to shut off the IC in order to prevent runaway thermal operation. It is not designed to

protect the IC or guarantee its operation. The performance of the IC’s characteristics is not guaranteed and it is

recommended that the device is replaced after the TSD is activated.

10) Serial data input

In the BD6753KV, DATA input string start with LSB first.

The serial settings are reset during standby mode operation and whenever the UVLO or TSD circuits are operating.

11) Power saving terminal

Be cancelled power saving mode after turned on power supply VCC and VM, because of PS terminal combines power

saving with serial reset function. If the case of power saving terminal always shorted power supply terminal, reset function

may not be well, and it may cause the IC to malfunction.

12) Testing on application board

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress.

Always discharge capacitors after each process or step. Always turn the IC's power supply off before connecting it to, or

removing it from a jig or fixture, during the inspection process. Ground the IC during assembly steps as an antistatic

measure. Use similar precaution when transporting and storing the IC.

13) Application example

The application circuit is recommended for use. Make sure to confirm the adequacy of the characteristics. When using the

circuit with changes to the external circuit constants, make sure to leave an adequate margin for external components

including static and transitional characteristics as well as dispersion of the IC.

14) Regarding input pin of the IC

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements to keep them isolated. P-N

junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode or

transistor. For example, the relation bet

ween each potential is as follows:

When GND > Pin A, the P-N junction operates as a parasitic diode.

When GND > Pin B, the P-N junction operates as a parasitic diode and transistor.

Parasitic elements can occur inevitably in the structure of the IC. The operation of parasitic elements can result in mutual

interference among circuits, operational faults, or physical damage. Accordingly, methods by which parasitic elements

operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin, should not be used.

Pin A

N

P+ P

P

Parasitic element

GND

Resistor Transistor (NPN)

Pin A

+

N N

P substrate

Parasitic

element

Fig.26 Example of Simple IC Architecture

Pin B

N

Parasitic element

C

P+

B

E

N

P

P+

N

P substrate

GND

GND

Pin B

B C

Other adjacent

elements

E

GND

Parasitic

element

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

15/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

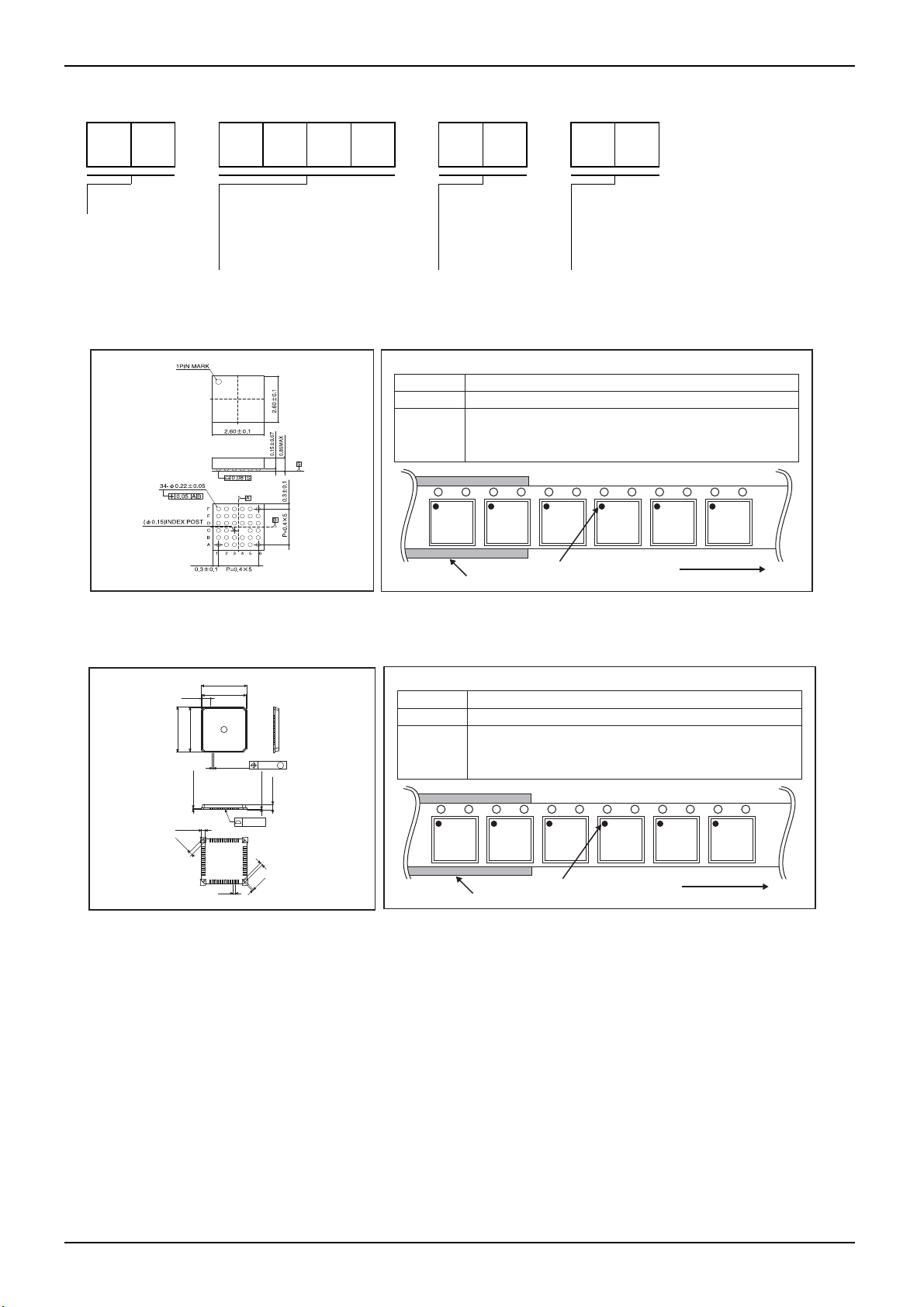

●Ordering part number

B D 6 3 7 3 G W - E 2

Technical Note

Part No. Part No.

Package

6373 : F.ON 6ch

6873 : F.ON 5ch+C.C. 1ch

6753 : F.ON 4ch+PWM 2ch

UCSP75M2 (BD6373GW)

<Tape and Reel information>

Quantity

Direction

of feed

(Unit:mm)

UQFN48

(1.4)

7.2± 0.1

0.6

(0.55)

7.0± 0.1

+0.1

-

37

48

0.22± 0.05

0.3

7.2± 0.1

7.0± 0.1

36

1

0.2± 0.05

0.4

<Tape and Reel information>

25

24

13

12

M

0.05

0.02

-

+0.03

0.95MAX

0.02

0.05

3-(0.45)

Notice :

Do not use the dotted line area

(0.2)

for soldering

(Unit : mm)

Quantity

Direction

of feed

Packaging and forming specification

GW : UCSP75M2

KN : UQFN48

KV : VQFP48C

Embossed carrier tapeTape

3000pcs

E2

The direction is the 1pin of product is at the upper left when you hold

()

reel on the left hand and you pull out the tape on the right hand

Reel

Embossed carrier tape (with dry pack)Tape

2500pcs

E2

The direction is the 1pin of product is at the upper left when you hold

()

reel on the left hand and you pull out the tape on the right hand

Reel

E2: Embossed tape and reel

(UCSP75M2/ UQFN48))

None: Tray

(VQFP48C)

1pin

Order quantity needs to be multiple of the minimum quantity.

∗

1pin

Order quantity needs to be multiple of the minimum quantity.

∗

Direction of feed

Direction of feed

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

16/17

2009.06 - Rev.A

BD6373GW, BD6873KN, BD6753KV

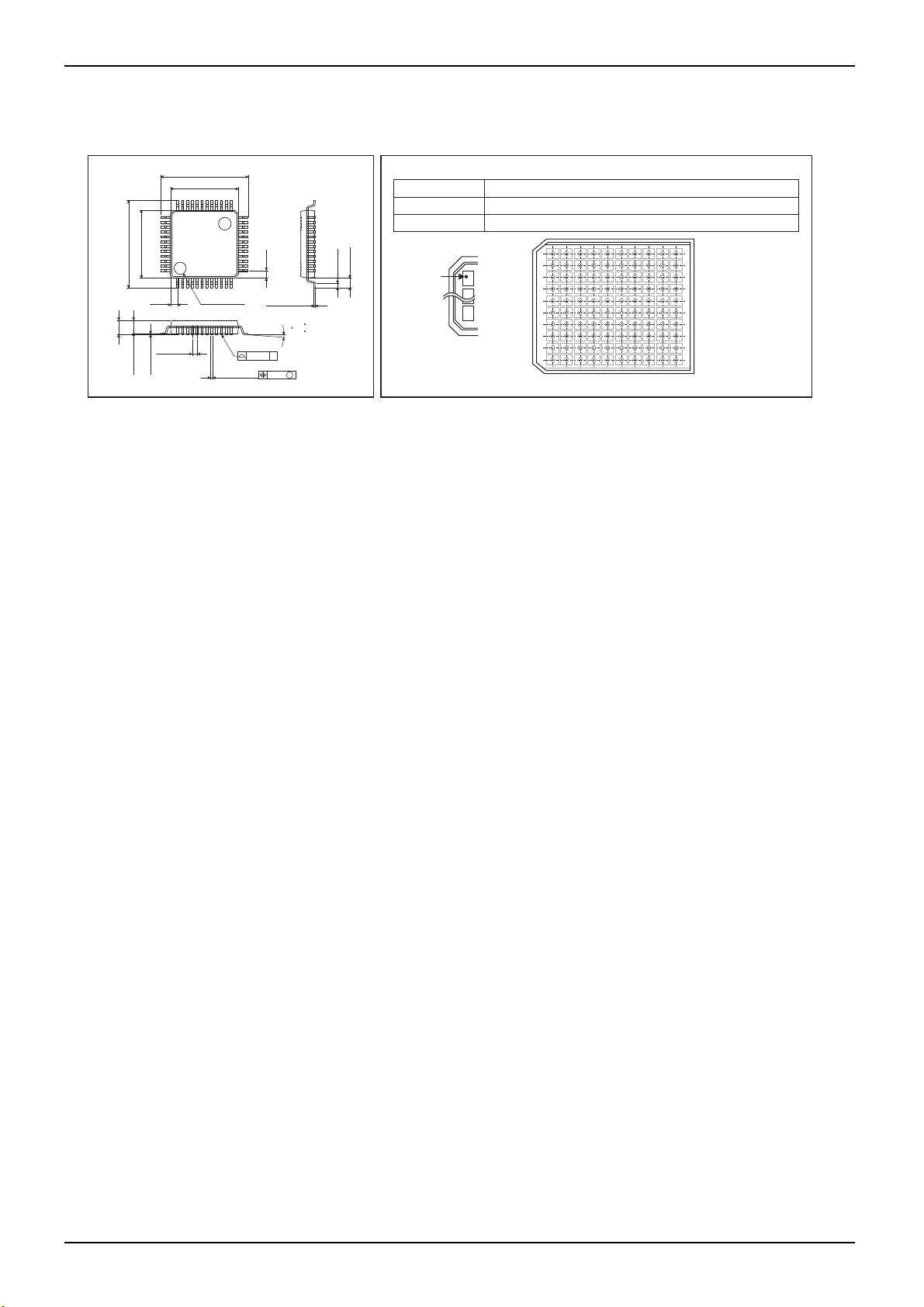

VQFP48C

7.0± 0.1

9.0± 0.2

1.6MAX

1.4± 0.05

37

48

0.75

0.1± 0.05

0.5± 0.1

36

9.0± 0.2

7.0± 0.1

1PIN MARK

0.22

25

24

0.75

13

121

+0.05

-

0.04

0.08 S

0.145

0.08

+0.05

-

0.03

4

M

+6

4

-

0.5±0.15

1.0±0.2

(Unit : mm)

<Tape and Reel information>

TrayContainer

Quantity

Direction of feed

1pin

1000pcs

Direction of product is fixed in a tray

Technical Note

Order quantity needs to be multiple of the minimum quantity.

∗

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

17/17

2009.06 - Rev.A

Notes

No copying or reproduction of this document, in part or in whole, is permitted without the

consent of ROHM Co.,Ltd.

The content specied herein is subject to change for improvement without notice.

The content specied herein is for the purpose of introducing ROHM's products (hereinaf ter

"Products"). If you wish to use any such Product, please be sure to refer to the specications,

which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein

illustrate the standard usage and operations of the Products. The peripheral conditions must

be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specied in this document.

However, should you incur any damage arising from any inaccuracy or misprint of such

information, ROHM shall bear no responsibility for such damage.

The technical information specied herein is intended only to show the typical functions of and

examples of application circuits for the Products. ROHM does not grant you, explicitly or

implicitly, any license to use or exercise intellectual property or other rights held by ROHM and

other par ties. ROHM shall bear no responsibility whatsoever for any dispute arising from the

use of such technical information.

Notice

The Products specied in this document are intended to be used with general-use electronic

equipment or devices (such as audio visual equipment, ofce-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specied in this document are not designed to be radiation tolerant.

While ROHM always makes ef forts to enhance the quality and reliability of its Products, a

Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard

against the possibility of physical injury, re or any other damage caused in the event of the

failure of any Product, such as derating, redundancy, re control and fail-safe designs. ROHM

shall bear no responsibility whatsoever for your use of any Product outside of the prescribed

scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or

system which requires an extremely high level of reliability the failure or malfunction of which

may result in a direct threat to human life or create a risk of human injur y (such as a medical

instrument, transportation equipment, aerospace machinery, nuclear-reactor controller,

fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of

any of the Products for the above special purposes. If a Product is intended to be used for any

such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specied herein that may

be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to

obtain a license or permit under the Law.

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact us.

ROHM Customer Support System

http://www.rohm.com/contact/

R0039

A

Loading...

Loading...