System Lens Driver Series for Mobile Phone Cameras

TECHNICAL NOTE

Parallel Interface Type

Lens Drivers for Stepping Motor

BD6360GUL

●Description

The BD6360GUL motor driver provides 2 Full-ON Drive H-bridge channel.

It is offered in an ultra small functional lens system for use in an auto focus or zoom system using a stepping motor.

And It integrates a power supply and wave-shaping circuit for the photo-interrupter necessary in order to determine the

location of the motor.

●Features

BD6360GUL

1) Ultra-small chip size package:2.1mm×2.1mm×0.55mm

2) Low ON-Resistance Power CMOS output:on high and low sides in total typ. 1.00Ω

3) ESD resistance (Human Body Model):8kV

4) Built-in voltage-regulator circuit for photo-interrupter and comparator circuits with hysteresis for photo-interrupter

output waveform

5) Input mode selection function (1.8V can be put into each control input terminal)

6) Built-in UVLO (Under Voltage Lockout Protection) function

7) Built-in TSD (Thermal Shut Down) circuit

8) Standby current consumption: 0μA Typ.

●Absolute Maximum Ratings (Ta=+25℃)

Parameter Symbol Limit Unit

Power supply voltage VCC -0.3~+6.5 V

Control input voltage VIN -0.3~VCC+0.3 V

Power dissipation Pd 730

Operating temperature range Topr -25~+85 °C

Junction temperature Tjmax +150 °C

Storage temperature Tstg -55~+150 °C

H-bridge output current Iout -500~+500

1

※

Reduced by 5.84mW/°C over 25°C, when mounted on a glass epoxy board (50mm 58mm 1.75mm; 8 layers)

2

※

Must not exceed Pd, ASO, or Tjmax of 150°C.

●Operating Conditions

Parameter Symbol Limit Unit

Power supply voltage VCC +2.3~+5.5 V

Control input voltage VIN 0~VCC V

H-bridge output current Iout -400~+400

3

※

Must not exceed Pd or ASO.

1

※

mW

2

※

mA/ch

3

※

mA/ch

Apr. 2008

●Electrical Characteristics

BD6360GUL Electrical Characteristics (Unless otherwise specified Ta=25°C, VCC=3.0V)

Parameter Symbol

Min. Typ.

Overall

Circuit current

during standby operation

ICCST - 0 5 μA

Circuit current ICC - 1.1 1.8 mA PS=3V with no signal, and no load

Control input (VIN=IN1A, IN1B, IN2A, IN2B, SEL, PS)

High level input voltage VINH 1.5 - VCC V

Low level input voltage VINL 0 - 0.5 V

High level input current IINH 15 30 60 μA VINH=3V, pull down resistance typ.100kΩ

Low level input current IINL -1 0 - μA VINL=0V

UVLO

UVLO voltage VUVLO 1.6 - 2.2 V

Photo-interrupter (PI) comparator

Input bias current

Output low level voltage

Output igh level voltage

IBIPI -3 0 3 μA

VLOPI 0 - 0.5 V

VHIPI VCC-0.5 - VCC V

Threshold voltage VTHPI 1.2 1.3 1.4 V Lo→Hi threshold voltage

Hysteresis voltage VHYSPI 200 300 400 mV Hi→Lo threshold voltage VTHPI-VHYSPI

Photo-interrupter (PI) regulator

ON-Resistance RONSW - - 10 Ω Io=-30mA

OFF current ILSW -1.0 0 - μA BIAS=0V

Full-ON Drive block (ch1 and ch2)

Output ON-Resistance RON - 1.00 1.25 Ω Io=+400mA on high and low sides in total

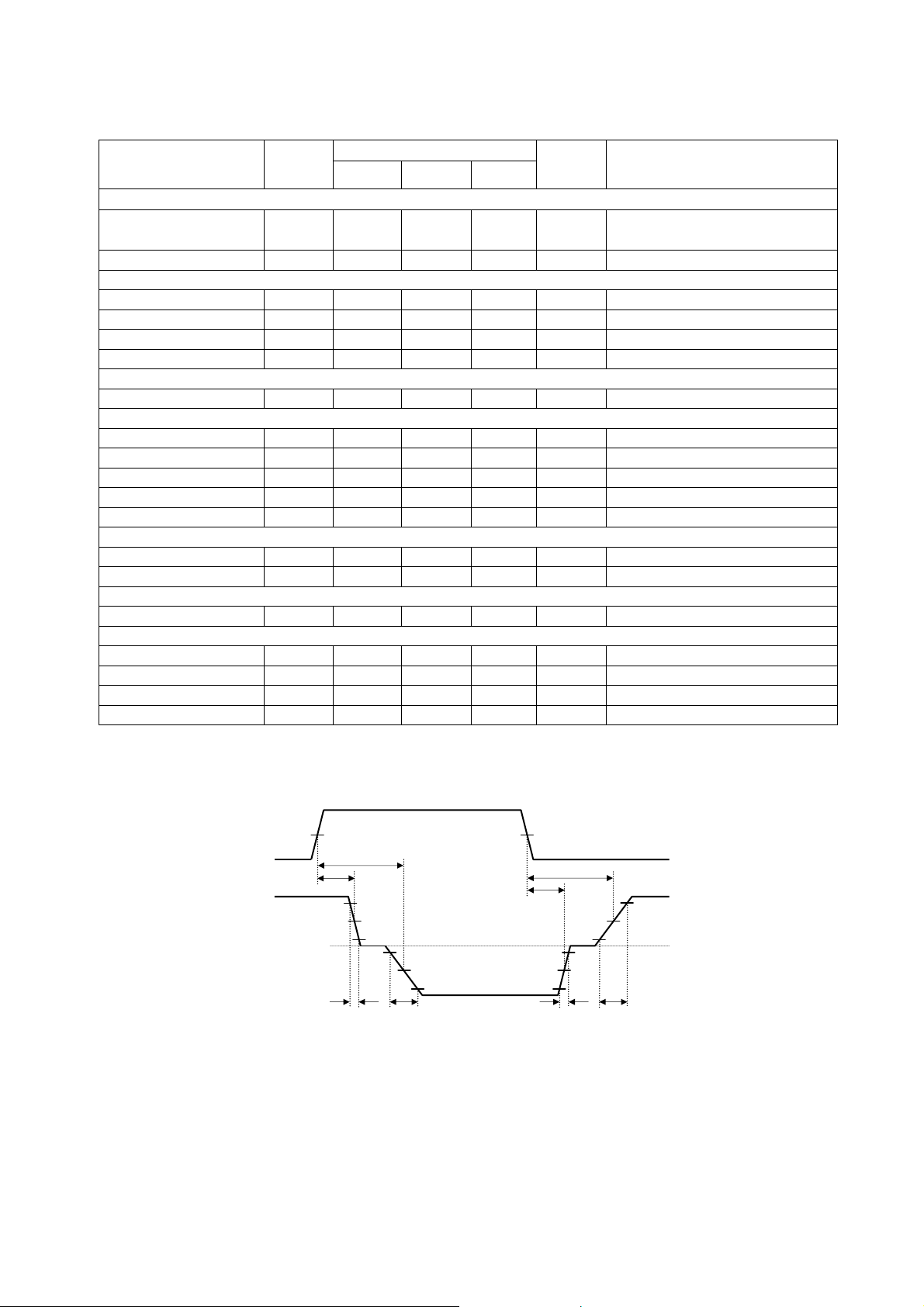

Output AC characteristic

Turn-on time - - - 2.0 μs Io=±400mA

Turn-off time toff - 0.08 0.5 μs Io=±400mA

Rise time tr 0.1 0.15 1.0 μs Io=±400mA

Fall time tf - 0.03 0.2 μs Io=±400mA

Limit

Max.

Unit Conditions

PS=0V

Io=+1mA

Io=-1mA

100%

50% 50%

VIN

Mottor current

ton

toff

90%

50% 50%

10%

-10%

-50% -50%

tf tr tf tr

-90% -90%

toff

-10%

ton

90%

10%

0%

100%

0%

-100%

Fig.1 BD6360GUL I/O Switching Waveform

2/8

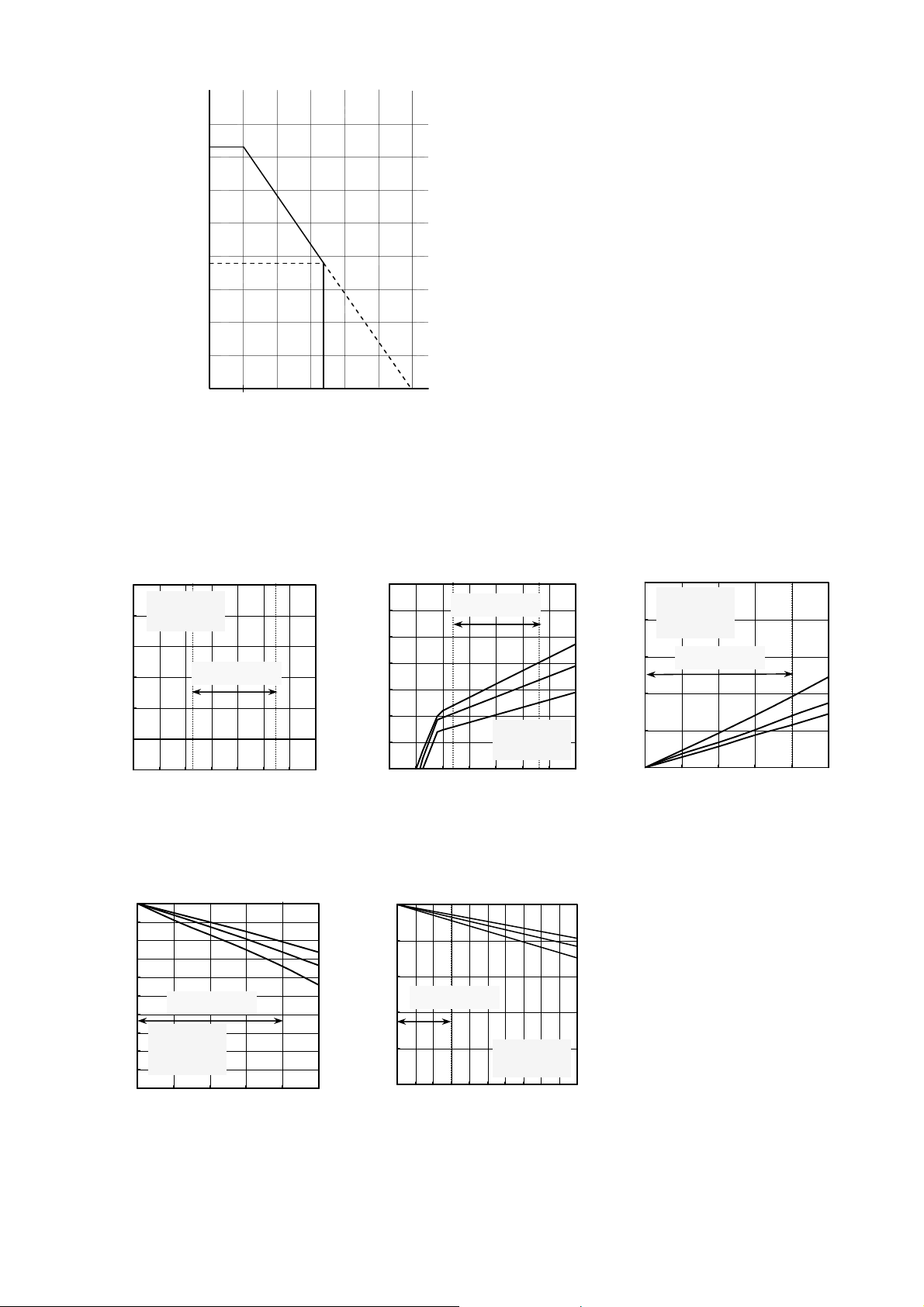

●Power Dissipation Reduction

730

380

Power Dissipation:Pd[mW]

0 25 85 150

Ambient Temperature:Ta [° C ]

Fig.2 BD6360GUL Power Dissipation Reduction

●Electrical Characteristic Diagrams

10.0

Top 85 ℃

Middle 25℃

8.0

Lower -25℃

6.0

4.0

2.0

Stand-by current, Icc [ μA]

0.0

Op. range (2.3V~5.5V)

-2.0

0.0 1.0 2.0 3.0 4. 0 5.0 6.0 7.0

Supply voltage, Vcc [V]

Fig.3 Standby Current

0.0

-0.1

-0.2

-0.3

-0.4

-0.5

-0.6

-0.7

Output voltage, VOUTH [V]

-0.8

-0.9

-1.0

Op. range (0~400mA)

Top -2 5℃

Middle 25℃

Lower 85℃

VM=VCC=3V

0.0 0.1 0.2 0.3 0.4 0.5

Output current, Io [A]

Fig.6 PMOS Output Voltage

3.5

3.0

2.5

2.0

1.5

1.0

Circuit current, Icc [mA]

0.5

0.0

0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0

Op. range (2.3V~5.5V)

Middle 25℃

Lower -25℃

Supply voltage, Vcc [V]

Top 85 ℃

Fig.4 Circuit Current

0.0

-0.1

-0.2

Op. range (0~30mA)

-0.3

Output voltage, VBIAS [V]

-0.4

-0.5

0 1020 3040 5060 7080 90100

Output current, Io [mA]

Top -2 5℃

Middle 25℃

Lower 85℃

0.5

Top 85 ℃

Middle 25℃

0.4

0.3

0.2

Output voltage, VOUTL [V]

0.1

0.0

Lower -25℃

VM=VCC=3V

Op. range (0~400mA)

0.0 0.1 0.2 0.3 0.4 0.5

Output current, Io [A]

Fig.5 NMOS Output Voltage

Fig.7 BIAS Output Voltage

3/8

●Block Diagram, Application Circuit Diagram, Pin Arrangement and Pin Function Table

_

p

1)BD6360GUL Block Diagram, Application Circuit Diagram, Pin Arrangement and Pin Function Table

Bypass filter Capacitor for power

supply input. See. P.6/8

Motor control input pin 1ch

Motor control input

in 2ch

Power -Saving

H: Active

L: Stand by

Input mode

selection

PS

IN1A

IN1B

IN2A

IN2B

SEL

4D

3D

2C

3B

3C

4C

Power Save

PS

Photo-interrupter regulator

Logic

VCC

0.1

BandGap

BIAS

~10uF

TSD & UVLO

Pre Driver

4B

VREF

VCC

BandGap

H bridge

H bridge

2A

3A 4A

CIN COUT

Input Comparator waveform

VCC

1ch FULL ON output pin

1D

OUT1A

OUT1B

1C

1B

OUT2A

OUT2B

1A

GND

2D

Output Comparator waveform

Fig.8 BD6360GUL Application Circuit Diagram

BD6360GUL Pin Function Table

1 2 3 4

A OUT2B CIN COUT BIAS

B OUT2A

INDEX

POST

IN2A VCC

C OUT1B IN1B IN2B SEL

D OUT1A GND IN1A PS

Fig.9 BD6360GUL Pin Arrangement (Top View)

No. Pin name Function

1A OUT2B H-bridge output pin ch2 B

2A CIN Comparator circuits with output waveform input pin

3A COUT Comparator circuits with output waveform output pin

4A BIAS Voltage-regulator for photo-interrupter

1B OUT2A H-bridge output pin ch2 A

2B

3B IN2A Control input pin ch2 A

4B VCC Power supply pin

1C OUT1B H-bridge output pin ch1 B

2C IN1B Control input pin ch1 B

3C IN2B Control input pin ch2 B

4C SEL Input mode selection pin ch1

1D OUT1A H-bridge output pin ch1 A

2D GND Ground pin

3D IN1A Control input pin ch1 A

4D PS Power-saving pin

4/8

M

2ch FULL ON output pin

●I/O Truth Table

BD6360GUL I/O Truth Table (x=1or2)

mode

PS SEL INxA INxB OUTxA OUTxB

INPUT OUTPUT

Output mode

L X Z Z Standby

EN/IN

L

H L H L Forward rotation

H H L H Reverse rotation

H

IN/IN H

L L Z Z Standby

L H L H Reverse rotation

H L H L Forward rotation

H H L L Brake

- L X X X Z Z Standby

At forward rotation, current flows from OUTxA to OUTxB. At reverse rotation, current flows form OUTxB to OUTxA.

L: Low, H: High, X: Don’t care, Z: Hi impedance

●Function Explanation

1) Power save function

When the L voltage is applied the PS pin, the IC’s inside circuit stop, and when 0V applied, the circuit current became

0μA(Typ.), especially.

When the IC drive, Serial input while the PS pin applied H voltage. (See the electrical characteristics; P.2/8)

2) Control Input Pin

IN1A, IN1B, IN2A, IN2B, SEL pins

The IN1A, IN1B, IN2A, IN2B are used to program and control the motor drive modes.

And, when the L voltage is applied to the SEL pin, the I/O logic can be set to EN(Enable)/IN mode, when the H voltage is

applied to the one, the I/O logic can be set to IN/IN mode. (See the electrical characteristics; P2/8, and the I/O Truth

Table; P5/8)

3) H-bridge on the output stage

Specify maximum current applied to the H-bridge within the operating range, in consideration of power dissipation.

(See the Operating Conditions; P.1/8)

4) Photo-interrupter regulator

Pay attention to the ON resistance with regard to the power source of the Photo interrupter.

(See the electrical characteristics; P.2/8)

5) The wave-shaping circuit convert

The wave-shaping circuit convert the distorted output signals from the photo-interrupter into clean rectangular waves,

then outputs them to the DSP.

A hysteresis function is included that blocks output signal chatter caused by input signal noise.

PS

CIN

COUT

Hi impedance

Fig.10 BD6360GUL Photo-interrupter I/O Timing Chart

H

L

1.3V

1.0V

VCC

0V

5/8

●I/O Circuit Diagram

A

A

PS, INxA, INxB, SEL OUTxA, OUTxB, GND

VCC

1kΩ

10kΩ

140kΩ

10kΩ

100kΩ

1kΩ

OUTx

10kΩ

PS

INx

INxB

SEL

CIN COUT

VCC

CIM

VCC

GND

VCC VCC

50Ω

Fig.11 BD6360GUL I/O Circuit Diagram(Resistance values are typical ones)

●Operation Notes

1) Absolute maximum ratings

Use of the IC in excess of absolute maximum ratings, such as the applied voltage (VCC) or operating temperature range

(Topr), may result in IC damage. Assumptions should not be made regarding the state of the IC (short mode or open

mode) when such damage is suffered. A physical safety measure, such as a fuse, should be implemented when using

the IC at times where the absolute maximum ratings may be exceeded.

2) Storage temperature range (Tstg)

As long as the IC is kept within this range, there should be no problems in the IC’s performance. Conversely, extreme

temperature changes may result in poor IC performance, even if the changes are within the above range.

3) Power supply and wiring

Be sure to connect the power terminals outside the IC. Do not leave them open. Because a return current is generated

by a counter electromotive force of the motor, take necessary measures such as putting a Capacitor between the power

source and the ground as a passageway for the regenerative current. Be sure to connect a Capacitor of proper

capacitance (0.1μF to 10μF) between the power source and the ground at the foot of the IC, and ensure that there is no

problem in properties of electrolytic Capacitors such as decrease in capacitance at low temperatures. When the

connected power source does not have enough current absorbing capability, there is a possibility that the voltage of the

power source line increases by the regenerative current an exceeds the absolute maximum rating of this product and

the peripheral circuits.

Therefore, be sure to take physical safety measures suc h as putting a zener diode for a voltage clamp between

the power source an the ground.

For this IC with a part consists of the CMOS block, it is possible that rush current may flow instantaneously due to the

unstable internal logic. Therefore, give special consideration to power coupling capacitance, width of power and ground

wirings, and routing of wiring.

4) Ground terminal and wiring

The potential at GND terminals should be made the lowest under any operating conditions. Ensure that there are no

terminals where the potentials are below the potential at GND terminals, including the transient phenomena. Use short

and thick power source and ground wirings to ensure low impedance.

5) Thermal design

Use a proper thermal design that allows for a sufficient margin of the power dissipation (Pd) at actual operating

conditions.

BIAS

VCC

BIAS

OUTxB

COUT

6/8

6) Pin short and wrong direction assembly of the device.

Use caution when positioning the IC for mounting on printed circuit boards. The IC may be damaged if there is any

connection error or if positive and ground power supply terminals are reversed. The IC may also be damaged if pins are

shorted together or are shorted to other circuit’s power lines.

7) Avoiding strong magnetic field

Malfunction may occur if the IC is used around a strong magnetic field.

8) ASO

Ensure that the output transistors of the motor driver are not driven under excess conditions of the absolute maximum

ratings and ASO.

9) TSD (Thermal Shut Down) circuit

If the junction temperature (Tjmax) reaches 175°C , the TSD circuit will operate, and the coil output circuit of the motor

will open. There is a temperature hysterics of approximately 25°C. The TSD circuit is designed only to shut off the IC in

order to prevent runaway thermal operation. It is not designed to protect the IC or guarantee its operation. The

performance of the IC’s characteristics is not guaranteed and it is recommended that the device is replaced after the

TSD is activated.

10) Testing an application board

When testing the IC on an application board, connecting a Capacitor to a pin with low impedance subjects the IC to

stress. Always discharge Capacitors after each process or step. Always turn the IC's power supply off before connecting

it to, or removing it from a jig or fixture, during the inspection process. Ground the IC during assembly steps as an

antistatic measure. Use similar precaution when transporting and storing the IC.

11) Regarding the input pin of the IC

+

This monolithic IC contains P

isolation and P substrate layers between adjacent elements to keep them isolated. P-N

junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode

or transistor. For example, the relation between each potential is as follows:

When GND > Pin A, the P-N junction operates as a parasitic diode.

When GND > Pin B, the P-N junction operates as a parasitic diode and transistor.

Parasitic elements can occur inevitably in the structure of the IC. The operation of parasitic elements can result in

mutual interference among circuits, operational faults, or physical damage. Accordingly, methods by which parasitic

elements operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin, should not

be used.

Pin A

N

P+ P

P

Parasitic element

GND

Resistor Transistor (NPN)

Pin A

+

N N

P substrate

Parasitic

element

Fig.12 Example of Simple IC Architecture

Pin B

N

Parasitic elements

C

P+

B

N

E

P

P substrate

GND

P+

N

GND

Pin B

B C

E

Parasitic

elements

GND

Other adjacent elements

7/8

●Selecting a Model Name when Ordering

(

B D

6 3 6 0 G

U

L

-

ROHM model name Part number Package type Taping type

VCSP50L2

< Dimension >

6360 : FULL ON 2ch

GUL : VCSP50L2

< Tape and Reel information >

Tape

Quantity

Direction

of feed

Embossed carrier tape (with dry pack)

3000pcs

E2

(The direction is the 1pin of product is at the upper left when you hold

reel on the left hand and you pull out the tape on the right hand.)

E2 : Reel-wound embossed taping

1234 1234 1234 1234 1234 1234

Unit:mm)

Reel

※When you order , please order in times the amount of package quantity.

1Pin

E 2

Direction of feed

8/8

Catalog No.08T102A '08.4 ROHM ©

Loading...

Loading...