Page 1

A

LED Drivers for LCD BackLights

Multifunction Backlight LED Driver

for Small LCD Panels (Charge Pump Type)

BD6083GUL

●Description

BD6083GUL is “Intelligent LED Driver” that is the most suitable for the cellular phone.

It has 3 - 6LED driver and output variable LDO4ch for LCD Backlight.

It has ALC function that is “Low Power Consumption System” realized.

It can be developed widely from the high End model to the Low End model.

As it has charge pump circuit for DCDC, it is no need to use coils, and it contributes to small space.

VCSP50L3 (3.15mm x 3.15mm 0.5mm pitch)

It adopts the very thin CSP package that is the most suitable for the slim phone.

●Features

1) Total 3 - 6LEDs driver for LCD Backlight

・It has 4LEDs (it can select 4LED or 3LED) for exclusire use of Main and 2LEDs which can chose independent

control or a main allotment by resister setting.

・Main Group” can be controlled by Auto Luminous Control (ALC) system.

“Main Group” can be controlled by external PWM signal.

・ON/ Off and a setup of LED current are possible at the time of the independent control by the independence.

2) Ambient Light sensor interface

・Incorporates various functions such as a sensor bias adjustment function, an ADC with an average filter, a gainoffset

adjustment function and an LOG conversion function so that options can be increased for illumination intensity

sensors (Photo Diode, Photo Transistor, Photo IC (Linear/LOG)).

・Incorporates an auto gain switching function for suppressing an illumination intensity sensor current

at high illumination intensity and improving sensitivity at low illumination intensity

・Capable of customizing an LED current value according to a table setting.

・Slope control loading and an independent control change are possible.

3) Charge Pump DC/DC for LED driver

・It has x1/x1.5/ x2 mode that will be selected automatically.

・The most suitable voltage up magnification is controlled automatically by LED port voltage.

・Soft start

4) 4ch Series Regulator (LDO)

・It has selectable output voltage by the register.(16 steps)

LDO1, LDO2, LDO3, LDO4: Iomax=150mA

5) Thermal shutdown

2

6) I

●Absolute Maximum Ratings (Ta=25

Maximum Voltage VMAX 7 V

Power Dissipation Pd 1280

Operating Temperature Range Topr -30 ~ +85 ℃

Storage Temperature Range Tstg -55 ~ +150 ℃

●Operating Conditions (VBAT≥VIO, Ta=-30~85

VBAT Input Voltage VBAT 2.7 ~ 5.5 V

VIO Pin Voltage VIO 1.65 ~ 3.3 V

C BUS FS mode (max 400 kHz) Compatibility

(Note) Power dissipation deleting is 10.24mW/ ℃ , when it’s used in over 25 ℃.

(It’s deleting is on the board that is ROHM’s standard)

functions、Over voltage protection (Auto-return type),Over current protection (Auto-return type) loading

℃)

Parameter Symbol Ratings Unit

(Note)

mW

℃)

Parameter Symbol Limits Unit

No.10040EAT16

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

1/45

2010.07 - Rev.

Page 2

A

BD6083GUL

●Electrical Characteristics (Unless otherwise specified, Ta=25℃, VBAT=3.6V, VIO=1.8V)

Parameter Symbol

Min. Typ. Max.

Limits

Unit Conditions

【Circuit Current】

VBAT Circuit Current 1 IBAT1 - 0.1 3.0 μA RESETB=0V, VIO= 0V

VBAT Circuit Current 2 IBAT2 - 0.5 3.0 μA RESETB=0V, VIO=1.8V

Technical Note

VBAT Circuit Current 3 IBAT3 - 61 65 mA

VBAT Circuit Current 4 IBAT4 - 92 102 mA

VBAT Circuit Current 5 IBAT5 - 123 140 mA

DC/DC x1 mode, Io=60mA

VBAT=4.0V

DC/DC x1.5 mode, Io=60mA

VBAT=3.6V

DC/DC x2 mode, Io=60mA

VBAT=2.7V

ALC Operating

VBAT Circuit Current 6 IBAT6 - 0.25 1.0 mA

ALCEN=1, AD cycle=0.5s setting

Except sensor current

VBAT Circuit Current 7 IBAT7 - 90 150 μA LDO1,2=ON, I

VBAT Circuit Current 8 IBAT8 - 90 150 μA LDO3,4=ON, I

【LED Driver】

LED Current Step (Setup) ILEDSTP1 128 Step LED1~6

LED Current Step (At slope) ILEDSTP2 256 Step LED1~6

LED Maximum Setup Current IMAXWLED - 25.6 - mA LED1~6

LED Current Accuracy IWLED -7% 15 +7% mA I

LED Current Matching ILEDMT - - 4 %

=15mA setting, VLED=1.0V

LED

Between LED1~6 at VLED=1.0V,

ILED=15mA

LED OFF Leak Current ILKLED - - 1.0 μA VLED=4.5V

LDO

LDO

=0mA

=0mA

【DC/DC(Charge Pump)】

Output Voltage VoCP - Vf+0.2 Vf+0.25 V Vf is forward direction of LED

Drive Ability IOUT - - 150 mA VBAT≥3.2V, VOUT=3.9V

Switching Frequency fosc 0.8 1.0 1.2 MHz

Over Voltage Protection

Detect Voltage

Over Current Protection

Detect Current

OVP - 5.6 - V

OCP - 250 375 mA VOUT=0V

【Sensor Interface】

SBIAS

Output Voltage

SBIAS

Maximum Output Current

SBIAS

Discharge Resister at OFF

SSENS Input Range VISS 0 -

VoS 2.85 3.0 3.15 V Io=200µA

IomaxS 30 - - mA

ROFFS - 1.0 1.5 kΩ

VoS×

255/256

V

ADC Resolution ADRES 8 bit

ADC Integral Calculus

Non-linearity

ADC Differential Calculus

Non-linearity

ADINL -3 - +3 LSB

ADDNL -1 - +1 LSB

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

2/45

2010.07 - Rev.

Page 3

A

BD6083GUL

●Electrical Characteristics (Unless otherwise specified, Ta=25℃, VBAT=3.6V, VIO=1.8V)

Parameter Symbol

【Regulator (LDO1)】

Output Voltage Vo1

Output Current Io1 - - 150 mA Vo=1.8V

Dropout Voltage Vsat1 - 0.2 0.3 V VBAT=2.5V, Io=150mA, Vo=2.8V

Load Stability ΔVo11 - 10 60 mV Io=1~150mA, Vo=1.8V

Input Voltage Stability ΔVo12 - 10 60 mV VBAT=3.4~4.5V, Io=50mA, Vo=1.8V

Ripple Rejection Ratio RR1 - 65 - dB

Short Circuit Current Limit Ilim1 - 200 400 mA Vo=0V

Discharge Resister at OFF ROFF1 - 1.0 1.5 kΩ

【Regulator (LDO2)】

Output Voltage Vo2

Output Current Io2 - - 150 mA Vo=2.5V

Dropout Voltage Vsat2 - 0.2 0.3 V VBAT=2.5V, Io=150mA, Vo=2.8V

Load Stability Δvo21 - 10 60 mV Io=1~150mA, Vo=2.5V

Input Voltage Stability Δvo22 - 10 60 mV VBAT=3.4~4.5V, Io=50mA, Vo=2.5V

Ripple Rejection Ratio RR2 - 65 - dB

Short Circuit Current Limit Ilim2 - 200 400 mA Vo=0V

Discharge Resister at OFF ROFF2 - 1.0 1.5 kΩ

Min. Typ. Max.

1.164 1.20 1.236 V Io=50mA

1.261 1.30 1.339 V Io=50mA

1.455 1.50 1.545 V Io=50mA

1.552 1.60 1.648 V Io=50mA

1.746 1.80 1.854 V Io=50mA <Initial Voltage>

2.134 2.20 2.266 V Io=50mA

2.328 2.40 2.472 V Io=50mA

2.425 2.50 2.575 V Io=50mA

2.522 2.60 2.678 V Io=50mA

2.619 2.70 2.781 V Io=50mA

2.716 2.80 2.884 V Io=50mA

2.813 2.90 2.987 V Io=50mA

2.910 3.00 3.090 V Io=50mA

3.007 3.10 3.193 V Io=50mA

3.104 3.20 3.296 V Io=50mA

3.201 3.30 3.399 V Io=50mA

1.164 1.20 1.236 V Io=50mA

1.261 1.30 1.339 V Io=50mA

1.455 1.50 1.545 V Io=50mA

1.552 1.60 1.648 V Io=50mA

1.746 1.80 1.854 V Io=50mA

2.134 2.20 2.266 V Io=50mA

2.328 2.40 2.472 V Io=50mA

2.425 2.50 2.575 V Io=50mA <Initial Voltage>

2.522 2.60 2.678 V Io=50mA

2.619 2.70 2.781 V Io=50mA

2.716 2.80 2.884 V Io=50mA

2.813 2.90 2.987 V Io=50mA

2.910 3.00 3.090 V Io=50mA

3.007 3.10 3.193 V Io=50mA

3.104 3.20 3.296 V Io=50mA

3.201 3.30 3.399 V Io=50mA

Limits

Unit Condition

f=100Hz, Vin=200mVp-p, Vo=1.2V

Io=50mA, BW=20Hz~20kHz

f=100Hz, Vin=200mVp-p, Vo=1.2V

Io=50mA, BW=20Hz~20kHz

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

3/45

2010.07 - Rev.

Page 4

A

BD6083GUL

●Electrical Characteristics (Unless otherwise specified, Ta=25℃, VBAT=3.6V, VIO=1.8V)

Parameter Symbol

【Regulator (LDO3)】

Output Voltage Vo3

Output Current Io3 - - 150 mA Vo=1.8V

Dropout Voltage Vsat3 - 0.2 0.3 V VBAT=2.5V, Io=150mA, Vo=2.8V

Load Stability ΔVo31 - 10 60 mV Io=1~150mA, Vo=1.8V

Input Voltage Stability ΔVo32 - 10 60 mV VBAT=3.4~4.5V, Io=50mA, Vo=1.8V

Ripple Rejection Ratio RR3 - 65 - dB

Short Circuit Current Limit Ilim3 - 200 400 mA Vo=0V

Discharge Resister at OFF ROFF3 - 1.0 1.5 kΩ

【Regulator (LDO4)】

Output Voltage Vo4

Output Current Io4 - - 150 mA Vo=2.8V

Dropout Voltage Vsat4 - 0.2 0.3 V VBAT=2.5V, Io=150mA, Vo=2.8V

Load Stability ΔVo41 - 10 60 mV Io=1~150mA, Vo=2.8V

Input Voltage Stability ΔVo42 - 10 60 mV VBAT=3.4~4.5V, Io=50mA, Vo=2.8V

Ripple Rejection Ratio RR4 - 65 - dB

Short Circuit Current Limit Ilim4 - 200 400 mA Vo=0V

Discharge Resister at OFF ROFF4 - 1.0 1.5 kΩ

Min. Typ. Max.

1.164 1.20 1.236 V Io=50mA

1.261 1.30 1.339 V Io=50mA

1.455 1.50 1.545 V Io=50mA

1.552 1.60 1.648 V Io=50mA

1.746 1.80 1.854 V Io=50mA <Initial Voltage>

2.134 2.20 2.266 V Io=50mA

2.328 2.40 2.472 V Io=50mA

2.425 2.50 2.575 V Io=50mA

2.522 2.60 2.678 V Io=50mA

2.619 2.70 2.781 V Io=50mA

2.716 2.80 2.884 V Io=50mA

2.813 2.90 2.987 V Io=50mA

2.910 3.00 3.090 V Io=50mA

3.007 3.10 3.193 V Io=50mA

3.104 3.20 3.296 V Io=50mA

3.201 3.30 3.399 V Io=50mA

1.164 1.20 1.236 V Io=50mA

1.261 1.30 1.339 V Io=50mA

1.455 1.50 1.545 V Io=50mA

1.552 1.60 1.648 V Io=50mA

1.746 1.80 1.854 V Io=50mA

2.134 2.20 2.266 V Io=50mA

2.328 2.40 2.472 V Io=50mA

2.425 2.50 2.575 V Io=50mA

2.522 2.60 2.678 V Io=50mA

2.619 2.70 2.781 V Io=50mA

2.716 2.80 2.884 V Io=50mA <Initial Voltage>

2.813 2.90 2.987 V Io=50mA

2.910 3.00 3.090 V Io=50mA

3.007 3.10 3.193 V Io=50mA

3.104 3.20 3.296 V Io=50mA

3.201 3.30 3.399 V Io=50mA

Limits

Unit Condition

f=100Hz, Vin=200mVp-p, Vo=1.2V

Io=50mA, BW=20Hz~20kHz

f=100Hz, Vin=200mVp-p, Vo=1.2V

Io=50mA, BW=20Hz~20kHz

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

4/45

2010.07 - Rev.

Page 5

A

BD6083GUL

Technical Note

●Electrical Characteristics (Unless otherwise specified, Ta=25℃, VBAT=3.6V, VIO=1.8V)

Parameter Symbol

Min. Typ. Max.

Limits

Unit Condition

【SDA, SCL】 (I2C Interface)

L Level Input Voltage VILI -0.3 - 0.25 ×VIO V

H Level Input Voltage VIHI 0.75 ×VIO - VBAT+0.3 V

Hysteresis of

Schmitt trigger Input

VhysI 0.05 ×VIO - - V

L Level Output Voltage VOLI 0 - 0.3 V SDA Pin, IOL=3 mA

Input Current linI - - 1 μA Input Voltage= 0.1×VIO ~ 0.9×VIO

【RESETB】 (CMOS Input Pin)

L Level Input Voltage VILR -0.3 - 0.25 ×VIO V

H Level Input Voltage VIHR 0.75 ×VIO - VBAT+0.3 V

Input Current IinR - - 1 μA Input Voltage = 0.1×VIO ~ 0.9×VIO

【WPWMIN】 (NMOS Input Pin)

L Level Input Voltage VILA -0.3 - 0.3 V

H Level Input Voltage VIHA 1.4 - VBAT+0.3 V

Input Current IinA - 3.6 10 μA Input Voltage = 1.8V

PWM Input Minimum

High Pulse Width

PWmin 250 - - μs WPWMIN Pin

【GC1, GC2】 (Sensor Gain Control CMOS Output Pin)

L Level Output Voltage VOLS - - 0.2 V IOL=1mA

H Level Output Voltage VOHS VoS-0.2 - - V IOH=1mA

●Power Dissipation (On the ROHM’s standard board)

1.6

1.4

1280mW

1.2

W)

(

1.0

0.8

0.6

0.4

Power Dissipation Pd

0.2

0.0

0 25 50 75 100 125 150

Ta(℃)

Information of the ROHM’s standard board

Material: glass-epoxy

Size : 50mm×58mm×1.75mm(8

th

layer)

Wiring pattern figure Refer to after page.

Fig.1 Power Dissipation

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

5/45

2010.07 - Rev.

Page 6

A

BD6083GUL

A

●Block Diagram / Application Circuit Example 1

6LED + ALC +PWM

1μF/10V

Technical Note

1μF/10V

C2N

OVP

C2P

TSD

CPGND

C6B5

A5

VOUT

D6

1μF/10V

LED1

A2

LED2

B1

LED3

B2

LED4

C2

LED5

D1

LED6

D2

LEDGND

C1

6LED

Main Back Light

IREF

LDO1

Vo Selectable

VREF

A3

GND1

Io=150mA

LDO2

Vo Selectable

Io=150mA

LDO3

Vo Selectable

Io=150mA

LDO4

Vo Selectable

Io=150mA

LDO1O

E6

LDO2O

E5

LDO3O

E4

LDO4O

E3

1μF/6.3V

1μF/6.3V

1μF/6.3V

1μF/6.3V

From CPU

From LCM

VIO Voltage

<ALS>

GC1

BH1621FVC

GC2

VBAT

GND

VBATCP

2.2µF/10V

RESETB

WPWMIN

SBIAS

VCC

1μF/6.3V

IOUT

VBAT1

VBAT2

VIO

SCL

SD

SSENS

SGND

GC2

GC1

C1P

C1N

A4

C5

B6

F4

F5

Charge Pump

Mode Control

D5

B4

C4

Level

D4

B3

F3

E1

F2

D3

E2

I/O

Sensor

I/F

Shift

A6 F1

T2

Charge Pump

x1 / x1.5 / x2

I2C interface

Digital Control

LED

control

(ALC)

A1 F6

T4

T3

T1

(Open)

(Open)

LED terminal voltage feedback

Fig.2 Block Diagram / Application Circuit Example 1

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

6/45

2010.07 - Rev.

Page 7

A

BD6083GUL

A

●Block Diagram / Application Circuit Example 2

5LED + ALC +PWM

1μF/10V

Technical Note

1μF/10V

From CPU

From LCM

VIO Voltage

<ALS>

GC1

BH1621FVC

GC2

VBAT

GND

VBATCP

2.2µF/10V

RESETB

WPWMIN

SBIAS

VCC

1μF/6.3V

IOUT

VBAT1

VBAT2

VIO

SCL

SD

SSENS

SGND

GC2

GC1

C2N

OVP

C2P

TSD

CPGND

C6B5

A5

VOUT

D6

1μF/10V

LED1

A2

LED2

B1

LED3

B2

LED4

C2

LED5

D1

LED6

D2

LEDGND

C1

5LED

Main Back Light

IREF

LDO1

Vo Selectable

VREF

A3

GND1

Io=150mA

LDO2

Vo Selectable

Io=150mA

LDO3

Vo Selectable

Io=150mA

LDO4

Vo Selectable

Io=150mA

LDO1O

E6

LDO2O

E5

LDO3O

E4

LDO4O

E3

1μF/6.3V

1μF/6.3V

1μF/6.3V

1μF/6.3V

C1P

C1N

A4

C5

B6

F4

F5

Charge Pump

Mode Control

D5

B4

C4

Level

D4

B3

F3

E1

F2

D3

E2

I/O

Sensor

I/F

Shift

A6 F1

T2

Charge Pump

x1 / x1.5 / x2

I2C interface

Digital Control

LED

control

(ALC)

A1 F6

T4

T3

T1

(Open)

(Open)

LED terminal voltage feedback

Fig.3 Block Diagram / Application Circuit Example 2

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

7/45

2010.07 - Rev.

Page 8

A

BD6083GUL

A

●Block Diagram / Application Circuit Example 3

4LED + 2LED + ALC +PWM

1μF/10V

Technical Note

1μF/10V

C2N

OVP

C2P

TSD

CPGND

C6B5

A5

VOUT

D6

1μF/10V

LED1

A2

LED2

B1

LED3

B2

LED4

C2

LED5

D1

LED6

D2

LEDGND

C1

6LED

Main Back Light

2LED

Sub Back Light

or

Key Back Light

IREF

LDO1

Vo Selectable

VREF

A3

GND1

Io=150mA

LDO2

Vo Selectable

Io=150mA

LDO3

Vo Selectable

Io=150mA

LDO4

Vo Selectable

Io=150mA

LDO1O

E6

LDO2O

E5

LDO3O

E4

LDO4O

E3

1μF/6.3V

1μF/6.3V

1μF/6.3V

1μF/6.3V

From CPU

From LCM

VIO Voltage

<ALS>

GC1

BH1621FVC

GC2

VBAT

GND

VBATCP

2.2µF/10V

RESETB

WPWMIN

SBIAS

VCC

1μF/6.3V

IOUT

VBAT1

VBAT2

VIO

SCL

SD

SSENS

SGND

GC2

GC1

C1P

C1N

A4

C5

B6

F4

F5

Charge Pump

Mode Control

D5

B4

C4

Level

D4

B3

F3

E1

F2

D3

E2

I/O

Sensor

I/F

Shift

A6 F1

T2

Charge Pump

x1 / x1.5 / x2

I2C interface

Digital Control

LED

control

(ALC)

A1 F6

T4

T3

T1

(Open)

(Open)

LED terminal voltage feedback

Fig.4 Block Diagram / Application Circuit Example 3

.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

8/45

2010.07 - Rev.

Page 9

A

BD6083GUL

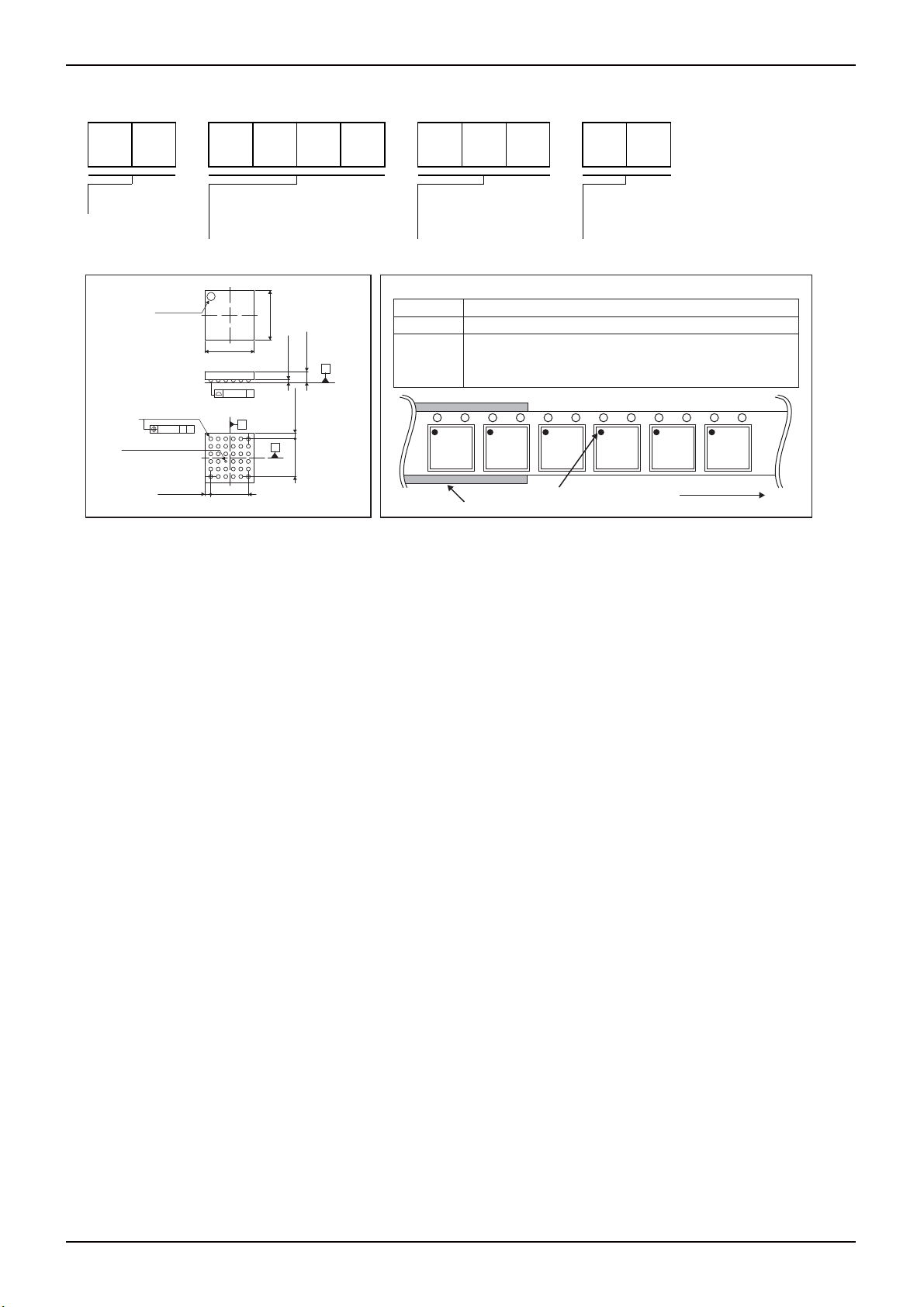

●Pin Arrangement [Bottom View]

F T4 SGND SBIAS VBAT1 VBAT2 T3

E SSENS GC1 LDO4O LDO3O LDO2O LDO1O

D LED5 LED6 GC2 SDA VIO VOUT

Technical Note

index

C LEDGND LED4

B LED2 LED3 WPWMIN RESETB C2N VBATCP

A T1 LED1 GND1 C1N CPGND T2

1 2 3 4 5 6

Total 35 Ball

SCL C1P C2P

Fig.5 Pin Arrangement

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

9/45

2010.07 - Rev.

Page 10

A

BD6083GUL

●Package Outline

VCSP50L3 CSP small package

SIZE : 3.15mm x 3.15mm (A difference in public:X,Y Both ±0.05mm)

Height : 0.55mm max

A ball pitch : 0.5 mm

Fig.6 Package Outline

Technical Note

(Unit : mm)

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

10/45

2010.07 - Rev.

Page 11

A

BD6083GUL

●Pin Functions

No Ball No. Pin Name I/O

1 B6 VBATCP - - GND Battery is connected A

2 F4 VBAT1 - - GND Battery is connected A

3 F5 VBAT2 - - GND Battery is connected A

4 A1 T1 O VBAT GND Test Output Pin(Open) N

5 A6 T2 I VBAT GND Test Input Pin (short to Ground) S

6 F6 T3 O VBAT GND Test Output Pin(Open) M

7 F1 T4 I VBAT GND Test Input Pin (short to Ground) S

8 D5 VIO - VBAT GND I/O Power supply is connected C

9 B4 RESETB I VBAT GND Reset input (L: reset, H: reset cancel) H

10 D4 SDA I/O VBAT GND I2C data input / output I

11 C4 SCL I VBAT GND I2C clock input H

12 A5 CPGND - VBAT - Ground B

13 A3 GND1 - VBAT - Ground B

14 C1 LEDGND - VBAT - Ground B

15 A4 C1N I/O VBAT GND Charge Pump capacitor is connected F

16 C5 C1P I/O - GND Charge Pump capacitor is connected G

17 B5 C2N I/O VBAT GND Charge Pump capacitor is connected F

18 C6 C2P I/O - GND Charge Pump capacitor is connected G

19 D6 VOUT O - GND Charge Pump output pin A

20 A2 LED1 I - GND LED is connected 1 for LCD Back Light E

21 B1 LED2 I - GND LED is connected 2 for LCD Back Light E

22 B2 LED3 I - GND LED is connected 3 for LCD Back Light E

23 C2 LED4 I - GND LED is connected 4 for LCD Back Light E

24 D1 LED5 I - GND LED is connected 5 for LCD Back Light E

25 D2 LED6 I - GND LED is connected 6 for LCD Back Light E

26 F3 SBIAS O VBAT GND Bias output for the Ambient Light Sensor Q

27 E1 SSENS I VBAT GND Ambient Light Sensor input N

28 E2 GC1 O VBAT GND Ambient Light Sensor gain control output 1 X

29 D3 GC2 O VBAT GND Ambient Light Sensor gain control output 2 X

30 F2 SGND - VBAT - Ground B

31 B3 WPWMIN I VBAT GND External PWM input for Back Light * L

32 E6 LDO1O O VBAT GND LDO1 output pin Q

33 E5 LDO2O O VBAT GND LDO2 output pin Q

34 E4 LDO3O O VBAT GND LDO3 output pin Q

35 E3 LDO4O O VBAT GND LDO4 output pin Q

* A setup of a register is separately necessary to make it effective.

ESD Diode

For Power For Ground

Functions

Technical Note

Equivalent

Circuit

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

11/45

2010.07 - Rev.

Page 12

A

BD6083GUL

●Equivalent Circuit

A VBATB E

C

VBAT

Technical Note

F

VBAT

J

Q

VBAT VBAT

G

VIO VBAT

R

VBATVBAT L

VBATVBAT

H

M

VBAT VBAT

S

VIOVBAT

VBATVBAT

I

N

U

VIO VBAT

VBAT

VBAT VBAT V

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

VBAT W

VIO

Fig.7 Equivalent Circuit

X

VoS VBAT

12/45

Y

VIO VBAT

2010.07 - Rev.

Page 13

A

BD6083GUL

Technical Note

●I2C BUS Format

The writing/reading operation is based on the I

2

C slave standard.

・Slave address

A7 A6 A5 A4 A3 A2 A1 R/W

1 1 1 0 1 1 0 1/0

・Bit Transfer

SCL transfers 1-bit data during H. SCL cannot change signal of SDA during H at the time of bit transfer. If SDA changes

while SCL is H, START conditions or STOP conditions will occur and it will be interpreted as a control signal.

SDA

SCL

SDA a state of stability

Data are effective

SDA

:

It can change

Fig.8

・START and STOP condition

When SDA and SCL are H, data is not transferred on the I

2

C- bus. This condition indicates, if SDA changes from H to L

while SCL has been H, it will become START (S) conditions, and an access start, if SDA changes from L to H while SCL

has been H, it will become STOP (P) conditions and an access end.

SDA

SCL

S P

START condition

STOP condition

Fig.9

・Acknowledge

It transfers data 8 bits each after the occurrence of START condition. A transmitter opens SDA after transfer 8bits data, and

a receiver returns the acknowledge signal by setting SDA to L.

DATA OUTPUT

BY TRANSMITTER

DATA OUTPUT

BY RECEIVER

SCL

START condition

S

12 89

not acknowledge

acknowledge

clock pulse for

acknowledgement

Fig.10

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

13/45

2010.07 - Rev.

Page 14

A

BD6083GUL

AAA

A

A

A

A

A

A

A2A1A

A

A

A

A

A

A

A

A A

A

A

A6A5A4A3A2A1A

A

A

A

A

Technical Note

・Writing protocol

A register address is transferred by the next 1 byte that transferred the slave address and the write-in command. The 3rd

byte writes data in the internal register written in by the 2nd byte, and after 4th byte or, the increment of register address is

carried out automatically. However, when a register address turns into the last address, it is set to 00h by the next

transmission. After the transmission end, the increment of the address is carried out.

*1 *1

X X X X X X X

S

7

6

R/W=0(write)

from master to slave

from slave to master

register addressslave address

5

4

3

D7D6 D5 D4 D3D2 D1 D0 D7 D6D5 D4 D3 D2 D1 D0

00

DATA

register address

increment

=acknowledge(SDA LOW)

=not acknowledge(SDA HIGH)

S=START condition

P=STOP condition

*1: Write Timing

DATA

register address

increment

P

Fig.11

・Reading protocol

It reads from the next byte after writing a slave address and R/W bit. The register to read considers as the following

address accessed at the end, and the data of the address that carried out the increment is read after it. If an address turns

into the last address, the next byte will read out 00h. After the transmission end, the increment of the address is carried

out.

X X X X X X X

R/W=1(read)

from master to slave

from slave to master

P

DATA

register address

increment

=acknowledge(SDA LOW)

=not acknowledge(SDA HIGH)

S=START condition

P=STOP condition

DATA slave address

register address

increment

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

1 S

Fig.12

・Multiple reading protocols

After specifying an internal address, it reads by repeated START condition and changing the data transfer direction. The

data of the address that carried out the increment is read after it. If an address turns into the last address, the next byte will

read out 00h. After the transmission end, the increment of the address is carried out.

S

slave address

R/W=0(write)

from master to slave

from slave to master

0

7

register address

D7 D6 D5 D4 D3D2D1D0 D7 D6 D5 D4 D3 D2 D1D0

DATA DATA

register address

increment

Sr 1

0X X X X X X X

X X X X X X X

slave address

=acknowledge(SDA LOW)

=not acknowledge(SDA HIGH)

S=START condition

P=STOP condition

Sr=repeated START condition

R/W=1(read)

P

register address

increment

Fig.13

As for reading protocol and multiple reading protocols, please do A(not acknowledge) after doing the final reading

operation. It stops with read when ending by A(acknowledge), and SDA stops in the state of Low when the reading data of

that time is 0. However, this state returns usually when SCL is moved, data is read, and A (not acknowledge) is done.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

14/45

2010.07 - Rev.

Page 15

A

BD6083GUL

S

Technical Note

●Timing Diagram

SDA

BUF

t

S

CL

SU;DAT

t

LOW

t

HD;STA

t

HD;DAT

S Sr P

t

t HIGH

HD;STA

t

SU;STA

t

SU;STO

t

Fig.14

●Electrical Characteristics(Unless otherwise specified, Ta=25

Parameter Symbol

2

【I

C BUS format】

o

C, VBAT=3.6V, VIO=1.8V)

Standard-mode Fast-mode

Min. Typ. Max. Min. Typ. Max.

SCL clock frequency fSCL 0 - 100 0 - 400 kHz

LOW period of the SCL clock tLOW 4.7 - - 1.3 - - μs

HIGH period of the SCL clock tHIGH 4.0 - - 0.6 - - μs

Unit

Hold time (repeated) START condition

After this period, the first clock is generated

t

HD;STA 4.0 - - 0.6 - - μs

Set-up time for a repeated START condition tSU;STA 4.7 - - 0.6 - - μs

Data hold time tHD;DAT 0 - 3.45 0 - 0.9 μs

Data set-up time tSU;DAT 250 - - 100 - - ns

Set-up time for STOP condition tSU;STO 4.0 - - 0.6 - - μs

Bus free time between a STOP

and START condition

BUF 4.7 - - 1.3 - - μs

t

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

15/45

2010.07 - Rev.

Page 16

A

BD6083GUL

A

Technical Note

●Register List

ddress W/R

00h W - - - - - - - SFTRST Software Reset

01h W - - - - W6MD W5MD W4MD MLEDMD LED Pin function setting

02h W WPWMEN ALCEN - - W6EN W5EN - MLEDEN LED Power Control

03h W - IMLED(6) IMLED(5) IMLED(4) IMLED(3) IMLED(2) IMLED(1) IMLED(0) Main group current setting

04h - - - - - - - - - -

05h W - IW5(6) IW5(5) IW5(4) IW5(3) IW5(2) IW5(1) IW5(0) LED5 current setting

06h W - IW6(6) IW6(5) IW6(4) IW6(3) IW6(2) IW6(1) IW6(0) LED6 current setting

07h - - - - - - - - - -

08h - - - - - - - - - -

09h W THL (3) THL (2) THL (1) THL (0) TLH (3) TLH (2) TLH (1) TLH (0) Main Current transition

0Ah W - ADCYC - GAIN - - MDCIR SBIASON Measurement mode setting

0Bh W - - - - CRV STEP (2) STEP (1) STEP (0) ALC Slope curve setup

0Ch R - - - - AMB (3) AMB (2) AMB (1) AMB (0) Ambient level

0Dh W - IU0 (6) IU0 (5) IU0 (4) IU0 (3) IU0 (2) IU0 (1) IU0 (0) LED Current at Ambient level 0h (ALC)

0Eh W - IU1 (6) IU1 (5) IU1 (4) IU1 (3) IU1 (2) IU1 (1) IU1 (0) LED Current max (ALC)

0Fh - - - - - - - - - -

10h - - - - - - - - - -

11h - - - - - - - - - -

12h - - - - - - - - - -

13h W - - - - LDO4EN LDO3EN LDO2EN LDO1EN LDO Power Control

14h W LDO2VSEL3 LDO2VSEL2 LDO2VSEL1 LDO2VSEL0 LDO1VSEL3 LDO1VSEL2 LDO1VSEL1 LDO1VSEL0

15h W LDO4VSEL3 LDO4VSEL2 LDO4VSEL1 LDO4VSEL0 LDO3VSEL3 LDO3VSEL2 LDO3VSEL1 LDO3VSEL0

Input "0” for "-".

A free address has the possibility to assign it to the register for the test.

Access to the register for the test and the undefined register is prohibited.

D7 D6 D5 D4 D3 D2 D1 D0

Register data

Function

LDO1 Vout Control

LDO2 Vout Control

LDO3 Vout Control

LDO4 Vout Control

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

16/45

2010.07 - Rev.

Page 17

A

BD6083GUL

●Register Map

Address 00h < Software Reset >

Address

00h W - - - - - - - SFTRST

Initial Value 00h - - - - - - - 0

Bit[7:1] : (Not used)

Bit0 : SFTRST Software Reset

Address 01h < LED Pin function setting>

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

01h W - - - - W6MD W5MD W4MD MLEDMD

Initial Value 02h - - - - 0 0 1 0

Bit[7:4] : (Not used)

Bit3 : W6MD LED6 control setting (individual / Main group)

Bit2 : W5MD LED5 control setting (individual / Main group)

Bit1 : W4MD LED4 Control Board setting (unuse / use)

Bit0 : MLEDMD Main group setting (Normal / ALC)

Set up a fixation in every design because it isn't presumed W*PW that it is changed dynamically.

And, do the setup of W*PW when each LED is Off.

R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

“0” : Reset cancel

“1” : Reset(All register initializing)

Refer to “Reset” for detail.

“0” : LED6 individual control (Initial Value)

“1” : LED6 Main group control

Refer to “LED Driver” for detail.

“0” : LED5 individual control (Initial Value)

“1” : LED5 Main group control

Refer to “LED Driver” for detail.

“0” : LED4 unuse

“1” : LED4 use (Main group Control) (Initial Value)

Refer to “LED Driver” for detail.

“0” : Main group Normal Mode(ALCNon-reflection)(Initial Value)

“1” : Main group ALC Mode

Refer to “(1) Auto Luminous Control ON/OFF” of “ALC” for detail.

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

17/45

2010.07 - Rev.

Page 18

A

BD6083GUL

Address 02h < LED Power Control>

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

02h W WPWMEN ALCEN - - W6EN W5EN - MLEDEN

Initial Value 00h 0 0 0 0 0 0 0 0

Bit7 : WPWMEN External PWM Input “WPWMIN” terminal Enable Control (Valid/Invalid)

“0” : External PWM input invalid (Initial Value)

“1” : External PWM input valid

Refer to “(10) Current Adjustment” of “ALC” for detail.

Bit6 : ALCEN ALC function Control (ON/OFF)

“0” : ALC block OFF (Initial Value)

“1” : ALC block ON (Ambient Measurement)

Refer to “(1) Auto Luminous Control ON/OFF” of “ALC” for detail.

Bit[5:4] : (Not used)

Bit3 : W6EN LED6 Control (ON/OFF)

“0” : LED6 OFF (Initial Value)

“1” : LED6 ON(individual control)

Refer to “LED Driver” for detail.

Bit2 : W5EN LED5 Control (ON/OFF)

“0” : LED5 OFF (Initial Value)

“1” : LED5 ON(individual control)

Refer to “LED Driver” for detail.

Bit1 : (Not used)

Bit0 : MLEDEN Main group LED Control (ON/OFF)

“0” : Main group OFF (Initial Value)

“1” : Main group ON

Refer to “(1) Auto Luminous Control ON/OFF” of “ALC” for detail.

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

18/45

2010.07 - Rev.

Page 19

A

BD6083GUL

Technical Note

Address 03h < Main group LED Current setting(Normal Mode) >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

03h W - IMLED(6) IMLED(5) IMLED(4) IMLED(3) IMLED(2) IMLED(1) IMLED(0)

Initial Value 00h - 0 0 0 0 0 0 0

Bit7 : (Not used)

Bit[6:0] : IMLED (6:0) Main Group LED Current Setting at non-ALC mode

“0000000” : 0.2 mA (Initial Value) “1000000” : 13.0 mA

“0000001” : 0.4 mA “1000001” : 13.2 mA

“0000010” : 0.6 mA “1000010” : 13.4 mA

“0000011” : 0.8 mA “1000011” : 13.6 mA

“0000100” : 1.0 mA “1000100” : 13.8 mA

“0000101” : 1.2 mA “1000101” : 14.0 mA

“0000110” : 1.4 mA “1000110” : 14.2 mA

“0000111” : 1.6 mA “1000111” : 14.4 mA

“0001000” : 1.8 mA “1001000” : 14.6 mA

“0001001” : 2.0 mA “1001001” : 14.8 mA

“0001010” : 2.2 mA “1001010” : 15.0 mA

“0001011” : 2.4 mA “1001011” : 15.2 mA

“0001100” : 2.6 mA “1001100” : 15.4 mA

“0001101” : 2.8 mA “1001101” : 15.6 mA

“0001110” : 3.0 mA “1001110” : 15.8 mA

“0001111” : 3.2 mA “1001111” : 16.0 mA

“0010000” : 3.4 mA “1010000” : 16.2 mA

“0010001” : 3.6 mA “1010001” : 16.4 mA

“0010010” : 3.8 mA “1010010” : 16.6 mA

“0010011” : 4.0 mA “1010011” : 16.8 mA

“0010100” : 4.2 mA “1010100” : 17.0 mA

“0010101” : 4.4 mA “1010101” : 17.2 mA

“0010110” : 4.6 mA “1010110” : 17.4 mA

“0010111” : 4.8 mA “1010111” : 17.6 mA

“0011000” : 5.0 mA “1011000” : 17.8 mA

“0011001” : 5.2 mA “1011001” : 18.0 mA

“0011010” : 5.4 mA “1011010” : 18.2 mA

“0011011” : 5.6 mA “1011011” : 18.4 mA

“0011100” : 5.8 mA “1011100” : 18.6 mA

“0011101” : 6.0 mA “1011101” : 18.8 mA

“0011110” : 6.2 mA “1011110” : 19.0 mA

“0011111” : 6.4 mA “1011111” : 19.2 mA

“0100000” : 6.6 mA “1100000” : 19.4 mA

“0100001” : 6.8 mA “1100001” : 19.6 mA

“0100010” : 7.0 mA “1100010” : 19.8 mA

“0100011” : 7.2 mA “1100011” : 20.0 mA

“0100100” : 7.4 mA “1100100” : 20.2 mA

“0100101” : 7.6 mA “1100101” : 20.4 mA

“0100110” : 7.8 mA “1100110” : 20.6 mA

“0100111” : 8.0 mA “1100111” : 20.8 mA

“0101000” : 8.2 mA “1101000” : 21.0 mA

“0101001” : 8.4 mA “1101001” : 21.2 mA

“0101010” : 8.6 mA “1101010” : 21.4 mA

“0101011” : 8.8 mA “1101011” : 21.6 mA

“0101100” : 9.0 mA “1101100” : 21.8 mA

“0101101” : 9.2 mA “1101101” : 22.0 mA

“0101110” : 9.4 mA “1101110” : 22.2 mA

“0101111” : 9.6 mA “1101111” : 22.4 mA

“0110000” : 9.8 mA “1110000” : 22.6 mA

“0110001” : 10.0 mA “1110001” : 22.8 mA

“0110010” : 10.2 mA “1110010” : 23.0 mA

“0110011” : 10.4 mA “1110011” : 23.2 mA

“0110100” : 10.6 mA “1110100” : 23.4 mA

“0110101” : 10.8 mA “1110101” : 23.6 mA

“0110110” : 11.0 mA “1110110” : 23.8 mA

“0110111” : 11.2 mA “1110111” : 24.0 mA

“0 111 0 0 0” : 11 .4 mA “1111 0 0 0 ” : 24 . 2 mA

“0 111 0 0 1” : 11.6 m A “1111 0 0 1 ” : 24 . 4 mA

“0 111 0 1 0” : 11 .8 mA “1111 0 1 0 ” : 24 . 6 mA

“0 111 0 11 ” : 12. 0 m A “1111011” : 24. 8 m A

“0 1111 0 0 ” : 12 . 2 mA “1111100” : 25.0 mA

“0 1111 0 1 ” : 12 . 4 m A “1111101” : 25.2 mA

“0 11111 0 ” : 12. 6 m A “1111110” : 25. 4 m A

“0 111111 ” : 12.8 m A “1111111 ” : 25.6 m A

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

19/45

2010.07 - Rev.

Page 20

A

BD6083GUL

Technical Note

Address 05h < LED5 Current setting(Independence control) >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

05h W - IW5(6) IW5(5) IW5(4) IW5(3) IW5(2) IW5(1) IW5(0)

Initial Value 00h - 0 0 0 0 0 0 0

Bit7 : (Not used)

Bit[6:0] : IW5 (6:0) LED5

“0000000” : 0.2 mA (Initial Value) “1000000” : 13.0 mA

“0000001” : 0.4 mA “1000001” : 13.2 mA

“0000010” : 0.6 mA “1000010” : 13.4 mA

“0000011” : 0.8 mA “1000011” : 13.6 mA

“0000100” : 1.0 mA “1000100” : 13.8 mA

“0000101” : 1.2 mA “1000101” : 14.0 mA

“0000110” : 1.4 mA “1000110” : 14.2 mA

“0000111” : 1.6 mA “1000111” : 14.4 mA

“0001000” : 1.8 mA “1001000” : 14.6 mA

“0001001” : 2.0 mA “1001001” : 14.8 mA

“0001010” : 2.2 mA “1001010” : 15.0 mA

“0001011” : 2.4 mA “1001011” : 15.2 mA

“0001100” : 2.6 mA “1001100” : 15.4 mA

“0001101” : 2.8 mA “1001101” : 15.6 mA

“0001110” : 3.0 mA “1001110” : 15.8 mA

“0001111” : 3.2 mA “1001111” : 16.0 mA

“0010000” : 3.4 mA “1010000” : 16.2 mA

“0010001” : 3.6 mA “1010001” : 16.4 mA

“0010010” : 3.8 mA “1010010” : 16.6 mA

“0010011” : 4.0 mA “1010011” : 16.8 mA

“0010100” : 4.2 mA “1010100” : 17.0 mA

“0010101” : 4.4 mA “1010101” : 17.2 mA

“0010110” : 4.6 mA “1010110” : 17.4 mA

“0010111” : 4.8 mA “1010111” : 17.6 mA

“0011000” : 5.0 mA “1011000” : 17.8 mA

“0011001” : 5.2 mA “1011001” : 18.0 mA

“0011010” : 5.4 mA “1011010” : 18.2 mA

“0011011” : 5.6 mA “1011011” : 18.4 mA

“0011100” : 5.8 mA “1011100” : 18.6 mA

“0011101” : 6.0 mA “1011101” : 18.8 mA

“0011110” : 6.2 mA “1011110” : 19.0 mA

“0011111” : 6.4 mA “1011111” : 19.2 mA

“0100000” : 6.6 mA “1100000” : 19.4 mA

“0100001” : 6.8 mA “1100001” : 19.6 mA

“0100010” : 7.0 mA “1100010” : 19.8 mA

“0100011” : 7.2 mA “1100011” : 20.0 mA

“0100100” : 7.4 mA “1100100” : 20.2 mA

“0100101” : 7.6 mA “1100101” : 20.4 mA

“0100110” : 7.8 mA “1100110” : 20.6 mA

“0100111” : 8.0 mA “1100111” : 20.8 mA

“0101000” : 8.2 mA “1101000” : 21.0 mA

“0101001” : 8.4 mA “1101001” : 21.2 mA

“0101010” : 8.6 mA “1101010” : 21.4 mA

“0101011” : 8.8 mA “1101011” : 21.6 mA

“0101100” : 9.0 mA “1101100” : 21.8 mA

“0101101” : 9.2 mA “1101101” : 22.0 mA

“0101110” : 9.4 mA “1101110” : 22.2 mA

“0101111” : 9.6 mA “1101111” : 22.4 mA

“0110000” : 9.8 mA “1110000” : 22.6 mA

“0110001” : 10.0 mA “1110001” : 22.8 mA

“0110010” : 10.2 mA “1110010” : 23.0 mA

“0110011” : 10.4 mA “1110011” : 23.2 mA

“0110100” : 10.6 mA “1110100” : 23.4 mA

“0110101” : 10.8 mA “1110101” : 23.6 mA

“0110110” : 11.0 mA “1110110” : 23.8 mA

“0110111” : 11.2 mA “1110111” : 24.0 mA

“0 111 0 0 0” : 11 .4 mA “1111 0 0 0 ” : 24 . 2 mA

“0 111 0 0 1” : 11.6 m A “1111 0 0 1 ” : 24 . 4 mA

“0 111 0 1 0” : 11 .8 mA “1111 0 1 0 ” : 24 . 6 mA

“0 111 0 11 ” : 12. 0 m A “1111011” : 24. 8 m A

“0 1111 0 0 ” : 12 . 2 mA “1111100” : 25.0 mA

“0 1111 0 1 ” : 12 . 4 m A “1111101” : 25.2 mA

“0 11111 0 ” : 12. 6 m A “1111110” : 25. 4 m A

“0 111111 ” : 12.8 m A “1111111 ” : 25.6 m A

Current setting

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

20/45

2010.07 - Rev.

Page 21

A

BD6083GUL

Technical Note

Address 06h < LED6 Current setting(Independence control) >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

06h W - IW6(6) IW6(5) IW6(4) IW6(3) IW6(2) IW6(1) IW6(0)

Initial Value 00h - 0 0 0 0 0 0 0

Bit7 : (Not used)

Bit[6:0] : IW6 (6:0) LED6

“0000000” : 0.2 mA (Initial Value) “1000000” : 13.0 mA

“0000001” : 0.4 mA “1000001” : 13.2 mA

“0000010” : 0.6 mA “1000010” : 13.4 mA

“0000011” : 0.8 mA “1000011” : 13.6 mA

“0000100” : 1.0 mA “1000100” : 13.8 mA

“0000101” : 1.2 mA “1000101” : 14.0 mA

“0000110” : 1.4 mA “1000110” : 14.2 mA

“0000111” : 1.6 mA “1000111” : 14.4 mA

“0001000” : 1.8 mA “1001000” : 14.6 mA

“0001001” : 2.0 mA “1001001” : 14.8 mA

“0001010” : 2.2 mA “1001010” : 15.0 mA

“0001011” : 2.4 mA “1001011” : 15.2 mA

“0001100” : 2.6 mA “1001100” : 15.4 mA

“0001101” : 2.8 mA “1001101” : 15.6 mA

“0001110” : 3.0 mA “1001110” : 15.8 mA

“0001111” : 3.2 mA “1001111” : 16.0 mA

“0010000” : 3.4 mA “1010000” : 16.2 mA

“0010001” : 3.6 mA “1010001” : 16.4 mA

“0010010” : 3.8 mA “1010010” : 16.6 mA

“0010011” : 4.0 mA “1010011” : 16.8 mA

“0010100” : 4.2 mA “1010100” : 17.0 mA

“0010101” : 4.4 mA “1010101” : 17.2 mA

“0010110” : 4.6 mA “1010110” : 17.4 mA

“0010111” : 4.8 mA “1010111” : 17.6 mA

“0011000” : 5.0 mA “1011000” : 17.8 mA

“0011001” : 5.2 mA “1011001” : 18.0 mA

“0011010” : 5.4 mA “1011010” : 18.2 mA

“0011011” : 5.6 mA “1011011” : 18.4 mA

“0011100” : 5.8 mA “1011100” : 18.6 mA

“0011101” : 6.0 mA “1011101” : 18.8 mA

“0011110” : 6.2 mA “1011110” : 19.0 mA

“0011111” : 6.4 mA “1011111” : 19.2 mA

“0100000” : 6.6 mA “1100000” : 19.4 mA

“0100001” : 6.8 mA “1100001” : 19.6 mA

“0100010” : 7.0 mA “1100010” : 19.8 mA

“0100011” : 7.2 mA “1100011” : 20.0 mA

“0100100” : 7.4 mA “1100100” : 20.2 mA

“0100101” : 7.6 mA “1100101” : 20.4 mA

“0100110” : 7.8 mA “1100110” : 20.6 mA

“0100111” : 8.0 mA “1100111” : 20.8 mA

“0101000” : 8.2 mA “1101000” : 21.0 mA

“0101001” : 8.4 mA “1101001” : 21.2 mA

“0101010” : 8.6 mA “1101010” : 21.4 mA

“0101011” : 8.8 mA “1101011” : 21.6 mA

“0101100” : 9.0 mA “1101100” : 21.8 mA

“0101101” : 9.2 mA “1101101” : 22.0 mA

“0101110” : 9.4 mA “1101110” : 22.2 mA

“0101111” : 9.6 mA “1101111” : 22.4 mA

“0110000” : 9.8 mA “1110000” : 22.6 mA

“0110001” : 10.0 mA “1110001” : 22.8 mA

“0110010” : 10.2 mA “1110010” : 23.0 mA

“0110011” : 10.4 mA “1110011” : 23.2 mA

“0110100” : 10.6 mA “1110100” : 23.4 mA

“0110101” : 10.8 mA “1110101” : 23.6 mA

“0110110” : 11.0 mA “1110110” : 23.8 mA

“0110111” : 11.2 mA “1110111” : 24.0 mA

“0 111 0 0 0” : 11 .4 mA “1111 0 0 0 ” : 24 . 2 mA

“0 111 0 0 1” : 11.6 m A “1111 0 0 1 ” : 24 . 4 mA

“0 111 0 1 0” : 11 .8 mA “1111 0 1 0 ” : 24 . 6 mA

“0 111 0 11 ” : 12. 0 m A “1111011” : 24. 8 m A

“0 1111 0 0 ” : 12 . 2 mA “1111100” : 25.0 mA

“0 1111 0 1 ” : 12 . 4 m A “1111101” : 25.2 mA

“0 11111 0 ” : 12. 6 m A “1111110” : 25. 4 m A

“0 111111 ” : 12.8 m A “1111111 ” : 25.6 m A

Current setting

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

21/45

2010.07 - Rev.

Page 22

A

BD6083GUL

Address 09h < Main Current slope time setting >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

09h W THL(3) THL(2) THL(1) THL(0) TLH(3) TLH(2) TLH(1) TLH(0)

Initial Value C7h 1 1 0 0 0 1 1 1

Bit[7:4] : THL (3:0) Main LED current Down transition per 0.2mA step

“0000” : 0.256 ms

“0001” : 0.512 ms

“0010” : 1.024 ms

“0011” : 2.048 ms

“0100” : 4.096 ms

“0101” : 8.192 ms

“0110” : 16.38 ms

“0111” : 32.77 ms

“1000” : 65.54 ms

“1001” : 131.1 ms

“1010” : 196.6 ms

“1011” : 262.1 ms

“1100” : 327.7 ms (Initial Value)

“1101” : 393.2 ms

“1110” : 458.8 ms

“1111” : 5 2 4 . 3 ms

Setting time is counted based on the switching frequency of Charge Pump.

The above value becomes the value of the Typ (1MHz) time.

Refer to “(8) Slope Process” of “ALC” for detail.

Bit[3:0] : TLH (3:0) Main LED current Up transition per 0.2mA step

“0000” : 0.256 ms

“0001” : 0.512 ms

“0010” : 1.024 ms

“0011” : 2.048 ms

“0100” : 4.096 ms

“0101” : 8.192 ms

“0110” : 16.38 ms

“0111” : 32.77 ms (Initial Value)

“1000” : 65.54 ms

“1001” : 131.1 ms

“1010” : 196.6 ms

“1011” : 262.1 ms

“1100” : 327.7 ms

“1101” : 393.2 ms

“1110” : 458.8 ms

“1111” : 5 2 4 . 3 ms

Setting time is counted based on the switching frequency of Charge Pump.

The above value becomes the value of the Typ (1MHz) time.

Refer to “(8) Slope Process” of “ALC” for detail.

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

22/45

2010.07 - Rev.

Page 23

A

BD6083GUL

Technical Note

Address 0Ah < ALC mode setting >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

0Ah W - ADCYC - GAIN - - MDCIR SBIASON

Initial Value 01h - 0 - 0 - - 0 1

Bit7 : (Not used)

Bit6 : ADCYC ADC Measurement Cycle

“0” : 0.52 s (Initial Value)

“1” : 1.05 s

Refer to “(4) A/D conversion” of “ALC” for detail.

Bit5 : (Not used)

Bit4 : GAIN Sensor Gain Switching Function Control

“0” : Auto Change (Initial Value)

“1” : Fixed

Refer to “(3) Gain control” of “ALC” for detail.

Bit[3:2] : (Not used)

Bit1 : MDCIR LED Current Reset Select by Mode Change

“0” : LED current non-reset when mode change (Initial Value)

“1” : LED current reset when mode change

Refer to “(9) LED current reset when mode change” of “ALC” for detail.

Bit0 : SBIASON

“0” : Measurement cycle synchronous

“1” : Usually ON (at ALCEN=1) (Initial Value)

Refer to “(4) A/D conversion” of “ALC” for detail.

Address 0Bh < ALC slope curve setting >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

0Bh W - - - - CRV STEP (2) STEP (1) STEP (0)

Initial Value 00h - - - - 0 0 0 1

Bit[7:4] : (Not used)

Bit3 : CRV Brightness Current Conversion Curve Type

“0” Log curve (Initial Value)

“1” linear

Bit[2:0] : STEP (2:0) Step At the time of Brightness Current Conversion

“000” : 1.0mA

“001” : 1.1mA (Initial Value)

“010” : 1.2mA

“011” : 1.3mA

“100” : 1.6mA

“101” : 1.7mA

“110” : 1.8mA

“111” : 1.9mA

Refer to “(7) Convert LED Current” of “ALC” for detail.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

23/45

2010.07 - Rev.

Page 24

A

BD6083GUL

Address 0Ch < Ambient level (Read Only) >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

0Ch R - - - - AMB(3) AMB(2) AMB(1) AMB(0)

Initial Value (00h) - - - - (0) (0) (0) (0)

Bit[7:4] : (Not used)

Bit[3:0] : AMB (3:0) Ambient Level

“0000” : 0h (Initial Value)

“0001” : 1h

“0010” : 2h

“0011” : 3h

“0100” : 4h

“0101” : 5h

“0110” : 6h

“0111” : 7h

“1000” : 8h

“1001” : 9h

“1010” : Ah

“1011” : Bh

“1100” : Ch

“1101” : Dh

“1110” : Eh

“1111” : Fh

It begins to read Ambient data through I

To the first AD measurement completion, it is AMB(3:0)=0000.

Refer to “(6) Ambient level detection” of “ALC” for detail.

2

C, and possible.

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

24/45

2010.07 - Rev.

Page 25

A

BD6083GUL

Technical Note

Address 0Dh < Ambient LED Current setting >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

0Dh W - IU0 (6) IU0 (5) IU0 (4) IU0 (3) IU0 (2) IU0 (1) IU0 (0)

Initial Value 13 - 0 0 1 0 0 1 1

Bit7 : (Not used)

Bit[6:0] : IU0 (6:0) Main Current at Ambient Level for 0h

“0000000” : 0.2 mA “1000000” : 13.0 mA

“0000001” : 0.4 mA “1000001” : 13.2 mA

“0000010” : 0.6 mA “1000010” : 13.4 mA

“0000011” : 0.8 mA “1000011” : 13.6 mA

“0000100” : 1.0 mA “1000100” : 13.8 mA

“0000101” : 1.2 mA “1000101” : 14.0 mA

“0000110” : 1.4 mA “1000110” : 14.2 mA

“0000111” : 1.6 mA “1000111” : 14.4 mA

“0001000” : 1.8 mA “1001000” : 14.6 mA

“0001001” : 2.0 mA “1001001” : 14.8 mA

“0001010” : 2.2 mA “1001010” : 15.0 mA

“0001011” : 2.4 mA “1001011” : 15.2 mA

“0001100” : 2.6 mA “1001100” : 15.4 mA

“0001101” : 2.8 mA “1001101” : 15.6 mA

“0001110” : 3.0 mA “1001110” : 15.8 mA

“0001111” : 3.2 mA “1001111” : 16.0 mA

“0010000” : 3.4 mA “1010000” : 16.2 mA

“0010001” : 3.6 mA “1010001” : 16.4 mA

“0010010” : 3.8 mA “1010010” : 16.6 mA

“0010011” : 4.0 mA

“0010100” : 4.2 mA “1010100” : 17.0 mA

“0010101” : 4.4 mA “1010101” : 17.2 mA

“0010110” : 4.6 mA “1010110” : 17.4 mA

“0010111” : 4.8 mA “1010111” : 17.6 mA

“0011000” : 5.0 mA “1011000” : 17.8 mA

“0011001” : 5.2 mA “1011001” : 18.0 mA

“0011010” : 5.4 mA “1011010” : 18.2 mA

“0011011” : 5.6 mA “1011011” : 18.4 mA

“0011100” : 5.8 mA “1011100” : 18.6 mA

“0011101” : 6.0 mA “1011101” : 18.8 mA

“0011110” : 6.2 mA “1011110” : 19.0 mA

“0011111” : 6.4 mA “1011111” : 19.2 mA

“0100000” : 6.6 mA “1100000” : 19.4 mA

“0100001” : 6.8 mA “1100001” : 19.6 mA

“0100010” : 7.0 mA “1100010” : 19.8 mA

“0100011” : 7.2 mA “1100011” : 20.0 mA

“0100100” : 7.4 mA “1100100” : 20.2 mA

“0100101” : 7.6 mA “1100101” : 20.4 mA

“0100110” : 7.8 mA “1100110” : 20.6 mA

“0100111” : 8.0 mA “1100111” : 20.8 mA

“0101000” : 8.2 mA “1101000” : 21.0 mA

“0101001” : 8.4 mA “1101001” : 21.2 mA

“0101010” : 8.6 mA “1101010” : 21.4 mA

“0101011” : 8.8 mA “1101011” : 21.6 mA

“0101100” : 9.0 mA “1101100” : 21.8 mA

“0101101” : 9.2 mA “1101101” : 22.0 mA

“0101110” : 9.4 mA “1101110” : 22.2 mA

“0101111” : 9.6 mA “1101111” : 22.4 mA

“0110000” : 9.8 mA “1110000” : 22.6 mA

“0110001” : 10.0 mA “1110001” : 22.8 mA

“0110010” : 10.2 mA “1110010” : 23.0 mA

“0110011” : 10.4 mA “1110011” : 23.2 mA

“0110100” : 10.6 mA “1110100” : 23.4 mA

“0110101” : 10.8 mA “1110101” : 23.6 mA

“0110110” : 11.0 mA “1110110” : 23.8 mA

“0110111” : 11.2 mA “1110111” : 24.0 mA

“0 111 0 0 0” : 11 .4 mA “1111 0 0 0 ” : 24 . 2 mA

“0 111 0 0 1” : 11.6 m A “1111 0 0 1 ” : 24 . 4 mA

“0 111 0 1 0” : 11 .8 mA “1111 0 1 0 ” : 24 . 6 mA

“0 111 0 11 ” : 12. 0 m A “1111011” : 24. 8 m A

“0 1111 0 0 ” : 12 . 2 mA “1111100” : 25.0 mA

“0 1111 0 1 ” : 12 . 4 m A “1111101” : 25.2 mA

“0 11111 0 ” : 12. 6 m A “1111110” : 25. 4 m A

“0 111111 ” : 12.8 m A “1111111 ” : 25.6 m A

(Initial Value) “1010011” : 16.8 mA

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

25/45

2010.07 - Rev.

Page 26

A

BD6083GUL

Technical Note

Address 0Eh < LED Max Current setting >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

0Eh W - IU1 (6) IU1 (5) IU1 (4) IU1 (3) IU1 (2) IU1 (1) IU1 (0)

Initial Value 63h - 1 1 0 0 0 1 1

Bit7 : (Not used)

Bit[6:0] : IU1 (6:0) LED Max Current (for ALC)

“0000000” : 0.2 mA “1000000” : 13.0 mA

“0000001” : 0.4 mA “1000001” : 13.2 mA

“0000010” : 0.6 mA “1000010” : 13.4 mA

“0000011” : 0.8 mA “1000011” : 13.6 mA

“0000100” : 1.0 mA “1000100” : 13.8 mA

“0000101” : 1.2 mA “1000101” : 14.0 mA

“0000110” : 1.4 mA “1000110” : 14.2 mA

“0000111” : 1.6 mA “1000111” : 14.4 mA

“0001000” : 1.8 mA “1001000” : 14.6 mA

“0001001” : 2.0 mA “1001001” : 14.8 mA

“0001010” : 2.2 mA “1001010” : 15.0 mA

“0001011” : 2.4 mA “1001011” : 15.2 mA

“0001100” : 2.6 mA “1001100” : 15.4 mA

“0001101” : 2.8 mA “1001101” : 15.6 mA

“0001110” : 3.0 mA “1001110” : 15.8 mA

“0001111” : 3.2 mA “1001111” : 16.0 mA

“0010000” : 3.4 mA “1010000” : 16.2 mA

“0010001” : 3.6 mA “1010001” : 16.4 mA

“0010010” : 3.8 mA “1010010” : 16.6 mA

“0010011” : 4.0 mA “1010011” : 16.8 mA

“0010100” : 4.2 mA “1010100” : 17.0 mA

“0010101” : 4.4 mA “1010101” : 17.2 mA

“0010110” : 4.6 mA “1010110” : 17.4 mA

“0010111” : 4.8 mA “1010111” : 17.6 mA

“0011000” : 5.0 mA “1011000” : 17.8 mA

“0011001” : 5.2 mA “1011001” : 18.0 mA

“0011010” : 5.4 mA “1011010” : 18.2 mA

“0011011” : 5.6 mA “1011011” : 18.4 mA

“0011100” : 5.8 mA “1011100” : 18.6 mA

“0011101” : 6.0 mA “1011101” : 18.8 mA

“0011110” : 6.2 mA “1011110” : 19.0 mA

“0011111” : 6.4 mA “1011111” : 19.2 mA

“0100000” : 6.6 mA “1100000” : 19.4 mA

“0100001” : 6.8 mA “1100001” : 19.6 mA

“0100010” : 7.0 mA “1100010” : 19.8 mA

“0100011” : 7.2 mA “1100011” : 20.0 mA

“0100100” : 7.4 mA “1100100” : 20.2 mA

“0100101” : 7.6 mA “1100101” : 20.4 mA

“0100110” : 7.8 mA “1100110” : 20.6 mA

“0100111” : 8.0 mA “1100111” : 20.8 mA

“0101000” : 8.2 mA “1101000” : 21.0 mA

“0101001” : 8.4 mA “1101001” : 21.2 mA

“0101010” : 8.6 mA “1101010” : 21.4 mA

“0101011” : 8.8 mA “1101011” : 21.6 mA

“0101100” : 9.0 mA “1101100” : 21.8 mA

“0101101” : 9.2 mA “1101101” : 22.0 mA

“0101110” : 9.4 mA “1101110” : 22.2 mA

“0101111” : 9.6 mA “1101111” : 22.4 mA

“0110000” : 9.8 mA “1110000” : 22.6 mA

“0110001” : 10.0 mA “1110001” : 22.8 mA

“0110010” : 10.2 mA “1110010” : 23.0 mA

“0110011” : 10.4 mA “1110011” : 23.2 mA

“0110100” : 10.6 mA “1110100” : 23.4 mA

“0110101” : 10.8 mA “1110101” : 23.6 mA

“0110110” : 11.0 mA “1110110” : 23.8 mA

“0110111” : 11.2 mA “1110111” : 24.0 mA

“0 111 0 0 0” : 11 .4 mA “1111 0 0 0 ” : 24 . 2 mA

“0 111 0 0 1” : 11.6 m A “1111 0 0 1 ” : 24 . 4 mA

“0 111 0 1 0” : 11 .8 mA “1111 0 1 0 ” : 24 . 6 mA

“0 111 0 11 ” : 12. 0 m A “1111011” : 24. 8 m A

“0 1111 0 0 ” : 12 . 2 mA “1111100” : 25.0 mA

“0 1111 0 1 ” : 12 . 4 m A “1111101” : 25.2 mA

“0 11111 0 ” : 12. 6 m A “1111110” : 25. 4 m A

“0 111111 ” : 12.8 m A “1111111 ” : 25.6 m A

(Initial Value)

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

26/45

2010.07 - Rev.

Page 27

A

BD6083GUL

Address 13h <LDO Power Control>

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

13h W/R - - - - LDO4EN LDO3EN LDO2EN LDO1EN

Initial Value 00h - - - - 0 0 0 0

Bit[7:4] : (Not used)

Bit3 : LDO4EN LDO4 control (ON/OFF)

“0” : LDO4 OFF (Initial Value)

“1” : LDO4 ON

Bit2 : LDO3EN LDO3 control (ON/OFF)

“0” : LDO3 OFF (Initial Value)

“1” : LDO3 ON

Bit1 : LDO2EN LDO2 control (ON/OFF)

“0” : LDO2 OFF (Initial Value)

“1” : LDO2 ON

Bit0 : LDO1EN LDO1 control (ON/OFF)

“0” : LDO1 OFF (Initial Value)

“1” : LDO1 ON

Address 14h < LDO1 Vout Control, LDO2 Vout Control >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

14h R /W LDO2VSEL3 LDO2VSEL2 LDO2VSEL1 LDO2VSEL0 LDO1VSEL3 LDO1VSEL2 LDO1VSEL1 LDO1VSEL0

Initial Value 74h 0 1 1 1 0 1 0 0

Bit[7:4] : LDO2VSEL [3:0]

“0000” : 1.20 V

“0001” : 1.30 V

“0010” : 1.50 V

“0011” : 1.60 V

“0100” : 1.80 V

“0101” : 2.20 V

“0110” : 2.40 V

“0111” : 2.50 V (Initial Value)

“1000” : 2.60 V

“1001” : 2.70 V

“1010” : 2.80 V

“1011” : 2.90 V

“1100” : 3.00 V

“1101” : 3.10 V

“1110” : 3.20 V

“1111” : 3.30 V

Bit[3:0] : LDO1VSEL [3:0]

“0000” : 1.20 V

“0001” : 1.30 V

“0010” : 1.50 V

“0011” : 1.60 V

“0100” : 1.80 V (Initial Value)

“0101” : 2.20 V

“0110” : 2.40 V

“0111” : 2.50 V

“1000” : 2.60 V

“1001” : 2.70 V

“1010” : 2.80 V

“1011” : 2.90 V

“1100” : 3.00 V

“1101” : 3.10 V

“1110” : 3.20 V

“1111” : 3.30 V

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

27/45

2010.07 - Rev.

Page 28

A

BD6083GUL

Address 15h < LDO3 Vout Control, LDO4 Vout Control >

Address R/W Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

15h R /W LDO4VSEL3 LDO4VSEL2 LDO4VSEL1 LDO4VSEL0 LDO3VSEL3 LDO3VSEL2 LDO3VSEL1 LDO3VSEL0

Initial Value A4h 1 0 1 0 0 1 0 0

Bit[7:4] : LDO4VSEL [3:0]

“0000” : 1.20 V

“0001” : 1.30 V

“0010” : 1.50 V

“0011” : 1.60 V

“0100” : 1.80 V

“0101” : 2.20 V

“0110” : 2.40 V

“0111” : 2.50 V

“1000” : 2.60 V

“1001” : 2.70 V

“1010” : 2.80 V (Initial Value)

“1011” : 2.90 V

“1100” : 3.00 V

“1101” : 3.10 V

“1110” : 3.20 V

“1111” : 3.30 V

Bit[3:0] : LDO3VSEL [3:0]

“0000” : 1.20 V

“0001” : 1.30 V

“0010” : 1.50 V

“0011” : 1.60 V

“0100” : 1.80 V (Initial Value)

“0101” : 2.20 V

“0110” : 2.40 V

“0111” : 2.50 V

“1000” : 2.60 V

“1001” : 2.70 V

“1010” : 2.80 V

“1011” : 2.90 V

“1100” : 3.00 V

“1101” : 3.10 V

“1110” : 3.20 V

“1111” : 3.30 V

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

28/45

2010.07 - Rev.

Page 29

A

BD6083GUL

Technical Note

●Reset

There are two kinds of reset, software reset and hardware reset

(1)Software reset

・All the registers are initialized by SFTRST="1".

・SFTRST is an automatically returned to "0". (Auto Return 0).

(2) Hardware reset

・It shifts to hardware reset by changing RESETB pin “H” → “L”.

・The condition of all the registers under hardware reset pin is returned to the Initial Value, and it stops accepting all address.

・It’s possible to release from a state of hardware reset by changing RESETB pin “L” → “H”.

・RESETB pin has delay circuit. It doesn’t recognize as hardware reset in “L” period under 5μs.

(3) Reset Sequence

・When hardware reset was done during software reset, software reset is canceled when hardware reset is canceled.

(Because the Initial Value of software reset is “0”)

●VIODET

The decline of the VIO voltage is detected, and faulty operation inside the IC is prevented by giving resetting to Levelsift block

Image Block Diagram

VIO VBAT

DEToutput

Inside reset

VBAT

2.6V

Reset by

VIODET

(typ)1.0V

VIO

VIODET

RESETB

Digital

pin

I/O

R

LEVEL

SHIFT

RESETB

DET output

Inside reset

Fig.15 Fig.16

When the VIO voltage becomes more than typ1.0V(Vth of NMOS in the IC), VIODET is removed.

On the contrary, when VIO is as follows 1.0V, it takes reset.(The VBAT voltage being a prescribed movement range)

●Thermal Shut Down

A thermal shutdown function is effective in the following block.

DC/DC (Charge Pump)

LED Driver

SBIAS

LDO1, LDO2, LDO3, LDO4

The thermal shutdown function is detection temperature that it works is about 195

Detection temperature has a hysteresis, and detection release temperature is about 175

℃.

o

C.

(Design reference value)

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

29/45

2010.07 - Rev.

Page 30

A

BD6083GUL

V

V

V

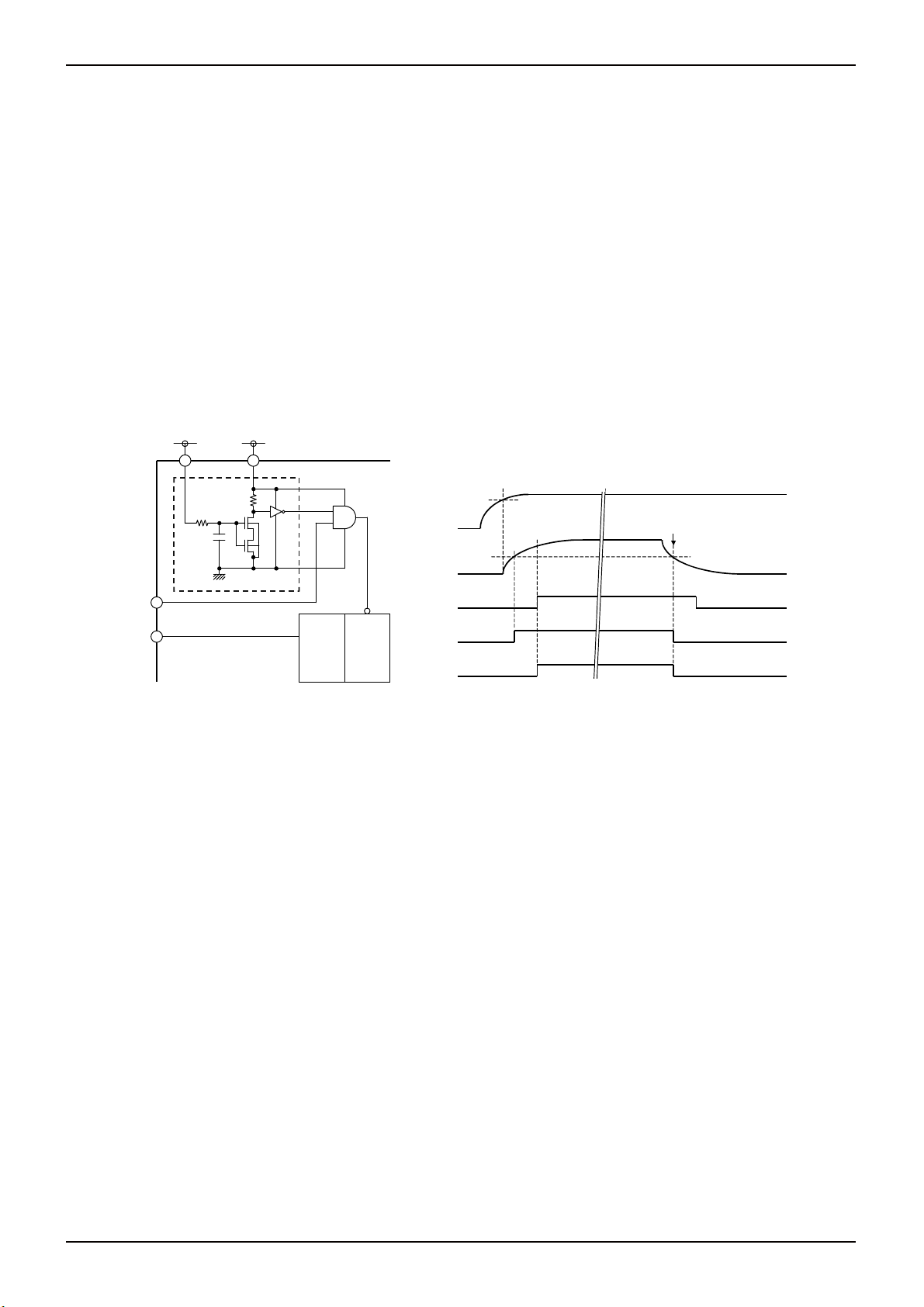

●DC / DC

Start

DC/DC circuit operates when any LED turns ON. (DCDCFON=0)

When the start of theDC/DC circuit is done, it has the soft start function to prevent a rush current.

Force of VBAT and VIO is to go as follows.

Technical Note

BAT

IO

RESETB

EN (*)

OUT

LEDcurrent

(*) An EN signal means the following in the upper figure.

EN = “MLEDEN” or “W*EN”

(= LED The LED lighting control of a setup of connection VOUT)

But, as for Ta > T

SOFT changes by the capacitor connected to VOUT and inside OSC.

T

SOFT is Typ 200μs (when the output capacitor of VOUT =1.0μF).

T

(typ : 195° C), a protection function functions, and an EN signal doesn't become effective.

TSD

Over Voltage protection / Over Current protection

DC/DC circuit output (VOUT) is equipped with the over-voltage protection and the over current protection function.

A VOUT over-voltage detection voltage is about 5.6V(typ). (VOUT at the time of rise in a voltage)

A detection voltage has a hysteresis, and a detection release voltage is about 5.4V (typ).

And, when VOUT output short to ground, input current of the battery terminal is limited by an over current protection

function.

T

VIOON=min 0.1ms

T

RSTB=min 0.1ms

T

SOFT

Fig.17

T

VIOOFF=min 0.1ms

T

RST=min 0ms

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

30/45

2010.07 - Rev.

Page 31

A

BD6083GUL

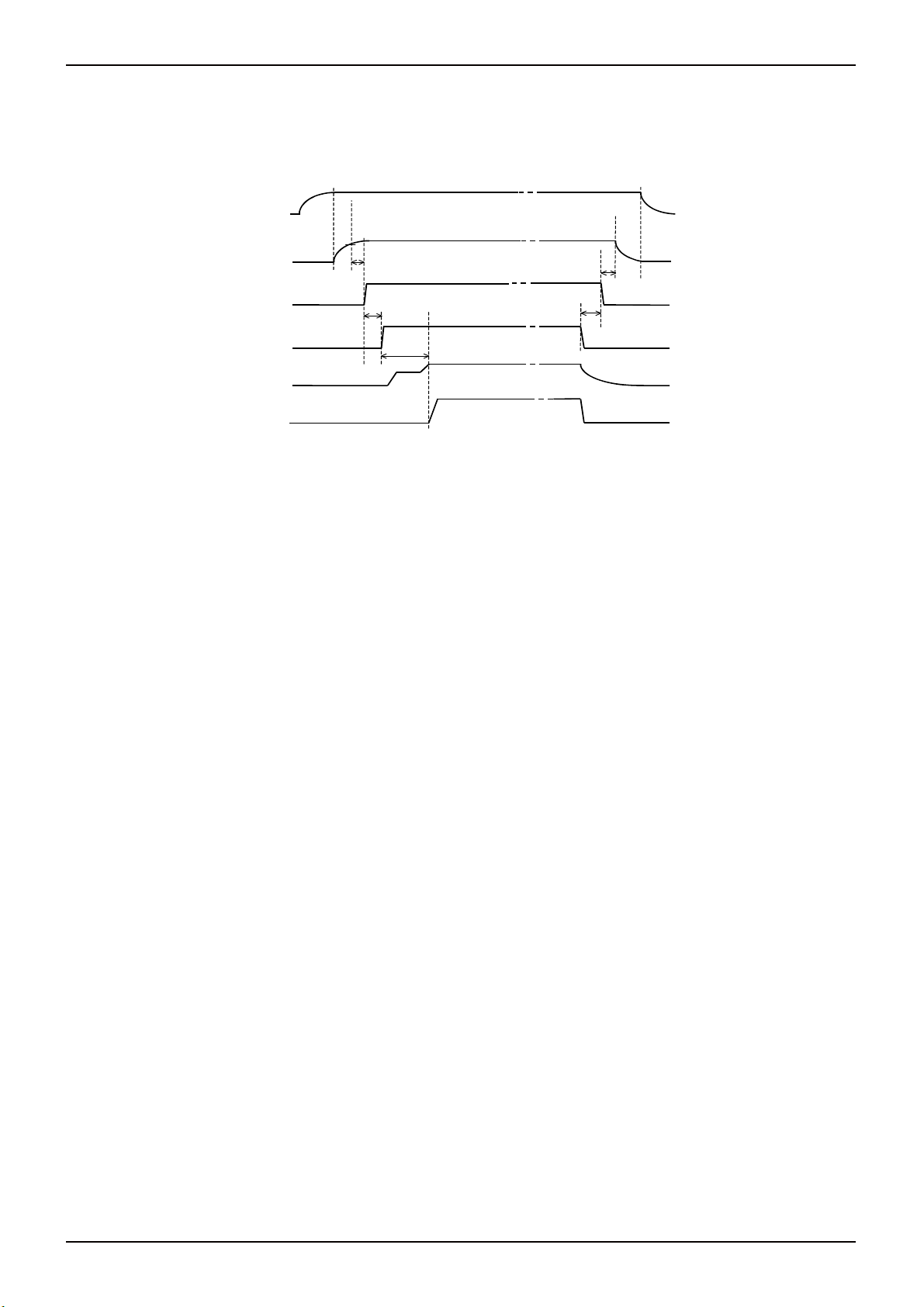

A

Mode transition

The transition of boosts multiple transits automatically by VBAT Voltage and the VOUT Pin Voltage.

The mode transition of the charge pump works as follows.

<x1.0→x1.5→x2.0 Mode transition>

The transition of the mode is done when VOUT was compared with VBAT and the next condition was satisfied.

x1.0

VBAT ≤ VOUT + (Ron10×Iout)

(LED Pin feedback:VOUT = Vf+0.2(Typ))

x1.5

VBAT×1.5 ≤ VOUT +(Ron15×Iout)

(LED Pin feedback:VOUT = Vf+0.2(Typ))

Ron10: x1 Charge pump on resistance 1.4Ω(Typ)

Ron15: x1.5 Charge pump on resistance 8.5Ω(Typ)

<x2.0→x1.5→x1.0 Mode transition>

The transition of the mode is done when the ratio of VOUT and VBAT is detected and it exceeds a fixed voltage ratio.

x1.5

VBAT / VOUT =1.16(Design value)

x2.0

VBAT / VOUT =1.12(Design value)

condition

mode down=”H”

mode down=”H”

STANDBY

1

○

SOFT

X1.0

X1.5

X2.0

Fig.18

→x1.5 Mode transition

→x2.0 Mode transition

→x1.0 Mode transition

→x1.5 Mode transition

ALL off

MLEDEN=”1” or W*EN=”1”

1

○

and

Ta< T

TSD

CP x1.0 mode

fter detecting VOUT>1.5V(typ), 128us(typ) wait

CP x1.0 mode

mode up=”H”

CP x1.5 mode

mode u p=”H”

CP x2.0 mode

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

31/45

2010.07 - Rev.

Page 32

A

BD6083GUL

Technical Note

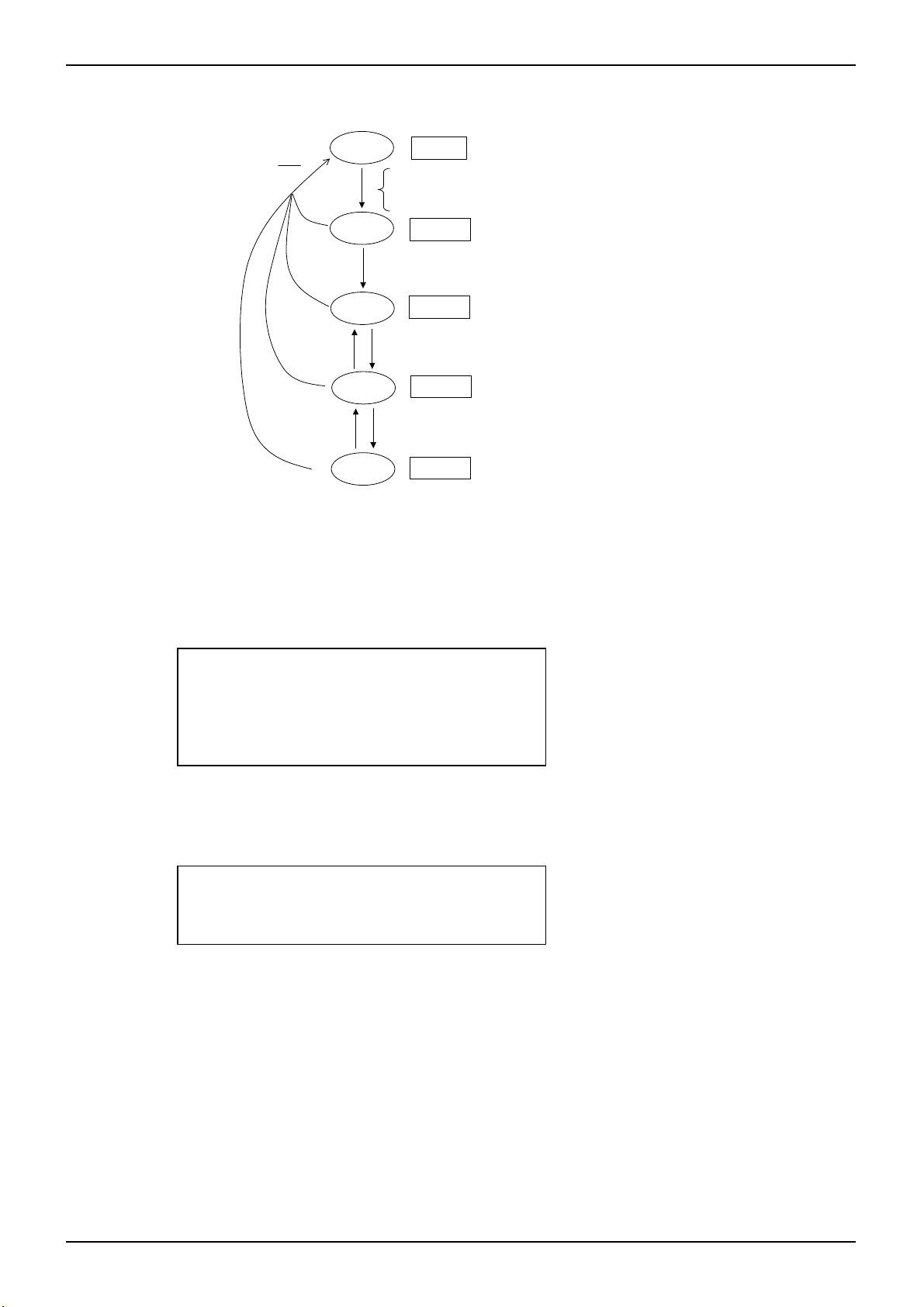

●LED Driver

The LED driver of 6ch is constructed as the ground plan.

Equivalence control is possible with LED1 - 4(LED4 can choose use/un-use with a register W4MD.).

LED5, LED6 is controllable individually.

As for LED5, LED6, grouping setting to the main control is possible, and main control becomes effective for the main group

in the allotment. LED5 and LED6 are setups of grouping to the main control.

When LED5 and LED6 are used by the individual control, a slope time setup (register THL and TLH) doesn't become

effective.

IMLED[6:0]

MLEDEN

MLEDMD

WPWMIN

LED1

LED2

LED3

LED4

W4MD

IW5[6:0]

W5EN

IW6[6:0]

W6EN

1

0

W5MD

1

0

W6MD

LED5

LED6

Fig.19

LED Composition which can be set up is the following.

The main, other1 and other2 are controllable to each.(Enable and current setting)

Main

(ALC,PWM)

Other1 Other2

6LEDs - -

5LEDs - -

5LEDs 1LED -

4LEDs - -

4LEDs 1 LED -

4LEDs 2 LEDs -

4LEDs 1 LED 1LED

3LEDs - -

3LEDs 1 LED -

3LEDs 2 LEDs -

3LEDs 1 LED 1LED

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

32/45

2010.07 - Rev.

Page 33

A

BD6083GUL

Technical Note

●ALC (Auto Luminous Control)

LCD backlight current adjustment is possible in the basis of the data detected by external ambient light sensor.

・Extensive selection of the ambient light sensors (Photo Diode, Photo Transistor, Photo IC(linear / logarithm)) is possible by

building adjustment feature of Sensor bias, gain adjustment and offset adjustment.

・Ambient data is changed into ambient level by digital data processing, and it can be read through I

2

C I / F.

・ Register setting can customize a conversion to LED current. (Initial Value is pre-set.)

・Natural dimming of LED driver is possible with the adjustment of the current transition speed.

Slope

process

DC current setup

WPWMIN

LED*

Main Grou p

setup

LCD

Backlight

Sensor

Always ON / Intermittence

SBIAS

SBIAS

SSENS

GC1

GC2

ADC

Control

Gain

PWM enabling

Conversion

Average

Logarithmic Conv.

Ambient Level

Current

Conversion

Slope Timer

Mode Sel ect

Gain Control ON/OFF

Ambient Level

Fig.20

(1)Auto Luminous Control ON/OFF

・ALC block can be independent setting ON/OFF.

・It can use only to measure the Ambient level.

Register: ALCEN

Register: MLEDEN

Register: MLEDMD

・Refer to under about the associate ALC mode and Main LED current.

ALCEN MLEDEN MLEDMD Sensor I/F LED control Mode Main LED current

0 0 x

0 1 0

OFF

( AMB(3:0)=0h )

0 1 1 IU0(6:0) (*1)

1 0 x

1 1 0

ON

1 1 1 ALC mode (*2)

(*1) At this mode, because Sensor I/F is OFF, AMB(3:0)=0h.

So, Main LED current is selected IU0(6:0).

(*2) At this mode, Main LED current is calculated (See(8)Convert LED Current)

It becomes current value corresponding to each brightness.

Effective also in ALC functional the case of not using it

:

OFF OFF -

ON Non ALC mode

OFF

ON

ALC mode

IMLED(6:0)

-

IMLED(6:0)

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

33/45

2010.07 - Rev.

Page 34

A

BD6083GUL

A

A

(2) I/V conversion

・External resistance for the I-V conversion (Rs)

are adjusted with adaptation of sensor characteristic

IOUT

SSENS voltage

VSSENS

Iout

VCC

Sensor IC

GND

SBIAS

SSENS

Rs

SBIAS

A/D

SGND

Rs : Sense resistance (A sensor output current is changed into the voltage value.)

SBIAS : Bias power supply terminal for the sensor

SSENS : Sense voltage input terminal

SSENS Voltage = Iout x Rs

Fig.21

Technical Note

Sensor Current (Iout)

mbient

Rs is large

Rs is small

SSENS Voltage (=Iout x Rs)

mbient

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

34/45

2010.07 - Rev.

Page 35

A

BD6083GUL

A

A

A

(3) Gain control

・Sensor gain switching function is built in to extend the dynamic range.

・It is controlled by register setup.

・When automatic gain control is off, the gain status can be set upin the manual.

Register : GAIN

・GC1 and GC2 are outputted corresponding to each gain status.

Example 1 (Use BH1621FVC) Example 2 Example 3

SBIAS

Application

example

VCC

IOUT

BH1621

GC1

GC2

GND

SSENS

GC1

GC2

SGND

Technical Note

High Gain mode

SSENS Voltage

uto Gain mode

SSENS Voltage

SBIAS

SSENS

1

9.5 (*1)

GC1

GC2

SGND

Low Gain mode

mbient

mbient

SBIAS

SSENS

GC1

GC2

SGND

Resister values are relative

Operating mode Auto Auto Fixed

GAIN setting 0 0 1

Gain status High Low High Low -

GC1 output

GC2 output L

: This means that it becomes High with A/D measurement cycle synchronously.

(*1) : Set up the relative ratio of the resistance in the difference in the brightness change of the High Gain mode and the Low Gain mode carefully.

L

L

L

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

35/45

L

2010.07 - Rev.

Page 36

A

BD6083GUL

A

A

A

A

A

A

A

(4) A/D conversion

・The detection of ambient data is done periodically for the low power.

・SBIAS and ADC are turned off except for the ambient measurement.

・The sensor current may be shut in this function, it can possible to decrease the current consumption.

・SBIAS pin and SSENS pin are pull-down in internal when there are OFF.

・SBIAS circuit has the two modes. (Usually ON mode or intermittent mode)

Register: ADCYC

Register: SBIASON

LCEN

DC Cycle

DCYC

16 times

SBIAS Output

DC Movement

GC1, GC2

MB(3:0)

wait= 64ms(typ)

T

Toprt= 80.4ms(typ)

(Operate time)

(Wait time)

TAD= 16.4ms(typ)

(A/D conversion time)

MB(3:0 )

When SBIASON=1

D start signal

GC1, GC2=00

16 times measurement

Fig.22

(5) Average filter

・Average filter is built in to rid noise or flicker. Average is 16 times

(6) Ambient level detection

・Averaged A/D value is converted to Ambient level corresponding to Gain control.

・Ambient level is judged to rank of 16 steps by ambient data.

・Ambient level is output through I

2

C.

Register: AMB(3:0)

GAIN 0 1

GAIN Setting Low High -

Ambient Level SSENS Voltage

0h

VoS×0 / 256 VoS×0 / 256

1h VoS×1 / 256 VoS×1 / 256

2h VoS×2 / 256 VoS×2 / 256

3h

4h

5h VoS×0 / 256

6h VoS×1 / 256

7h

8h

9h

Ah

Bh

Ch

Dh

Eh

Fh

※In the Auto Gain control mode, sensor gain changes in gray-colored ambient level.

※“/”: This means that this zone is not outputted in this mode.

VoS

VoS

VoS

VoS

VoS

VoS×2 / 256

VoS×3 / 256

VoS×4 / 256

VoS×6 / 256

VoS

×7 / 256

VoS

×11 / 256

×12 / 256

VoS

×20 / 256

VoS

VoS

×21 / 256

VoS

×36 / 256

×37 / 256

VoS

×64 / 256

VoS

VoS

×65 / 256

×114 / 256

×115 / 256

×199 / 256

×200 / 256

×255 / 256

VoS

×3 / 256

VoS

×4 / 256

×5 / 256

VoS

×7 / 256

VoS

VoS

×8 / 256

VoS

×12 / 256

×13 / 256

VoS

×21 / 256

VoS

×22 / 256

VoS

VoS

×37 / 256

VoS

×38 / 256

×65 / 256

VoS

×66 / 256

VoS

VoS

×113 / 256

VoS×114 / 256

VoS×199 / 256

VoS×200 / 256

VoS×255 / 256

×3 / 256

VoS

VoS

×4 / 256

VoS

×5 / 256

×6 / 256

VoS

×7 / 256

VoS

VoS

×9 / 256

VoS

×10 / 256

×13 / 256

VoS

×14 / 256

VoS

VoS

×19 / 256

VoS

×20 / 256

×27 / 256

VoS

×28 / 256

VoS

VoS

×38 / 256

VoS

×39 / 256

×53 / 256

VoS

×54 / 256

VoS

VoS

×74 / 256

VoS×75 / 256

×104 / 256

VoS

×105 / 256

VoS

VoS

×144 / 256

VoS

×145 / 256

×199 / 256

VoS

×200 / 256

VoS

VoS

×255 / 256

ADone= 1.024ms(typ)

T

Technical Note

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

36/45

2010.07 - Rev.

Page 37

A

BD6083GUL

Technical Note

(7)Convert LED Current

・LED current can be assigned as each of 16 steps of the ambient level.

・Convert LED Current by Min Current setting,Max Current setting,step setting and curbu setting.

Register: IU0

IU1

CRV

STEP [2:0]

Conversion Table (Initial Value) Step Table Setting

Ambient

Level

Coefficient

CRV=0 CRV=1 CRV=0 CRV=1

Ambient

Level

0h 0 0 8h 6.5 8

1h 0.25 1 9h 8 9

2h 0.5 2 Ah 10 10

3h 1 3 Bh 12 11

4h 1.5 4 Ch 13 12

5h 2.5 5 Dh 14 13

6h 3.5 6 Eh 15 14

7h 5 7 Fh 16 15

Coefficient

STEP[2:0] ΔI

000 1.0mA

001 1.1mA

010 1.2mA

011 1.3mA

100 1.6mA

101 1.7mA

110 1.8mA

111 1.9mA

I=

ΔI×Coefficient+IU0

※ I≧IU1:I=IU1

※ ΔI×Coefficient

Drop under 1mA

The example of a setting

IU0=4mA

IU1=20mA

30

25

20

15

30

25

20

15

SLP=1mA

SLP=1.1mA

SLP=1.2mA

SLP=1.3mA

SLP=1.6mA

SLP=1.7mA

SLP=1.8mA

SLP=1.9mA

CRV=0

SLP=1mA

SLP=1.1mA

SLP=1.2mA

SLP=1.3mA

SLP=1.6mA

SLP=1.7mA

SLP=1.8mA

SLP=1.9mA

CRV=1

LED Current(mA)

LED Current(mA)

10

10

5

0

03691215

AMB

Ambient Level

Ch Fh0h 3h 6h 9h

5

0

0h 3h 6h 9h

03691215

AMB

Ambient Level

Ch

C

Fh

Fig.23 Fig.24

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

37/45

2010.07 - Rev.

Page 38

A

BD6083GUL

(8) Slope process

・Slope process is given to LED current to dim naturally.

・LED current changes in the 256Step gradation in sloping.

・Up(dark→bright),Down(bright→dark) LED current transition speed

are set individually.

Register: THL (3:0)

Register: TLH (3:0)

・Main LED current changes as follows at the time as the slope.

TLH (THL) is setup of time of the current step 2/256.

TLH

25.6mA

256

=0.1mA

THL

Fig.25

(9) LED current reset when mode change

・When mode is changed (ALC↔Non ALC),

it can select the way to sloping.

Register : MDCIR

“0” : LED current non-reset when mode change

“1” : LED current reset when mode change

Technical Note

Current Data which is set

LED Current

TLH(3:0)

NonALC

NonALC

THL (3:0)

mode

mode

TLH(3:0)

Main LED current

Up/Down transition Speed

is set individually

time

Zoom

Main LED current

time

NonALC

mode

IMLED(6:0) IMLED(6:0)

ALC

mode

IU*(6:0)

MDCIR= “0”

Main LED current

0mA

time

NonALC

mode

IMLED(6:0) IMLED(6:0)

Main LED current

0mA

ALC

mode

IU*(6:0)

MDCIR= “1”

time

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

38/45

2010.07 - Rev.

Page 39

A

BD6083GUL

A

f

Technical Note

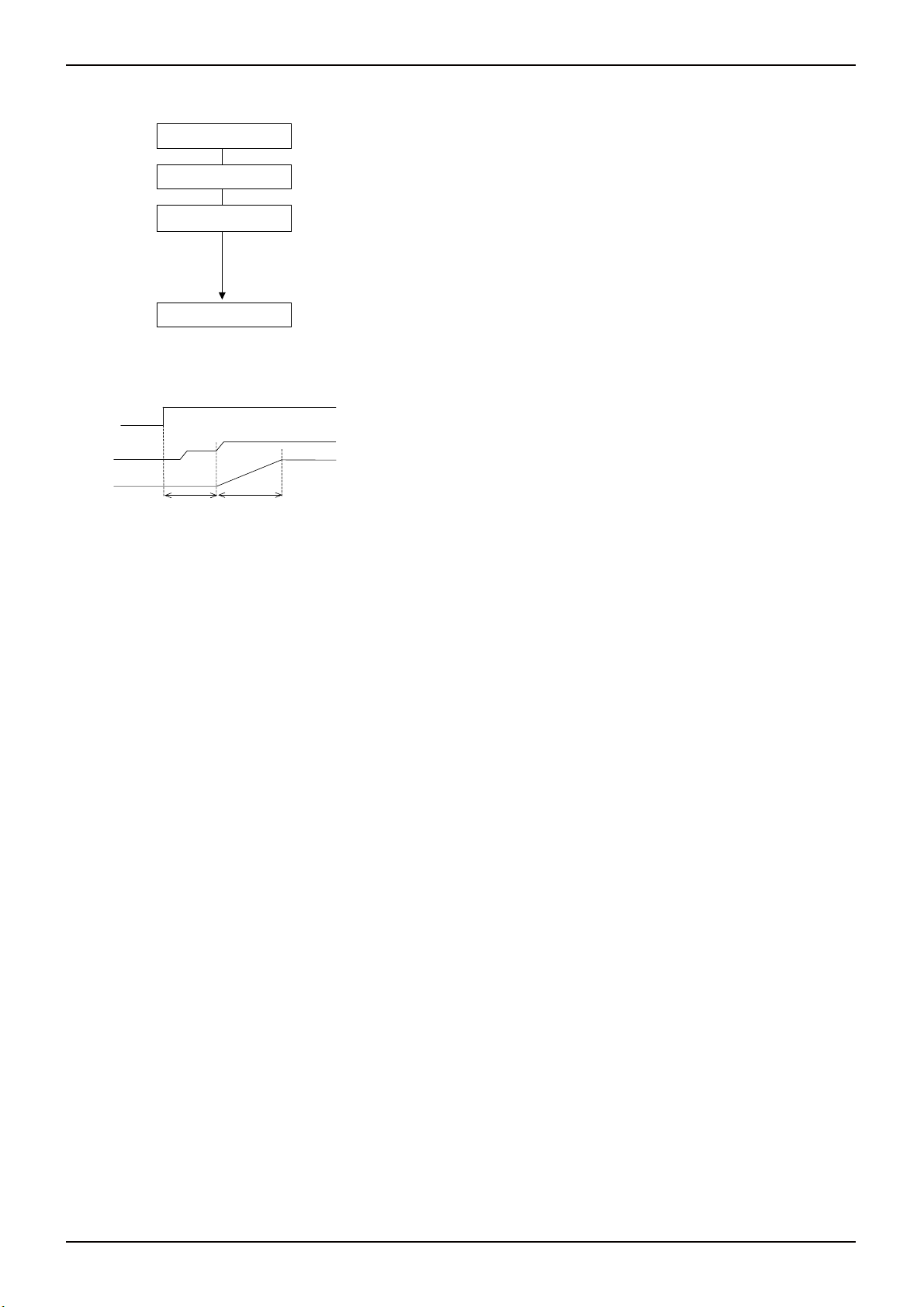

(10) Current adjustment

・When the register setting permits it, PWM drive by the external terminal (WPWMIN) is possible.

Register : WPWMEN

・It is suitable for the intensity correction by external control, because PWM based on Main LED current of register

setup or ALC control.

WPWMEN

(Register)

0

1

" Normal operation " depends on the setup of each register.

WPWMIN(External Pin) Main group LED current

L Normal operation

H Normal operation

L Forced OFF

H Normal operation

EN(*)

Internal Soft-Start Time

DC/DC Output

WPWMIN input

WPWMEN

LED Current

EN(*) : it means “MLEDEN” or “W*EN”.

It is possible to make it a WPWMIN input and WPWMEN=1 in front of EN(*).

PWM drive becomes effective after the time of an LED current standup.

When rising during PWM operation, as for the standup time of a DC/DC output, only the rate o

PWM Duty becomes late. Appearance may be influenced when extremely late frequency and

extremely low Duty are inputted.

Please secure 250 μs or more of H sections at the time of PWM pulse Force.

Fig.26

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

39/45

2010.07 - Rev.

Page 40

A

BD6083GUL

V

V

●I/O

When the RESETB pin is Low, the input buffers (SDA and SCL) are disabling for the Low consumption power.

When RESETB=L, output is fixed at “H.”

Technical Note

EN

Level shifter

Logic

SCL

(SDA)

RESETB

Fig.27

Special care should be taken because a current path may be formed via a terminal protection diode, depending on an I/O

power-on sequence or an input level.

●About the start of LDO1~LDO4

It must start as follows.

BAT

IO

RESETB

LDO1EN or LDO2EN or

LDO3EN or LDO4EN

LDO1O or LDO2O or

LDO3O or LDO4O

(LDO output)

T

VBATON

T

VIOON=min 0.1ms

T

RSTB=min 0.1ms

T

RISE = max 1m s

T

VBATOFF

T

VIOOFF=min 1ms

T

RST=min 0ms

Fig.28

<Start Sequence>

VBAT ON (Enough rise up) → VIO ON (Enough rise up) → Reset release → LDO ON (Register access acceptable)

<End Sequence>

LDO OFF → Reset → VIO OFF (Enough fall down) → VBAT OFF

●About the pin management of the function that isn't used and test pins

Setting it as follows is recommended with the test pin and the pin which isn't used.

Set up pin referring to the “Equivalent circuit diagram” so that there may not be a problem under the actual use.