Page 1

Kurzcharakteristik

system) oder separat bereitgestellt werden.

Die Steckeinheit - Zentrale Recheneinheit ZVE K 2521 ... K 2524 - ist eine zentrale

Baugruppe das Mikrorechnersystems K1520 und kann an das realisierte Bussystem

angeschlossen worden, über des Daten-, Adreß- und Steuersignale mit anderen

Steckeinheiten des X 1520 ausgetauscht worden können. Weiterhin ist der Einsatz

der Steckeinheit als selbständiger Mikrorechner (Single-board-Rechner) möglich.

Die ZRE ist auf der Systembasis das Schaltkreises U880 aufgebaut.

Die Grundvariante K 2521 umfaßt die zentrale Verarbeitungseinheit (ZVE), den

Speicher (RAM, PROM), den Zähler/Zeitgeber (CTC) und die parallele Ein/Ausgabe

mit Zusatzelektronik sowie quarzstabilisertem Taktgenerator und Rücksetzschaltung.

Durch Abrüstung von Baugruppen worden die Varianten X 2522 (ohne Taktgenerator),

K 2523 (ohne CTC) und K 2524 (ohne Taktgenerator und CTC) abgeleitet.

Die ZVE kann Daten aus dem Speicher oder von peripheren Geräten verarbeiten und

den Datentransport mit dem Speicher und Anschlußsteuereinheiten organisieren.

Dabei wird die Arbeitsweise der ZVE durch das im Speicher des X 1520 enthaltene Programm bestimmt. Der Zähler/Zeitgeber kann zur Echt-Zeit-Verarbeitung Unterbrechungen veranlassen und dadurch die ZVE entlasten. Über den Parallel

Ein/Ausgabebaustein können ZRESteckeinheiten untereinander oder externe Geräte

an die ZRE gekoppelt werden.

An das Kopplungsinterface einen Masterrechners können bis zu drei weitere

Slaverechner zu einem Mehrrechnersystem zusammengeschaltet werden.

Der Taktgenerator erzeugt den im Mikrorechner K 1520 erforderlichen Systemtakt,

und die Rücksetzschaltung bewirkt nach dem Einschalten der Stromversorgung

den logischen Ausgangszustand.

Technische Beschreibung

Takterzeugung (nur K 2521 und K 2523)

Ein Quarzgenerator erzeugt eine Grundfrequenz von 9830,4 KHz ± 0,1 %. Diese

wird mit Hilfe eines Dualzählers auf die Systemfrequenz von 2,4576 MHz + 0,1 %

geteilt (Testverhältnis 1:1). Ein folgender Treiber speist den Koppelbus mit dem

Signal TAKTO. Diese Verbindung kann durch die Wickelbrücke X6 - X7 unterbrochen werden. Das ist z.B. notwendig, wenn der Takt separat. erzeugt wird,

wenn dieser vom Entwicklungssystem über den Busverstärker K 4120 oder von

einer anderen ZRE (s.a. Mehrrechnersystem) zugeführt wird.

Der Treiber gewährleistet folgende elektrische Bedingungen:

Low-Ausgangsspannung U0L 0,4 V bei I0L

High-Ausgangsspannung U0H 2,4 V bei I0H

Taktzykluszeit tz = 407 ns +/- 0,1 %

Taktentkopplung

Unabhängig vom Ort der Takterzeugung wird das Signal TAKTO auf dem Koppelbus

eingespeist und kann hier an andere Rechner oder Geräte weitergeleitet werden.

In jedem Falle wird auf der ZRE eine Taktentkopplung realisiert, indem des Signal

TAKTO des Koppelbus verstärkt und als Signal TAKT an der entsprechenden

Klemme des Systembus eingespeist wird.

Die Typen K 2521 und K 2523 erzeugen TAKTO selbst.

Für die Typen K 2522 und K 2524 muß TAKTO von einem anderen Rechner

(Mehrrechnersystem), vom Busverstärker K 4120 (Kopplung mit Entwicklungs-

Page 2

Rücksetzschaltung

Nach dem Einschalten der Betriebsspannung 5P wird ein Kondensator aufgeladen

und mit einem Schwellwertschalter überwacht. Solange die Einschaltschwelle noch

nicht erreicht ist, wird das Systembussignal /RESET auf "low" über einen Treiber mit

offenem Kollektor gezogen. Am Treiber ist ein Kollektorwiderstand von 1KOhm

angeordnet. Damit werden folgende elektrische Daten realisiert:

U0L0,4 V für I0L5 mA

U0H2,4 V für I0H- 2,25 mA.

Die Zeit vom Zuschalten der 5P bis zur "low-high"-Flanke von /RESET beträgt

mindestens 300 ms.

Zentrale Verarbeitungseinheit (ZVE)

Struktur

Die ZVE besteht aus dem Mikroprozessor (MP) Q300 (U880) und der Ergänzungselektronik. Der MP realisiert die logischen Funktionen der ZVE.

Die Ergänzungselektronik gewährleistet die elektrischen Bedingungen für die Ankopplung an den Systembus des MR K 1520 und besteht aus folgenden

Komponenten

- Verstärker für /RESET und TAKT (mit Ziehwiderstand zur Pegelanhebung

mitbenutzt von PIO und CTC).

- Arbeitswiderstände und Abblockdioden für ZVE-Steuersignale mit offenem Kollektor

bzw. Drain (/NMI, /WAIT, /INT, /BUSRQ).

- Bildung der Bus-Anforderungsbestätigung /BA0 durch eine Stufe mit offenem Kollektor

(zum Zweck den externen BUS-Abschaltens im WAIT-Zustand) aus dem Signal /BUSAK.

- Verstärker für Adreßbus AB0:15, Datenbus DB0:7 und Systemsteuersignale

/MREQ, /M1, /IORQ, /RD, /WR, /RFSH, /HUT, die mit BA0 hochohmig geschaltet werden:

/M1 und /HALT besitzen Ziehwiderstände, die dann an ihnen High-Pegel erzeugen.

Nur die Datenbusverstärker arbeiten bidirektional und werden mit RD oder M1 in

Richtung ZVE gesteuert.

Funktion

Die Aufgabe der ZVE besteht in der Abarbeitung der im Speicher stehenden

Programme und in der Reaktion auf Unterbrechungssignale von externen Einheiten.

Dazu muß die ZVE über den Systembus mit den Speicher- und E/A-Einheiten

Informationen austauschen.

Die Ergänzungselektronik hat keinen Einfluß auf die Funktion das Schaltkreises

Q300 (U880).

All seine programmtechni schon Eigenschaften sind nutzbar.

Folgende elektrische Besonderheiten sind allerdings zu beachten:

-Im Ruhezustand verstärken die Datenbustreiber in Richtung Systembus

- Auf der ZRE sind alle Widerstände der Systembusleitungen für offenen

Kollektor bzw. Drain vorhanden

-/BA0 ist mit offenem Kollektor ausgeführt

-Auch /RFSH, /M1 und /HALT werden bei BUSAK hochohmig geschaltet.

/M1 und /HALT werden aber dabei durch Widerstände auf high gezogen.

Page 3

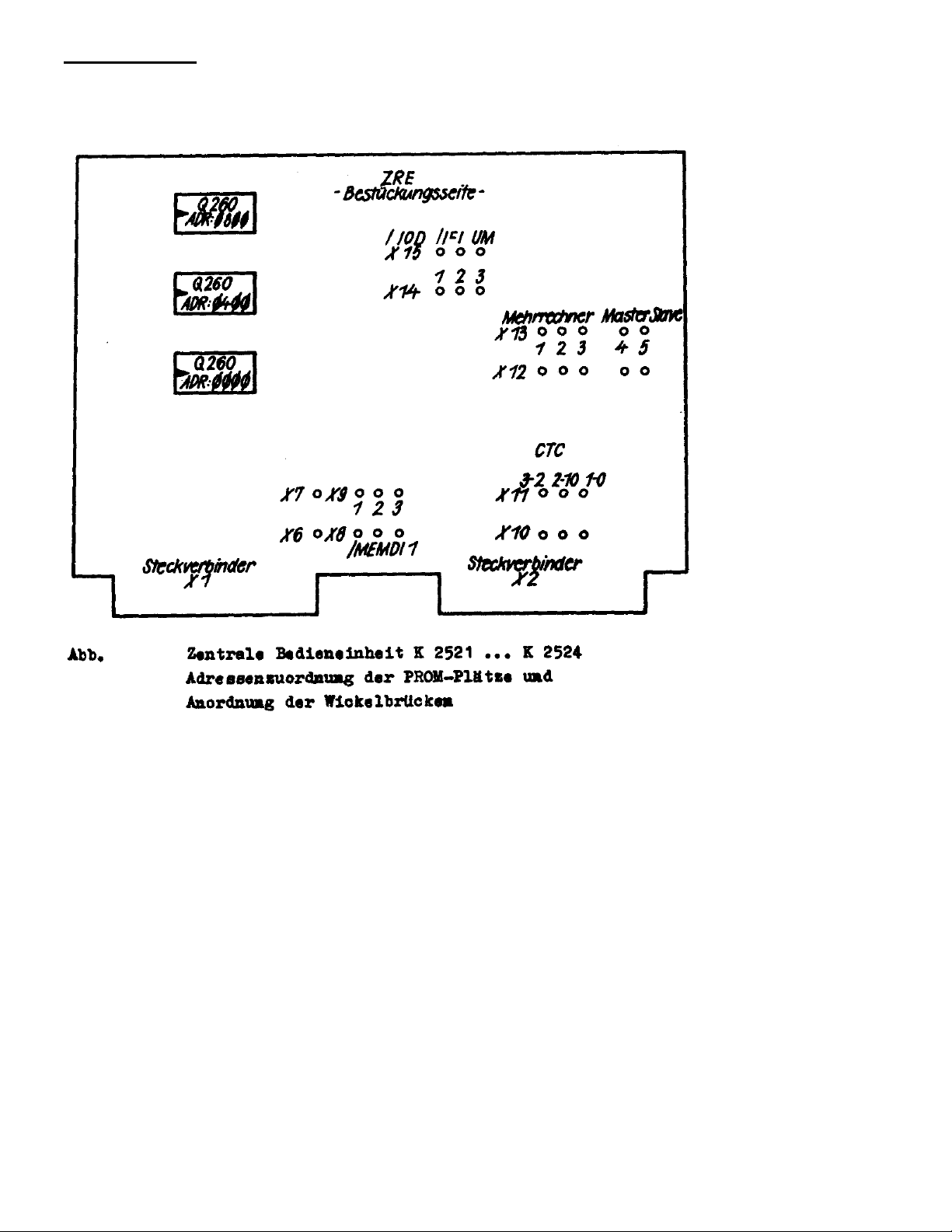

Struktur

Die Speichereinheit besteht aus einem 3K Byte Festwertspeicher und einem

1K Byte Schreib-Lese-Speicher. Der Festwertspeicher wird durch 3 EPROM vom

Typ U555 realisiert. Diese sind auf Steckfassungen angeordnet und dadurch leicht

austauschbar. Sie belegen den Adressenbereich von 0000H bis 0BFFH.

Die Zuordnung der Adreßbereiche zu den Bestückungsplätzen ist aus der Abbildung

zu ersehen. Der Schreib-Lese-Speicher wird bitweise durch 8 statische

n-MOS-RAM-Schaltkreise vom Typ U202 (oft auch SU-Typ KP565RY2) realisiert.

Er belegt den Adreßbereich von 0C00H bis 0FFFH.

Der gesamte Speicher ist mit dem Systembus über folgende Signale verbunden:

AB0:15 Adreßbus

DB0:7 Datenbus

/MEMRQ Speicheranforderung (negiert)

/RD Lesesteuersignal (negiert)

/WR Schreibsteuersignal (negiert)

/MEMDI Speicherfreigabe (negiert) evtl. durch Umwickeln ersetzt

durch /MEMDI1 oder /MEMDI2

/RDYBereitsignal des Speichers (negiert)

/RFSH Refresh-Signal (negiert)

Die elektrischen Bedingungen dieser Signale entsprechen den allgemeinen

Forderungen des Systembusses K 1520.

Standerdmäßig wird zur Speichersperrung das Signal MEMDI verwendet. Der

Anwender kann aber auch wahlweise die Signale MEMDI1 bzw. MEMD12 verwenden,

die er allerdings selbst (negiert) bereitstellen muß. Auf diese Weise ist eine Erweiterung des Speicheradreßbereiches über 64K hinaus möglich.

Die Auswahl erfolgt durch die Wickelbrücken

X8:1 - X9:1 für /MEMDI

X8:2 - X9:2 für /MEMDI1

X8:3 - X9:3 für /MEMDI2

Funktion

Die Aktivierung des Speichers erfolgt durch /MREQ = low, falls AB12 bis AB15 low

/RFSH, /MEMDI bzw. /MEMDI1 bzw. /MEMDI2 (je nach Verdrahtung) high sind.

Daraufhin wird den Signal /RDY (offener Kollektor) auf low gezogen, die

Decodierung der Adreßbits AB10 und AB11 sowie der Datenbusverstärker aktiviert.

Dabei werden vier CS-Signale gebildet, die zur Ansteuerung der vier 1K ByteSpeichermatrizen dienen. Auf welches Byte innerhalb der Matrix zugegriffen wird,

entscheiden die die Speicherschaltkreise direkt steuernden Adreßbits AB0 bis AB9.

Beim RAM bewirkt das Signal /WR = low das Einschreiben der verstärkten Datenbussignale DB0 bis DB7 in den Speicher. Dabei ist der DB-Puffer durch /RD = high in

Richtung zum Speicher gesteuert und legt die Daten an dessen Eingänge. Beim

Lesen wird der DB-Puffer durch /RD - low in Richtung Systembus gesteuert und

das von der mit CS aktivierten Speichermatrix gelieferte Datenbyte verstärkt.

Page 4

Zähler/Zeitgeber

Der Zähler/Zeitgeber ist nur auf den Typen K 2521 und K 2522 realisiert.

Page 5

Struktur

Der Zähler/Zeitgeber besteht aus dem Schaltkreis Q302 (CTC U857) und der

Ergänzungselektronik. Die Ergänzungselektronik dient der Anpassung des

Q302 an die elektrischen und logischen Bedingung des Systembusses K 1520.

Sie wird mit den Q301 (PIO U855) gemeinsam benutzt und besteht im

wesentlichen aus Datenpuffer mit Richtungssteuerung und Adressenentschlüsselung zur Bildung des Bausteinauswahl- und RDY-Signals.

Systembus

Die elektrischen und logischen Bedingung« den CTC entsprechen denen des

Systembusses K 1520, lt. TGL 37271.

Page 6

Koppelbus_

Die anwenderspezifischen Ein- und Ausgangssignale des CTC

sind an den Koppelbus geführt und konstruktiv wie folgt angeordnet:

Steckver.-Klemme

CLK/TRG0 X2:B25

CLK/TRG1 X2:B24

CLK/TRG2 X2:B23

CLK/TRG3 X2:A22

Nulldurchgangs-/Triggerausgänge

ZC/TO0 X2:A25

ZC/TO1X2:A24

ZC/TO2 X2:A23

Funktion

Der Anwender kann alle Möglichkeiten nutzen die der Schaltkreis Q302 (CTC)bietet.

Die oben angeführten Signale werden unbeschaltet zur Verfügung gestellt. Durch

Wickelbrücken können die Kanäle aber auch wie folgt in Reihe geschaltet werden

X10:3 - X11:3 : ZC/TO0CLK/TRG1

X10:2 - X11:2 : ZC/TO1CLK/TRG2

X10:1 - X11:1 : ZC/TO2 CLK/TRG3

Der Schaltkreis wird vom Systembus über die Ergänzungselektronik angesteuert,

falls auf dem Adreßbus AB7 bis AB0 die Adressen 80H bis 83H liegen, /IODI, /M1

high und /IORQ low sind. Die Verdrahtung der Bits AB0 und AB1 realisiert folgende

Bedeutung der Adressen

AB7:0Kanal

80H0

81H1

82H 2

83H3

Der CTC besitzt in der Interruptkette der ZRE die höchste Priorität. Der Datenbuspuffer

ist bidirektional und wird in Richtung Systembus gesteuert, wenn der CTC ausgewählt

wird und dabei /RD = low ist (LeseZugriff) oder /IORQ und /M1 low, IEI und /IE0 high

sind (Unterbrechungsquittung).Bei Ein- und Ausgabezugriff sowie Interruptanerkennung

wird jeweils /RDY auf low gezogen.

Page 7

Page 8

Parallele Ein/Ausgabe

Struktur

Die Schaltung zur parallelen Ein- und Ausgebe besteht aus dem Schaltkreis

Q301(U855), einer Ergänzungselektronik und einer Koppelelektronik. Die

Ergänzungselektronik dient der Anpassung des Q301 an die elektrischen

und logischen Bedingungen den Systembusses K 1520. Sie wird bei den

Typen K 2521 und K 2522 mit dem Q302 (CTC) gemeinsam genutzt und

besteht aus Datenverstärkern mit Richtungssteuerlogik, Adressenentschlüsselung

zur Bildung der CS-Signale und des RDY-Signals, der Auswahl des IEI-Signale

mit einer Look-Ahead-Carry-Schaltung sowie einigen Verstärkern. Der Q301 kann

zur Kopplung von bis zu vier K 1520 benutzt werden. Er besitzt dazu eine

Koppelelektronik zur Synchronisierung des Datenaustausches. Diese kann durch

Wickelverbindungen vom Q301 getrennt oder für die Verwendung als Master- bzw.

Slave-Rechner verdrahtet werden.

Page 9

Anschlußbedingungen

Koppelbus

Verwendung zur parallelen Ein- und Ausgabe

Die elektrischen und logischen Bedingungen entsprechen denen des Schaltkreises Q301. Konstruktiv sind Signale wie folgt angeordnet:

- Verwendung zur Mehrrechner-Kopplung

Die Mehrrechnerkopplung verwendet einen Koppelbus aus 8 Datenleitungen, 2

Datensynchronisationsleitungen, 7 Leitungen zur Adressierung, Quittierung und

Statuskennzeichnung, eine Leitung zur Verbindung der /RESET-Signale und (bei

Verwendung eines zentralen Taktgenerators) eine Leitung zur Verteilung des zentralen

Taktes. Sie sind logisch und elektrisch aufeinander abgestimmt und werden über alle

vier Rechner durchgehend verdrahtet. Konstruktiv sind die Signale wie folgt

angeordnet:

Page 10

Verwendung zur Ein- und Ausgabe

Hierbei sind vom Anwender alle Möglichkeiten des Schaltkreises Q301 (PIO)

nutzbar. Das peripherieseitige Interface wird unbeschaltet zur Verfügung gestellt.

Der Schaltkreis wird vom Systembus über die Ergänzungselektronik angesteuert,

falls auf dem Adreßbus AB7 bis AB0 die Adressen 84H bis 87H liegen.

/M1, /IODI high und /IORQ low sind. Durch disjunktive Verknüpfung von M1 mit

RESET wird das Rücksetzen der PIO ermöglicht. Die Verbindung von AB0 mit

B/A-SEL und AB1 mit C/D-SEL realisiert die folgende Bedeutung der Adressen:

AB7: 0 Bedeutung des Bytes auf DB0:7

84H Daten von/zu Port A

85H Daten von/zu Port B

86H Steuerwort zum Port A

87H Steuerwort zum Port B

Durch Verbindung des Signals IEI der PIO mit IEO des CTC wird beim K 2521 und

K 2522 die Interruptpriorität nach dem CTC eingeordnet. Der Datenbusverstärker

ist bidirektional und wird in Richtung Systembus gesteuert, wenn die PIO ausgewählt

wird und dabei /RD - low ist (Lesezugriff) oder /IORQ und /M1 low sind und IEI und /IEO

high sind (Unterbrechungsquittung).

Bei Ein- und Ausgabezugriff sowie Interruptanerkennung wird jeweils /RDY auf low

Page 11

1. Auswahl von /IODI durch Verbindung X14:1 - X15:1

(Normalfall:ZRE hat höchste Priorität)

Auswahl von /IEI des Systembus durch Verbindung X 14:2 - X15:2 (ZRE wird

innerhalb der Prioritätskette eingereiht).

Auswahl von UM durch Verbindung X14:3 - Z15:3 (für spezielle Kopplung mit

dem Entwicklungssystem MRES 20 über BVE K 4120).

Verwendung zur Mehrrechnerkopplung

Durch eine zusätzliche Koppelelektronik und spezielle Verdrahtung des Koppelbusses ist hier der Q301(PIO) nur noch eingeschränkt nutzbar. Die Verbindung

mit dem Systembus entspricht der Verwendung als Parallel-E/A-Interface.

Durch die Koppelverdrahtung entsteht ein Mehrrechnersystem aus einem Master

(gekennzeichnet durch das Masterregime der Koppelelektronik) und bis zu drei

Slaves (gekennzeichnet durch das Slaveregime der Koppelelektronik).

Der Datenaustausch kann nur zwischen Master und jeweils einem aktiven Slave

erfolgen.

Die Funktionen des Kopplungsinterface werden vom Schaltkreis Q301 (PIO)

wie folgt realisiert.

Port B arbeitet im Modus 3. Bit B0 des Masters realisiert das Statuskennzeichen PB0,

welches die Übertragungsrichtung kennzeichnen kann. In den Slaves wird PBO als

Bit 0 des Porto B empfangen Das, Bit B1 des Q301 einen jeden Rechners stellt im

High-Zustand die Funktionsfähigkeit der Koppelelektronik her, d.h. die Bereitschaft zur

Datenübertragung über die Datenleitungen. Die Datenleitungen PAO:7 des Koppelbusses werden direkt von den Datenleitungen A/ :7 des Porto A des Q301 gebildet,

welches je nach Übertragungsrichtung im Modus 0 (Ausgabe) oder 1 (Eingabe)

arbeiten muß.

Im Slave werden das eigene ARDY und B1 des Q301 und PRDY (welches ARDY und

B1 des Masters entspricht) konjunktiv verknüpft und ein etwa 1s langer Strobe-Impuls

erzeugt, der den Datenaustausch im Slave und Master (dort als PSTB) quittiert.

Während der Einleitung des Datenaustausches vom Master

wird der jeweilige Slave durch die Bits PB2 bis PB4 (d.h. B2 bis B4 von Port B

des Q301) adressiert. Leitet ein Slave die Übertragung ein, so erfolgt die

Adressierung durch die Bits PB5:7 (d.h. B5:7 des Q301). Durch die Adressierung

wird im jeweiligen Partner eine Unterbrechung ausgelöst, die nach Vorbereitung

des Datenaustausches zur Quittierung über die jeweiligen Adreßleitungen (PB2:4

zum Slave, PB5:7 zum Master führt.

Von diesen Funktionen ausgehend muß während der Initialisierungsphase

folgende Programmierung des Q301 erfolgen:

Betriebssteuerwort Port A Master OFH (Mode 0)

Slave 4FH (Mode 1)

Betriebssteuerwort Port B CFH (Mode 3)

Bit-E/A-Steuerwort Port B Master E0H

Slave 1 DDH

Slave 2 BDH

Slave 3 7DH

Interruptvektor (niederer Adressenteil der Interrupt-Tabellen-Zeile:

programmspezifisch festgelegt).

Page 12

Interruptsteuerwort Port A87H

Interruptsteuerwort Port B B7H

Interruptmaskenwort Port B Master 1FH

Slave 1 FBH

Slave 2 F7H

Slave 3 EFH

Vor dem Setzen des Interruptsteuerwortes und der Interruptmaske in irgend einem

Rechner muß programmäßig gewährleistet werden, daß die Ausgabebits von Port B

in allen Rechnern auf low gesetzt sind.

Entsteht in einem Rechner eine Bedingung zum Datenaustausch, so wird durch

Adressierung des Partners der Verbindungsaufbau eingeleitet. Nach dem Setzen

des Status PBO vom Master und dem Aktivieren der Koppelelektronik durch die

jeweiligen Bit 1 des Port B wird des Quittierungssignal zurückgeschickt. Beide

Rechner verzweigen in die Datenaustauschroutine die den üblichen Datenaustausch

über die Ports A abwickeln. Danach erfolgt der Abbau der Verbindungen durch Rücksetzen der Adreß- und Quittungsleitungen.

Loading...

Loading...