Page 1

R

- TLP-1071XL

- TLP-1071XL

TLP-1071XL

Service Manual

Service Manual

Page 2

Page 3

: .

r::---ì

I ~w>

00",- I

..o~Z

I uo~ I

Iou_u

w'-

~

O

~N

Q.~

wU

w-

Page 4

ALlGNMENTPROCEDURES I

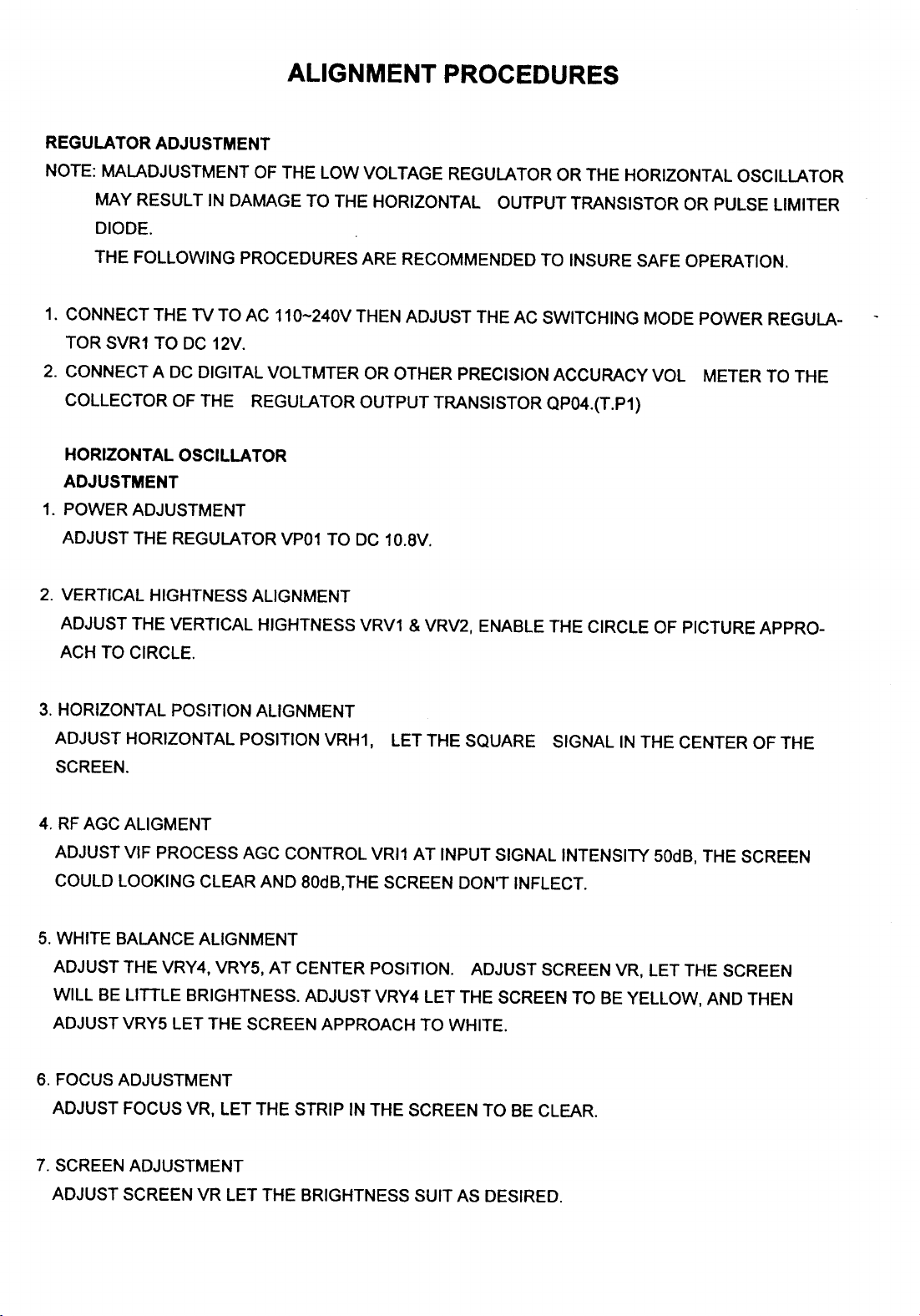

REGULATORADJUSTMENT

MAY RESULT IN DAMAGE TO THE HORIZONTAL OUTPUTTRANSISTOR OR PULSE LlMITER

DI ODE.

THE FOLLOWING PROCEDURES ARE RECOMMENDED TO INSURE SAFE OPERATION.

1. CONNECT THE TV TO AC 11 0-240V THEN ADJUST THE AC SWITCHING MODE POWER REGULA-

2. CONNECT A DC DIGITAL VOL TMTER OR OTHER PRECISION ACCURACY VOL METER TO THE

HORIZONTAL OSCILLATOR

ADJUSTMENT

1. POWER ADJUSTMENT

ADJUST THE REGULATOR VPO1 TO DC 10.8V.

2. VERTICAL HIGHTNESS ALlGNMENT

ADJUST THE VERTICAL HIGHTNESS VRV1 & VRV2, ENABLE THE CIRCLE OF PICTURE APPRO-

ADJUST HORIZONTAL POSITION VRH1, LET THE SQUARE SIGNAL IN THE CENTER OF THE

SCREEN.

4. RF AGC ALiGMENT

ADJUST VIF PROCESS AGC CONTROL VRI1 AT INPUT SIGNAL INTENSITY 50dB, THE SCREEN

COULD LOOKING CLEAR AND 80dB,THE SCREEN DON'T INFLECT.

5. WHITE BALANCE ALlGNMENT

ADJUST THE VRY4, VRY5, AT CENTER POSITION. ADJUST SCREEN VR, LET THE SCREEN

WILL BE LITTLE BRIGHTNESS. ADJUST VRY4 LET THE SCREEN TO BE YELLOW, AND THEN

ADJUST VRY5 LET THE SCREEN APPROACH TO WHITE.

6. FOCUS ADJUSTMENT

ADJUST FOCUS VR, LET THE STRIP IN THE SCREEN TO BE CLEAR.

7. SCREEN ADJUSTMENT

ADJUST SCREEN VR LET THE BRIGHTNESS SUIT AS DESIRED.

Page 5

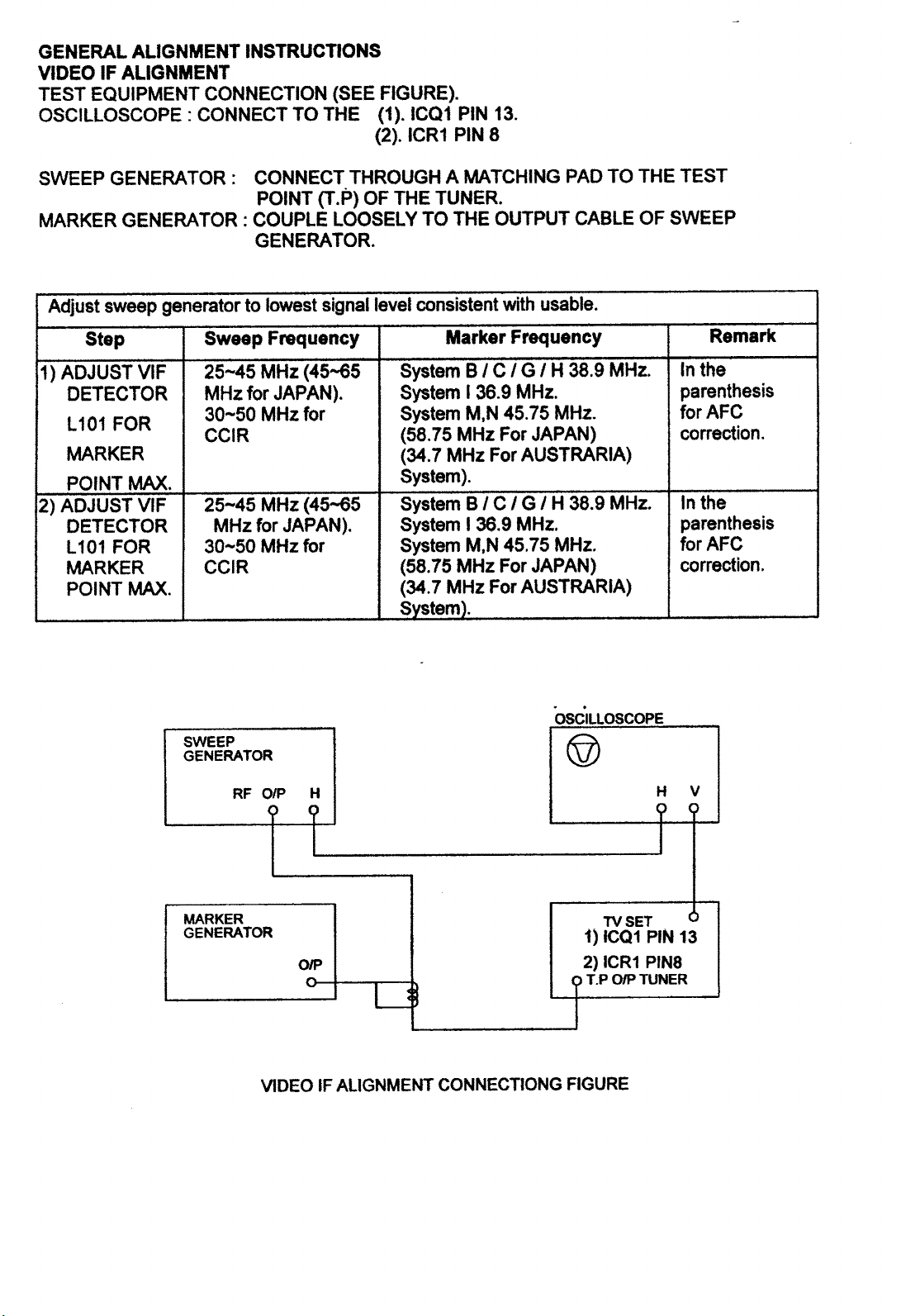

Page 6

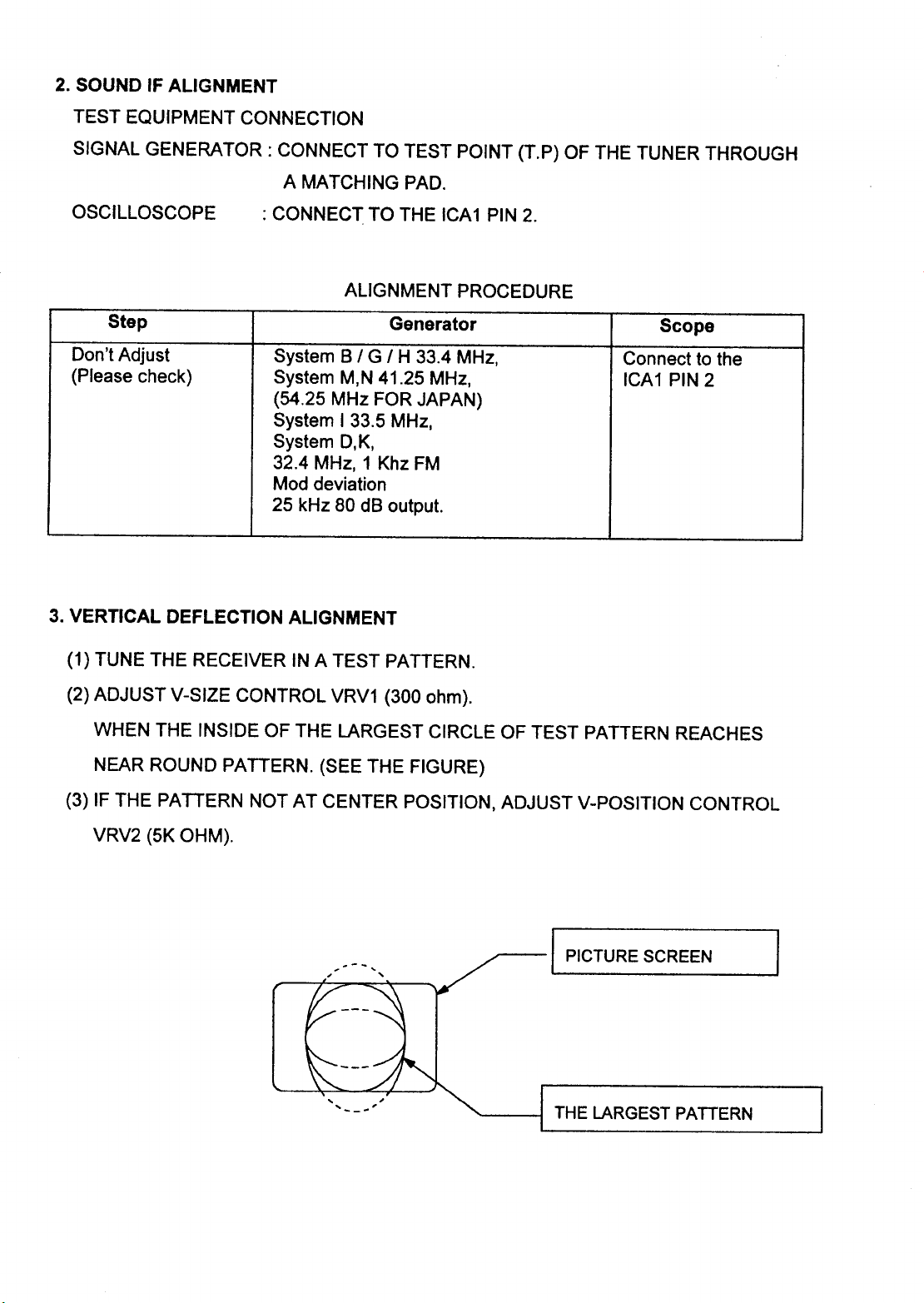

A MA TCHING PAD.

OSCILLOSCOPE : CONNECT TO THE ICA1 PIN 2.

ALlGNMENTPROCEDURE

Don't Adjust System BIG I H 33.4 MHz, Connect to the

(Please check) System M,N 41.25 MHz, ICA1 PIN 2

System I 33.5 MHz,

System D,K,

32.4 MHz, 1 Khz FM

Mod deviation

25 kHz 80 dB output.

3. VERTICAL DEFLECTION ALlGNMENT

(1) TUNE THE RECEIVER IN A TEST PATTERN.

WHEN THE INSIDE OF THE LARGEST CIRCLE OF TEST PATTERN REACHES

NEAR ROUND PATTERN. (SEE THE FIGURE)

(3) IF THE PATTERN NOT AT CENTER POSITION, ADJUST V-POSITION CONTROL

VRV2 (5K OHM).

IPICTURE SCREEN I

THE LARGEST PATTERN

Page 7

Page 8

Page 9

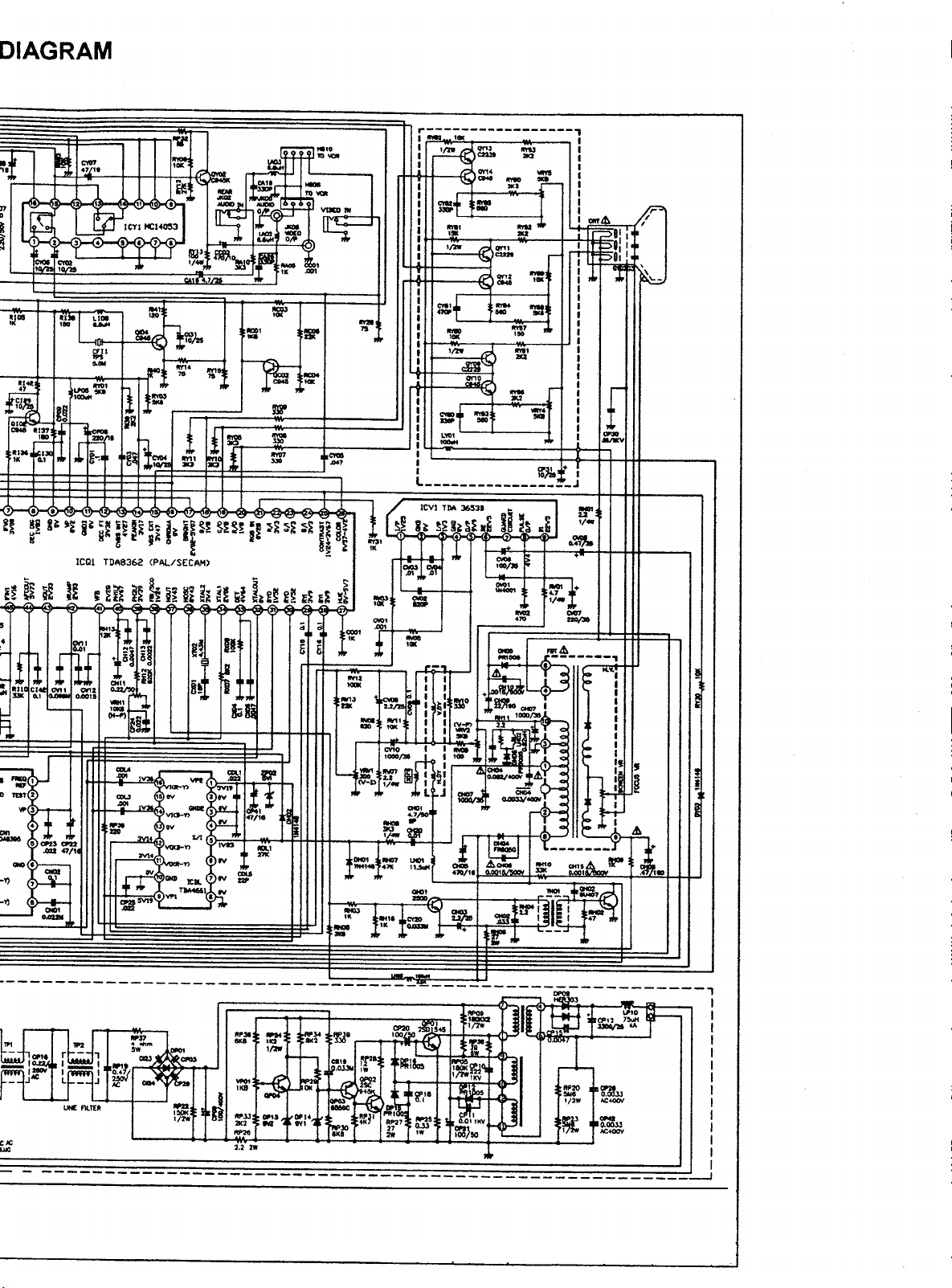

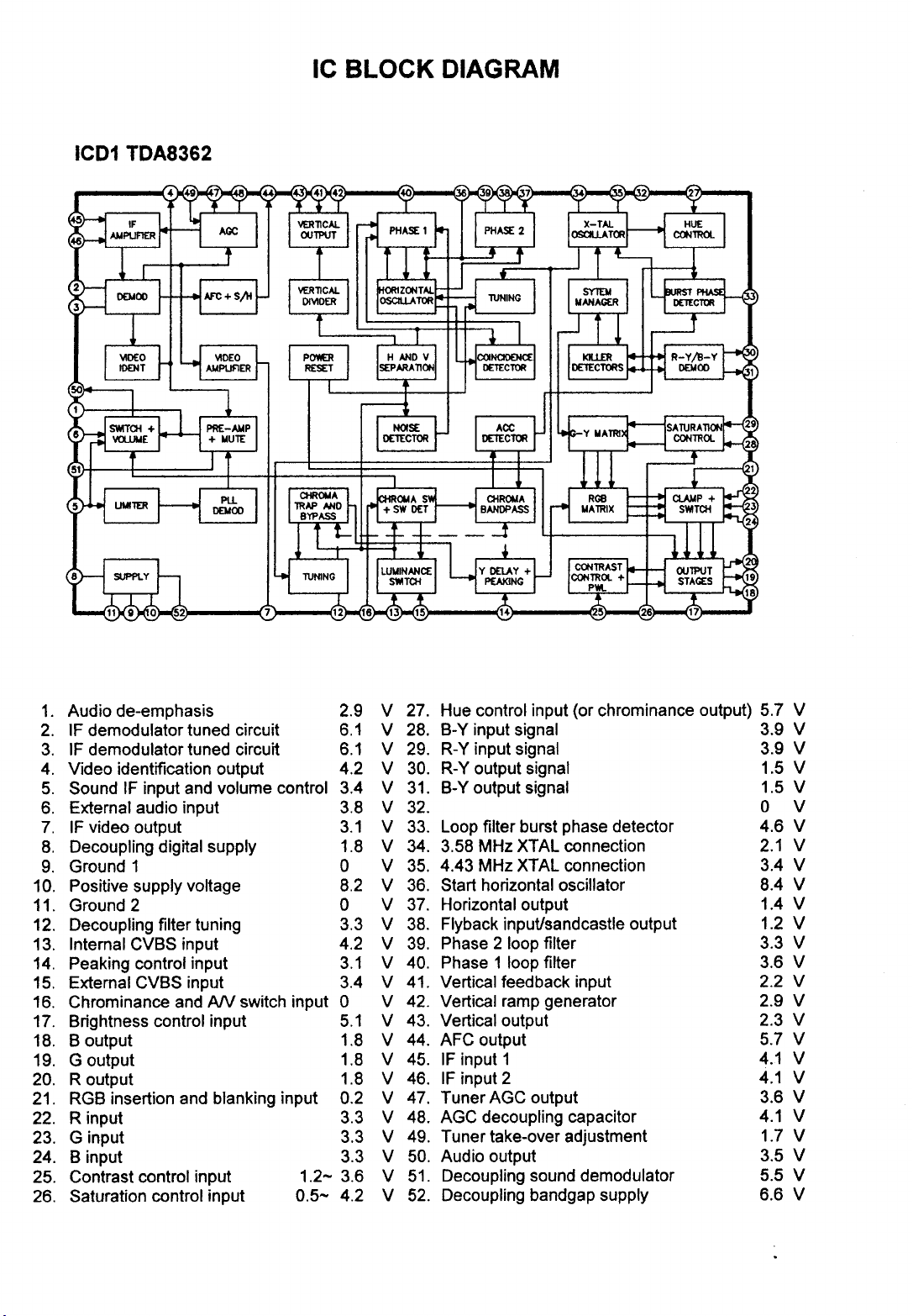

IC BLOCK DIAGRAM I

2. IF demodulator tuned circuit 6.1 V 28. B. Y input signal 3.9 V

3. IF demodulator tuned circuit 6.1 V 29. R-Y input signal 3.9 V

4. Video identification output 4.2 V 30. R- Y output signal 1.5 V

5. Sound IF input and volume contrai 3.4 V 31. B- Y output signal 1.5 V

6. External audio input 3.8 V 32. O V

7. IF video output 3.1 V 33. Loop filter burst phase detector 4.6 V

8. Decoupling digital supply 1.8 V 34. 3.58 MHz XTAL connection 2.1 V

9. Ground 1 O V 35. 4.43 MHz XTAL connection 3.4 V

10. Positive supply voltage 8.2 V 36. Start horizontal oscillator 8.4 V

11. Ground 2 O V 37. Horizontal output 1.4 V

12. Decoupling filter tuning 3.3 V 38. Flyback inputlsandcastle output 1.2 V

13. Internai CVBS input 4.2 V 39. Phase 2 loop filter 3.3 V

14. Peaking contrai input 3.1 V 40. Phase 1 loop filter 3.6 V

15. External CVBS input 3.4 V 41. Vertical feedback input 2.2 V

16. Chrominance and AN switch input O V 42. Vertical ramp generator 2.9 V

17. Brightness contrai input 5.1 V 43. Verticaloutput 2.3 V

18. B output 1.8 V 44. AFC output 5.7 V

19. G output 1.8 V 45. IF input 1 4.1 V

20. R output 1.8 V 46. IF input 2 4.1 V

21. RGB insertion and blanking input 0.2 V 47. TunerAGC output 3.6 V

22. R input 3.3 V 48. AGC decoupling capacitor 4.1 V

23. G input 3.3 V 49. Tuner take-over adjustment 1.7 V

24. B input 3.3 V 50. Audio output 3.5 V

25. Contrast contrai input 1.2- 3.6 V 51. Decoupling sound demodulator 5.5 V

26. Saturation contrai input 0.5- 4.2 V 52. Decoupling bandgap supply 6.6 V

Page 10

Page 11

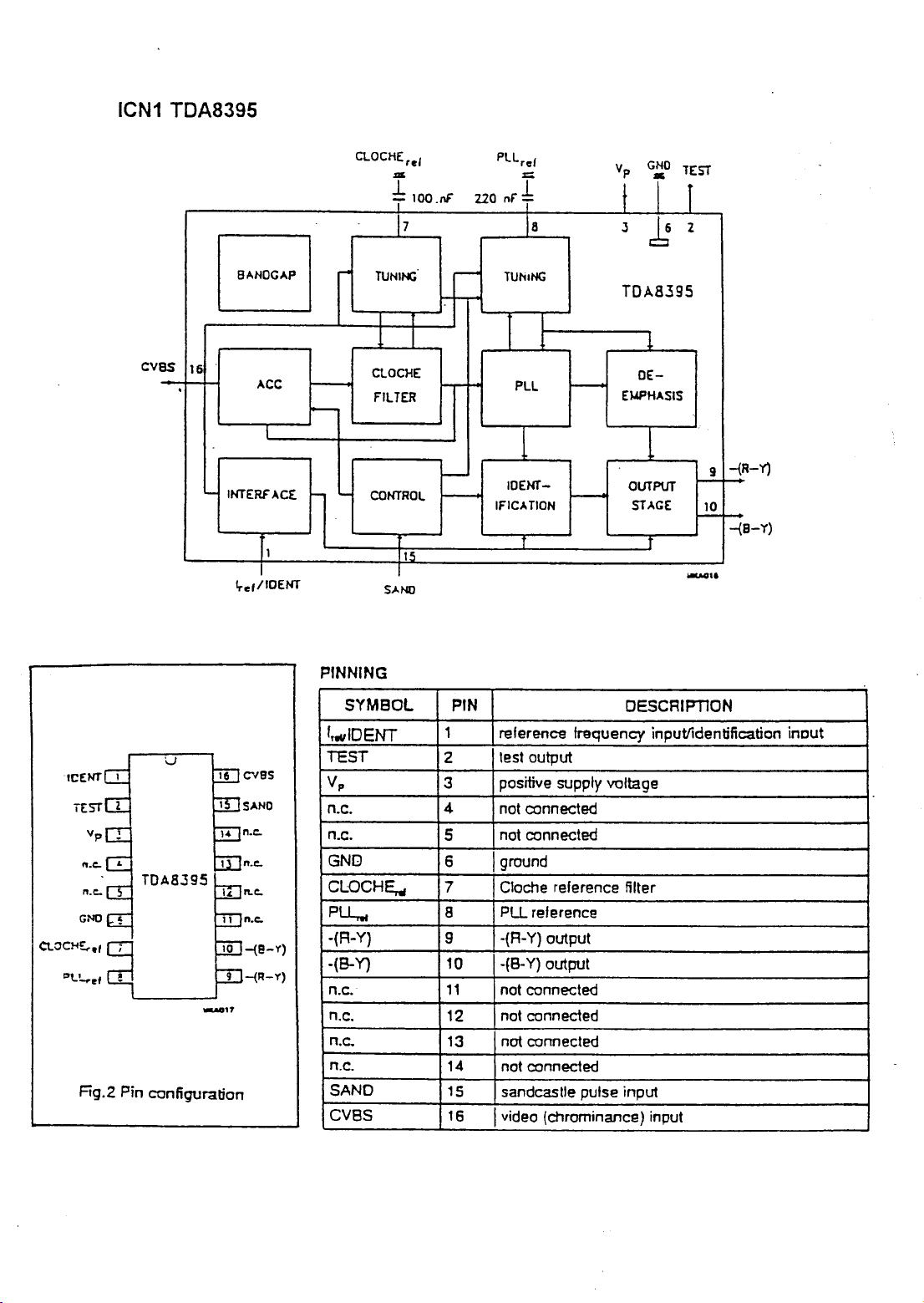

CLOCHE PlL

b 100.nF no nF:h

7 8 J 6 2

L~~=:J TOA8395

cves 16 OE-

FILTER EJAPH"SIS

EST..=. P-

INTE OUTPUT

IFICATION STAGE IO

1 1

lref/ICENT SANO

PINNING

f,.uIDENT 1 referencs trequency input/identification incut

TEST 2 lesI oUtput

ICEHT es V p 3 positive supply voltage

TEST ANO n.c. 4. not connected

vp .c- n.c. 5 not connected

".c- .c- GND 6 I ground

".~ ~ CLOCHE,., 7 C1oc!1e relerence lilter

GNO .c- PLL,., a PLL reference

,.. .,CHe" -(A-Y) 9 -(A-Y) output

...'-" -_I -{e-V')

~L'-..ef -{R-V')

_'7 n.c. 12 not connected

-(8- Y) 10 -(B- Y) output

n.c. 11 not connected

9 -{R-Y)

-{e-Y)

_'6

n.c. 13 not connected

n.c. 14 not connected

Fig.2 Pin conliguration SANO 15 sandcastle pulse input

CV8S 16 I video (c!1rominance) input

Page 12

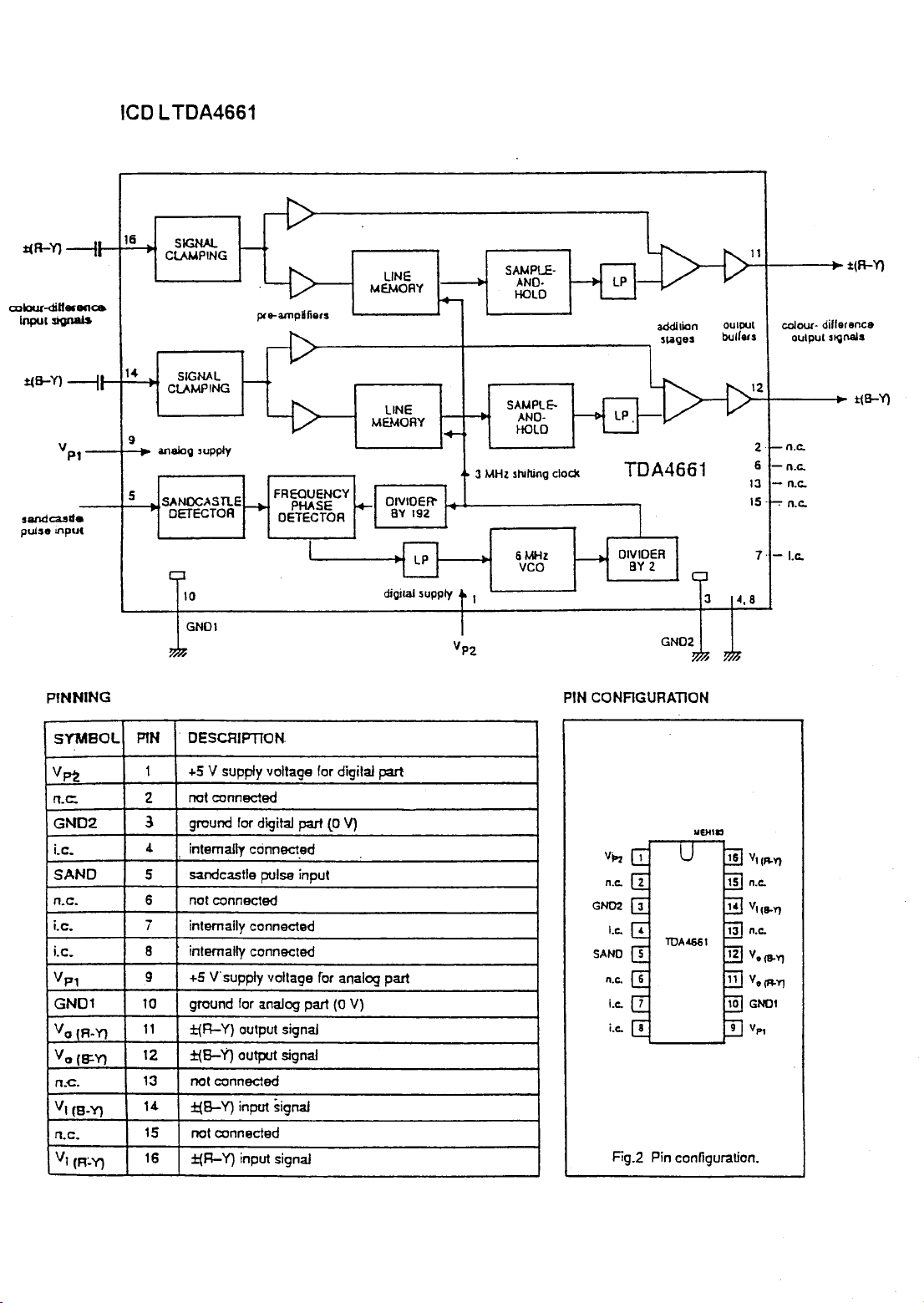

t(R-Y) -f C~G

~--[~~J---+G Il UNE SAMPLE- t(B-Y}

MEMOAY ~~D LP

cckxJC -{ijn -enca

Inpu .;...nal- pc&-amplliets

I --addIlion QUIPUt coIOUl- dilletenca

) 1 SIGNAL

ay

SAMPlE- t{B-Y}

ANO.

V P1 an&kJo supply Z n.c.

sandcasda OETECTOR

puise InpUt

9

5

SA NOCA STl 15 .n.c.

O diQilal suppiy I ~. 8

NOI

HOLO

3 MHz shihino clod< TDA4661 6 n.c.

6MHz 7 -I.c.

VCO

bul/8fs QutpUI Slçnals

13 n.c.

SYMBOL PTN CESCRIFnON.

V Pio 1 +5 V SUPp/y voltage for digilaJ part

n.c: 2 not connected

GNO2. 3 ground far digitaJ part lO V)

i.c. 4 intemaJly conn9cted v

SANO 5 sandcastle pulsa inpui

n.c. 6 noi conneded G

i.c. ì inlemally conneded I.c. n.c.

i.c. B inlemally connecled SANO v'(8-y)

V P1 9 +5 V' supply vollage for analog part n.c. V. (R-Y)

GNO1 10 ground for anaJog part (O V) i.c. GNO1

Va R.Y) 11 :f:(R-Y) OUlput signaJ i.c. vf'1

Va (e:;Y) 12 :f:(B-Y} OUtpJl signaJ

n.-c. 13 noI connected

VI (B-V) 14 :t(B-Y) inptrt signaJ

n.c. 15 noi connected

n.c. n.c.

N02 V

"EHla

V.~ 1(~Y)

1(8-Y)

VI (R:'V) 16 :t(R-Y) input signaJ Fig.2 Pin configuralion.

Page 13

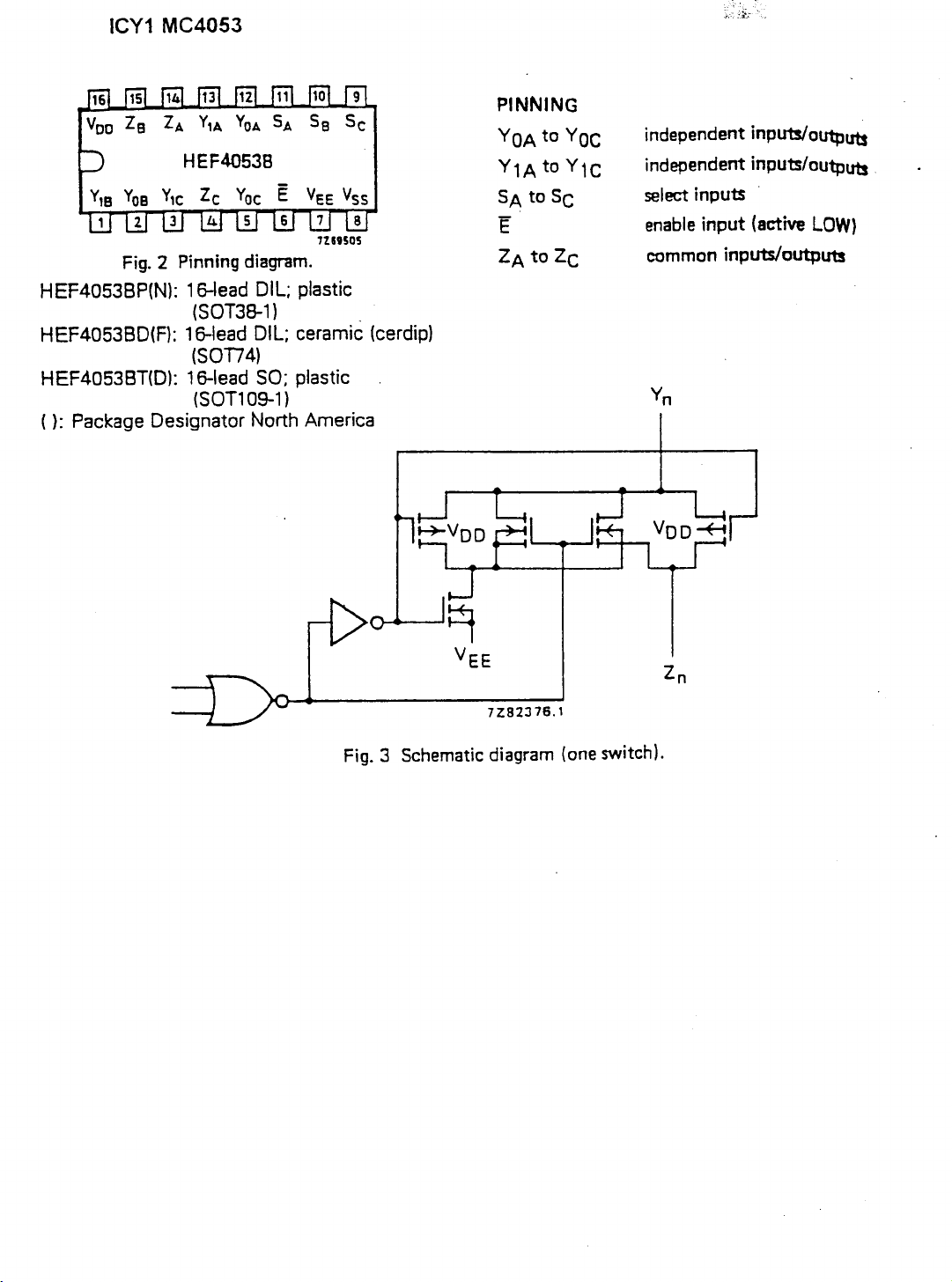

Vcc Ze ZA Y1A YOA SA Se Sc

HEF40538 Y1A to Y1C independent inputs/outputs

PINNING

Y OA to YOC independent inpu'tS/oUtputs

7U9S0S

HEF40538P{N): 16-lead DIL; plastic

(SOT38-1)

(SOn 4)

HEF40538T(D): 16-lead SO; plastic

(SOT109-1) Yn

( ): Package Designator North America

E enable input (active LOW)

n

7Z82376.1

Fig. 3 Schematic diagram (one switch).

Page 14

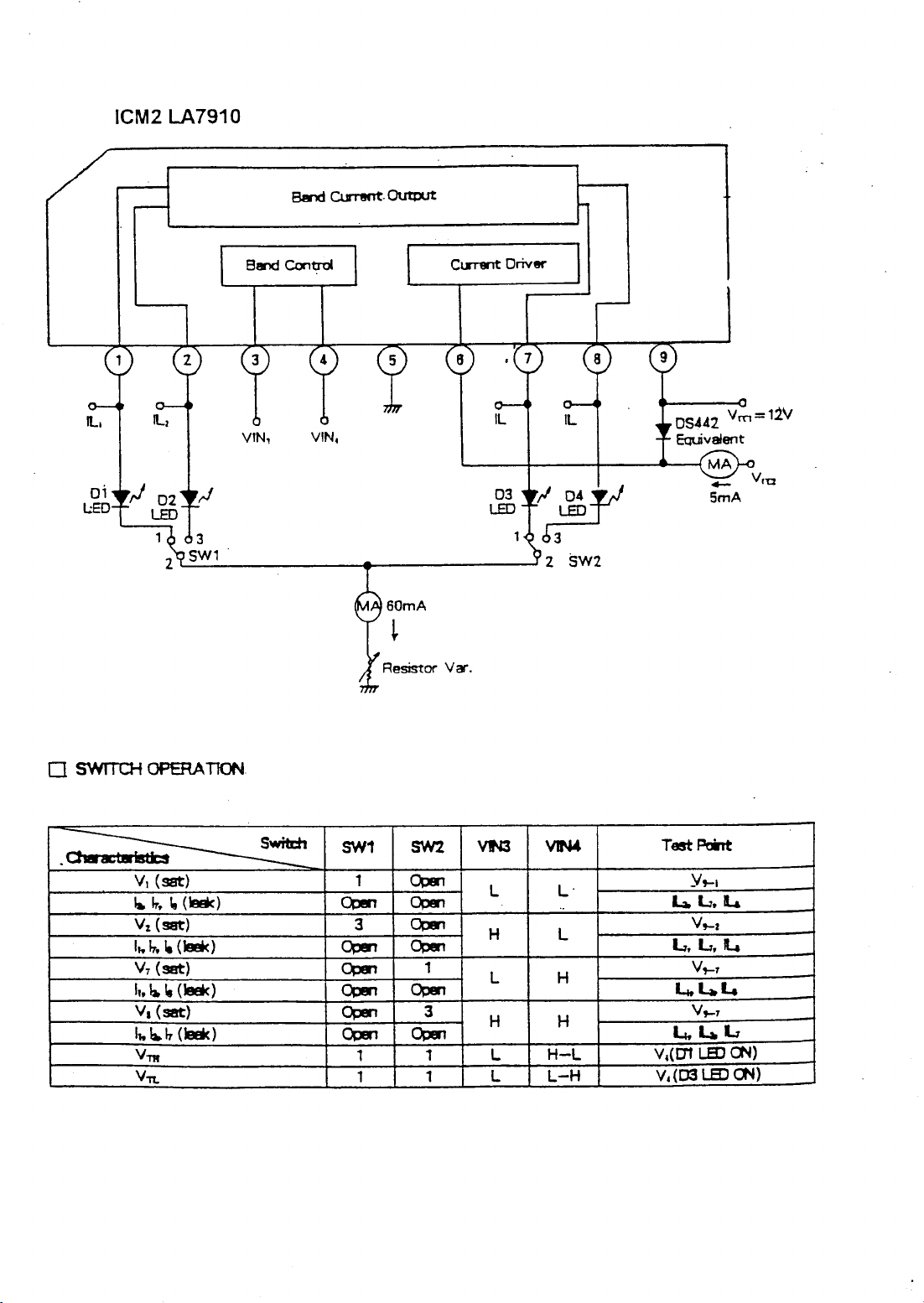

88"d~-~

8end CmtrQ C~ Driver

V1N, V!N,

11'1

11:2

'?

2 5W2

O 5Wrra-f OPERA ~

.O. s: t8 8tk:s ~

VI (-) 1 ~ L L- Y"-I

I. Ir. ~ (~) ~ ~ -La. L. V1(~) 3 ~ H L V,,-z

1..1r. -(&;c) ~ ~ ~. L. L.

V7 (-) ~ 1 L H V"-1

1,.1.1. (&;c) ~ ~ 44l-.

VI (~) ~ 3 H H V,.-1

119~1r (&;c) ~ ~ 4 ~ L

V-nf 1 1 L H-L V.(D'f L8J (114)

V1t. 1 1 L L-H V.(D3L8J(1I4)

5wita1 5W1 5W2. VM VD'U Tc ~

Page 15

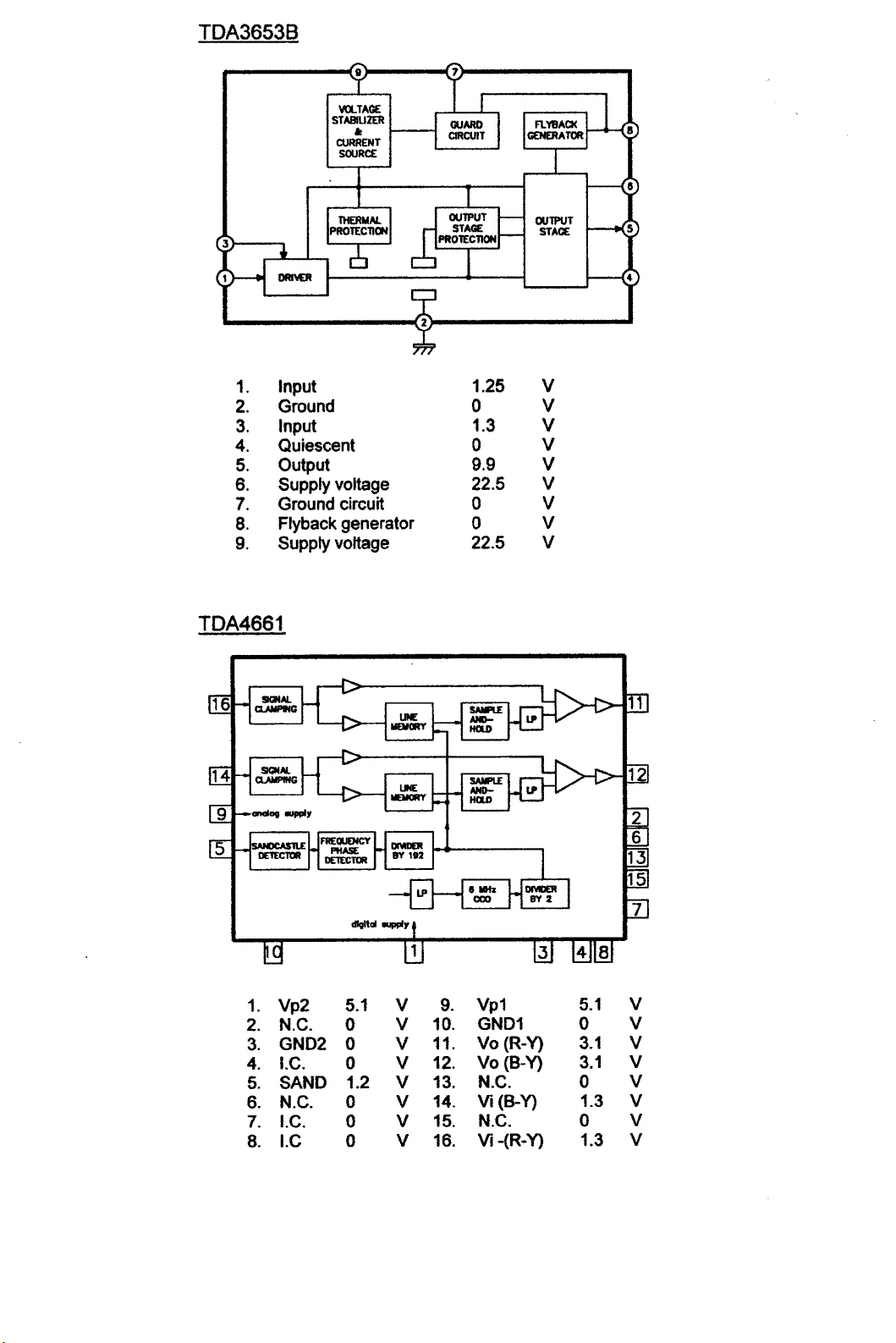

TOA36538 9 7 +

VOLTAGE FLY8ACK

STABllIZER GUARO GENERATOR 8

CURRENT

SOURCE

8

..Vp

.back

Inpui J TH OUTPUT 5

PRO STAGE

ORIVER 4

I 2 7Z,7647.1

2. ground O V

3. inpu t 1.3 V

4. quiescen t O V

5. output 9.9 V

6. supply voltage 22.5 V

7. guard circuit

8. flyback generator

9. supply valtage 22.5 V

IO

Page 16

,

I

,

I -

O~I

~-=I ...

> -,

o,

I

.D : c.

~...&'aG-

;."~u ;--=.

O~;"'" ...:=~o

~ O ~ : "'"

? lò.!E:-

I I c.. C-

L ~i~5.G -

...o

l}!!{ ,l: ~ :;~5 ~

-"">

~ t ~ ~

I

,. -, --."""

r ' ~=.

I~~~l~if~~~ -, J

: i , ~ ;-.

I ;: i. -16: 'r I

I fL-=~~=O!~: :'

I ~ 'f -

I ti --,;~-

I .

< -J ="'> - 1-oD ~ = ~ ~.,. - ]0 -

I ;~- I~:"I ~ =~x --

_::_- -~ ,- <~... -.., ~

I -T

~:D ~-~-:;~-~- ~ l

'" ",1 ;-'11S-

.~~ li~ ~: ~J .,...", .<-- "

~"'I ~ I .~

tO- ~ ---~

Il '... ~m' J cl ~

~ [l8 [ffi .o I~ ffi i

II : ~ i;:'i§] ~

I~-=

I '

..

X

~ ~

-a-

.!M"'-~ X

~ -cncncncn r..

~ G 1-

<t'; I~

tI:

<t

C

~ J~ = I~,

U"~

o -:1 G m! ~

-J G=iwr~

m ..Q.lcn '-' G Q .!.: IW

a.. = o

cn _I-

>< ';j~cn In -: ~

>< "":0-"" o. ~

I -.i --=

--.s-

~ ;5 ! ~ ~ x~ ~ l' c.. -_o;

O I -; ~ _.

O ~5'% .a ._00'

-:~ o

G='W w o

.w u' .' .

--.x D

"~o.:.~~ tC

..I -

lo! COi O o cn ~

1 -c..

H:!] I~ ~

I ~ .E z

~ c.. ~

I >-

...M

o -

~ O,.,. i~': ~... ,

l' g ~

lo. ~ }~ ~

J o

Page 17

~ ~

o IO I/) I/) ~~

~~~~~~. ~~~.,~c;c;

E-oalE-oE-oE-'~t' ~~E-'è/J~:li~

.,~~j~~<~~c;~"~b~a~

~U~~~~A

IUUUOO ..,UUU

~~f/)<UJ2~ ~~~UJQ~~~

O~IO",I/)O...I/)O~ I/)~I/)~~

...0~0~000"'001/)"'0"'00

",O.O~~~OOO~_~IOO"'O

I I I I I I I I I I I I I I I I I

~"""","""~~"'~N""""'_"'N

""""'NNNNOOI/)NN"""ON~

I I I I I I I I I I I I I I I I I

1O~1O~1O~"'IOI/)I/)IOIOIOOIOION

~~~O~NM.~~~~~O~NM

"""""""""~"'~"'~"""~~.~

~ ~ "'.,~ ~O ...~. O .~~ '" ~ ~ ~~oV""

~~~~~~~~E-o~

~

~

IO

~~

+ 10~

+ ~ lfij

al § IO... ~-+ ~

O ~ ,..-IO :I:

~ C; ."'~ §; O

~ ZS"'~~O., ~

3~~ ~~~~~~~~~~~~~

~ ~.~.~I .x~~~

~~~~~~~o~~~~~~E-oZ~

~ 8~~88~~f~~8~~~~~~

~ ",N_-001O~1O~~~1O-"'0- 0000-1O0000000001O~

~ OO~~"""~"'~-NO"""O-~

I IIIIIIIIIIIIIIIII

~ -"""""""'-N..."'NIO~N~"'.

1O~01/)0"'01/)0~~"'01O1O"'1/)

O""""'O""""'."'N~~N<N'"

I I I I I I I I I I I I I I I I I

1O1O1O1O1O"'~~~1O~~~~~"'~

G

~ ~-~~~~~"""NNN"""

~

f.-o::i ~

~ ~ ;

~ ~ ~~< ~

r_' O~ E-o~~~e:

~ ~~~~~O~~

~~~~~~

r!.~28~~ ~~ ~ g

OO~O~OO~~ ~~~~~

IO"'O~~N~_O U~ ~

O~~OO~-~~ -~

~II~I~~I~ ~r~~~ I~~~

"'~~"'~"'N~. ~~u~u~2~~

I I I I I I I I I ~~f/)...~~~ -

a)~~a)~~a)~~ -

a)1/)~~~~a)1/)1O ~IO~~~"'~~'"

...'" ~ ~ 10 ~~ ~~ O... N N'" 'J'~ '~'"

~ a~ ~ +

§t;~., UZZOUrz. ...;~

~ ~~:I: ~ S

~ E~ ;' ~ ~~Ut! ~M

:! ~UJ~U~. Zj~~.~C;~f/)~

01O00000~0

~01O1O~~~~~

I I I I r I I I I

~l'iJo~~~~~~

I I I I I I I I I

~~~~~~~"'~

~~1Oa)1O~~0~

O~N(,).IÒ~~~

~fl)ODfl)IOODIOfl)C)

+ f/) ~ ...

QA <

I/)~ -=

+ O -" ~~

~ OD'" .~O I/)

~~~~ ~~~ ;:)C;i:'C;~~

...~~0;1 .

~g~~g

I ~ UJ al

~-~~~~~~8~~5~~~~~t U:I:U~~~t~ou~~~~g~ <f/)f/)Qv'U<~f/)f/)~~~QAf/) ~~O fl)",~..."'0'" ~"'...'"

~. -"'~~~

V "'0000 NI/) 8 1O~000.1/)

O ~I/)"'~~~O~ "'000~-'"

I I I I I I I I I I I I I I I I

~",~N"'~ONfl)"""OO"'~O

OO"""~~~NOON~"'O~~

",~~",~~~...~~0~0~a)~

N"'fl)Ofl)~N~I/)OD~~"'~IOfl)

.IÒ~~~~O~N(,).IÒ~~~~

8"'0~~0~000~

Page 18

~§

>

I~

> 2~

o

~~

5=

1I-'i ~ Q§

-§~~ r I ~~ ~

~~~ I

I a Q;: I ~O~

~o~ -~

QF:2

I I ~ ~

I I

a o.. I (.)~ L -

0..1 o..

~ o.. I! ~ ~ i~! I

~~~ I -~~ 0::0

I>- (.)

I -I

I 9 x oe

~ x Q LL~ I

I ~~ ,- ~

o 0..0

~~ I ~~ ~~ I ~~

I ~~ I

L ~

ImliJ m~ ~:2

I

I-~

Page 19

1. VIDEO HEAD SWITCHING POSITION

.Connection Method

R307

PTO1 PIN3

PLAY

D

R592

1) Play back the test tape. (Color Bar DP-2)

2) Set the Oscilloscope in the chop mode connect the CH1 to SW pulse (PTO1 PIN), the CH2 to VIDEO

with CH1 triggering.

3) Adjust R592 far the positive tigger unitill 6.5:!O.5 H cycles before the vertical SYNC pulse.

CH1 (FTO1 <D PINI

VERTICALSYNC

CH2 ~ ~IGGER

sw 30Hz

Page 20

1. VIDEO HEAD SWITCHING POSITION

R292 Rec

R01

.Connection Method

R292

D

.Adjustment Procedure

1) Set the power on mode.

2) Set the input to open mode.

3) Connect the Audio leve! meter to both R01.

4) After inserting a blank tape, record in SP mode.

5) Adjust R292 to obtain 3.0 mVrms.

Page 21

3-1 POWER CIRCUIT

A. CHECKING THE POWER CI~CUIT

o VES

o VES

Check converter power PCB NO I Check converter ~I"'D I

O VES

I Check FOO1 FUSE. I

O YES

Is voltage applied to the collect of 0002 NO

R010, R016, R018. ~

O VES

I Check power circuito I

p ower PCBOUTPUT is DC 12V? ~ I \.IIICI,.'I\ \.iUIIVCILCI tJUVVCI r\.lc. I

[ ~~::~~J 0004, QO09 and RO01, RO03, RO09, Check CO06.

Page 22

Page 23

~'l!E!3~

~~

Noise appears NO

[~~~~~J .on the screen Check flow A

on Ihe whole.

NO Is SW pulse supplied NO Check D.PG inpul

tram pin@ot IC601? and connector.

Is Enve.wavetrom

[~:~~~:J supplied lo al pin@ot Check pattem

PTO1

VES

I """'v" ,'u"u v" vUOI. I Amp and Head dusl. I ~v "V_~ I

C..

Auto stop during

playback

VES

Is Reel pulse NO Check reel sensor.

applied lo pin (Z)and S603 S604

@ot IC601? '

VES

Is D.FG applied lo Check connector

pin@ot IC601 D.FG circuits.

VES

I Check IC601 I

Page 24

D.

III~II.

NO I rhor-1t nnwçor ~ir~llit I

t.Is Motor 12V supplied? I Check power ClrCUI.. I

'~'r1~'

E.

NO I r-"~~I, r-~no [:I~..n I

NO I ChecklC601 I

Check connector

and Motor.

Is Motor 12V supplied? Check power circuito

NO

I Check C508, R510 I

NO Check circuit 01 R604,

R605, R606.

NO

Check R655, R656

ChecklC601

Page 25

F.

le~_tit!MII!~R

pin@of IC601? VIDEO IC and Pattem

I Check Motor.!

G.

li__~_~_ì-

Doe5 X601 cry5tal 05ciliate? NO I Check IC601 and X601. I

15 CAM SW DATA Correct. and CAM SW contact.

I Check IC602. I

..YES'

I Check IC 601. I

'. t ..

ES

? NO Recheck connector

Page 26

H.

VES

CAM DATA i5 changed I Check connector.L ~I Check DECK parto I

when CST IN? I ~"vv" vv""vv,v"i I ~"vv" ~-~" t'~". I

VES

I Chek IC602 I I Check IC601 I

Page 27

I.

When mains is

pin@and@of IC601?

VES

IsfUùsignal applied to NO I ,.,..~~" ~C"i I

pin@and@of IC601? I Check X601j

VES

[~::~~~:~~~~~::::::J unplugged is 3.6V at NO Check C602

[~:~=J

Page 28

15 the output at pin@NOl59Vappliedtopin0NO I Check ""..'~r ~;~. ,;. l

of IC201? ~ of IC201? I ~..""'" f'VW~1 C"..UI.. I

p o er irc 't

VES

15 5V applied to NO

@ of IC201?

VES I Choc' SYSCON I

VES

15 there Audio output NO Check circuit adjacent

at pin @ of IC201? to R211, R212

VES

15 pin @ of IC201 NO I Check IC2011

GND? I ""I~"I\ ""~V I I

VES

I CheckPJ201 I

L. and HEAD. I

Page 29

B. Troubleshooting of REC mode

pin ~ of IC201? R209, R210, C207

I~ 5V applied to NO I Check SVSCON. I

pln@ of1C201? I v,'c""...,...vv". I

ES

Is there output at pin @ NO I Check IC201. I

of IC201? I -, ,-_., ,--- ,. I

VES

Does T201 oscillate? NO Is the v.ol~e above 10V NO I Check IC201. I

Base: OV

I Check T201 I

Is record current NO I Asjust Record currenl I

normal? I '.-J--"'---'~--"-"~ I

VES

Is pin G) of IC201 OV? NO I Check IC201. I

VES

" Clean HEAD. ~

[~~:~~::~..~~~~~~~:~] .collector:above 10V Check IC201.

Page 30

A.EE MODE Picture N.G

~ NO ~. .'. .NO I Check S~rt jack I

15 5ignal output from NO 15 5V supplied lo pin@ NO Check

I I or.ANjack. I

VES

VES

Is Seria! clock and data NO Check

5ignal inpui inlo IC601<D.CDpin

pin@.@of IC301?

15 QV SYNC(H) 5upplied lo

anode of 0301 at 5 vo115?

VES

VES

VES

[:~:::~:~::::~~~]

Page 31

NO I ~L~~.,, a."'_:_..:6 I

1- Check HEADAMP circuitj

Is ON/OFF 5V supplied to pin@and NO I ~L~_'. ,...a", '- ~\I I

Is EE(L) supplied to anode ot No.1 ~L__'. --""l \ I

DAO1 at 5volt? 1- Check EE(L) I

NO I ~L__'- roro", "'_6- 1

-.I~ Check SSB Dataj

Is the luminance signal tram pin@oflC301 NO .r "'L__'. " , I

Is the luminance signal trom@ot IC301 --No.1 ~L " , l

fed to pin @ot IC301 1- Check IC302 I

VES

fed lo pin@ot IC301? I Change IC301j

I Check Une out ~

Page 32

NO I ,", O.OI.-A..,A..n_: :' I

IsON/OFF5Vsuppliedtopin@and No.1 '""'__O_""L"""""""~\I I

VES

Is QV SYNC supplied to anode of No.1 '"' ,. """ ""LO,", I

0301 at O volts? I Check QV SYNC I

VES

Is the PAL colour signal tram pin@ NO ~ Check IC301 pin@,@serial

of IC301 fed to pin @ of IC302? clock and data input

I Choc" 10302 I '. of IC301 fed to pin@ -~ Check IC302

VES

Is the signal tram pin@of NO ~ I Ch~~k C317 I

IC301 fedtopin@oflC301 I vlleC"V"11 I

NO I '"' o'"'"".. I

..-~ I Change IC301 I

, I Check Une out .I

Page 33

No Port I/O Port Name Port Function Initlal

1 P40 O V. ClK VIDEO SERIAl ClOCK

2 P41 O V. DATA VIDEO SERIAl DATA

4 P43 O Amute_H AUDIO MUTE OUTPUT

5 P44 O PWR ON (l) POWER ON (l) OUTPUT

6 P45 I OPTION PORT AUTO REPEAT (l)/NO AUTO REPEAT (H)

8 P47 I C.SYNC COMPOSITE SYNC INPUT FOR SYNC DETECT

9 P30 O SlOW STEP SlOW STEP OUTPUT

10 P31 O CAP I CTl(l) CAPSTAN CURRENT LlMIT CONTROl OUTPUT

11 P32 O CAP REV (H) CAPSTAN ROTATE DIRECTION OUTPUT

12 P33 I C.SYNC COMPOSITE SYNC INPUT (REC-REFERENCE)

13 P34 I REMOTE REMOCON SIGNAl INPUT

14 P35 I T_REEl.P TAKE-UP REEl PUlSE INPUT

15 P36 I V.SYNC VERTICAl SYNC INPUT FOR NTSC/PAl SEl.

18 P65 I C.PG CAPSTAN FG INPUT

19 P66 1 C.FG CAPSTAN FG INPUT

20 P67 1 PB.CTl PLAY BACK CONTROl SIGNAl INPUT

21 TEST I Vcc(+5V)

22 POO O QV.SYNC QUASI V.SYNC OUTPUT IN SPECIAl PB MODE

23 P01 O V.SWP VIDEO HEAD SWITCHING PUlSE OUTPUT

24 P02 O A.SWP AUDIO HEAD SWITCHING PUlSE OUTPUT

25 P03 O PWR/STB lED POWER/STAND-BY lED OUTPUT

26 P04 O Rewind (l) lED REWIND lED OUTPUT

27 P05 O Play lED PLAY LED OUTPUT

28 P06 O FF (R) lED FAST FORWARD lED OUTPUT

29 P07 O Cassette-in lED Cassette-in lED OUTPUT

30 PWMO O D.PWM DRUM PWM OUTPUT

31 PWM1 O C.PWM CAPSTAN PWM OUTPUT

32 VSS I GND GND

Page 34

No Port I/O Port Name Port Function Initlal

34 P26 O Record LED Record LED OUTPUT

35 P25 O No-col-kill(H) TVNCR LED OUTPUT

37 P23 O NOT USED

38 P22 O HIFI_CLK HIFIIC CONTROL I C BUS CLOCK

39 P21 O TV (H)NCR(L) INPUT SELECTION OUTPUT

40 P20 O REC CTL RECORD CONTROL SIGNAL OUTPUT

41 P10 O LM ON(H) LOADING MOTOR DRIVE LOGIC

42 P11 O LM+/- LOADING MOTOR DRIVE LOGIC

43 P12 O 60Hz/50Hz NTSC OR PAL DETECT OUTPUT

44 P13 O REC (H) REC MODE OUTPUT

45 CLK NOT USED

46 RESET I RESET RESETINPUT

50 P63 I Mesecam(H) Mesecam(H) input ports

51 P62 I KEY 3 Forwired remocon (STOP,PLAY,FF,REW)

52 P61 I T.END(L) END SENSOR INPUT

53 P60 I T.END(L) END SENSOR INPUT

54 P57 I KEY2 KEY Input 2 (REC,REW,FF,PAS/STL)

55 P56 I CAM 2 CAM Input 2 (CAM C,REC SATETY)

56 P55 I KEY 1 KEY Input 1 (pwr,sUej,a/r,ply)

57 P54 I PG DELAY ADJUST INPUT

58 P53 I TRK DL Y PATH ADJUST INPUT

59 P52 I PG DL Y PG DELAY ADJUST INPUT

P51 I ENVE. DET DC ENVE. INPUT FOR AUTO TRACKING

61 P50 I OPTION 1 DRUM & NTSC/PAUAUTO SELECTION INPUT

62 Vref I Avcc NO CONVERTER REFERENCE VOL T AGE

63 A.GND I GND NO CONVERTER GND

64 Vcc I Vcc Vcc( +5V)

Page 35

Page 36

Page 37

A 8 C D E

.

r~11111111 ,

L307 -l

R3OI

I~

I~

CAI4 ~A17

~ eI<2

LAO4 CAI~

Z7~ 3»-

~

~-

2K2

!I

RAO7

2K2

_4

~

l'''

~

!

RAO6

1)( L-

i ::

~ 0.1

CA1~ LAC8

om I~

RAOZ

1- CADS

RAO3 + CA22

la U~

.I~

~I

R323

7

A B C DL

Page 38

Page 39

A B C

-

1

TD DECK

PJ201

1 CTL (+)

2 CTL (-)

4

5 GND

6Il

2i

3

4

5

A B C

Page 40

Page 41

RUJl

lOK

1

~

3

ICOI

BA7107

~

812

UD1 PB-<: ~

Page 42

Page 43

> >

C\!>\()

C)!: C)!: D W

w »ZOZ

WW,~~ I

WW°Q.~

°

\Dl..-

l..-

~ 00 D r-u;::: ~ ci

D I- +

l-

+ ~~ /\o.ç/nt

a \DO \() !ooS :

000 \D C\! ,Oc)!: I

c)!: \D , ,Oc,.., I U'~

:J q

uci .-.oc,..,

\() ~ t'o 20dJ

U .q- .çJOJ I.q-,

> I o I

O:J ,C~ J 101;:8

Ur I I Ik: ~

.q- L -_J 8 I 2

C\!

0 \D ~O"'~C').

> I.. .-1\.0 ~In ~~~=~=

00

U Q) r --.,

I-ir' ,.q- I

'o I

'° 1

1 Oc,.., I

L J

o

C) \()

°> C\! o~

C\! M

N o

C\Jo

oM

\() oC\J

u ~OO 0'-'

CC\!

~...~

.°

oC >

> .

In

00'

~ °3

o U .-.

> +

C)

.-.IJ)

° C\!

°

l..-~

C\!

>

v

.-.

~ -c

C\!

U

~

'-'l..-

~ .

Page 44

ROADSTAR MANAGEMENT SA.

(INTERNATIONAL SERVICE DIVISION)

Via Passeggiata, 1 - BALERNA - SWITZERLAND

Tel. +4191-6975155 - Fax. +4191-6975151

e-mail: aftersal@roadstar.com

ROADSTAR ITALIA S.P.A.

SERVICE DIVISION (DOMESTIC ITALY)

Viale Matteotti, 22 - CERNOBBIO (CO) -ITALY

Tel. +39031-342340 - Fax. +39031-3346291

Loading...

Loading...