RICOH RF5C62, RP5C62, RS5C62 Datasheet

REAL-TIME CLOCK

RP/RF/RS5C62

ELECTRONIC DEVICES DIVISION

NO.EA-012-9803

APPLICATION MANUAL

NOTICE

1. The products and the product specifications described in this application manual are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use

the products, please refer to Ricoh sales representatives for the latest information thereon.

2. This application manual may not be copied or otherwise reproduced in whole or in part without prior written consent of Ricoh.

3. Please be sure to take any necessary formalities under relevant laws or regulations before exporting or otherwise taking out of your country the products or the technical information described herein.

4. The technical information described in this application manual shows typical characteristics of and example

application circuits for the products. The release of such information is not to be construed as a warranty of or a

grant of license under Ricoh's or any third party's intellectual property rights or any other rights.

5. The products listed in this document are intended and designed for use as general electronic components in

standard applications (office equipment, computer equipment, measuring instruments, consumer electronic

products, amusement equipment etc.). Those customers intending to use a product in an application requiring

extreme quality and reliability, for example, in a highly specific application where the failure or misoperation of

the product could result in human injury or death (aircraft, spacevehicle, nuclear reactor control system, traffic

control system, automotive and transportation equipment, combustion equipment, safety devices, life support

system etc.) should first contact us.

6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor

products are likely to fail with certain probability. In order prevent any injury to persons or damages to property

resulting from such failure, customers should be careful enough to incorporate safety measures in their design,

such as redundancy feature, fire-containment feature and fail-safe feature. We do not assume any liability or

responsibility for any loss or damage arising from misuse or inappropriate use of the products.

7. Anti-radiation design is not implemented in the products described in this application manual.

8. Please contact Ricoh sales representatives should you have any questions or comments concerning the products or the technical information.

June 1995

OUTLINE

......................................................................................................

1

FEATURES

....................................................................................................

1

BLOCK DIAGRAM

.........................................................................................

1

PIN CONFIGURATION

...................................................................................

2

PIN DESCRIPTION

........................................................................................

2

ABSOLUTE MAXIMUM RATINGS

...................................................................

3

RECOMMENDED OPERATING CONDITION

....................................................

3

DC ELECTRICAL CHARACTERISTICS

...........................................................

4

AC ELECTRICAL CHARACTERISTICS

...........................................................

5

TIMING CHART

.............................................................................................

5

FUNCTIONAL DESCRIPTION

.........................................................................

6

1. Addressing

.................................................................................................

6

2. Functions of Registers

...................................................................................

7

3. Functions of Counters

..................................................................................

15

USAGE

........................................................................................................

17

1. Reading and Writing Operations

......................................................................

17

2. Handling of CE Pin

......................................................................................

18

3. Configuration of Oscillatory Circuit

....................................................................

19

4. Adjustment of Oscillation Frequencies

...............................................................

20

5. Interrupts

.................................................................................................

22

6. Timer

......................................................................................................

23

7. Detection of Stop of Oscillation

........................................................................

24

8. Typical Power Supply Circuit

...........................................................................

25

9. Typical Connection between RP/RF/RS5C62 and CPU

...........................................

26

10. Typical Characteristics

..................................................................................

27

11. Typical Software-controlled Processes

...............................................................

29

RP/RF/RS5C62

APPLICATION MANUAL

CONTENTS

QUESTIONS AND ANSWERS ON USE

.........................................................

34

PACKAGE DIMENSIONS

..............................................................................

42

TAPING SPECIFICATIONS

...........................................................................

43

REAL-TIME CLOCK

1

RP/RF/RS5C62

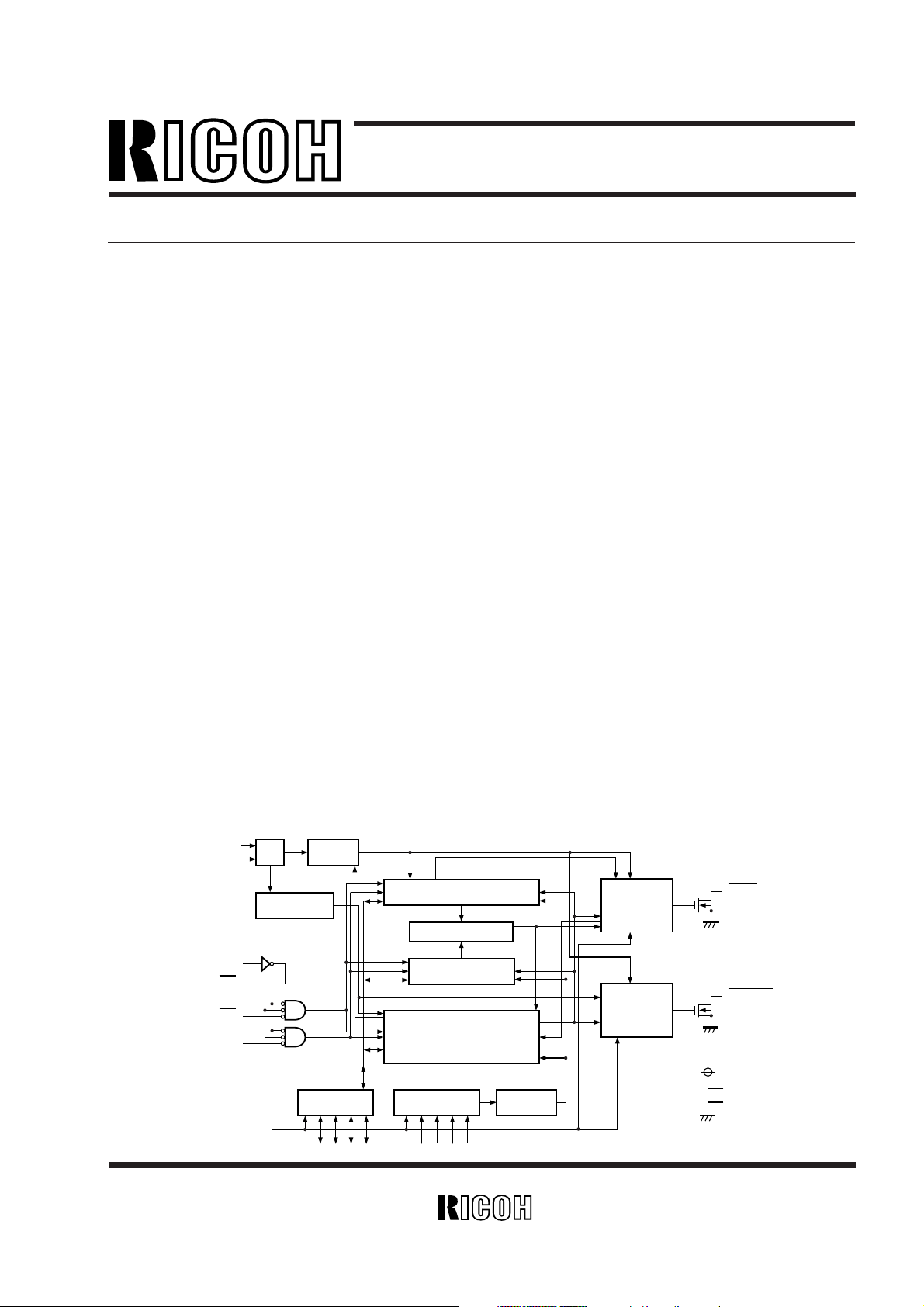

OUTLINE

The RP/RF/RS5C62 are CMOS LSIs which serve microcomputers as real-time clocks providing time, calendar,

and alarm functions in direct coupling with the data buses of CPUs such as 8086 and 68000. A built-in timer counter

acts as a watchdog timer or interrupt timer. They are available in three different types of packages: the DIP type,

the SOP type, and the SSOP type.

• Directly connected to CPU, enabling fast access.

• 4bit bidirectional data bus, and 4bit address bus.

• The oscillator is driven by a constant voltage, so the oscillation frequency is stable even when the power supply

voltage fluctuates.

• Built-in timer counter using internal clock.

• Generates cyclic CPU interrupts, and generates alarm-match interrupts.

• Interrupt flag and interrupt inhibit.

• Clock (hour, minute, second), calendar (leap year, year, month, day, day-of-the-week), alarm (hour, minute).

• 12-or 24-hour mode is selectable.

• Recognizes leap years automatically.

• All clock and alarm data expressed in BCD codes.

• ±30 seconds adjustment function.

• Determines whether clock data is valid or invalid.

• Consumes very low power due to CMOS technology, so it can be backed up by batteries.

• Power supply voltage between 3.0 to 5.0V.

• Time keeping supply voltage between 2.0 to 6.0V.

• Package : 18pin DIP for RP5C62, 18pin SOP for RF5C62, 20pin SSOP for RS5C62.

FEATURES

BLOCK DIAGRAM

INTERRURT

CONTROL

TIMER

CONTROL REGISTER

ADDRESS BUS

CONTROL

DATA BUS

CONTROL

D0D1D2

DIV

OSC DETECT

OSC

OSCIN

OSCOUT

CE

D3 A0A1A2A3

ADDRESS

DECODER

ALARM REGISTER

COMPARATOR

WATCH & CALENDAR

VDD

VSS

TMOUT

CS

RD

WR

INTR

Function

CS and CE are used when interfacing external devices. They may be accessed

when CS is low and CE is high. CE is connected to an output of power down

detector on the system power supply side, and CS is connected to the microcomputer address bus.

Timer output may be used as an interrupt free-run timer or watchdog timer.

When CE is low (running on battery backup), operation stops (there is no output).

It is N-ch open drain output.

Address input is connected to the CPU address bus. It is gated internally with CE.

When RD falls from high to low, the contents of the counters or registers specified

by A0 to A3 are output to D0 to D3. It is valid when CS is low and CE is high. It is

CMOS input.

When WR falls from high to low or rises from low to high, the contents of D0 to

D3 are written to registers or counters specified by A0 to A3. WR is valid when CS

is low and CE is high. It is CMOS input.

D0 to D3 are connected to the CPU data bus. The input section is gated internally

with CE. It is CMOS input/output.

INTR outputs cyclic interrupts or alarm interrupts to CPU. It also operates when

CE is low (at battery backup). It is N-ch open drain output.

Crystal oscillator of 32.768kHz must be connected between OSCIN and OSCOUT.

Capacitance is connected externally between V

DD and OSCIN and VDD and

OSCOUT, forming the oscillator circuit.

V

DD connects to +5V or +3V and VSS to ground.

2

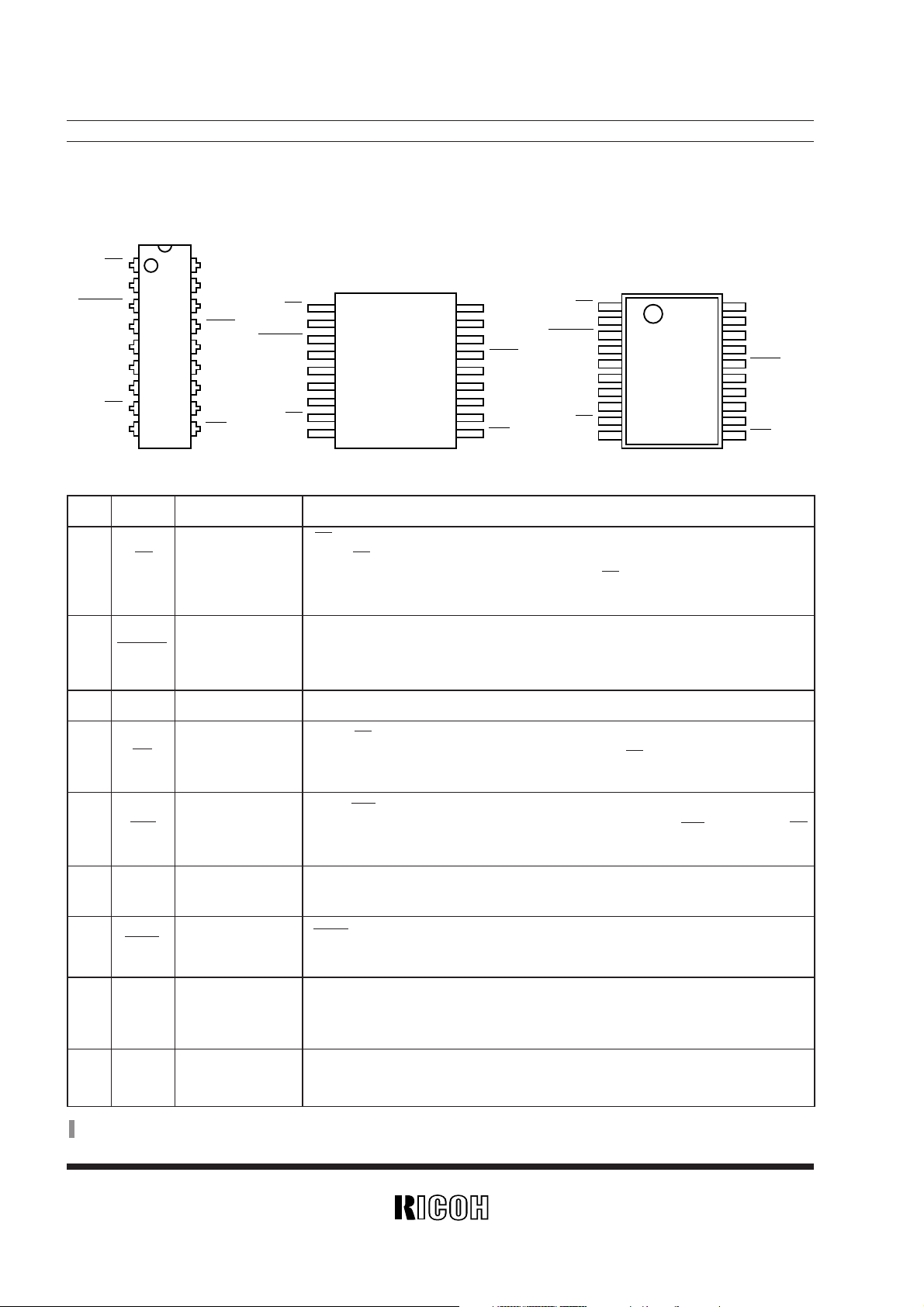

PIN CONFIGURATION

RP/RF/RS5C62

VDD

VDD

OSCOUT

OSCOUT

OSCIN

OSCIN

D3

D2

D1

D0

INTR

WR

CS

CE

TMOUT

A1

A2

A3

RD

A0

VSS

1

2

3

5

6

7

8

4

9

18

17

16

14

13

12

11

15

10

INTR

D3

D2

D1

D0

WR

CE

A0

A1

A2

A3

VSS

18

17

16

15

14

13

12

11

10

1

2

3

4

5

6

7

8

9

CS

TMOUT

RD

VDD

OSCOUT

OSCIN

NC

INTR

D3

D2

D1

D0

WR

CS

CE

TMOUT

NC

A0

A1

A2

A3

RD

VSS

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

PIN DESCRIPTION

Pin No.

Symbol Name

1 CS Chip select input

2 CE Chip enable input

3

TMOUT

Timer output

4–7 A0–A3 Address input

8 RD

Read control input

10 WR

Write control input

11–14

D0–D3

Bi-directional data

bus

15 INTR Interrupt output

16 OSCIN Oscillator circuit

17

OSCOUT

input/output

18 V

DD

9 VSS

Power supply

*

) The pin numbers marked in the above table indicate the pins on the 18pin packages.

• RP5C62 (18pin DIP) • RF5C62 (18pin SOP) • RS5C62 (20pin SSOP)

3

RP/RF/RS5C62

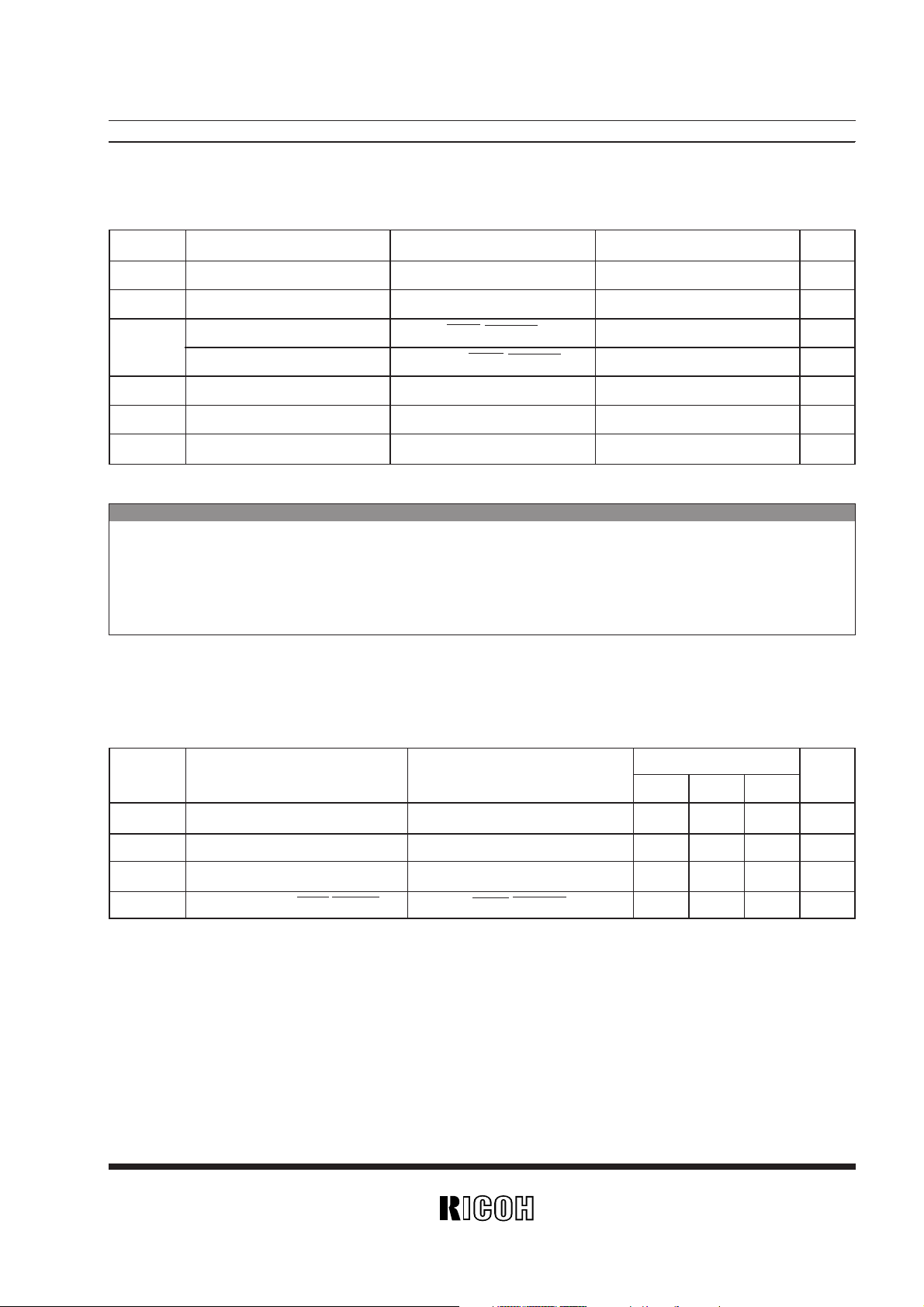

ABSOLUTE MAXIMUM RATINGS

RECOMMENDED OPERATING CONDITION

ABSOLUTE MAXIMUM RATINGS

VSS=0V

Symbol Item Conditions Ratings Unit

VDD Supply Voltage –0.3 to +7.0 V

VI Input Voltage –0.3 to +VDD+0.3 V

VO

Output Voltage 1 INTR, TMOUT –0.3 to +12.0 V

Output Voltage 2 Except INTR, TMOUT –0.3 to +VDD+0.3 V

PD Maximum Power Dissipation TA=25˚C 300 mW

Topt Operating Temperature –20 to +70 ˚C

Tstg Storage Temperature –40 to +125 ˚C

V

SS=0V, Topt=–20 to +70˚C

Symbol Item Conditions

Limits

Unit

MIN. TYP. MAX.

VDD Supply Voltage 2.7 5.0 6.0 V

VCLK Time Keeping Supply voltage 2.0 6.0 V

fXT Crystal Oscillation Frequency 32.768 kHz

V

PUP

Pull-up Voltage for INTR, TMOUT pin

INTR, TMOUT 10 V

Absolute Maximum ratings are threshold limit values that must not be exceeded even for an instant under

any conditions. Moreover, such values for any two items must not be reached simultaneously. Operation

above these absolute maximum ratings may cause degradation or permanent damage to the device. These

are stress ratings only and do not necessarily imply functional operation below these limits.

4

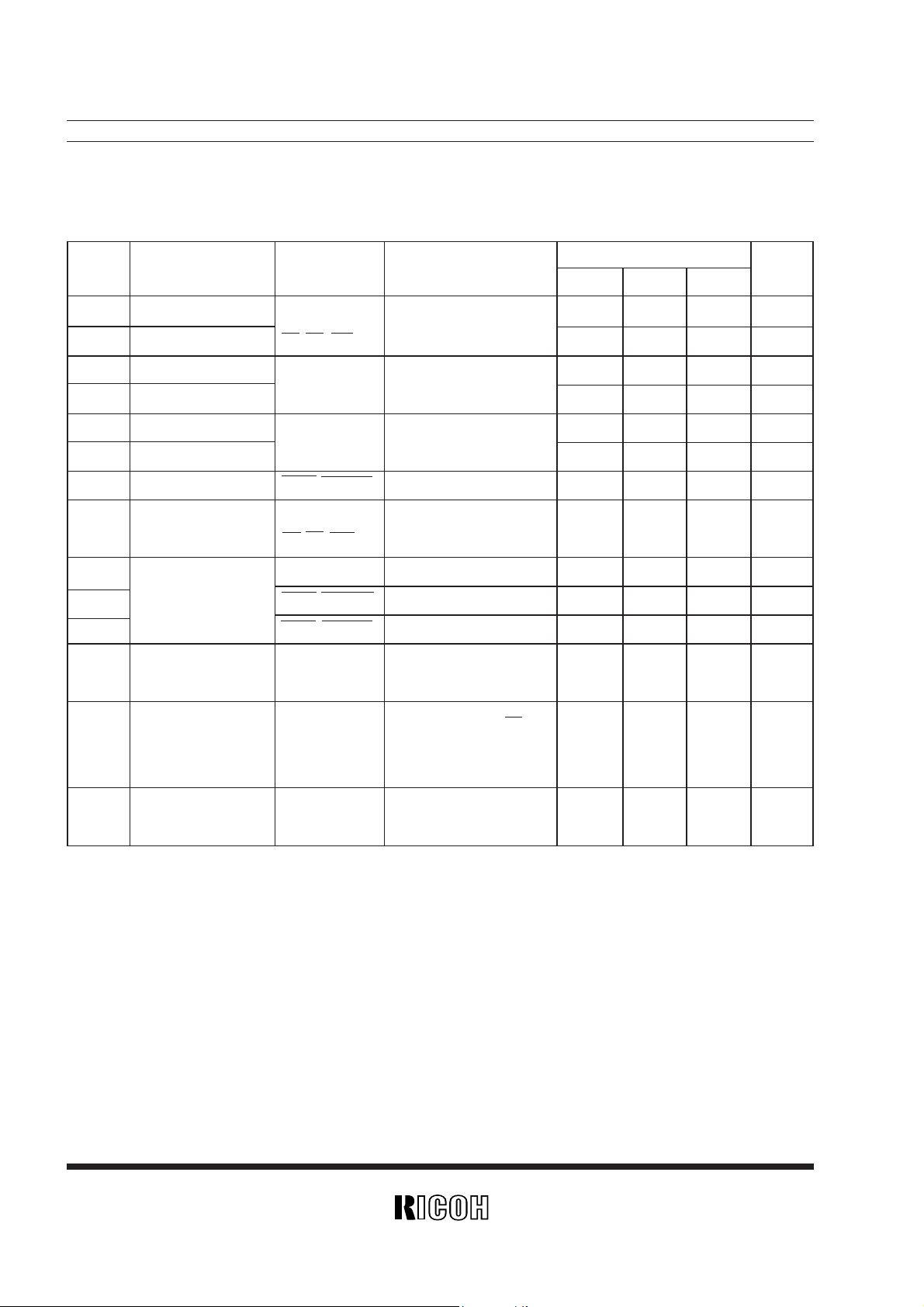

DC ELECTRICAL CHARACTERISTICS

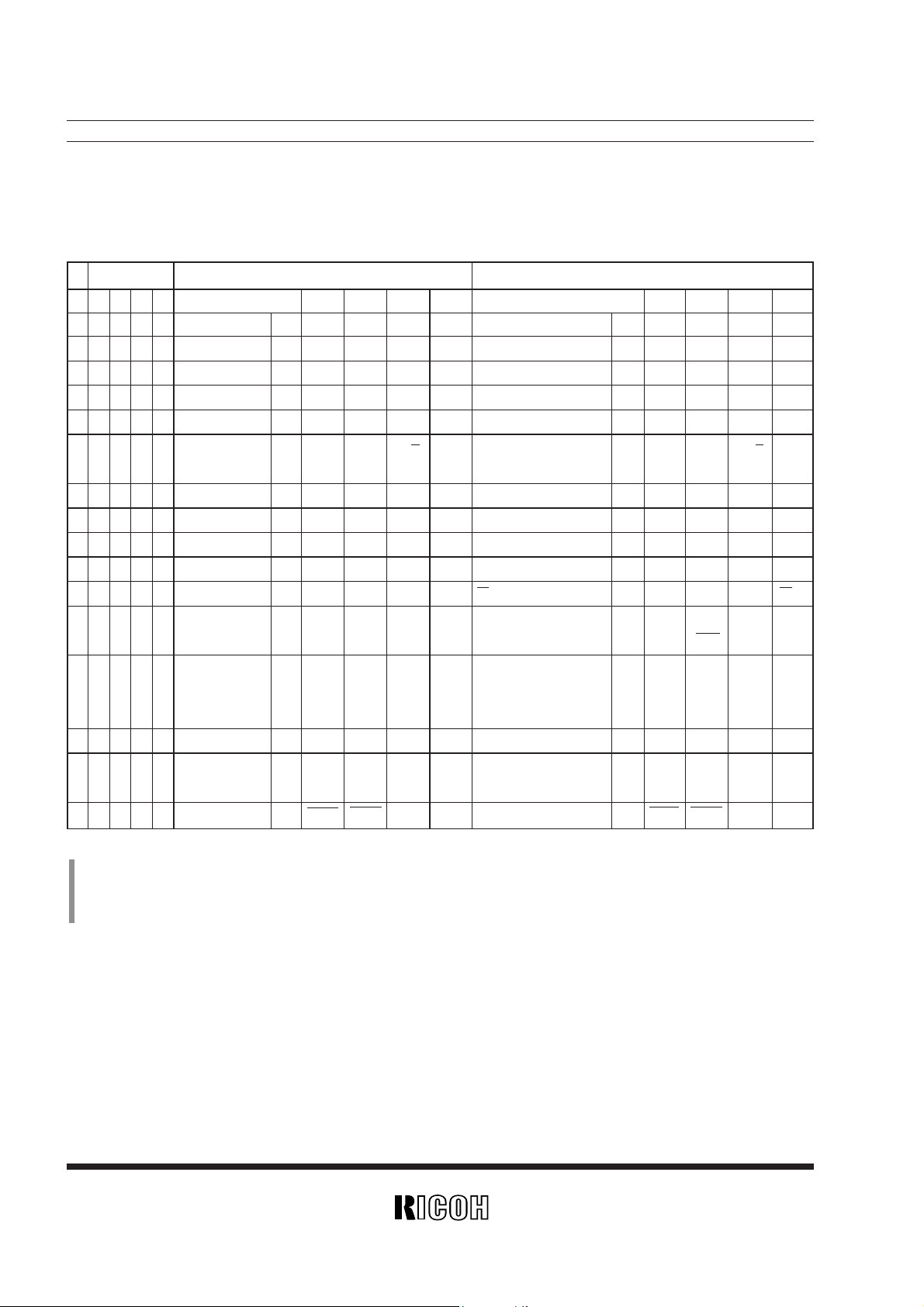

RP/RF/RS5C62

Unless Noted, VSS=0V, VDD=5V±10%, Topt=–20 to +70˚C, X'tal=32.768kHz, (R1²35k½), CG=10pF, CD=10pF

Symbol Item Pin Name Conditions

Limits

Unit

MIN. TYP. MAX.

VIH1 “H” input voltage

A0 to A3, D0 to D3

2.2 VDD+0.3 V

VIL1 “L” input voltage CS, RD, WR –0.3 0.8 V

VIH2 “H” input voltage

CE

0.8´VDD VDD+0.3 V

VIL2 “L” input voltage –0.3 0.2´VDD V

VOH1 “H” output voltage

D0 to D3

I

OH1=–400µA

2.4 V

VOL1 “L” output voltage

I

OL1=2mA

0.4 V

VOL2 “L” output voltage INTR, TMOUT IOL2=2mA 0.4 V

I

ILK Input leak current

A0 to A3, CE,

V

ILK=VDD or VSS –1 1 µA

CS, RD, WR

IOZ1

Output off leak

D0 to D3 V

OZ1=VDD or VSS –5 5 µA

IOZ2

current

INTR, TMOUT V

OZ2

=VDD –2 2 µA

IOZ3 INTR, TMOUT VOZ3=10V –5 5 µA

I

DD1

Consumption

V

DD

VDD=2.5V, CE=L

3 µA

current for back-up Others : OPEN

Consumption

V

DD=5.5V, CE=H, CS=H,

I

DD2

current for stand-by

V

DD Output : OPEN 8 µA

Input : VDD or VSS

¶f

Oscillation frequency OSCIN V

DD=2.5 to 5.5V

–1 1 ppm

drift for voltage drift OSCOUT Topt=25˚C

5

RP/RF/RS5C62

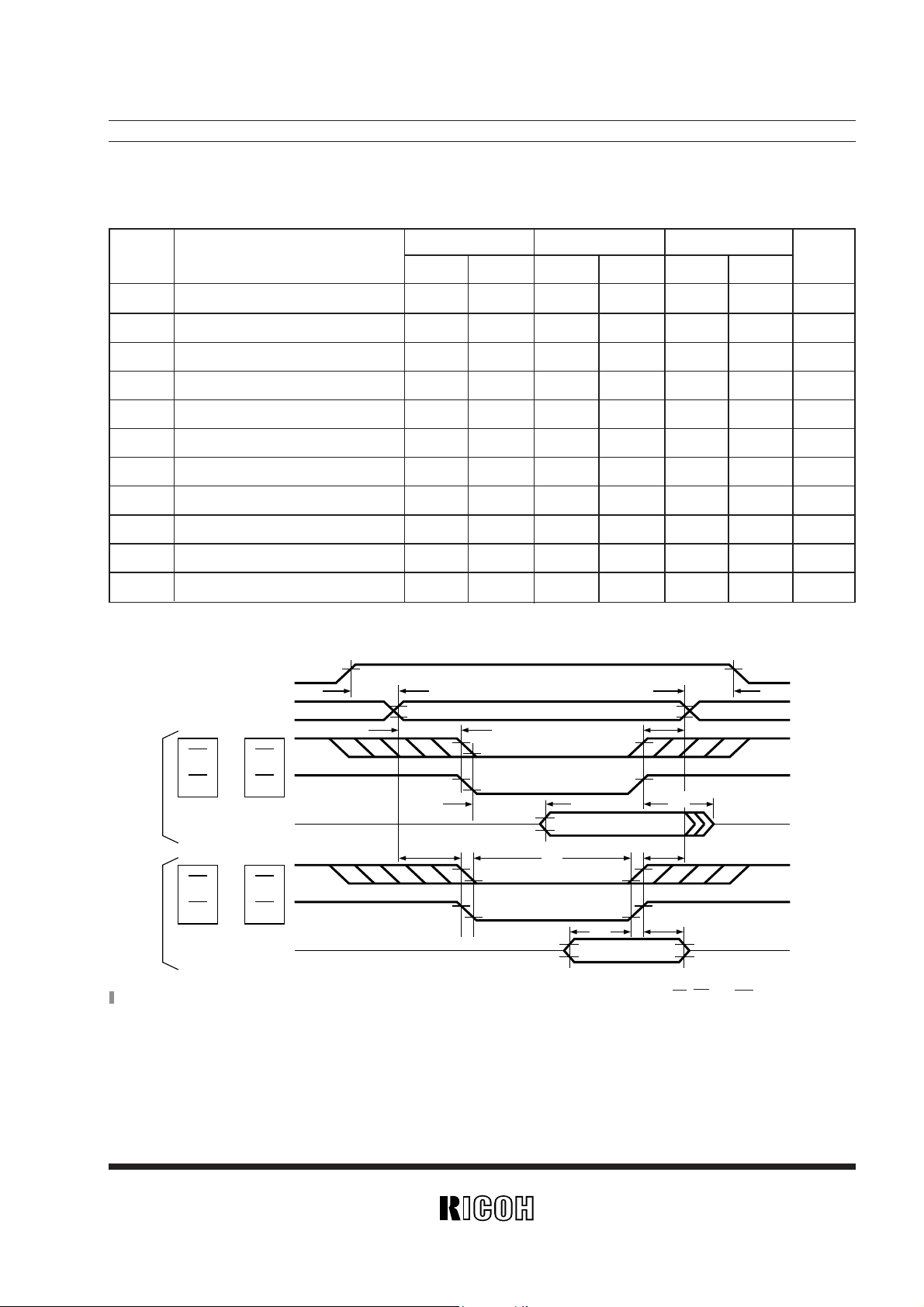

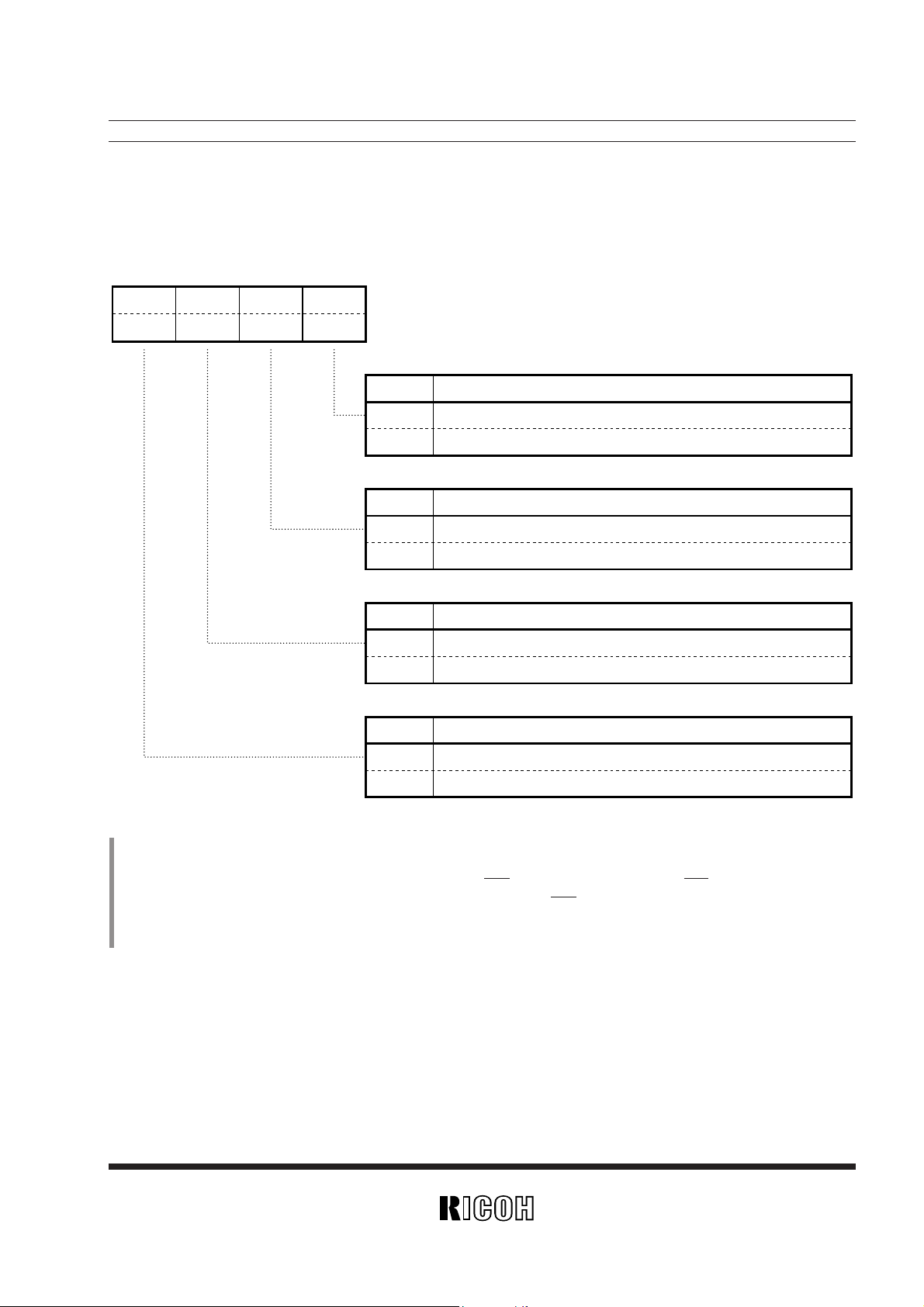

AC ELECTRICAL CHARACTERISTICS

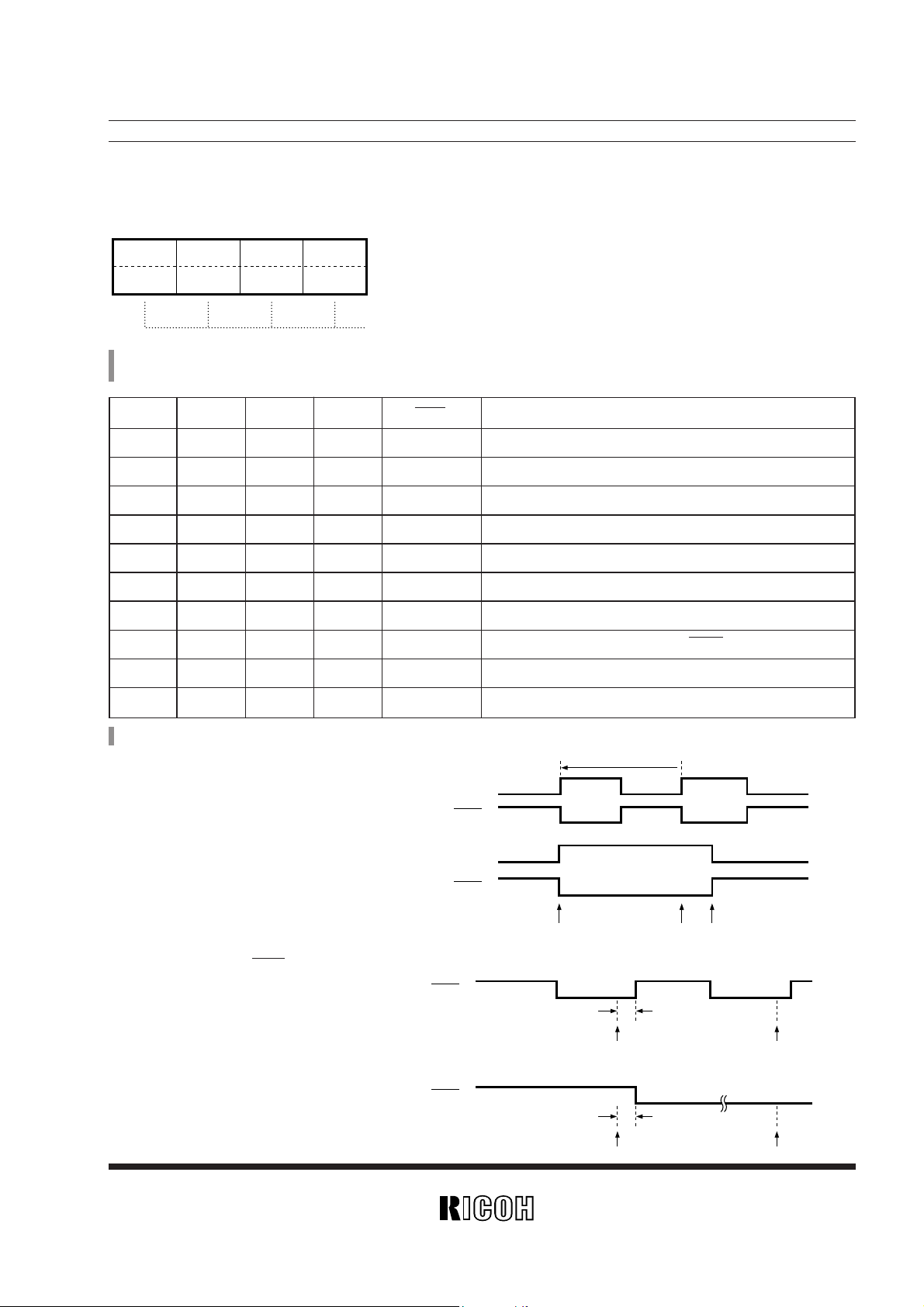

TIMING CHART

VSS=0V, Topt=–20 to +70˚C

Symbol Item

V

DD=5V±10% VDD=3V±10% VDD=5V±20%

Unit

MIN. MAX. MIN. MAX. MIN. MAX.

tCES CE Setup Time 500 1,000 500 ns

tCEH CE Hold Time 500 1,000 500 ns

tAS (RD) Address Setup Time (For Read) 20 20 20 ns

tAS (WR) Address Setup Time (For Write) 20 20 20 ns

tAH (RD) Address Hold Time (For Read) 10 10 10 ns

tAH (WR) Address Hold Time (For Write) 10 10 10 ns

tRR Output Data Delay Time

(CL=100pF)

120 295 150 ns

tRZ Output Data Floating Time 70 95 75 ns

tW Write Pulse Width 120 195 150 ns

tDS Input Data Setup Time 60 95 75 ns

tDH Input Data Hold Time 10 10 10 ns

*

) The diagonally shaded sections marked in the above timing chart indicate the allowable high or low levels of the CS, RD, and WR pin inputs.

Input/Output Conditions

(V

DD= 5V±10%) (VDD= 3V±10%) (VDD= 5V±20%)

V

IH = 2.2V VIH = 0.8 ´ VDD VIH = 2.4V

V

IL = 0.8V VIL = 0.2 ´ VDD VIL = 0.4V

V

OH= 2.2V VOH= 0.8 ´ VDD VOH= 2.4V

V

OL = 0.8V VOL = 0.2 ´ VDD VOL= 0.4V

CE

tCES tCEH

A0 to A3

tAH(RD)tAS(RD)

CS

Read

Write

RD

D0 to D3

(Read Data)

CS

WR

D0 to D3

(Write Data)

RD

or

CS

tRR

Valid

tAS(WR)

WR

or

CS

tW

tDS

Valid

tRZ

tAH(WR)

tDH

6

RP/RF/RS5C62

FUNCTIONAL DESCRIPTION

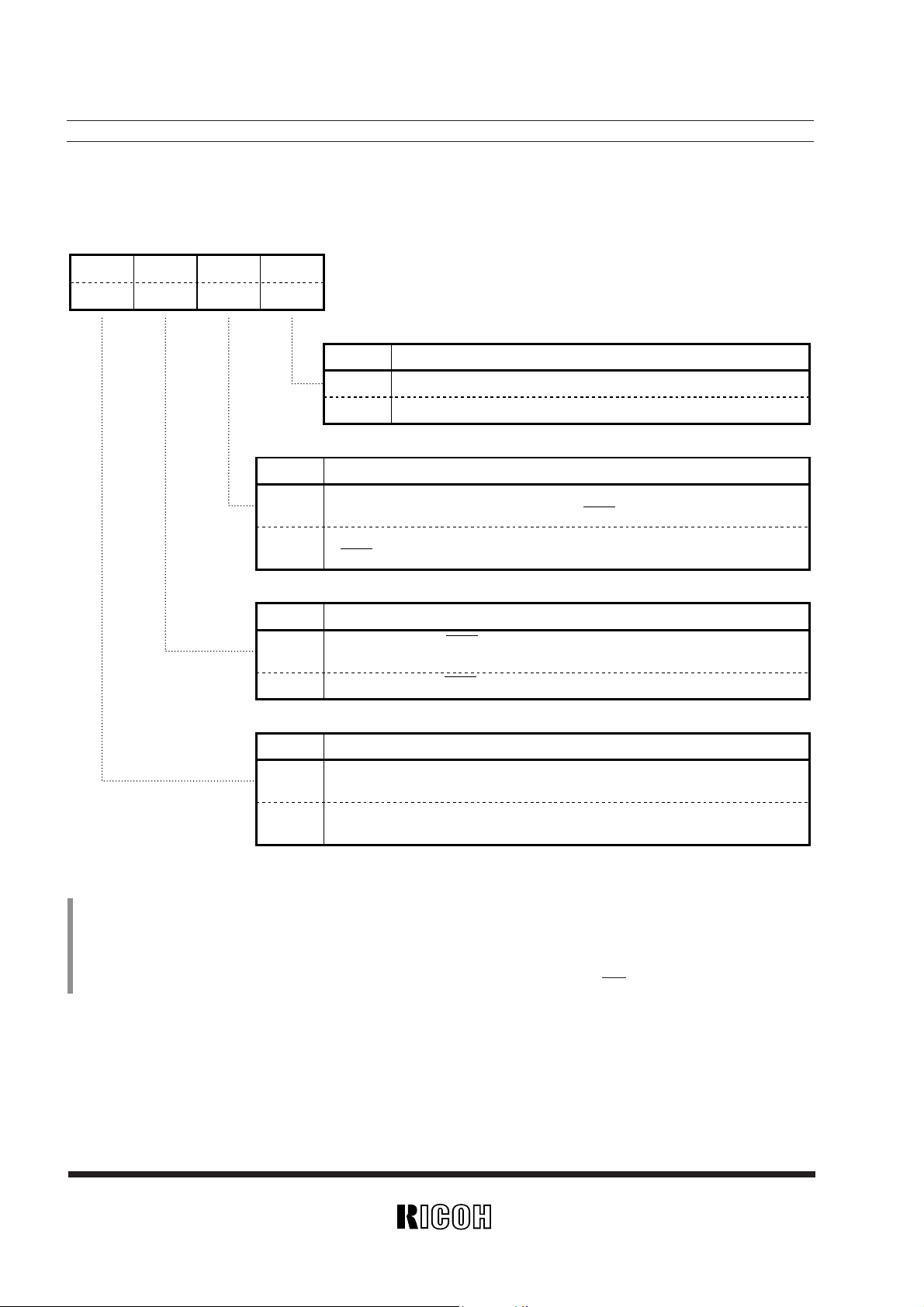

1. Addressing

Address Bus BANK 0 (BANK=0) BANK 1 (BANK=1)

A3 A2 A1 A0 Description D3 D2 D1 D0 Description D3 D2 D1 D0

0 0 0 0 0 1 sec. Counter R/W S8 S4 S2 S1

Cyclic interrupt select Reg.

W/O CT3 CT2 CT1 CT0

1 0 0 0 1 10 sec. Counter R/W S40 S20 S10

Adust Reg.

W/O ADJ

2 0 0 1 0 1 min. Counter R/W M8 M4 M2 M1 1 min. alarm Reg. R/W AM8 AM4 AM2 AM1

3 0 0 1 1 10 min. Counter R/W M40 M20 M10 10 min. alarm Reg. R/W AM40 AM20 AM10

4 0 1 0 0 1 hour Counter R/W H8 H4 H2 H1 1 hour alarm Reg. R/W AH8 AH4 AH2 AH1

5 0 1 0 1 10 hour Counter R/W

P/A

H10 10 hour alarm Reg. R/W

AP/A

AH10

or H20 or AH20

6 0 1 1 0

day-of-the-week Counter

R/W W4 W2 W1

7 0 1 1 1 1 day Counter R/W D8 D4 D2 D1

8 1 0 0 0 10 day Counter R/W D20 D10

9 1 0 0 1 1 month Counter R/W MO8 MO4 MO2 MO1

A 1 0 1 0

10 month Counter

R/W MO10 12/24 select Reg. W/O 12/24

B 1 0 1 1 1 year Counter R/W Y

8 Y4 Y2 Y1 Leap Year Reg.

R/O LY

1 LY0

R/W LYE

W/O TM

2 TM1 TM0

C 1 1 0 0 10 year Counter R/W Y80 Y40 Y20 Y10 Timer Clock Select Reg. R/W TM3

R/O TMFG

D 1 1 0 1 Control Reg. 1 W/O WTEN ALEN TMR BANK Control Reg. 1 W/O WTEN ALEN TMR BANK

E 1 1 1 0 Control Reg. 2

R/O BSY

Control Reg. 2

R/O BSY

R/W CTFG ALFG XSTP R/W CTFG ALFG XSTP

F 1 1 1 1 Control Reg. 3 W/O TSTA TSTB

WTRST

Control Reg. 3 W/O TSTA TSTB

WTRST

*

1) R/W bits can be read and written. R/O bits can only be read. W/O bits can only be written.

*

2) It is no problem to attempt writing to R/O bits and blank bits, but the attempt will fail.

*

3) If W/O bits and blank bits are read, the returned value is 0.

*

4) The control registers 1, 2, and 3 have the same address assignment for BANK0 and BANK1.

7

RP/RF/RS5C62

2. Functions of Registers

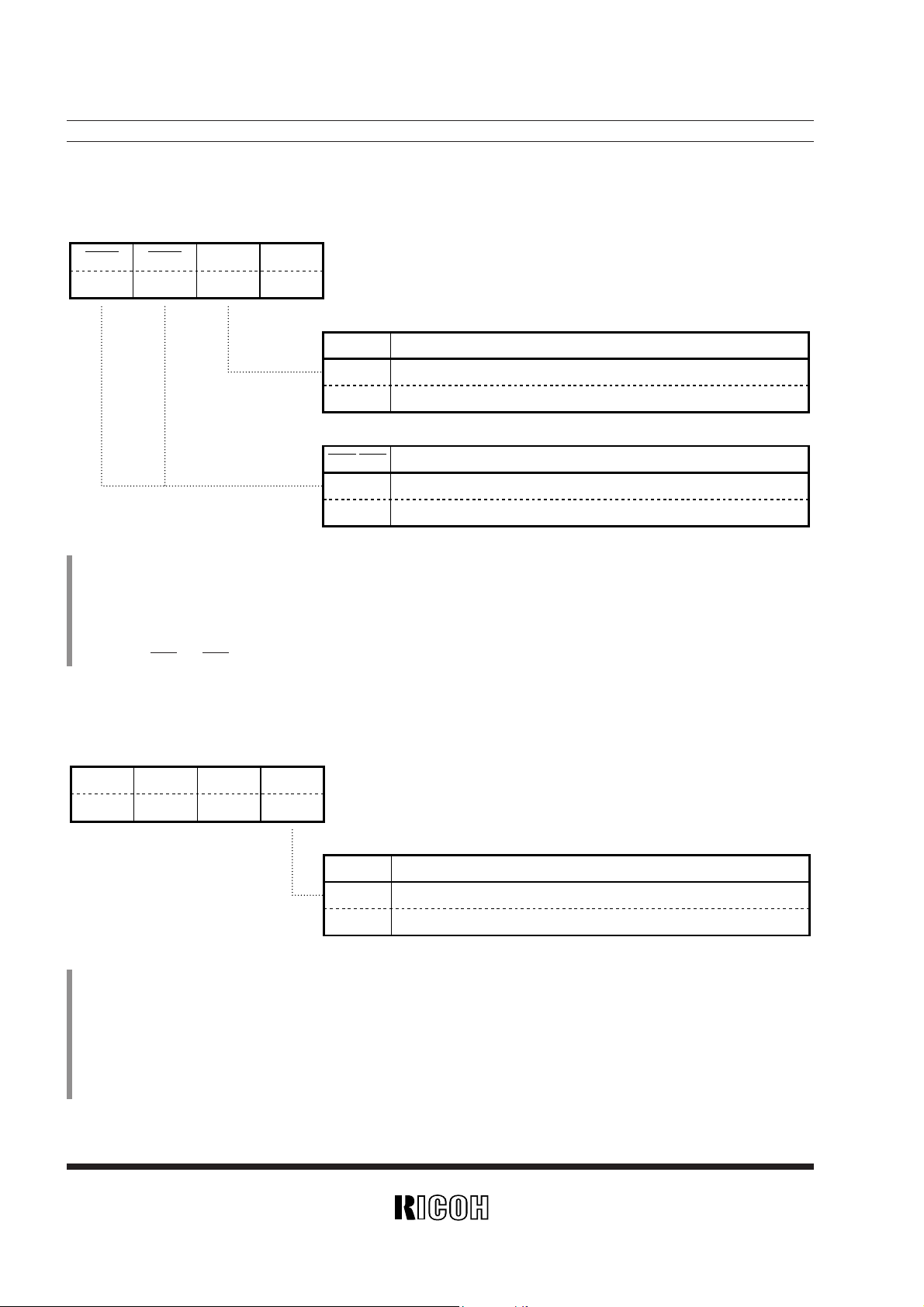

2.1 Control Register 1 (Bank0/1 at “Dh”)

D3 D2 D1 D0

0

0 0 0

WTEN ALEN TMR BANK

(For write operation)

(For read operation)

*

1

Bank switching bit

BANK

Function

0

1

Specifies selection of BANK0 in the address table.

Specifies selection of BANK1 in the address table.

TMR

Function

0

1

Specifies no change.

Specifies resetting of the timer conditional on restart.

Timer resetting bit

*

2

ALEN

Function

0

1

Disables an alarm interrupt.

Enables an alarm interrupt.

Alarm operation setting bit

*

3

WTEN

Function

0

1

Disables a carry to the 1-second time digit.

Enables a carry to the 1-second time digit.

Time count operation setting bit

*

4

*

1) The BANK bit is intended for only write operation and always read as “0”.

*

2) The timer frequency can be set by the timer clock selection register.

*

3) Setting the ALEN bit to “0” during output of an alarm interrupt from the INTR pin (while it is held low) turns off the INTR pin.

Setting the ALEN bit to “1” in matching between clock time and alarm time drives the INTR pin low within a maximum of 61.1µs.

*

4) A 1-second carry with the WTEN bit set to “0” increments the second digit by 1 upon setting of the WTEN bit to “1”. This bit will

automatically be set to “1” upon driving low the CE pin.

8

RP/RF/RS5C62

2.2 Control Register 2 (BANK0/1 at “Eh”)

D3 D2 D1 D0

BSY

CTFG ALFG XSTP

CTFG ALFG XSTP

(For write operation)

(For read operation)

XSTP

Function

0

1

Indicates the progress of oscillation. Intended for setting to “0”.

Indicates the stop of oscillation. Not intended for setting to “1”.

ALFG

Function

0

1

Indicates an alarm interrupt is disabled or indicates mismatching between clock

time and alarm time (upon turning off the INTR pin). Intended for setting to “0”.

Indicates matching between clock time and alarm time (upon driving low the

INTR pin). Not intended for setting to “0”.

Alarm time match indication bit

*

3

CTFG

Function

0

1

Indicates that the INTR pin is turned off. Intended for setting to “0” in the level

mode.

Indicates that the INTR pin is driven low. Not intended for setting to “0”.

Cyclic interrupt indication bit

*

4

BSY

Function

0

1

Indicates the normal state of the time and calendar counters (no carry or no

reset pulse).

Indicates the busy state of the time and calendar counters (a carry or a reset

pulse generated).

Time/calendar counter state indication bit

*

5

*

*

1

Oscillation stop detection bit

*

2

*

1) The BSY bit is intended for only read operation and is not intended for write operation.

*

2) The XSTP bit is used to detect the stop of the crystal oscillator. The XSTP bit is set to “1” upon the stop of oscillation and held at “1” after the restart

of oscillation. Upon detection of the stop of oscillation, the built-in timer counter is reset (because the TM

3 bit in the timer clock selection register is

reset).

*

3) When the ALEN bit is set to “1”, the ALFG bit is also set to “1” upon output of an alarm interrupt from the INTR pin (while it is held low).

9

RP/RF/RS5C62

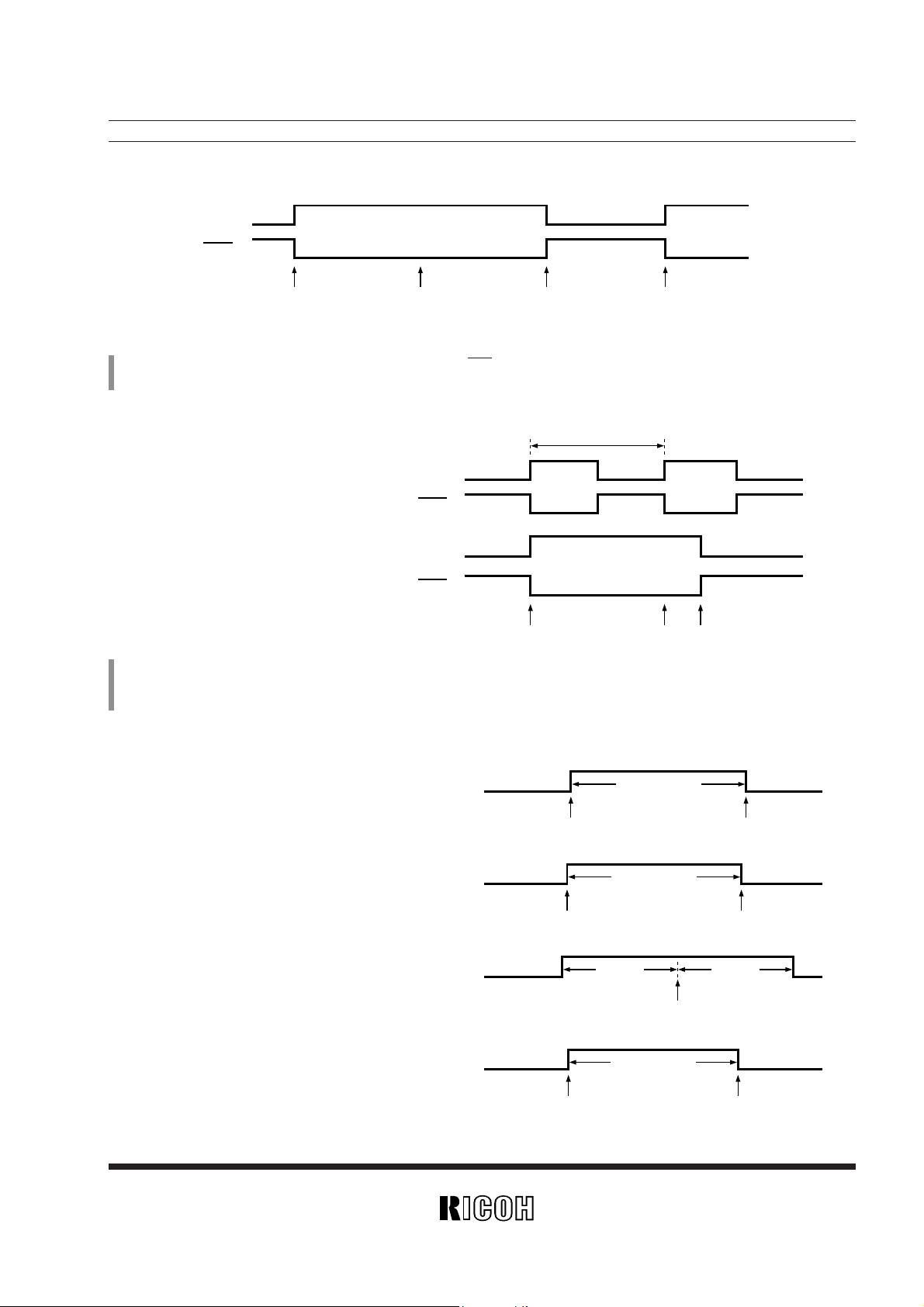

*

4) The CTFG bit is set to “1” upon output of a cyclic interrupt from the INTR pin (while it is held low).

(A cyclic interrupt may occur in the pulse mode and the level mode.)

ALFG

INTR

Alarm time match Alarm time match Setting the ALFG

bit to “0”

Alarm time match

CTFG

INTR

CTFG

INTR

Interrupt

Preset interrupt cycle

Setting the CTFG bit to “0”Interrupt

*

5) When the BSY bit is set to “1”, write operation must not be performed upon the time and calendar counters which are being updated. Normally, read

operation must be performed from the counters upon setting the BSY bit to “0”. Reading from them without checking the BSY bit requires separate

software for preventing reading errors. The BSY bit is set to “1” in the four cases below:

Setting the ADJ bit to “1”

Setting the WTEN bit to “1”

Setting the WTRST bit to “1” Completion of reset

Completion of pulse for carry to second digit

Completion of correction by +1

Completion of adjustment

MAX.122.1µs

MAX.122.1µs

MAX.122.1µs

30.5µs91.6µs

• Pulse mode

(The CT3 bit is set to “0”.)

(The CTFG bit is not intended for write

operation.)

• Level mode

(The CT3 bit is set to “1”.)

(The CTFG bit is intended for setting to “0”

only.)

(I) Adjustment by ±30 seconds

(II) Correction by +1

(when there is a 1-second carry in transition of the

WTEN bit from“0” to “1”)

(III)Normal 1-second carry

(IV) Counter resetting (setting of WTRST bit)

(Resetting the 1 to 8Hz dividers)

10

RP/RF/RS5C62

2.3 Control Register 3 (BANK0/1 at “Fh”)

D3 D2 D1 D0

0

0 0 0

(For write operation)

(For read operation)

*

2

Bit for resetting lower-order counter than the second counter.

*

3

WTRST

Function

0

1

Specifies normal operation.

Specifies resetting of 1- to 8-Hz dividers conditional on restart.

TSTA,TSTB

Function

0

1

Specifies setting of the test mode.

Specifies setting of normal operation.

Test mode setting bits

*

4

TSTA TSTB

WTRST

*

*

1

*

1) The bit marked with “*” is not intended for write operation.

*

2) This bit is intended for only write operation and always read as “0”.

*

3) When set to “1”, the WTRST bit specifies resetting of the lower-order counter than the 1 second counter ranging from 8Hz and 4Hz to 2Hz and 1Hz

conditional on restart. The WTRST bit is used to adjust the lower-order counter than the 1 second counter. After the WTRST bit is set to “1”, the

BSY bit is set to “1” for a maximum of 122.1µs.

*

4) Both the TSTA and TSTB bits must be set to “1” to specify normal operation and will automatically be set to “1” upon driving low the CE pin.

2.4 Adjustment Register (BANK1 at “1h”)

D3 D2 D1 D0

0

0 0 0

(For write operation)

(For read operation)

*

2

Second digit adjustment bit

*

3

Function

0

1

Specifies normal operation.

Specifies adjustment of second digit.

*

*

1

*

*

ADJ

ADJ

*

1) The bits marked with “*” are not intended for write operation.

*

2) This bit is intended for only write operation and always read as “0”.

*

3) The ADJ bit is used to correct the second digit. When set to “1”, the ADJ bit functions as follows:

1) For digits ranging from 00 seconds to 29 seconds ® Resets the lower-order counter than the 1 second counter (in the same manner as the

WTRST bit) and sets the second digit to “00”.

2) For digits ranging from 30 seconds to 59 seconds ® Resets the second and lower-order counters (in the same manner as the WTRST bit), sets

the second digit to “00” and increments the minute digit by 1. The BSY bit is set to “1” for a maximum of 122.1µs after the ADJ bit is set to “1”.

11

RP/RF/RS5C62

2.5 Interrupt Cycle Selection Register (BANK1 at “0h”)

D3 D2 D1 D0

0

0 0 0

CT

3 CT2 CT1 CT0 (For write operation)

(For read operation)

*

1

Interrupt cycle/output mode selection bits

*

2

*

1) These bits are intended for only write operation and always read as “0”.

*

2) The CT3 to CT0 bits are used to set interrupt cycles and output modes as shown in the table below:

*

) The bits marked with “*” are set to “0” or “1”.

CTFG

Preset interrupt cycle

INTR

CTFG

INTR

Interrupt Setting the CTFG bit to “0”(Interrupt)

• Pulse mode

(The CT3 bit is set to “0”.)

(The CTFG bit is not intended for write operation.)

• Level mode

(The CT3 bit is set to “1”.)

(The CTFG bit is intended for setting to “0” only.)

CT3 CT2 CT1 CT0 INTR Remarks

*

0 0 0 “OFF” Disable a cyclic interrupt.

*

0 0 1 2048Hz Specify a cycle (T) of 0.488ms (1/2048Hz).

*

0 1 0 1024Hz Specify a cycle (T) of 0.977ms (1/1024Hz).

*

0 1 1 128Hz Specify a cycle (T) of 7.813ms (1/128Hz).

*

1 0 0 16Hz Specify a cycle (T) of 62.5ms (1/16Hz).

*

1 0 1 1Hz Specify a cycle (T) of 1s (1/1Hz).

*

1 1 0 1/60Hz Specify a cycle (T) of 60s (1/1/60Hz).

*

1 1 1 “ON” Specify the fixed low level of the INTR pin output.

0

* * *

Pulse mode Specify a duty cycle of 50%. See below.

1

* * *

Level mode See below.

• Relationship between INTR pin output and

upward second count

INTR

INTR

Upward second count Upward second count

Upward second count Upward second count

(1) Pulse mode (when 1Hz or 1/60Hz is selected)

(2) Level mode (when 1Hz or 1/60Hz is selected)

30.5µs

30.5µs

Loading...

Loading...