Page 1

APPLICATION NOTE

R01AN1666EJ0220

RX Family

Rev. 2.20

ADC Module Using Firmware Integration Technology

Introduction

This module provides support for all features of the 12-bit A/D Converter on the RX110, RX111, RX113, RX130,

RX210, RX230, RX231, RX631, RX63N, RX64M, RX65N and RX71M.

Target Device

The following is a list of devices that are currently supported by this API:

• RX110, RX111, RX113, RX130 Groups

• RX210 Group

• RX230, RX231 Groups

• RX631, RX63N Groups

• RX64M Group

• RX65N Group

• RX71M Group

When using this application note with other Renesas MCUs, careful evaluation is recommended after making

modifications to comply with the alternate MCU.

Dec 01, 2016

Related Documents

• Firmware Integration Technology User’s Manual (R01AN1833)

• Board Support Package Firmware Integration Technology Module (R01AN1685)

• Adding Firmware Integration Technology Modules to Projects (R01AN1723)

• Adding Firmware Integration Technology Modules to CS+ Projects (R01AN1826)

R01AN1666EJ0220 Rev. 2.20 Page 1 of 74

Dec 01, 2016

Page 2

RX Family ADC Module Using Firmware Integration Technology

Contents

1. Overview ........................................................................................................................................... 3

2. API Information.................................................................................................................................. 4

2.1 Hardware Requirements ................................................................................................................... 4

2.2 Hardware Resource Requirements ................................................................................................... 4

2.3 Software Requirements ..................................................................................................................... 4

2.4 Limitations ......................................................................................................................................... 4

2.5 Supported Toolchains ....................................................................................................................... 4

2.6 Header Files ...................................................................................................................................... 4

2.7 Integer Types .................................................................................................................................... 4

2.8 Configuration Overview ..................................................................................................................... 5

2.9 Code Size .......................................................................................................................................... 5

2.10 API Data Structures .......................................................................................................................... 6

2.11 Return Values.................................................................................................................................. 51

2.12 Adding a FIT Module to Your Project .............................................................................................. 51

3. API Functions .................................................................................................................................. 52

3.1 Summary ......................................................................................................................................... 52

3.2 R_ADC_Open() ............................................................................................................................... 53

3.3 R_ADC_Control() ............................................................................................................................ 56

3.4 R_ADC_Read() ............................................................................................................................... 67

3.5 R_ADC_ReadAll() ........................................................................................................................... 68

3.6 R_ADC_Close()............................................................................................................................... 69

3.7 R_ADC_GetVersion() ...................................................................................................................... 70

4. Pin Setting ....................................................................................................................................... 71

5. Demo Projects ................................................................................................................................. 72

5.1 s12ad_int_demo_rskrx113 .............................................................................................................. 72

5.2 s12ad_poll_demo_rskrx113 ............................................................................................................ 72

5.3 s12ad_poll_demo_rskrx130 ............................................................................................................ 72

5.4 s12ad_demo_rskrx64m ................................................................................................................... 72

5.5 s12ad_demo_rskrx71m ................................................................................................................... 72

5.6 s12ad_demo_rskrx231 .................................................................................................................... 72

5.7 Adding a Demo to a Workspace ..................................................................................................... 73

R01AN1666EJ0220 Rev. 2.20 Page 2 of 74

Dec 01, 2016

Page 3

RX Family ADC Module Using Firmware Integration Technology

1. Overview

This A/D Converter (ADC) driver supports the S12ADa peripheral on the RX63x, the S12ADb peripheral on the

RX11x/RX210, the S12ADC peripheral on the RX64M/RX71M, the S12ADE peripheral on the RX130/RX230/RX231

and the S12ADFa peripheral on the RX65x.

Depending on the MCU chosen, some features include, but are not limited to single scans, grouped single scans, and

continuous scanning. Peripheral features include register left or right alignment, clearing data after register reads,

summation and average of conversion results, and the ability to store data on alternate triggers of a channel. Channel,

temperature and internal reference voltage sensor specific features include setting sampling time using state counts, and

opting out of summation of samples. There is no dependency on any other software except for the board support

package (r_bsp module).

The ADC begins conversion when it receives a trigger. When the conversion is complete, a flag is set and an interrupt

issued if enabled. If the ADC is operating in a single scan mode, only one scan takes place per trigger. If the ADC is

operating in a continuous mode, scans continue indefinitely after the initial trigger occurs.

The trigger source may be synchronous from an MTU peripheral, Event Link Controller (ELC), or a TPU peripheral

(non-RX11x); asynchronous from an external trigger on ADTRG#, or from setting a bit in software. Note that even

though a software trigger is an asynchronous action, the hardware manual reserves the term “asynchronous trigger” to

refer to asynchronous external hardware triggers. Additionally, although the temperature sensor on the RX210 has its

own independent trigger, the driver hides this operation and the application should be written as if the standard software

trigger is being used.

The driver provides a Control() command for polled applications which checks to see if a scan completed after a trigger

occurs. If interrupts are in use, the interrupt will call a Callback function specified in the Open() function. The only

argument to the Callback function specifies whether the default scan has completed or a Group B scan has completed.

In general, the peripheral operates on a single trigger source. However, in a group mode, two different trigger sources

are used. Each group can contain one or more unique channels and may be scanned at different trigger intervals.

The majority of the driver serves to initialize the A/D peripheral and provide functions to read conversion results.

Settings which are common to all channels such as conversion alignment or addition count are set in the Open() call.

Specific channel enabling is done via a Control() command. Two Read() functions are provided- one which retrieves a

single conversion value and another which retrieves all conversion registers whether the channel is enabled or not.

For the RX11x/RX21x/RX63x there are 13 to 24 channels available for conversion depending upon the MCU chosen.

All MCUs include a Temperature and an Internal Reference Voltage sensor. Each has its own conversion register. In

addition, in non-RX63x MCUs, a single channel can be designated as a “double trigger”. This means the scan-complete

flag/interrupt occurs on every other scan. On an odd scan, the conversion result is placed in its normal data register. On

an even scan, the result is placed in a special register. Double trigger cannot be used with sensors or other channels

(unless the other channels are in Group B), and a sensor can only be scanned by itself.

For the RX64M/RX71M/RX65x there are 8 channels on Unit 0, 21 channels and two sensors (Temperature and Internal

Reference Voltage) on Unit 1. In addition, a single channel on each unit can be designated as a “double trigger”

channel. This means that the scan-complete flag/interrupt occurs on every other scan. On an odd scan, the conversion

result is placed in its normal data register. On an even scan, the result is placed in a special register. Double trigger

cannot be used with sensors or other channels (unless the other channels are in other Groups.). Sensors and channels

may be scanned together on Unit 1. A built-in level and window comparator is available for channels and sensors. The

sensors are available on unit 1 and a Sample & Hold feature is available on unit 0 for sampling up to 3 channels

simultaneously. A virtual channel is available for Self-Diagnosis against various voltages, and a Disconnect Detection

Assist feature allows for an initial charging or discharging of the internal capacitor. This 12-bit converter may also be

configured for 8 or 10-bit resolution for slightly faster conversion if desired, and an input is available for an external

amplifier (positive or negative gain) for up to 8 channels on unit 1.

R01AN1666EJ0220 Rev. 2.20 Page 3 of 74

Dec 01, 2016

Page 4

RX Family ADC Module Using Firmware Integration Technology

2. API Information

This Driver API follows the Renesas API naming standards.

2.1 Hardware Requirements

This driver requires your MCU support the following features:

• S12ADa, S12ADb, S12ADC, S12ADE or S12ADFa peripheral

2.2 Hardware Resource Requirements

This section details the hardware peripherals that this driver requires. Unless explicitly stated, these resources must be

reserved for the driver and the user cannot use them.

2.2.1 S12ADa/S12ADb/S12ADC/S12ADE/S12ADFa

This driver makes use of all features available on these peripherals.

2.2.2 GPIO

This driver utilizes port pins corresponding to each individual analog channel. These pins may not be used for GPIO.

2.3 Software Requirements

This driver is dependent upon the following packages:

• Renesas Board Support Package (r_bsp)

2.4 Limitations

Registers, settings, or usage notes vary depending on the mode used in the 12-bit A/D converter. APIs in this

application note must be used according to the 12-bit A/D converter chapter in the User's Manual: Hardware for the

MCU used.

2.5 Supported Toolchains

This driver is tested and working with the following toolchains:

• Renesas RX Toolchain v2.05.00

2.6 Header Files

Compile time configurable options are located in r_s12ad_rx\ref\r_s12ad_rx_config_reference.h. This file should be

copied into the r_config subdirectory of the project and renamed to r_s12ad_rx_config.h. It is this renamed file that

should be modified if needed and the original kept as a reference.

All API calls and their supporting interface definitions are located in r_s12ad_rx\r_s12ad_rx_if.h. Both this file and

r_s12ad_rx_config.h should be included by the User’s application.

2.7 Integer Types

This project uses ANSI C99 “Exact width integer types” in order to make the code clearer and more portable. These

types are defined in stdint.h.

R01AN1666EJ0220 Rev. 2.20 Page 4 of 74

Dec 01, 2016

Page 5

RX Family ADC Module Using Firmware Integration Technology

If this equate is set to 1, parameter checking is included

utilizes the system default setting.

// 1.8V <= AVcc0 < 2.7V

This equate is for the Temperature Sensor gain

2.8 Configuration Overview

All configurable options that can be set at build time are located in the file “r_s12ad_rx_config.h”. A summary of these

settings are provided in the following table:

Configuration options in r_s12ad_rx_config.h

#define ADC_CFG_PARAM_CHECKING_ENABLE 1

#define ADC_CFG_PGA_GAIN 0

// 2.7V <= AVcc0 < 3.6V

//#define ADC_CFG_PGA_GAIN 1

// 3.6V <= AVcc0 < 4.5V

//#define ADC_CFG_PGA_GAIN 2

// 4.5V <= AVcc0 <= 5.5V

//#define ADC_CFG_PGA_GAIN 3

Table 1: Info about the configuration

in the build. If the equate is set to 0, the parameter

checking is omitted from the build. Setting this equate

to BSP_CFG_PARAM_CHECKING_ENABLE

amplifier on the RX210. The default is a value of 0

which is good for all target voltages. For best

temperature resolution, the voltage range which most

accurately reflects the AVcc0 should have its #define

uncommented.

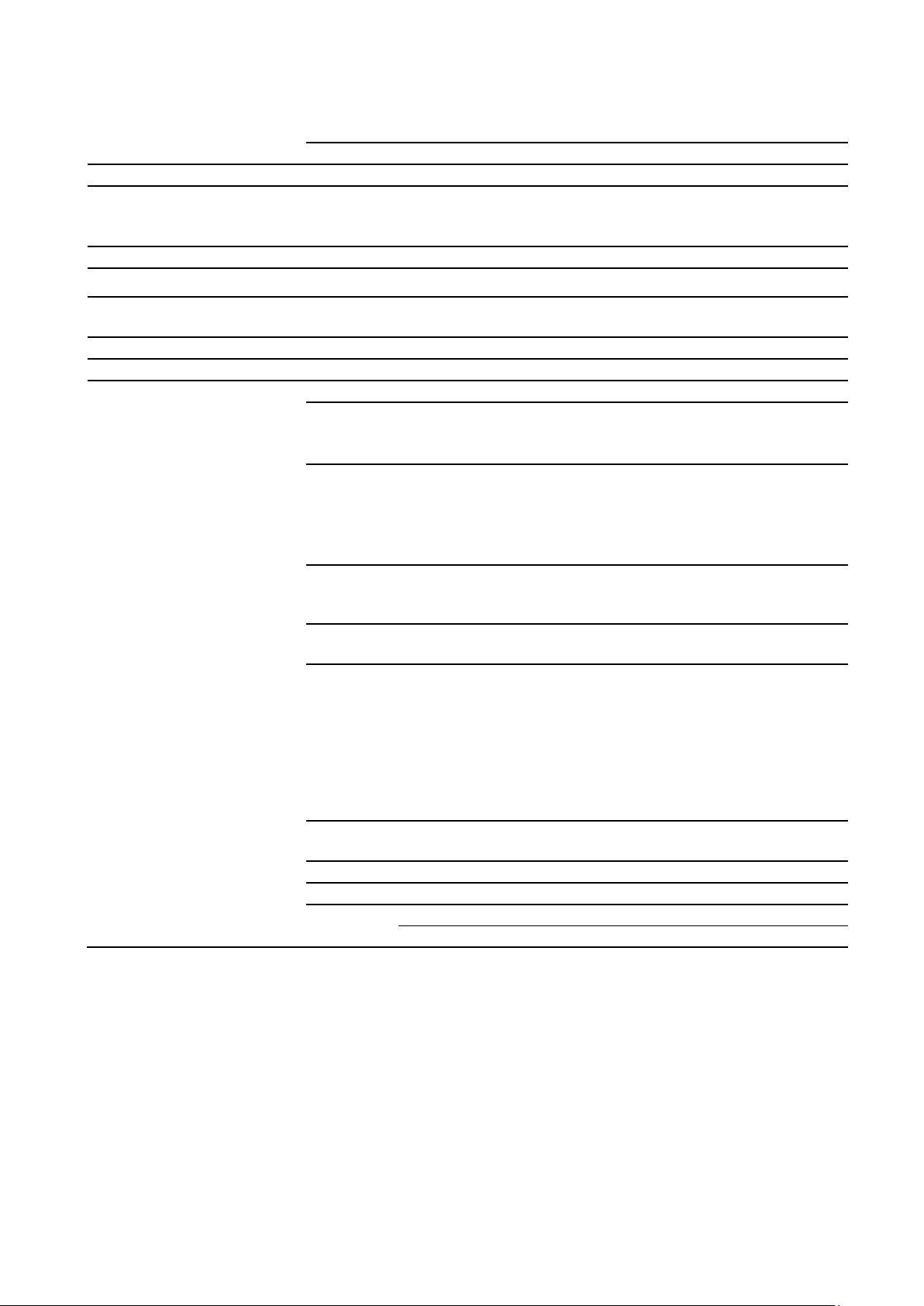

2.9 Code Size

The code size is based on optimization level 2 and optimization type for size for the RXC toolchain in Section 2.5. The

ROM (code and constants) and RAM (global data) sizes are determined by the build-time configuration options set in

the module configuration header file.

With Parameter Checking Without Parameter Checking

ROM: 1354 bytes ROM: 983 bytes

RX110

RAM: 12 bytes RAM: 12 bytes

ROM: 1234 bytes ROM: 950 bytes

RX111

RAM: 124 bytes RAM: 124 bytes

ROM: 1471 bytes ROM: 1100 bytes

RX113

RAM: 12 bytes RAM: 12 bytes

ROM: 2560 bytes ROM: 1879 bytes

RX130

RAM: 12 bytes RAM: 12 bytes

ROM: 1671 bytes ROM: 1200 bytes

RX210

RAM: 12 bytes RAM: 12 bytes

ROM and RAM code sizes

R01AN1666EJ0220 Rev. 2.20 Page 5 of 74

Dec 01, 2016

Page 6

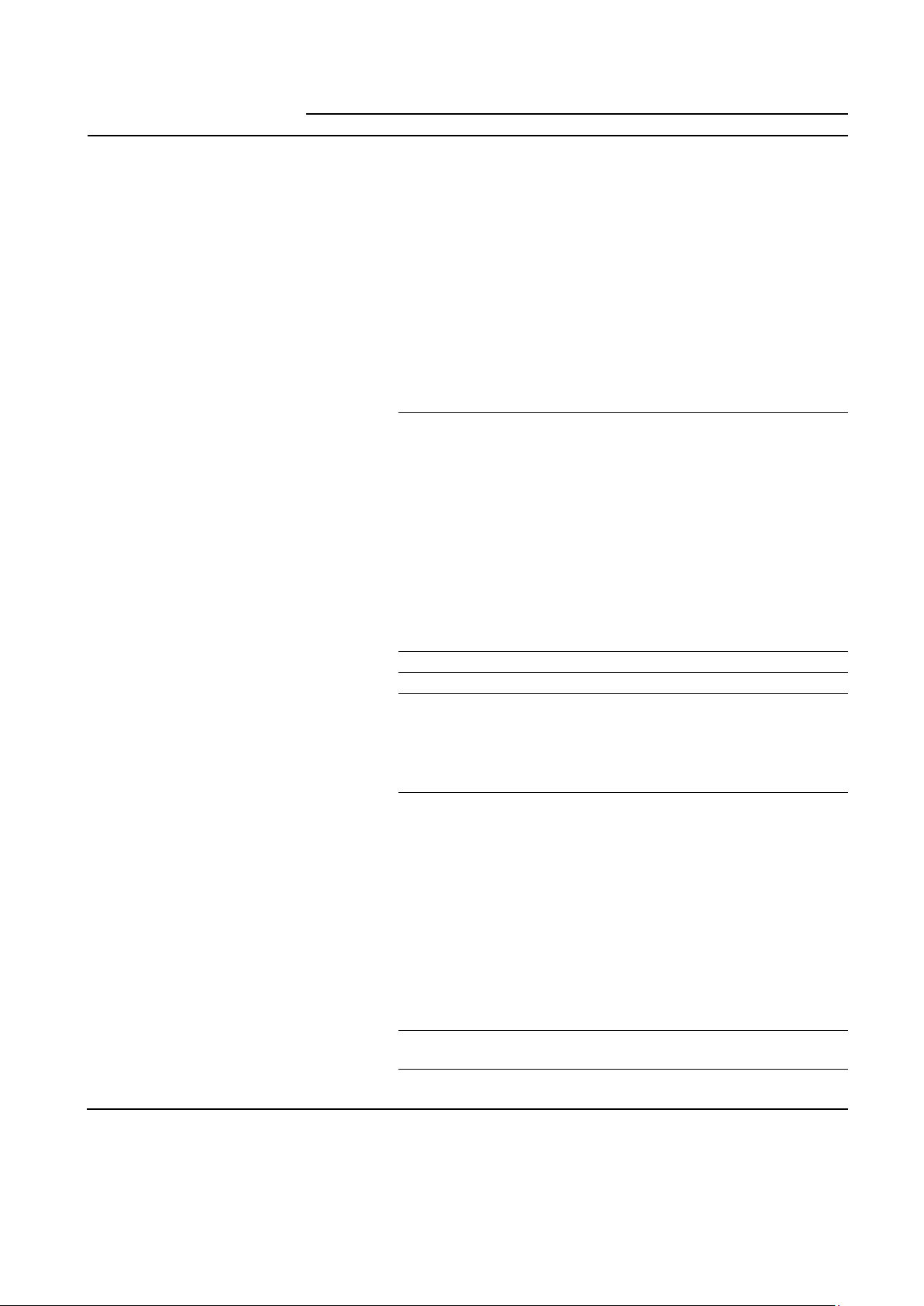

RX Family ADC Module Using Firmware Integration Technology

ROM: 2327 bytes ROM: 1616 bytes

RX230, RX231

RAM: 12 bytes RAM: 12 bytes

ROM: 1030 bytes ROM: 792 bytes

RX63N

RAM: 12 bytes RAM: 12 bytes

ROM: 3277 bytes ROM: 2464 bytes

RX64M

RAM: 32 bytes RAM: 32 bytes

ROM: 5176 bytes ROM: 4114 bytes

RX65N

RAM: 40 bytes RAM: 40 bytes

ROM: 3277 bytes ROM: 2464 bytes

RX71M

RAM: 32 bytes RAM: 32 bytes

Table 2: ROM and RAM code size

2.10 API Data Structures

This section details the data structures that are used with the driver’s API functions.

To provide strong type checking and reduce errors, many parameters used in API functions require arguments to be

passed using the provided type definitions. Allowable values are defined in the public interface files:

r_s12ad_rx_if.h

src/targets/rx110/r_s12ad_rx110_if.h

src/targets/rx111/r_s12ad_rx111_if.h

src/targets/rx113/r_s12ad_rx113_if.h

src/targets/rx130/r_s12ad_rx130_if.h

src/targets/rx210/r_s12ad_rx210_if.h

src/targets/rx230/r_s12ad_rx230_if.h

src/targets/rx231/r_s12ad_rx231_if.h

src/targets/rx63x/r_s12ad_rx63x_if.h

src/targets/rx64m/r_s12ad_rx64m_if.h

src/targets/rx65x/r_s12ad_rx65x_if.h

src/targets/rx71m/r_s12ad_rx71m_if.h

2.10.1 MCU Common Interface Types (r_s12ad_rx_if.h)

/* CALLBACK FUNCTION ARGUMENT DEFINITIONS */

typedef enum e_adc_cb_evt // callback function events

{

ADC_EVT_SCAN_COMPLETE, // normal/Group A scan complete

ADC_EVT_SCAN_COMPLETE_GROUPB, // Group B scan complete

#if (defined(BSP_MCU_RX65_ALL))

ADC_EVT_SCAN_COMPLETE_GROUPC, // Group C scan complete

#endif

#if (defined(BSP_MCU_RX64M) || defined(BSP_MCU_RX71M) ||

defined(BSP_MCU_RX65_ALL))

ADC_EVT_CONDITION_MET // 1+ chans/sensors met comparator condition

#endif

defined(BSP_MCU_RX65_ALL))

R01AN1666EJ0220 Rev. 2.20 Page 6 of 74

Dec 01, 2016

Page 7

RX Family ADC Module Using Firmware Integration Technology

ADC_EVT_CONDITION_METB // 1+ chans/sensors met comparator condition

#endif

} adc_cb_evt_t;

typedef struct st_adc_cb_args // callback arguments

{

adc_cb_evt_t event;

#if (defined(BSP_MCU_RX64M) || defined(BSP_MCU_RX71M) ||

defined(BSP_MCU_RX65_ALL))

uint32_t compare_flags; // valid only for compare event

#if (defined(BSP_MCU_RX65_ALL))

uint32_t compare_flagsb; // valid only for compare event b

#endif

uint8_t unit;

#endif

} adc_cb_args_t;

/* INTERFACE FUNCTIONS */

adc_err_t R_ADC_Open(uint8_t const unit,

adc_mode_t const mode,

adc_cfg_t * const p_cfg,

void (* const p_callback)(void *p_args));

adc_err_t R_ADC_Control(uint8_t const unit,

adc_cmd_t const cmd,

void * const p_args);

adc_err_t R_ADC_Read(uint8_t const unit,

adc_reg_t const reg_id,

uint16_t * const p_data);

adc_err_t R_ADC_ReadAll(adc_data_t * const p_all_data);

adc_err_t R_ADC_Close(uint8_t const unit);

uint32_t R_ADC_GetVersion(void);

2.10.2 RX110 Interface Types ( r_s12ad_rx110_if.h )

/* ADC_OPEN() ARGUMENT DEFINITIONS */

typedef enum e_adc_mode

{

ADC_MODE_SS_TEMPERATURE, // single scan temperature sensor

ADC_MODE_SS_INT_REF_VOLT, // single scan internal ref voltage sensor

ADC_MODE_SS_ONE_CH, // single scan one channel

ADC_MODE_SS_MULTI_CH, // 1 trigger source, scan multiple channels

ADC_MODE_CONT_ONE_CH, // continuous scan one channel

ADC_MODE_CONT_MULTI_CH, // continuous scan multiple channels

ADC_MODE_SS_ONE_CH_DBLTRIG, // on even trig save to ADDBLDR & interrupt

ADC_MODE_SS_MULTI_CH_GROUPED, // 2 trigger sources, scan multiple channels

ADC_MODE_SS_MULTI_CH_GROUPED_DBLTRIG_A,

ADC_MODE_MAX // This definition DO NOT USE for R_ADC_Open() argument

} adc_mode_t;

typedef enum e_adc_trig // trigger sources (set to TRSA bit or TRSB bit)

{

ADC_TRIG_ASYNC_ADTRG = 0, // ext asynchronous trigger; not for

// Group modes nor double trigger modes

ADC_TRIG_SYNC_TRG0AN = 1, // MTU0 TRGA

ADC_TRIG_SYNC_TRG0BN = 2, // MTU0 TRGB

ADC_TRIG_SYNC_TRGAN = 3, // MTUx TRGA

R01AN1666EJ0220 Rev. 2.20 Page 7 of 74

Dec 01, 2016

Page 8

RX Family ADC Module Using Firmware Integration Technology

ADC_TRIG_SYNC_TRG0EN = 4, // MTU0 TRGE

ADC_TRIG_SYNC_TRG0FN = 5, // MTU0 TRGF

ADC_TRIG_SOFTWARE = 16 // software trigger; not for Group modes

// nor double trigger modes

// This is not set to TRSA or TRSB

} adc_trig_t;

typedef enum e_adc_add

{

ADC_ADD_OFF = 0, // addition is turned off for chans/sensors

ADC_ADD_TWO_SAMPLES = 1,

ADC_ADD_THREE_SAMPLES = 2,

ADC_ADD_FOUR_SAMPLES = 3

} adc_add_t;

typedef enum e_adc_align

{

ADC_ALIGN_RIGHT = 0x0000,

ADC_ALIGN_LEFT = 0x8000

} adc_align_t;

typedef enum e_adc_clear

{

ADC_CLEAR_AFTER_READ_OFF = 0x0000,

ADC_CLEAR_AFTER_READ_ON = 0x0020

} adc_clear_t;

typedef enum e_adc_speed

{

ADC_CONVERT_SPEED_NORM = 0x0000,

ADC_CONVERT_SPEED_HIGH = 0x0400

} adc_speed_t;

typedef struct st_adc_cfg

{

adc_add_t add_cnt;

adc_align_t alignment; // ignored if addition used

adc_clear_t clearing;

adc_speed_t conv_speed;

adc_trig_t trigger; // default and Group A trigger source

adc_trig_t trigger_groupb; // valid only for group modes

uint8_t priority; // for S12ADIO int; 1=lo 15=hi 0=off/polled

uint8_t priority_groupb; // GBADI interrupt priority; 0-15

} adc_cfg_t;

/* ADC_CONTROL() ARGUMENT DEFINITIONS */

typedef enum e_adc_cmd

{

// Commands for special hardware configurations

ADC_CMD_SET_SAMPLE_STATE_CNT,

// Commands to enable channels or sensors

ADC_CMD_ENABLE_CHANS, // enables chans and A & B INT if pri != 0

ADC_CMD_ENABLE_TEMP_SENSOR, // enables sensor and INT if priority != 0

ADC_CMD_ENABLE_VOLT_SENSOR, // enables sensor and INT if priority != 0

// Commands to enable hardware triggers or cause software trigger

ADC_CMD_ENABLE_TRIG, // ADCSR.TRGE=1 for sync/async triggers

ADC_CMD_SCAN_NOW, // software trigger start scan

R01AN1666EJ0220 Rev. 2.20 Page 8 of 74

Dec 01, 2016

Page 9

RX Family ADC Module Using Firmware Integration Technology

// Commands to poll for scan completion

ADC_CMD_CHECK_SCAN_DONE, // for Normal or GroupA scan

ADC_CMD_CHECK_SCAN_DONE_GROUPA,

ADC_CMD_CHECK_SCAN_DONE_GROUPB,

// Advanced control commands

ADC_CMD_DISABLE_TRIG, // ADCSR.TRGE=0 for sync/async trigs

ADC_CMD_DISABLE_INT, // interrupt disable; ADCSR.ADIE=0

ADC_CMD_ENABLE_INT, // interrupt enable; ADCSR.ADIE=1

ADC_CMD_DISABLE_INT_GROUPB, // interrupt disable; ADCSR.GBADIE=0

ADC_CMD_ENABLE_INT_GROUPB, // interrupt enable; ADCSR.GBADIE=1

} adc_cmd_t;

/* for ADC_CMD_SET_SAMPLE_STATE_CNT */

typedef enum e_adc_sst_reg // sample state registers

{

ADC_SST_CH0 = 0,

ADC_SST_CH1,

ADC_SST_CH2,

ADC_SST_CH3,

ADC_SST_CH4,

ADC_SST_CH6,

ADC_SST_CH8_TO_15,

ADC_SST_TEMPERATURE,

ADC_SST_VOLTAGE,

ADC_SST_REG_MAX = ADC_SST_VOLTAGE

} adc_sst_reg_t;

#define ADC_SST_CNT_MIN (6) // minimum sampling state count

#define ADC_SST_CNT_MAX (255)

#define ADC_SST_CNT_DEFAULT (20)

typedef struct st_adc_time

{

adc_sst_reg_t reg_id;

uint8_t num_states; // 6-255; default=20; ch8-15 use same value

} adc_time_t;

/* for ADC_CMD_ENABLE_CHANS */

// Bitwise OR these masks together for desired channels

#define ADC_MASK_CH0 (1<<0)

#define ADC_MASK_CH1 (1<<1)

#define ADC_MASK_CH2 (1<<2)

#define ADC_MASK_CH3 (1<<3)

#define ADC_MASK_CH4 (1<<4)

#define ADC_MASK_CH6 (1<<6)

#define ADC_MASK_CH8 (1<<8)

#define ADC_MASK_CH9 (1<<9)

#define ADC_MASK_CH10 (1<<10)

#define ADC_MASK_CH11 (1<<11)

#define ADC_MASK_CH12 (1<<12)

#define ADC_MASK_CH13 (1<<13)

#define ADC_MASK_CH14 (1<<14)

#define ADC_MASK_CH15 (1<<15)

#define ADC_MASK_GROUPB_OFF (0)

#define ADC_MASK_ADD_OFF (0)

typedef struct st_adc_ch_cfg // bit 0 is ch0; bit 15 is ch15

R01AN1666EJ0220 Rev. 2.20 Page 9 of 74

Dec 01, 2016

Page 10

RX Family ADC Module Using Firmware Integration Technology

{

uint32_t chan_mask; // channels/bits 0-15

uint32_t chan_mask_groupb; // valid for group modes

uint32_t add_mask; // valid if add enabled in Open()

} adc_ch_cfg_t;

/* ADC_READ() ARGUMENT DEFINITIONS */

typedef enum e_adc_reg

{

ADC_REG_CH0 = 0,

ADC_REG_CH1 = 1,

ADC_REG_CH2 = 2,

ADC_REG_CH3 = 3,

ADC_REG_CH4 = 4,

ADC_REG_CH6 = 6,

ADC_REG_CH8 = 8,

ADC_REG_CH9 = 9,

ADC_REG_CH10 = 10,

ADC_REG_CH11 = 11,

ADC_REG_CH12 = 12,

ADC_REG_CH13 = 13,

ADC_REG_CH14 = 14,

ADC_REG_CH15 = 15,

ADC_REG_TEMP = 16,

ADC_REG_VOLT = 17,

ADC_REG_DBLTRIG = 18,

ADC_REG_MAX = ADC_REG_DBLTRIG

} adc_reg_t;

#define ADC_REG_ARRAY_MAX (16)

/* ADC_READALL() ARGUMENT DEFINITIONS */

typedef struct st_adc_data

{

uint16_t chan[ADC_REG_ARRAY_MAX]; // chns/indexes used depends upon MCU

uint16_t temp;

uint16_t volt;

uint16_t dbltrig;

} adc_data_t;

2.10.3 RX111 Interface Types ( r_s12ad_rx111_if.h )

/* ADC_OPEN() ARGUMENT DEFINITIONS */

typedef enum e_adc_mode

{

ADC_MODE_SS_TEMPERATURE, // single scan temperature sensor

ADC_MODE_SS_INT_REF_VOLT, // single scan internal ref voltage sensor

ADC_MODE_SS_ONE_CH, // single scan one channel

ADC_MODE_SS_MULTI_CH, // 1 trigger source, scan multiple channels

ADC_MODE_CONT_ONE_CH, // continuous scan one channel

ADC_MODE_CONT_MULTI_CH, // continuous scan multiple channels

ADC_MODE_SS_ONE_CH_DBLTRIG, // on even trig save to ADDBLDR & interrupt

ADC_MODE_SS_MULTI_CH_GROUPED, // 2 trigger sources, scan multiple channels

ADC_MODE_SS_MULTI_CH_GROUPED_DBLTRIG_A,

ADC_MODE_MAX // This definition DO NOT USE for R_ADC_Open() argument

} adc_mode_t;

typedef enum e_adc_trig // trigger sources (set to TRSA bit or TRSB bit)

{

ADC_TRIG_ASYNC_ADTRG = 0, // ext asynchronous trigger; not for Group modes

// nor double trigger modes

R01AN1666EJ0220 Rev. 2.20 Page 10 of 74

Dec 01, 2016

Page 11

RX Family ADC Module Using Firmware Integration Technology

ADC_TRIG_SYNC_TRG0AN = 1, // MTU0 TRGA

ADC_TRIG_SYNC_TRG0BN = 2, // MTU0 TRGB

ADC_TRIG_SYNC_TRGAN_OR_UDF4N = 3, // MTUx TRGA or MTU4 underflow

//(complementary PWM mode)

ADC_TRIG_SYNC_TRG0EN = 4, // MTU0 TRGE

ADC_TRIG_SYNC_TRG0FN = 5, // MTU0 TRGF

ADC_TRIG_SYNC_TRG4AN = 6, // MTU4 TADCORA

ADC_TRIG_SYNC_TRG4BN = 7, // MTU4 TADCORB

ADC_TRIG_SYNC_TRG4AN_AND_TRG4BN = 8, // MTU4 TADCORA and MTU4 TADCORB

ADC_TRIG_SYNC_ELC = 9, // ELC

ADC_TRIG_SOFTWARE = 16 // software trigger; not for Group modes

// nor double trigger modes

// This is not set to TRSA or TRSB

} adc_trig_t;

typedef enum e_adc_add

{

ADC_ADD_OFF = 0, // addition is turned off for chans/sensors

ADC_ADD_TWO_SAMPLES = 1,

ADC_ADD_THREE_SAMPLES = 2,

ADC_ADD_FOUR_SAMPLES = 3

} adc_add_t;

typedef enum e_adc_align

{

ADC_ALIGN_RIGHT = 0x0000,

ADC_ALIGN_LEFT = 0x8000

} adc_align_t;

typedef enum e_adc_clear

{

ADC_CLEAR_AFTER_READ_OFF = 0x0000,

ADC_CLEAR_AFTER_READ_ON = 0x0020

} adc_clear_t;

typedef enum e_adc_speed

{

ADC_CONVERT_SPEED_NORM = 0x0000,

ADC_CONVERT_SPEED_HIGH = 0x0400

} adc_speed_t;

typedef struct st_adc_cfg

{

adc_add_t add_cnt;

adc_align_t alignment; // ignored if addition used

adc_clear_t clearing;

adc_speed_t conv_speed;

adc_trig_t trigger; // default and Group A trigger source

adc_trig_t trigger_groupb; // valid only for group modes

uint8_t priority; // for S12ADIO int; 1=lo 15=hi 0=off/polled

uint8_t priority_groupb;// GBADI interrupt priority; 0-15

} adc_cfg_t;

/* ADC_CONTROL() ARGUMENT DEFINITIONS */

typedef enum e_adc_cmd

{

// Commands for special hardware configurations

ADC_CMD_SET_SAMPLE_STATE_CNT,

R01AN1666EJ0220 Rev. 2.20 Page 11 of 74

Dec 01, 2016

Page 12

RX Family ADC Module Using Firmware Integration Technology

// Commands to enable channels or sensors

ADC_CMD_ENABLE_CHANS, // enables chans and A & B INT if pri != 0

ADC_CMD_ENABLE_TEMP_SENSOR, // enables sensor and INT if priority != 0

ADC_CMD_ENABLE_VOLT_SENSOR, // enables sensor and INT if priority != 0

// Commands to enable hardware triggers or cause software trigger

ADC_CMD_ENABLE_TRIG, // ADCSR.TRGE=1 for sync/async triggers

ADC_CMD_SCAN_NOW, // software trigger start scan

// Commands to poll for scan completion

ADC_CMD_CHECK_SCAN_DONE, // for Normal or GroupA scan

ADC_CMD_CHECK_SCAN_DONE_GROUPA,

ADC_CMD_CHECK_SCAN_DONE_GROUPB,

// Advanced control commands

ADC_CMD_DISABLE_TRIG, // ADCSR.TRGE=0 for sync/async trigs

ADC_CMD_DISABLE_INT, // interrupt disable; ADCSR.ADIE=0

ADC_CMD_ENABLE_INT, // interrupt enable; ADCSR.ADIE=1

ADC_CMD_DISABLE_INT_GROUPB, // interrupt disable; ADCSR.GBADIE=0

ADC_CMD_ENABLE_INT_GROUPB, // interrupt enable; ADCSR.GBADIE=1

} adc_cmd_t;

/* for ADC_CMD_SET_SAMPLE_STATE_CNT */

typedef enum e_adc_sst_reg // sample state registers

{

ADC_SST_CH0 = 0,

ADC_SST_CH1,

ADC_SST_CH2,

ADC_SST_CH3,

ADC_SST_CH4,

ADC_SST_CH6,

ADC_SST_CH8_TO_15,

ADC_SST_TEMPERATURE,

ADC_SST_VOLTAGE,

ADC_SST_REG_MAXX = ADC_SST_VOLTAGE

} adc_sst_reg_t;

#define ADC_SST_CNT_MIN (6) // RX111

#define ADC_SST_CNT_MAX (255)

#define ADC_SST_CNT_DEFAULT (20)

typedef struct st_adc_time

{

adc_sst_reg_t reg_id;

uint8_t num_states; // 6-255; default=20; ch8-15 use same value

} adc_time_t;

/* for ADC_CMD_ENABLE_CHANS */

// Bitwise OR these masks together for desired channels

#define ADC_MASK_CH0 (1<<0)

#define ADC_MASK_CH1 (1<<1)

#define ADC_MASK_CH2 (1<<2)

#define ADC_MASK_CH3 (1<<3)

#define ADC_MASK_CH4 (1<<4)

#define ADC_MASK_CH6 (1<<6)

#define ADC_MASK_CH8 (1<<8)

#define ADC_MASK_CH9 (1<<9)

#define ADC_MASK_CH10 (1<<10)

#define ADC_MASK_CH11 (1<<11)

#define ADC_MASK_CH12 (1<<12)

R01AN1666EJ0220 Rev. 2.20 Page 12 of 74

Dec 01, 2016

Page 13

RX Family ADC Module Using Firmware Integration Technology

#define ADC_MASK_CH13 (1<<13)

#define ADC_MASK_CH14 (1<<14)

#define ADC_MASK_CH15 (1<<15)

#define ADC_MASK_GROUPB_OFF (0)

#define ADC_MASK_ADD_OFF (0)

typedef struct st_adc_ch_cfg // bit 0 is ch0; bit 15 is ch15

{

uint32_t chan_mask; // channels/bits 0-15

uint32_t chan_mask_groupb; // valid for group modes

uint32_t add_mask; // valid if add enabled in Open()

} adc_ch_cfg_t;

/* ADC_READ() ARGUMENT DEFINITIONS */

typedef enum e_adc_reg

{

ADC_REG_CH0 = 0,

ADC_REG_CH1 = 1,

ADC_REG_CH2 = 2,

ADC_REG_CH3 = 3,

ADC_REG_CH4 = 4,

ADC_REG_CH6 = 6,

ADC_REG_CH8 = 8,

ADC_REG_CH9 = 9,

ADC_REG_CH10 = 10,

ADC_REG_CH11 = 11,

ADC_REG_CH12 = 12,

ADC_REG_CH13 = 13,

ADC_REG_CH14 = 14,

ADC_REG_CH15 = 15,

ADC_REG_TEMP = 16,

ADC_REG_VOLT = 17,

ADC_REG_DBLTRIG = 18,

ADC_REG_MAX

} adc_reg_t;

#define ADC_REG_ARRAY_MAX (16)

/* ADC_READALL() ARGUMENT DEFINITIONS */

typedef struct st_adc_data

{

uint16_t chan[ADC_REG_ARRAY_MAX]; // chns/indexes used depends upon MCU

uint16_t temp;

uint16_t volt;

uint16_t dbltrig;

} adc_data_t;

2.10.4 RX113 Interface Types (r_s12ad_rx113_if.h)

/* ADC_OPEN() ARGUMENT DEFINITIONS */

typedef enum e_adc_mode

{

ADC_MODE_SS_TEMPERATURE, // single scan temperature sensor

ADC_MODE_SS_INT_REF_VOLT, // single scan internal ref voltage sensor

ADC_MODE_SS_ONE_CH, // single scan one channel

ADC_MODE_SS_MULTI_CH, // 1 trigger source, scan multiple channels

ADC_MODE_CONT_ONE_CH, // continuous scan one channel

ADC_MODE_CONT_MULTI_CH, // continuous scan multiple channels

ADC_MODE_SS_ONE_CH_DBLTRIG, // on even trig save to ADDBLDR & interrupt

ADC_MODE_SS_MULTI_CH_GROUPED, // 2 trigger sources, scan multiple channels

R01AN1666EJ0220 Rev. 2.20 Page 13 of 74

Dec 01, 2016

Page 14

RX Family ADC Module Using Firmware Integration Technology

ADC_MODE_SS_MULTI_CH_GROUPED_DBLTRIG_A,

ADC_MODE_MAX // This definition DO NOT USE for R_ADC_Open() argument

} adc_mode_t;

typedef enum e_adc_trig // trigger sources (set to TRSA bit or TRSB bit)

{

ADC_TRIG_ASYNC_ADTRG = 0, // ext asynchronous trigger; not for

// Group modes nor double trigger modes

ADC_TRIG_SYNC_TRG0AN = 1, // MTU0 TRGA

ADC_TRIG_SYNC_TRG0BN = 2, // MTU0 TRGB

ADC_TRIG_SYNC_TRGAN_OR_UDF4N = 3, // MTUx TRGA or MTU4 underflow

//(complementary PWM mode)

ADC_TRIG_SYNC_TRG0EN = 4, // MTU0 TRGE

ADC_TRIG_SYNC_TRG0FN = 5, // MTU0 TRGF

ADC_TRIG_SYNC_TRG4AN = 6, // MTU4 TADCORA

ADC_TRIG_SYNC_TRG4BN = 7, // MTU4 TADCORB

ADC_TRIG_SYNC_TRG4AN_AND_TRG4BN = 8, // MTU4 TADCORA and MTU4 TADCORB

ADC_TRIG_SYNC_ELC = 9, // ELC

ADC_TRIG_SOFTWARE = 16 // software trigger; not for Group modes

// nor double trigger modes

// This is not set to TRSA or TRSB

} adc_trig_t;

typedef enum e_adc_add

{

ADC_ADD_OFF = 0, // addition is turned off for chans/sensors

ADC_ADD_TWO_SAMPLES = 1,

ADC_ADD_THREE_SAMPLES = 2,

ADC_ADD_FOUR_SAMPLES = 3

} adc_add_t;

typedef enum e_adc_align

{

ADC_ALIGN_RIGHT = 0x0000,

ADC_ALIGN_LEFT = 0x8000

} adc_align_t;

typedef enum e_adc_clear

{

ADC_CLEAR_AFTER_READ_OFF = 0x0000,

ADC_CLEAR_AFTER_READ_ON = 0x0020

} adc_clear_t;

typedef enum e_adc_speed

{

ADC_CONVERT_SPEED_NORM = 0x0000,

ADC_CONVERT_SPEED_HIGH = 0x0400

} adc_speed_t;

typedef struct st_adc_cfg

{

adc_add_t add_cnt;

adc_align_t alignment; // ignored if addition used

adc_clear_t clearing;

adc_speed_t conv_speed;

adc_trig_t trigger; // default and Group A trigger source

adc_trig_t trigger_groupb; // valid only for group modes

uint8_t priority; // for S12ADIO int; 1=lo 15=hi 0=off/polled

uint8_t priority_groupb; // GBADI interrupt priority; 0-15

R01AN1666EJ0220 Rev. 2.20 Page 14 of 74

Dec 01, 2016

Page 15

RX Family ADC Module Using Firmware Integration Technology

} adc_cfg_t;

/* ADC_CONTROL() ARGUMENT DEFINITIONS */

typedef enum e_adc_cmd

{

// Commands for special hardware configurations

ADC_CMD_USE_INT_VOLT_AS_HVREF,

ADC_CMD_SET_SAMPLE_STATE_CNT,

// Commands to enable channels or sensors

ADC_CMD_ENABLE_CHANS, // enables chans and A & B INT if pri != 0

ADC_CMD_ENABLE_TEMP_SENSOR, // enables sensor and INT if priority != 0

ADC_CMD_ENABLE_VOLT_SENSOR, // enables sensor and INT if priority != 0

// Commands to enable hardware triggers or cause software trigger

ADC_CMD_ENABLE_TRIG, // ADCSR.TRGE=1 for sync/async triggers

ADC_CMD_SCAN_NOW, // software trigger start scan

// Commands to poll for scan completion

ADC_CMD_CHECK_SCAN_DONE, // for Normal or GroupA scan

ADC_CMD_CHECK_SCAN_DONE_GROUPA,

ADC_CMD_CHECK_SCAN_DONE_GROUPB,

// Advanced control commands

ADC_CMD_DISABLE_TRIG, // ADCSR.TRGE=0 for sync/async trigs

ADC_CMD_DISABLE_INT, // interrupt disable; ADCSR.ADIE=0

ADC_CMD_ENABLE_INT, // interrupt enable; ADCSR.ADIE=1

ADC_CMD_DISABLE_INT_GROUPB, // interrupt disable; ADCSR.GBADIE=0

ADC_CMD_ENABLE_INT_GROUPB, // interrupt enable; ADCSR.GBADIE=1

} adc_cmd_t;

/* for ADC_CMD_SET_SAMPLE_STATE_CNT */

typedef enum e_adc_sst_reg // sample state registers

{

ADC_SST_CH0 = 0,

ADC_SST_CH1,

ADC_SST_CH2,

ADC_SST_CH3,

ADC_SST_CH4,

ADC_SST_CH5,

ADC_SST_CH6,

ADC_SST_CH7,

ADC_SST_CH8_TO_15,

ADC_SST_CH21,

ADC_SST_TEMPERATURE,

ADC_SST_VOLTAGE,

ADC_SST_REG_MAX = ADC_SST_VOLTAGE

} adc_sst_reg_t;

#define ADC_SST_CNT_MIN (6)

#define ADC_SST_CNT_MAX (255)

#define ADC_SST_CNT_DEFAULT (20)

typedef struct st_adc_time

{

adc_sst_reg_t reg_id;

uint8_t num_states; // ch8-15 use the same value

} adc_time_t;

R01AN1666EJ0220 Rev. 2.20 Page 15 of 74

Dec 01, 2016

Page 16

RX Family ADC Module Using Firmware Integration Technology

/* for ADC_CMD_ENABLE_CHANS */

// Bitwise OR these masks together for desired channels

#define ADC_MASK_CH0 (1<<0)

#define ADC_MASK_CH1 (1<<1)

#define ADC_MASK_CH2 (1<<2)

#define ADC_MASK_CH3 (1<<3)

#define ADC_MASK_CH4 (1<<4)

#define ADC_MASK_CH5 (1<<5)

#define ADC_MASK_CH6 (1<<6)

#define ADC_MASK_CH7 (1<<7)

#define ADC_MASK_CH8 (1<<8)

#define ADC_MASK_CH9 (1<<9)

#define ADC_MASK_CH10 (1<<10)

#define ADC_MASK_CH11 (1<<11)

#define ADC_MASK_CH12 (1<<12)

#define ADC_MASK_CH13 (1<<13)

#define ADC_MASK_CH14 (1<<14)

#define ADC_MASK_CH15 (1<<15)

#define ADC_MASK_CH21 (1<<21)

#define ADC_MASK_GROUPB_OFF (0)

#define ADC_MASK_ADD_OFF (0)

typedef struct st_adc_ch_cfg // bit 0 is ch0; bit 15 is ch15

{

uint32_t chan_mask; // channels/bits 0-15, 21

uint32_t chan_mask_groupb; // valid for group modes

uint32_t add_mask; // valid if add enabled in Open()

} adc_ch_cfg_t;

/* ADC_READ() ARGUMENT DEFINITIONS */

typedef enum e_adc_reg

{

ADC_REG_CH0 = 0,

ADC_REG_CH1,

ADC_REG_CH2,

ADC_REG_CH3,

ADC_REG_CH4,

ADC_REG_CH5,

ADC_REG_CH6,

ADC_REG_CH7,

ADC_REG_CH8,

ADC_REG_CH9,

ADC_REG_CH10,

ADC_REG_CH11,

ADC_REG_CH12,

ADC_REG_CH13,

ADC_REG_CH14,

ADC_REG_CH15,

ADC_REG_CH21,

ADC_REG_TEMP,

ADC_REG_VOLT,

ADC_REG_DBLTRIG,

ADC_REG_MAX = ADC_REG_DBLTRIG

} adc_reg_t;

#define ADC_REG_ARRAY_MAX (17)

/* ADC_READALL() ARGUMENT DEFINITIONS */

R01AN1666EJ0220 Rev. 2.20 Page 16 of 74

Dec 01, 2016

Page 17

RX Family ADC Module Using Firmware Integration Technology

typedef struct st_adc_data

{

uint16_t chan[ADC_REG_ARRAY_MAX]; // chnls/indexes used depends upon MCU

uint16_t temp;

uint16_t volt;

uint16_t dbltrig; // Not used on RX63x

} adc_data_t;

2.10.5 RX130 Interface Types (r_s12ad_rx130_if.h)

/***** ADC_OPEN() ARGUMENT DEFINITIONS *****/

typedef enum e_adc_mode

{

ADC_MODE_SS_TEMPERATURE, // single scan temperature sensor

ADC_MODE_SS_INT_REF_VOLT, // single scan internal ref voltage sensor

ADC_MODE_SS_ONE_CH, // single scan one channel

ADC_MODE_SS_MULTI_CH, // 1 trigger source, scan multiple channels

ADC_MODE_CONT_ONE_CH, // continuous scan one channel

ADC_MODE_CONT_MULTI_CH, // continuous scan multiple channels

ADC_MODE_SS_ONE_CH_DBLTRIG, // on even triggers save to ADDBLDR &

interrupt

ADC_MODE_SS_MULTI_CH_GROUPED, // 2 trigger sources, scan multiple channels

ADC_MODE_SS_MULTI_CH_GROUPED_DBLTRIG_A,

ADC_MODE_MAX

} adc_mode_t;

typedef enum e_adc_align

{

ADC_ALIGN_RIGHT = 0x0000,

ADC_ALIGN_LEFT = 0x8000

} adc_align_t;

typedef enum e_adc_add // Addition and averaging of sampled data.

{

ADC_ADD_OFF = 0, // addition is turned off for chans/sensors

ADC_ADD_TWO_SAMPLES = 1, // Two samples are added,Register

ADADC.ADC[1,0]

ADC_ADD_THREE_SAMPLES = 2, // Three samples are added

ADC_ADD_FOUR_SAMPLES = 3, // Four samples are added

ADC_ADD_SIXTEEN_SAMPLES = 5, // Sixteen samples are added

ADC_ADD_AVG_2_SAMPLES = 0x81, // average 2 samples

ADC_ADD_AVG_4_SAMPLES = 0x83, // average 4 samples

} adc_add_t;

typedef enum e_adc_clear

{

ADC_CLEAR_AFTER_READ_OFF = 0x0000,

ADC_CLEAR_AFTER_READ_ON = 0x0020

} adc_clear_t;

typedef enum e_adc_trig // trigger sources (set to TRSA bit or TRSB bit)

{

ADC_TRIG_ASYNC_ADTRG = 0, // external asynchronous trigger; not for Group

// modes nor double trigger modes

ADC_TRIG_SYNC_TRG0AN = 1, // MTU0 TRGA

ADC_TRIG_SYNC_TRG0BN = 2, // MTU0 TRGB

ADC_TRIG_SYNC_TRGAN_OR_UDF4N = 3, // MTUx TRGA or MTU4 underflow

//(complementary PWM mode)

R01AN1666EJ0220 Rev. 2.20 Page 17 of 74

Dec 01, 2016

Page 18

RX Family ADC Module Using Firmware Integration Technology

ADC_TRIG_SYNC_TRG0EN = 4, // MTU0 TRGE

ADC_TRIG_SYNC_TRG0FN = 5, // MTU0 TRGF

ADC_TRIG_SYNC_TRG4AN = 6, // MTU4 TADCORA

ADC_TRIG_SYNC_TRG4BN = 7, // MTU4 TADCORB

ADC_TRIG_SYNC_TRG4AN_AND_TRG4BN = 8, // MTU4 TADCORA and MTU4 TADCORB

ADC_TRIG_SYNC_ELC = 9, // ELC

ADC_TRIG_SOFTWARE = 10, // software trigger; not for Group modes

// nor double trigger modes

// This is not set to TRSA or TRSB

ADC_TRIG_NONE = 0x3F

} adc_trig_t;

typedef enum e_adc_speed

{

ADC_CONVERT_SPEED_DEFAULT = 0,

ADC_CONVERT_SPEED_HIGH = 0,

ADC_CONVERT_CURRENT_LOW = 1

} adc_speed_t;

typedef struct st_adc_cfg

{

adc_speed_t conv_speed; // ADCSR.ADHSC, rx130 has two conversion

speeds

adc_align_t alignment; // ADCER.ADRFMT, Left or Right

alignment,ignored if addition used

adc_add_t add_cnt; // ADADC.ADC, Addition/average count

select.

adc_clear_t clearing; // ADCER.ACE, Automatic clearing

enable/disable after read

adc_trig_t trigger; // ADSTRGR.TRSA, default and Group A

trigger source

adc_trig_t trigger_groupb; // valid only for group modes

uint8_t priority; // for S12ADIO int; 1=lo 15=hi 0=off/polled

uint8_t priority_groupb; // S12GBADI interrupt priority; 0-15

} adc_cfg_t;

/***** ADC_CONTROL() ARGUMENT DEFINITIONS *****/

typedef enum e_adc_cmd

{

// Commands for special hardware configurations

ADC_CMD_USE_VREFL0, // Low reference. Default is to use AVSS0.

ADC_CMD_USE_VREFH0, // High reference. Default is to use AVCC0.

ADC_CMD_SET_DDA_STATE_CNT, // For Disconnect Detection Assist

ADC_CMD_SET_SAMPLE_STATE_CNT, // Set the conversion time

// Command to configure channels, sensors, and comparator

ADC_CMD_ENABLE_CHANS, // Configure channels to scan

ADC_CMD_ENABLE_TEMP_SENSOR, // "configure" temperature sensor

ADC_CMD_ENABLE_VOLT_SENSOR, // "configure" internal ref voltage sensor

ADC_CMD_EN_COMPARATOR_LEVEL, // Enable comparator for threshold compare

ADC_CMD_EN_COMPARATOR_WINDOW, // Enable comparator for range compare

// Commands to enable hardware triggers or cause software trigger

ADC_CMD_ENABLE_TRIG, // ADCSR.TRGE=1 for sync/asynchronous

triggers

ADC_CMD_SCAN_NOW, // Software trigger start scan

// Commands to poll for scan completion and comparator results

R01AN1666EJ0220 Rev. 2.20 Page 18 of 74

Dec 01, 2016

Page 19

RX Family ADC Module Using Firmware Integration Technology

ADC_CMD_CHECK_SCAN_DONE, // For Normal or GroupA scan

ADC_CMD_CHECK_SCAN_DONE_GROUPA,

ADC_CMD_CHECK_SCAN_DONE_GROUPB,

ADC_CMD_CHECK_CONDITION_MET, // comparator condition

// Advanced control commands

ADC_CMD_DISABLE_TRIG, // ADCSR.TRGE=0 for sync/async trigs

ADC_CMD_DISABLE_INT, // interrupt disable; ADCSR.ADIE=0

ADC_CMD_ENABLE_INT, // interrupt enable; ADCSR.ADIE=1

ADC_CMD_DISABLE_INT_GROUPB, // interrupt disable; ADCSR.GBADIE=0

ADC_CMD_ENABLE_INT_GROUPB, // interrupt enable; ADCSR.GBADIE=1

} adc_cmd_t;

/* for ADC_CMD_SET_DDA_STATE_CNT */

typedef enum e_adc_charge // Disconnection Detection Assist (DDA)

{

ADC_DDA_DISCHARGE = 0x00,

ADC_DDA_PRECHARGE = 0x01,

ADC_DDA_OFF = 0x02,

} adc_charge_t;

#define ADC_DDA_STATE_CNT_MIN (2) //ADDISCR.ADNDIS[0..3] bits.

#define ADC_DDA_STATE_CNT_MAX (15)

typedef struct st_adc_dda

{

adc_charge_t method; // Discharge or Precharge

uint8_t num_states; // 2-15 (0 = DISABLED, 1 is invalid)

} adc_dda_t;

/* for ADC_CMD_SET_SAMPLE_STATE_CNT */

typedef enum e_adc_sst_reg // sample state registers

{

ADC_SST_CH0 = 0,

ADC_SST_CH1,

ADC_SST_CH2,

ADC_SST_CH3,

ADC_SST_CH4,

ADC_SST_CH5,

ADC_SST_CH6,

ADC_SST_CH7,

ADC_SST_CH16_TO_21_CH24_TO_CH26,

ADC_SST_TEMPERATURE,

ADC_SST_VOLTAGE,

ADC_SST_REG_MAX = ADC_SST_VOLTAGE

} adc_sst_reg_t;

#define ADC_SST_CNT_MIN (5) //For PCLKB:ADCLK = 1:1, 1:2, 1:4, 1:8

#define ADC_SST_CNT_MAX (255)

#define ADC_SST_CNT_DEFAULT (13)

typedef struct st_adc_sst

{

adc_sst_reg_t reg_id;

uint8_t num_states; // ch16-21, 24-26 use the same value

} adc_sst_t;

R01AN1666EJ0220 Rev. 2.20 Page 19 of 74

Dec 01, 2016

Page 20

RX Family ADC Module Using Firmware Integration Technology

/* for ADC_CMD_CONFIGURE_SCAN */

// Bitwise OR these masks together for desired channels and sensors

// Used for all commands containing a "mask" or "flags" field

#define ADC_MASK_CH0 (1<<0)

#define ADC_MASK_CH1 (1<<1)

#define ADC_MASK_CH2 (1<<2)

#define ADC_MASK_CH3 (1<<3)

#define ADC_MASK_CH4 (1<<4)

#define ADC_MASK_CH5 (1<<5)

#define ADC_MASK_CH6 (1<<6)

#define ADC_MASK_CH7 (1<<7)

#define ADC_MASK_CH16 (1<<16)

#define ADC_MASK_CH17 (1<<17)

#define ADC_MASK_CH18 (1<<18)

#define ADC_MASK_CH19 (1<<19)

#define ADC_MASK_CH20 (1<<20)

#define ADC_MASK_CH21 (1<<21)

#define ADC_MASK_CH24 (1<<24)

#define ADC_MASK_CH25 (1<<25)

#define ADC_MASK_CH26 (1<<26)

#define ADC_MASK_TEMP (1<<8) // temperature sensor

#define ADC_MASK_VOLT (1<<9) // internal reference voltage sensor

#define ADC_MASK_SENSORS (ADC_MASK_TEMP | ADC_MASK_VOLT)

#define ADC_MASK_GROUPB_OFF (0)

#define ADC_MASK_ADD_OFF (0)

#define ADC_MASK_SAMPLE_HOLD_OFF (0)

typedef enum e_adc_grpa // action when groupa interrupts groupb

scan

{

ADC_GRPA_PRIORITY_OFF = 0, // groupa ignored and does not interrupt

groupb

ADC_GRPA_GRPB_WAIT_TRIG = 1, // groupb restarts at next trigger

ADC_GRPA_GRPB_RESTART_SCAN = 3, // groupb restarts immediately

ADC_GRPA_GRPB_CONT_SCAN= 0x8001, // groupb restarts immediately and scans

continuously

} adc_grpa_t;

typedef enum e_adc_diag // Self-Diagnosis Channel

{

ADC_DIAG_OFF = 0x00,

ADC_DIAG_0_VOLT = 0x01,

ADC_DIAG_HALF_VREFH0 = 0x02,

ADC_DIAG_VREFH0 = 0x03,

ADC_DIAG_ROTATE_VOLTS = 0x04,

} adc_diag_t;

typedef enum e_adc_elc

{

ADC_ELC_SCAN_DONE = 0, // normal scan or Group A scan complete

ADC_ELC_GROUPB_SCAN_DONE,

ADC_ELC_ALL_SCANS_DONE,

} adc_elc_t;

typedef struct st_adc_ch_cfg

{

uint32_t chan_mask; // channels/bits 0-7, 16-21, 24-26

uint32_t chan_mask_groupb; // valid for group modes

adc_grpa_t priority_groupa; // valid for group modes

R01AN1666EJ0220 Rev. 2.20 Page 20 of 74

Dec 01, 2016

Page 21

RX Family ADC Module Using Firmware Integration Technology

uint32_t add_mask; // valid if add enabled in Open()

adc_diag_t diag_method; // self-diagnosis virtual channel

adc_elc_t signal_elc; //

} adc_ch_cfg_t;

/* for ADC_CMD_EN_COMPARATOR_LEVEL and ADC_CMD_EN_COMPARATOR_WINDOW */

typedef struct st_adc_cmpwin_cfg // bit-OR ADC_MASK_xxx to

{ // indicate channels/sensors

uint32_t compare_mask; // channels/sensors to compare

uint32_t inside_window_mask; // condition met when within range

// default=0 met when outside range

uint16_t level_lo; // Low-value of window

uint16_t level_hi; // High-value of window

bool windowa_enable; // comparison window A enable

} adc_cmpwin_t;

/* for ADC_CMD_CHECK_CONDITION_MET use uint32_t */

/***** ADC_READ() ARGUMENT DEFINITIONS *****/

typedef enum e_adc_reg

{

ADC_REG_CH0 = 0, // Channel 0

ADC_REG_CH1,

ADC_REG_CH2,

ADC_REG_CH3,

ADC_REG_CH4,

ADC_REG_CH5,

ADC_REG_CH6,

ADC_REG_CH7, // Channel 7

ADC_REG_CH16, // Channel 16

ADC_REG_CH17,

ADC_REG_CH18,

ADC_REG_CH19,

ADC_REG_CH20,

ADC_REG_CH21,

ADC_REG_CH24,

ADC_REG_CH25,

ADC_REG_CH26,

ADC_REG_TEMP, // A/D Temperature sensor output

ADC_REG_VOLT, // A/D Internal Voltage Reference

ADC_REG_DBLTRIG, // Data Duplication register

ADC_REG_DBLTRIGA, // loaded when first multi-source trigger was A

ADC_REG_DBLTRIGB, // loaded when first multi-source trigger was B

ADC_REG_SELF_DIAG, // self-diagnosis register

ADC_REG_MAX = ADC_REG_SELF_DIAG

} adc_reg_t;

/* ADC_READALL() ARGUMENT DEFINITIONS */

typedef struct st_adc_data

{

uint16_t chan[17];

uint16_t temp;

uint16_t volt;

uint16_t dbltrig;

uint16_t self_diag;

} adc_data_t;

R01AN1666EJ0220 Rev. 2.20 Page 21 of 74

Dec 01, 2016

Page 22

RX Family ADC Module Using Firmware Integration Technology

2.10.6 RX210 Interface Types (r_s12ad_rx210_if.h)

/* ADC_OPEN() ARGUMENT DEFINITIONS */

typedef enum e_adc_mode

{

ADC_MODE_SS_TEMPERATURE, // single scan temperature sensor

ADC_MODE_SS_INT_REF_VOLT, // single scan internal ref voltage sensor

ADC_MODE_SS_ONE_CH, // single scan one channel

ADC_MODE_SS_MULTI_CH, // 1 trigger source, scan multiple channels

ADC_MODE_CONT_ONE_CH, // continuous scan one channel

ADC_MODE_CONT_MULTI_CH, // continuous scan multiple channels

ADC_MODE_SS_ONE_CH_DBLTRIG, // on even trig save to ADDBLDR & interrupt

ADC_MODE_SS_MULTI_CH_GROUPED, // 2 trigger sources, scan multiple channels

ADC_MODE_SS_MULTI_CH_GROUPED_DBLTRIG_A,

ADC_MODE_MAX // This definition DO NOT USE for R_ADC_Open() argument

} adc_mode_t;

typedef enum e_adc_trig // trigger sources (set to TRSA bit or TRSB bit)

{

ADC_TRIG_ASYNC_ADTRG = 0, // ext asynchronous trigger; not for Group

// modes nor double trigger modes

ADC_TRIG_SYNC_TRG0AN = 1, // MTU0 TRGA

ADC_TRIG_SYNC_TRG0BN = 2, // MTU0 TRGB

ADC_TRIG_SYNC_TRGAN_OR_UDF4N = 3, // MTUx TRGA or MTU4 underflow

//(complementary PWM mode)

ADC_TRIG_SYNC_TRG0EN = 4, // MTU0 TRGE

ADC_TRIG_SYNC_TRG0FN = 5, // MTU0 TRGF

ADC_TRIG_SYNC_TRG4AN = 6, // MTU4 TADCORA

ADC_TRIG_SYNC_TRG4BN = 7, // MTU4 TADCORB

ADC_TRIG_SYNC_TRG4AN_AND_TRG4BN = 8, // MTU4 TADCORA and MTU4 TADCORB

ADC_TRIG_SYNC_ELC = 9, // ELC

ADC_TRIG_SYNC_TEMPS = 10, // for temperature sensor, use

// ADC_TRIG_SOFTWARE

ADC_TRIG_SYNC_TPUTRGAN = 11, // TPUx TRGA

ADC_TRIG_SYNC_TPUTRG0AN = 12, // TPU0 TRGA

ADC_TRIG_SOFTWARE = 16 // software trigger; not for Group modes

// nor double trigger modes

// This is not set to TRSA or TRSB

} adc_trig_t;

typedef enum e_adc_add

{

ADC_ADD_OFF = 0, // addition is turned off for chans/sensors

// add not allowed for temperature sensor

ADC_ADD_TWO_SAMPLES = 1,

ADC_ADD_THREE_SAMPLES = 2,

ADC_ADD_FOUR_SAMPLES = 3

} adc_add_t;

typedef enum e_adc_align

{

ADC_ALIGN_RIGHT = 0x0000,

ADC_ALIGN_LEFT = 0x8000

} adc_align_t;

typedef enum e_adc_clear

{

ADC_CLEAR_AFTER_READ_OFF = 0x0000,

ADC_CLEAR_AFTER_READ_ON = 0x0020

} adc_clear_t;

R01AN1666EJ0220 Rev. 2.20 Page 22 of 74

Dec 01, 2016

Page 23

RX Family ADC Module Using Firmware Integration Technology

typedef struct st_adc_cfg

{

adc_add_t add_cnt;

adc_align_t alignment; // ignored if addition used

adc_clear_t clearing;

adc_trig_t trigger; // default and Group A trigger source

adc_trig_t trigger_groupb; // valid only for group modes

uint8_t priority; // for S12ADIO int; 1=lo 15=hi 0=off/polled

uint8_t priority_groupb; // GBADI interrupt priority; 0-15

} adc_cfg_t;

/* ADC_CONTROL() ARGUMENT DEFINITIONS */

typedef enum e_adc_cmd

{

// Commands for special hardware configurations

ADC_CMD_SET_DDA_STATE_CNT, // for Disconnect Detection Assist

ADC_CMD_SET_SAMPLE_STATE_CNT,

// Commands to enable channels or sensors

ADC_CMD_ENABLE_CHANS, // enables chans and A & B INT if pri != 0

ADC_CMD_ENABLE_TEMP_SENSOR, // enables sensor and INT if priority != 0

ADC_CMD_ENABLE_VOLT_SENSOR, // enables sensor and INT if priority != 0

// Commands to enable hardware triggers or cause software trigger

ADC_CMD_ENABLE_TRIG, // ADCSR.TRGE=1 for sync/async triggers

ADC_CMD_SCAN_NOW, // software trigger start scan

// Commands to poll for scan completion

ADC_CMD_CHECK_SCAN_DONE, // for Normal or GroupA scan

ADC_CMD_CHECK_SCAN_DONE_GROUPA,

ADC_CMD_CHECK_SCAN_DONE_GROUPB,

// Advanced control commands

ADC_CMD_DISABLE_TRIG, // ADCSR.TRGE=0 for sync/async trigs

ADC_CMD_DISABLE_INT, // interrupt disable; ADCSR.ADIE=0

ADC_CMD_ENABLE_INT, // interrupt enable; ADCSR.ADIE=1

ADC_CMD_DISABLE_INT_GROUPB, // interrupt disable; ADCSR.GBADIE=0

ADC_CMD_ENABLE_INT_GROUPB, // interrupt enable; ADCSR.GBADIE=1

} adc_cmd_t;

/* for ADC_CMD_SET_DDA_STATE_CNT */

typedef enum e_adc_charge // Disconnection Detection Assist (DDA)

{

ADC_DDA_DISCHARGE = 0x00,

ADC_DDA_PRECHARGE = 0x01,

ADC_DDA_OFF = 0x02,

} adc_charge_t;

#define ADC_DDA_STATE_CNT_MIN (1)

#define ADC_DDA_STATE_CNT_MAX (15)

typedef struct st_adc_dda

{

adc_charge_t method;

uint8_t num_states; // 1-15

} adc_dda_t;

/* for ADC_CMD_SET_SAMPLE_STATE_CNT */

R01AN1666EJ0220 Rev. 2.20 Page 23 of 74

Dec 01, 2016

Page 24

RX Family ADC Module Using Firmware Integration Technology

typedef enum e_adc_sst_reg // sample state registers

{

ADC_SST_CH0 = 0,

ADC_SST_CH1,

ADC_SST_CH2,

ADC_SST_CH3,

ADC_SST_CH4,

ADC_SST_CH5,

ADC_SST_CH6,

ADC_SST_CH7,

ADC_SST_CH8_TO_15,

ADC_SST_TEMPERATURE,

ADC_SST_VOLTAGE,

ADC_SST_REG_MAX = ADC_SST_VOLTAGE

} adc_sst_reg_t;

#define ADC_SST_CNT_MIN (12)

#define ADC_SST_CNT_MAX (255)

#define ADC_SST_CNT_DEFAULT (20)

typedef struct st_adc_time

{

adc_sst_reg_t reg_id;

uint8_t num_states; // ch8-15 use the same value

} adc_time_t;

/* for ADC_CMD_ENABLE_CHANS */

// Bitwise OR these masks together for desired channels

#define ADC_MASK_CH0 (1<<0)

#define ADC_MASK_CH1 (1<<1)

#define ADC_MASK_CH2 (1<<2)

#define ADC_MASK_CH3 (1<<3)

#define ADC_MASK_CH4 (1<<4)

#define ADC_MASK_CH5 (1<<5)

#define ADC_MASK_CH6 (1<<6)

#define ADC_MASK_CH7 (1<<7)

#define ADC_MASK_CH8 (1<<8)

#define ADC_MASK_CH9 (1<<9)

#define ADC_MASK_CH10 (1<<10)

#define ADC_MASK_CH11 (1<<11)

#define ADC_MASK_CH12 (1<<12)

#define ADC_MASK_CH13 (1<<13)

#define ADC_MASK_CH14 (1<<14)

#define ADC_MASK_CH15 (1<<15)

#define ADC_MASK_GROUPB_OFF (0)

#define ADC_MASK_ADD_OFF (0)

#define ADC_MASK_SAMPLE_HOLD_OFF (0)

typedef enum e_adc_diag // Self-Diagnosis Channel

{

ADC_DIAG_OFF = 0x00,

ADC_DIAG_0_VOLT = 0x01,

ADC_DIAG_HALF_VREFH0 = 0x2,

ADC_DIAG_VREFH0 = 0x3,

ADC_DIAG_ROTATE_VOLTS = 0x4

} adc_diag_t;

#define ADC_SST_SH_CNT_MIN (4) // minimum sample&hold states

#define ADC_SST_SH_CNT_MAX (255) // maximum sample&hold states

#define ADC_SST_SH_CNT_DEFAULT (20) // default sample&hold states

R01AN1666EJ0220 Rev. 2.20 Page 24 of 74

Dec 01, 2016

Page 25

RX Family ADC Module Using Firmware Integration Technology

typedef struct st_adc_ch_cfg // bit 0 is ch0; bit 15 is ch15

{

uint32_t chan_mask; // channels/bits 0-15

uint32_t chan_mask_groupb; // valid for group modes

uint32_t add_mask; // valid if add enabled in Open()

adc_diag_t diag_method; // self-diagnosis virtual channel

uint8_t sample_hold_mask; // channels/bits 0-2

uint8_t sample_hold_states; // minimum .4us

} adc_ch_cfg_t;

/* ADC_READ() ARGUMENT DEFINITIONS */

typedef enum e_adc_reg

{

ADC_REG_CH0 = 0,

ADC_REG_CH1,

ADC_REG_CH2,

ADC_REG_CH3,

ADC_REG_CH4,

ADC_REG_CH5,

ADC_REG_CH6,

ADC_REG_CH7,

ADC_REG_CH8,

ADC_REG_CH9,

ADC_REG_CH10,

ADC_REG_CH11,

ADC_REG_CH12,

ADC_REG_CH13,

ADC_REG_CH14,

ADC_REG_CH15,

ADC_REG_TEMP,

ADC_REG_VOLT,

ADC_REG_DBLTRIG,

ADC_REG_SELF_DIAG,

ADC_REG_MAX = ADC_REG_SELF_DIAG

} adc_reg_t;

#define ADC_REG_ARRAY_MAX (16)

/* ADC_READALL() ARGUMENT DEFINITIONS */

typedef struct st_adc_data

{

uint16_t chan[ADC_REG_ARRAY_MAX];

uint16_t temp;

uint16_t volt;

uint16_t dbltrig;

uint16_t self_diag;

} adc_data_t;

2.10.7 RX230 Interface Types (r_s12ad_rx230_if.h)

/***** ADC_OPEN() ARGUMENT DEFINITIONS *****/

typedef enum e_adc_mode

{

ADC_MODE_SS_TEMPERATURE, // single scan temperature sensor

ADC_MODE_SS_INT_REF_VOLT, // single scan internal ref voltage sensor

ADC_MODE_SS_ONE_CH, // single scan one channel

ADC_MODE_SS_MULTI_CH, // 1 trigger source, scan multiple channels

ADC_MODE_CONT_ONE_CH, // continuous scan one channel

ADC_MODE_CONT_MULTI_CH, // continuous scan multiple channels

R01AN1666EJ0220 Rev. 2.20 Page 25 of 74

Dec 01, 2016

Page 26

RX Family ADC Module Using Firmware Integration Technology

ADC_MODE_SS_ONE_CH_DBLTRIG, // on even triggers save to ADDBLDR &

// interrupt

ADC_MODE_SS_MULTI_CH_GROUPED, // 2 trigger sources, scan multiple channels

ADC_MODE_SS_MULTI_CH_GROUPED_DBLTRIG_A,

ADC_MODE_MAX // This definition DO NOT USE for R_ADC_Open() argument

} adc_mode_t;

typedef enum e_adc_align

{

ADC_ALIGN_RIGHT = 0x0000,

ADC_ALIGN_LEFT = 0x8000

} adc_align_t;

typedef enum e_adc_add // Addition and averaging of sampled data.

{

ADC_ADD_OFF = 0, // addition is turned off for chans/sensors

ADC_ADD_TWO_SAMPLES = 1, // Two samples are added,

// Register ADADC.ADC[1,0]

ADC_ADD_THREE_SAMPLES = 2, // Three samples are added

ADC_ADD_FOUR_SAMPLES = 3, // Four samples are added

ADC_ADD_SIXTEEN_SAMPLES = 5, // Sixteen samples are added

ADC_ADD_AVG_2_SAMPLES = 0x81, // average 2 samples

ADC_ADD_AVG_4_SAMPLES = 0x83, // average 4 samples

} adc_add_t;

typedef enum e_adc_clear

{

ADC_CLEAR_AFTER_READ_OFF = 0x0000,

ADC_CLEAR_AFTER_READ_ON = 0x0020

} adc_clear_t;

typedef enum e_adc_trig // trigger sources (set to TRSA bit or TRSB bit)

{

ADC_TRIG_ASYNC_ADTRG = 0, // external asynchronous trigger; not for Group

// modes nor double trigger modes

ADC_TRIG_SYNC_TRG0AN = 1, // MTU0 TRGA

ADC_TRIG_SYNC_TRG0BN = 2, // MTU0 TRGB

ADC_TRIG_SYNC_TRGAN_OR_UDF4N = 3, // MTUx TRGA or MTU4 underflow

//(complementary PWM mode)

ADC_TRIG_SYNC_TRG0EN = 4, // MTU0 TRGE

ADC_TRIG_SYNC_TRG0FN = 5, // MTU0 TRGF

ADC_TRIG_SYNC_TRG4AN = 6, // MTU4 TADCORA

ADC_TRIG_SYNC_TRG4BN = 7, // MTU4 TADCORB

ADC_TRIG_SYNC_TRG4AN_AND_TRG4BN = 8, // MTU4 TADCORA and MTU4 TADCORB

ADC_TRIG_SYNC_ELC = 9, // ELC

ADC_TRIG_SYNC_TPUTRGAN = 13, // TPUx TRGA

ADC_TRIG_SYNC_TPUTRG0AN = 14, // TPU0 TRGA

ADC_TRIG_SOFTWARE = 15, // software trigger; not for Group modes

// nor double trigger modes

// This is not set to TRSA or TRSB

ADC_TRIG_NONE = 0x3F

} adc_trig_t;

typedef enum e_adc_speed

{

ADC_CONVERT_SPEED_DEFAULT = 0,

ADC_CONVERT_SPEED_HIGH = 0,

ADC_CONVERT_CURRENT_LOW = 1

} adc_speed_t;

R01AN1666EJ0220 Rev. 2.20 Page 26 of 74

Dec 01, 2016

Page 27

RX Family ADC Module Using Firmware Integration Technology

typedef struct st_adc_cfg

{

adc_speed_t conv_speed; // ADCSR.ADHSC, rx230 has two

// conversion speeds

adc_align_t alignment; // ADCER.ADRFMT, Left or Right

// alignment,ignored if addition used

adc_add_t add_cnt; // ADADC.ADC, Addition/average

// count select.

adc_clear_t clearing; // ADCER.ACE, Automatic clearing

// enable/disable after read

adc_trig_t trigger; // ADSTRGR.TRSA, default and Group A

// trigger source

adc_trig_t trigger_groupb; // valid only for group modes

uint8_t priority; // for S12ADIO int; 1=lo 15=hi 0=off/polled

uint8_t priority_groupb; // S12GBADI interrupt priority; 0-15

} adc_cfg_t;

/***** ADC_CONTROL() ARGUMENT DEFINITIONS *****/

typedef enum e_adc_cmd

{

// Commands for special hardware configurations

ADC_CMD_USE_VREFL0, // Low reference. Default is to use AVSS0.

ADC_CMD_USE_VREFH0, // High reference. Default is to use AVCC0.

ADC_CMD_SET_DDA_STATE_CNT, // For Disconnect Detection Assist

ADC_CMD_SET_SAMPLE_STATE_CNT, // Set the conversion time

// Command to configure channels, sensors, and comparator

ADC_CMD_ENABLE_CHANS, // Configure channels to scan

ADC_CMD_ENABLE_TEMP_SENSOR, // "configure" temperature sensor

ADC_CMD_ENABLE_VOLT_SENSOR, // "configure" internal ref voltage sensor

ADC_CMD_EN_COMPARATOR_LEVEL, // Enable comparator for threshold compare

ADC_CMD_EN_COMPARATOR_WINDOW, // Enable comparator for range compare

// Commands to enable hardware triggers or cause software trigger

ADC_CMD_ENABLE_TRIG, // ADCSR.TRGE=1 for sync/asynchronous

// triggers

ADC_CMD_SCAN_NOW, // Software trigger start scan

// Commands to poll for scan completion and comparator results

ADC_CMD_CHECK_SCAN_DONE, // For Normal or GroupA scan

ADC_CMD_CHECK_SCAN_DONE_GROUPA,

ADC_CMD_CHECK_SCAN_DONE_GROUPB,

ADC_CMD_CHECK_CONDITION_MET, // comparator condition

// Advanced control commands

ADC_CMD_DISABLE_TRIG, // ADCSR.TRGE=0 for sync/async trigs

ADC_CMD_DISABLE_INT, // interrupt disable; ADCSR.ADIE=0

ADC_CMD_ENABLE_INT, // interrupt enable; ADCSR.ADIE=1

ADC_CMD_DISABLE_INT_GROUPB, // interrupt disable; ADCSR.GBADIE=0

ADC_CMD_ENABLE_INT_GROUPB, // interrupt enable; ADCSR.GBADIE=1

} adc_cmd_t;

/* for ADC_CMD_SET_DDA_STATE_CNT */

typedef enum e_adc_charge // Disconnection Detection Assist (DDA)

{

ADC_DDA_DISCHARGE = 0x00,

R01AN1666EJ0220 Rev. 2.20 Page 27 of 74

Dec 01, 2016

Page 28

RX Family ADC Module Using Firmware Integration Technology

ADC_DDA_PRECHARGE = 0x01,

ADC_DDA_OFF = 0x02

} adc_charge_t;

#define ADC_DDA_STATE_CNT_MIN (2) //ADDISCR.ADNDIS[0..3] bits.

#define ADC_DDA_STATE_CNT_MAX (15)

typedef struct st_adc_dda

{

adc_charge_t method; // Discharge or Precharge

uint8_t num_states; // 2-15 (0 = DISABLED, 1 is invalid)

} adc_dda_t;

/* for ADC_CMD_SET_SAMPLE_STATE_CNT */

typedef enum e_adc_sst_reg // sample state registers

{

ADC_SST_CH0 = 0,

ADC_SST_CH1,

ADC_SST_CH2,

ADC_SST_CH3,

ADC_SST_CH4,

ADC_SST_CH5,

ADC_SST_CH6,

ADC_SST_CH7,

ADC_SST_CH16_TO_31,

ADC_SST_TEMPERATURE,

ADC_SST_VOLTAGE,

ADC_SST_REG_MAX = ADC_SST_VOLTAGE

} adc_sst_reg_t;

#define ADC_SST_CNT_MIN (5) //For PCLKB:ADCLK = 1:1, 1:2, 1:4, 1:8

//#define ADC_SST_CNT_MIN (6) //For PCLKB:ADCLK = 2:1, 4:1

#define ADC_SST_CNT_MAX (255)

#define ADC_SST_CNT_DEFAULT (13)

typedef struct st_adc_sst

{

adc_sst_reg_t reg_id;

uint8_t num_states; // ch16-31 use the same value

} adc_sst_t;

/* for ADC_CMD_CONFIGURE_SCAN */

// Bitwise OR these masks together for desired channels and sensors

// Used for all commands containing a "mask" or "flags" field

#define ADC_MASK_CH0 (1<<0)

#define ADC_MASK_CH1 (1<<1)

#define ADC_MASK_CH2 (1<<2)

#define ADC_MASK_CH3 (1<<3)

#define ADC_MASK_CH4 (1<<4)

#define ADC_MASK_CH5 (1<<5)

#define ADC_MASK_CH6 (1<<6)

#define ADC_MASK_CH7 (1<<7)

#define ADC_MASK_CH16 (1<<16)

#define ADC_MASK_CH17 (1<<17)

#define ADC_MASK_CH18 (1<<18)

#define ADC_MASK_CH19 (1<<19)

#define ADC_MASK_CH20 (1<<20)

#define ADC_MASK_CH21 (1<<21)

R01AN1666EJ0220 Rev. 2.20 Page 28 of 74

Dec 01, 2016

Page 29

RX Family ADC Module Using Firmware Integration Technology

#define ADC_MASK_CH22 (1<<22)

#define ADC_MASK_CH23 (1<<23)

#define ADC_MASK_CH24 (1<<24)

#define ADC_MASK_CH25 (1<<25)

#define ADC_MASK_CH26 (1<<26)

#define ADC_MASK_CH27 (1<<27)

#define ADC_MASK_CH28 (1<<28)

#define ADC_MASK_CH29 (1<<29)

#define ADC_MASK_CH30 (1<<30)

#define ADC_MASK_CH31 (1<<31)

#define ADC_MASK_TEMP (1<<8) // temperature sensor

#define ADC_MASK_VOLT (1<<9) // internal reference voltage sensor

#define ADC_MASK_SENSORS (ADC_MASK_TEMP | ADC_MASK_VOLT)

#define ADC_MASK_GROUPB_OFF (0)

#define ADC_MASK_ADD_OFF (0)

#define ADC_MASK_SAMPLE_HOLD_OFF (0)

typedef enum e_adc_grpa // action when groupa interrupts groupb

// scan

{

ADC_GRPA_PRIORITY_OFF = 0, // groupa ignored and does not interrupt

// groupb

ADC_GRPA_GRPB_WAIT_TRIG = 1, // groupb restarts at next trigger

ADC_GRPA_GRPB_RESTART_SCAN = 3, // groupb restarts immediately

ADC_GRPA_GRPB_CONT_SCAN= 0x8001, // groupb restarts immediately and scans

// continuously

} adc_grpa_t;

typedef enum e_adc_diag // Self-Diagnosis Channel

{

ADC_DIAG_OFF = 0x00,

ADC_DIAG_0_VOLT = 0x01,

ADC_DIAG_HALF_VREFH0 = 0x02,

ADC_DIAG_VREFH0 = 0x03,

ADC_DIAG_ROTATE_VOLTS = 0x04

} adc_diag_t;

typedef enum e_adc_elc

{

ADC_ELC_SCAN_DONE = 0, // normal scan or Group A scan complete

ADC_ELC_GROUPB_SCAN_DONE,

ADC_ELC_ALL_SCANS_DONE

} adc_elc_t;

typedef struct st_adc_ch_cfg

{

uint32_t chan_mask; // channels/bits 0-7, 16-31

uint32_t chan_mask_groupb; // valid for group modes

adc_grpa_t priority_groupa; // valid for group modes

uint32_t add_mask; // valid if add enabled in Open()

adc_diag_t diag_method; // self-diagnosis virtual channel

adc_elc_t signal_elc; //

} adc_ch_cfg_t;

/* for ADC_CMD_EN_COMPARATOR_LEVEL and ADC_CMD_EN_COMPARATOR_WINDOW */

typedef struct st_adc_cmpwin_cfg // bit-OR ADC_MASK_xxx to

{ // indicate channels/sensors

uint32_t compare_mask; // channels/sensors to compare

R01AN1666EJ0220 Rev. 2.20 Page 29 of 74

Dec 01, 2016

Page 30

RX Family ADC Module Using Firmware Integration Technology

uint32_t inside_window_mask; // condition met when within range

// default=0 met when outside range

uint16_t level_lo; // Low-value of window

uint16_t level_hi; // High-value of window

bool windowa_enable; // comparison window A enable

} adc_cmpwin_t;

/* for ADC_CMD_EN_COMPARATOR_WINDOW */

typedef struct st_adc_cmpwin_cfg // bit-OR ADC_MASK_xxx to

{ // indicate channels/sensors

uint32_t compare_mask; // channels/sensors to compare

uint32_t inside_window_mask; // condition met when within range

// default=0 met when outside range

uint16_t level_lo; // Low-value of window

uint16_t level_hi; // High-value of window

uint8_t int_priority; // S12CMPI priority level

// 1=low 15=hi 0=polled

} adc_cmpwin_t;

/* for ADC_CMD_CHECK_CONDITION_MET use uint32_t */

/***** ADC_READ() ARGUMENT DEFINITIONS *****/

typedef enum e_adc_reg

{

ADC_REG_CH0 = 0, // Channel 0

ADC_REG_CH1,

ADC_REG_CH2,

ADC_REG_CH3,

ADC_REG_CH4,

ADC_REG_CH5,

ADC_REG_CH6,

ADC_REG_CH7, // Channel 7

ADC_REG_CH16, // Channel 16

ADC_REG_CH17,

ADC_REG_CH18,

ADC_REG_CH19,

ADC_REG_CH20,

ADC_REG_CH21,

ADC_REG_CH22,

ADC_REG_CH23,

ADC_REG_CH24,

ADC_REG_CH25,

ADC_REG_CH26,

ADC_REG_CH27,

ADC_REG_CH28,

ADC_REG_CH29,

ADC_REG_CH30,

ADC_REG_CH31, // Channel 31

ADC_REG_TEMP, // A/D Temperature sensor output

ADC_REG_VOLT, // A/D Internal Voltage Reference

ADC_REG_DBLTRIG, // Data Duplication register

ADC_REG_DBLTRIGA, // loaded when first multi-source trigger was A

ADC_REG_DBLTRIGB, // loaded when first multi-source trigger was B

ADC_REG_SELF_DIAG, // self-diagnosis register

ADC_REG_MAX = ADC_REG_SELF_DIAG

} adc_reg_t;

R01AN1666EJ0220 Rev. 2.20 Page 30 of 74

Dec 01, 2016

Page 31

RX Family ADC Module Using Firmware Integration Technology

/* ADC_READALL() ARGUMENT DEFINITIONS */

typedef struct st_adc_data

{

uint16_t chan[24];

uint16_t temp;

uint16_t volt;

uint16_t dbltrig;

uint16_t self_diag;

} adc_data_t;

2.10.8 RX231 Interface Types (r_s12ad_rx231_if.h)

/* ADC_OPEN() ARGUMENT DEFINITIONS */

typedef enum e_adc_mode

{

ADC_MODE_SS_TEMPERATURE, // single scan temperature sensor

ADC_MODE_SS_INT_REF_VOLT, // single scan internal ref voltage sensor

ADC_MODE_SS_ONE_CH, // single scan one channel

ADC_MODE_SS_MULTI_CH, // 1 trigger source, scan multiple channels

ADC_MODE_CONT_ONE_CH, // continuous scan one channel

ADC_MODE_CONT_MULTI_CH, // continuous scan multiple channels

ADC_MODE_SS_ONE_CH_DBLTRIG, // on even triggers save to ADDBLDR & int

ADC_MODE_SS_MULTI_CH_GROUPED, // 2 trigger sources, scan multiple channels

ADC_MODE_SS_MULTI_CH_GROUPED_DBLTRIG_A,

ADC_MODE_MAX // This definition DO NOT USE for R_ADC_Open() argument

} adc_mode_t;

typedef enum e_adc_align

{

ADC_ALIGN_RIGHT = 0x0000,

ADC_ALIGN_LEFT = 0x8000

} adc_align_t;

typedef enum e_adc_add

{

ADC_ADD_OFF = 0, // addition is turned off for chans/sensors

ADC_ADD_TWO_SAMPLES = 1, // Two samples are added,Reg ADADC.ADC[1,0]

ADC_ADD_THREE_SAMPLES = 2, // Three samples are added

ADC_ADD_FOUR_SAMPLES = 3, // Four samples are added

ADC_ADD_SIXTEEN_SAMPLES = 5, // Sixteen samples are added

ADC_ADD_AVG_2_SAMPLES = 0x81, // average 2 samples

ADC_ADD_AVG_4_SAMPLES = 0x83, // average 4 samples

} adc_add_t;

typedef enum e_adc_clear

{

ADC_CLEAR_AFTER_READ_OFF = 0x0000,

ADC_CLEAR_AFTER_READ_ON = 0x0020

} adc_clear_t;

typedef enum e_adc_trig // trigger sources (set to TRSA bit or TRSB bit)

{

ADC_TRIG_ASYNC_ADTRG = 0, // external asynchronous trigger; not for Group

// modes nor double trigger modes

ADC_TRIG_SYNC_TRG0AN = 1, // MTU0 TRGA

ADC_TRIG_SYNC_TRG0BN = 2, // MTU0 TRGB

R01AN1666EJ0220 Rev. 2.20 Page 31 of 74

Dec 01, 2016

Page 32

RX Family ADC Module Using Firmware Integration Technology

ADC_TRIG_SYNC_TRGAN_OR_UDF4N = 3, // MTUx TRGA or MTU4 underflow

//(complementary PWM mode)

ADC_TRIG_SYNC_TRG0EN = 4, // MTU0 TRGE

ADC_TRIG_SYNC_TRG0FN = 5, // MTU0 TRGF

ADC_TRIG_SYNC_TRG4AN = 6, // MTU4 TADCORA

ADC_TRIG_SYNC_TRG4BN = 7, // MTU4 TADCORB

ADC_TRIG_SYNC_TRG4AN_AND_TRG4BN = 8, // MTU4 TADCORA and MTU4 TADCORB

ADC_TRIG_SYNC_ELC = 9, // ELC

ADC_TRIG_SYNC_TPUTRGAN = 13, // TPUx TRGA

ADC_TRIG_SYNC_TPUTRG0AN = 14, // TPU0 TRGA

ADC_TRIG_SOFTWARE = 15, // software trigger; not for Group modes

// nor double trigger modes

// This is not set to TRSA or TRSB

ADC_TRIG_NONE = 0x3F

} adc_trig_t;

typedef enum e_adc_speed

{

ADC_CONVERT_SPEED_DEFAULT = 0,

ADC_CONVERT_SPEED_HIGH = 0,

ADC_CONVERT_CURRENT_LOW = 1

} adc_speed_t;

typedef struct st_adc_cfg

{

adc_speed_t conv_speed; // ADCSR.ADHSC, Two conversion speeds

adc_align_t alignment; // ADCER.ADRFMT, L or R align

adc_add_t add_cnt; // ADADC.ADC, Addition/average cnt select.

adc_clear_t clearing; // ADCER.ACE, Auto clearing enable/disable

adc_trig_t trigger; // ADSTRGR.TRSA, default & Grp A trig src

adc_trig_t trigger_groupb; // valid only for group modes

uint8_t priority; // for S12ADIO int; 1=lo 15=hi 0=off/polled

uint8_t priority_groupb; // S12GBADI interrupt priority; 0-15

} adc_cfg_t;

/* ADC_CONTROL() ARGUMENT DEFINITIONS */

typedef enum e_adc_cmd

{

// Commands for special hardware configurations

ADC_CMD_USE_VREFL0, // Low reference. Default is to use AVSS0.

ADC_CMD_USE_VREFH0, // High reference. Default is to use AVCC0.

ADC_CMD_SET_DDA_STATE_CNT, // For Disconnect Detection Assist

ADC_CMD_SET_SAMPLE_STATE_CNT, // Set the conversion time

// Command to configure channels, sensors, and comparator

ADC_CMD_ENABLE_CHANS, // Configure channels to scan

ADC_CMD_ENABLE_TEMP_SENSOR, // "configure" temperature sensor

ADC_CMD_ENABLE_VOLT_SENSOR, // "configure" internal ref voltage sensor

ADC_CMD_EN_COMPARATOR_LEVEL, // Enable comparator for threshold compare

ADC_CMD_EN_COMPARATOR_WINDOW, // Enable comparator for range compare

// Commands to enable hardware triggers or cause software trigger

ADC_CMD_ENABLE_TRIG, // ADCSR.TRGE=1 for sync/async triggers

ADC_CMD_SCAN_NOW, // Software trigger start scan

// Commands to poll for scan completion and comparator results

ADC_CMD_CHECK_SCAN_DONE, // For Normal or GroupA scan

ADC_CMD_CHECK_SCAN_DONE_GROUPA,

ADC_CMD_CHECK_SCAN_DONE_GROUPB,

R01AN1666EJ0220 Rev. 2.20 Page 32 of 74

Dec 01, 2016

Page 33

RX Family ADC Module Using Firmware Integration Technology

ADC_CMD_CHECK_CONDITION_MET, // comparator condition

// Advanced control commands

ADC_CMD_DISABLE_TRIG, // ADCSR.TRGE=0 for sync/async trigs

ADC_CMD_DISABLE_INT, // interrupt disable; ADCSR.ADIE=0

ADC_CMD_ENABLE_INT, // interrupt enable; ADCSR.ADIE=1

ADC_CMD_DISABLE_INT_GROUPB, // interrupt disable; ADCSR.GBADIE=0

ADC_CMD_ENABLE_INT_GROUPB, // interrupt enable; ADCSR.GBADIE=1

} adc_cmd_t;

/* for ADC_CMD_SET_DDA_STATE_CNT */

typedef enum e_adc_charge // Disconnection Detection Assist (DDA)

{

ADC_DDA_DISCHARGE = 0x00,

ADC_DDA_PRECHARGE = 0x01,

ADC_DDA_OFF = 0x02,

} adc_charge_t;

#define ADC_DDA_STATE_CNT_MIN (2) //ADDISCR.ADNDIS[0..3] bits.

#define ADC_DDA_STATE_CNT_MAX (15)

typedef struct st_adc_dda

{

adc_charge_t method; // Discharge or Precharge

uint8_t num_states; // 2-15 (0 = DISABLED, 1 is invalid)

} adc_dda_t;

/* for ADC_CMD_SET_SAMPLE_STATE_CNT */

typedef enum e_adc_sst_reg // sample state registers

{

ADC_SST_CH0 = 0,

ADC_SST_CH1,

ADC_SST_CH2,

ADC_SST_CH3,

ADC_SST_CH4,

ADC_SST_CH5,

ADC_SST_CH6,

ADC_SST_CH7,

ADC_SST_CH16_TO_31,

ADC_SST_TEMPERATURE,

ADC_SST_VOLTAGE,

ADC_SST_REG_MAX = ADC_SST_VOLTAGE

} adc_sst_reg_t;

#define ADC_SST_CNT_MIN (5) //For PCLKB:ADCLK = 1:1, 1:2, 1:4, 1:8

//#define ADC_SST_CNT_MIN (6) //For PCLKB:ADCLK = 2:1, 4:1

#define ADC_SST_CNT_MAX (255)

#define ADC_SST_CNT_DEFAULT (13)

typedef struct st_adc_sst

{

adc_sst_reg_t reg_id;

uint8_t num_states; // ch16-31 use the same value

} adc_sst_t;

/* for ADC_CMD_CONFIGURE_SCAN */

// Bitwise OR these masks together for desired channels and sensors

// Used for all commands containing a "mask" or "flags" field

#define ADC_MASK_CH0 (1<<0)

#define ADC_MASK_CH1 (1<<1)

#define ADC_MASK_CH2 (1<<2)

R01AN1666EJ0220 Rev. 2.20 Page 33 of 74

Dec 01, 2016

Page 34

RX Family ADC Module Using Firmware Integration Technology

#define ADC_MASK_CH3 (1<<3)

#define ADC_MASK_CH4 (1<<4)

#define ADC_MASK_CH5 (1<<5)

#define ADC_MASK_CH6 (1<<6)

#define ADC_MASK_CH7 (1<<7)

#define ADC_MASK_CH16 (1<<16)

#define ADC_MASK_CH17 (1<<17)

#define ADC_MASK_CH18 (1<<18)

#define ADC_MASK_CH19 (1<<19)

#define ADC_MASK_CH20 (1<<20)

#define ADC_MASK_CH21 (1<<21)

#define ADC_MASK_CH22 (1<<22)

#define ADC_MASK_CH23 (1<<23)

#define ADC_MASK_CH24 (1<<24)

#define ADC_MASK_CH25 (1<<25)

#define ADC_MASK_CH26 (1<<26)

#define ADC_MASK_CH27 (1<<27)

#define ADC_MASK_CH28 (1<<28)

#define ADC_MASK_CH29 (1<<29)

#define ADC_MASK_CH30 (1<<30)

#define ADC_MASK_CH31 (1<<31)

#define ADC_MASK_TEMP (1<<8) // temperature sensor

#define ADC_MASK_VOLT (1<<9) // internal reference voltage sensor

#define ADC_MASK_SENSORS (ADC_MASK_TEMP | ADC_MASK_VOLT)

#define ADC_MASK_GROUPB_OFF (0)

#define ADC_MASK_ADD_OFF (0)

#define ADC_MASK_SAMPLE_HOLD_OFF (0)

typedef enum e_adc_grpa // action when groupa interrupts groupb

scan

{

ADC_GRPA_PRIORITY_OFF = 0, // groupa ignored and doesn’t int groupb

ADC_GRPA_GRPB_WAIT_TRIG = 1, // groupb restarts at next trigger

ADC_GRPA_GRPB_RESTART_SCAN= 3, // groupb restarts immediately

ADC_GRPA_GRPB_CONT_SCAN = 0x8001, // groupb restarts immed, scans cont

} adc_grpa_t;

typedef enum e_adc_diag // Self-Diagnosis Channel

{