Page 1

REJ09B0339-0200

R8C/2C Group, R8C/2D Group

16

Hardware Manual

RENESAS MCU

R8C FAMILY / R8C/2x SERIES

All information contained in these materials, including products and product specifications,

represents information on the product at the time of publication and is subject to change by

Renesas Technology Corp. without notice. Please review the latest information published

by Renesas Technology Corp. through various means, including the Renesas Technology

Corp. website (http://www.renesas.com).

Rev.2.00

Revision Date: Dec 05, 2007

www.renesas.com

Page 2

Notes regarding these materials

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate

Renesas products for their use. Renesas neither makes warranties or representations with respect to the

accuracy or completeness of the information contained in this document nor grants any license to any

intellectual property rights or any other rights of Renesas or any third party with respect to the information in

this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising

out of the use of any information in this document, including, but not limited to, product data, diagrams, charts,

programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military

applications such as the development of weapons of mass destruction or for the purpose of any other military

use. When exporting the products or technology described herein, you should follow the applicable export

control laws and regulations, and procedures required by such laws and regulations.

4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and

application circuit examples, is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas products listed in this

document, please confirm the latest product information with a Renesas sales office. Also, please pay regular

and careful attention to additional and different information to be disclosed by Renesas such as that disclosed

through our website. (http://www.renesas.com )

5. Renesas has used reasonable care in compiling the information included in this document, but Renesas

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information

included in this document.

6. When using or otherwise relying on the information in this document, you should evaluate the information in

light of the total system before deciding about the applicability of such information to the intended application.

Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any

particular application and specifically disclaims any liability arising out of the application and use of the

information in this document or Renesas products.

7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas

products are not designed, manufactured or tested for applications or otherwise in systems the failure or

malfunction of which may cause a direct threat to human life or create a risk of human injury or which require

especially high quality and reliability such as safety systems, or equipment or systems for transportation and

traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication

transmission. If you are considering the use of our products for such purposes, please contact a Renesas

sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

(1) artificial life support devices or systems

(2) surgical implantations

(3) healthcare intervention (e.g., excision, administration of medication, etc.)

(4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who

elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas

Technology Corp., its affiliated companies and their officers, directors, and employees against any and all

damages arising out of such applications.

9. You should use the products described herein within the range specified by Renesas, especially with respect

to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation

characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or

damages arising out of the use of Renesas products beyond such specified ranges.

10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific

characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use

conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and

injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for

hardware and software including but not limited to redundancy, fire control and malfunction prevention,

appropriate treatment for aging degradation or any other applicable measures. Among others, since the

evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or

system manufactured by you.

11. In case Renesas products listed in this document are detached from the products to which the Renesas

products are attached or affixed, the risk of accident such as swallowing by infants and small children is very

high. You should implement safety measures so that Renesas products may not be easily detached from your

products. Renesas shall have no liability for damages arising out of such detachment.

12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written

approval from Renesas.

13. Please contact a Renesas sales office if you have any questions regarding the information contained in this

document, Renesas semiconductor products, or if you have any other inquiries.

Page 3

General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes

on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under

General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each

other, the description in the body of the manual takes precedence.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the

manual.

The input pins of CMOS products are generally in the high-impedance state. In operation

with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the

vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur

due to the false recognition of the pin state as an input signal become possible. Unused

pins should be handled as described under Handling of Unused Pins in the manual.

2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register

settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states

of pins are not guaranteed from the moment when power is supplied until the reset

process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset

function are not guaranteed from the moment when power is supplied until the power

reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become

stable. When switching the clock signal during program execution, wait until the target clock

signal has stabilized.

When the clock signal is generated with an external resonator (or from an external

oscillator) during a reset, ensure that the reset line is only released after full stabilization of

the clock signal. Moreover, when switching to a clock signal produced with an external

resonator (or by an external oscillator) while program execution is in progress, wait until

the target clock signal is stable.

5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm

that the change will not lead to problems.

The characteristics of MPU/MCU in the same group but having different part numbers may

differ because of the differences in internal memory capacity and layout pattern. When

changing to products of different part numbers, implement a system-evaluation test for

each of the products.

Page 4

How to Use This Manual

1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical

characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic

knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual.

The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral

functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur

within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer

to the text of the manual for details.

The following documents apply to the R8C/2C Group, R8C/2D Group. Make sure to refer to the latest versions of

these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web

site.

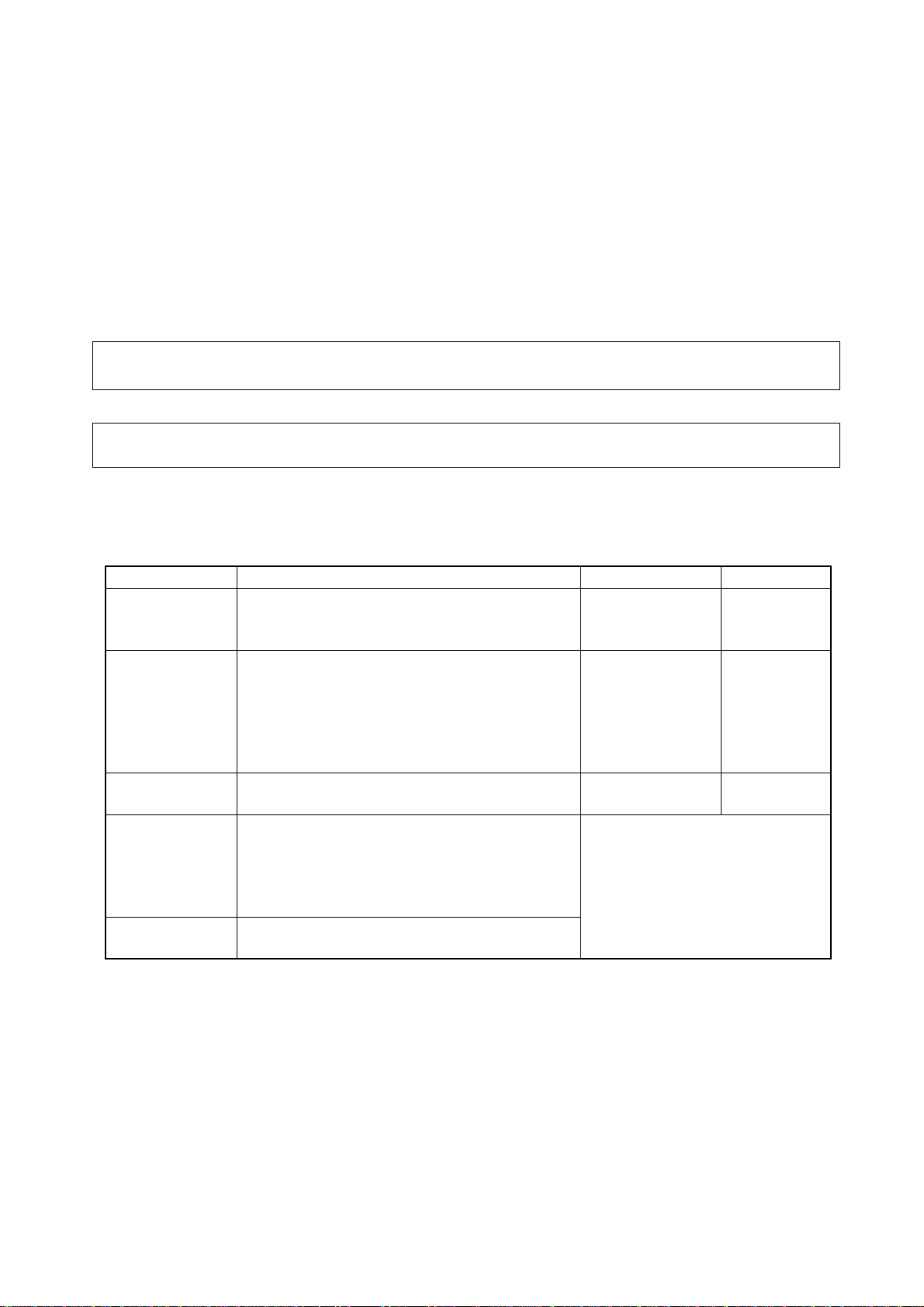

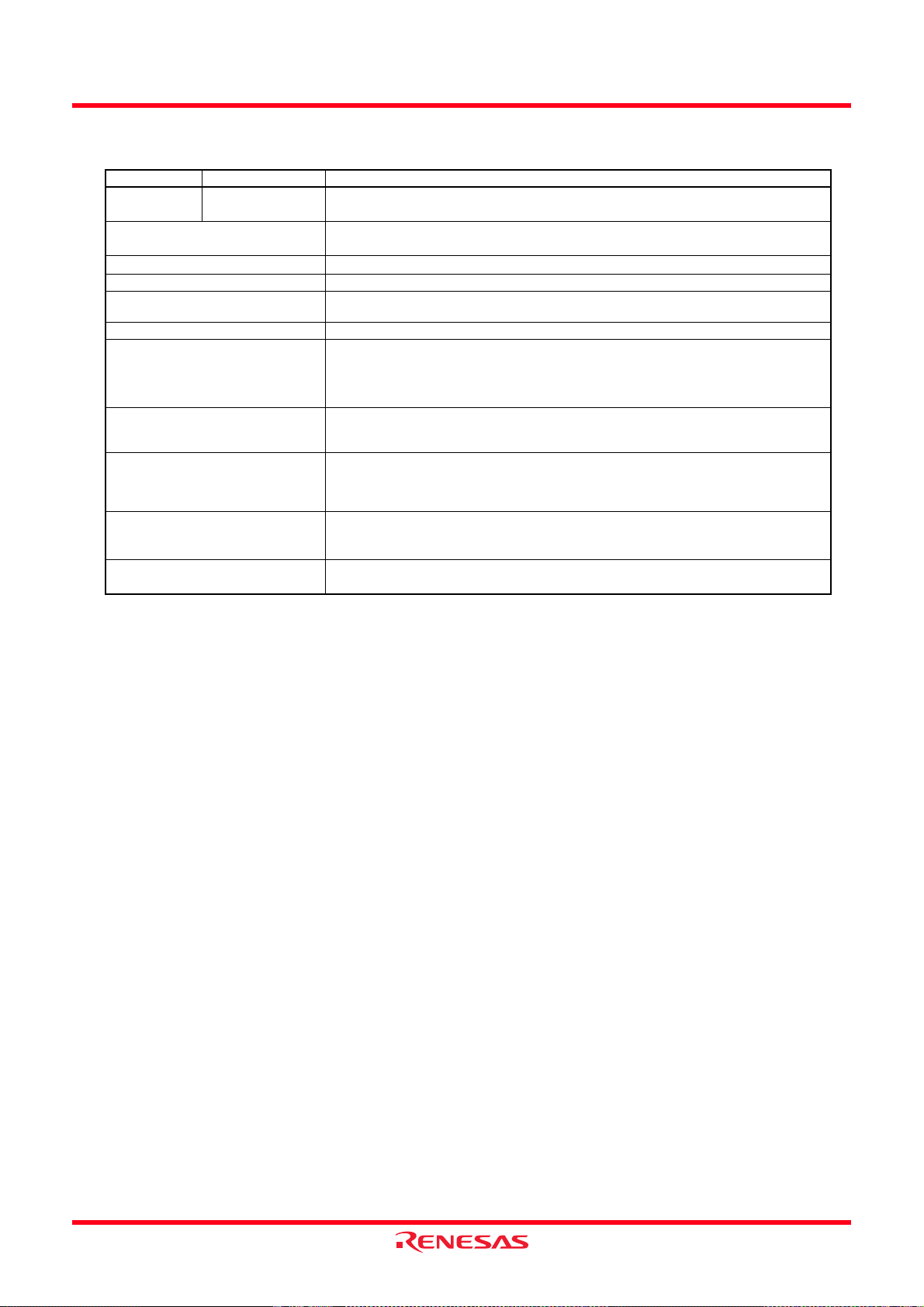

Document Type Description Document Title Document No.

Datasheet Hardware overview and electrical characteristics R8C/2C Group,

R8C/2D Group

Datasheet

Hardware manual Hardware specifications (pin assignments,

memory maps, peripheral function

specifications, electrical characteristics, timing

charts) and operation description

Note: Refer to the application notes for details on

using peripheral functions.

Software manual Description of CPU instruction set R8C/Tiny Series

Application note Information on using peripheral functions and

application examples

Sample programs

Information on writing programs in assembly

language and C

Renesas

technical update

Product specifications, updates on documents,

etc.

R8C/2C Group,

R8C/2D Group

Hardware Manual

Software Manual

Available from Renesas

Technology Web site.

REJ03B0183

This hardware

manual

REJ09B0001

Page 5

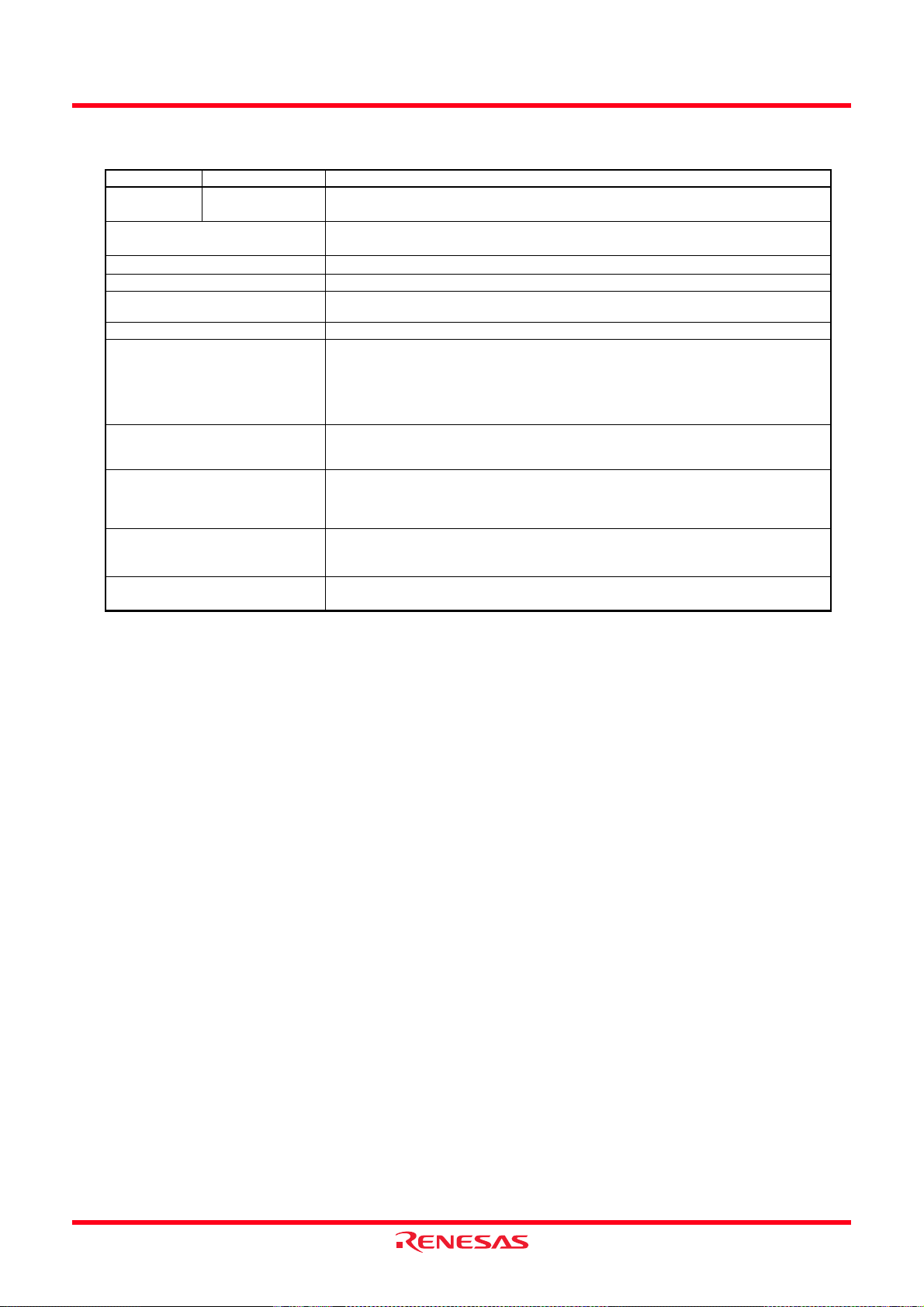

2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described

below.

(1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word

“register,” “bit,” or “pin” to distinguish the three categories.

Examples the PM03 bit in the PM0 register

P3_5 pin, VCC pin

(2) Notation of Numbers

The indication “b” is appended to numeric values given in binary format. However, nothing is appended to the

values of single bits. The indication “h” is appended to numeric values given in hexadecimal format. Nothing

is appended to numeric values given in decimal format.

Examples Binary: 11b

Hexadecimal: EFA0h

Decimal: 1234

Page 6

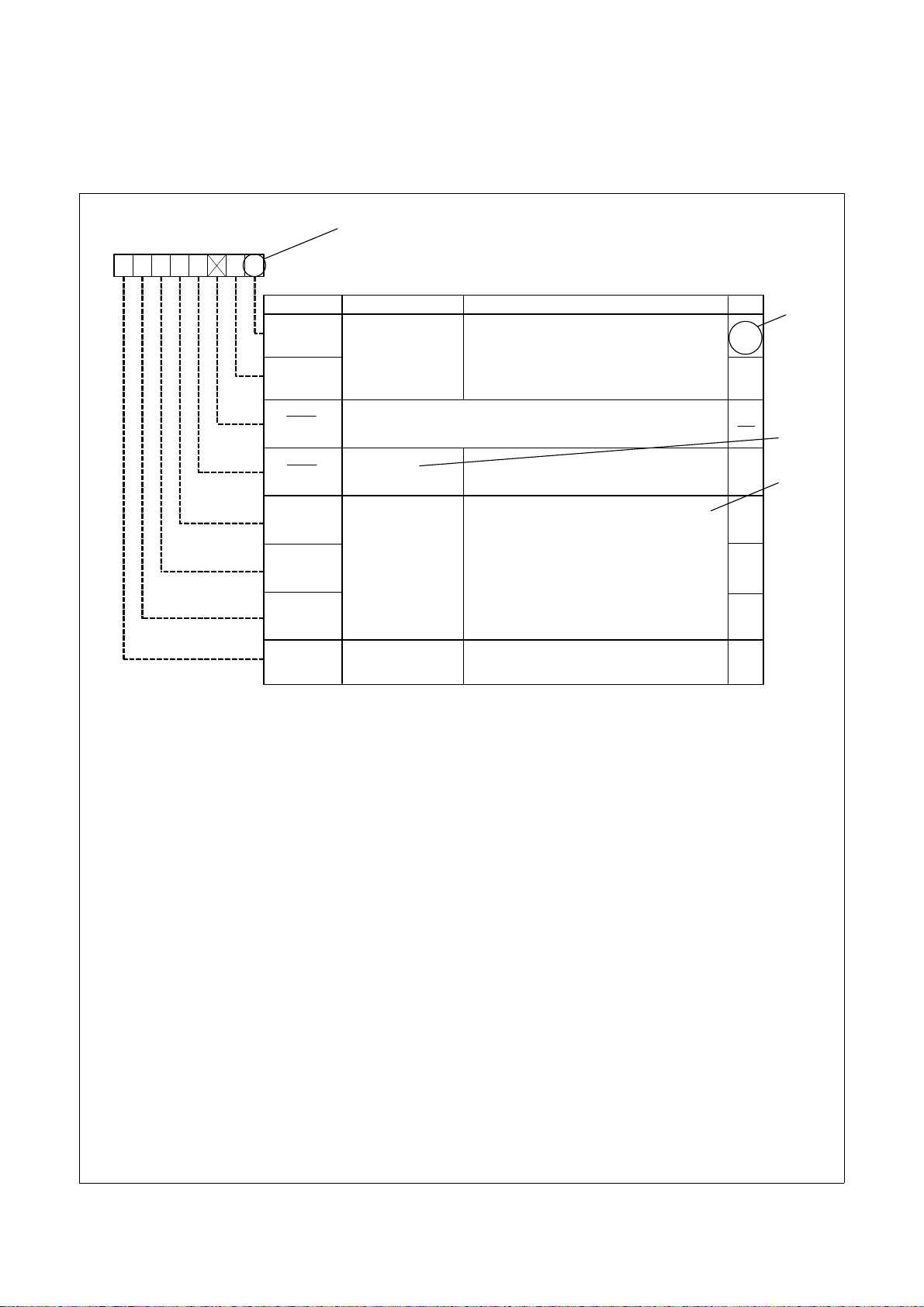

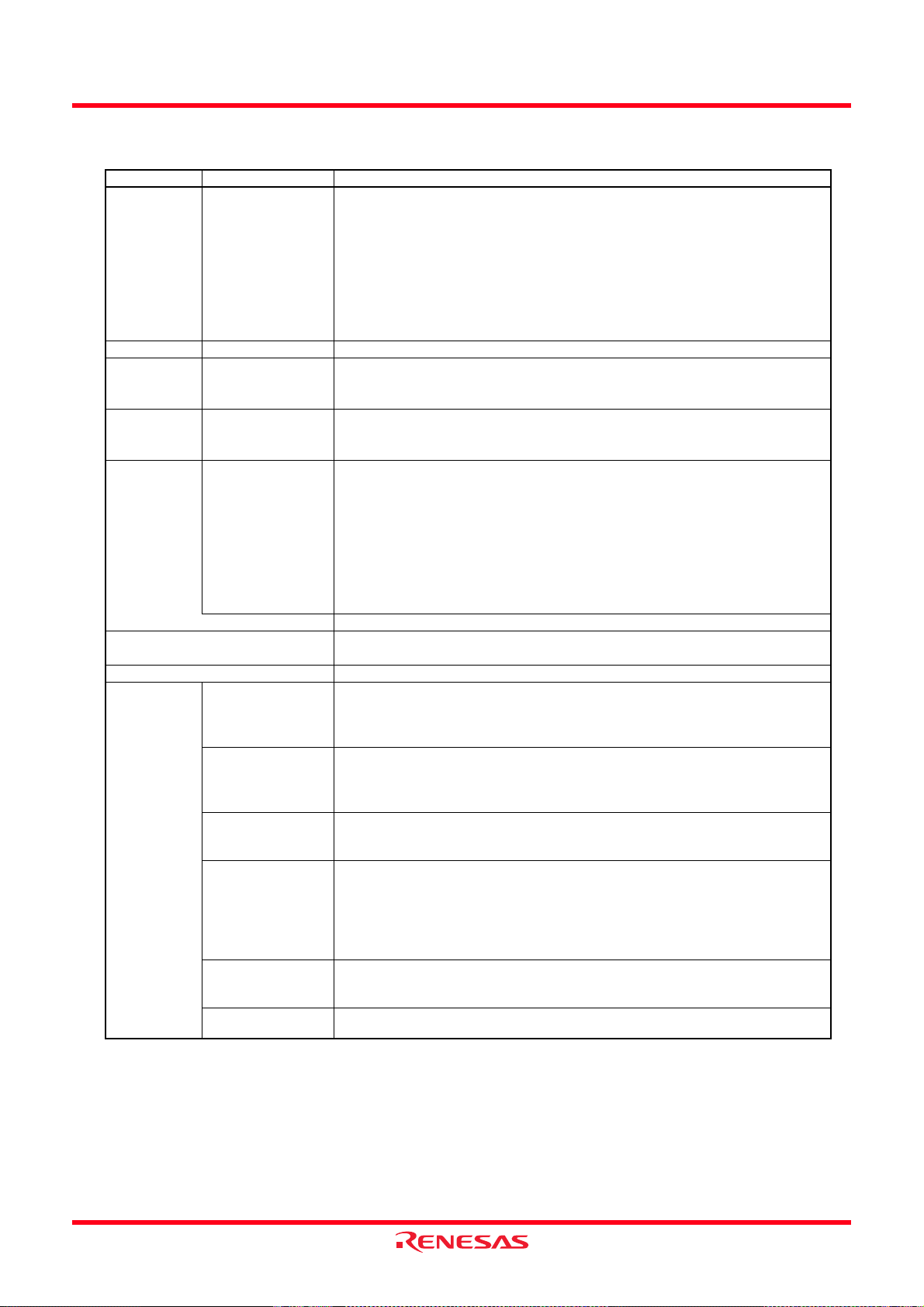

3. Register Notation

The symbols and terms used in register diagrams are described below.

XXX Register

b7 b6 b5 b4 b3 b2 b1 b0

0

XXX0

XXX1

(b2)

(b3)

XXX4

XXX5

XXX6

XXX7

*1

Symbol Address After Reset

XXX XXX 00h

Bit NameBit Symbol

XXX bits

Nothing is assigned. If necessary, set to 0.

When read, the content is undefined.

Reserved bits

XXX bits

XXX bit

b1 b0

1 0: XXX

0 1: XXX

1 0: Do not set.

1 1: XXX

Set to 0.

Function varies according to the operating

mode.

0: XXX

1: XXX

Function

RW

RW

RW

RW

RW

WO

RW

RO

*2

*3

*4

*1

Blank: Set to 0 or 1 according to the application.

0: Set to 0.

1: Set to 1.

X: Nothing is assigned.

*2

RW: Read and write.

RO: Read only.

WO: Write only.

−: Nothing is assigned.

*3

• Reserved bit

Reserved bit. Set to specified value.

*4

• Nothing is assigned

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information

on the individual modes.

Page 7

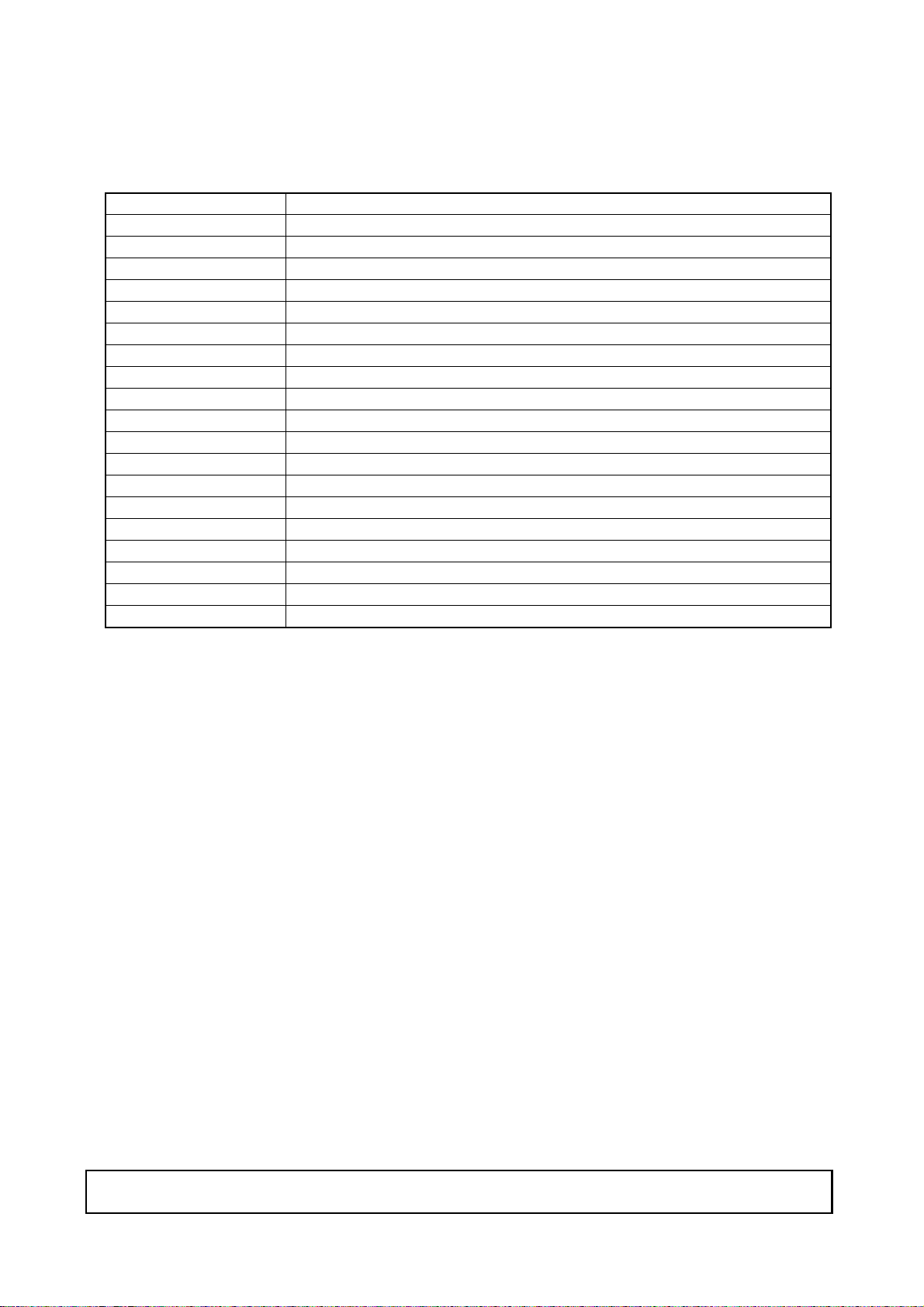

4. List of Abbreviations and Acronyms

Abbreviation Full Form

ACIA Asynchronous Communication Interface Adapter

bps bits per second

CRC Cyclic Redundancy Check

DMA Direct Memory Access

DMAC Direct Memory Access Controller

GSM Global System for Mobile Communications

Hi-Z High Impedance

IEBus Inter Equipment bus

I/O Input/Output

IrDA Infrared Data Association

LSB Least Significant Bit

MSB Most Significant Bit

NC Non-Connection

PLL Phase Locked Loop

PWM Pulse Width Modulation

SFR Special Function Registers

SIM Subscriber Identity Module

UART Universal Asynchronous Receiver/Transmitter

VCO Voltage Controlled Oscillator

All trademarks and registered trademarks are the property of their respective owners.

Page 8

Table of Contents

SFR Page Reference ........................................................................................................................... B - 1

1. Overview ......................................................................................................................................... 1

1.1 Features ..................................................................................................................................................... 1

1.1.1 Applications .......................................................................................................................................... 1

1.1.2 Specifications ........................................................................................................................................ 2

1.2 Product List ............................................................................................................................................... 6

1.3 Block Diagram ........................................ .................................. .................................. ............................. 9

1.4 Pin Assignment ........................................................................................................................................ 10

1.5 Pin Functions ........................................................................................................................................... 13

2. Central Processing Unit (CPU) ..................................................................................................... 15

2.1 Data Registers (R0, R1, R2, and R3) ...................................................................................................... 16

2.2 Address Registers (A0 and A1) ............................................................................................................... 16

2.3 Frame Base Register (FB) ....................................................................................................................... 16

2.4 Interrupt Table Register (INTB) .............................................................................................................. 16

2.5 Program Counter (PC) ................................................................... ... ....................................................... 16

2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) .................................................................. 16

2.7 Static Base Register (SB) ........................................................................................................................ 16

2.8 Flag Register (FLG) ................................................................................................................................ 16

2.8.1 Carry Flag (C) ..................................................................................................................................... 16

2.8.2 Debug Flag (D) ................................................................................................................................... 16

2.8.3 Zero Flag (Z) ....................................................................................................................................... 16

2.8.4 Sign Flag (S) ....................................................................................................................................... 16

2.8.5 Register Bank Select Flag (B) ............................................................................................................ 16

2.8.6 Overflow Flag (O) .............................................................................................................................. 16

2.8.7 Interrupt Enable Flag (I) ................................................................... .................................................. 17

2.8.8 Stack Pointer Select Flag (U) .............................................................................................................. 17

2.8.9 Processor Interrupt Priority Level (IPL) ........................................... .................................. ................ 17

2.8.10 Reserved Bit .............................. ................................................................. ......................................... 17

3. Memory ......................................................................................................................................... 18

3.1 R8C/2C Group ......................................................................................................................................... 18

3.2 R8C/2D Group ........................................................................................................................................ 19

4. Special Function Registers (SFRs) ............................................................................................... 20

5. Resets ........................................................................................................................................... 32

5.1 Hardware Reset ....................................................................................................................................... 35

5.1.1 When Power Supply is Stable .................................................................... ......................................... 35

5.1.2 Power On ............................................................................................................................................ 35

5.2 Power-On Reset Function ....................................................................................................................... 37

5.3 Voltage Monitor 0 Reset ......................................................................................................................... 38

5.4 Voltage Monitor 1 Reset ......................................................................................................................... 38

5.5 Voltage Monitor 2 Reset ......................................................................................................................... 38

5.6 Watchdog Timer Reset ............................................................................................................................ 39

5.7 Software Reset ......................................................................................................................................... 39

A - 1

Page 9

6. Voltage Detection Circuit .............................................................................................................. 40

6.1 VCC Input Voltage .................................................................................................................................. 47

6.1.1 Monitoring Vdet0 ............................................................ .................................. ................................. 47

6.1.2 Monitoring Vdet1 ............................................................ .................................. ................................. 47

6.1.3 Monitoring Vdet2 ............................................................ .................................. ................................. 47

6.2 Voltage Monitor 0 Reset ......................................................................................................................... 48

6.3 Voltage Monitor 1 Interrupt and Voltage Monitor 1 Reset ..................................................................... 49

6.4 Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset ..................................................................... 51

7. Programmable I/O Ports ............................................................................................................... 53

7.1 Functions of Programmable I/O Ports ..................................................................................................... 53

7.2 Effect on Peripheral Functions ................................................................................................................ 54

7.3 Pins Other than Programmable I/O Ports ................................................................................................ 54

7.4 Port settings ...................................... ................................. .................................. .................................... 71

7.5 Unassigned Pin Handling ........................................................................................................................ 92

8. Processor Mode ............................................................................................................................ 93

8.1 Processor Modes .................................... .................................. .................................. .............................. 93

9. Bus ................................................................................................................................................ 94

10. Clock Generation Circuit ............................................................................................................... 96

10.1 XIN Clock ..................................... .................................. ................................. ..................................... 106

10.2 On-Chip Oscillator Clocks .................................................................................................................... 107

10.2.1 Low-Speed On-Chip Oscillator Clock .............................................................................................. 107

10.2.2 High-Speed On-Chip Oscillator Clock ............................................................................................. 107

10.3 XCIN Clock ........................................................................................................................................... 108

10.4 CPU Clock and Peripheral Function Clock ........................................................................................... 109

10.4.1 System Clock ...................................................................................................................... .............. 109

10.4.2 CPU Clock ..................................................................................... .................................. ................. 109

10.4.3 Peripheral Function Clock (f1, f2, f4, f8, and f32) ........................................................................... 109

10.4.4 fOCO ................................................................................................................................................. 109

10.4.5 fOCO40M ......................................................................................................................................... 109

10.4.6 fOCO-F ............................................................................................................................................. 109

10.4.7 fOCO-S ............................................................................................................................................. 109

10.4.8 fOCO128 ........................................................................................................................................... 109

10.4.9 fC4 and fC32 .................................. .................................. ................................................................. 110

10.5 Power Control ........................................................................................................................................ 111

10.5.1 Standard Operating Mode ................................................................................................................. 111

10.5.2 Wait Mode .............................................. .................................. ........................................................ 113

10.5.3 Stop Mode ......................................................................................................................................... 117

10.6 Oscillation Stop Detection Function ..................................................................................................... 120

10.6.1 How to Use Oscillation Stop Detection Function ........................................... .................................. 120

10.7 Notes on Clock Generation Circuit ....................................................................................................... 123

10.7.1 Stop Mode ......................................................................................................................................... 123

10.7.2 Wait Mode .............................................. .................................. ........................................................ 123

10.7.3 Oscillation Stop Detection Function ................................................................................................. 123

10.7.4 Oscillation Circuit Constants ...................................................................................................... ...... 123

A - 2

Page 10

11. Protection .................................................................................................................................... 124

12. Interrupts ..................................................................................................................................... 125

12.1 Interrupt Overview ........................................................................................................................ ........ 125

12.1.1 Types of Interrupts ............................................................................................................................ 125

12.1.2 Software Interrupts ........................................................................................................................ ... 126

12.1.3 Special Interrupts ................................................................................................................ .............. 127

12.1.4 Peripheral Function Interrupt ............................................................................................................ 127

12.1.5 Interrupts and Interrupt Vectors ........................................................................................................ 128

12.1.6 Interrupt Control ............................................................................................................................... 130

12.2 INT

12.2.1 INTi

12.2.2 INTi

Interrupt ......................................................................................................................................... 139

Interrupt (i = 0 to 3) .................................................................................................................. 139

Input Filter (i = 0 to 3) ............................................ .................................. ............................... 142

12.3 Key Input Interrupt ................................................................................................................................ 143

12.4 Address Match Interrupt ........................... ............................................................................................. 145

12.5 Timer RC Interrupt, Timer RD Interrupt, Clock Synchronous Serial I/O with Chip Select Interrupts, and

2

I

C bus Interface Interrupt (Interrupts with Multiple Interrupt Request Sources) ................................ 147

12.6 Notes on Interrupts ................................................................................................................................ 149

12.6.1 Reading Address 00000h .................................................................................................................. 149

12.6.2 SP Setting .................................................................................................................................. ........ 149

12.6.3 External Interrupt and Key Input Interrupt ....................................................................................... 149

12.6.4 Changing Int e rrupt Sources .............................................................................................................. 150

12.6.5 Changing Interrupt Control Register Contents ................................................................................. 151

13. Watchdog Timer ......................................................................................................................... 152

13.1 Count Source Protection Mode Disabled .............................................................................................. 156

13.2 Count Source Protection Mode Enabled ............................................................................................... 157

14. Timers ......................................................................................................................................... 158

14.1 Timer RA ............................................................................................................................................... 161

14.1.1 Timer Mode ...................................................................................................................................... 164

14.1.2 Pulse Output Mode .................................................. ......................................................................... 166

14.1.3 Event Counter Mode ......................................................................................................................... 168

14.1.4 Pulse Width Measurement Mode ...................................................................................................... 170

14.1.5 Pulse Period Measurement Mode .......................................... ........................................................... 173

14.1.6 Notes on Timer RA ............................................................................................................. .............. 176

14.2 Timer RB ............................................................................................................................................... 177

14.2.1 Timer Mode ...................................................................................................................................... 181

14.2.2 Programmable Waveform Generation Mode .................................... ................................................ 184

14.2.3 Programmable One-shot Generation Mode ...................................................................................... 186

14.2.4 Programmable Wait One-Shot Generation Mode ............................................................................. 190

14.2.5 Notes on Timer RB ........................................................................................................................... 194

14.3 Timer RC ............................................................................................................................................... 198

14.3.1 Overview ........................................................................................................................................... 198

14.3.2 Registers Associated with Timer RC ................................................................................................ 200

14.3.3 Common Items for Multiple Modes ................................................................................................. 210

14.3.4 Timer Mode (Input Capture Function) ............................................................................................. 216

14.3.5 Timer Mode (Output Compare Function) ......................................................................................... 221

14.3.6 PWM Mode ......................... .................................. .................................. .................................. ........ 227

A - 3

Page 11

14.3.7 PWM2 Mode ................................................................................................................. .................... 232

14.3.8 Timer RC Interrupt ........................................................................................................................... 238

14.3.9 Notes on Timer RC ........................................................................................................................... 239

14.4 Timer RD ............................................................................................................................................... 240

14.4.1 Count Sources ................................................................................................................................... 245

14.4.2 Buffer Operation ............................................................................................................................... 246

14.4.3 Synchronous Operation ..................... .................................................................... ............................ 248

14.4.4 Pulse Output Forced Cutoff .............................................................................................................. 249

14.4.5 Input Capture Function ..................................................................................................................... 251

14.4.6 Output Compare Function ................................................................ ................................. ............... 266

14.4.7 PWM Mode ......................... .................................. .................................. .................................. ........ 284

14.4.8 Reset Synchronous PWM Mode ....................................................................................................... 298

14.4.9 Complementary PWM Mode ............................................................................................................ 309

14.4.10 PWM3 Mode ..................................................................................................................................... 324

14.4.11 Timer RD Interrupt ........................................................................................................................... 338

14.4.12 Notes on Timer RD ........................................................................................................................... 340

14.5 Timer RE ............................................................................................................................................... 346

14.5.1 Real-Time Clock Mode .................................................................................................................... 347

14.5.2 Output Compare Mode .................................................... .................................. ............................... 355

14.5.3 Notes on Timer RE ........................................................................................................................... 361

14.6 Timer RF ............................................................................................................................................... 364

14.6.1 Input Capture Mode .......................................................................................................................... 369

14.6.2 Output Compare Mode .................................................... .................................. ............................... 372

14.6.3 Notes on Timer RF ........................................................................................................................... 376

15. Serial Interface ............................................................................................................................ 377

15.1 Clock Synchronous Serial I/O Mode .............. ....................................................................................... 384

15.1.1 Polarity Select Function ................................................................................................................. ... 388

15.1.2 LSB First/MSB First Select Function ............................................................................................... 388

15.1.3 Continuous Receive Mode ................................................................................................................ 389

15.2 Clock Asynchronous Serial I/O (UART) Mode .......................................... .......................................... 390

15.2.1 Bit Rate .................................. .................................. .................................. ....................................... 395

15.3 Notes on Serial Interface ....................................................................................................................... 396

16. Clock Synchronous Serial Interface ............................................................................................ 397

16.1 Mode Selection ...................................................................................................................................... 397

16.2 Clock Synchronous Serial I/O with Chip Select (SSU) ........................................................................ 398

16.2.1 Transfer Clock ............................................................................................................ ...................... 407

16.2.2 SS Shift Register (SSTRSR) ....................................................................................................... ...... 409

16.2.3 Interrupt Requests ........................................... .................................. ............................... ................. 410

16.2.4 Communication Modes and Pin Functions .................................................................................... ... 411

16.2.5 Clock Synchronous Communication Mode ...................................................................................... 412

16.2.6 Operation in 4-Wire Bus Communication Mode .............................................................................. 419

16.2.7 SCS

Pin Control and Arbitration ...................................................................................................... 425

16.2.8 Notes on Clock Synchronous Serial I/O with Chip Select ............................................................... 426

16.3 I

2

C bus Interface ................................................................................................................................. ... 427

16.3.1 Transfer Clock ............................................................................................................ ...................... 437

16.3.2 Interrupt Requests ........................................... .................................. ............................... ................. 438

16.3.3 I

2

C bus Interface Mode ..................................................................................................................... 439

A - 4

Page 12

16.3.4 Clock Synchronous Serial Mode ...................................................................................................... 450

16.3.5 Examples of Register Setting ............................................................................................................ 453

16.3.6 Noise Canceller ............................................................................................................. .................... 457

16.3.7 Bit Synchronization Circuit .............................................................................................................. 458

16.3.8 Notes on I

2

C bus Interface ................................................................................................................ 459

17. Hardware LIN .............................................................................................................................. 460

17.1 Features ............................................................................................................................. .................... 460

17.2 I nput/Output Pins ................................................................................................................. ................. 461

17.3 Register Configuration .......................................................................................................................... 462

17.4 Functional Description .......................................................................................................................... 464

17.4.1 Master Mode ..................................................................................................................................... 464

17.4.2 Slave Mode ....................................................................................................................................... 467

17.4.3 Bus Collision Detection Function ..................................................................................................... 471

17.4.4 Hardware LIN End Processing ......................................................................................................... 472

17.5 I nterrupt Requests ......... .................................. ................................................................. ...................... 473

17.6 Notes on Hardware LIN ........................................................................................................................ 474

18. A/D Converter ............................................................................................................................. 475

18.1 Common Items for Multiple Modes ...................................................................................................... 480

18.1.1 Input/Output Pins .............................................................................................................................. 480

18.1.2 Sample and Hold .................................. .................................. ........................................................... 480

18.1.3 A/D Conversion Cycles ...................................................................................................... .............. 480

18.1.4 A/D Conversion Start Condition ..................... .................................................................................. 481

18.1.5 A/D Conversion Result ..................................................................................................................... 482

18.1.6 Low Current Consumption Function ................................................................................................ 482

18.2 One-Shot Mode ............................................................................................................................... ...... 483

18.3 Repeat Mode 0 ................................................................................................................................. ...... 484

18.4 Repeat Mode 1 ................................................................................................................................. ...... 485

18.5 S ingle Sweep Mode ..................................... .................................. ........................................................ 486

18.6 Repeat Sweep Mode .............................................................................................................................. 488

18.7 Internal Equivalent Circuit of Analog Input .......................................................................................... 490

18.8 Output Impedance of Sensor under A/D Conversion ............................................................................ 491

18.9 Notes on A/D Converter ........................................................................................................................ 492

19. D/A Converter ............................................................................................................................. 493

20. Flash Memory ............................................................................................................................. 495

20.1 Overview ................................................................................................................................. .............. 495

20.2 Memory Map ............................................... .......................................................................................... 496

20.3 Functions to Prevent Rewriting of Flash Memory ................................................................................ 498

20.3.1 ID Code Check Function ............................................................................................................... ... 498

20.3.2 ROM Code Protect Function ............................................................................................................ 499

20.4 CPU Rewrite Mode ........................................................... .................................. .................................. 500

20.4.1 EW0 Mode ........................................................................................................................................ 501

20.4.2 EW1 Mode ........................................................................................................................................ 501

20.4.3 Software Commands .............................................................................................................. ........... 510

20.4.4 Status Registers ........................................................................................................... ...................... 515

20.4.5 Full Status Check .............................................................................................................................. 516

A - 5

Page 13

20.5 Standard Serial I/O Mode ...................................................................................................................... 518

20.5.1 ID Code Check Function ............................................................................................................... ... 518

20.6 P arallel I/O Mode .................................................................................................................................. 522

20.6.1 ROM Code Protect Function ............................................................................................................ 522

20.7 Notes on Flash Memory ................................................................................................................ ........ 523

20.7.1 CPU Rewrite Mode ........................................................................ .................................. ................. 523

21. Electrical Characteristics ............................................................................................................ 526

22. Usage Notes ............................................................................................................................... 551

22.1 Notes on Clock Generation Circuit ....................................................................................................... 551

22.1.1 Stop Mode ......................................................................................................................................... 551

22.1.2 Wait Mode .............................................. .................................. ........................................................ 551

22.1.3 Oscillation Stop Detection Function ................................................................................................. 551

22.1.4 Oscillation Circuit Constants ...................................................................................................... ...... 551

22.2 Notes on Interrupts ................................................................................................................................ 552

22.2.1 Reading Address 00000h .................................................................................................................. 552

22.2.2 SP Setting .................................................................................................................................. ........ 552

22.2.3 External Interrupt and Key Input Interrupt ....................................................................................... 552

22.2.4 Changing Int e rrupt Sources .............................................................................................................. 553

22.2.5 Changing Interrupt Control Register Contents ................................................................................. 554

22.3 Notes on Timers .................................................................................................................................... 555

22.3.1 Notes on Timer RA ............................................................................................................. .............. 555

22.3.2 Notes on Timer RB ........................................................................................................................... 556

22.3.3 Notes on Timer RC ........................................................................................................................... 560

22.3.4 Notes on Timer RD ............................................................................................................. .............. 561

22.3.5 Notes on Timer RE ........................................................................................................................... 567

22.3.6 Notes on Timer RF ........................................................................................................................... 570

22.4 Notes on Serial Interface ....................................................................................................................... 571

22.5 Notes on Clock Synchronous Serial Interface ....................................................................................... 572

22.5.1 Notes on Clock Synchronous Serial I/O with Chip Select ............................................................... 572

22.5.2 Notes on I

2

C bus Interface ................................................................................................................ 572

22.6 Notes on Hardware LIN ........................................................................................................................ 573

22.7 Notes on A/D Converter ........................................................................................................................ 574

22.8 Notes on Flash Memory ................................................................................................................ ........ 575

22.8.1 CPU Rewrite Mode ........................................................................ .................................. ................. 575

22.9 Notes on Noise ........................................................................................................................... ........... 578

22.9.1 Inserting a Bypass Capacitor between VCC and VSS Pins as a Countermeasure against Noise and

Latch-up ............................................................................................................................................ 578

22.9.2 Countermeasures against Noise Error of Port Control Registers ..................................................... 578

23. Notes on On-Chip Debugger ...................................................................................................... 579

24. Notes on Emulator Debugger ..................................................................................................... 580

Appendix 1. Package Dimensions ........................................................................................................ 581

Appendix 2. Connection Examples between Serial Writer and On-Chip Debugging Emulator ............ 582

A - 6

Page 14

Appendix 3. Example of Oscillation Evaluation Circuit ......................................................................... 583

Index ..................................................................................................................................................... 584

A - 7

Page 15

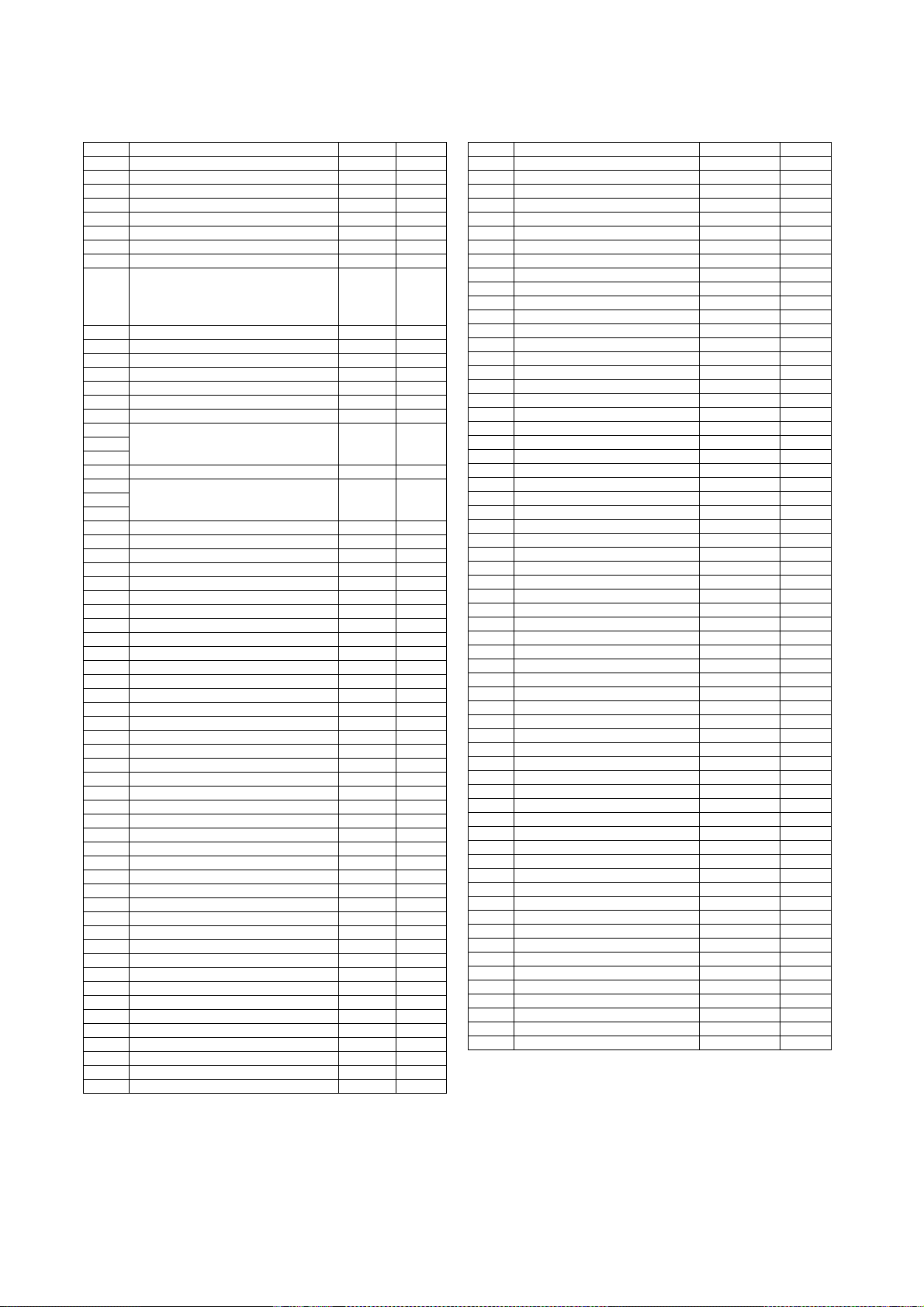

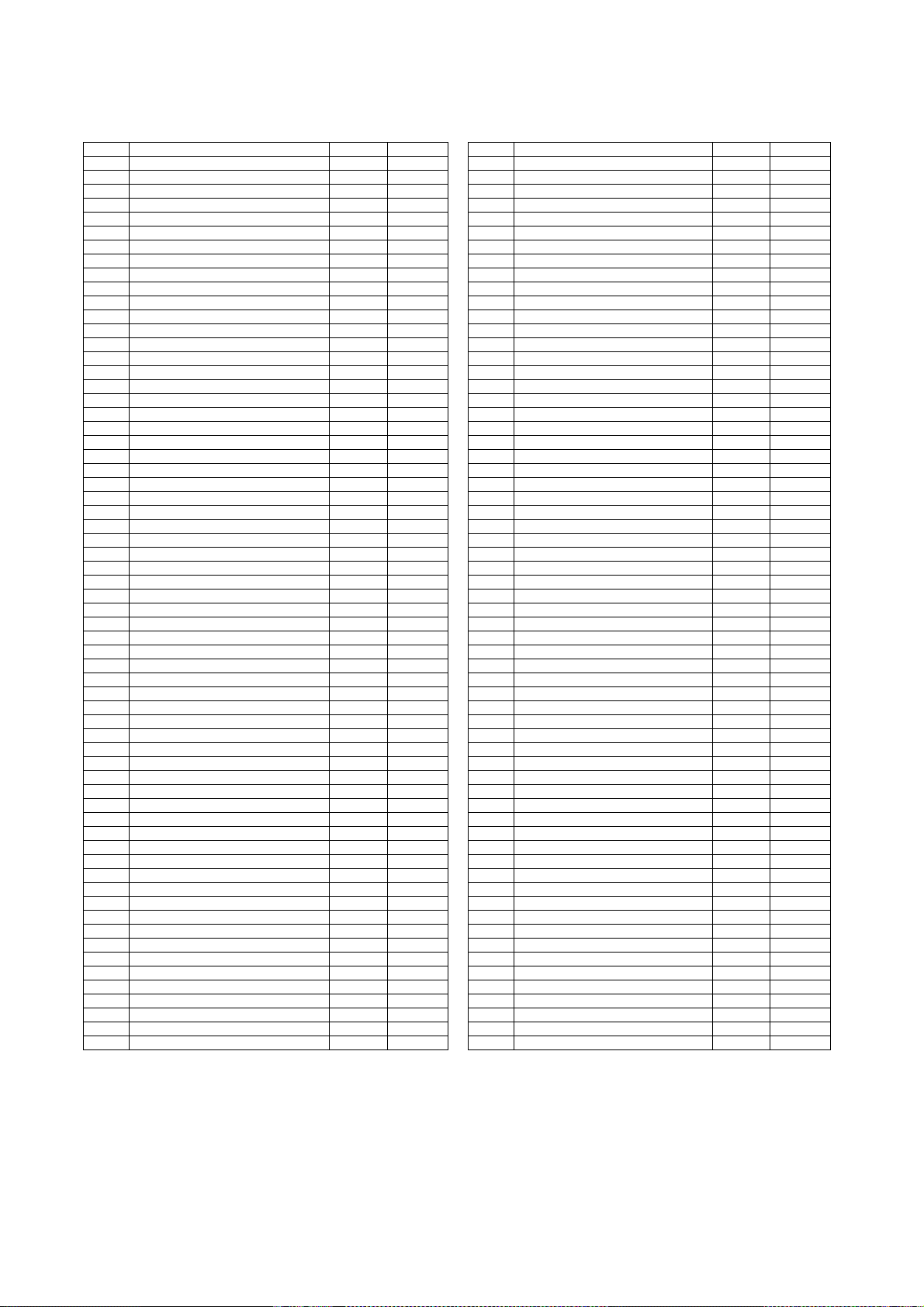

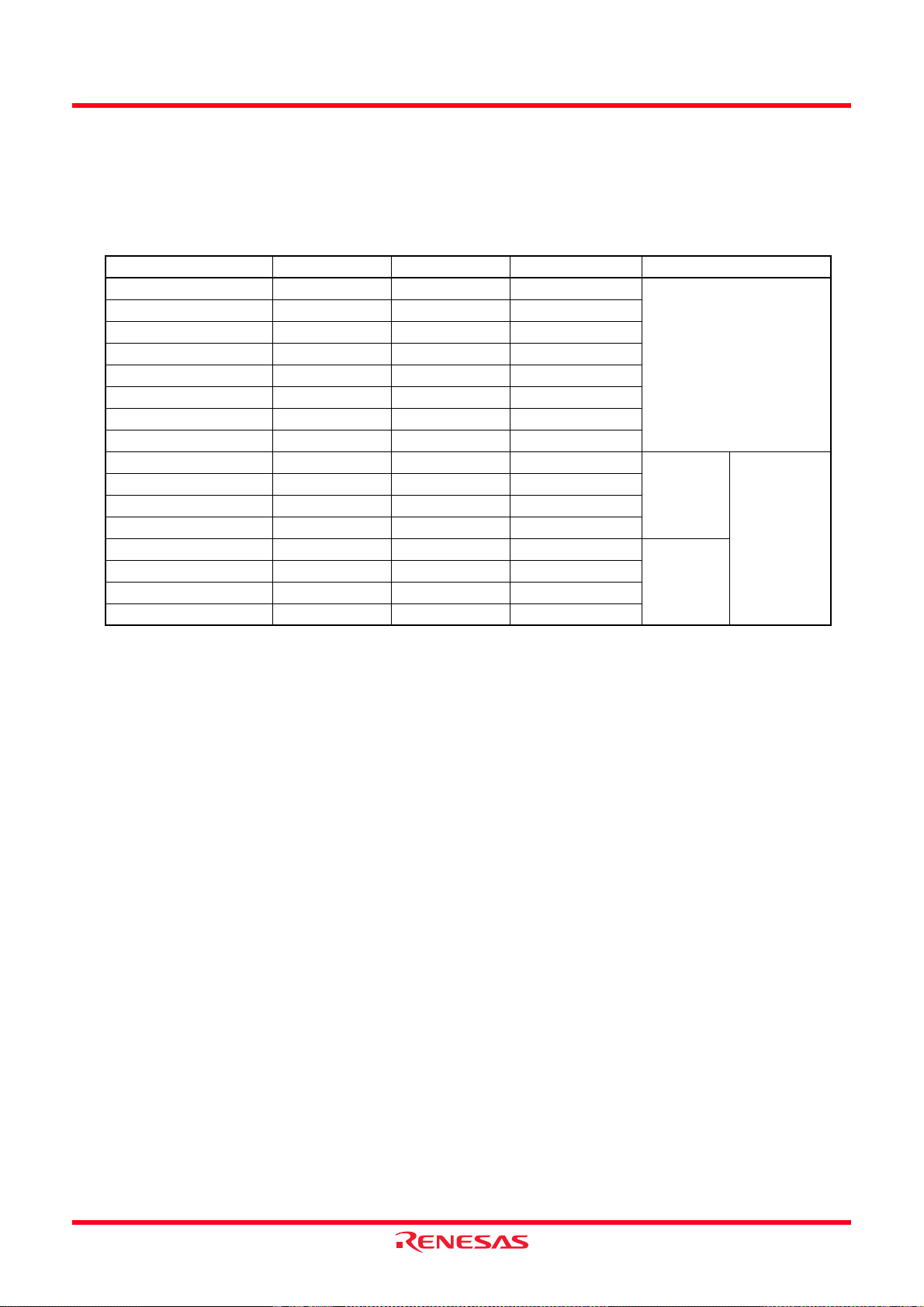

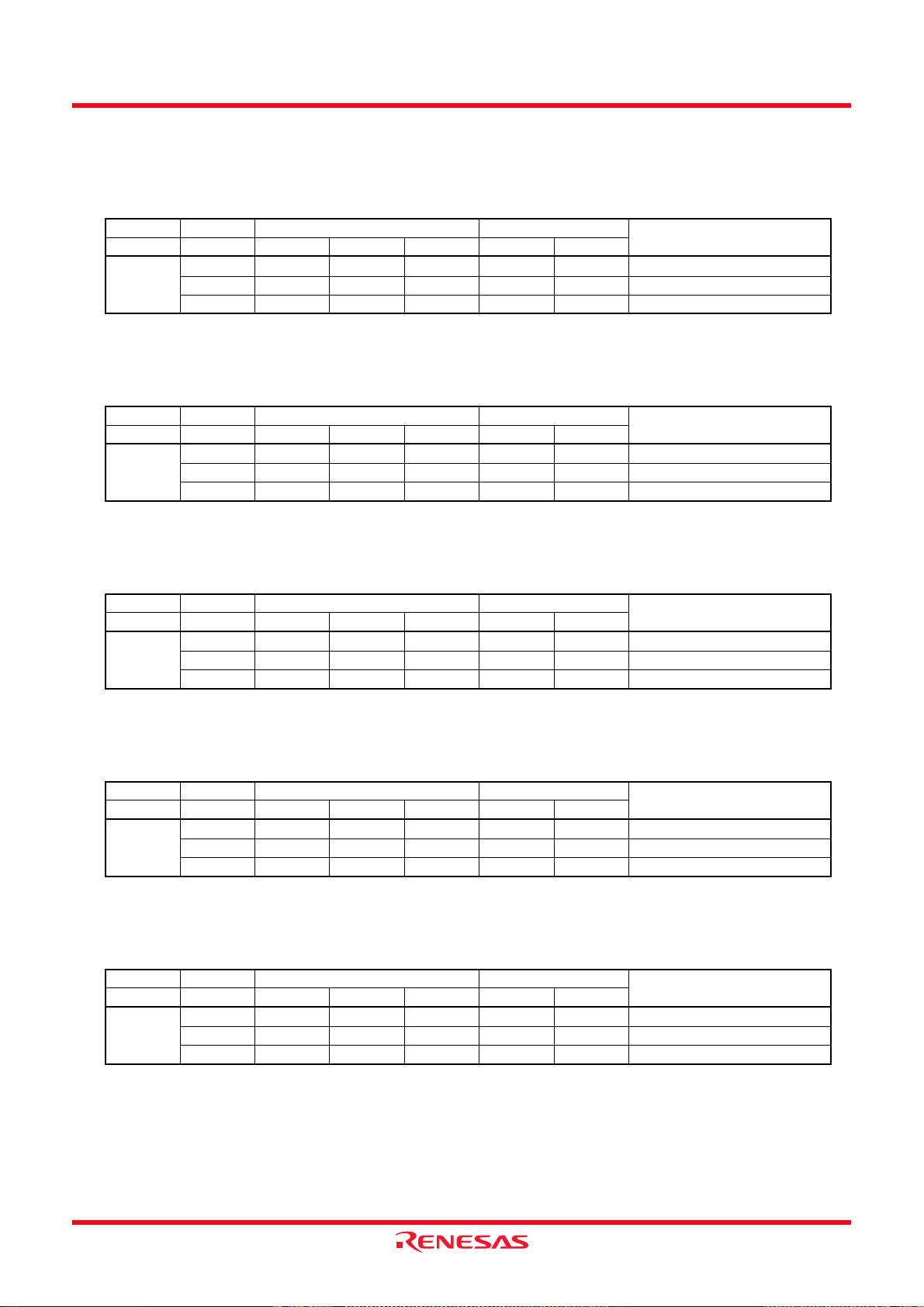

SFR Page Reference

Address Register Symbol Page

0000h

0001h

0002h

0003h

0004h Processor Mode Register 0 PM0 93

0005h Processor Mode Register 1 PM1 93

0006h System Clock Control Registe r 0 CM0 99

0007h System Clock Control Registe r 1 CM1 100

0008h Module Operation Enable Register MSTCR 201, 253,

0009h

000Ah Protect Register PRCR 124

000Bh

000Ch Oscillation Stop Detection Register OCD 101

000Dh Watchdog Timer Reset Register WDTR 154

000Eh Watchdog Timer Start Register WDTS 154

000Fh Watchdog Timer Control Register WDC 154

0010h Address Match Interrupt Register 0 RMAD0 146

0011h

0012h

0013h Address Match Interrupt Enable Register AIER 146

0014h Address Match Interrupt Register 1 RMAD1 146

0015h

0016h

0017h

0018h

0019h

001Ah

001Bh

001Ch Count Source Protection Mode Register CSPR 155

001Dh

001Eh

001Fh

0020h

0021h

0022h

0023h High-Speed On-Chip Oscillator Control Register 0 FRA0 102

0024h High-Speed On-Chip Oscillator Control Register 1 FRA1 102

0025h High-Speed On-Chip Oscillator Control Register 2 FRA2 103

0026h

0027h

0028h Clock Prescaler Reset Flag CPSRF 104

0029h

002Ah

002Bh High-Speed On-Chip Oscillator Control Register 6 FRA6 103

002Ch High-Speed On-Chip Oscillator Control Register 7 FRA7 103

002Dh

002Eh

002Fh

0030h

0031h Voltage Detection Register 1 VCA1 43

0032h Voltage Detection Register 2 VCA2 43, 104

0033h

0034h

0035h

0036h Voltage Monitor 1 Circuit Control Register VW1C 45

0037h Voltage Monitor 2 Circuit Control Register VW2C 46

0038h Voltage Monitor 0 Circuit Control Register VW0C 44

0039h

003Ah

003Bh

003Ch

003Dh

003Eh

003Fh

NOTE:

1. The blank regions are reserved. Do not access locations in these

268, 286,

300, 311,

326, 399,

regions.

429

Address Register Symbol Page

0040h

0041h

0042h

0043h

0044h

0045h

0046h

0047h Timer RC Interrupt Control Register TRCIC 131

0048h Timer RD0 Interrupt Control Register TRD0IC 131

0049h Timer RD1 Interrupt Control Register TRD1IC 131

004Ah Timer RE Interrupt Control Register TREIC 130

004Bh UART2 Transmit Interrupt Control Register S2TIC 130

004Ch UART2 Receive Interrupt Control Register S2RIC 130

004Dh Key Input Interrupt Control Register KUPIC 130

004Eh

004Fh SSU/IIC Interrupt Control Register SSUIC/IICIC 131

0050h Compare 1 Interrupt Control Register CMP1IC 130

0051h UART0 Transmit Interrupt Control Register S0TIC 130

0052h UART0 Receive Interrupt Control Register S0RIC 130

0053h UART1 Transmit Interrupt Control Register S1TIC 130

0054h UART1 Receive Interrupt Control Register S1RIC 130

0055h INT2 Interrupt Control Register INT2IC 132

0056h Timer RA Interrupt Control Register TRAIC 130

0057h

0058h Timer RB Interrupt Control Register TRBIC 130

0059h INT1 Interrupt Control Register INT1IC 132

005Ah INT3 Interrupt Control Register INT3IC 132

005Bh Timer RF Interrupt Control Register TRFIC 130

005Ch Compare 0 Interrupt Control Register CMP0IC 130

005Dh INT0 Interrupt Control Register INT0IC 132

005Eh A/D Conversion Interrupt Control Register ADIC 130

005Fh Capture Interrupt Control Register CAPIC 130

0060h

0061h

0062h

0063h

0064h

0065h

0066h

0067h

0068h

0069h

006Ah

006Bh

006Ch

006Dh

006Eh

006Fh

0070h

0071h

0072h

0073h

0074h

0075h

0076h

0077h

0078h

0079h

007Ah

007Bh

007Ch

007Dh

007Eh

007Fh

B - 1

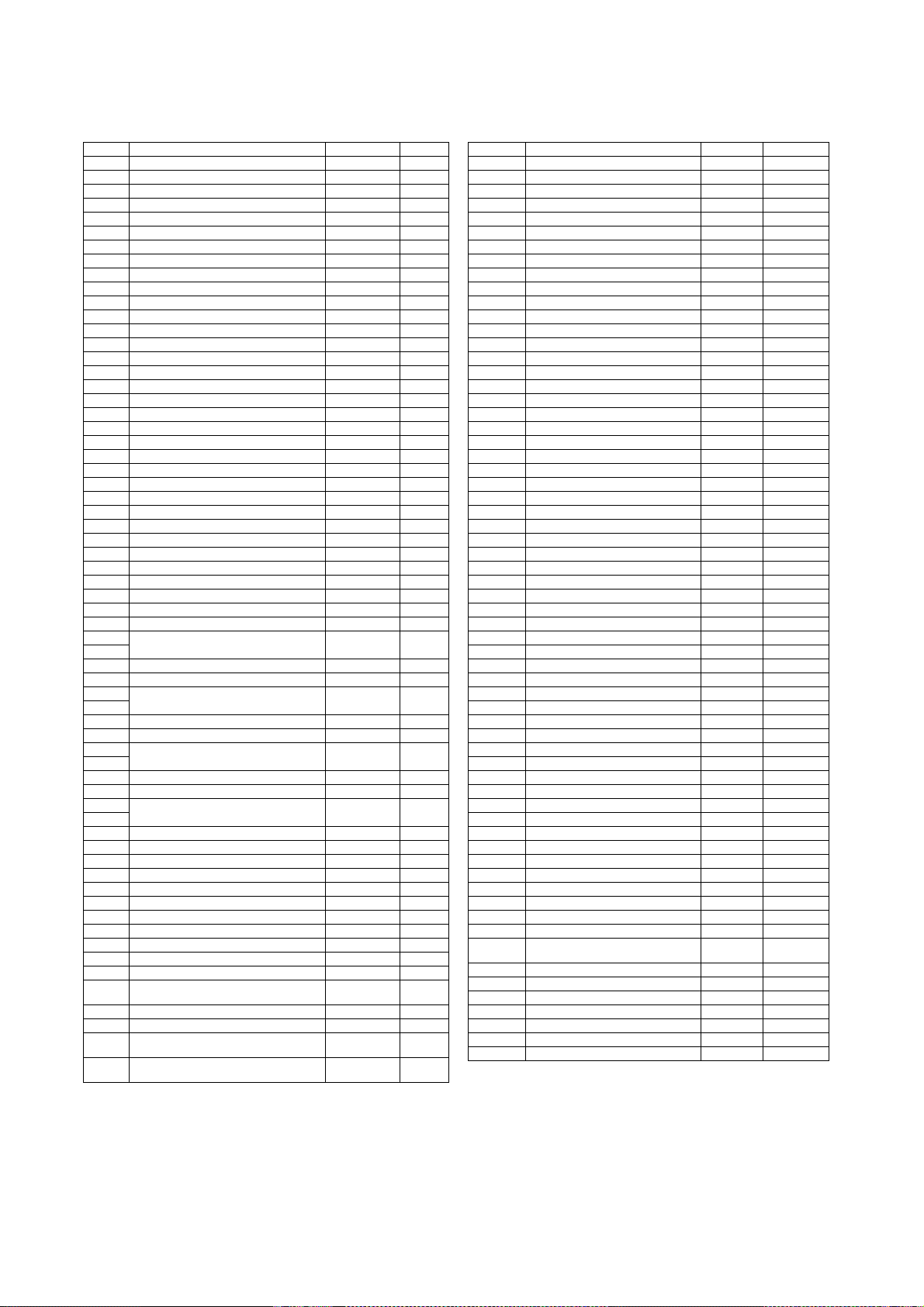

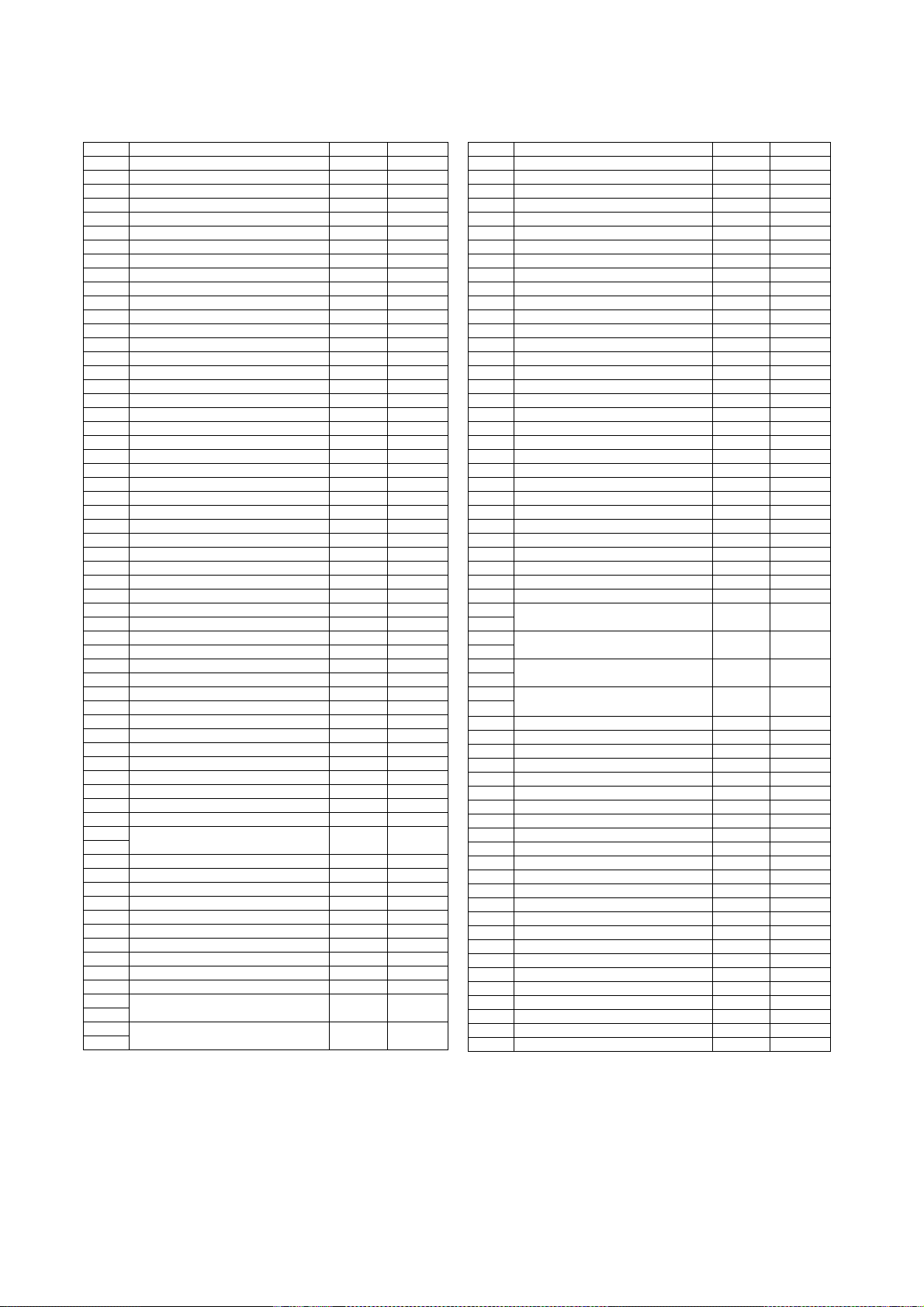

Page 16

Address Register Symbol Page

0080h

0081h

0082h

0083h

0084h

0085h

0086h

0087h

0088h

0089h

008Ah

008Bh

008Ch

008Dh

008Eh

008Fh

0090h

0091h

0092h

0093h

0094h

0095h

0096h

0097h

0098h

0099h

009Ah

009Bh

009Ch

009Dh

009Eh

009Fh

00A0h UART0 Transmit/Receive Mode Register U0MR 380

00A1h UART0 Bit Rate Register U0BRG 380

00A2h UART0 Transmit Buffer Register U0TB 381

00A3h

00A4h UART0 Transmit / Receive Control Register 0 U0C0 381

00A5h UART0 Transmit / Receive Control Register 1 U0C1 382

00A6h UART0 Receive Buffer Register U0RB 382

00A7h

00A8h UART1 Transmit/Receive Mode Register U1MR 380

00A9h UART1 Bit Rate Register U1BRG 380

00AAh UART1 Transmit Buffer Register U1TB 381

00ABh

00ACh UART1 Transmit/Receive Control Register 0 U1C0 381

00ADh UART1 Transmit/Receive Control Register 1 U1C1 382

00AEh UART1 Receive Buffer Register U1RB 382

00AFh

00B0h

00B1h

00B2h

00B3h

00B4h

00B5h

00B6h

00B7h

SS Control Register H / IIC bus Control Register 1

00B8h

00B9h

SS Control Register L / IIC bus Control Register 2

00BAh SS Mode Register / IIC bus Mode Register SSMR/ICMR 402, 432

00BBh SS Enable Register / IIC bus Interr upt Enable

Register

00BCh SS Status Register / IIC bus Status Register SSSR/ICSR 404, 434

00BDh SS Mode Register 2 / Slave Address Register SSMR2/SAR 405, 435

00BEh SS Transmit Data Register/IIC Bus Transmit

Data Register

00BFh SS Receive Data Register/IIC Bus Receive

Data Register

SSCRH/ICCR1 400, 430

SSCRL/ICCR2 401, 431

SSER/ICIER 403, 433

SSTDR/ICDRT 406, 435

SSRDR/ICDRR 406, 436

NOTE:

1. The blank regions are reserved. Do not access locations in these

regions.

Address Register Symbol Page

00C0h

00C1h

00C2h

00C3h

00C4h

00C5h

00C6h

00C7h

00C8h

00C9h

00CAh

00CBh

00CCh

00CDh

00CEh

00CFh

00D0h

00D1h

00D2h

00D3h

00D4h

00D5h

00D6h

00D7h

00D8h D/A Register 0 DA0 494

00D9h

00DAh D/A Register 1 DA1 494

00DBh

00DCh D/A Control Register DACON 494

00DDh

00DEh

00DFh

00E0h Port P0 Register P0 68

00E1h Port P1 Register P1 68

00E2h Port P0 Direction Register PD0 67

00E3h Port P1 Direction Register PD1 67

00E4h Port P2 Register P2 68

00E5h Port P3 Register P3 68

00E6h Port P2 Direction Register PD2 67

00E7h Port P3 Direction Register PD3 67

00E8h Port P4 Register P4 68

00E9h Port P5 Register P5 68

00EAh Port P4 Direction Register PD4 67

00EBh Port P5 Direction Register PD5 67

00ECh Port P6 Register P6 68

00EDh

00EEh Port P6 Direction Register PD6 67

00EFh

00F0h

00F1h

00F2h

00F3h

00F4h Port P2 Drive Capacity Control Register P2DRR 69

00F5h UART1 Function Select Register U1SR 383

00F6h

00F7h

00F8h Port Mode Register PMR 69, 139, 383,

00F9h External Input Enable Register INTEN 140

00FAh INT Input Filter Select Register INTF 141

00FBh Key Input Enable Register KIEN 144

00FCh Pull-Up Control Register 0 PUR0 70

00FDh Pull-Up Control Register 1 PUR1 70

00FEh

00FFh

406, 436

B - 2

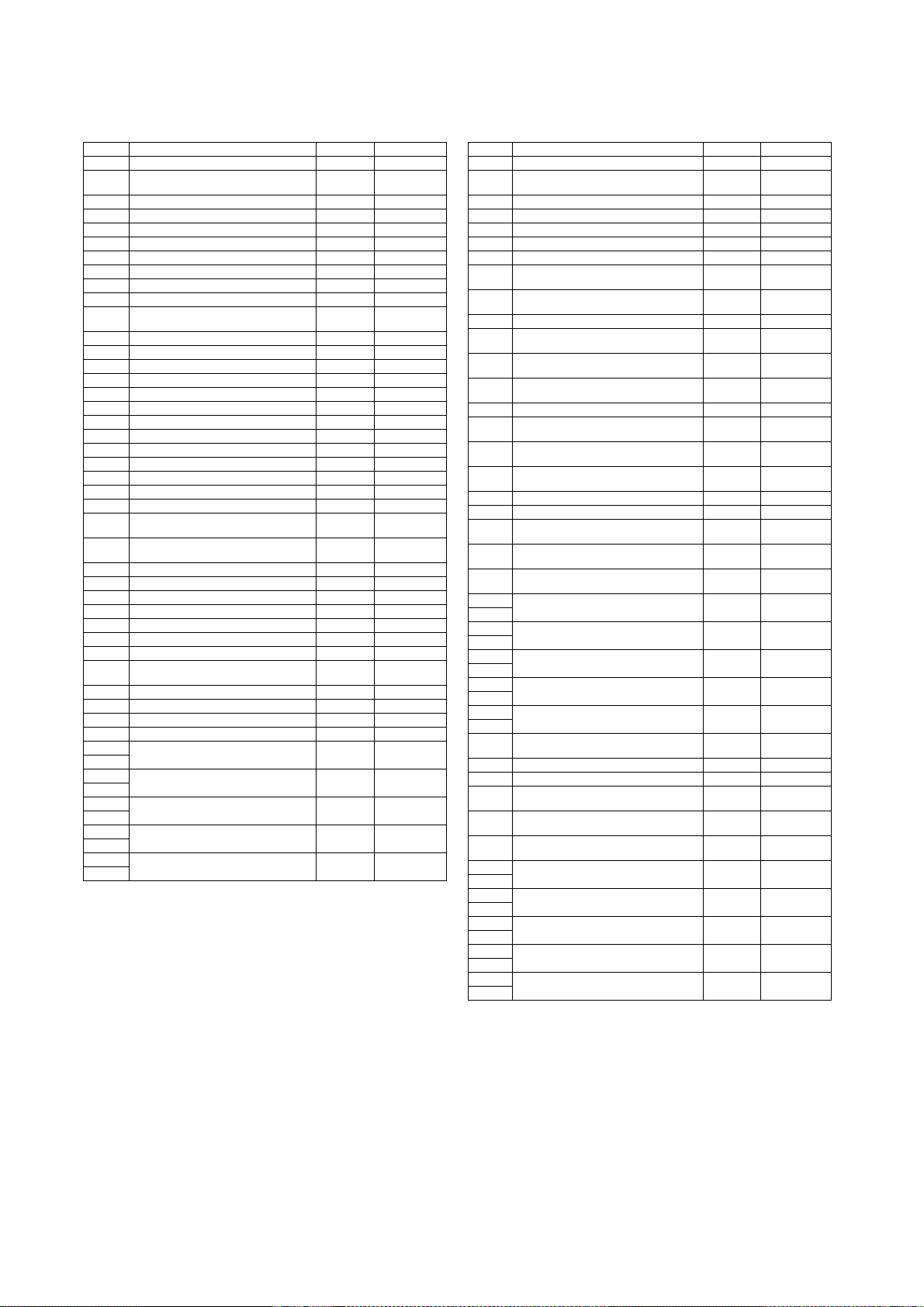

Page 17

Address Register Symbol Page

0100h Timer RA Control Register TRACR 162

0101h Timer RA I/O Control Register TRAIOC 162, 164, 167,

0102h Timer RA Mode Register TRAMR 163

0103h Timer RA Prescaler Register TRAPRE 163

0104h Timer RA Register TRA 163

0105h LIN Control Register 2 LINCR2 462

0106h LIN Control Register LINCR 462

0107h LIN Status Register LINST 463

0108h Timer RB Control Register TRBCR 178

0109h Timer RB One-Shot Control Register TRBOCR 178

010Ah Timer RB I/O Control Register TRBIOC 179, 181, 185,

010Bh Timer RB Mode Register TRBMR 179

010Ch Timer RB Prescaler Register TRBPRE 180

010Dh Timer RB Secondary Register TRBSC 180

010Eh Timer RB Primary Register TRBPR 180

010Fh

0110h

0111h

0112h

0113h

0114h

0115h

0116h

0117h

0118h Timer RE Second Data Register / Counter

Data Register

0119h Timer RE Minute Data Register / Compare

Data Register

011Ah Timer RE Hour Data Register TREHR 350

011Bh Timer RE Day of Week Data Register TREWK 350

011Ch Timer RE Control Register 1 TRECR1 351, 358

011Dh Timer RE Control Register 2 TRECR2 352, 358

011Eh Timer RE Clock Source Select Register TRECSR 353, 359

011Fh

0120h Timer RC Mode Register TRCMR 201

0121h Timer RC Control Register 1 TRCCR1 202, 225, 229,

0122h Timer RC Interrupt Enable Register TRCIER 203

0123h Timer RC Status Register TRCSR 204

0124h Timer RC I/O Control Register 0 TRCIOR0 209, 218, 223

0125h Timer RC I/O Control Register 1 TRCIOR1 209, 219, 224

0126h Timer RC Counter TRC 205

0127h

0128h Timer RC General Register A TRCGRA 205

0129h

012Ah Timer RC General Register B TRCGRB 205

012Bh

012Ch Timer RC General Register C TRCGRC 205

012Dh

012Eh Timer RC General Register D TRCGRD 205

012Fh

NOTE:

1. The blank regions are reserved. Do not access locations in these

regions.

TRESEC 349, 357

TREMIN 349, 357

169, 171, 174

187, 192

234

Address Register Symbol Page

0130h Timer RC Control Register 2 TRCCR2 206

0131h Timer RC Digital Filter Function Select

Register

0132h Timer RC Output Master Enable Register TRCOER 208

0133h

0134h

0135h

0136h

0137h Timer RD Start Register TRDSTR 254, 269, 287,

0138h Timer RD Mode Register TRDMR 254, 269, 287,

0139h Timer RD PWM Mode Register TRDPMR 255, 270, 288

013Ah Timer RD Function Control Register TRDFCR 256, 271, 289,

013Bh Timer RD Output Master En able Register 1 TRDOER1 272, 290, 303,

013Ch Timer RD Ou tput Master Enable Register 2 TRDOER2 2 72, 290, 303,

013Dh Timer RD Output Control Register TRDOCR 273, 291, 331

013Eh Timer RD Digital Filter Function Select

Register 0

013Fh Timer RD Digital Filter Function Select

Register 1

0140h Timer RD Control Register 0 TRDCR0 258, 274, 291,

0141h Timer RD I/O Control Register A0 TRDIORA0 259, 275

0142h Timer RD I/O Control Register C0 TRDIORC0 260, 276

0143h Timer RD Status Register 0 TRDSR0 261, 277, 292,

0144h Timer RD Interrupt Enable Register 0 TRDIER0 262, 278, 293,

0145h Timer RD PWM Mode Output Level Control

Register 0

0146h Timer RD Counter 0 TRD0 262, 279, 294,

0147h

0148h Timer RD General Register A0 TRDGRA0 263, 279, 295,

0149h

014Ah Timer RD General Register B0 TRDGRB0 263, 279, 295,

014Bh

014Ch Timer RD General Register C0 TRDGRC0 263, 279, 295,

014Dh

014Eh Timer RD General Register D0 TRDGRD0 263, 279, 295,

014Fh

0150h Timer RD Control Register 1 TRDCR1 258, 274, 291,

0151h Timer RD I/O Control Register A1 TRDIORA1 259, 275

0152h Timer RD I/O Control Register C1 TRDIORC1 260, 276

0153h Timer RD Status Register 1 TRDSR1 261, 277, 292,

0154h Timer RD Interrupt Enable Register 1 TRDIER1 262, 278, 293,

0155h Timer RD PWM Mode Output Level Control

Register 1

0156h Timer RD Counter 1 TRD1 262, 279, 294,

0157h

0158h Timer RD General Register A1 TRDGRA1 263, 279, 295,

0159h

015Ah Timer RD General Register B1 TRDGRB1 263, 279, 295,

015Bh

015Ch Timer RD General Register C1 TRDGRC1 263, 279, 295,

015Dh

015Eh Timer RD General Register D1 TRDGRD1 263, 279, 295,

015Fh

TRCDF 207

301, 312, 327

301, 313, 328

302, 314, 329

315, 330

315, 330

TRDDF0 257

TRDDF1 257

304, 316, 332

305, 317, 333

306, 318, 334

TRDPOCR0 294

306, 319, 334

307, 319, 335

307, 319, 335

307, 335

307, 319, 335

316

305, 317, 333

306, 318, 334

TRDPOCR1 294

319

307, 319, 335

307, 319, 335

307, 319, 335

307, 319, 335

B - 3

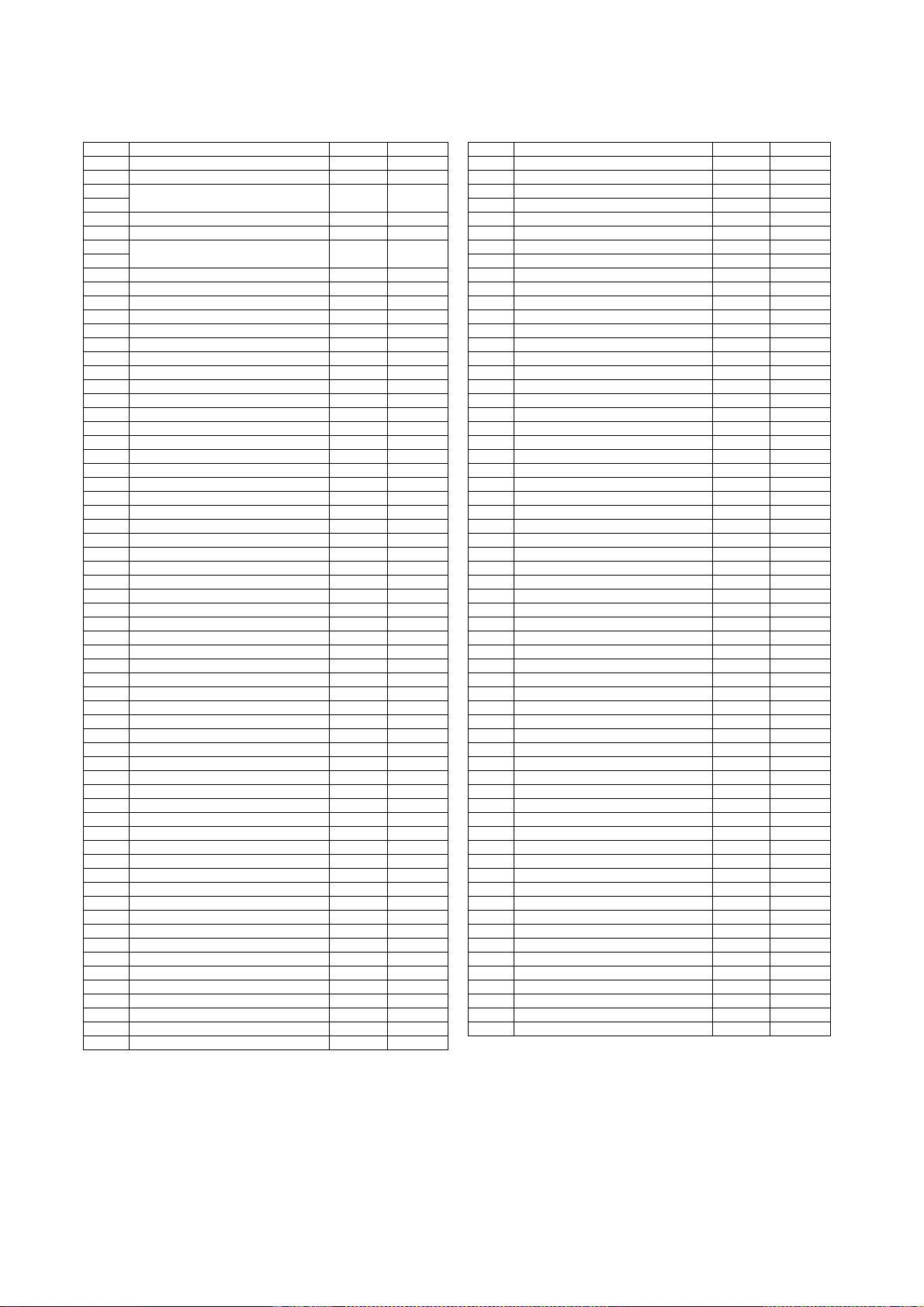

Page 18

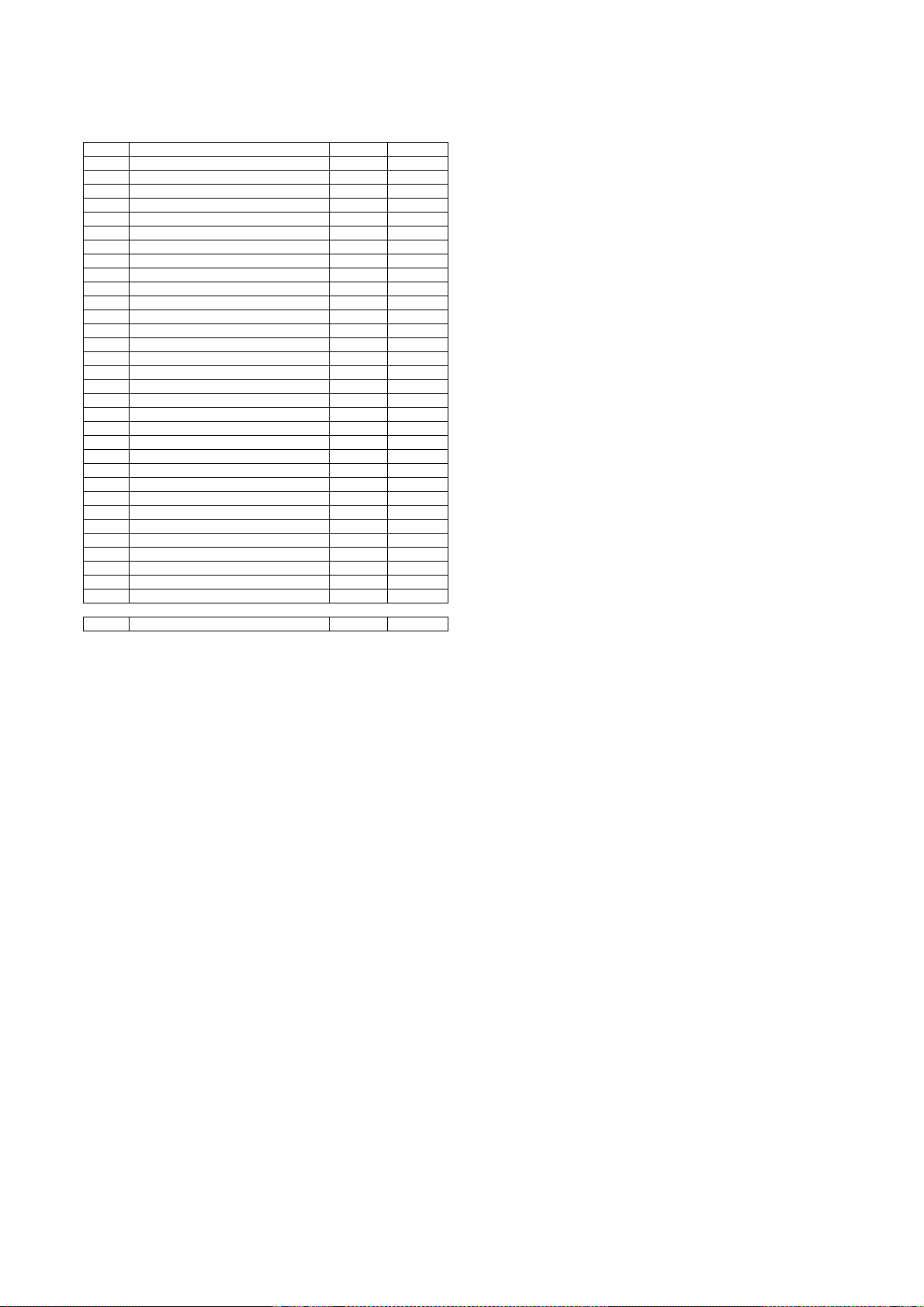

Address Register Symbol Page

0160h UART2 Transmit/Receive Mode Register U2MR 380

0161h UART2 Bit Rate Register U2BRG 380

0162h UART2 Transmit Buffer Registe r U2TB 381

0163h

0164h UART2 Transmit/Receive Control Register 0 U2C0 381

0165h UART2 Transmit/Receive Control Register 1 U2C1 382

0166h UART2 Receive Buffer Register U2RB 382

0167h

0168h

0169h

016Ah

016Bh

016Ch

016Dh

016Eh

016Fh

0170h

0171h

0172h

0173h

0174h

0175h

0176h

0177h

0178h

0179h

017Ah

017Bh

017Ch

017Dh

017Eh

017Fh

0180h

0181h

0182h

0183h

0184h

0185h

0186h

0187h

0188h

0189h

018Ah

018Bh

018Ch

018Dh

018Eh

018Fh

0190h

0191h

0192h

0193h

0194h

0195h

0196h

0197h

0198h

0199h

019Ah

019Bh

019Ch

019Dh

019Eh

019Fh

NOTE:

1. The blank regions are reserved. Do not access locations in these

regions.

Address Register Symbol Page

01A0h

01A1h

01A2h

01A3h

01A4h

01A5h

01A6h

01A7h

01A8h

01A9h

01AAh

01ABh

01ACh

01ADh

01AEh

01AFh

01B0h

01B1h

01B2h

01B3h Flash Memory Control Register 4 FMR4 506

01B4h

01B5h Flash Memory Control Register 1 FMR1 505

01B6h

01B7h Flash Memory Control Register 0 FMR0 504

01B8h

01B9h

01BAh

01BBh

01BCh

01BDh

01BEh

01C0h

01C1h

01C2h

01C3h

01C4h

01C5h

01C6h

01C7h

01C8h

01C9h

01CAh

01CBh

01CCh

01CDh

01CEh

01CFh

01D0h

01D1h

01D2h

01D3h

01D4h

01D5h

01D6h

01D7h

01D8h

01D9h

01DAh

01DBh

01DCh

01DDh

01DEh

01DFh

B - 4

Page 19

Address Register Symbol Page

01E0h

01E1h

01E2h

01E3h

01E4h

01E5h

01E6h

01E7h

01E8h

01E9h

01EAh

01EBh

01ECh

01EDh

01EEh

01EFh

01F0h

01F1h

01F2h

01F3h

01F4h

01F5h

01F6h

01F7h

01F8h

01F9h

01FAh

01FBh

01FCh

01FDh

01FEh

01FFh

0200h

0201h

0202h

0203h

0204h

0205h

0206h

0207h

0208h

0209h

020Ah

020Bh

020Ch

020Dh

020Eh

020Fh

0210h

0211h

0212h

0213h

0214h

0215h

0216h

0217h

0218h

0219h

021Ah

021Bh

021Ch

021Dh

021Eh

021Fh

NOTE:

1. The blank regions are reserved. Do not access locations in these

regions.

Address Register Symbol Page

0220h

0221h

0222h

0223h

0224h

0225h

0226h

0227h

0228h

0229h

022Ah

022Bh

022Ch

022Dh

022Eh

022Fh

0230h

0231h

0232h

0233h

0234h

0235h

0236h

0237h

0238h

0239h

023Ah

023Bh

023Ch

023Dh

023Eh

023Fh

0240h

0241h

0242h

0243h

0244h

0245h

0246h

0247h

0248h

0249h

024Ah

024Bh

024Ch

024Dh

024Eh

024Fh

0250h

0251h

0252h

0253h

0254h

0255h

0256h

0257h

0258h

0259h

025Ah

025Bh

025Ch

025Dh

025Eh

025Fh

B - 5

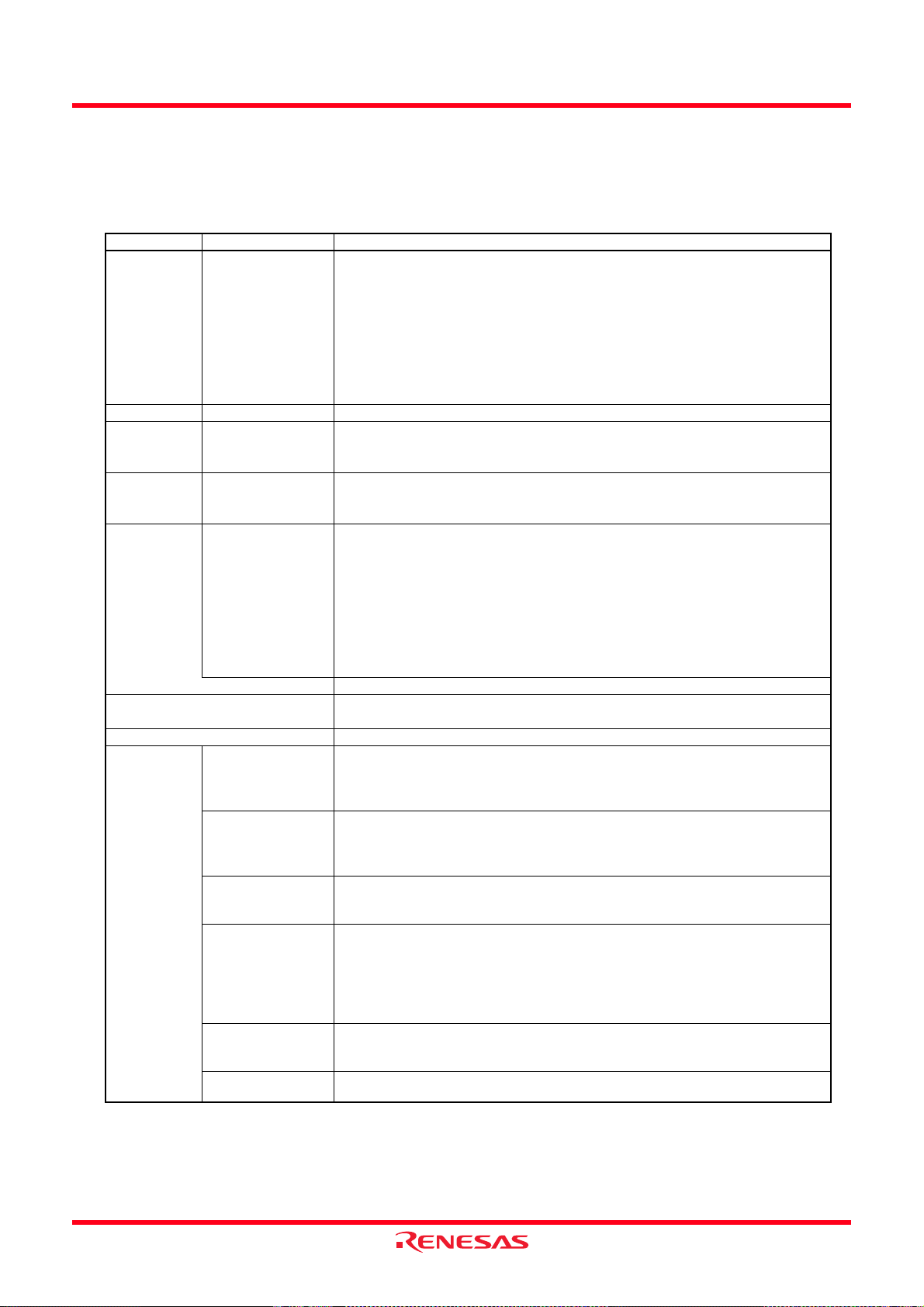

Page 20

Address Register Symbol Page

0260h

0261h

0262h

0263h

0264h

0265h

0266h

0267h

0268h

0269h

026Ah

026Bh

026Ch

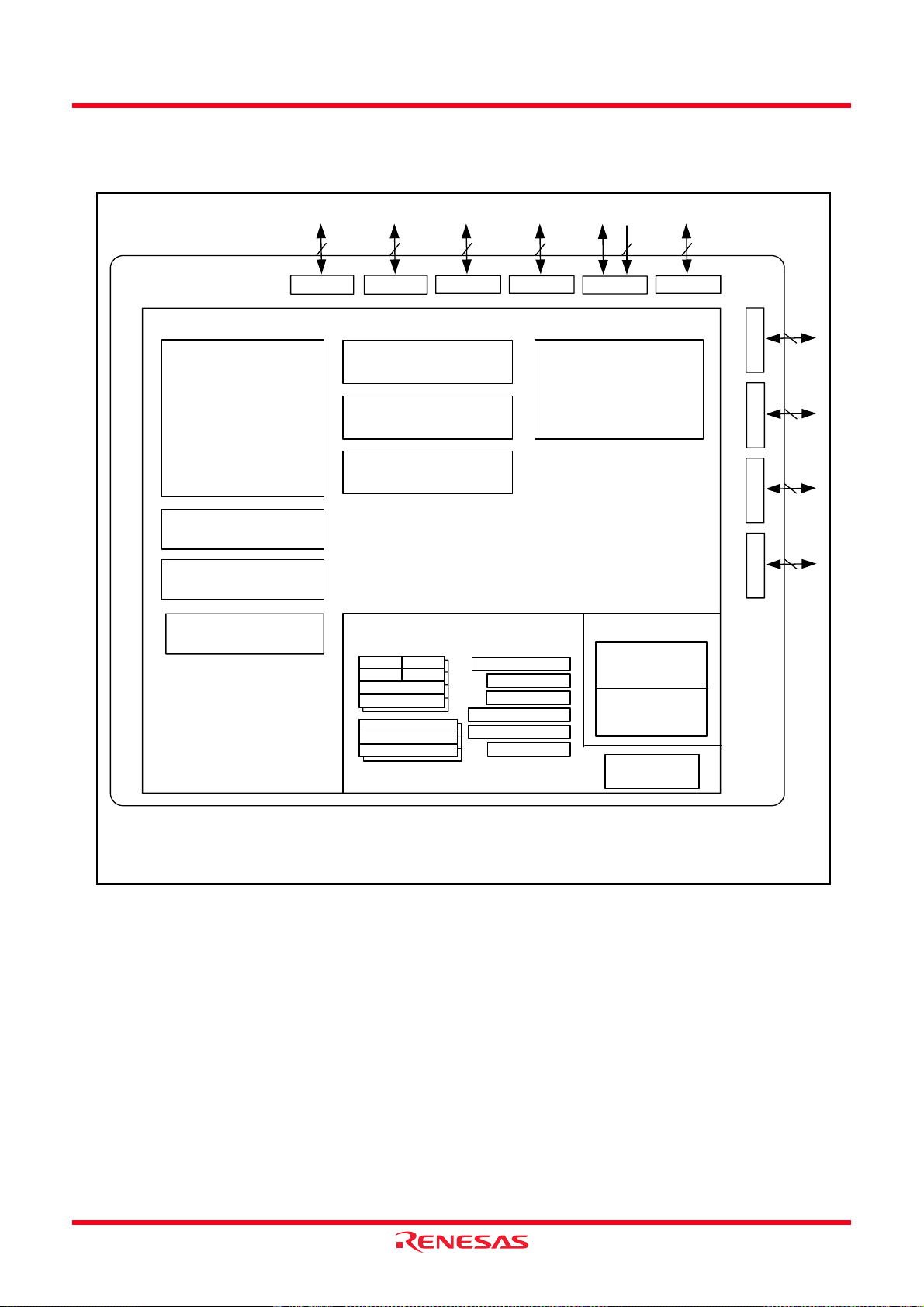

026Dh

026Eh

026Fh

0270h

0271h

0272h

0273h

0274h

0275h

0276h

0277h

0278h

0279h

027Ah

027Bh

027Ch

027Dh

027Eh

027Fh

0280h

0281h

0282h

0283h

0284h

0285h

0286h

0287h

0288h

0289h

028Ah

028Bh

028Ch

028Dh

028Eh

028Fh

0290h Timer RF Register TRF 366

0291h

0292h

0293h

0294h

0295h

0296h

0297h

0298h

0299h

029Ah Timer RF Control Register 0 TRFCR0 367

029Bh Timer RF Control Register 1 TRFCR1 368

029Ch Capture / Compare 0 Register TRFM0 366

029Dh

029Eh Compare 1 Register TRFM1 366

029Fh

NOTE:

1. The blank regions are reserved. Do not access locations in these

regions.

Address Register Symbol Page

02A0h

02A1h

02A2h

02A3h

02A4h

02A5h

02A6h

02A7h

02A8h

02A9h

02AAh

02ABh

02ACh

02ADh

02AEh

02AFh

02B0h

02B1h

02B2h

02B3h

02B4h

02B5h

02B6h

02B7h

02B8h

02B9h

02BAh

02BBh

02BCh

02BDh

02BEh

02BFh

02C0h A/D Register 0 AD0 477

02C1h

02C2h A/D Register 1 AD1 477

02C3h

02C4h A/D Register 2 AD2 477

02C5h

02C6h A/D Register 3 AD3 477

02C7h

02C8h

02C9h

02CAh

02CBh

02CCh

02CDh

02CEh

02CFh

02D0h

02D1h

02D2h

02D3h

02D4h A/D Control Register 2 ADCON2 477

02D5h

02D6h A/D Control Register 0 ADCON0 478

02D7h A/D Control Register 1 ADCON1 479

02D8h

02D9h

02DAh

02DBh

02DCh

02DDh

02DEh

02DFh

B - 6

Page 21

Address Register Symbol Page

02E0h Port P7 Direction Register PD7 67

02E1h

02E2h Port P7 Register P7 68

02E3h

02E4h Port P8 Direction Register PD8 67

02E5h Port P9 Direction Register PD9 67

02E6h Port P8 Register P8 68

02E7h Port P9 Register P9 68

02E8h

02E9h

02EAh

02EBh

02ECh

02EDh

02EEh

02EFh

02F0h

02F1h

02F2h

02F3h

02F4h

02F5h

02F6h

02F7h

02F8h

02F9h

02FAh

02FBh

02FCh Pull-Up Control Register 2 PUR2 70

02FDh

02FEh

02FFh Timer RF Output Control Register TRFOUT 368

FFFFh Option Function Select Register OFS 34, 155, 499

NOTE:

1. The blank regions are reserved. Do not access locations in these

regions.

B - 7

Page 22

R8C/2C Group, R8C/2D Group

REJ09B0339-0200

RENESAS MCU

1. Overview

1.1 Features

The R8C/2C Group and R8C/2D Group of single-chip MCUs incorporates the R8C/ Tiny Series CPU core,

employing sophisticated instructions for a high level of efficiency. With 1 Mbyte of address space, and it is capable

of executing instructions at high speed. In addition, the CPU core boasts a multiplier for high-speed operation

processing.

Power consumption is low, and the supported operating modes allow additional power control. These MCUs also

use an anti-noise configuration to reduce emissions of electromagnetic noise and are designed to withstand EMI.

Integration of many peripheral functions, including multifunction timer and serial interface, reduces the number of

system components.

Furthermore, the R8C/2D Group has on-chip data flash (1 KB × 2 blocks).

The difference between the R8C/2C Group and R8C/2D Group is only the presence or absence of data flash. Their

peripheral functions are the same.

1.1.1 Applications

Electronic household appliances, office equipment, audio equipment, consumer equipment, etc.

Rev.2.00

Dec 05, 2007

Rev.2.00 Dec 05, 2007 Page 1 of 585

REJ09B0339-0200

Page 23

R8C/2C Group, R8C/2D Group 1. Overview

1.1.2 Specifications

Tables 1.1 and 1.2 outlines the Specifications for R8C/2C Group and Tables 1.3 and 1.4 outlines the

Specifications for R8C/2D Group.

Table 1.1 Specifications for R8C/2C Group (1)

Item Function Specification

CPU Central processing

unit

Memory ROM, RAM Refer to Table 1.5 Product List for R8C/2C Group.

Power Supply

Voltage

Detection

I/O Ports Programmable I/O

Clock Clock generation

Interrupts • External: 5 sources, Internal: 23 sources, Software: 4 sources