Page 1

REJ09B0042-0600O

The revision list can be viewed directly by

clicking the title page.

The revision list summarizes the locations of

revisions and additions. Details should always

be checked by referring to the relevant text.

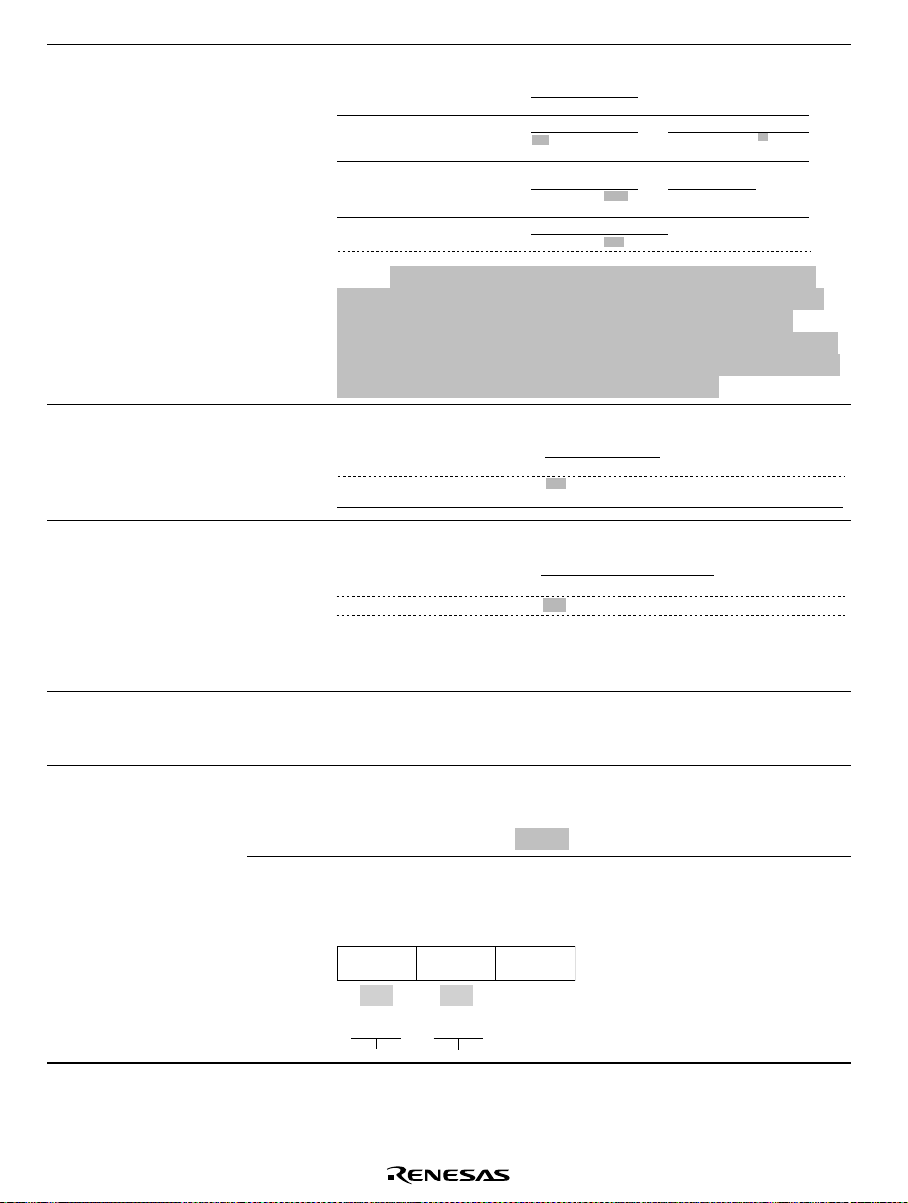

H8/38024, H8/38024S,

8

H8/38024F-ZTAT, H8/38124

Hardware Manual

Renesas 8-Bit Single-Chip Microcomputer

H8 Family/H8/300L Super Low Power Series

Group

Rev. 6.00

Revision Date: Aug 27, 2004

Page 2

Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and

more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas

Technology Corp. product best suited to the customer's application; they do not convey any license

under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or

a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or

circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and

algorithms represents information on products at the time of publication of these materials, and are

subject to change by Renesas Technology Corp. without notice due to product improvements or

other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or

an authorized Renesas Technology Corp. product distributor for the latest product information

before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising

from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means,

including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data,

diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total

system before making a final decision on the applicability of the information and products. Renesas

Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the

information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or

system that is used under circumstances in which human life is potentially at stake. Please contact

Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when

considering the use of a product contained herein for any specific purposes, such as apparatus or

systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in

whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must

be exported under a license from the Japanese government and cannot be imported into a country

other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the

country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products

contained therein.

Rev. 6.00, 08/04, page ii of xxx

Page 3

General Precautions on Handling of Product

1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are

used as test pins or to reduce noise. If something is connected to the NC pins, the

operation of the LSI is not guaranteed.

2. Trea t ment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins

are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfunction may occur.

3. Processing before Initialization

Note: When power is first supplied, the product’s state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the

chip and a low level is input on the reset pin. During the period where the states are

undefined, the register settings and the output state of each pin are also undefined. Design

your system so that it does not malfunction beca use of processing while it is in this

undefined state. For those products which have a reset function, reset the LSI immediately

after the power supply has been turned on.

4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers

may have been be allocated to these addresses. Do not access these registers; the system’s

operation is not guaranteed if they are accessed.

Rev. 6.00, 08/04, page iii of xxx

Page 4

Configuration of This Manual

This manual comprises the following items:

1. General Precautions on Handling of Product

2. Configuration of This Manual

3. Preface

4. Contents

5. Overview

6. Description of Functional Modules

• CPU and System-Control Modules

• On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the

module. However, the generic style includes the following items:

i) Feature

ii) Input/Output Pin

iii) Register Description

iv) Operation

v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section

includes notes in relation to the descr i ptions given, and usage notes are give n, as required, as the

final part of each section.

7. List of Registers

8. Electrical Characteristics

9. Appendix

• Product Codes, Package Dimensions, etc.

Rev. 6.00, 08/04, page iv of xxx

Page 5

Preface

The H8/38024 Group is a single-chip microcomputer built around the high-speed H8/300L CPU

and equipped with peripheral system functions on-chip. The H8/38024 Group incorporates

peripheral functions including ROM, RAM, timer, serial communications interface (SCI), 10-bit

PWM, A/D converter, LCD controller/driver, and I/O ports. It is a microcomputer allowing the

implementation of a sophisticated control system. Versions are available with types of internal

ROM: flash memory (F-ZTAT™

application products with a great deal of specification fluidity, and allows for rapid and flexible

response to contingencies arising between the initial stages of production and full-scale

production.

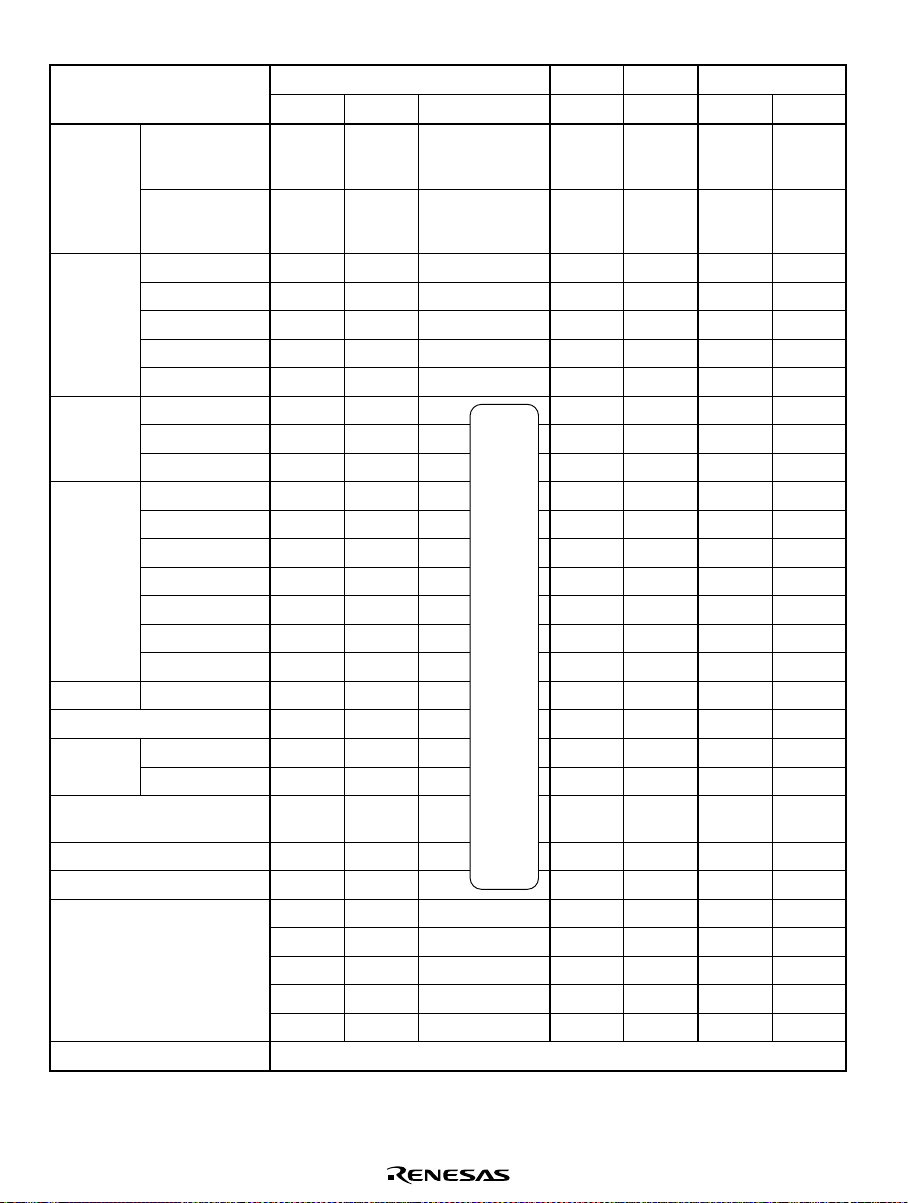

Below is a table listing the product specifications for each group.

Notes: 1. F-ZTAT is a trademark of Renesas Technology Corp.

2. ZTAT is a trademark of Renesas Technology Corp.

1

*

) and PROM (ZTAT™

2

*

). This makes it possible to design

Rev. 6.00, 08/04, page v of xxx

Page 6

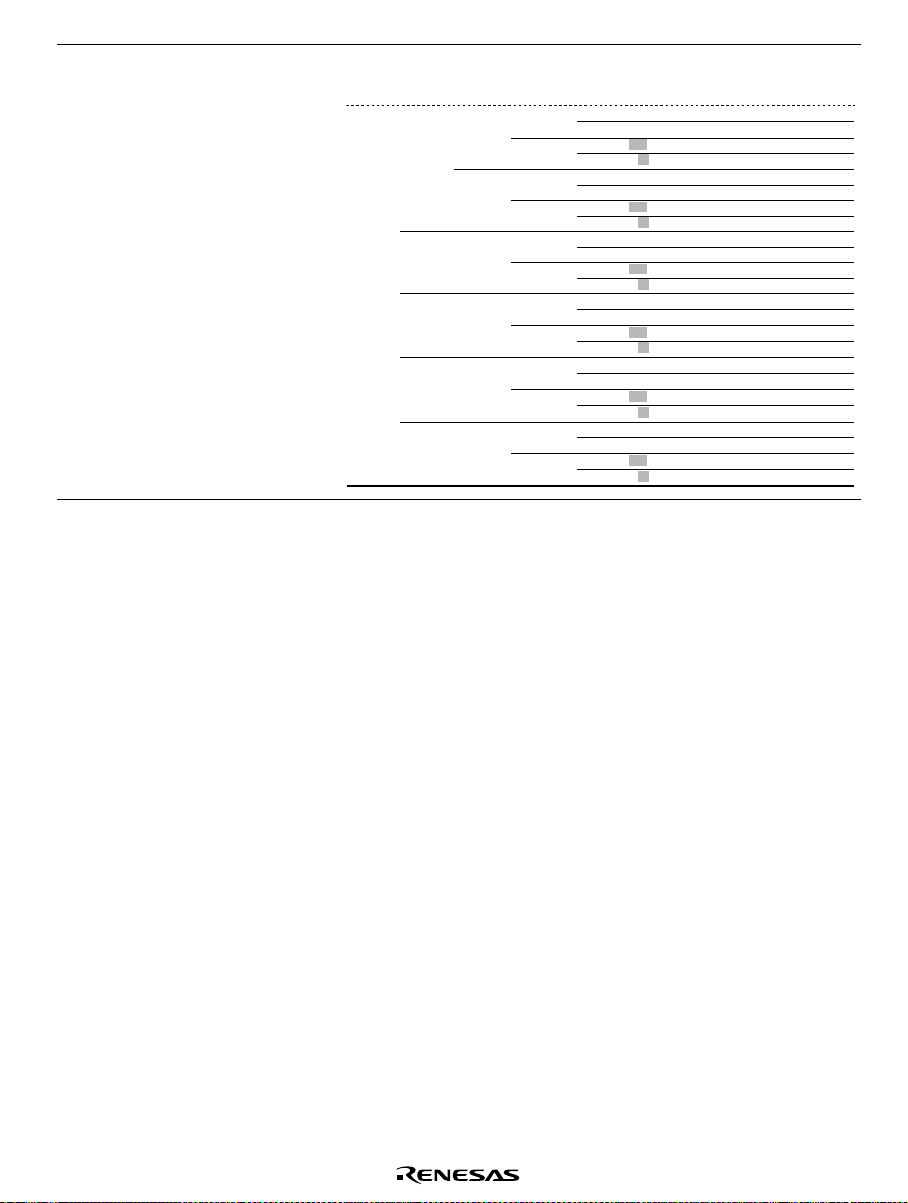

Specifications

Item

Memory ROM 32 Kbytes 8 Kbytes

RAM 1 Kbyte 512 bytes

Operating

voltage and

operating

frequency

I/O portsInput only 999 9999

Timers Clock (timer A) 1 1 1 1 1 1 1

SCI UART/Synchronous 8 × 18 × 18 × 18 × 18 × 18 × 18 × 1

A-D 10 × 8 10 × 8 10 × 8 10 × 8 10 × 8 10 × 8 10 × 8

LCD seg 32 32 32 32 32 32 32

External interrupt (internal

wakeup)

POR (power-on reset) — — — — — 1 1

LVD (low-voltage detecti on ci rc ui t) — — — — — 1 1

Package FP-80A FP-80A FP-80A FP-80A FP-80A FP-80A FP-80A

Operating temperature Standard specifications: –20 to 70°C, WTR: –40 to 85°C

4.5 to 5.5 V 16 MHz 16 MHz — — — 16 MHz 16 MHz

2.7 to 5.5 V 10 MHz 10 MHz — — — 16 MHz 16 MHz

1.8 to 5.5 V 4 MHz 4 MHz — — — — —

2.7 to 3.6 V — — 10 MHz 10 MHz 10 MHz — —

1.8 to 3.6 V — — — — 4 MHz — —

Output only 6 6 6 6 6 6 6

I/O 515151 51515050

Reload (timer C) 1 1 1 1 1 1 1

Compare (timer F) 1 1 1 1 1 1 1

Capture (timer G) 1 1 1 1 1 1 1

AEC 111 1111

WDT 1 1 1 1 1

WDT (discrete) 11

com 444 4444

ZTAT Mask Flash Flash Mask Flash Mask

13(8) 13(8) 13(8) 13(8) 13(8) 13(8) 13(8)

FP-80B FP-80B FP-80B FP-80B

TFP-80C TFP-80C TFP-80C TFP-80C TFP-80C TFP-80C TFP-80C

38024 38024R 38024S 38124

to

32 Kbytes

or

1 Kbyte

Chip Chip Chip Chip

32 Kbytes 32 Kbytes 8 Kbytes

to

32 Kbytes

1 Kbyte 1 Kbyte 512 bytes

or

1 Kbyte

Please

use R

version.

TLP85V TLP85V TLP85V

32 Kbytes 8 Kbytes

to

32 Kbytes

1 Kbyte 512 bytes

or

1 Kbyte

Rev. 6.00, 08/04, page vi of xxx

Page 7

Target Readers: This manual is designed for use by people who design application systems using

the H8/38024 Group, H8/38024S Group, H8/38024F-ZTAT, and H8/38124 Group.

To use this manual, basic knowledge of electric circuits, logic circuits and microcomputers is

required.

Purpose: This manual provides the information of the hardware functions and electrical

characteristics of the H8/38024 Group, H8/38024S Group, H8/38024F-ZTAT, and H8/38124

Group. The H8/300L Series Programming Manual contains detailed information of executable

instructions. Please read the Programming Manual together with this manual.

How to Use the Book:

• To understa nd gene ra l fu nc tio n s

→ Read the manual from the beginning.

The manual explains the CPU, system control functions, peripheral functions and electrical

characteristics in that order.

• To understanding CPU functions

→ Refer to the separate H8/300L Series Programming Manual.

Explanatory Note: Bit sequence: upper bit at left, and lower bit at right

List of Related Documents: The latest documents are available on our Web site. Please make

sure that you have the late st version.

(http://www.renesas.com/)

• User manual for H8/38024 Group

Name of Document Document No.

H8/38024 Group, H8/38024S Group, H8/38024F-ZTAT™,

H8/38124 Group Hardware Manual

H8/300L Series Programming Manual ADE-602-040

This manual

• User manual for development tools

Name of Document Document No.

H8S, H8/300 Series, C/C++ Compiler, Assembler, Optimizing Linkage

Editor User’s Manual

High-Performance Debugging Interface User’s Manual ADE-702-161A

High-Performance Embedded Workshop ADE-702-201A

ADE-702-247

• Application note

Name of Document Document No.

H8/300 Series, H8/300L Series software ADE-502-052

Rev. 6.00, 08/04, page vii of xxx

Page 8

Notes: The following limitations apply to H8/38024 and H8/38124 programming and debugging

when the on-chip emulator is used.

1. Pin 95 is not available because it is used exclusively by the on-chip emulator.

2. Pins 33, 34, and 35 are unavailable for use. In order to use these pins additional

hardware must be mounted on the user board.

3. The address range H'7000 to H'7FFF is used by the on-chip emulator and is unavailable

to the user.

4. The address range H'F780 to H'FB7F must not be accessed under any circumstances.

5. When the on-chip emulator is being used, pin 95 is I/O, pins 33 and 34 are input, and

pin 35 is output.

6. When using the on-chip emulator, pins OSC1 and OSC2 should be connected to an

oscillator, or an external clock should be supplied to pin OSC1, even if the on-chip

oscillator of the H8/38124 Group is selected.

Rev. 6.00, 08/04, page viii of xxx

Page 9

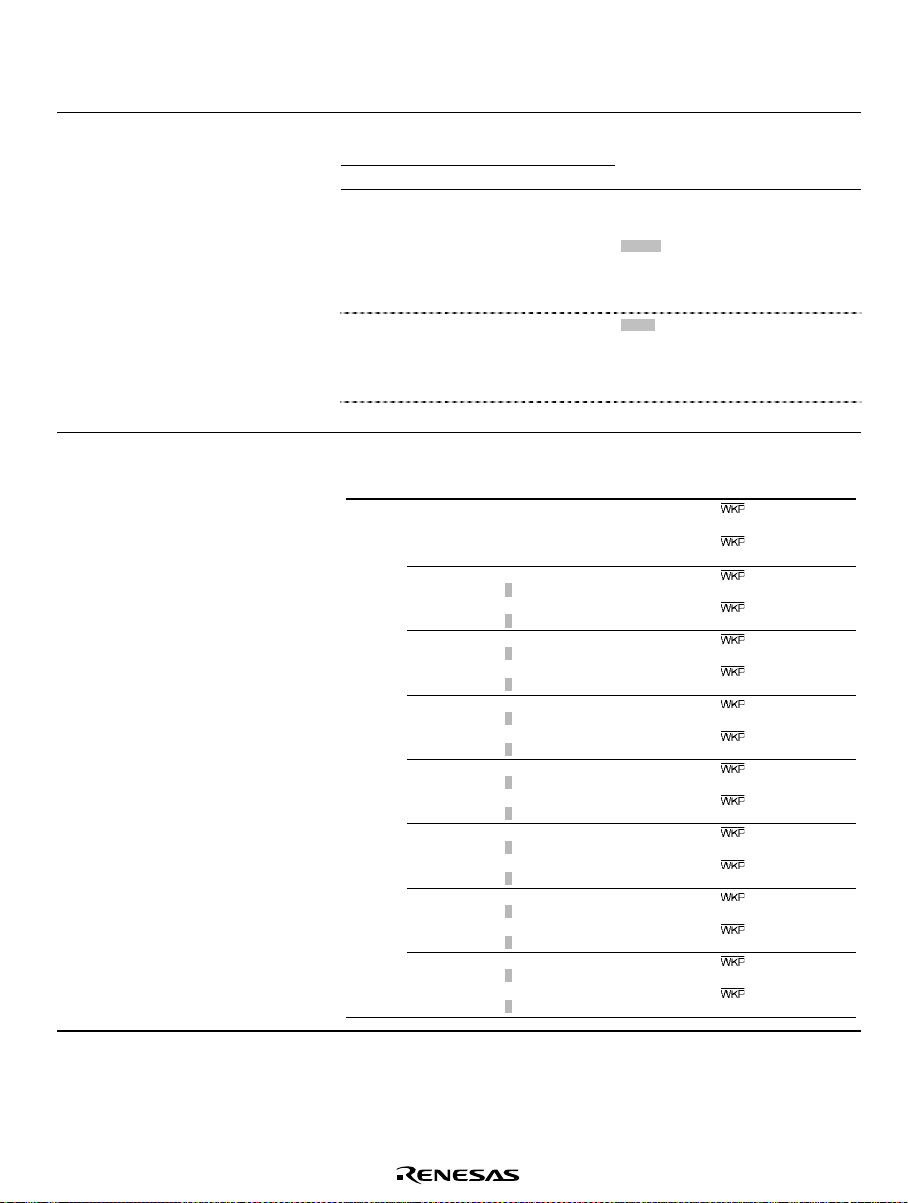

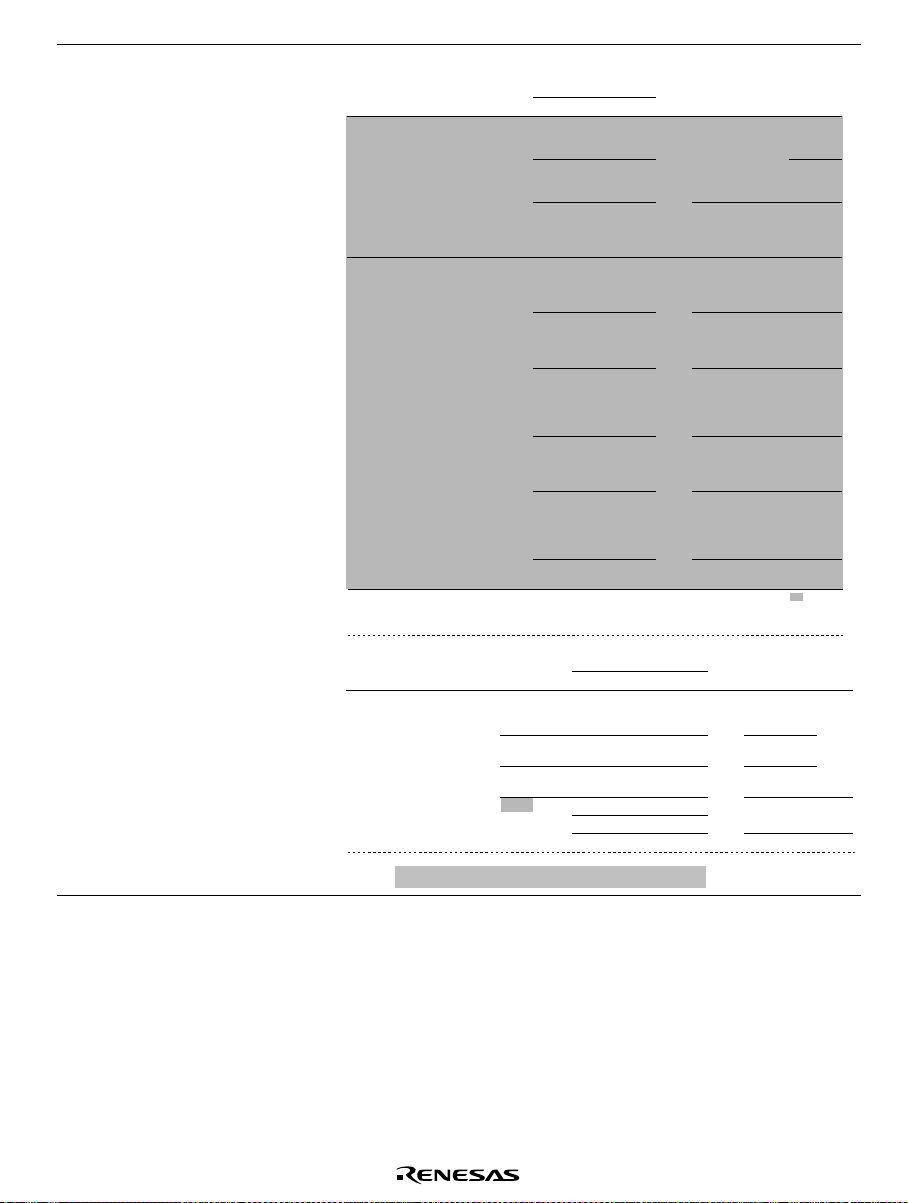

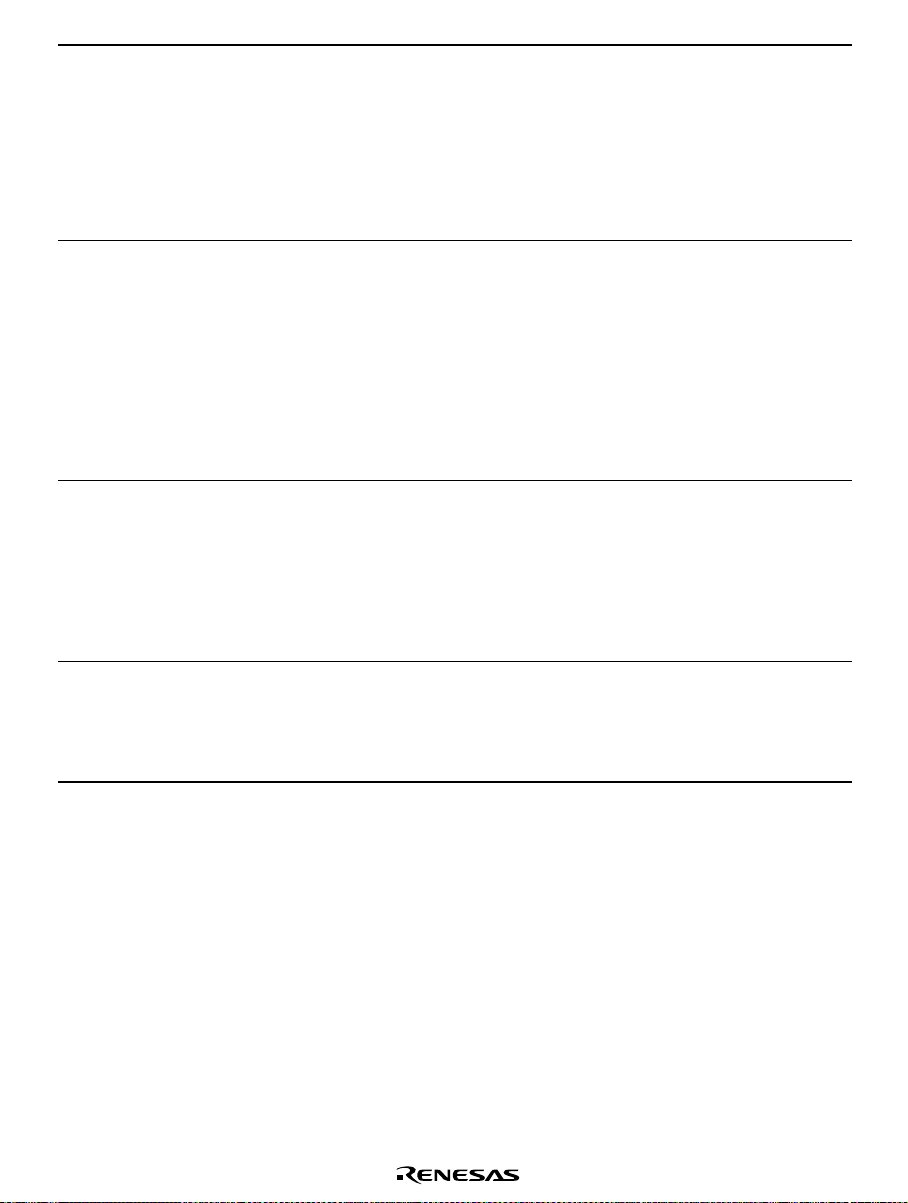

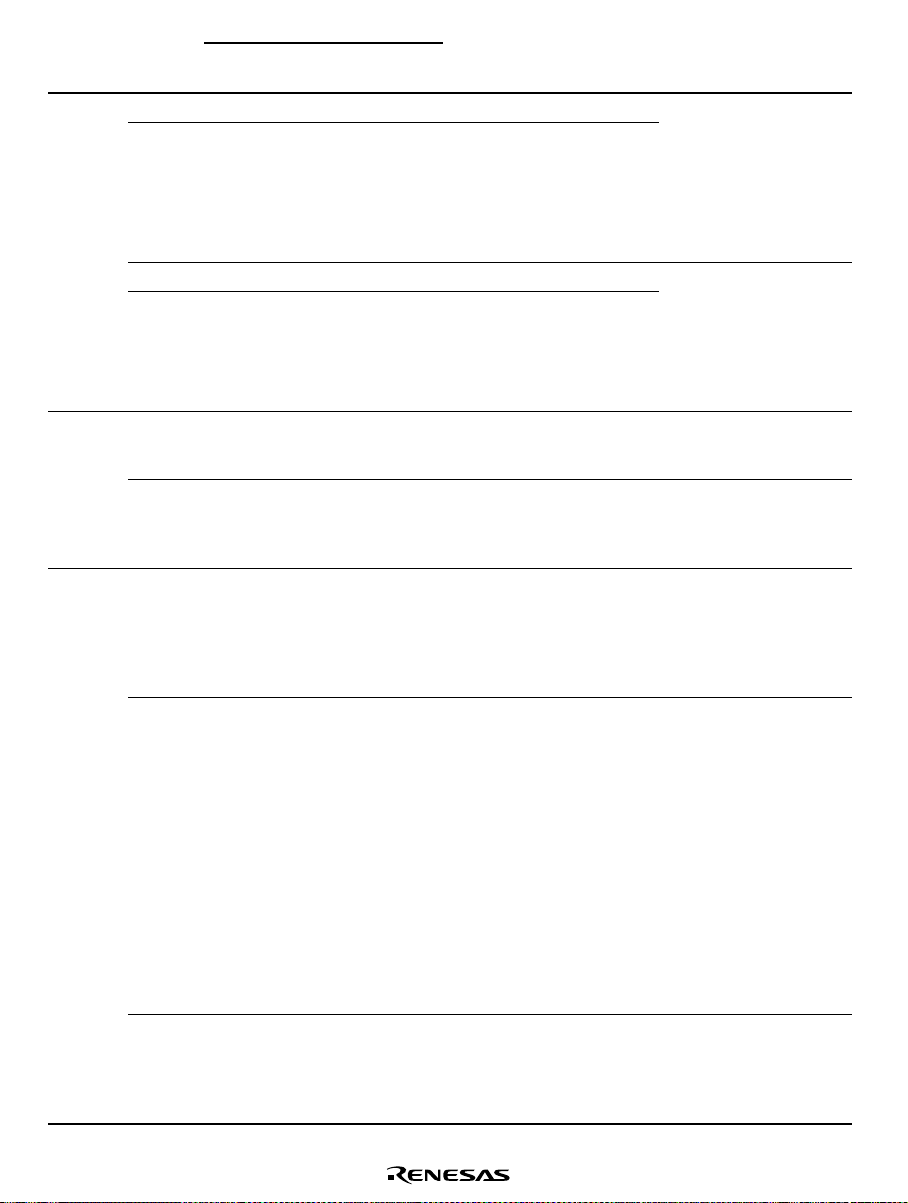

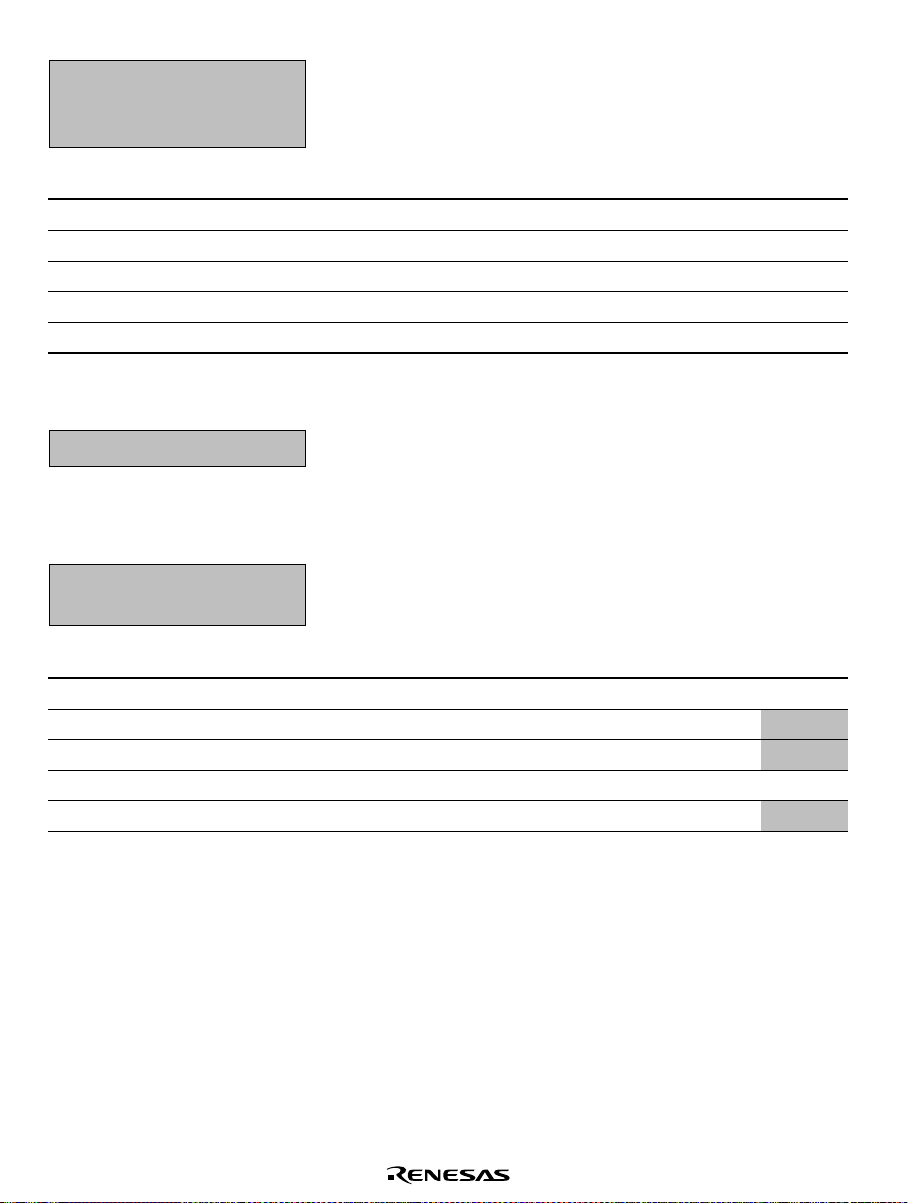

List of Items Revised or Added for This Version

Item Page Revisions (See Manual for Details)

1.1 Overview

Table 1.1 Features

6 Table 1.1 amended

Product Code

Mask ROM Version ZTAT Version F-ZTAT Version Package

HD64338024 HD64738024 HD64F38024R

HD64338020 — — FP-80A

HD64F38024

FP-80A

FP-80B

TFP-80C

TLP-85V (HD64F38024R only)

Die (mask ROM/F-ZTAT version

only)

FP-80B

TFP-80C

Die

ROM/RAM Size

(Byte)

32K/1K

8K/512

3.4.2 Notes on

Rewriting Port Mode

Registers

Table 3.5 Conditions

under which Interrupt

Request Flag is Set

to 1

97 Table 3.5 amended

Interrupt Request

Flags Set to 1 Conditions

IWPR IWPF7

When PMR5 bit WKP7 is changed from 0 to 1 while pin

WKEGS7 = 0.

When PMR5 bit WK P 7 is changed fro m 1 to 0 while pin

WKEGS7 = 1.

IWPF6

When PMR5 bit WKP6 is changed from 0 to 1 while pin

WKEGS6 = 0.

When PMR5 bit WK P 6 is changed fro m 1 to 0 while pin

WKEGS6 = 1.

IWPF5

When PMR5 bit WKP5 is changed from 0 to 1 while pin

WKEGS5 = 0.

When PMR5 bit WK P 5 is changed fro m 1 to 0 while pin

WKEGS5 = 1.

IWPF4

When PMR5 bit WKP4 is changed from 0 to 1 while pin

WKEGS4 = 0.

When PMR5 bit WK P 4 is changed fro m 1 to 0 while pin

WKEGS4 = 1.

IWPF3

When PMR5 bit WKP3 is changed from 0 to 1 while pin

WKEGS3 = 0.

When PMR5 bit WK P 3 is changed fro m 1 to 0 while pin

WKEGS3 = 1.

IWPF2

When PMR5 bit WKP2 is changed from 0 to 1 while pin

WKEGS2 = 0.

When PMR5 bit WK P 2 is changed fro m 1 to 0 while pin

WKEGS2 = 1.

IWPF1

When PMR5 bit WKP1 is changed from 0 to 1 while pin

WKEGS1 = 0.

When PMR5 bit WK P 1 is changed fro m 1 to 0 while pin

WKEGS1 = 1.

IWPF0

When PMR5 bit WKP0 is changed from 0 to 1 while pin

WKEGS0 = 0.

When PMR5 bit WK P 0 is changed fro m 1 to 0 while pin

WKEGS0 = 1.

is low and WEGR bit

7

is low and WEGR bit

7

is low and WEGR bit

6

is low and WEGR bit

6

is low and WEGR bit

5

is low and WEGR bit

5

is low and WEGR bit

4

is low and WEGR bit

4

is low and WEGR bit

3

is low and WEGR bit

3

is low and WEGR bit

2

is low and WEGR bit

2

is low and WEGR bit

1

is low and WEGR bit

1

is low and WEGR bit

0

is low and WEGR bit

0

Rev. 6.00, 08/04, page ix of xxx

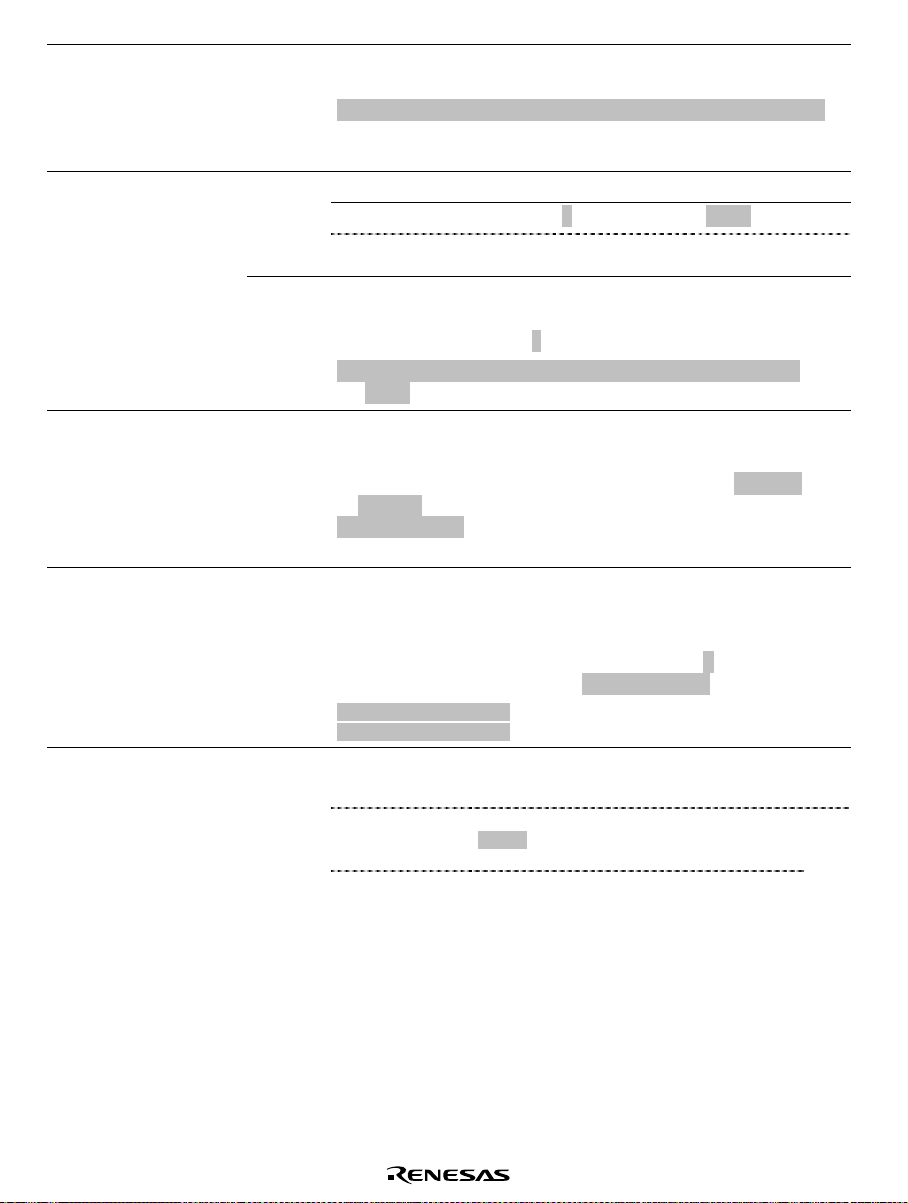

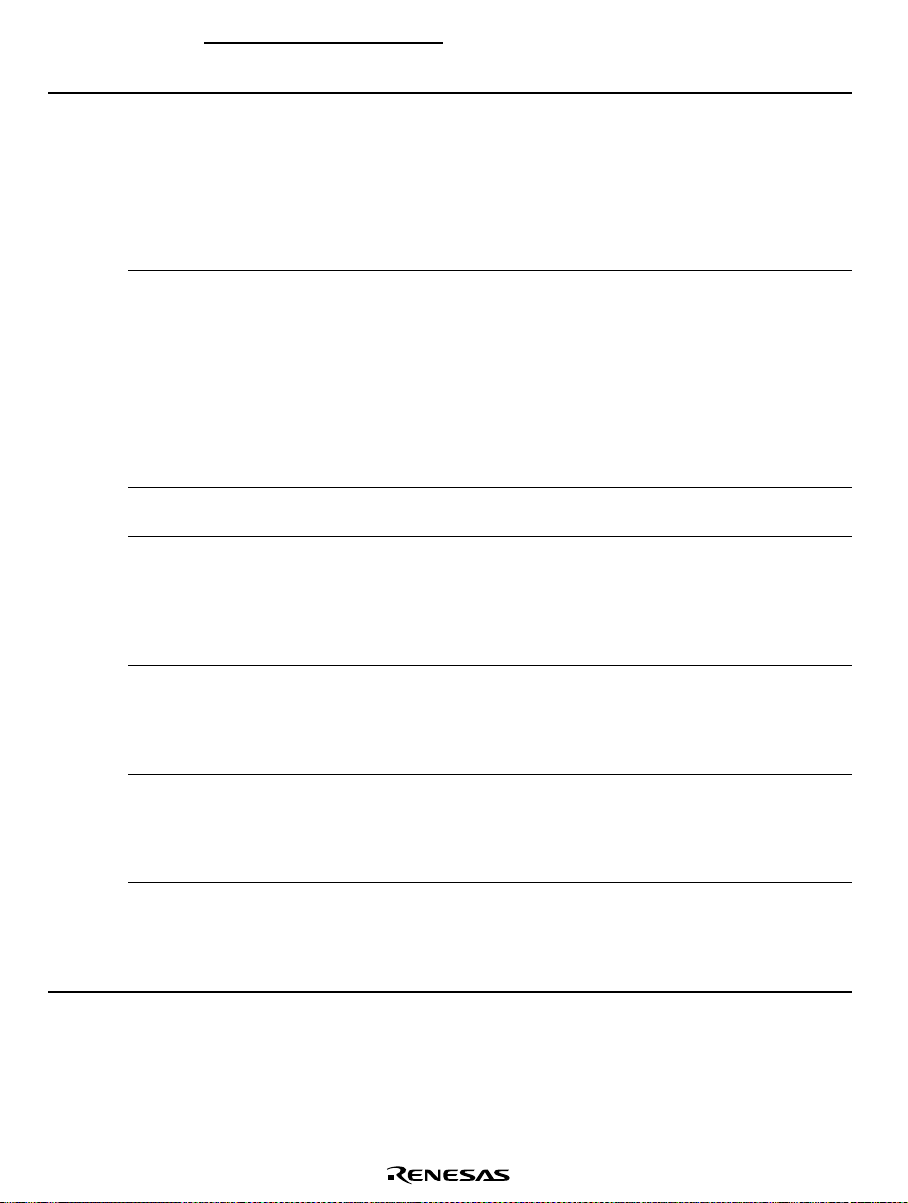

Page 10

Item Page Revisions (See Manual for Details)

4.1.1 Block Diagram

Figure 4.2 Block

Diagram of Clock Pulse

102 Figure 4.2 amended

(Before) Internal reset signal → (After) Internal reset signal

(other than watchdog timer or low-voltage detect circuit reset)

Generators (H8/38124

Group)

4.2 System Clock

Generator

105 Table 4.2

Frequency (MHz) 4 4.193

Table 4.2 Crystal

Oscillator Parameters

On-Chip Oscillator

Selection Method

(H8/38124 Group Only)

108 Note added

The on-chip oscillator is selected by setting the IRQAEC pin

input level during resets.*

* Other than watchdog timer or low-voltage detect circuit

reset.

4.4 Prescalers 111 Prescalers S (PPS)

Description amended

The output from prescaler S is shared by timer A,

timer G, SCI3, the A/D converter, the LCD controller,

F,

watchdog timer, and the 10-bit PWM. The divider ratio can be

set separately for each on-chip peripheral function.

4.5.1 Definition of

Oscillation Stabilization

Wait Time

5.1 Overview

Table 5.1 Operating

Modes

115 2. Wait time

Description amended, notes *1, *2 added

Oscillation stabilization wait time = oscillation stabilization time + wait time

Notes: 1. H8/38024 Group

2. H8/38124 Group

117 Table 5.1 amended

Operating Mode Description

Watch mode The CPU halts. The time-base function of timer A, timer F,

= t

+ (8 to 16,384 states)

rc

(to 131,072 states)

timer G, AEC and LCD controller/driver are operable on the

subclock

timer C, timer

1

*

................. (1)

2

*

Rev. 6.00, 08/04, page x of xxx

Page 11

Item Page Revisions (See Manual for Details)

8.1 Overview

Table 8.1 Port

Functions

187,

188

Table 8.1 amended

Port Description Pins Other Functions

Port 3

• 8-bit I/O port

• MOS input pull-up

• Large-current

• MOS open drain

option

2

*

port

output selectable

(only P3

5

P3

/AEVL

7

P3

/AEVH

6

P3

to P3

5

3

P32, TMOFH

, TMOFL

P3

1

P3

/UD Timer C count up/down

0

)

(Before) Input terminal → (After) input pin

8.9.1 Overview

Figure 8.8 Port

9 Pin

222 Figure 8.8 figure title amended

Configuration

9.2.1 Overview 238 Features

Description deleted

• Use of module standby mode enables this module to be

placed in standby mode independently when not used.

9.4.2 Register

Descriptions

258 Timer Control Register F (TCRF)

Bits 2 to—Clock Select L (CKSL2 to CKSL0)

Note * amended

Note: * …. Note that the timer F counter may increment if the

setting of IRQ3 in port mode register 1 (PMR1) is changed

0 to 1 or from 1 to 0 while the TMIF pin is low order to changed

the TMIF pin function.

9.6.1 Overview 290 Feature

• On-chip the H8/38/124 Group, 10 internal clocks (φ/64, φ/128,

φ/256, φ/512, φ/1024, φ/2048, φ/4096, φ/8192, φw/32, or

watchdog on-chip oscillator) are available for selection for use

by the counter.

Figure 9.17 (2) Block

Diagram of Watchdog

Timer (H8/38124

Group)

292 Block Diagram

Figure amended

(Before) On-chip oscillator → (After)

oscillator

Function

Switching

Registers

Asynchronous counter event

input pins AEVL, AEVH

None PMR2

Timer F output compare

output

selection input

PMR3

ECCR

PMR3

PMR3

Watchdog on-chip

from

Rev. 6.00, 08/04, page xi of xxx

Page 12

Item Page Revisions (See Manual for Details)

9.6.2 Register

Descriptions

297 Timer Mode Register (TMW)

Bits 3 to 0—Clock Select (CKS3 to CKS0)

Bit table amended

Bit 3

CKS3

Bit 2

CKS2

Bit 1

CKS1

Bit 0

CKS0 Description

0XXX

Watchdog on-chip oscillat or

9.7.2 Register

Configurations

309 Event Counter Control/Status Register (ECCSR)

Description amended

• Bit 7—Control

• Bit 6—Counter

9.7.3 Operation

Figure 9.22 Event

Counter Operation

Waveform

316 Event Counter PWM Operation

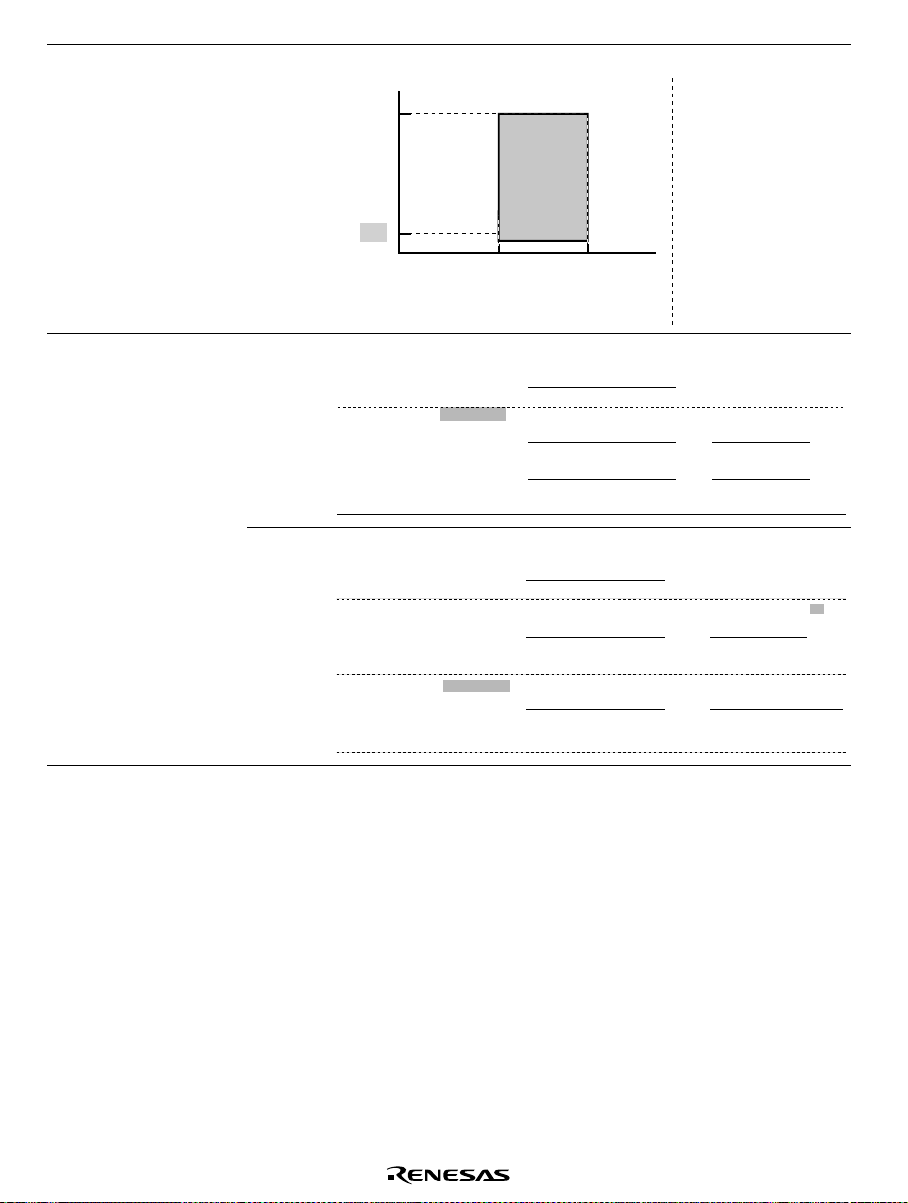

Figure 9.22 amended

Ndr: Value of ECPWDRH and ECPWDRL Fixed

= H’FFFF

14.1 Overview 423 Note * added

Note: * The voltage maintained in standby mode is the same as

the RAM data retaining voltage (VRAM). See section 16.8.2,

DC Characteristics, for information on retaining voltage.

14.2.1 Low-Voltage

Detection Control

Register (LVDCR)

428 Note added

Note: Setting values marked with an asterisk (*) are invalid.

Table 14.3 LVDCR

Settings and Function

Register Selections

14.2.2 Low-Voltage

Detection Status

Register (LVDSR)

14.3.2 Low-Voltage

Detection Circuit

LVDR (Reset by Low

Voltage Detect) Circuit:

428 Note amended

Note: * These bits

432 Description amended

To operate the LVDR, set the LVDE bit in LVDCR to 1, wait for

150 µs (t

LVDON

detection power supply have stabilized, based on overflow of

LVDNT, etc., then set the LVDRE bit in LVDCR to 1.

LVDI (Interrupt by Low

Voltage Detect) Circuit:

433 Description amended

To operate the LVDI, set the LVDE bit in LVDCR to 1, wait for

150 µs (t

LVDON

detection power supply have stabilized, based on overflow of

LVDNT, etc., then set the LVDDE and LVDUE bits in LVDCR to

1.

Overflow H (OVH)

Overflow L (OVL)

low when Ndr

initialized by resets trigged by LVDR.

) until the reference voltage and the low-voltage-

) until the reference voltage and the low-voltage-

Rev. 6.00, 08/04, page xii of xxx

Page 13

Item Page Revisions (See Manual for Details)

14.3.2 Low-Voltage

Detection Circuit

Operation and

Cancellation Setting

Procedure Using LVDR

437 Description amended

2. After waiting for LVDCNT overflow, etc., to ensure that the

stabilization time (t

and low voltage detection power supply has elapsed, clear

bits LVDDF and LVDUF in LVDSR to 0.

= 150 µs) for the reference voltage

LVDON

and LVDI:

16.4.2 DC

Characteristics

Table 16.8 DC

Characteristics

16.8.1 Power Supply

462 Table amended

Item Sym bol Applicable Pi ns Min Typ Max Unit Test Condit i on Not es

output low

current

(per pin)

IOLOutput pins

except port 9

P9

P93 to P9

487 Figure amended

to P9

0

Values

——0.5 mAAllowable

— — 25.0 mA

2

— — 10.0

— — 10.0 mA

5

Voltage and Operating

Ranges

Power Supply Voltage

and Oscillation

Frequency Range (OnChip Oscillator

Selected)

1

*

2

*

5

*

Rev. 6.00, 08/04, page xiii of xxx

Page 14

Item Page Revisions (See Manual for Details)

16.8.1 Power Supply

490 Figure amended

Voltage and Operating

Ranges

1.0

Analog Power Supply

Voltage and A/D

Converter Operating

Range (On-Chip

Oscillator Selected)

16.8.2 DC

Characteristics

Table 16.21 DC

Characteristics

492 Table 16.21 amended

φ (MHz)

0.35

2.7 5.5

AV

CC (V)

• Active (high-speed) mode

• Sleep (high-speed) mode

Item Symbol Applicable Pins Min Typ Max Unit Test Condition Notes

V

Output

high

voltage

OH

P13, P14, P17,

P3

to P37,

0

P4

to P42,

0

P5

to P57,

0

to P67,

P6

0

P7

to P77,

0

P8

to P87,

0

PA

to PA

0

3

Values

VCC – 1.0 — — V VCC = 4.0 V to 5.5 V

V

– 0.5 — — VCC = 4.0 V to 5.5 V

CC

VCC – 0.3 — — –IOH = 0.1 mA

493 Table 16.21 amended

Item Symbol Applicable Pins Min Typ Max Unit Test Condition Notes

Output low

V

P90 to P9

voltage

Pull-up

MOS

current

OL

–I

p

P1

3

P3

0

P5

0

P6

0

5

, P14, P17,

to P37,

to P57,

to P6

7

Values

——1.5 VCC = 4.0 V to 5.5 V

——1.0 V

20 — 200 µAVVCC = 5.0 V,

— 40 — VCC = 2.7 V,

= 1.0 mA

–I

OH

= 0.5 mA

–I

OH

= 15 mA

I

OL

= 4.0 V to 5.5 V

CC

= 10 mA

I

OL

= 0.0 V

V

IN

V

= 0.0 V

IN

Reference

value

Rev. 6.00, 08/04, page xiv of xxx

Page 15

Item Page Revisions (See Manual for Details)

16.8.2 DC

Characteristics

Table 16.21 DC

Characteristics

497 to

499

Table 16.21 amended, note *6 added

Item Symbol Applicable Pins Min Typ Max Unit Test Condition Notes

I

Watch

WATCHVCC

mode

current

consumption

I

Standby

STBYVCC

mode

current

consumption

V

RAM

RAM data

retaining

voltage

V

CC

Values

— TBD — µA

— 1.8 —

— 1.8 6.0 VCC = 2.7 V,

— TBD — µA

— 0.5 —

— 0.05 — VCC = 2.7 V,

— 0.6 — VCC = 5.0 V,

— 0.16 —

— 1.0 5.0

2.0 —— V

VCC = 2.7 V,

T

= 25°C,

a

32-kHz crystal

resonator used,

LCD not used

32-kHz crystal

resonator used,

LCD not used

V

= 2.7 V,

CC

T

= 25°C,

a

32-kHz crystal

resonator not used

= 2.7 V,

V

CC

T

= 25°C,

a

32-kHz crystal

resonator not used

T

= 25°C,

a

SUBSTP (subclock

oscillator control

register) setting = 1

T

= 25°C,

a

32-kHz crystal

resonator not used

= 5.0 V,

V

CC

T

= 25°C,

a

SUBSTP (subclock

oscillator control

register) setting = 1

32-kHz crystal

resonator not used

1 *3 *4

*

Reference

value

2 *3 *4

*

Reference

value

3 *4

*

1 *3 *4

*

Reference

value

2 *3 *4

*

Reference

value

2 *4

*

Reference

value

2 *3 *4

*

Reference

value

4

*2 *

Reference

value

3 *4

*

6

*

Item Symbol

Allowable output low

current (per pin)

I

OL

Applicable

Pins Min Typ Max Unit

Output pins

except ports 3

and 9

Values

——2.0 mA

Port 3 ——10.0

Output pins

except port 9

——0.5

Port 9 ——15.0

——10.0

——8.0

Note: 6. Voltage maintained in standby mode

Rev. 6.00, 08/04, page xv of xxx

Test

Condition Notes

VCC = 4.0 V to

5.5 V

= 4.0 V to

V

CC

5.5 V

5

= 4.0 V to

*

V

CC

5.5 V

Page 16

Item Page Revisions (See Manual for Details)

16.8.3 AC

Characteristics

Table 16.22 Control

Signal Timing

500,

501

Table 16.22 amended, note *2 added

Item Symbol

System clock

oscillation

frequency

OSC clock (φ

cycle time

System clock (φ)

cycle time

f

OSC

)

t

OSC

OSC

t

cyc

Applicable

Pins Min Typ Max Unit Test Condition

OSC1, OSC

OSC1, OSC262.5 — 500 ns F igure 16.1

Values

2.0 — 16.0

2

0.7 — 2.0 On-chip oscillator

500 — 1429 On-chip oscillator

2 — 128 t

—— 182 µs

Note: 2. These characteristics are given as ranges between

minimum and maximum values in order to account for factors

such as temperature, power supply voltage, and variation

among production lots. When designing systems, make sure to

give due consideration to the SPEL range. Please see the Web

site for this product for actual performance data.

16.8.5 LCD

Characteristics

Table 16.25 LCD

Characteristics

503 Table 16.25 amended

Applicable

Item Symbol

Liquid crystal

display volt age

V

LCDV1

Pins

Values

Min Typ Max Unit Test Condition

2.7 — 5.5 V

MHz

OSC

selected

selected

Reference

Figure

2

*

Reference

Figure

2

*

16.8.7 Power Supply

506 Table 16.27

Voltage Detection

Circuit Characteristics

Table 16.27 Power

Item Symbol Min Typ Max Unit Test Conditions

LVD stabilization time T

150 ——µs

LVDON

Supply Voltage

Detection Circuit

Characteristics (1)

16.8.8 Power-On

509 Title amended

Reset Circuit

Characteristics

B.2 Functions 574 PWCR1—PWM1 Control Register

Note 1 amended

Notes: 1. tφ: Period of

PWM1 input clock

589 OSCCR—Clock Pulse Generator Control Register

Bit table amended

2

IRQAECF

R

1

OSCF

R

0

0

R/W

Rated Values

Rev. 6.00, 08/04, page xvi of xxx

Page 17

Item Page Revisions (See Manual for Details)

E. List of Product

Codes

Table E.1 H8/38024

Group Product Code

Lineup

618 Table E.1 amended

Product Type Product Code Mark Code

H8/38124 HD64F38124H F38124H 80-pin QFP (FP-80A)

H8/38124

Group

F-ZTAT

versions

Mask ROM

versions

H8/38123 HD64338123H 38123(***)H 80-pin QFP (FP-80A)Mask ROM

versions

H8/38122 HD64338122H 38122(***)H 80-pin QFP (FP-80A)Mask ROM

versions

H8/38121 HD64338121H 38121(***)H 80-pin QFP (FP-80A)

Mask ROM

versions

H8/38120 HD64338120H 38120(***)H 80-pin QFP (FP-80A)Mask ROM

versions

Regular

specifications

Wide-range

specifications

Regular

specifications

specifications

Regular

specifications

specifications

Regular

specifications

Wide-range

specifications

Regular

specifications

Wide-range

specifications

Regular

specifications

specifications

HD64F38124W F38124W 80-pin TQFP (TFP-80C)

HD64F38124HW F38124H 80-pin QFP (FP-80A)

HD64F38124WW F38124W 80-pin TQFP (TFP-80C)

HD64338124H 38124(***)H 80-pin QFP (FP-80A)

HD64338124W 38124(***) 80-pin TQFP (TFP-80C)

HD64338124HW 38124(***)H 80-pin QFP (FP-80A)Wide-range

HD64338124WW 38124(***) 80-pin TQFP (TFP-80C)

HD64338123W 38123(***) 80-pin TQFP (TFP-80C)

HD64338123HW 38123(***)H 80-pin QFP (FP-80A)Wide-range

HD64338123WW 38123(***) 80-pin TQFP (TFP-80C)

HD64338122W 38122(***) 80-pin TQFP (TFP-80C)

HD64338122HW 38122(***)H 80-pin QFP (FP-80A)

HD64338122WW 38122(***) 80-pin TQFP (TFP-80C)

HD64338121W 38121(***) 80-pin TQFP (TFP-80C)

HD64338121HW 38121(***)H 80-pin QFP (FP-80A)

HD64338121WW 38121(***) 80-pin TQFP (TFP-80C)

HD64338120W 38120(***) 80-pin TQFP (TFP-80C)

HD64338120HW 38120(***)H 80-pin QFP (FP-80A)Wide-range

HD64338120WW 38120(***) 80-pin TQFP (TFP-80C)

Package

(Package Code)

Rev. 6.00, 08/04, page xvii of xxx

Page 18

Rev. 6.00, 08/04, page xviii of xxx

Page 19

Contents

Section 1 Overview............................................................................................................. 1

1.1 Overview........................................................................................................................... 1

1.2 Internal Block Diagram..................................................................................................... 7

1.3 Pin Arrangement and Functions........................................................................................ 9

1.3.1 Pin Arrangement.................................................................................................. 9

1.3.2 Pin Functions ....................................................................................................... 19

Section 2 CPU...................................................................................................................... 25

2.1 Overview........................................................................................................................... 25

2.1.1 Features................................................................................................................ 25

2.1.2 Address Space...................................................................................................... 26

2.1.3 Register Configuration......................................................................................... 26

2.2 Register Descriptions........................................................................................................27

2.2.1 General Registers................................................................................................. 27

2.2.2 Control Registers ................................................................................................. 27

2.2.3 Initial Register Values.......................................................................................... 29

2.3 Data Formats..................................................................................................................... 29

2.3.1 Data Formats in General Registers ...................................................................... 30

2.3.2 Memory Data Formats......................................................................................... 31

2.4 Addressing Modes.............................................................................................................32

2.4.1 Addressing Modes............................................................................................... 32

2.4.2 Effective Address Calculation.............................................................................. 34

2.5 Instruction Set................................................................................................................... 38

2.5.1 Data Transfer Instructions.................................................................................... 40

2.5.2 Arithmetic Operations.......................................................................................... 42

2.5.3 Logic Operations.................................................................................................. 43

2.5.4 Shift Operations................................................................................................... 43

2.5.5 Bit Manipulations................................................................................................. 45

2.5.6 Branching Instructions......................................................................................... 49

2.5.7 System Control Instructions................................................................................. 51

2.5.8 Block Data Transfer Instruction........................................................................... 52

2.6 Basic Operational Timing................................................................................................. 54

2.6.1 Access to On-Chip Memory (RAM, ROM)......................................................... 54

2.6.2 Access to On-Chip Peripheral Modules............................................................... 55

2.7 CPU States........................................................................................................................ 57

2.7.1 Overview.............................................................................................................. 57

2.7.2 Program Execution State...................................................................................... 58

2.7.3 Program Halt State............................................................................................... 58

2.7.4 Exception-Handling State.................................................................................... 58

Rev. 6.00, 08/04, page xix of xxx

Page 20

2.8 Memory Map .................................................................................................................... 59

2.8.1 Memory Map....................................................................................................... 59

2.9 Application Notes ............................................................................................................. 64

2.9.1 Notes on Data Access.......................................................................................... 64

2.9.2 Notes on Bit Manipulation................................................................................... 66

2.9.3 Notes on Use of the EEPMOV Instruction.......................................................... 72

Section 3 Exception Handling......................................................................................... 73

3.1 Overview........................................................................................................................... 73

3.2 Reset.................................................................................................................................. 73

3.2.1 Overview.............................................................................................................. 73

3.2.2 Reset Sequence.................................................................................................... 73

3.2.3 Interrupt Immediately after Reset........................................................................ 74

3.3 Interrupts........................................................................................................................... 75

3.3.1 Overview.............................................................................................................. 75

3.3.2 Interrupt Control Registers.................................................................................. 77

3.3.3 External Interrupts............................................................................................... 87

3.3.4 Internal Interrupts ................................................................................................ 88

3.3.5 Interrupt Operations............................................................................................. 89

3.3.6 Interrupt Response Time...................................................................................... 94

3.4 Application Notes ............................................................................................................. 95

3.4.1 Notes on Stack Area Use..................................................................................... 95

3.4.2 Notes on Rewriting Port Mode Registers............................................................. 96

3.4.3 Method for Clearing Interrupt Request Flags ...................................................... 98

Section 4 Clock Pulse Generators................................................................................... 101

4.1 Overview........................................................................................................................... 101

4.1.1 Block Diagram..................................................................................................... 101

4.1.2 System Clock and Subclock................................................................................. 102

4.1.3 Register Descriptions........................................................................................... 102

4.2 System Clock Generator................................................................................................... 104

4.3 Subclock Generator........................................................................................................... 109

4.4 Prescalers.......................................................................................................................... 111

4.5 Note on Oscillators ........................................................................................................... 112

4.5.1 Definition of Oscillation Stabilization Wait Time............................................... 113

4.5.2 Notes on Use of Crystal Oscillator Element (Excl uding Ceramic Oscillator

Element)............................................................................................................... 115

4.5.3 Note on Use of HD64F38024.............................................................................. 116

4.6 Notes on H8/38124 Group................................................................................................ 116

Section 5 Power-Down Modes........................................................................................ 117

5.1 Overview........................................................................................................................... 117

5.1.1 System Control Registers..................................................................................... 120

Rev. 6.00, 08/04, page xx of xxx

Page 21

5.2 Sleep Mode ....................................................................................................................... 124

5.2.1 Transition to Sleep Mode..................................................................................... 124

5.2.2 Clearing Sleep Mode............................................................................................ 125

5.2.3 Clock Frequency in Sleep (Medium-Speed) Mode.............................................. 125

5.3 Standby Mode................................................................................................................... 126

5.3.1 Transition to Standby Mode................................................................................. 126

5.3.2 Clearing Standby Mode....................................................................................... 126

5.3.3 Oscillator Stabilization Time after Standby Mode is Cleared.............................. 127

5.3.4 Standby Mode Transition and Pin States............................................................. 128

5.3.5 Notes on External Input Signal Changes before/after Standby Mode.................. 129

5.4 Watch Mode...................................................................................................................... 131

5.4.1 Transition to Watch Mode................................................................................... 131

5.4.2 Clearing Watch Mode.......................................................................................... 131

5.4.3 Oscillator StabilizationTime after Watch Mode is Cleared ................................. 131

5.4.4 Notes on External Input Signal Changes before/after Watch Mode .................... 131

5.5 Subsleep Mode.................................................................................................................. 132

5.5.1 Transition to Subsleep Mode............................................................................... 132

5.5.2 Clearing Subsleep Mode...................................................................................... 132

5.6 Subactive Mode ................................................................................................................ 133

5.6.1 Transition to Subactive Mode.............................................................................. 133

5.6.2 Clearing Subactive Mode..................................................................................... 133

5.6.3 Operating Frequency in Subactive Mode............................................................. 133

5.7 Active (Medium-Speed) Mode ......................................................................................... 134

5.7.1 Transition to Active (Medium-Speed) Mode....................................................... 134

5.7.2 Clearing Active (Medium-Speed) Mode.............................................................. 134

5.7.3 Operating Frequency in Active (Medium-Speed) Mode...................................... 134

5.8 Direct Transfer.................................................................................................................. 135

5.8.1 Overview of Direct Transfer................................................................................ 135

5.8.2 Direct Transition Times....................................................................................... 136

5.8.3 Notes on External Input Signal Changes before/after Direct Transition.............. 138

5.9 Module Standby Mode...................................................................................................... 139

5.9.1 Setting Module Standby Mode ............................................................................ 139

5.9.2 Clearing Module Standby Mode.......................................................................... 139

Section 6 ROM..................................................................................................................... 141

6.1 Overview........................................................................................................................... 141

6.1.1 Block Diagram..................................................................................................... 141

6.2 H8/38024 PROM Mode.................................................................................................... 142

6.2.1 Setting to PROM Mode ....................................................................................... 142

6.2.2 Socket Adapter Pin Arrangement and Memory Map........................................... 142

6.3 H8/38024 Programming.................................................................................................... 145

6.3.1 Writing and Verifying.......................................................................................... 145

6.3.2 Programming Precautions.................................................................................... 150

Rev. 6.00, 08/04, page xxi of xxx

Page 22

6.4 Reliability of Programmed Data....................................................................................... 151

6.5 Flash Memory Overview .................................................................................................. 152

6.5.1 Features................................................................................................................ 152

6.5.2 Block Diagram..................................................................................................... 153

6.5.3 Block Configuration............................................................................................. 154

6.5.4 Register Configuration......................................................................................... 155

6.6 Descriptions of Registers of the Flash Memory................................................................ 156

6.6.1 Flash Memory Control Register 1 (FLMCR1)..................................................... 156

6.6.2 Flash Memory Control Register 2 (FLMCR2)..................................................... 158

6.6.3 Erase Block Register (EBR)................................................................................ 159

6.6.4 Flash Memory Power Control Register (FLPWCR)............................................ 159

6.6.5 Flash Memory Enable Register (FENR).............................................................. 160

6.7 On-Board Programming Modes........................................................................................ 161

6.7.1 Boot Mode........................................................................................................... 162

6.7.2 Programming/Erasing in User Program Mode..................................................... 164

6.7.3 Notes on On-Board Programming ....................................................................... 165

6.8 Flash Memory Programming/Erasing............................................................................... 165

6.8.1 Program/Program-Verify..................................................................................... 165

6.8.2 Erase/Erase-Verify............................................................................................... 169

6.8.3 Interrupt Handling when Programming/Erasing Flash Memory.......................... 169

6.9 Program/Erase Protection ................................................................................................. 171

6.9.1 Hardware Protection............................................................................................ 171

6.9.2 Software Protection.............................................................................................. 171

6.9.3 Error Protection.................................................................................................... 171

6.10 Programmer Mode ............................................................................................................ 172

6.10.1 Socket Adapter..................................................................................................... 172

6.10.2 Programmer Mode Commands............................................................................ 172

6.10.3 Memory Read Mode............................................................................................ 175

6.10.4 Auto-Program Mode............................................................................................ 178

6.10.5 Auto-Erase Mode................................................................................................. 180

6.10.6 Status Read Mode................................................................................................ 181

6.10.7 Status Polling....................................................................................................... 183

6.10.8 Programmer Mode Transition Time .................................................................... 183

6.10.9 Notes on Memory Programming.......................................................................... 184

6.11 Power-Down States for Flash Memory............................................................................. 184

Section 7 RAM..................................................................................................................... 185

7.1 Overview........................................................................................................................... 185

7.1.1 Block Diagram..................................................................................................... 185

Section 8 I/O Ports.............................................................................................................. 187

8.1 Overview........................................................................................................................... 187

8.2 Port 1................................................................................................................................. 189

Rev. 6.00, 08/04, page xxii of xxx

Page 23

8.2.1 Overview.............................................................................................................. 189

8.2.2 Register Configuration and Description............................................................... 189

8.2.3 Pin Functions ....................................................................................................... 194

8.2.4 Pin States.............................................................................................................. 195

8.2.5 MOS Input Pull-Up.............................................................................................. 195

8.3 Port 3................................................................................................................................. 196

8.3.1 Overview.............................................................................................................. 196

8.3.2 Register Configuration and Description............................................................... 196

8.3.3 Pin Functions ....................................................................................................... 201

8.3.4 Pin States.............................................................................................................. 202

8.3.5 MOS Input Pull-Up.............................................................................................. 202

8.4 Port 4................................................................................................................................. 203

8.4.1 Overview.............................................................................................................. 203

8.4.2 Register Configuration and Description............................................................... 203

8.4.3 Pin Functions ....................................................................................................... 205

8.4.4 Pin States.............................................................................................................. 206

8.5 Port 5................................................................................................................................. 207

8.5.1 Overview.............................................................................................................. 207

8.5.2 Register Configuration and Description............................................................... 207

8.5.3 Pin Functions ....................................................................................................... 210

8.5.4 Pin States.............................................................................................................. 211

8.5.5 MOS Input Pull-Up.............................................................................................. 211

8.6 Port 6................................................................................................................................. 212

8.6.1 Overview.............................................................................................................. 212

8.6.2 Register Configuration and Description............................................................... 212

8.6.3 Pin Functions ....................................................................................................... 214

8.6.4 Pin States.............................................................................................................. 215

8.6.5 MOS Input Pull-Up.............................................................................................. 215

8.7 Port 7................................................................................................................................. 216

8.7.1 Overview.............................................................................................................. 216

8.7.2 Register Configuration and Description............................................................... 216

8.7.3 Pin Functions ....................................................................................................... 218

8.7.4 Pin States.............................................................................................................. 218

8.8 Port 8................................................................................................................................. 219

8.8.1 Overview.............................................................................................................. 219

8.8.2 Register Configuration and Description............................................................... 219

8.8.3 Pin Functions ....................................................................................................... 221

8.8.4 Pin States.............................................................................................................. 221

8.9 Port 9................................................................................................................................. 222

8.9.1 Overview.............................................................................................................. 222

8.9.2 Register Configuration and Description............................................................... 222

8.9.3 Pin Functions ....................................................................................................... 225

8.9.4 Pin States.............................................................................................................. 225

Rev. 6.00, 08/04, page xxiii of xxx

Page 24

8.10 Port A................................................................................................................................ 226

8.10.1 Overview.............................................................................................................. 226

8.10.2 Register Configuration and Description............................................................... 226

8.10.3 Pin Functions....................................................................................................... 228

8.10.4 Pin States ............................................................................................................. 229

8.11 Port B................................................................................................................................ 230

8.11.1 Overview.............................................................................................................. 230

8.11.2 Register Configuration and Description............................................................... 230

8.11.3 Pin Functions....................................................................................................... 232

8.12 Input/Output Data Inversion Function.............................................................................. 233

8.12.1 Overview.............................................................................................................. 233

8.12.2 Register Configuration and Descriptions............................................................. 234

8.12.3 Note on Modification of Serial Port Control Register......................................... 235

8.13 Application Note............................................................................................................... 236

8.13.1 The Management of the Un-Use Terminal.......................................................... 236

Section 9 Timers.................................................................................................................. 237

9.1 Overview........................................................................................................................... 237

9.2 Timer A............................................................................................................................. 238

9.2.1 Overview.............................................................................................................. 238

9.2.2 Register Descriptions........................................................................................... 240

9.2.3 Timer Operation................................................................................................... 243

9.2.4 Timer A Operation States.................................................................................... 243

9.2.5 Application Note.................................................................................................. 244

9.3 Timer C............................................................................................................................. 244

9.3.1 Overview.............................................................................................................. 244

9.3.2 Register Descriptions........................................................................................... 246

9.3.3 Timer Operation................................................................................................... 249

9.3.4 Timer C Operation States..................................................................................... 251

9.4 Timer F ............................................................................................................................. 252

9.4.1 Overview.............................................................................................................. 252

9.4.2 Register Descriptions........................................................................................... 255

9.4.3 CPU Interface ...................................................................................................... 262

9.4.4 Operation............................................................................................................. 265

9.4.5 Application Notes................................................................................................ 268

9.5 Timer G............................................................................................................................. 271

9.5.1 Overview.............................................................................................................. 271

9.5.2 Register Descriptions........................................................................................... 273

9.5.3 Noise Canceler..................................................................................................... 278

9.5.4 Operation............................................................................................................. 280

9.5.5 Application Notes................................................................................................ 284

9.5.6 Timer G Application Example............................................................................. 289

9.6 Watchdog Timer............................................................................................................... 290

Rev. 6.00, 08/04, page xxiv of xxx

Page 25

9.6.1 Overview.............................................................................................................. 290

9.6.2 Register Descriptions........................................................................................... 293

9.6.3 Timer Operation................................................................................................... 299

9.6.4 Watchdog Timer Operation States....................................................................... 300

9.7 Asynchronous Event Counter (AEC)................................................................................ 301

9.7.1 Overview.............................................................................................................. 301

9.7.2 Register Configurations....................................................................................... 304

9.7.3 Operation ............................................................................................................. 313

9.7.4 Asynchronous Event Counter Operation Modes.................................................. 317

9.7.5 Application Notes................................................................................................ 318

Section 10 Serial Communication Interface................................................................ 319

10.1 Overview........................................................................................................................... 319

10.1.1 Features................................................................................................................ 319

10.1.2 Block Diagram..................................................................................................... 321

10.1.3 Pin Configuration................................................................................................. 322

10.1.4 Register Configuration......................................................................................... 322

10.2 Register Descriptions........................................................................................................ 323

10.2.1 Receive Shift Register (RSR) .............................................................................. 323

10.2.2 Receive Data Register (RDR).............................................................................. 323

10.2.3 Transmit Shift Register (TSR)............................................................................. 324

10.2.4 Transmit Data Register (TDR)............................................................................. 324

10.2.5 Serial Mode Register (SMR)................................................................................ 325

10.2.6 Serial Control Register 3 (SCR3)......................................................................... 328

10.2.7 Serial Status Register (SSR) ................................................................................ 332

10.2.8 Bit Rate Register (BRR) ...................................................................................... 336

10.2.9 Clock stop register 1 (CKSTPR1)........................................................................ 342

10.2.10 Serial Port Control Register (SPCR).................................................................... 342

10.3 Operation........................................................................................................................... 344

10.3.1 Overview.............................................................................................................. 344

10.3.2 Operation in Asynchronous Mode....................................................................... 348

10.3.3 Operation in Synchronous Mode ......................................................................... 357

10.3.4 Multiprocessor Communication Function............................................................ 364

10.4 Interrupts........................................................................................................................... 371

10.5 Application Notes ............................................................................................................. 372

Section 11 10-Bit PWM..................................................................................................... 377

11.1 Overview........................................................................................................................... 377

11.1.1 Features................................................................................................................ 377

11.1.2 Block Diagram..................................................................................................... 378

11.1.3 Pin Configuration................................................................................................. 379

11.1.4 Register Configuration......................................................................................... 380

11.2 Register Descriptions........................................................................................................ 380

Rev. 6.00, 08/04, page xxv of xxx

Page 26

11.2.1 PWM Control Register (PWCRm) ...................................................................... 380

11.2.2 PWM Data Registers U and L (PWDRUm, PWDRLm) ..................................... 382

11.2.3 Clock Stop Register 2 (CKSTPR2)...................................................................... 383

11.3 Operation .......................................................................................................................... 384

11.3.1 Operation............................................................................................................. 384

11.3.2 PWM Operation Modes....................................................................................... 385

Section 12 A/D Converter................................................................................................. 387

12.1 Overview........................................................................................................................... 387

12.1.1 Features................................................................................................................ 387

12.1.2 Block Diagram..................................................................................................... 388

12.1.3 Pin Configuration................................................................................................. 389

12.1.4 Register Configuration......................................................................................... 389

12.2 Register Descriptions........................................................................................................ 390

12.2.1 A/D Result Registers (ADRRH, ADRRL)........................................................... 390

12.2.2 A/D Mode Register (AMR)................................................................................. 390

12.2.3 A/D Start Register (ADSR) ................................................................................. 392

12.2.4 Clock Stop Register 1 (CKSTPR1)...................................................................... 393

12.3 Operation .......................................................................................................................... 394

12.3.1 A/D Conversion Operation.................................................................................. 394

12.3.2 Start of A/D Conversion by External Trigger Input............................................. 394

12.3.3 A/D Converter Operation Modes......................................................................... 395

12.4 Interrupts........................................................................................................................... 395

12.5 Typical Use....................................................................................................................... 395

12.6 A/D Conversion Accuracy Definitions............................................................................. 398

12.7 Application Notes ............................................................................................................. 400

12.7.1 Application Notes ................................................................................................ 400

12.7.2 Permissible Signal Source Impedance................................................................. 400

12.7.3 Influences on Absolute Precision......................................................................... 400

Section 13 LCD Controller/Driver................................................................................. 403

13.1 Overview........................................................................................................................... 403

13.1.1 Features................................................................................................................ 403

13.1.2 Block Diagram..................................................................................................... 404

13.1.3 Pin Configuration................................................................................................. 406

13.1.4 Register Configuration......................................................................................... 406

13.2 Register Descriptions........................................................................................................ 407

13.2.1 LCD Port Control Register (LPCR)..................................................................... 407

13.2.2 LCD Control Register (LCR)............................................................................... 409

13.2.3 LCD Control Register 2 (LCR2).......................................................................... 411

13.2.4 Clock Stop Register 2 (CKSTPR2)...................................................................... 413

13.3 Operation .......................................................................................................................... 414

13.3.1 Settings up to LCD Display................................................................................. 414

Rev. 6.00, 08/04, page xxvi of xxx

Page 27

13.3.2 Relationship between LCD RAM and Display.................................................... 416

13.3.3 Operation in Power-Down Modes ....................................................................... 421

13.3.4 Boosting the LCD Drive Power Supply............................................................... 422

Section 14 Power-On Reset and Low-Voltage Detection Circuits

(H8/38124 Group Only)............................................................................... 423

14.1 Overview........................................................................................................................... 423

14.1.1 Features................................................................................................................ 423

14.1.2 Block Diagram..................................................................................................... 424

14.1.3 Pin Description..................................................................................................... 425

14.1.4 Register Descriptions........................................................................................... 425

14.2 Individual Register Descriptions....................................................................................... 425

14.2.1 Low-Voltage Detection Control Register (LVDCR) ........................................... 425

14.2.2 Low-Voltage Detection Status Register (LVDSR).............................................. 428

14.2.3 Low-Voltage Detection Counter (LVDCNT)...................................................... 430

14.2.4 Clock Stop Register 2 (CKSTPR2)...................................................................... 430

14.3 Operation........................................................................................................................... 431

14.3.1 Power-On Reset Circuit....................................................................................... 431

14.3.2 Low-Voltage Detection Circuit............................................................................ 432

Section 15 Power Supply Circuit (H8/38124 Group Only)..................................... 439

15.1 When Using Internal Power Supply Step-Down Circuit................................................... 439

15.2 When Not Using Internal Power Supply Step-Down Circuit............................................ 440

Section 16 Electrical Characteristics.............................................................................. 441

16.1 H8/38024 ZTAT Version and Mask ROM Version Absolute Maximum Ratings............ 441

16.2 H8/38024 ZTAT Version and Mask ROM Version Electrical Characteristics................. 442

16.2.1 Power Supply Voltage and Operating Range....................................................... 442

16.2.2 DC Characteristics............................................................................................... 444

16.2.3 AC Characteristics............................................................................................... 450

16.2.4 A/D Converter Characteristics............................................................................. 453

16.2.5 LCD Characteristics ............................................................................................. 454

16.3 H8/38024 F-ZTAT Version and H8/38024R F-ZTAT Version Absolute Maximum

Ratings.............................................................................................................................. 455

16.4 H8/38024 F-ZTAT Version and H8/38024R F-ZTAT Version Electrical Characteristics 456

16.4.1 Power Supply Voltage and Operating Range....................................................... 456

16.4.2 DC Characteristics............................................................................................... 458

16.4.3 AC Characteristics............................................................................................... 464

16.4.4 A/D Converter Characteristics............................................................................. 467

16.4.5 LCD Characteristics ............................................................................................. 468