Page 1

REJ09B0110-0120

R8C/12 Group

16

Hardware Manual

RENESAS 16-BIT SINGLE-CHIP MICROCOMPUTER

M16C FAMILY / R8C /Tiny SERIES

All information contained in these materials, including products and product specifications,

represents information on the product at the time of publication and is subject to change by

Renesas Technology Corp. without notice. Please review the latest information published

by Renesas Technology Corp. through various means, including the Renesas Technology

Corp. website (http://www.renesas.com).

Rev. 1.20

Revision date: Jan 27, 2006

www.renesas.com

Page 2

Keep safety first in your circuit designs!

1.

Renesas Technology Corp. puts the maximum effort into making semiconductor products

better and more reliable, but there is always the possibility that trouble may occur with

them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

1.

These materials are intended as a reference to assist our customers in the selection of the

Renesas Technology Corp. product best suited to the customer's application; they do not

convey any license under any intellectual property rights, or any other rights, belonging to

Renesas Technology Corp. or a third party.

2.

Renesas Technology Corp. assumes no responsibility for any damage, or infringement of

any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3.

All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these

materials, and are subject to change by Renesas Technology Corp. without notice due to

product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other

loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://

www.renesas.com).

4.

When using any or all of the information contained in these materials, including product

data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information

and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

5.

Renesas Technology Corp. semiconductors are not designed or manufactured for use in a

device or system that is used under circumstances in which human life is potentially at

stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology

Corp. product distributor when considering the use of a product contained herein for any

specific purposes, such as apparatus or systems for transportation, vehicular, medical,

aerospace, nuclear, or undersea repeater use.

6.

The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7.

If these products or technologies are subject to the Japanese export control restrictions,

they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/

or the country of destination is prohibited.

8.

Please contact Renesas Technology Corp. for further details on these materials or the

products contained therein.

Page 3

How to Use This Manual

0

1. Introduction

This hardware manual provides detailed information on the R8C/12 Group of microcomputers.

Users are expected to have basic knowledge of electric circuits, logical circuits and microcomputers.

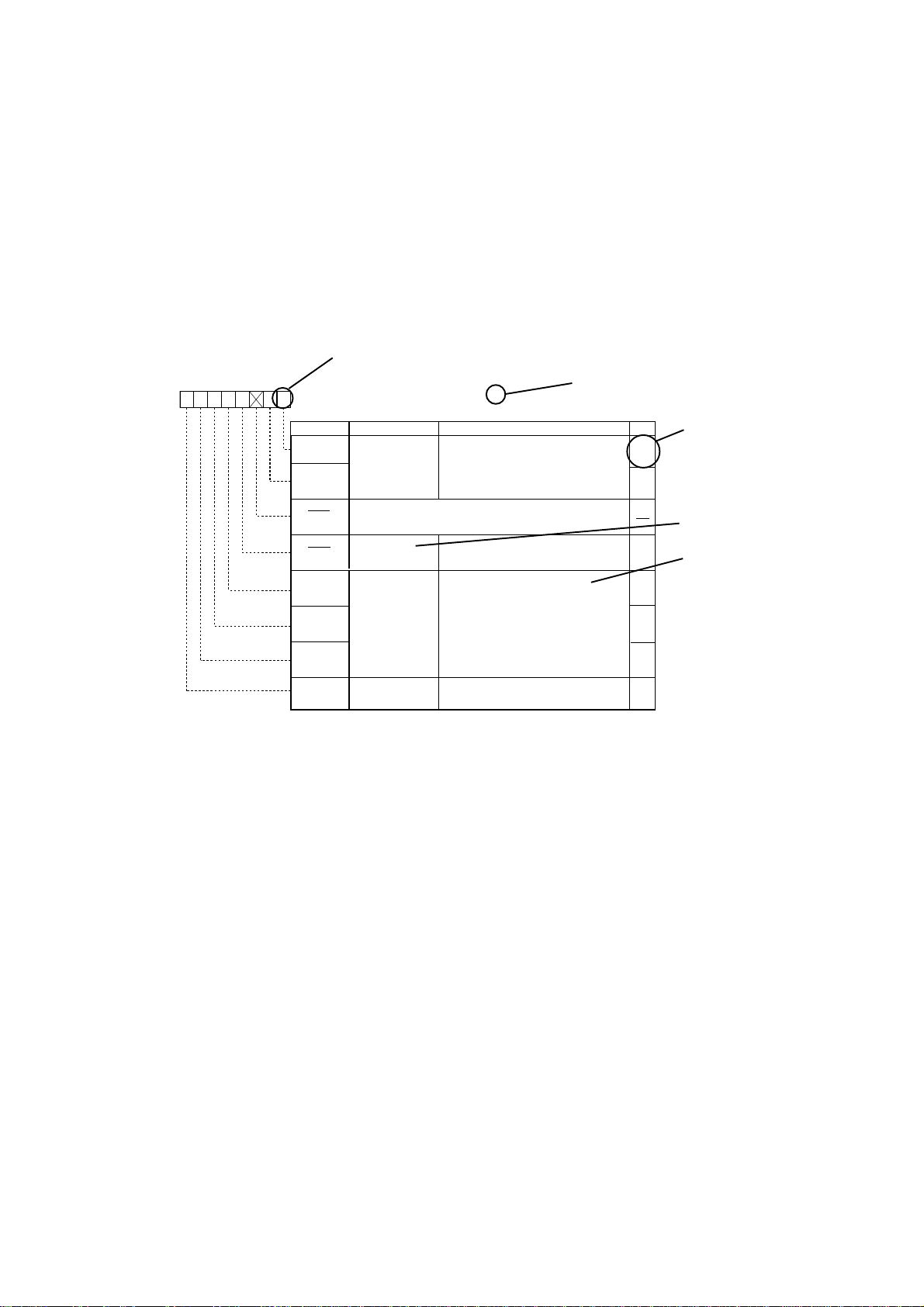

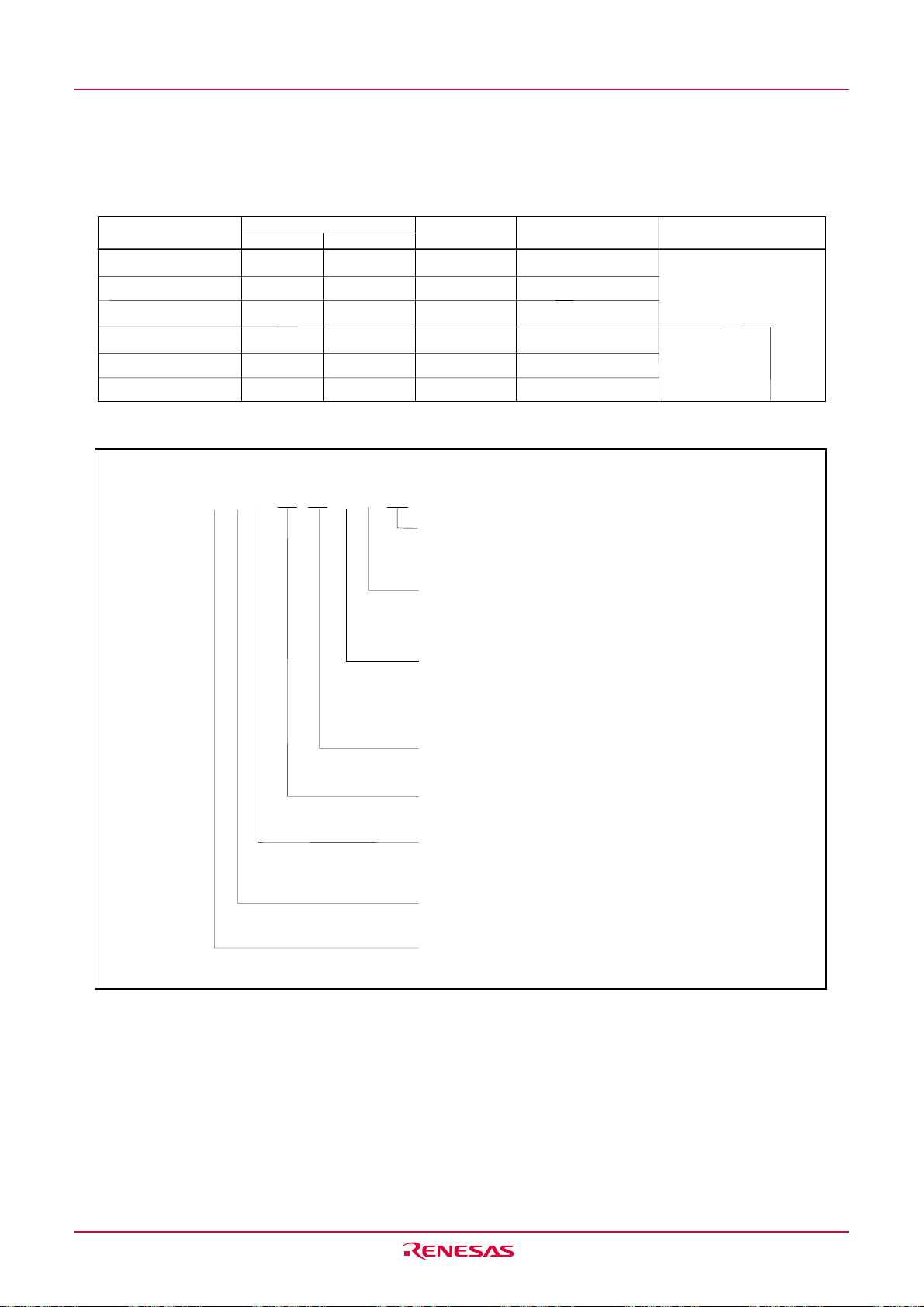

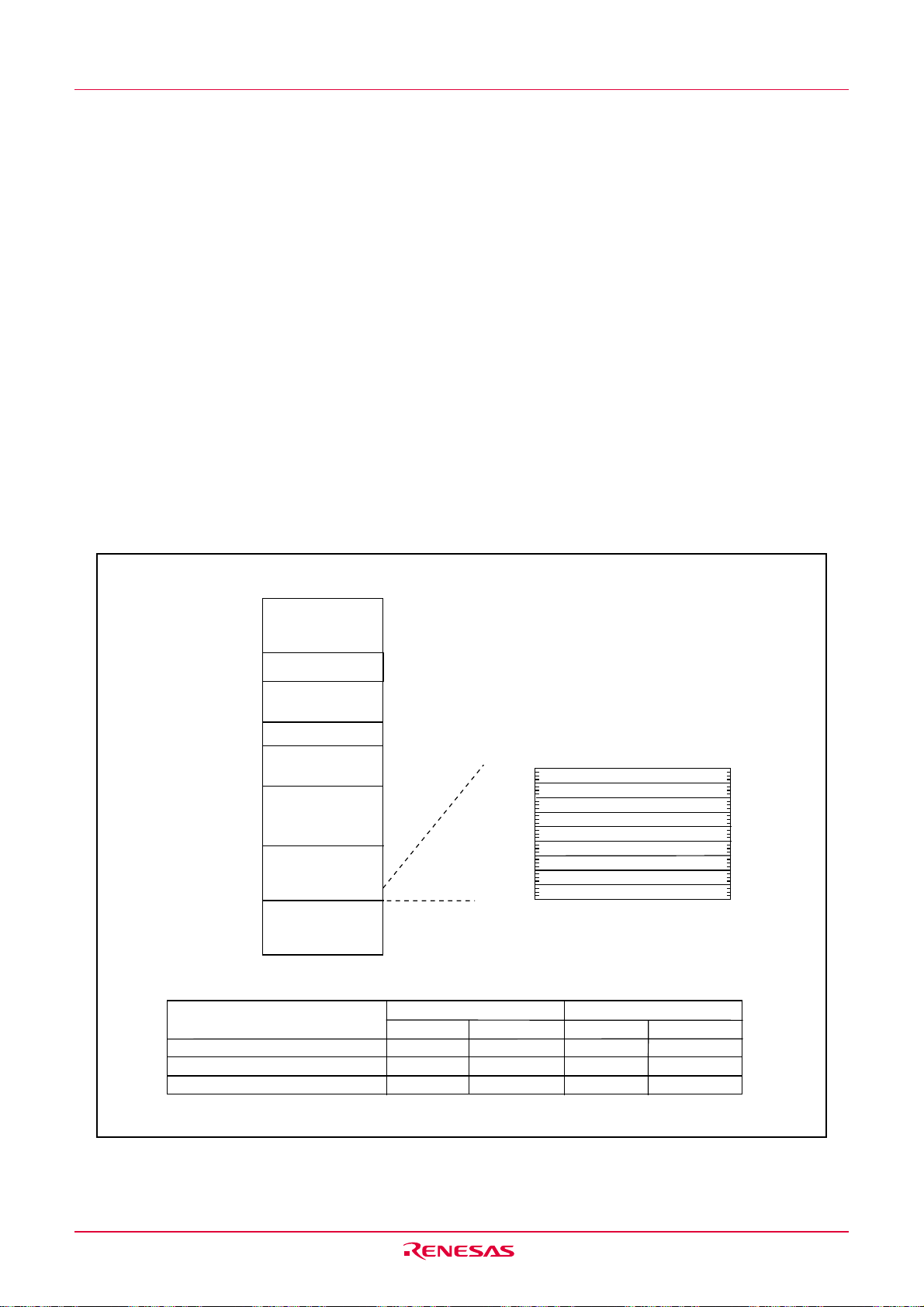

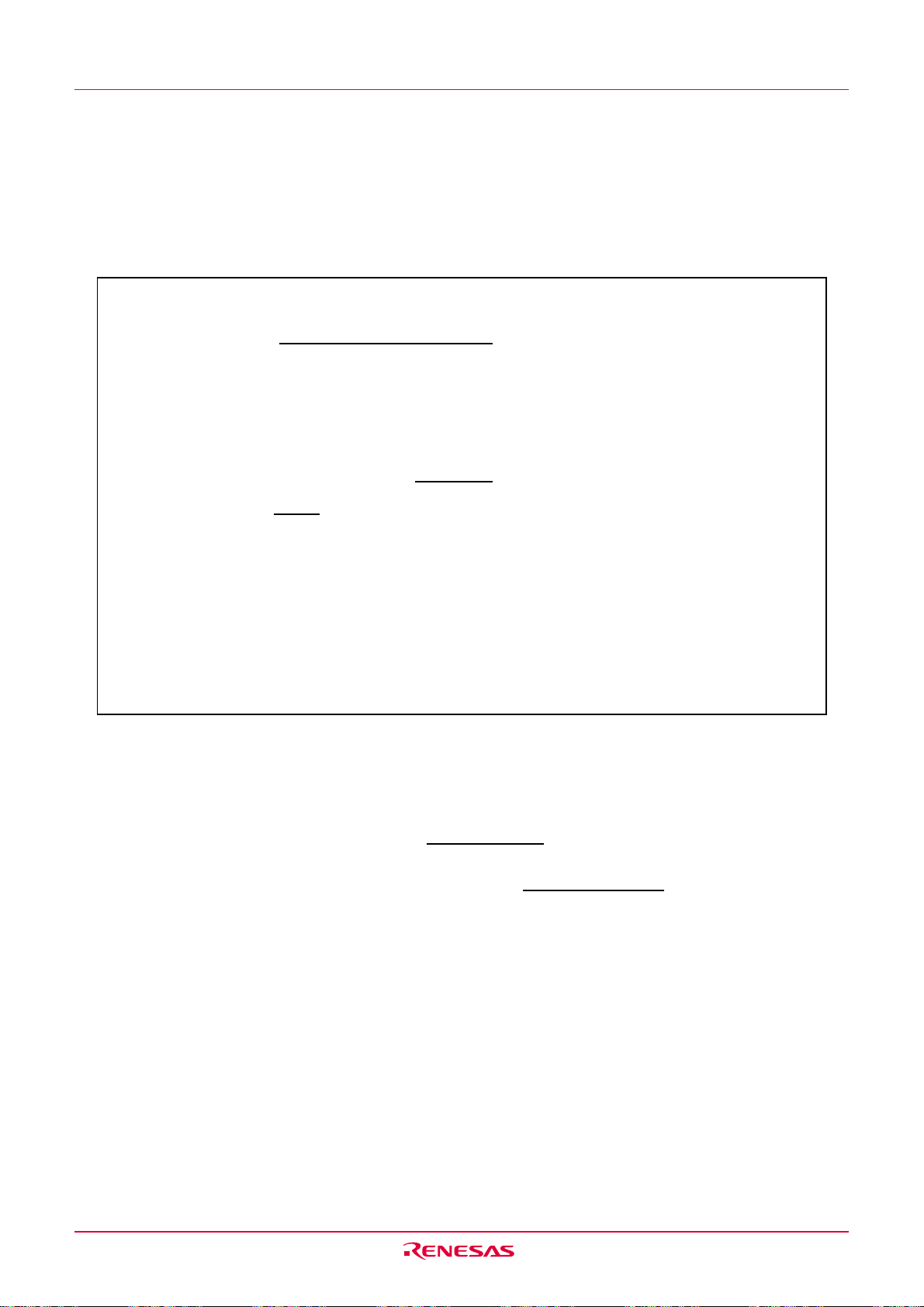

2. Register Diagram

The symbols, and descriptions, used for bit function in each register are shown below.

X X X r e g i s t e r

b 7b 6b 5b 4b 3b2b 1b 0

0

d d r e s

f t e r r e s e

X

S y m b o lA

X X XX

X X X

XXX1

(b2)

( b 3 )

XXX4

XXX5

X X X 6

X X X 7

Bit NameBit symbol

X X X B i t

N o t h i n g i s a s s i g n e d .

W h e n w r i t e , s h o u l d s e t t o " 0 " . W h e n r e a d , i t s c o n t e n t i s i n d e t e r m i n a t e .

R e s e r v e d B i t

X X X B i t

XXX Bit

sA

X0

b 1 b 0

1 0 : X X X

0 1 : X X X

1 0 : A v o i d t h i s s e t t i n g

1 1 : X X X

Must set to “0”

Function varies depending on each

operation mode

0: XXX

1: XXX

0

h

t

Function

*5

*1

Blank:Set to “0” or “1” according to the application

0: Set to “0”

1: Set to “1”

X: Nothing is assigned

*2

RW: Read and write

RO: Read only

WO: Write only

−: Nothing is assigned

*3

•Reserved bit

Reserved bit. Set to specified value.

*4

•Nothing is assigned

Nothing is assigned to the bit concerned. As the bit may be use for future functions,

set to “0” when writing to this bit.

•Do not set to this value

The operation is not guaranteed when a value is set.

•Function varies depending on mode of operation

Bit function varies depending on peripheral function mode.

Refer to respective register for each mode.

*5

Follow the text in each manual for binary and hexadecimal notations.

*1

RW

RW

RW

RW

R W

W O

R W

RO

*2

*3

*4

Page 4

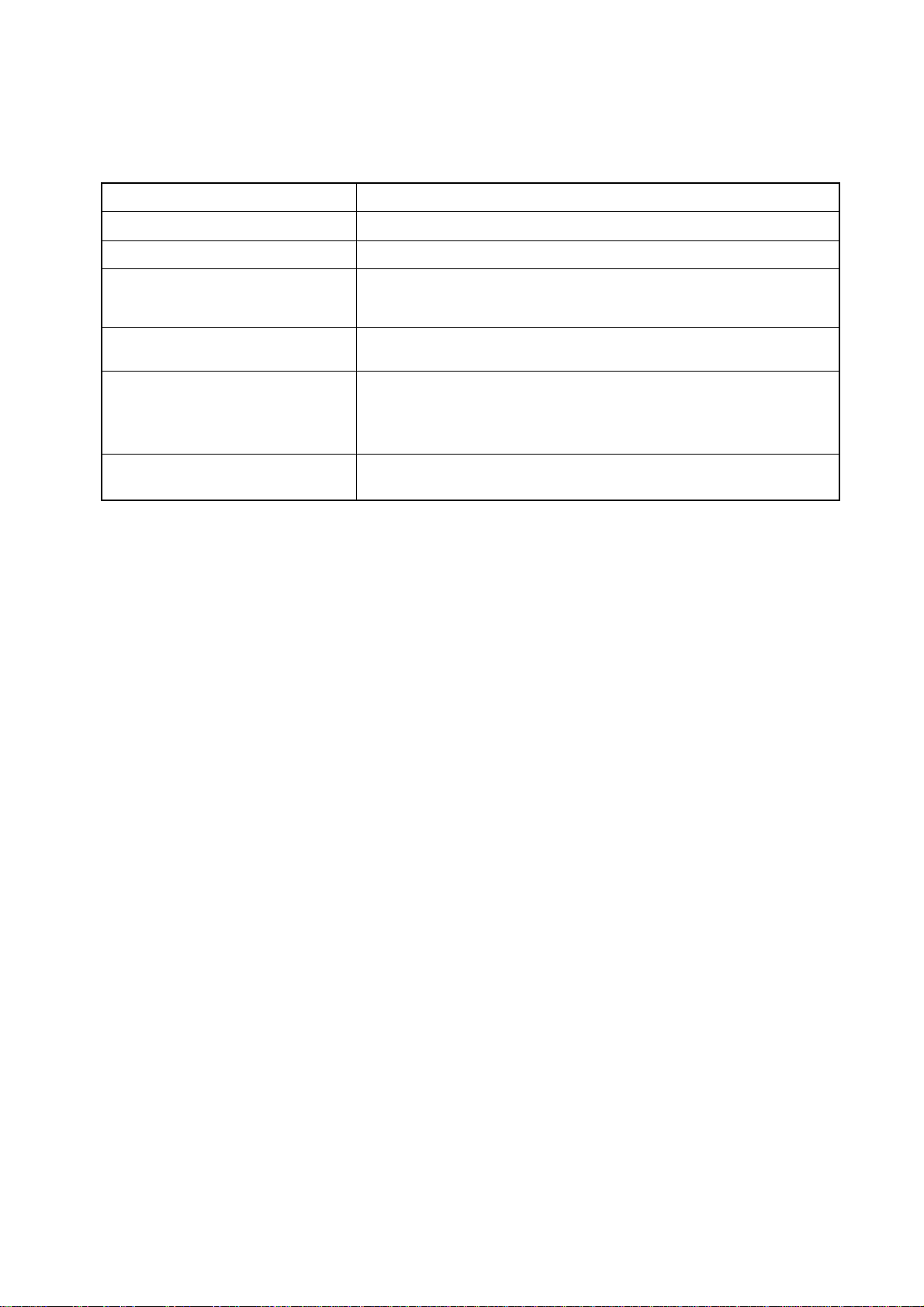

3. M16C Family Documents

The following documents were prepared for the M16C family.

(1)

Document

Short Sheet

Data Sheet

Hardware Manual

Software Manual

Application Note

RENESAS TECHNICAL UPDATE

NOTES:

1. Before using this material, please visit the our website to verify that this is the most updated

document available.

Hardware overview

Hardware overview and electrical characteristics

Hardware specifications (pin assignments, memory maps, peripheral

specifications, electrical characteristics, timing charts).

*Refer to the application note for how to use peripheral functions.

Detailed description of assembly instructions and microcomputer

performance of each instruction

• Usage and application examples of peripheral functions

• Sample programs

• Introduction to the basic functions in the M16C family

• Programming method with Assembly and C languages

Preliminary report about the specification of a product, a document,

etc.

Contents

Page 5

Table of Contents

SFR Page Reference

Chapter 1. Overview............................................................. 1

1.1 Applications ...................................................................................................................1

1.2 Performance Overview..................................................................................................2

1.3 Block Diagram ............................................................................................................... 3

1.4 Product Information ...................................................................................................... 4

1.5 Pin Assignments............................................................................................................5

1.6 Pin Description ..............................................................................................................6

Chapter 2. Central Processing Unit (CPU)......................... 7

2.1 Data Registers (R0, R1, R2 and R3 ) .............................................................................7

2.2 AddressRegisters (A0 and A1) ......................................................................................8

2.3 Frame Base Register( FB ).............................................................................................8

2.4 Interrupt Table Register (INTB ).....................................................................................8

2.5 Program Counter (PC )...................................................................................................8

2.6 User Stack Pointer (USP ) and Interrupt Stack Pointer (ISP )..................................... 8

2.7 Static Base Register (SB ) ............................................................................................. 8

2.8 Flag Register (FLG ) ....................................................................................................... 8

2.8.1 Carry Flag ( C Flag )................................................................................................................................8

2.8.2 Debug Flag ( D Flag ) ..............................................................................................................................8

2.8.3 Zero Flag ( Z Flag )..................................................................................................................................8

2.8.4 Sign Flag ( S Flag ).................................................................................................................................. 8

2.8.5 Register Bank Select Flag ( B Flag ) .....................................................................................................8

2.8.6 Overflow Flag ( O Flag)........................................................................................................................... 8

2.8.7 Interrupt Enable Flag ( I Flag ) ...............................................................................................................8

2.8.8 Stack Pointer Select Flag ( U Flag )....................................................................................................... 8

2.8.9 Processor Interrupt Priority Level ( IPL ) ..............................................................................................8

2.8.10 Reserved Area.......................................................................................................................................8

Chapter 3. Memory............................................................... 9

Chapter 4. Special Function Registers (SFR).................. 10

Chapter 5. Reset.................................................................. 14

5.1 Hardware Reset ............................................................................................................14

5.2 Software Reset..............................................................................................................14

5.3 Watchdog Timer Reset................................................................................................. 14

Chapter 6. Clock Generation Circuit.................................. 17

6.1 Main Clock.....................................................................................................................21

6.2 On-Chip Oscillator Clock .............................................................................................22

A-1

Page 6

6.3 CPU Clock and Peripheral Function Clock ................................................................ 23

6.3.1 CPU Clock.............................................................................................................................................. 23

6.3.2 Peripheral Function Clock (f1, f2, f8, f32, fAD, f1SIO, f8SIO, f32SIO) .......................................................23

6.3.3 fRING and fRING128 ...................................................................................................................................................................23

6.4 Power Control ...............................................................................................................24

6.4.1 Normal Operation Mode .......................................................................................................................24

6.4.2 Wait Mode ..............................................................................................................................................25

6.4.3 Stop Mode..............................................................................................................................................26

6.5 Oscillation Stop Detection Function...........................................................................28

6.5.1 How to Use Oscillation Stop Detection Function ..............................................................................28

Chapter 7. Protection.......................................................... 30

Chapter 8. Processor Mode................................................ 31

8.1 Types of Processor Mode ............................................................................................31

Chapter 9. Bus..................................................................... 32

Chapter 10. Interrupt........................................................... 33

10.1 Interrupt Overview......................................................................................................33

10.1.1 Type of Interrupts................................................................................................................................33

10.1.2 Software Interrupts .............................................................................................................................34

10.1.3 Hardware Interrupts............................................................................................................................35

10.1.4 Interrupts and Interrupt Vector..........................................................................................................36

10.1.5 Interrupt Control .................................................................................................................................38

______

10.2 INT Interrupt ................................................................................................................46

10.2.1 INT0 Interrupt ......................................................................................................................................46

10.2.2 INT0 Input Filter...................................................................................................................................47

10.2.3 INT1 Interrupt and INT2 Interrupt ......................................................................................................48

10.2.4 INT3 Interrupt ......................................................................................................................................49

________

_______

______ ______

______

10.3 Key Input Interrupt .....................................................................................................50

10.4 Address Match Interrupt ............................................................................................51

Chapter 11. Watchdog Timer.............................................. 53

Chapter 12. Timers.............................................................. 55

12.1 Timer X ...........................................................................................................................56

12.1.1 Timer Mode ..........................................................................................................................................58

12.1.2 Pulse Output Mode .............................................................................................................................59

12.1.3 Event Counter Mode ........................................................................................................................... 60

12.1.4 Pulse Width Measurement Mode.......................................................................................................61

12.1.5 Pulse Period Measurement Mode..................................................................................................... 63

12.2 Timer Y ...........................................................................................................................65

12.2.1 Timer Mode ..........................................................................................................................................68

12.2.2 Programmable Waveform Generation Mode ....................................................................................70

A-2

Page 7

12.3 Timer Z ...........................................................................................................................73

12.3.1 Timer Mode..........................................................................................................................................76

12.3.2 Programmable Waveform Generation Mode ....................................................................................78

12.3.3 Programmable One-shot Generation Mode...................................................................................... 80

12.3.4 Programmable Wait One-shot Generation Mode ............................................................................. 83

12.4 Timer C...........................................................................................................................86

Chapter 13. Serial Interface................................................ 89

13.1 Clock Synchronous Serial I/O Mode.........................................................................94

13.1.1 Polarity Select Function .....................................................................................................................97

13.1.2 LSB First/MSB First Select Function ................................................................................................97

13.1.3 Continuous Receive Mode ................................................................................................................. 98

13.2 Clock Asynchronous Serial I/O (UART) Mode ......................................................... 99

13.2.1 TxD10/RxD1 Select Function (UART1)............................................................................................102

13.2.2 TxD11 Select Function (UART1) ......................................................................................................102

13.2.3 Bit Rate ..............................................................................................................................................103

Chapter 14. A/D Converter................................................ 104

14.1 One-shot Mode ......................................................................................................... 108

14.2 Repeat Mode ............................................................................................................. 109

14.3 Sample & Hold .......................................................................................................... 111

14.4 A/D conversion cycles ........................................................................................... 111

14.5 Internal Equivalent Circuit of Analog Input...........................................................112

14.6 Inflow Current Bypass Circuit ................................................................................ 113

14.7 Output Impedance of Sensor under A/D Conversion........................................... 114

Chapter 15. Programmable I/O Ports .............................. 116

15. 1 Description...............................................................................................................116

15.1.1 Port Pi Direction Register (PDi Register, i = 0, 1, 3, 4)................................................................... 116

15.1.2 Port Pi Register (Pi Register, i = 0 to 4)........................................................................................... 116

15.1.3 Pull-up Control Register 0, Pull-up Control Register 1 (PUR0 and PUR1 Registers) ................. 116

15.1.4 Port P1 Drive Capacity Control Register (DRR Register)..............................................................116

15.2 Port setting................................................................................................................123

15.3 Unassigned Pin Handling ........................................................................................ 129

Chapter 16. Electrical Characteristics............................. 130

Chapter 17. Flash Memory Version ................................. 141

17.1 Overview....................................................................................................................141

17.2 Memory Map..............................................................................................................142

17.3 Functions To Prevent Flash Memory from Rewriting............................................ 143

17.3.1 ID Code Check Function ..................................................................................................................143

17.4 CPU Rewrite Mode....................................................................................................144

17.4.1 EW0 Mode..........................................................................................................................................145

17.4.2 EW1 Mode..........................................................................................................................................145

17.4.3 Software Commands ........................................................................................................................151

17.4.4 Status Register..................................................................................................................................155

17.4.5 Full Status Check..............................................................................................................................156

A-3

Page 8

17.5 Standard Serial I/O Mode .........................................................................................158

17.5.1 ID Code Check Function ..................................................................................................................158

Chapter 18. On-chip Debugger ........................................ 162

18.1 Address Match Interrupt ..........................................................................................162

18.2 Single Step Interrupt ................................................................................................162

18.3 UART1........................................................................................................................162

18.4 BRK Instrucstion ...................................................................................................... 162

Chapter 19. Usage Notes.................................................. 163

19.1 Stop Mode and Wait Mode.......................................................................................163

19.1.1 Stop Mode..........................................................................................................................................163

19.1.2 Wait Mode ..........................................................................................................................................163

19.2 Interrupt.....................................................................................................................164

19.2.1 Reading Address 0000016 ............................................................................................................................................ 164

19.2.2 SP Setting ..........................................................................................................................................164

19.2.3 External Interrupt and Key Input Interrupt .....................................................................................164

19.2.4 Watchdog Timer Interrupt ................................................................................................................164

19.2.5 Changing Interrupt Factor................................................................................................................ 165

19.2.6 Changing Interrupt Control Register ..............................................................................................166

19.3 Clock Generation Circuit ......................................................................................... 167

19.3.1 Oscillation Stop Detection Function ...............................................................................................167

19.3.2 Oscillation Circuit Constants...........................................................................................................167

19.4 Timers........................................................................................................................168

19.4.1 Timers X, Y and Z..............................................................................................................................168

19.4.2 Timer X...............................................................................................................................................168

19.4.3 Timer Y ...............................................................................................................................................168

19.4.4 Timer Z ...............................................................................................................................................168

19.4.5 Timer C...............................................................................................................................................168

19.5 Serial Interface..........................................................................................................169

19.6 A/D Converter............................................................................................................170

19.7 Flash Memory Version ............................................................................................. 171

19.7.1 CPU Rewrite Mode ............................................................................................................................171

19.8 Noise..........................................................................................................................174

Chapter 20. Usage Notes for On-chip Debugger............ 175

Appendix 1 Package Dimensions.................................... 176

Appendix 2 Connecting Examples for Serial Writer and

On-chip Debugging Emulator .......................................... 177

Appendix 3 Example of Oscillation Evaluation Circuit.. 179

Register Index ................................................................... 180

A-4

Page 9

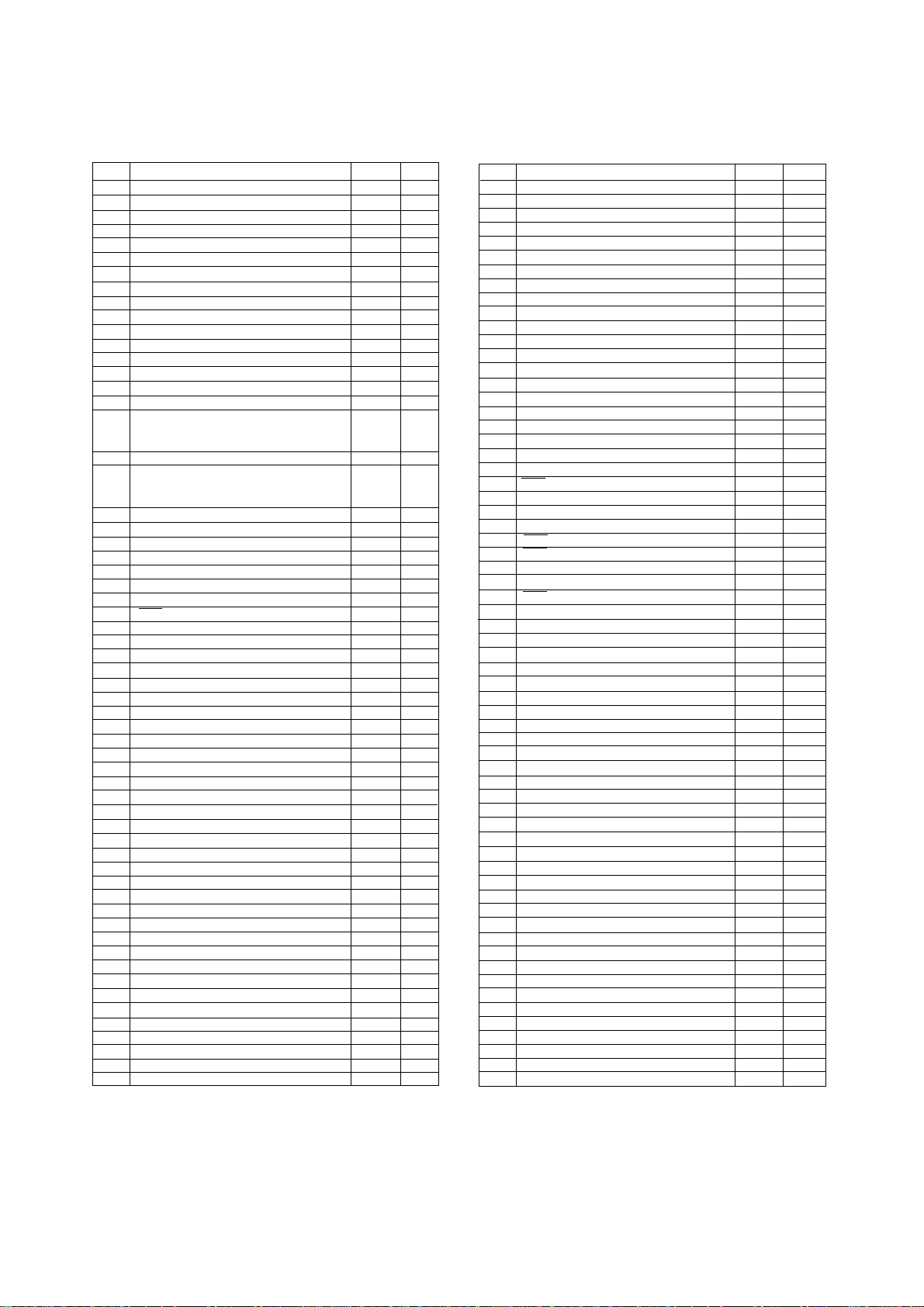

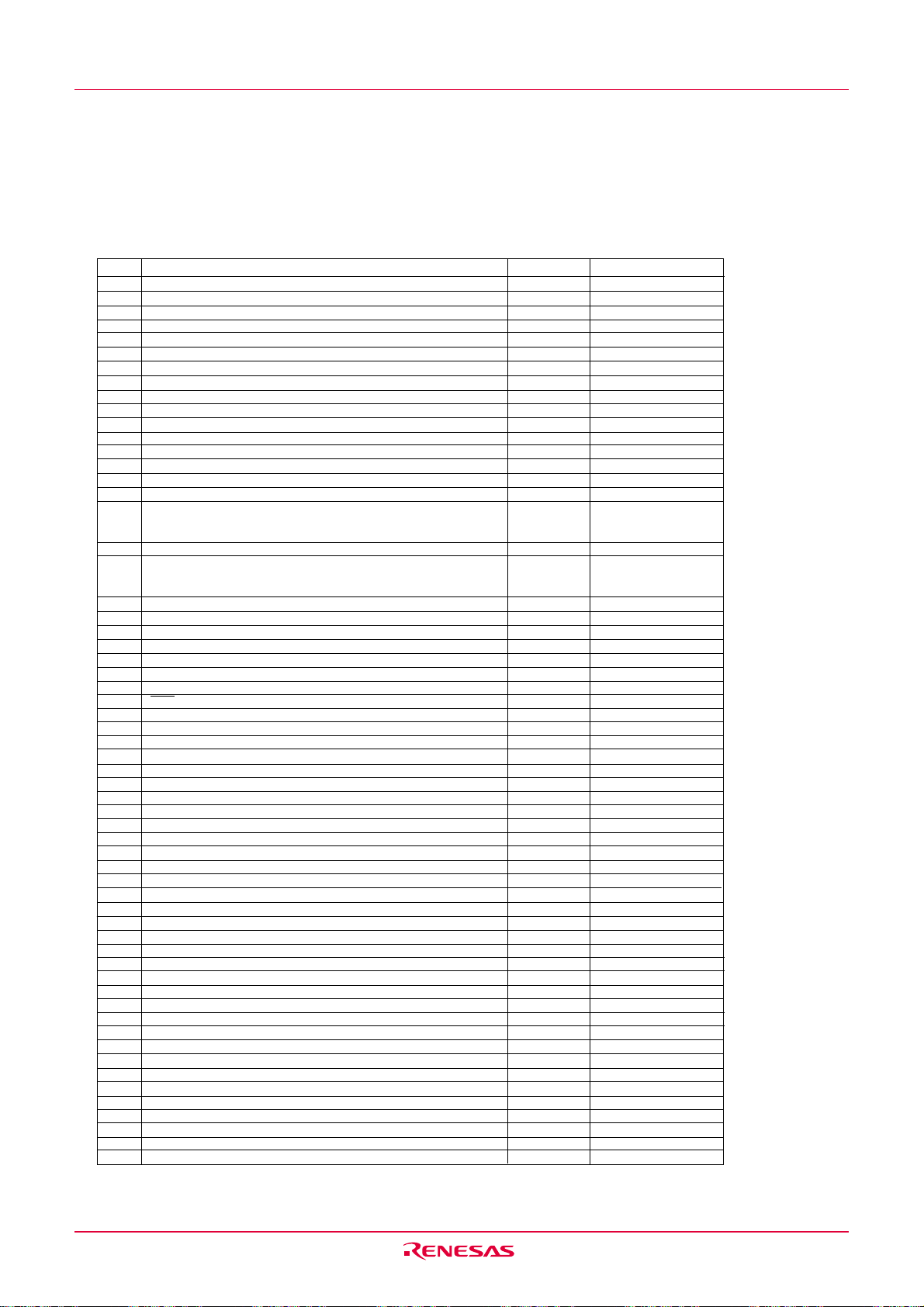

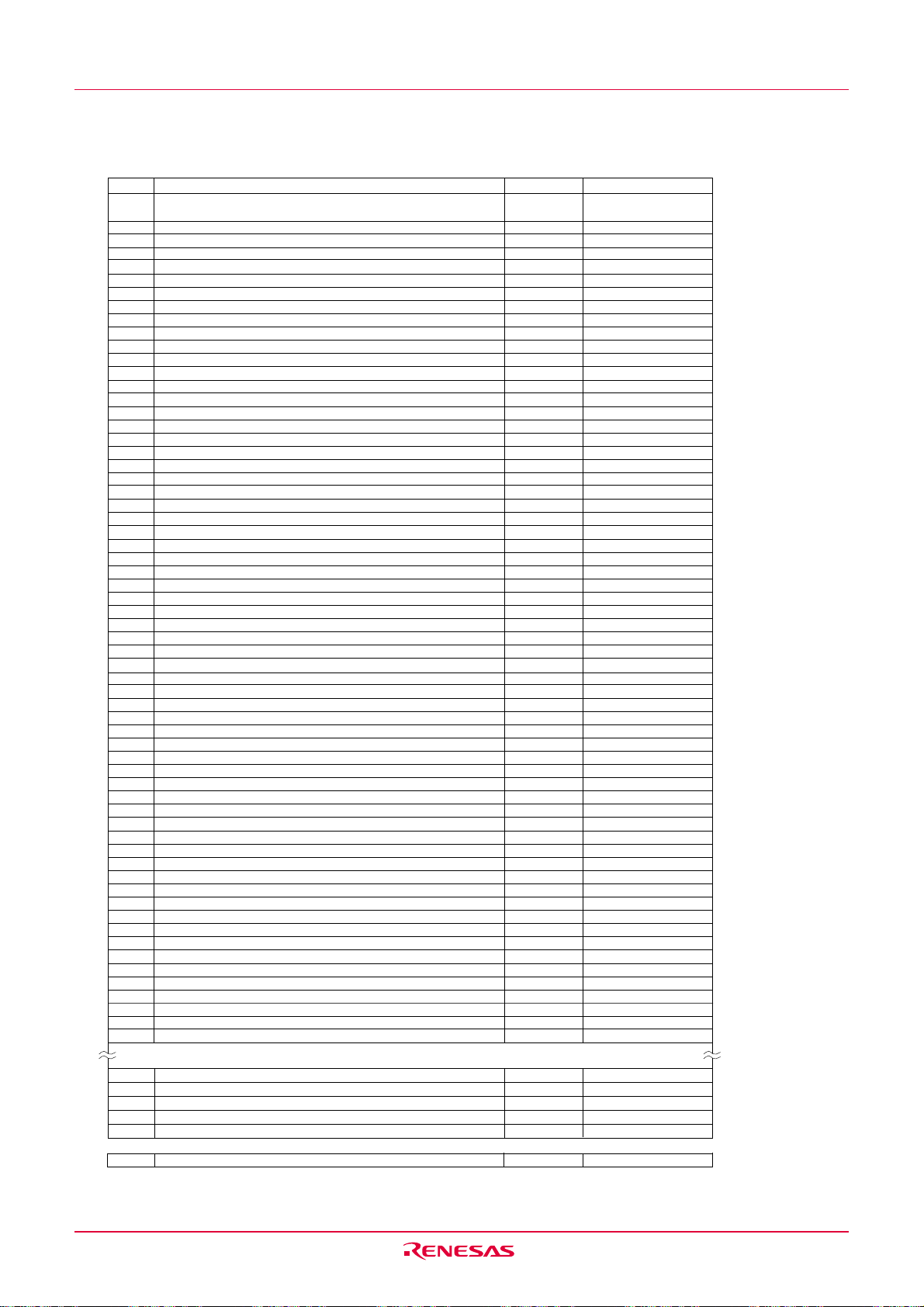

SFR Page Reference

A d d r e s s R

0 0 0 01

6

0 0 0 11

6

0 0 0 21

6

0 0 0 31

6

M

P r o c e s s o r m o d e r e g i s t e r 0P

0 0 0 41

6

M

0 0 0 51

6

P r o c e s s o r m o d e r e g i s t e r 1P

M

0 0 0 61

6

S y s t e m c l o c k c o n t r o l r e g i s t e r 0C

M

0 0 0 71

6

S y s t e m c l o c k c o n t r o l r e g i s t e r 1C

0 0 0 81

6

0 0 0 91

6

A d d r e s s m a t c h i n t e r r u p t e n a b l e r e g i s t e rA I E R5 2

R C

0 0 0 A1

6

P r o t e c t r e g i s t e rP

0 0 0 B1

6

C

0 0 0 C1

6

O s c i l l a t i o n s t o p d e t e c t i o n r e g i s t e rO

D T

0 0 0 D1

6

W a t c h d o g t i m e r r e s e t r e g i s t e rW

D T

0 0 0 E1

6

W a t c h d o g t i m e r s t a r t r e g i s t e rW

D

0 0 0 F1

6

W a t c h d o g t i m e r c o n t r o l r e g i s t e rW

M A D

0 0 1 01

6

A d d r e s s m a t c h i n t e r r u p t r e g i s t e r 0R

0 0 1 11

6

0 0 1 21

6

0 0 1 31

6

M A D

0 0 1 41

6

A d d r e s s m a t c h i n t e r r u p t r e g i s t e r 1R

0 0 1 51

6

0 0 1 61

6

0 0 1 71

6

0 0 1 81

6

0 0 1 91

6

0 0 1 A1

6

0 0 1 B1

6

0 0 1 C1

6

0 0 1 D1

6

N T 0

0 0 1 E1

6

I N T 0 i n p u t f i l t e r s e l e c t r e g i s t e rI

0 0 1 F1

6

0 0 2 01

6

0 0 2 11

6

0 0 2 21

6

0 0 2 31

6

0 0 2 41

6

0 0 2 51

6

0 0 2 61

6

0 0 2 71

6

0 0 2 81

6

0 0 2 91

6

0 0 2 A1

6

0 0 2 B1

6

0 0 2 C1

6

0 0 2 D1

6

0 0 2 E1

6

0 0 2 F1

6

0 0 3 01

6

0 0 3 11

6

0 0 3 21

6

0 0 3 31

6

0 0 3 41

6

0 0 3 51

6

0 0 3 61

6

0 0 3 71

6

0 0 3 81

6

0 0 3 91

6

0 0 3 A1

6

0 0 3 B1

6

0 0 3 C1

6

0 0 3 D1

6

0 0 3 E1

6

0 0 3 F1

6

e g i s t e

rS

y m b o l

P a g e

03 1

13 1

01 9

11 9

R3 0

D2 0

R5 4

S5 4

C5 4

05 2

15 2

F4 6

Blank columns are all reserved space. No use is allowed.

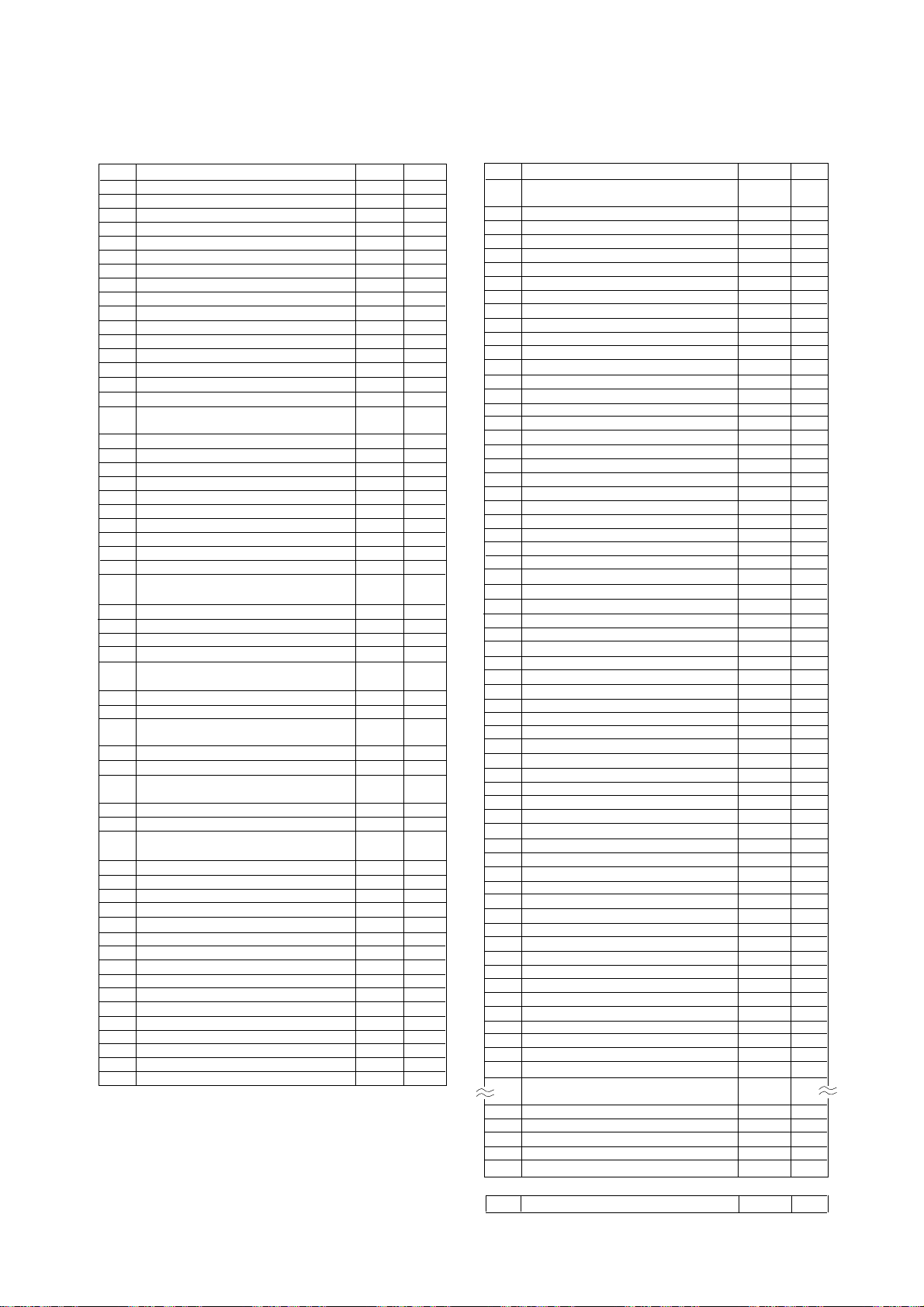

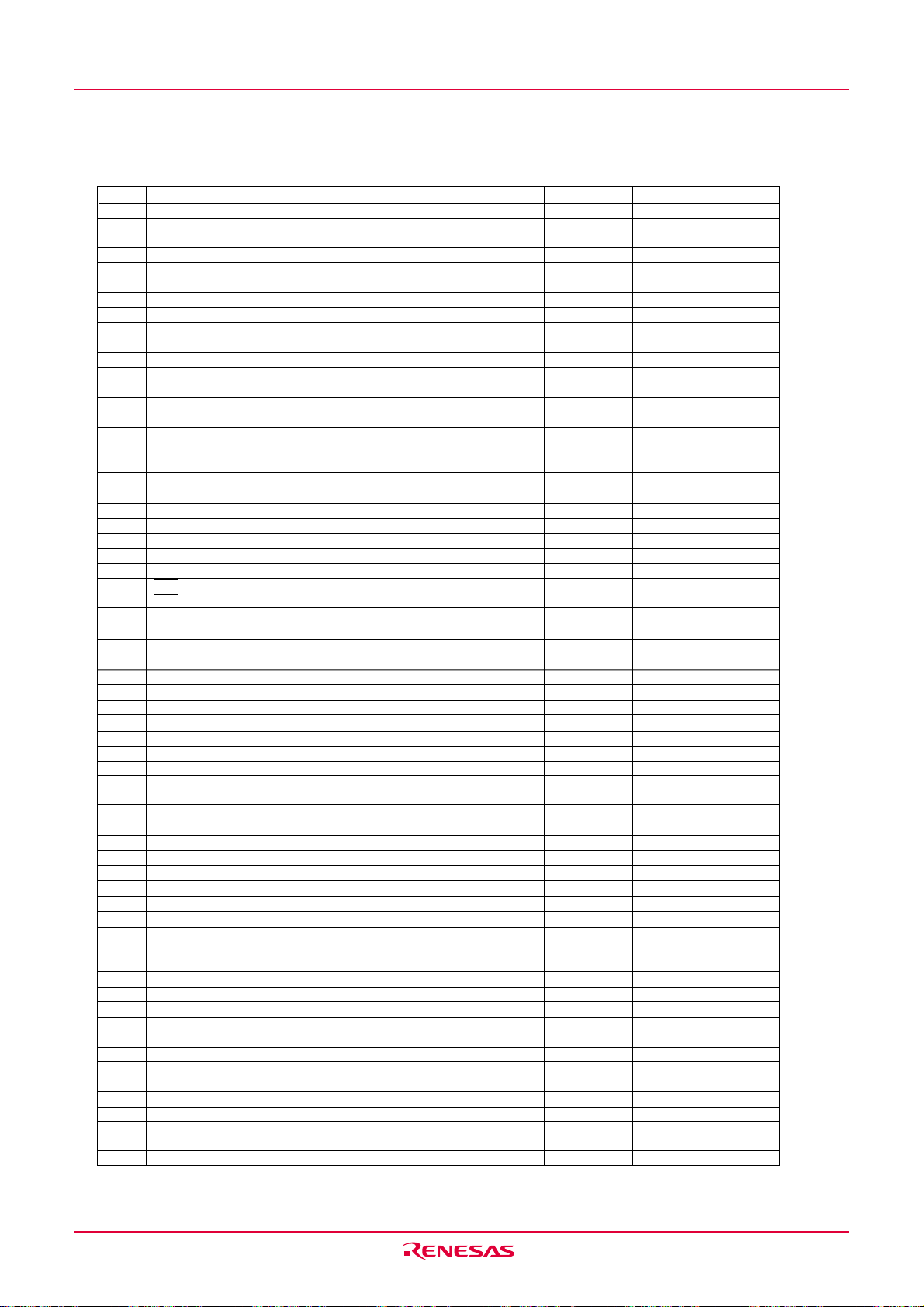

A d d r e s s R

0 0 4 01

6

0 0 4 11

6

0 0 4 21

6

0 0 4 31

6

0 0 4 41

6

0 0 4 51

6

0 0 4 61

6

0 0 4 71

6

0 0 4 81

6

0 0 4 91

6

0 0 4 A1

6

0 0 4 B1

6

0 0 4 C1

6

U P I

0 0 4 D1

6

K e y i n p u t i n t e r r u p t c o n t r o l r e g i s t e rK

0 0 4 E1

6

A D c o n v e r s i o n i n t e r r u p t c o n t r o l r e g i s t e rA D I C3 9

0 0 4 F1

6

0 0 5 01

6

0 T I

0 0 5 11

6

U A R T 0 t r a n s m i t i n t e r r u p t c o n t r o l r e g i s t e r S

0 R I

0 0 5 21

6

U A R T 0 r e c e i v e i n t e r r u p t c o n t r o l r e g i s t e r S

1 T I

0 0 5 31

6

U A R T 1 t r a n s m i t i n t e r r u p t c o n t r o l r e g i s t e r S

1 R I

0 0 5 41

6

U A R T 1 r e c e i v e i n t e r r u p t c o n t r o l r e g i s t e r S

N T 2 I

0 0 5 51

6

I N T 2 i n t e r r u p t c o n t r o l r e g i s t e rI

X I

0 0 5 61

6

T i m e r X i n t e r r u p t c o n t r o l r e g i s t e rT

Y I

0 0 5 71

6

T i m e r Y i n t e r r u p t c o n t r o l r e g i s t e rT

Z I

0 0 5 81

6

T i m e r Z i n t e r r u p t c o n t r o l r e g i s t e rT

N T 1 I

0 0 5 91

6

I N T 1 i n t e r r u p t c o n t r o l r e g i s t e rI

N T 3 I

0 0 5 A1

6

I N T 3 i n t e r r u p t c o n t r o l r e g i s t e rI

C I

0 0 5 B1

6

T i m e r C i n t e r r u p t c o n t r o l r e g i s t e rT

0 0 5 C1

6

N T 0 I

0 0 5 D1

6

I N T 0 i n t e r r u p t c o n t r o l r e g i s t e rI

0 0 5 E1

6

0 0 5 F1

6

0 0 6 01

6

0 0 6 11

6

0 0 6 21

6

0 0 6 31

6

0 0 6 41

6

0 0 6 51

6

0 0 6 61

6

0 0 6 71

6

0 0 6 81

6

0 0 6 91

6

0 0 6 A1

6

0 0 6 B1

6

0 0 6 C1

6

0 0 6 D1

6

0 0 6 E1

6

0 0 6 F1

6

0 0 7 01

6

0 0 7 11

6

0 0 7 21

6

0 0 7 31

6

0 0 7 41

6

0 0 7 51

6

0 0 7 61

6

0 0 7 71

6

0 0 7 81

6

0 0 7 91

6

0 0 7 A1

6

0 0 7 B1

6

0 0 7 C1

6

0 0 7 D1

6

0 0 7 E1

6

0 0 7 F1

6

e g i s t e

rS

y m b o l

P a g e

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

C3 9

B-1

Page 10

SFR Page Reference

A d d r e s s R

Y Z M

0 0 8 01

6

T i m e r Y , Z m o d e r e g i s t e rT

R E

Pr e s c a l e r Y r e g i s t e rP

0 0 8 11

6

Y S

T i m e r Y s e c o n d a r y r e g i s t e rT

0 0 8 21

6

Y P

T i m e r Y p r i m a r y r e g i s t e rT

0 0 8 31

6

U

T i m e r Y , Z w a v e f o r m o u t p u t c o n t r o l r e g i s t e r P

0 0 8 41

6

R E

Pr e s c a l e r Z r e g i s t e rP

0 0 8 51

6

Z S

T i m e r Z s e c o n d a r y r e g i s t e rT

0 0 8 61

6

Z P

T i m e r Z p r i m a r y r e g i s t e rT

0 0 8 71

6

0 0 8 81

6

0 0 8 91

6

Y Z O

T i m e r Y , Z o u t p u t c o n t r o l r e g i s t e rT

0 0 8 A1

6

X M

T i m e r X m o d e r e g i s t e rT

0 0 8 B1

6

R E

Pr e s c a l e r X r e g i s t e rP

0 0 8 C1

6

T i m e r X r e g i s t e r r e g i s t e rT

0 0 8 D1

6

C S

T i m e r c o u n t s o u r c e s e t t i n g r e g i s t e rT

0 0 8 E1

6

0 0 8 F1

6

0 0 9 01

6

T i m e r C r e g i s t e rT

0 0 9 11

6

0 0 9 21

6

0 0 9 31

6

0 0 9 41

6

0 0 9 51

6

N T E

E x t e r n a l i n p u t e n a b l e r e g i s t e rI

0 0 9 61

6

0 0 9 71

6

I E

K e y i n p u t e n a b l e r e g i s t e rK

0 0 9 81

6

0 0 9 91

6

C C

T i m e r C c o n t r o l r e g i s t e r 0T

0 0 9 A1

6

C C

T i m e r C c o n t r o l r e g i s t e r 1T

0 0 9 B1

6

M

C a p t u r e r e g i s t e rT

0 0 9 C1

6

0 0 9 D1

6

0 0 9 E1

6

0 0 9 F1

6

0 M

0 0 A 01

6

U A R T 0 t r a n s m i t / r e c e i v e m o d e r e g i s t e r U

0 B R

0 0 A 11

6

U A R T 0 b i t r a t e g e n e r a t o r U

0 T

0 0 A 21

6

U A R T 0 t r a n s m i t b u f f e r r e g i s t e rU

0 0 A 31

6

0 C

0 0 A 41

6

U A R T 0 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 0 U

0 C

0 0 A 51

6

U A R T 0 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 1 U

0 R

0 0 A 61

6

U A R T 0 r e c e i v e b u f f e r r e g i s t e r U

0 0 A 71

6

1 M

0 0 A 81

6

U A R T 1 t r a n s m i t / r e c e i v e m o d e r e g i s t e r U

1 B R

0 0 A 91

6

U A R T 1 b i t r a t e g e n e r a t o rU

1 T

0 0 A A1

6

U A R T 1 t r a n s m i t b u f f e r r e g i s t e rU

0 0 A B1

6

1 C

0 0 A C1

6

U A R T 1 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 0 U

1 C

0 0 A D1

6

U A R T 1 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 1 U

1 R

0 0 A E1

6

U A R T 1 r e c e i v e b u f f e r r e g i s t e r U

0 0 A F1

6

C O

0 0 B 01

0 0 B 11

0 0 B 21

0 0 B 31

0 0 B 41

0 0 B 51

0 0 B 61

0 0 B 71

0 0 B 81

0 0 B 91

0 0 B A1

0 0 B B1

0 0 B C1

0 0 B D1

0 0 B E1

0 0 B F1

6

6

6

6

6

6

6

6

6

6

6

6

6

6

t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 2 U

U A R T

6

6

e g i s t e

rS

y m b o l

P a g e

R6 5 / 7 3

Y6 6

C6 6

R6 6

M6 7 / 7 5

Z7 4

C7 4

R7 4

C6 6 / 7 4

R5 6

X5 7

X5 7

S5 7

C8

N4 6

N5 0

08 7

18 7

08 7

R9 2

G9 1

B9 1

09 2

19 3

B9 1

R9 2

G9 1

B9 1

09 2

19 3

B9 1

N9 3

7

Blank columns are all reserved space. No use is allowed.

A d d r e s s

0 0 C 0

0 0 C 1

0 0 C 2

0 0 C 3

0 0 C 4

0 0 C 5

0 0 C 6

0 0 C 7

0 0 C 8

0 0 C 9

0 0 C A

0 0 C B

0 0 C C

0 0 C D

0 0 C E

0 0 C F

0 0 D 0

0 0 D 1

0 0 D 2

0 0 D 3

0 0 D 4

0 0 D 5

0 0 D 6

0 0 D 7

0 0 D 8

0 0 D 9

0 0 D A

0 0 D B

0 0 D C

0 0 D D

0 0 D E

0 0 D F

00E0

00E1

00E2

00E3

00E4

00E5

00E6

00E7

00E8

00E9

00EA

00EB

00EC

00ED

00EE

00EF

00F0

00F1

00F2

00F3

00F4

00F5

00F6

00F7

00F8

00F9

03FA

00FB

00FC

00FD

00FE

00FF

01B3

01B4

01B5

01B6

01B7

1 6

A D r e g i s t e rA

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

D C O N 21 0

A D c o n t r o l r e g i s t e r 2A

1 6

1 6

D C O N 01 0

A D c o n t r o l r e g i s t e r 0A

1 6

D C O N 11 0

A D c o n t r o l r e g i s t e r 1 A

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

1 6

Port P0 register P0 121

16

16

Port P1 register P1 121

16

Port P0 direction register PD0 121

D

16

P o r t P 1 d i r e c t i o n r e g i s t e rP

16

16

P o r t P 3 r e g i s t e rP

16

D

P o r t P 3 d i r e c t i o n r e g i s t e rP

16

P o r t P 4 r e g i s t e rP

16

16

16

Port P4 direction register PD4 121

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

Pull-up control register 0 PUR0 122

U R

16

P u l l - u p c o n t r o l r e g i s t e r 1 P

P o r t P 1 d r i v e c a p a c i t y c o n t r o l r e g i s t e r D R R1 2 2

16

16

M R

16

F l a s h m e m o r y c o n t r o l r e g i s t e r 4 F

16

16

Flash memory control register 1 FMR1 148

16

M R

16

F l a s h m e m o r y c o n t r o l r e g i s t e r 0 F

R e g i s t e rS

y m b o l

Page

D1 0 7

11 2 1

31 2 1

31 2 1

41 2 1

11 2 2

41 4 8

01 4 7

7

6

6

B-2

0 F F F F

F

1 6

O p t i o n f u n c t i o n s e l e c t r e g i s t e rO

S 5 4

Page 11

R8C/12 Group

REJ09B0110-0120

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

1. Overview

This MCU is built using the high-performance silicon gate CMOS process using a R8C Tiny Series CPU

core and is packaged in a 32-pin plastic molded LQFP. This MCU operates using sophisticated instructions

featuring a high level of instruction efficiency. With 1M bytes of address space, it is capable of executing

instructions at high speed.

The data flash ROM (2 KB X 2 blocks) is embedded.

1.1 Applications

Electric household appliance, office equipment, housing equipment (sensor, security), general industrial

equipment, audio, etc.

Rev.1.20

Jan 27, 2006

Rev.1.20 Jan 27, 2006 page 1 of 181

REJ09B0110-0120

Page 12

R8C/12 Group 1. Overview

1.2 Performance Overview

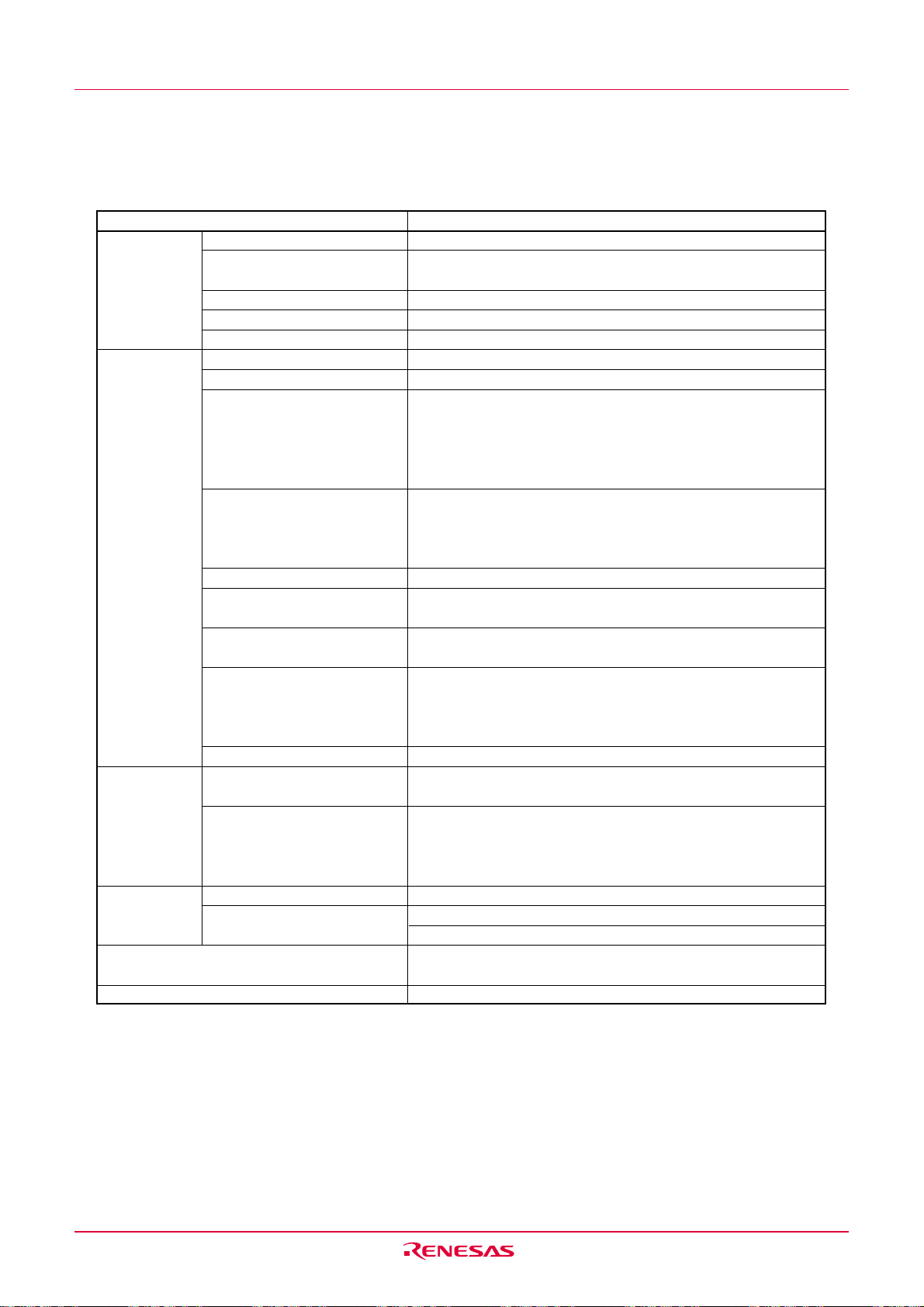

Table 1.1. lists the performance outline of this MCU.

Table 1.1 Performance outline

Item Performance

CPU Number of basic instructions 89 instructions

Minimum instruction execution time

Operating mode Single-chip

Address space 1M bytes

Memory capacity See Table 1.2 “Product List”

Peripheral Port Input/Output: 22 (including LED drive port), Input: 2

function LED drive port I/O port: 8

Timer Timer X: 8 bits x 1 channel, Timer Y: 8 bits x 1 channel,

Serial Interface •1 channel

A/D converter 10-bit A/D converter: 1 circuit, 8 channels

Watchdog timer 15 bits x 1 (with prescaler)

Interrupt Internal: 9 factors, External: 5 factors,

Clock generation circuit 2 circuits

Oscillation stop detection function

Electrical Supply voltage VCC = 3.0 to 5.5 V (f(XIN) = 16 MHZ)

characteristics

Power consumption Typ.8mA (VCC = 5.0 V (f(XIN) = 16 MHZ)

Flash memory Program/erase supply voltage

Program/erase endurance 10,000 times (Data flash)

Operating ambient temperature -20 to 85 °C

Package 32-pin plastic mold LQFP

62.5 ns (f(XIN) = 16 MHZ, VCC = 3.0 to 5.5 V)

100 ns (f(XIN) = 10 MHZ, VCC = 2.7 to 5.5 V)

Timer Z: 8 bits x 1 channel

(Each timer equipped with 8-bit prescaler)

Timer C: 16 bits x 1 channel

(Input capture circuit)

Clock synchronous, UART

•1 channel

UART

Reset start function selectable

Software: 4 factors, Priority level: 7 levels

•Main clock generation circuit (Equipped with a built-in

feedback resistor)

•On-chip oscillator

Main clock oscillation stop detection function

VCC = 2.7 to 5.5 V (f(XIN) = 10 MHZ)

Typ.5mA (VCC = 3.0 V, (f(XIN) = 10 MHZ)

Typ.35µA (VCC = 3.0 V, Wait mode, peripheral clock stops)

Typ.0.7µA (VCC = 3.0 V, Stop mode)

VCC = 2.7 to 5.5 V

1,000 times (Program ROM)

-40 to 85 °C (D-version)

Rev.1.20 Jan 27, 2006 page 2 of 181

REJ09B0110-0120

Page 13

R8C/12 Group 1. Overview

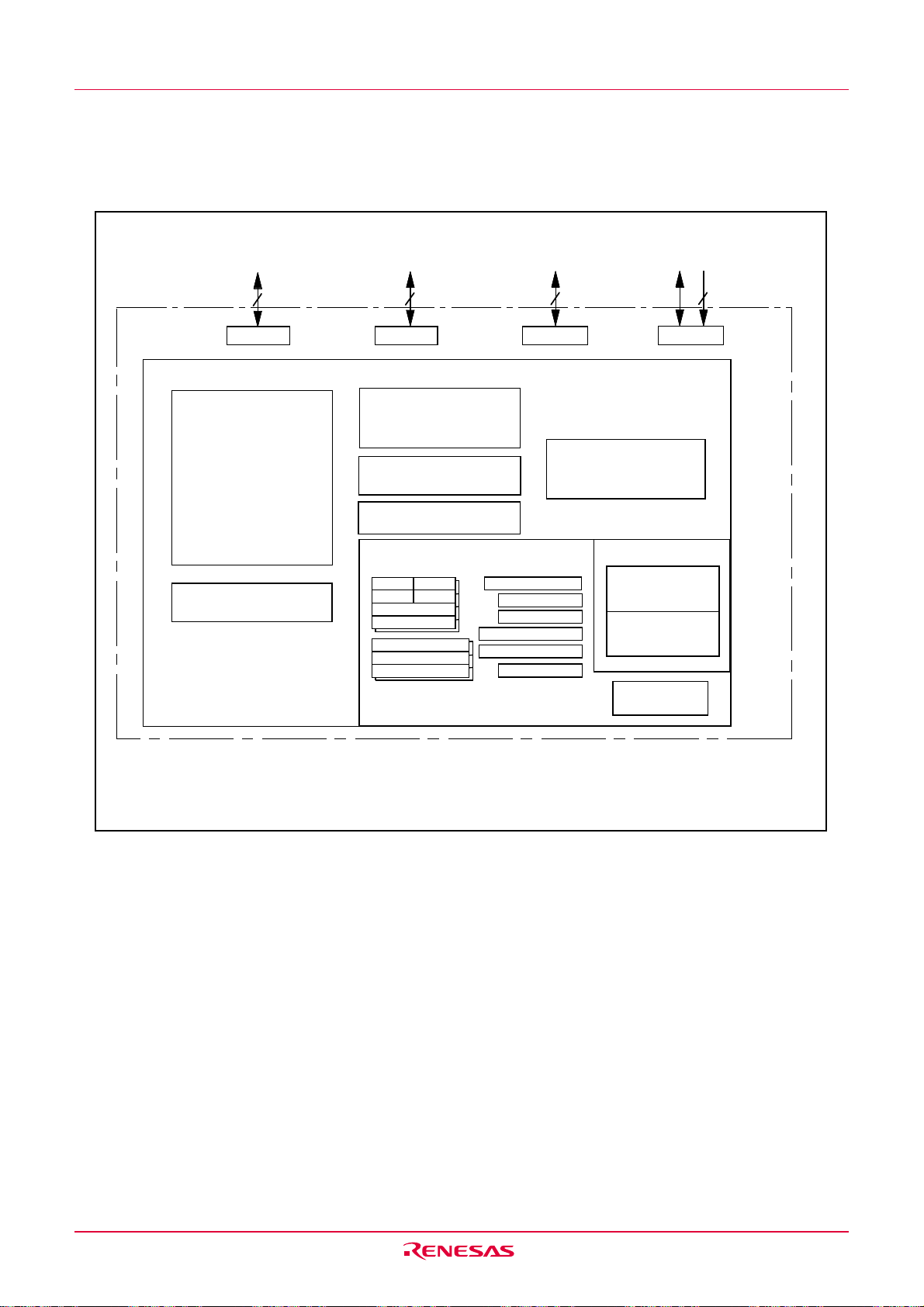

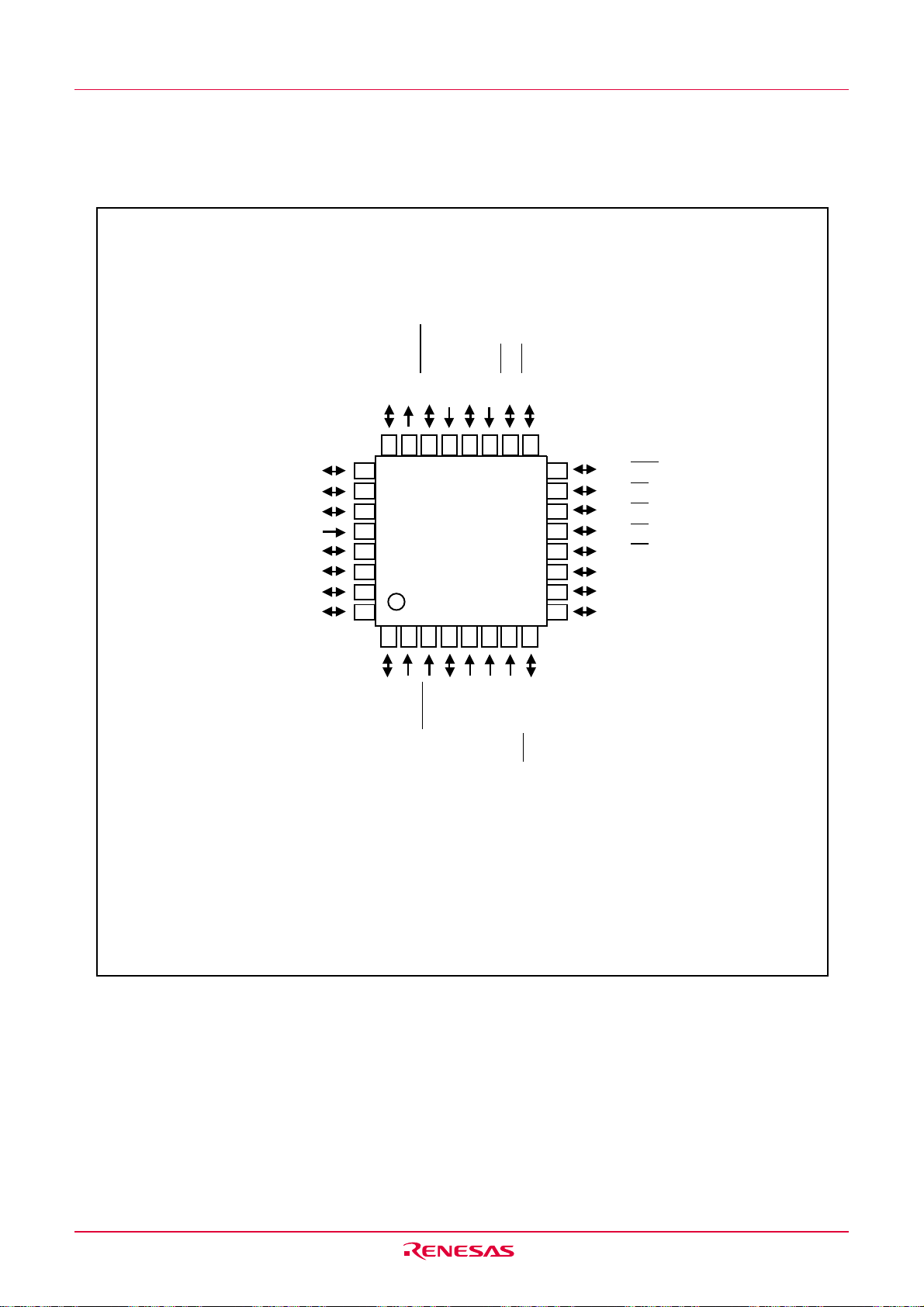

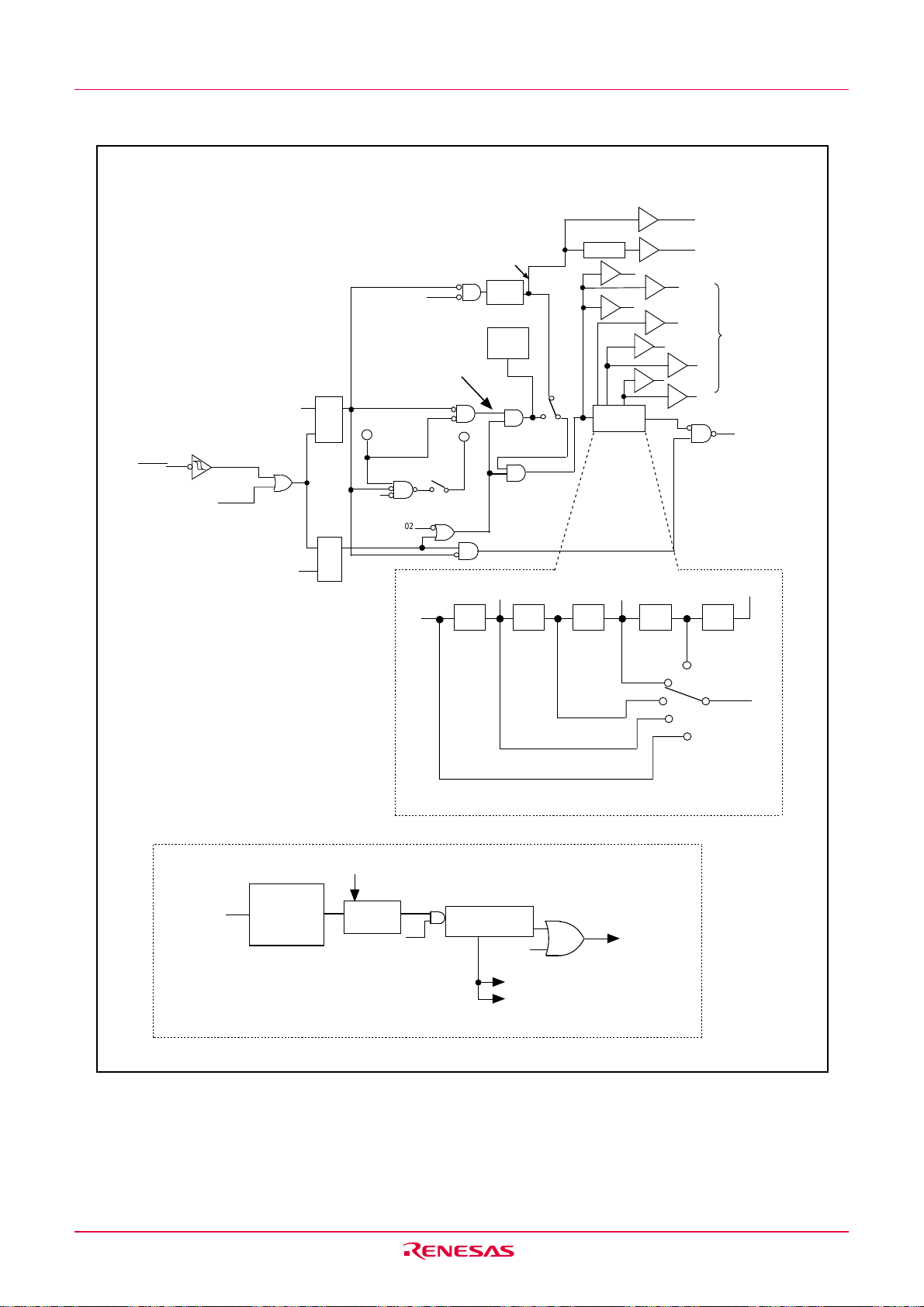

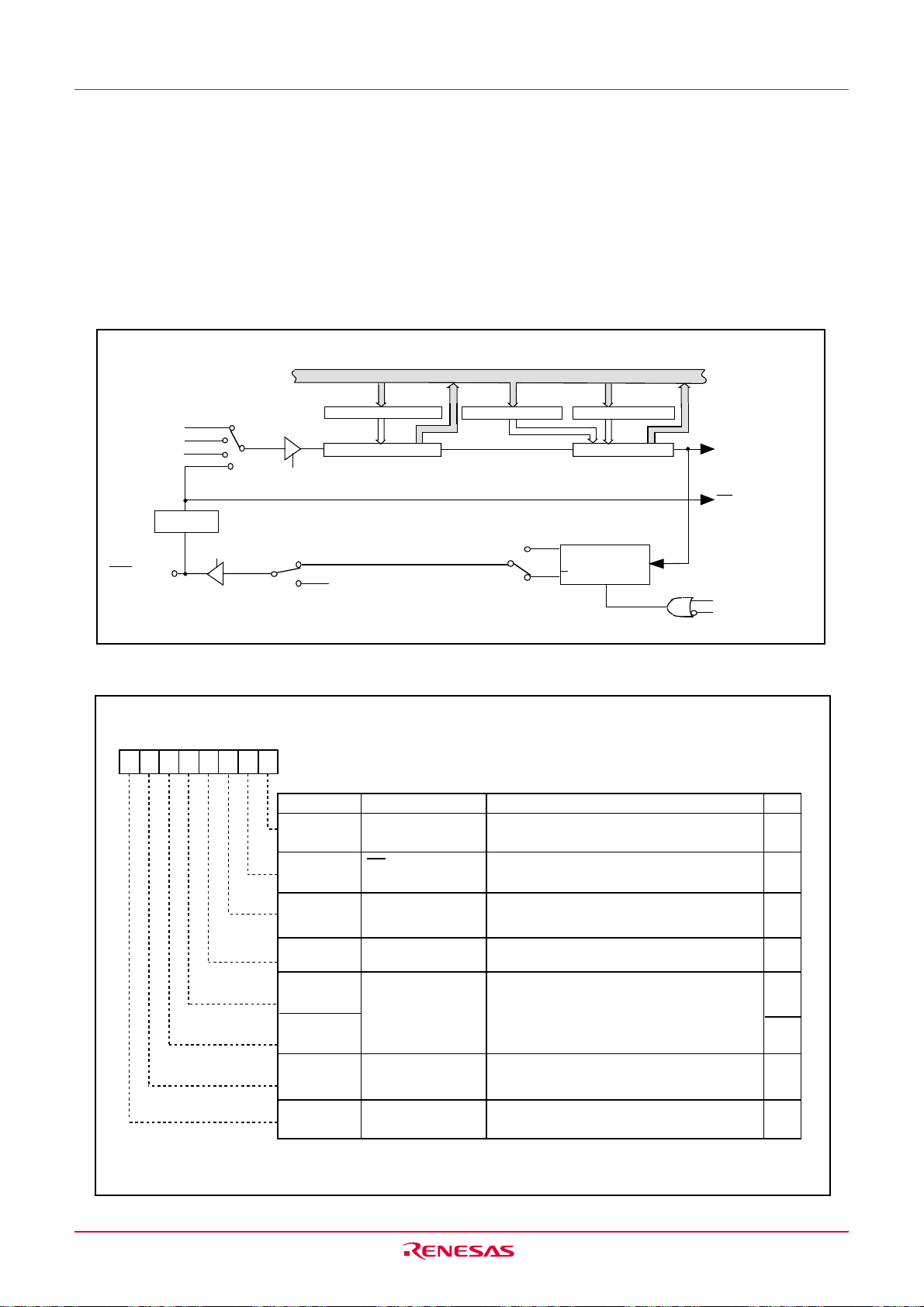

1.3 Block Diagram

Figure 1.1. shows this MCU block diagram.

I / O p o r t

P o r t P 0

Pe r i p h e r a l f u n c t i o n s

T i m e r

T i m e r X ( 8 b i t s )

T i m e r Y ( 8 b i t s )

T i m e r Z ( 8 b i t s )

T i m e r C ( 1 6 b i t s )

Watchdog timer

(15 bits)

ROM

RAM

1 2

Port P4

(1)

(2)

8

8

Port P1

A / D c o n v e r t e r

( 1 0 b i t s ✕ 8 c h a n n e l s )

U A R T o r C l o c k s y n c h r o n o u s

s e r i a l I / O

( 8 b i t s ✕ 1 c h a n n e l )

U A R T

( 8 b i t s ✕ 1 c h a n n e l )

R8C/Tiny Series CPU core

R0LR0H

R1H R1L

R 2

R3

A 0

A1

FB

P o r t P 3

S B

USP

I S P

INTB

PC

FLG

5

System clock generator

I N

- X

O U T

X

O n - c h i p o s c i l l a t o r

M e m o r y

M u l t i p l i e r

Figure 1.1 Block Diagram

NOTES:

1. ROM size depends on MCU type.

2. RAM size depends on MCU type.

Rev.1.20 Jan 27, 2006 page 3 of 181

REJ09B0110-0120

Page 14

R8C/12 Group 1. Overview

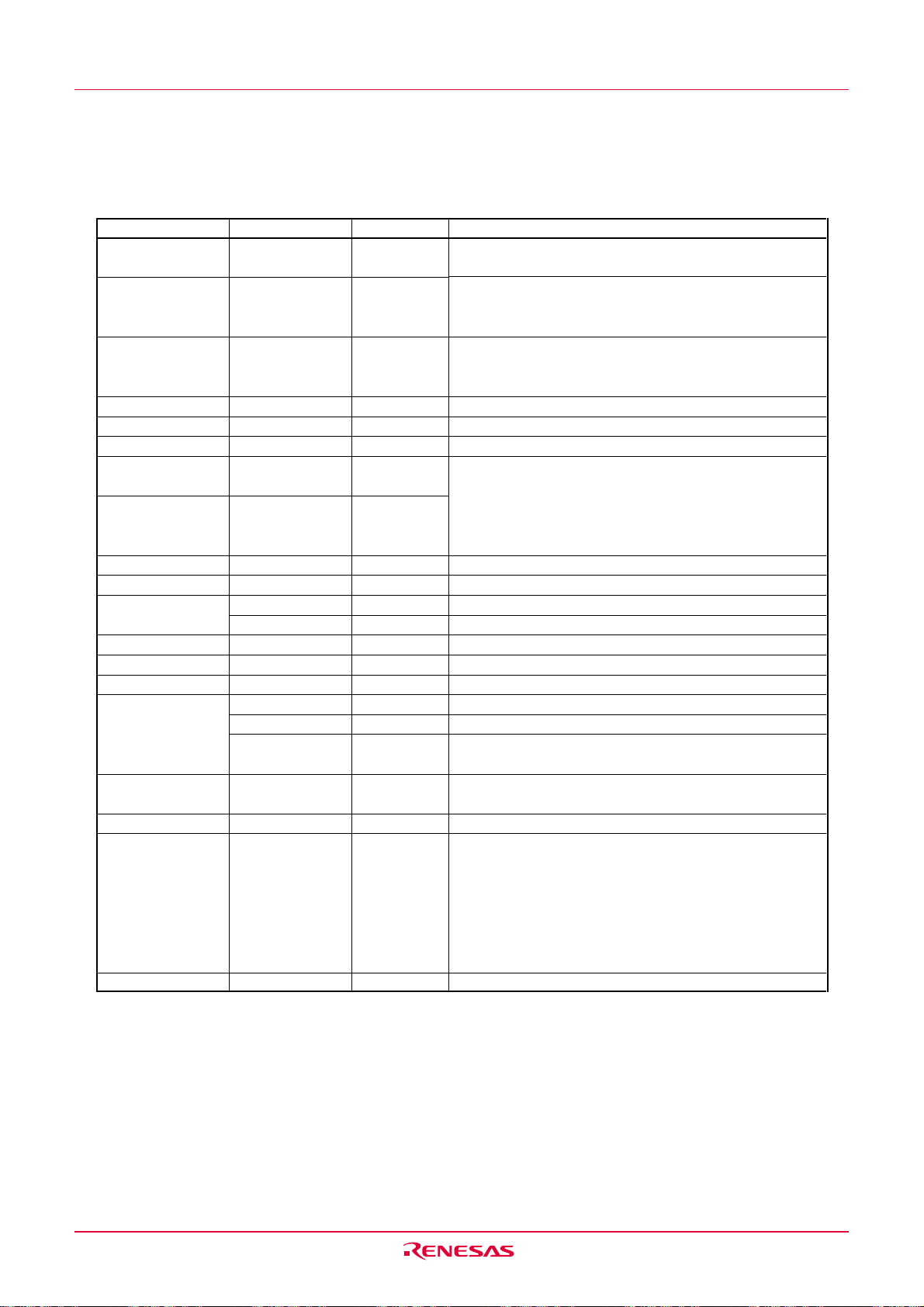

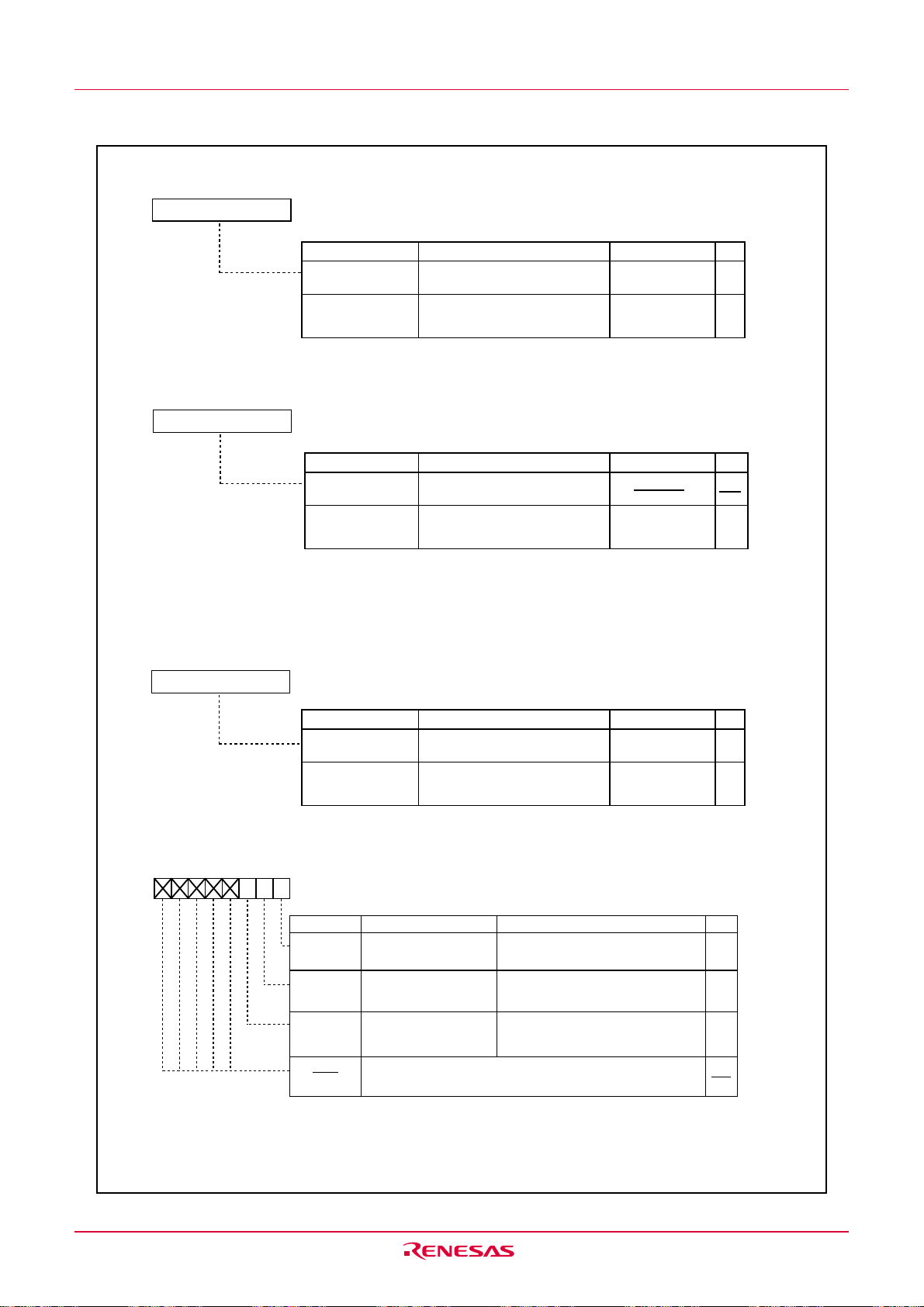

1.4 Product Information

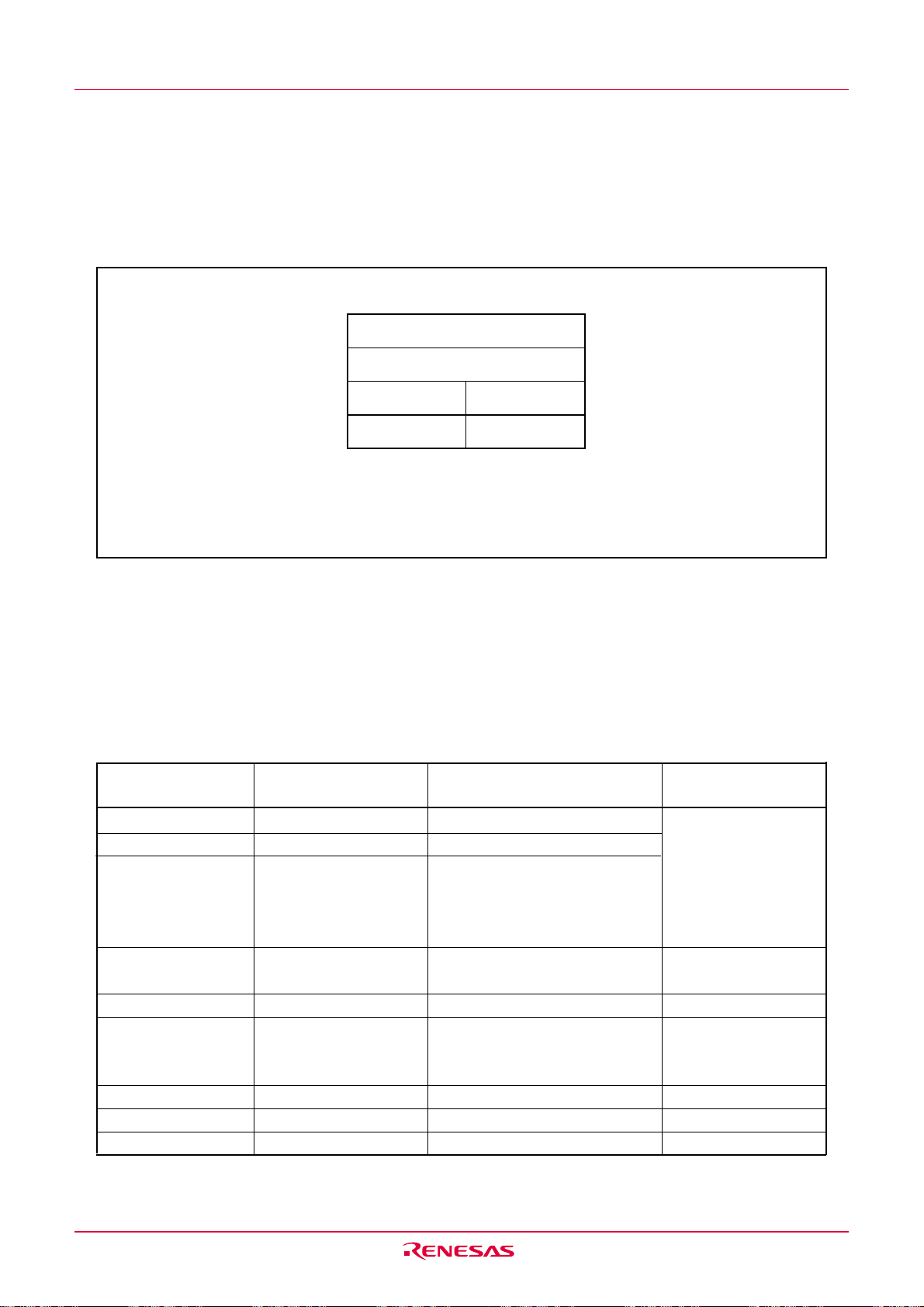

Table 1.2 lists the product information.

Table 1.2 Product Information

Type No.

R5F21122FP

R5F21123FP

R5F21124FP

R5F21122DFP

R5F21123DFP

R5F21124DFP

ROM capacity

Program ROM

8K bytes

12K bytes

16K bytes

8K bytes

12K bytes

16K bytes

T y p e N o .R 5 F 2 11 24DF P

Data flash

2K bytes x 2

2K bytes x 2

2K bytes x 2

2K bytes x 2

2K bytes x 2

2K bytes x 2

As of January 2006

RAM capacity

512 bytes

768 bytes

1K bytes

512 bytes

768 bytes

1K bytes

P a c k a g e t y p e :

F P : P L Q P 0 0 3 2 G B - A

C l a s s i f i c a t i o n :

D : O p e r a t i n g a m b i e n t t e m p e r a t u r e – 4 0 ° C t o 8 5 ° C

N o s y m b o l : O p e r a t i n g a m b i e n t t e m p e r a t u r e – 2 0 ° C t o 8 5 ° C

Package type

PLQP0032GB-A

PLQP0032GB-A

PLQP0032GB-A

PLQP0032GB-A

PLQP0032GB-A

PLQP0032GB-A

Flash memory version

D version

Remarks

R O M c a p a c i t y :

2 : 8 K B y t e s .

3 : 1 2 K B y t e s .

4 : 1 6 K B y t e s .

R 8 C /1 2 g r o u p

R 8 C / T i n y s e r i e s

Memory type:

F: Flash memory version

R e n e s a s M C U

R e n e s a s s e m i c o n d u c t o r s

Figure 1.2 Type No., Memory Size, and Package

Rev.1.20 Jan 27, 2006 page 4 of 181

REJ09B0110-0120

Page 15

R8C/12 Group 1. Overview

p

1.5 Pin Assignments

Figure 1.3 shows the pin configuration (top view).

PIN CONFIGURATION (top view)

1

R

N

I

C

F

/

/

3

2

R

T

T

V

/

C

/

/

C

3

2

3

3

V

I N

I N

T

C N T

P

P

A

1 6

1 4

1 3

1 2

1 0

P45/INT

1 5

P10/KI

P11/KI

P12/KI

P13/KI

1 1

P14/TxD

P15/RxD

9

P16/CLK

0

0

1

2

3

0

0

0

P 06/ A N

P05/AN

P 04/ A N

M O D E

P03/AN

P02/AN

P01/AN

P00/AN7/TxD

0

T

R

0

)

N

(

3

/

C

7

C

0

V

C N T

I

A

P

O

Z

S

/

/

S

0

1

3

V

3

P

T

E

P

A

U

2 4 2 3 2 2 2 1 2 0 1 9 1 8 1 7

1

2

3

4

5

6

11

2 5

2 6

2 7

2 8

2 9

3 0

3 1

3 2

R8C/12 Group

1 2 3 4 5 6 7 8

T x

R x

P

N O T E S :

1 . P 4

2 . W h e n u s i n g o n - c h i p d e b u g g e r , d o n o t u s e

3 . D o n o t c o n n e c t I V c c t o V c c .

Figure 1.3 Pin Configuration (Top View)

)

6

1

S

S

D

V

/

0

C

E S E

1

D

N

/

7

3

P

7

f u n c t i o n s o n l y a s a n i n p u t p o r t .

0

0

/ A N7/ T x D

S

T

(

1

S

7

V

4

/

P

T

R

O

X

U

P

1 1

a n d P 37/ T x D

0

C

4

C

R

V

/

N

I

X

/

1

T

/

7

1

P

I N

C N T

1 0

Package: PLQP0032GB-A (32P6U-A)

/ R x D1.

Rev.1.20 Jan 27, 2006 page 5 of 181

REJ09B0110-0120

Page 16

R8C/12 Group 1. Overview

1.6 Pin Description

Table 1.3 shows the pin description

Table 1.3 Pin description

Signal name Pin name I/O type

Power supply Vcc, I

input Vss

IVcc IVcc O

Apply 2.7 V to 5.5 V to the Vcc pin. Apply 0 V to the

Vss pin.

This pin is to stabilize internal power supply.

Connect this pin to Vss via a capacitor (0.1 µF).

Do not connect to Vcc.

Analog power AVcc, I

supply input AVss

Reset input

___________

RESET I

CNVss CNVss I

MODE MODE I

Main clock input XIN I

Power supply input pins for A/D converter. Connect the

AVcc pin to Vcc. Connect the AVss pin to Vss. Connect a

capacitor between pins AVcc and AVss.

Input “L” on this pin resets the MCU.

Connect this pin to Vss via a resistor.

Connect this pin to Vcc via a resistor.

These pins are provided for the main clock generating circuit I/O. Connect a ceramic resonator or a crys-

Main clock output XOUT O

tal oscillator between the XIN and XOUT pins. To use

an externally derived clock, input it to the XIN pin and

_____

INT interrupt input

Key input interrupt

Timer X CNTR0 I/O

_______ _______

INT0 to INT3 I

_____ _____

KI0 to KI3 I

__________

CNTR0 O

Timer Y CNTR1 I/O

Timer Z TZOUT O

Timer C TCIN I

Serial interface CLK0 I/O

RxD0, RxD1 I

TxD0, TxD10,O

leave the XOUT pin open.

______

INT interrupt input pins.

Key input interrupt pins.

Timer X I/O pin

Timer X output pin

Timer Y I/O pin

Timer Z output pin

Timer C input pin

Transfer clock I/O pin.

Serial data input pins.

Serial data output pins.

TxD11

Reference voltage VREF I

input

A/D converter AN0 to AN7 I

I/O port P00 to P07, I/O

P10 to P17,

P30 to P33, P37,

P45

Reference voltage input pin for A/sD converter. Connect the VREF pin to Vcc.

Analog input pins for A/D converter

These are 8-bit CMOS I/O ports. Each port has an

input/output select direction register, allowing each

pin in that port to be directed for input or output individually.

Any port set to input can select whether to use a pullup resistor or not by program.

P10 to P17 also function as LED drive ports.

Input port P46, P47 I

Port for input-only.

NOTES :

1. Refer to "19.8 Noise" for the connecting reference resistor value.

Function

(1)

Rev.1.20 Jan 27, 2006 page 6 of 181

REJ09B0110-0120

Page 17

R8C/12 Group 2. Central Processing Unit (CPU)

2. Central Processing Unit (CPU)

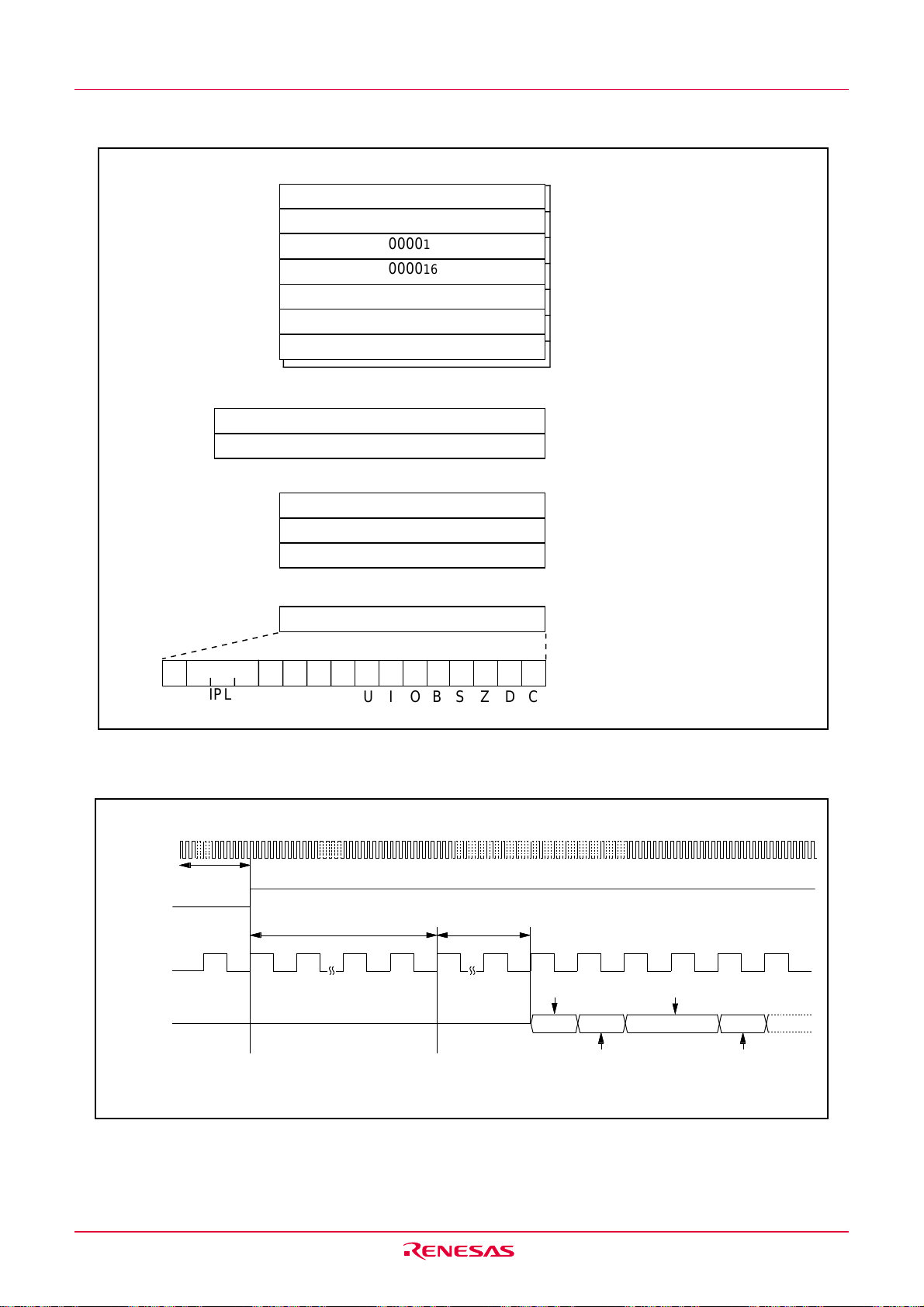

Figure 2.1 shows the CPU registers. The CPU has 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB

comprise a register bank. Two sets of register banks are provided.

b31

R2

R 3

b19

b15 b8 b7 b0

R 0 H ( h i g h - o r d e r o f R 0 )

R1H(high-order of R1)

b15 b0

INTBH

T h e 4 - h i g h o r d e r b i t s o f I N T B a r e I N T B H a n d

t h e 1 6 - l o w b i t s o f I N T B a r e I N T B L .

b 1 9

b15 b0

b15 b 0

b15 b 0 b7 b 8

I P L

R0L(low-order of R0)

R1L(low-order of R1)

R 2

R 3

A 0

A 1

F B

INTBL

PC

USP

ISP

SB

F L G

D a t a r e g i s t e r s

A d d r e s s r e g i s t e r s

F r a m e b a s e r e g i s t e r s

I n t e r r u p t t a b l e r e g i s t e r

b0

P r o g r a m c o u n t e r

User stack pointer

I n t e r r u p t s t a c k p o i n t e r

Static base regist er

F l a g r e g i s t e r

CDZSBOIU

C a r r y f l a g

Debug flag

Zero flag

S i g n f l a g

R e g i s t e r b a n k s e l e c t f l a g

O v e r f l o w f l a g

I n t e r r u p t e n a b l e f l a g

S t a c k p o i n t e r s e l e c t f l a g

Reserved bit

P r o c e s s o r i n t e r r u p t p r i o r i t y l e v e l

R e s e r v e d b i t

( 1 )

( 1 )

( 1 )

N O T E S :

1 . A r e g i s t e r b a n k c o m p r i s e s t h e s e r e g i s t e r s . T w o s e t s o f r e g i s t e r b a n k s a r e p r o v i d e d

Figure 2.1 CPU Register

2.1 Data Registers (R0, R1, R2 and R3)

R0 is a 16-bit register for transfer, arithmetic and logic operations. The same applies to R1 to R3. The

R0 can be split into high-order bit (R0H) and low-order bit (R0L) to be used separately as 8-bit data

registers. The same applies to R1H and R1L as R0H and R0L. R2 can be combined with R0 to be

used as a 32-bit data register (R2R0). The same applies to R3R1 as R2R0.

Rev.1.20 Jan 27, 2006 page 7 of 181

REJ09B0110-0120

Page 18

R8C/12 Group 2. Central Processing Unit (CPU)

2.2 Address Registers (A0 and A1)

A0 is a 16-bit register for address register indirect addressing and address register relative addressing.

They also are used for transfer, arithmetic and logic operations. The same applies to A1 as A0. A0 can

be combined with A0 to be used as a 32-bit address register (A1A0).

2.3 Frame Base Register (FB)

FB is a 16-bit register for FB relative addressing.

2.4 Interrupt Table Register (INTB)

INTB is a 20-bit register indicates the start address of an interrupt vector table.

2.5 Program Counter (PC)

PC, 20 bits wide, indicates the address of an instruction to be executed.

2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

The stack pointer (SP), USP and ISP, are 16 bits wide each. The U flag of FLG is used to switch

between USP and ISP.

2.7 Static Base Register (SB)

SB is a 16-bit register for SB relative addressing.

2.8 Flag Register (FLG)

FLG is a 11-bit register indicating the CPU state.

2.8.1 Carry Flag (C)

The C flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic logic unit.

2.8.2 Debug Flag (D)

The D flag is for debug only. Set to “0”.

2.8.3 Zero Flag (Z)

The Z flag is set to “1” when an arithmetic operation resulted in 0; otherwise, “0”.

2.8.4 Sign Flag (S)

The S flag is set to “1” when an arithmetic operation resulted in a negative value; otherwise, “0”.

2.8.5 Register Bank Select Flag (B)

The register bank 0 is selected when the B flag is “0”. The register bank 1 is selected when this flag

is set to “1”.

2.8.6 Overflow Flag (O)

The O flag is set to “1” when the operation resulted in an overflow; otherwise, “0”.

2.8.7 Interrupt Enable Flag (I)

The I flag enables a maskable interrupt.

An interrupt is disabled when the I flag is set to “0”, and are enabled when the I flag is set to “1”. The

I flag is set to “0” when an interrupt request is acknowledged.

2.8.8 Stack Pointer Select Flag (U)

ISP is selected when the U flag is set to “0”, USP is selected when the U flag is set to “1”.

The U flag is set to “0” when a hardware interrupt request is acknowledged or the INT instruction of

software interrupt numbers 0 to 31 is executed.

2.8.9 Processor Interrupt Priority Level (IPL)

IPL, 3 bits wide, assigns processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has greater priority than IPL, the interrupt is enabled.

2.8.10 Reserved Bit

When write to this bit, set to “0”. When read, its content is indeterminate.

Rev.1.20 Jan 27, 2006 page 8 of 181

REJ09B0110-0120

Page 19

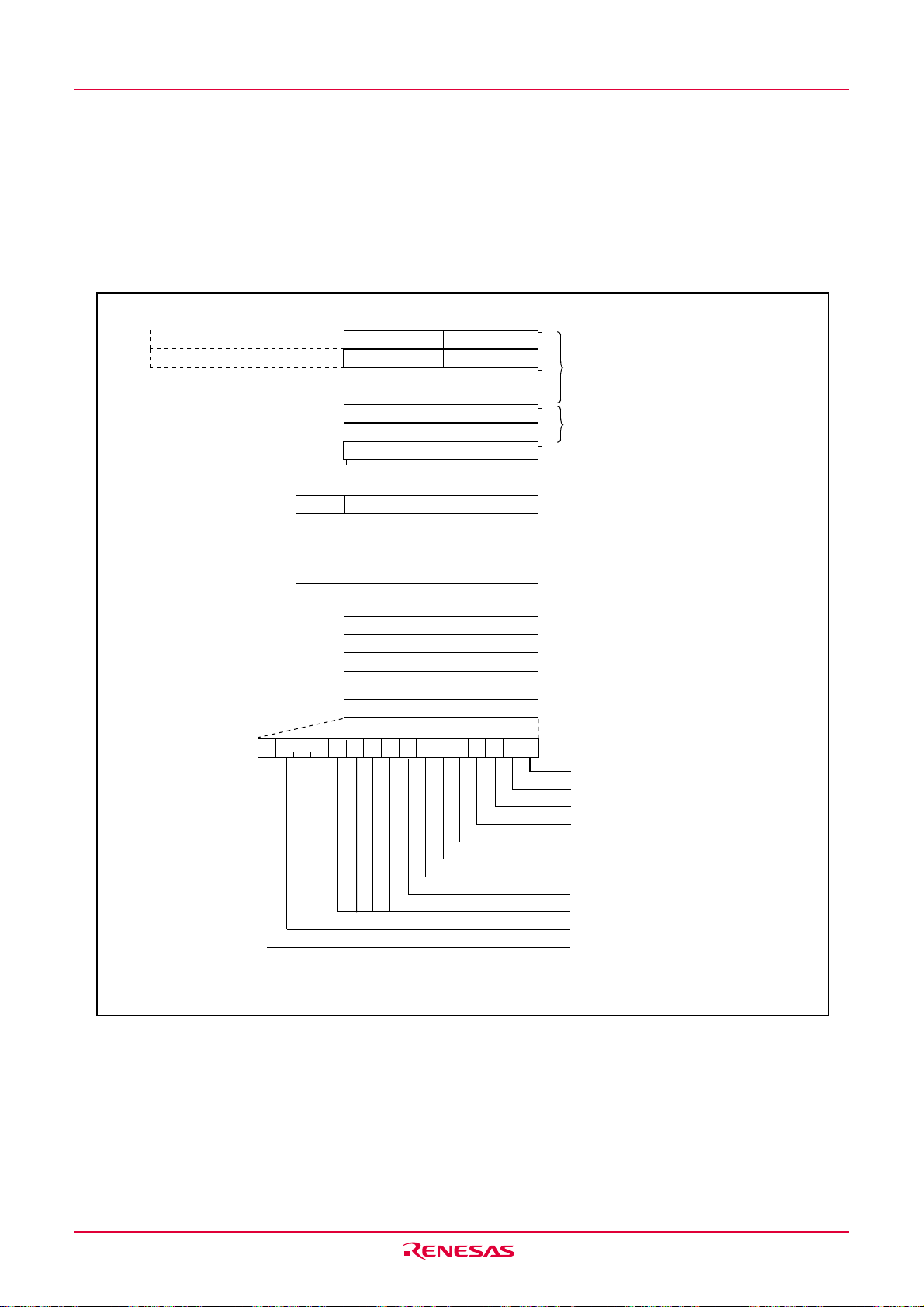

R8C/12 Group 3. Memory

s

s

s

3. Memory

Figure 3.1 is a memory map of this MCU. This MCU provides 1-Mbyte address space from addresses

0000016 to FFFFF16.

The internal ROM (program ROM) is allocated lower addresses beginning with address 0FFFF16. For

example, a 16-Kbyte internal ROM is allocated addresses from 0C00016 to 0FFFF16.

The fixed interrupt vector table is allocated addresses 0FFDC16 to 0FFFF16. They store the starting

address of each interrupt routine.

The internal ROM (data flash) is allocated addresses from 0200016 to 02FFF16.

The internal RAM is allocated addresses beginning with address 0040016. For example, a 1-Kbyte internal RAM is allocated addresses 0040016 to 007FF16. The internal RAM is used not only for storing data,

but for calling subroutines and stacks when interrupt request is acknowledged.

Special function registers (SFR) are allocated addresses 0000016 to 002FF16. The peripheral function

control registers are located them. All addresses, which have nothing allocated within the SFR, are reserved area and cannot be accessed by users.

0 0 0 0 0

1 6

( S e e C h a p t e r 4 f o r d e t a i l s . )

0 0 2 F F

1 6

00400

16

I n t e r n a l R A M

0 X X X X

1 6

0 2 0 0 0

1 6

I n t e r n a l R O M

( d a t a f l a s h )

0 2 F F F

1 6

0 Y Y Y Y

1 6

I n t e r n a l R O M

0 F F F F

F F F F F

( p r o g r a m R O M )

1 6

E x p a n s i o n a r e a

1 6

N O T E S :

1 . T h e d a t a f l a s h b l o c k A ( 2 K b y t e s ) a n d b l o c k B ( 2 K b y t e s ) a r e s h o w n .

2 . B l a n k s p a c e a r e r e s e r v e d . N o a c c e s s i s a l l o w e d .

T y p e n a m e

R 5 F 2 1 1 2 4 F P , R 5 F 2 1 1 2 4 D F P

R 5 F 2 1 1 2 3 F P , R 5 F 2 1 1 2 3 D F P

R 5 F 2 1 1 2 2 F P , R 5 F 2 1 1 2 2 D F P

S F R

(1 )

Internal ROM

S i z e

16K bytes

12K bytes

8K bytes

0FFDC

16

0FFFF

16

Address 0YYYY

0C000

16

0D000

16

0E000

16

U n d e f i n e d i n s t r u c t i o n

Overflow

B R K i n s t r u c t i o n

Address match

W a t c h d o g t i m e r • O s c i l l a t i o n s t o p d e t e c t i o n

Single step

(Reserved)

(Reserved)

R e s e t

Internal RAM

16

S i z e

1 K b y t e

7 6 8 b y t e

5 1 2 b y t e

A d d r e s s 0 X X X X

007FF

006FF

005FF

1 6

16

16

16

Figure 3.1 Memory Map

Rev.1.20 Jan 27, 2006 page 9 of 181

REJ09B0110-0120

Page 20

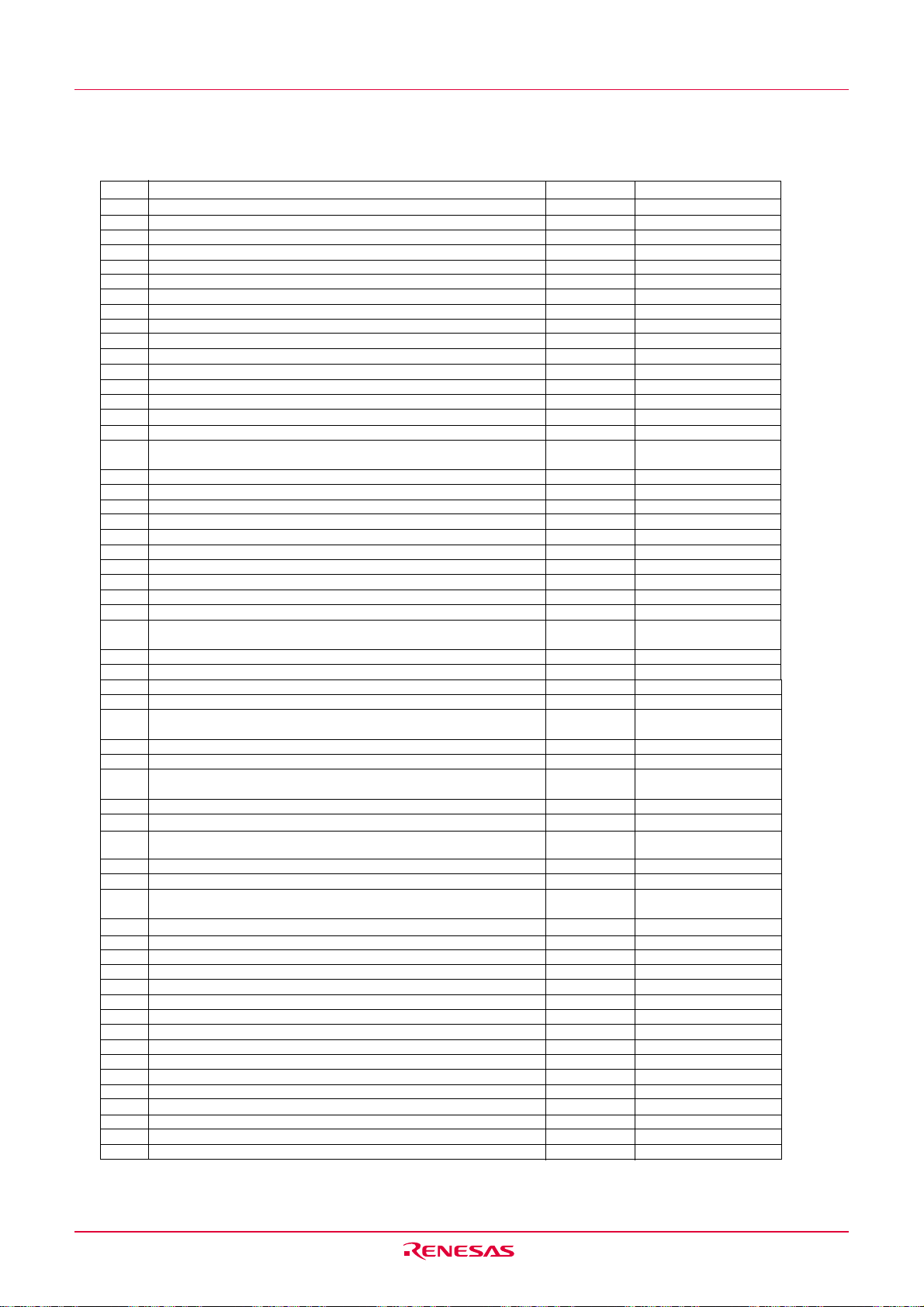

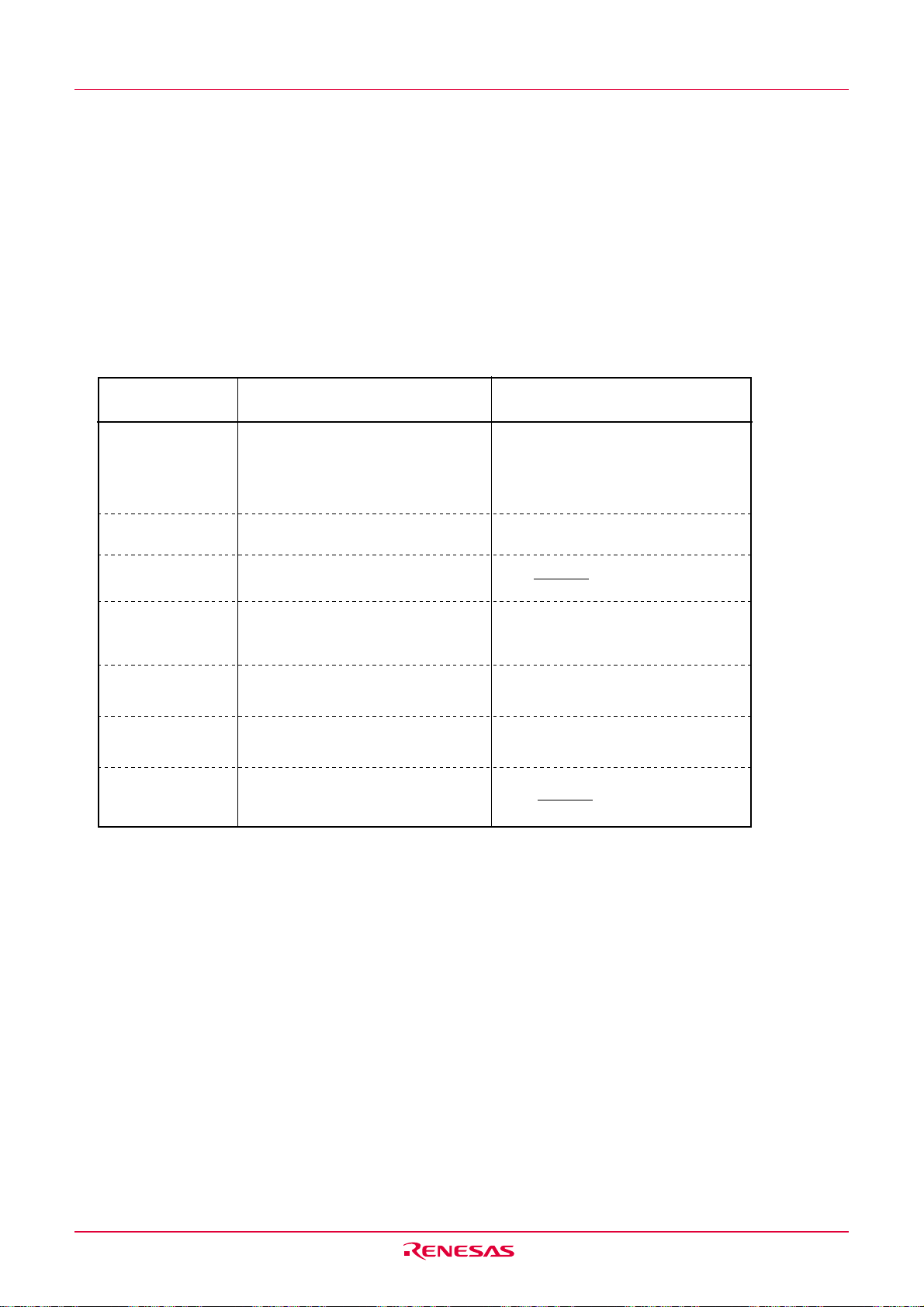

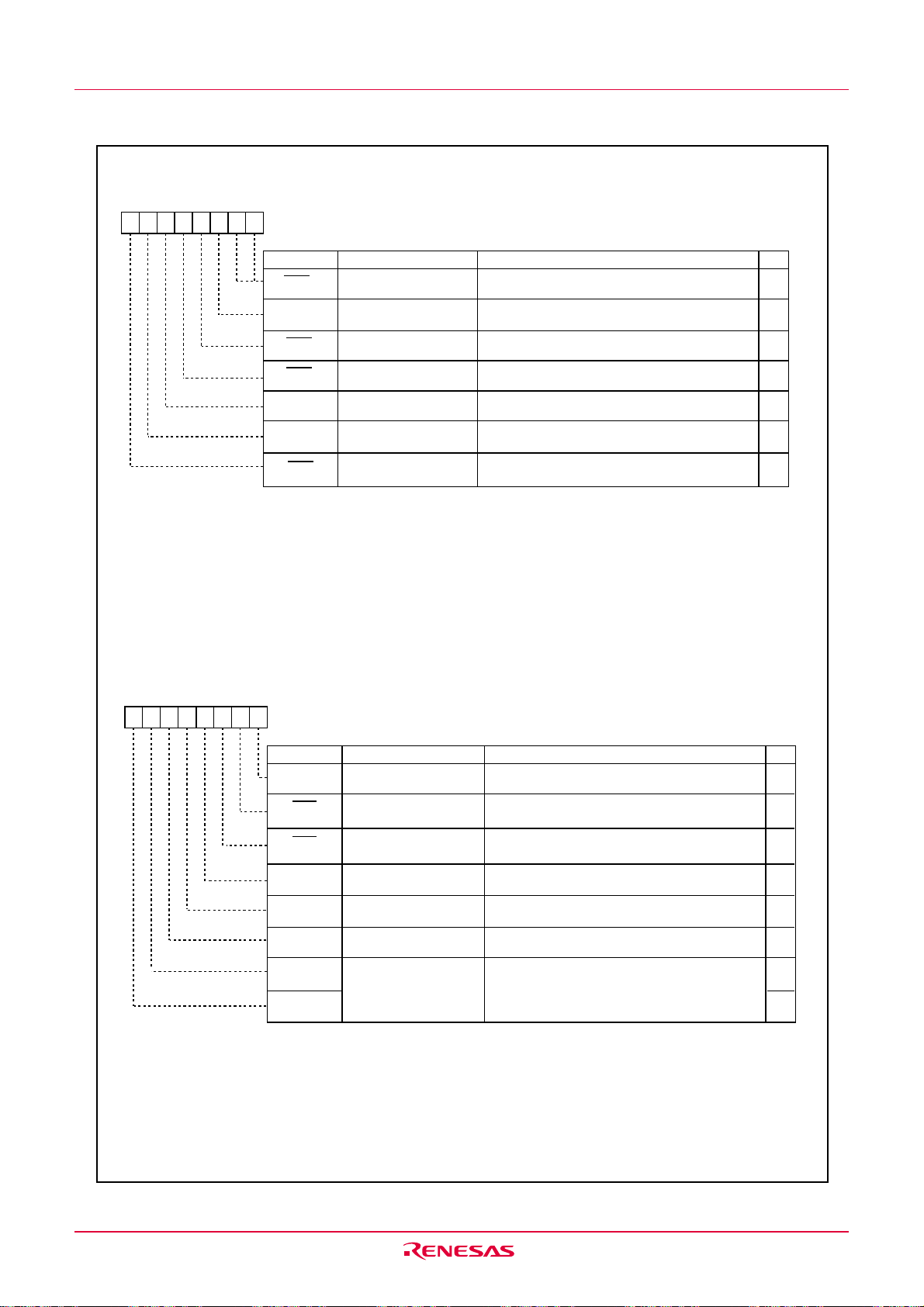

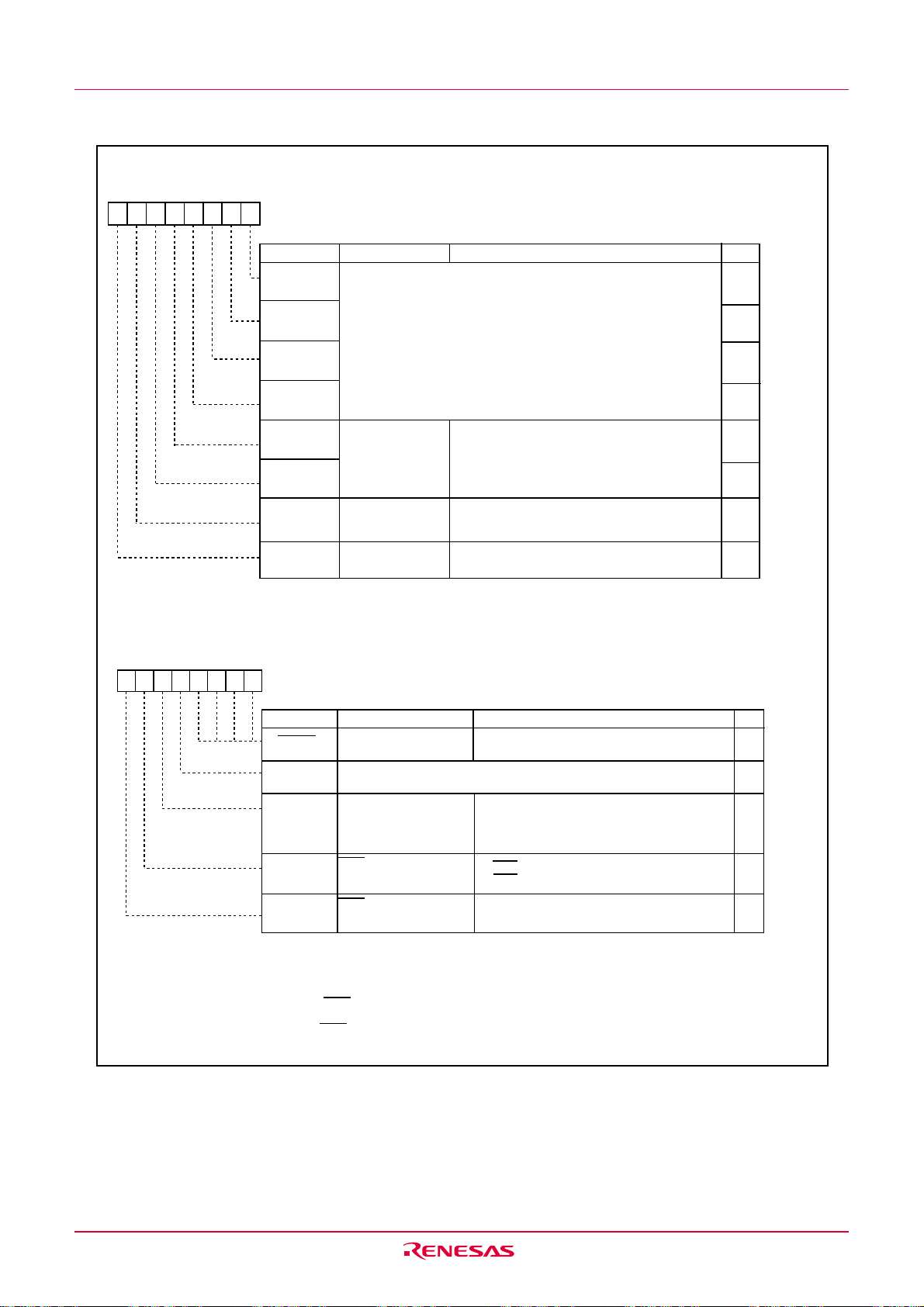

R8C/12 Group 4. Special Function Register (SFR)

4. Special Function Register (SFR)

SFR(Special Function Register) is the control register of peripheral functions. Tables 4.1 to 4.4 list the SFR

information

Table 4.1 SFR Information(1)

A d d r e s s

0 0 0 0

1 6

0 0 0 1

1 6

0 0 0 2

1 6

0 0 0 3

1 6

M

X X

0 0 0 4

1 6

P r o c e s s o r m o d e r e g i s t e r 0P

0 0 0 5

1 6

Processor mode register 1 PM1 00XXX0X0

M

1 1 0 1 0 0

0 0 0 6

1 6

S y s t e m c l o c k c o n t r o l r e g i s t e r 0C

M

0 1 0 0 0 0

0 0 0 7

1 6

S y s t e m c l o c k c o n t r o l r e g i s t e r 1C

0 0 0 8

1 6

I E

X X X X X 0

0 0 0 9

1 6

A d d r e s s m a t c h i n t e r r u p t e n a b l e r e g i s t e rA

0 0 0 A

1 6

Protect register PRCR 00XXX000

0 0 0 B

1 6

C

0 0 0 0 1 0

0 0 0 C

1 6

O s c i l l a t i o n s t o p d e t e c t i o n r e g i s t e rO

D T

0 0 0 D

1 6

W a t c h d o g t i m e r r e s e t r e g i s t e rW

0 0 0 E

1 6

Watchdog timer start register WDTS XX

D

0 0 1 1 1 1

0 0 0 F

1 6

W a t c h d o g t i m e r c o n t r o l r e g i s t e rW

M A D

0 0 1 0

1 6

A d d r e s s m a t c h i n t e r r u p t r e g i s t e r 0R

0 0 1 1

1 6

0 0 1 2

1 6

0 0 1 3

1 6

M A D

0 0 1 4

1 6

A d d r e s s m a t c h i n t e r r u p t r e g i s t e r 1R

0 0 1 5

1 6

0 0 1 6

1 6

0 0 1 7

1 6

0 0 1 8

1 6

0 0 1 9

1 6

0 0 1 A

1 6

0 0 1 B

1 6

0 0 1 C

1 6

0 0 1 D

1 6

N T 0

X X X X 0 0

0 0 1 E

1 6

I N T 0 i n p u t f i l t e r s e l e c t r e g i s t e rI

0 0 1 F

1 6

0 0 2 0

1 6

0 0 2 1

1 6

0 0 2 2

1 6

0 0 2 3

1 6

0 0 2 4

1 6

0 0 2 5

1 6

0 0 2 6

1 6

0 0 2 7

1 6

0 0 2 8

1 6

0 0 2 9

1 6

0 0 2 A

1 6

0 0 2 B

1 6

0 0 2 C

1 6

0 0 2 D

1 6

0 0 2 E

1 6

0 0 2 F

1 6

0 0 3 0

1 6

0 0 3 1

1 6

0 0 3 2

1 6

0 0 3 3

1 6

0 0 3 4

1 6

0 0 3 5

1 6

0 0 3 6

1 6

0 0 3 7

1 6

0 0 3 8

1 6

0 0 3 9

1 6

0 0 3 A

1 6

0 0 3 B

1 6

0 0 3 C

1 6

0 0 3 D

1 6

0 0 3 E

1 6

0 0 3 F

1 6

N O T E S :

1 . B l a n k s p a c e s a r e r e s e r v e d . N o a c c e s s i s a l l o w e d .

X : U n d e f i n e d

(1)

Register Symbol After reset

0X

00

10

X0X 0 0

0

0

RX

D0

RX

C0

00

0 0

X 0

10

0 0

X 0

0

X

1 6

16

1

0

1 6

1 6

1 6

0

1 6

1 6

1 6

FX

2

2

2

2

0

2

2

2

2

0

2

Rev.1.20 Jan 27, 2006 page 10 of 181

REJ09B0110-0120

Page 21

R8C/12 Group 4. Special Function Register (SFR)

Table 4.2 SFR Information(2)

A d d r e s s

0 0 4 0

1 6

0 0 4 1

1 6

0 0 4 2

1 6

0 0 4 3

1 6

0 0 4 4

1 6

0 0 4 5

1 6

0 0 4 6

1 6

0 0 4 7

1 6

0 0 4 8

1 6

0 0 4 9

1 6

0 0 4 A

1 6

0 0 4 B

1 6

0 0 4 C

1 6

U P I

X X X X 0 0

0 0 4 D

1 6

K e y i n p u t i n t e r r u p t c o n t r o l r e g i s t e rK

D I

X X X X 0 0

0 0 4 E

1 6

A D c o n v e r s i o n i n t e r r u p t c o n t r o l r e g i s t e rA

0 0 4 F

1 6

0 0 5 0

1 6

0 0 5 1

1 6

UART0 transmit interrupt control register

X X X X 0 0

0 0 5 2

1 6

U A R T 0 r e c e i v e i n t e r r u p t c o n t r o l r e g i s t e r

X X X X 0 0

0 0 5 3

1 6

U A R T 1 t r a n s m i t i n t e r r u p t c o n t r o l r e g i s t e r

X X X X 0 0

0 0 5 4

1 6

U A R T 1 r e c e i v e i n t e r r u p t c o n t r o l r e g i s t e r

0 0 5 5

1 6

INT2 interrupt contro l register INT2IC XXXXX000

X I

X X X X 0 0

0 0 5 6

1 6

T i m e r X i n t e r r u p t c o n t r o l r e g i s t e rT

Y I

X X X X 0 0

0 0 5 7

1 6

T i m e r Y i n t e r r u p t c o n t r o l r e g i s t e rT

Z I

X X X X 0 0

0 0 5 8

1 6

T i m e r Z i n t e r r u p t c o n t r o l r e g i s t e rT

0 0 5 9

1 6

INT1 interrupt contro l register INT1IC XXXXX000

0 0 5 A

1 6

INT3 interrupt contro l register INT3IC XXXXX000

C I

X X X X 0 0

0 0 5 B

1 6

T i m e r C i n t e r r u p t c o n t r o l r e g i s t e rT

0 0 5 C

1 6

N T 0 I

X 0 0 X 0 0

0 0 5 D

1 6

I N T 0 i n t e r r u p t c o n t r o l r e g i s t e rI

0 0 5 E

1 6

0 0 5 F

1 6

0060

16

0061

16

0062

16

0063

16

0064

16

0065

16

0066

16

0067

16

0068

16

0069

16

006A

16

006B

16

006C

16

006D

16

006E

16

006F

16

0070

16

0071

16

0072

16

0073

16

0074

16

0075

16

0076

16

0077

16

0078

16

0079

16

007A

16

007B

16

007C

16

007D

16

007E

16

007F

16

N O T E S :

1 . B l a n k s p a c e s a r e r e s e r v e d . N o a c c e s s i s a l l o w e d .

(1)

R e g i s t e rS

X : U n d e f i n e d

y m b o l

A

CX

CX

f t e r r e s e

t

0

0

S0TIC XXXXX000

S 0 R I CX

S 1 T I CX

S 1 R I CX

CX

CX

CX

CX

CX

0

0

0

0

0

0

0

0

2

2

2

2

2

2

2

2

2

2

2

2

2

2

Rev.1.20 Jan 27, 2006 page 11 of 181

REJ09B0110-0120

Page 22

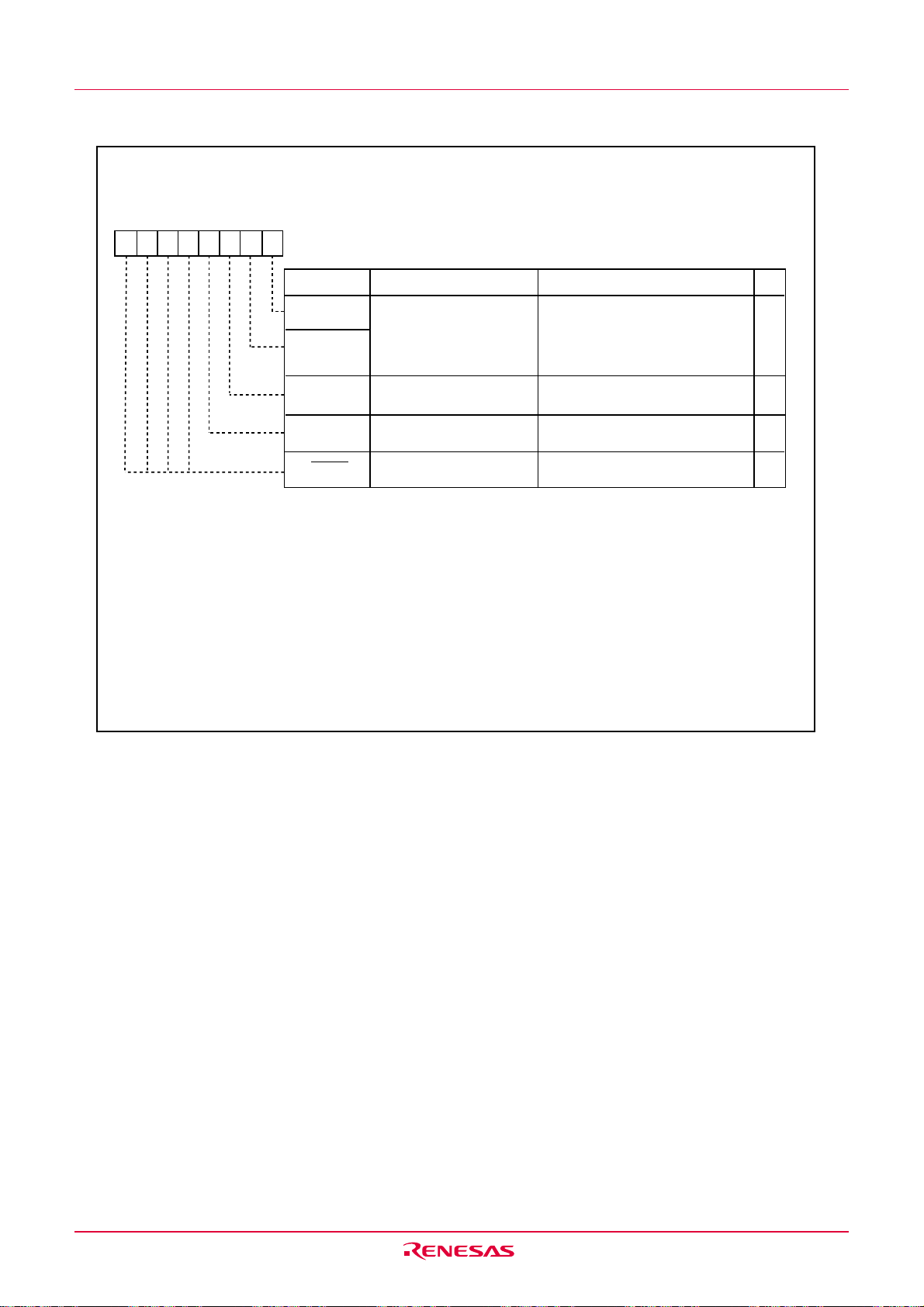

R8C/12 Group 4. Special Function Register (SFR)

Table 4.3 SFR Information(3)

A d d r e s s

N O T E S :

1 . B l a n k s p a c e s a r e r e s e r v e d . N o a c c e s s i s a l l o w e d .

Y Z M

0 0 8 0

1 6

T i m e r Y , Z m o d e r e g i s t e rT

R E

0 0 8 1

1 6

P r e s c a l e r Y r e g i s t e rP

Y S

0 0 8 2

1 6

T i m e r Y s e c o n d a r y r e g i s t e rT

Y P

0 0 8 3

1 6

T i m e r Y p r i m a r y r e g i s t e rT

U

0 0 8 4

1 6

T i m e r Y , Z w a v e f o r m o u t p u t c o n t r o l r e g i s t e rP

R E

0 0 8 5

1 6

P r e s c a l e r Z r e g i s t e rP

Z S

0 0 8 6

1 6

T i m e r Z s e c o n d a r y r e g i s t e rT

Z P

0 0 8 7

1 6

T i m e r Z p r i m a r y r e g i s t e rT

0 0 8 8

1 6

0 0 8 9

1 6

Y Z O

T i m e r Y , Z o u t p u t c o n t r o l r e g i s t e rT

0 0 8 A

1 6

X M

T i m e r X m o d e r e g i s t e rT

0 0 8 B

1 6

R E

P r e s c a l e r X r e g i s t e rP

0 0 8 C

1 6

T i m e r X r e g i s t e rT

0 0 8 D

1 6

C S

T i m e r c o u n t s o u r c e s e t t i n g r e g i s t e rT

0 0 8 E

1 6

0 0 8 F

1 6

0 0 9 0

1 6

T i m e r C r e g i s t e rT

0 0 9 1

1 6

0 0 9 2

1 6

0 0 9 3

1 6

0 0 9 4

1 6

0 0 9 5

1 6

N T E

0 0 9 6

1 6

E x t e r n a l i n p u t e n a b l e r e g i s t e rI

0 0 9 7

1 6

I E

K e y i n p u t e n a b l e r e g i s t e rK

0 0 9 8

1 6

0 0 9 9

1 6

C C

T i m e r C c o n t r o l r e g i s t e r 0T

0 0 9 A

1 6

C C

T i m e r C c o n t r o l r e g i s t e r 1T

0 0 9 B

1 6

M

0 0 9 C

1 6

C a p t u r e r e g i s t e rT

0 0 9 D

1 6

0 0 9 E

1 6

0 0 9 F

1 6

0 0 A 0

1 6

U A R T 0 t r a n s m i t / r e c e i v e m o d e r e g i s t e r

0 B R

0 0 A 1

1 6

U A R T 0 b i t r a t e r e g i s t e r U

0 T

0 0 A 2

1 6

U A R T 0 t r a n s m i t b u f f e r r e g i s t e rU

0 0 A 3

1 6

0 0 0 1 0 0

0 0 A 4

1 6

U A R T 0 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 0

0 0 0 0 0 1

0 0 A 5

1 6

U A R T 0 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 1

0 R

0 0 A 6

1 6

U A R T 0 r e c e i v e b u f f e r r e g i s t e r U

0 0 A 7

1 6

0 0 A 8

1 6

U A R T 1 t r a n s m i t / r e c e i v e m o d e r e g i s t e r

1 B R

0 0 A 9

1 6

U A R T 1 b i t r a t e g e n e r a t o rU

1 T

0 0 A A

1 6

U A R T 1 t r a n s m i t b u f f e r r e g i s t e rU

0 0 A B

1 6

0 0 0 1 0 0

0 0 A C

1 6

U A R T 1 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 0

0 0 0 0 0 1

0 0 A D

1 6

U A R T 1 t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 1

1 R

0 0 A E

1 6

U A R T 1 r e c e i v e b u f f e r r e g i s t e r U

0 0 A F

1 6

0 0 B 0

1 6

U A R T t r a n s m i t / r e c e i v e c o n t r o l r e g i s t e r 2

0 0 B 1

1 6

0 0 B 2

1 6

0 0 B 3

1 6

0 0 B 4

1 6

0 0 B 5

1 6

0 0 B 6

1 6

0 0 B 7

1 6

0 0 B 8

1 6

0 0 B 9

1 6

0 0 B A

1 6

0 0 B B

1 6

0 0 B C

1 6

0 0 B D

1 6

0 0 B E

1 6

0 0 B F

1 6

(1)

R e g i s t e rS

X : U n d e f i n e d

y m b o l

A

R0

YF

CF

RF

M0

ZF

CF

RF

C0

R0

XF

XF

S0

C0

N0

N0

00

10

00

U 0 M R0

GX

BX

U 0 C 00

U 0 C 10

BX

U 1 M R0

GX

BX

U 1 C 00

U 1 C 10

BX

U C O N0

0 0

0 0

X X

X X

X X

X X

f t e r r e s e

1 6

0

F

1 6

F

1 6

F

1 6

0

1 6

F

1 6

F

1 6

F

1 6

0

1 6

0

1 6

F

1 6

F

1 6

0

1 6

0

1 6

1 6

0

1 6

0

1 6

0

1 6

0

1 6

0

1 6

1 6

0

1 6

X

1 6

X

1 6

1 6

0

0

X

1 6

1 6

0

1 6

X

1 6

X

1 6

1 6

0

0

X

1 6

1 6

0

1 6

t

2

2

2

2

Rev.1.20 Jan 27, 2006 page 12 of 181

REJ09B0110-0120

Page 23

R8C/12 Group 4. Special Function Register (SFR)

Table 4.4 SFR Information(4)

A d d r e s s

X X X X X X

0 0 C 0

1 6

A D r e g i s t e rA

0 0 C 1

1 6

0 0 C 2

1 6

0 0 C 3

1 6

0 0 C 4

1 6

0 0 C 5

1 6

0 0 C 6

1 6

0 0 C 7

1 6

0 0 C 8

1 6

0 0 C 9

1 6

0 0 C A

1 6

0 0 C B

1 6

0 0 C C

1 6

0 0 C D

1 6

0 0 C E

1 6

0 0 C F

1 6

0 0 D 0

1 6

0 0 D 1

1 6

0 0 D 2

1 6

0 0 D 3

1 6

D C O N

0 0 D 4

1 6

A D c o n t r o l r e g i s t e r 2A

0 0 D 5

1 6

D C O N

0 0 0 0 X X

0 0 D 6

1 6

A D c o n t r o l r e g i s t e r 0A

D C O N

0 0 D 7

1 6

A D c o n t r o l r e g i s t e r 1 A

0 0 D 8

1 6

0 0 D 9

1 6

0 0 D A

1 6

0 0 D B

1 6

0 0 D C

1 6

0 0 D D

1 6

0 0 D E

1 6

0 0 D F

1 6

00E0

16

P o r t P 0 r e g i s t e rP

00E1

16

P o r t P 1 r e g i s t e rP

00E2

16

Port P0 direction register PD0 00

00E3

16

Port P1 direction register PD1 00

00E4

16

00E5

16

P o r t P 3 r e g i s t e rP

00E6

16

D

00E7

16

P o r t P 3 d i r e c t i o n r e g i s t e rP

00E8

16

P o r t P 4 r e g i s t e rP

00E9

16

D

00EA

16

P o r t P 4 d i r e c t i o n r e g i s t e rP

00EB

16

00EC

16

00ED

16

00EE

16

00EF

16

00F0

16

00F1

16

00F2

16

00F3

16

00F4

16

00F5

16

00F6

16

00F7

16

00F8

16

00F9

16

03FA

16

00FB

16

U R

0 X X 0 0 0

00FC

16

P u l l - u p c o n t r o l r e g i s t e r 0 P

00FD

16

Pull-up control register 1 PUR1 XXXXXX0X

R

00FE

16

P o r t P 1 d r i v e c a p a c i t y c o n t r o l r e g i s t e r D

00FF

16

R e g i s t e r

(1)

S y m b o lA

DX

0X

1X

f t e r r e s e

X X X X X X X X

20

0

1 6

00

10

0

1 6

X

1 6

X

1 6

X

2

2

X

2

16

16

3X

30

4X

40

00

R0

X

1 6

0

1 6

X

1 6

0

1 6

0

2

0

2

1 6

t

01B3

16

Flash memory control register 4 FMR4 01000000

01B4

16

01B5

16

Flash memory control register 1 FMR1 1000000X

01B6

16

M R

0 0 0 0 0 0

01B7

16

F l a s h m e m o r y c o n t r o l r e g i s t e r 0 F

( 2 )

1 6

a n d 0 1 B 8

1 6

t o 0 2 F F

1 6

a r e a l l r e s e r v e d . N o a c c e s s i s a l l o w e d .

0 F F F F

1 6

O p t i o n f u n c t i o n s e l e c t r e g i s t e r

N O T E S :

1 . B l a n k c o l u m n s , 0 1 0 0

2 . T h e w a t c h d o g t i m e r c o n t r o l b i t i s a s s i g n e d . R e f e r t o " F i g u r e 1 1 . 2 O F S , W D C , W D T R a n d W D T S r e g i s t e r s " f o r t h e O F S r e g i s t e r d e t a i l s

X : U n d e f i n e d

1 6

t o 0 1 B 2

00

O F S

( N o t e 2 )

Rev.1.20 Jan 27, 2006 page 13 of 181

REJ09B0110-0120

2

2

1

2

Page 24

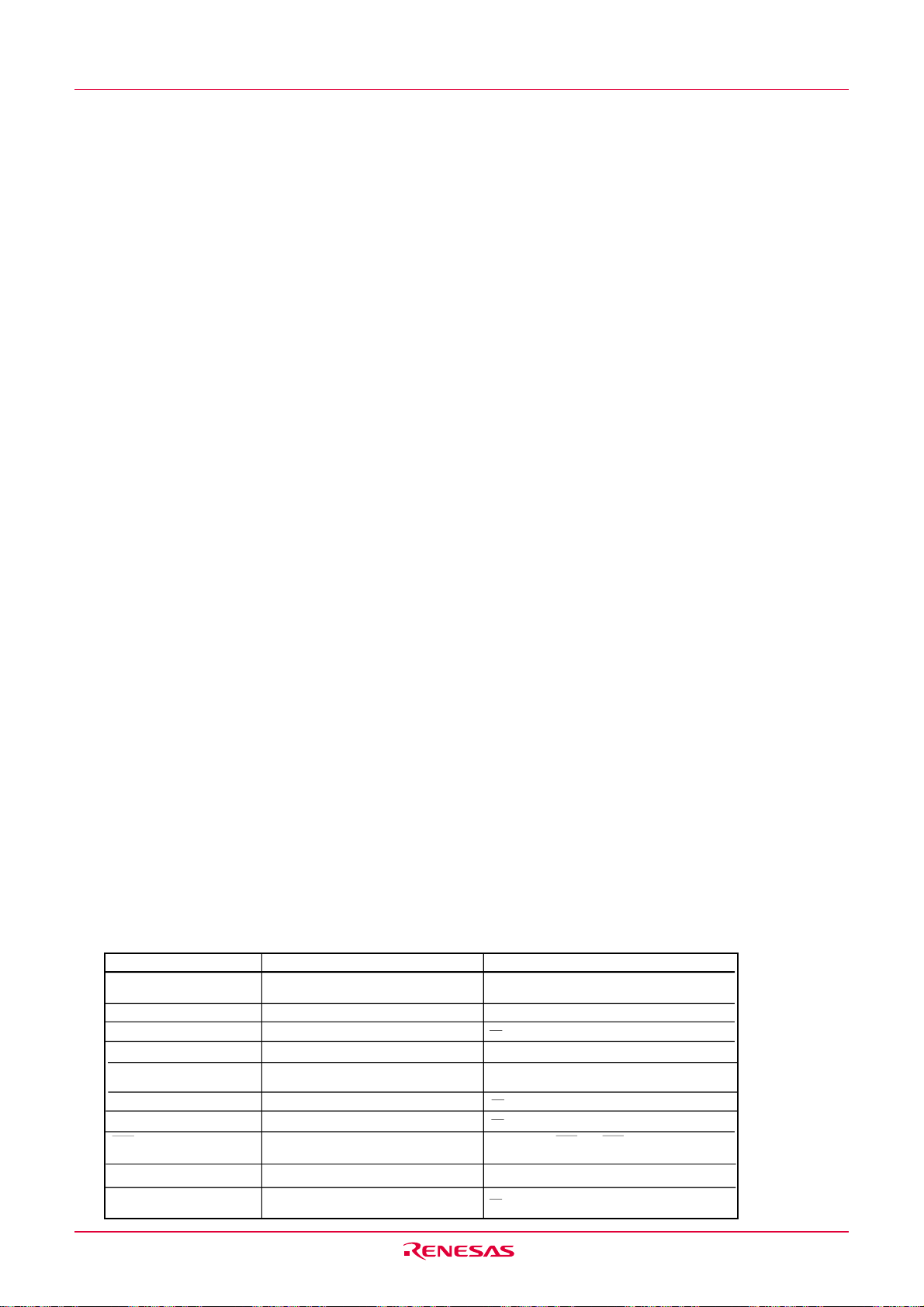

R8C/12 Group 5. Reset

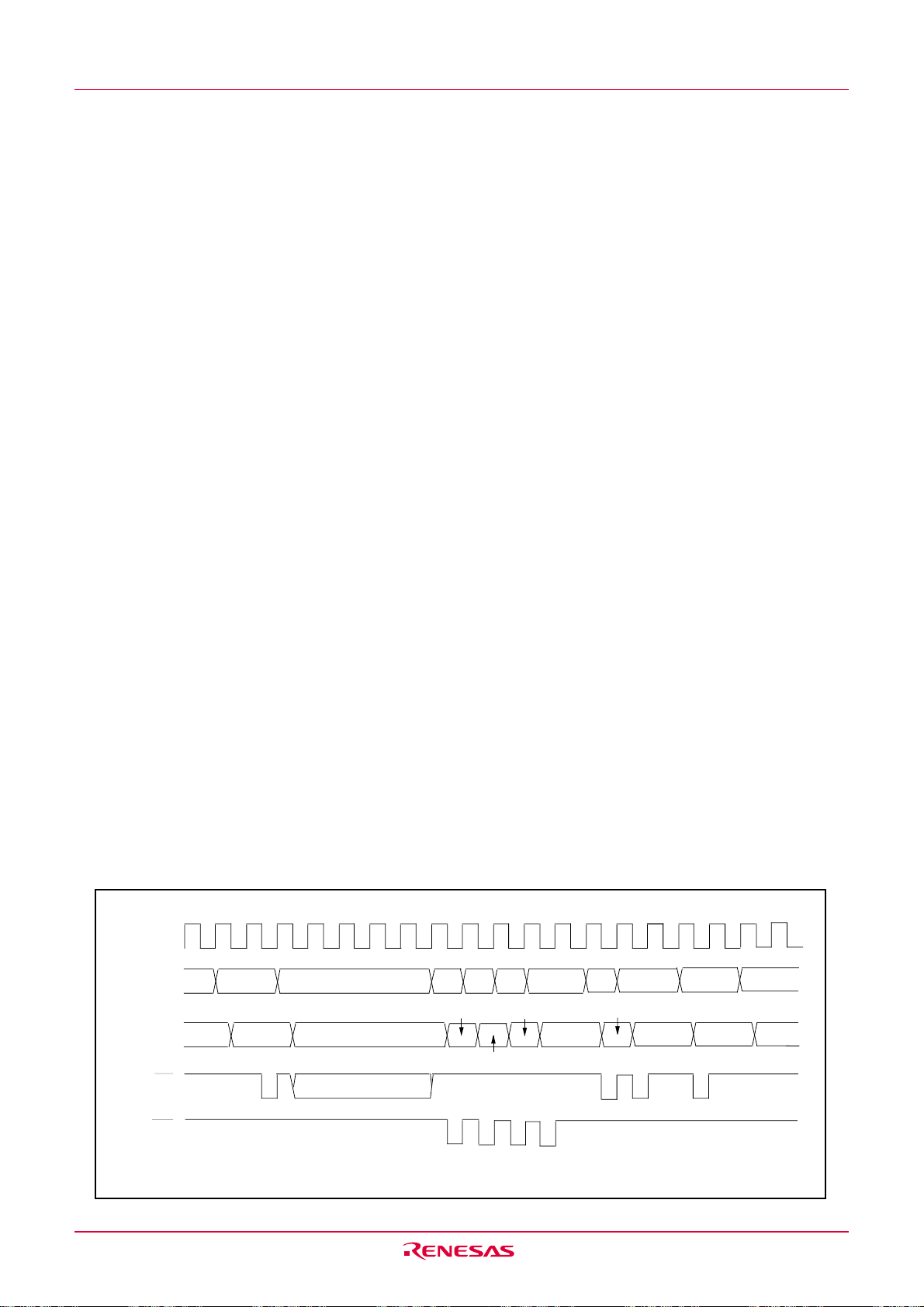

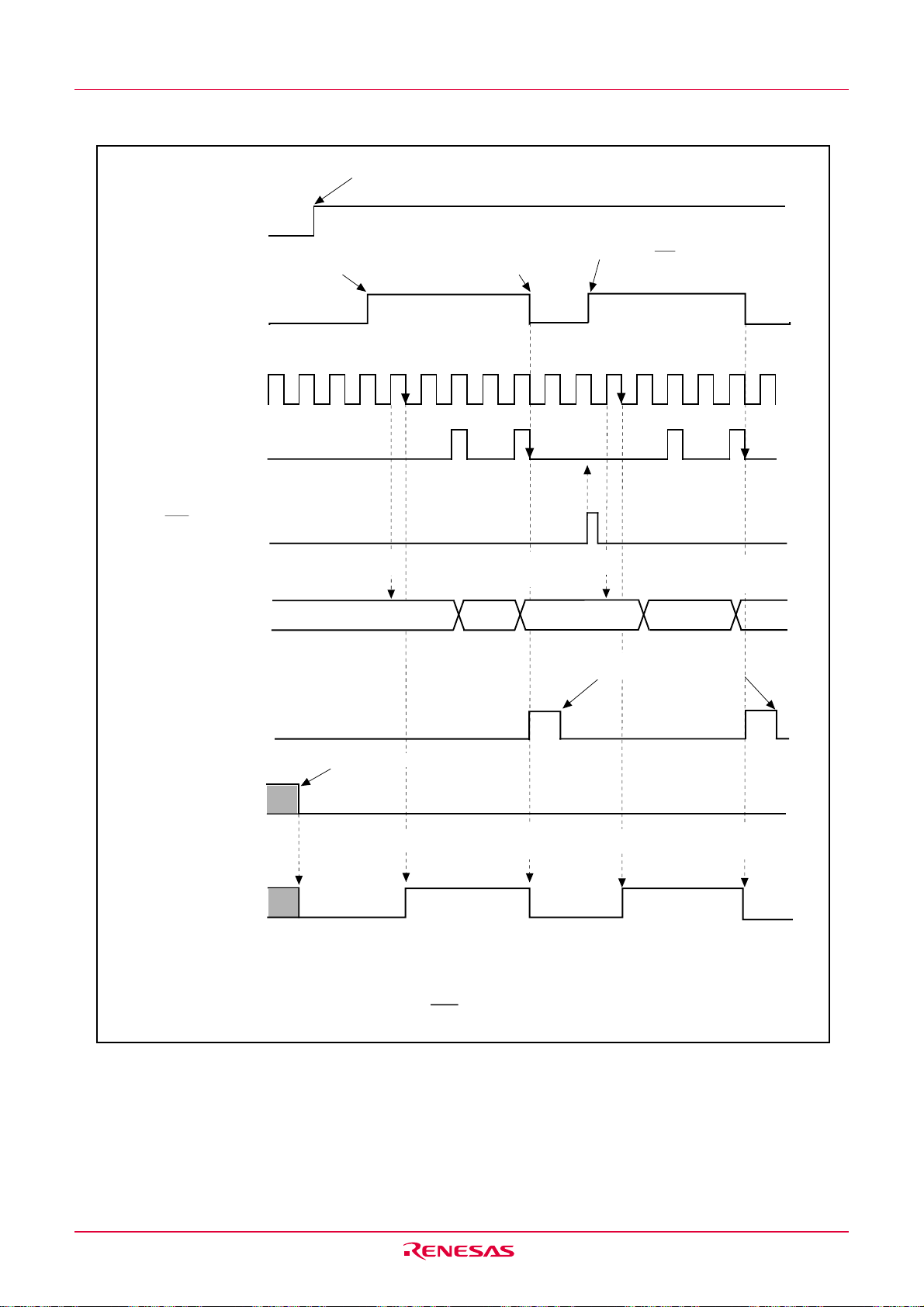

5. Reset

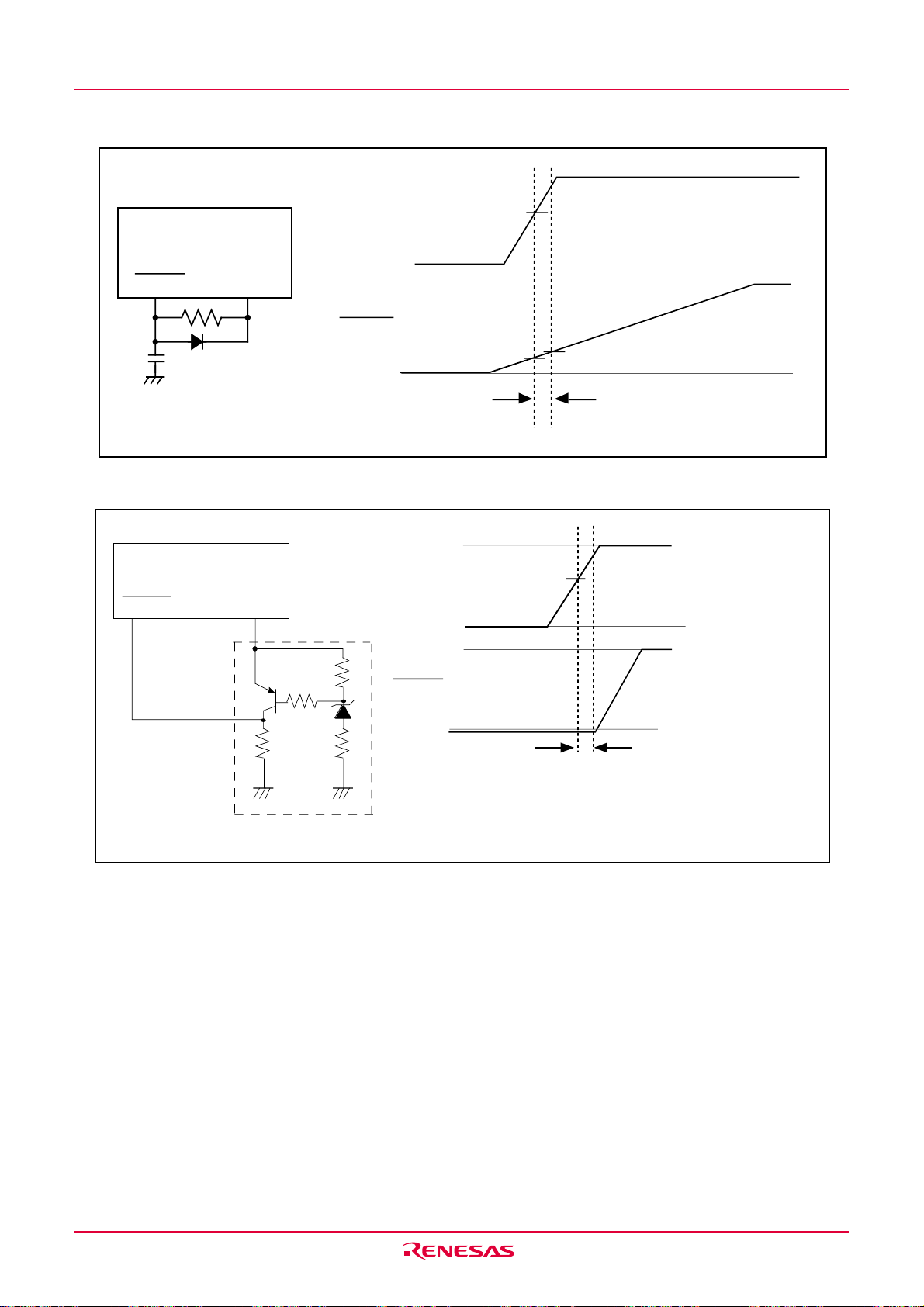

There are three types of resets: a hardware reset, a software reset, and an watchdog timer reset.

5.1 Hardware Reset

A reset is applied using the RESET pin. When an “L” signal is applied to the RESET pin while

the power supply voltage is within the recommended operating condition, the pins are initialized (see Table 5.1 “Pin Status When RESET Pin Level is 'L'”). When the input level at the

____________

RESET pin is released from “L” to “H”, the CPU and SFR are initialized, and the program is

executed starting from the address indicated by the reset vector. Figure 5.1 shows the CPU

register status after reset and figure 5.2 shows the reset sequence. After reset, the on-chip

oscillator clock divided by 8 is automatically selected for the CPU. The internal RAM is not

initialized. If the RESET pin is pulled “L” while writing to the internal RAM, the internal RAM

becomes indeterminate. Figures 5.3 to 5.4 show the reset circuit example. Refer to Chapter 4,

“Special Function Register (SFR)” for the status of SFR after reset.

____________

____________ ____________

____________

• When the power supply is stable

____________

(1) Apply an “L” signal to the RESET pin.

(2) Wait for 500 µs (1/fRING ✕ 20).

____________

(3) Apply an “H” signal to the RESET pin.

• Power on

____________

(1) Apply an “L” signal to the RESET pin.

(2) Let the power supply voltage increase until it meets the recommended operating condition.

(3) Wait td(P-R) or more until the internal power supply stabilizes.

(4) Wait for 500 µs (1/fRING ✕ 20).

____________

(5) Apply an “H” signal to the RESET pin.

Table 5.1 Pin Status When RESET Pin Level is “L”

____________

Pin name

P0

P1

0

to P33, P3

P3

P45

to P47

7

Input port

Input port

Input port

Input port

Status

5.2 Software Reset When the PM03 bit in the PM0 register is set to “1” (microcomputer reset), the microcomputer has its

pins, CPU, and SFR initialized. Then the program is executed starting from the address indicated by

the reset vector. After reset, the on-chip oscillator clock divided by 8 is automatically selected for the

CPU.