Page 1

REJ10J1564-0104

A

32

SH7285 CPU Board

M3

-HS85

User's Manual

Renesas 32-Bit RISC Microcomputers

SuperH

TM

RISCengine Family / SH7285 Group

Rev. 1.04

Issued: Jul 15, 2008

Page 2

Notes regarding these materials

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate

Renesas products for their use. Renesas neither makes warranties or representations with respect to the

accuracy or completeness of the information contained in this document nor grants any license to any

intellectual property rights or any other rights of Renesas or any third party with respect to the information in

this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising

out of the use of any information in this document, including, but not limited to, product data, diagrams, charts,

programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military

applications such as the development of weapons of mass destruction or for the purpose of any other military

use. When exporting the products or technology described herein, you should follow the applicable export

control laws and regulations, and procedures required by such laws and regulations.

4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and

application circuit examples, is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas products listed in this

document, please confirm the latest product information with a Renesas sales office. Also, please pay regular

and careful attention to additional and different information to be disclosed by Renesas such as that disclosed

through our website. (http://www.renesas.com )

5. Renesas has used reasonable care in compiling the information included in this document, but Renesas

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information

included in this document.

6. When using or otherwise relying on the information in this document, you should evaluate the information in

light of the total system before deciding about the applicability of such information to the intended application.

Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any

particular application and specifically disclaims any liability arising out of the application and use of the

information in this document or Renesas products.

7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas

products are not designed, manufactured or tested for applications or otherwise in systems the failure or

malfunction of which may cause a direct threat to human life or create a risk of human injury or which require

especially high quality and reliability such as safety systems, or equipment or systems for transportation and

traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication

transmission. If you are considering the use of our products for such purposes, please contact a Renesas

sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

(1) artificial life support devices or systems

(2) surgical implantations

(3) healthcare intervention (e.g., excision, administration of medication, etc.)

(4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who

elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas

Technology Corp., its affiliated companies and their officers, directors, and employees against any and all

damages arising out of such applications.

9. You should use the products described herein within the range specified by Renesas, especially with respect

to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation

characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or

damages arising out of the use of Renesas products beyond such specified ranges.

10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific

characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use

conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and

injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for

hardware and software including but not limited to redundancy, fire control and malfunction prevention,

appropriate treatment for aging degradation or any other applicable measures. Among others, since the

evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or

system manufactured by you.

11. In case Renesas products listed in this document are detached from the products to which the Renesas

products are attached or affixed, the risk of accident such as swallowing by infants and small children is very

high. You should implement safety measures so that Renesas products may not be easily detached from your

products. Renesas shall have no liability for damages arising out of such detachment.

12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written

approval from Renesas.

13. Please contact a Renesas sales office if you have any questions regarding the information contained in this

document, Renesas semiconductor products, or if you have any other inquiries.

Page 3

Table of Contents

Chapter1 Overview..............................................................................................................................1-1

1.1 Overview .................................................................................................................................................................... 1-2

1.2 Configuration..............................................................................................................................................................1-2

1.3 External Specifications...............................................................................................................................................1-3

1.4 External View .............................................................................................................................................................1-4

1.5 M3A-HS85 Block Diagram.......................................................................................................................................... 1-5

1.6 M3A-HS85 Board Overview .......................................................................................................................................1-6

1.7 M3A-HS85 Memory Mapping.....................................................................................................................................1-8

1.8 Absolute Maximum Ratings...................................................................................................................................... 1-11

1.9 Recommended Operating Conditions ...................................................................................................................... 1-11

Chapter2 Functional Overview ............................................................................................................2-1

2.1 Functional Overview................................................................................................................................................... 2-2

2.2 CPU............................................................................................................................................................................ 2-3

2.3 Memory ...................................................................................................................................................................... 2-4

2.3.1 SH7285 On-Chip Memory................................................................................................................................. 2-4

2.3.2 SRAM................................................................................................................................................................ 2-4

2.3.3 SDRAM.............................................................................................................................................................2-5

2.3.4 EEPROM...........................................................................................................................................................2-6

2.4 Serial Port Interface.................................................................................................................................................... 2-7

2.5 I/O Ports.....................................................................................................................................................................2-8

2.6 Power Supply Module...............................................................................................................................................2-11

2.7 USB Interface...........................................................................................................................................................2-12

2.8 Clock Module............................................................................................................................................................ 2-13

2.9 Reset Module........................................................................................................................................................... 2-14

2.10 Interrupt Switches................................................................................................................................................... 2-14

2.11 E10A-USB Interface...............................................................................................................................................2-15

Chapter3 Operational Specifications...................................................................................................3-1

3.1 M3A-HS85 Connectors Outline.................................................................................................................................. 3-2

3.1.1 H-UDI Connector (J1, J2).................................................................................................................................. 3-3

3.1.2 Serial Port Connector (J3)................................................................................................................................. 3-5

3.1.3 Power Supply Connector (J4) ........................................................................................................................... 3-6

3.1.4 External Power Supply Connector for SH7285 (J5, J6).....................................................................................3-7

3.1.5 DC Power Jack (J7) .......................................................................................................................................... 3-8

3.1.6 Extension Connectors (J8-J12).........................................................................................................................3-9

3.1.7 Extension Connector (J13).............................................................................................................................. 3-15

3.1.8 USB Connector (J14)......................................................................................................................................3-16

3.1.9 GND Connector (J15) ..................................................................................................................................... 3-17

3.2 Outline of Switches and LEDs..................................................................................................................................3-18

3.2.1 CPU Power Supply Select Jumpers (JP1) ...................................................................................................... 3-19

3.2.2 External Power Supply Select Jumper (JP2, JP3, JP4, JP5)..........................................................................3-20

3.2.3 FWE Pin Select Jumper (JP6)......................................................................................................................... 3-21

Rev. 1.04 2008.07.15 (i)

REJ10J1564-0104

Page 4

3.2.4 Serial Port Select Jumper (JP7, JP8)..............................................................................................................3-22

3.2.5 Switch and LED Functions.............................................................................................................................. 3-23

3.2.6 Jumper Switch Setting when Using Development Tool................................................................................... 3-25

3.3 Board Dimensions of M3A-HS85.............................................................................................................................. 3-26

Appendix.............................................................................................................................................A-1

M3A-HS85 SCHEMATICS

Rev. 1.04 2008.07.15 (ii)

REJ10J1564-0104

Page 5

Chapter1Overview

Chapter1

Overview

1-1

Page 6

1

1.1 Overview

1.1 Overview

The M3A-HS85 is the CPU board designed for users to evaluate the functionalit y and performance of the SH7285

group of Renesas Technology original microcomputer, as well as develop and evaluate the application software for

this group of microcomputers. The Sh7285’s data bus, address bus and various internal peripheral circuit function

pins are connected to the extension connector of the M3A-HS85, al lowing users to evaluate the timing relationship

with peripheral devices using measurement instruments or develop extension boards tailored to suit development

purposes. Furthermore, the E10A-USB or the on-chip emulator made by Renesas Technology can also be connected

to the M3A-HS85.

1.2 Configuration

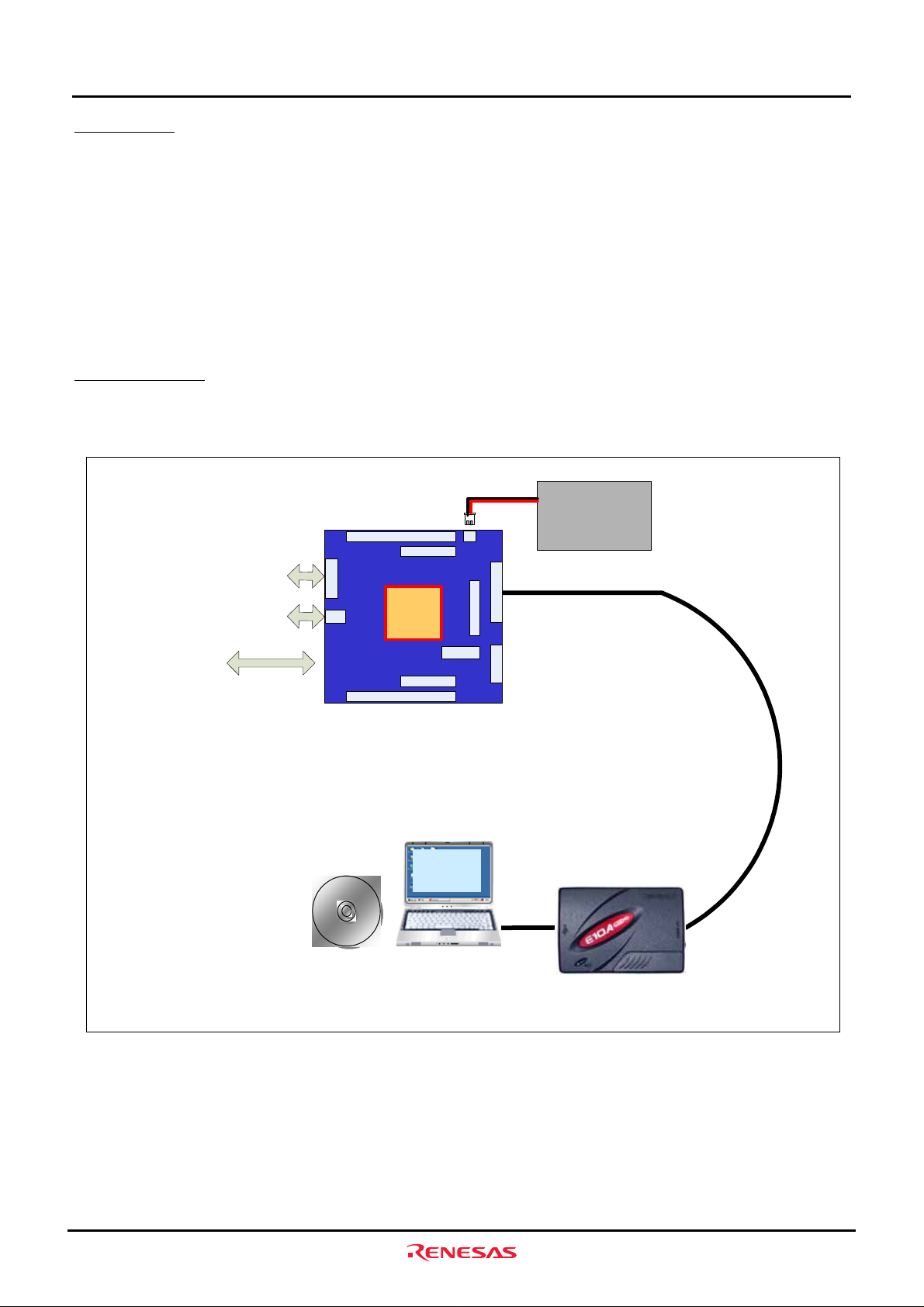

Figure 1.2.1 shows an example of system configuration using the M3A-HS85.

SH7285 CPU Board

M3A-HS85

Serial port

connector

USB

Extension

connector

High-performance

Embeded Workshop(HEW)

SuperH RISC engine

C/C++ compiler package

* : It is necessary to prepare separately for software development.

*

*

Figure 1.2.1 Example System Configuration of M3A-HS85

SH7285

HEW

debugger

Host

computer

USB

*

DC 5V

Power Supply

(1.5A min.)

H-UDI connector

(14-pin or 36-pin)

E10A-USB

*

*

Overview

Rev.1.04 2008.07.10

REJ10J1564-0104

1-2

Page 7

1

1.3 External Specifications

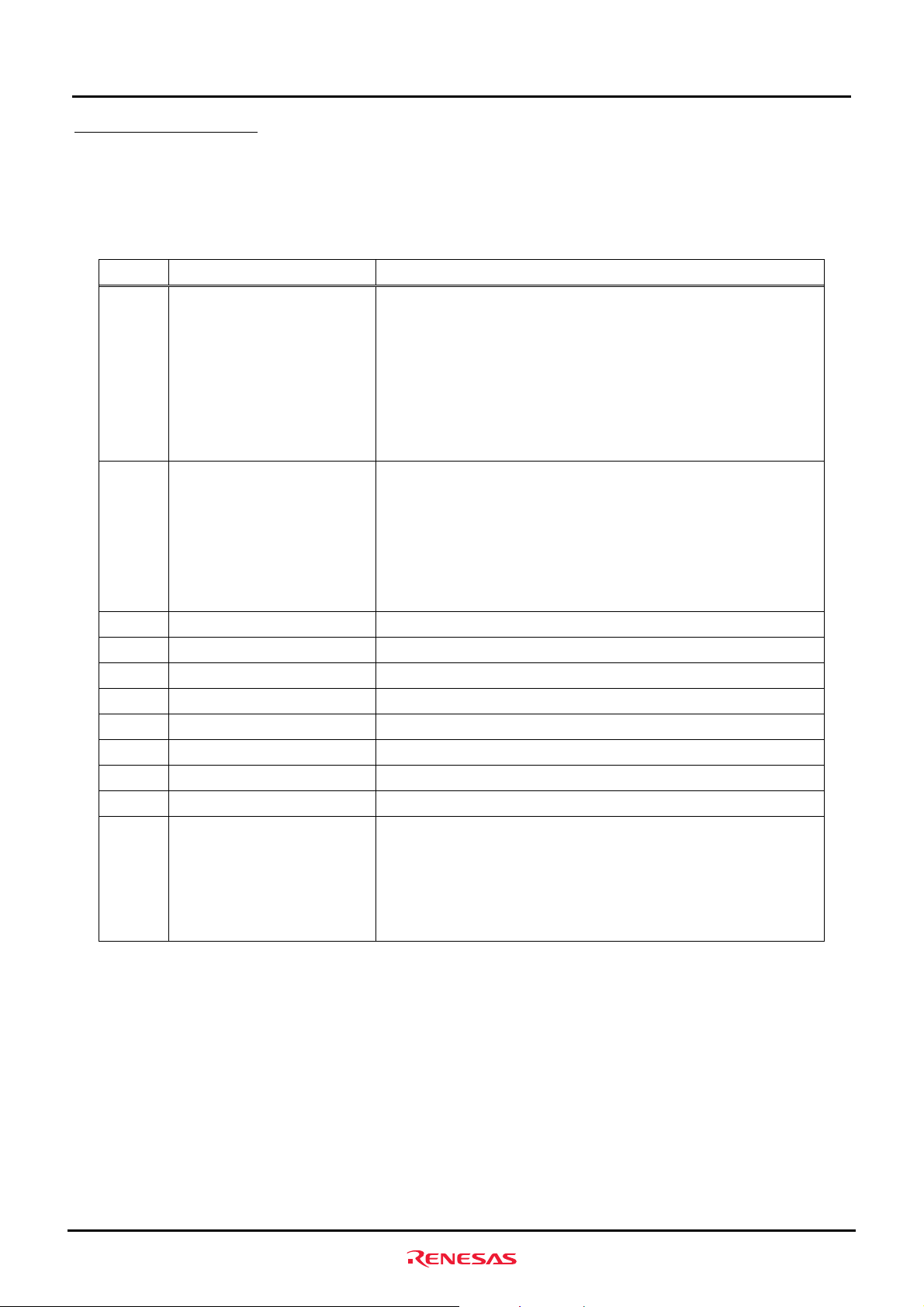

Table 1.3.1 lists the external specifications of M3A-HS85.

Table 1.3.1 External Specifications of M3A-HS85

No. Item Content

SH7285

z Input(XIN) Clock: 12.5 MHz

z CPU Clock: Maximum 100 MHz

1 CPU

2 Memory

3 Connector

4 LED

5 Switch

6 Package Dimension

z Bus Clock: Maximum 50 MHz

z On-chip memory

• Flash Memory: 768 KB

• RAM: 32 KB

z SRAM: 2-Mbyte (16-bit bus width x 1 pc.) (Not mounted)

*Can be mounted only when SH7285 is used in 3.3V.

z SDRAM: 16-Mbyte (16-bit bus width x 1 pc.) (Not mounted)

*Can be mounted only when SH7285 is used in 3.3V.

z EEPROM: 128k-bit (Not mounted)

HN58X24128FPIE x 1 pc. (I

z Extension connector (Bus,I/O,VCC,GND)

z USB connector (Standard-B receptacle)

z Serial port connector (D-sub 9-pin)

z H-UDI connector (14-pin)

z H-UDI connector (36-pin)

z POWER LED (1pc.)

z User LED (6pcs.)

z Reset switch (1pc.)

z NMI switch (1pc.)

z IRQ1 switch (1 pc.)

z DIP switch for system setting (1pc., 4 poles)

z DIP switch for user (1pc., 4 poles)

z Dimensions : 100mm x 100mm

z Mounting form : 6-layer, double side mounted

z Board configuration : 1 board

2

C bus connection)

Overview

1.3 External Specifications

Rev.1.04 2008.07.10

REJ10J1564-0104

1-3

Page 8

1

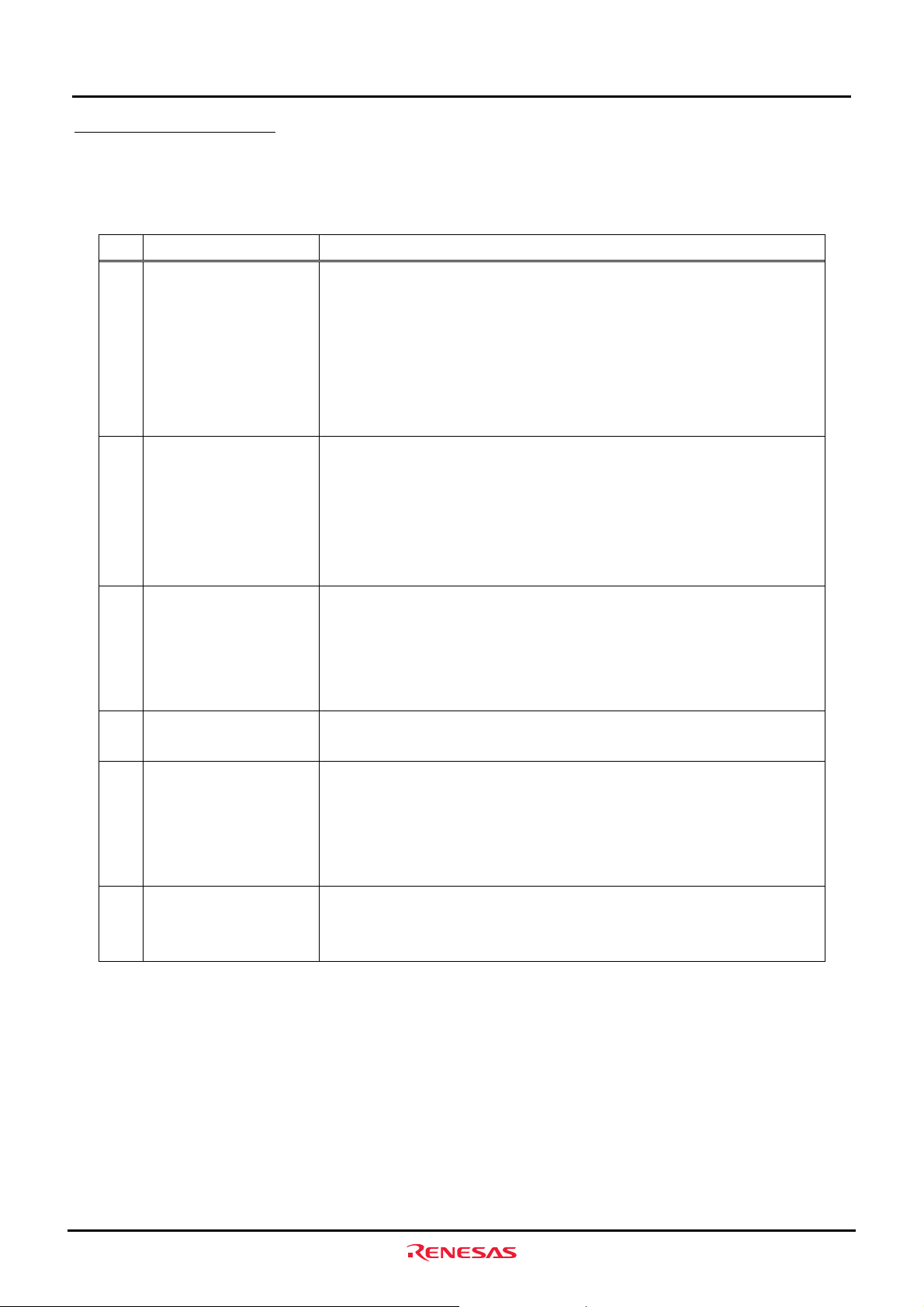

1.4 External View

Figure 1.4.1 shows the external view of M3A-HS85.

Figure 1.4.1 External View of M3A-HS85

Overview

1.4 External View

Rev.1.04 2008.07.10

REJ10J1564-0104

1-4

Page 9

1

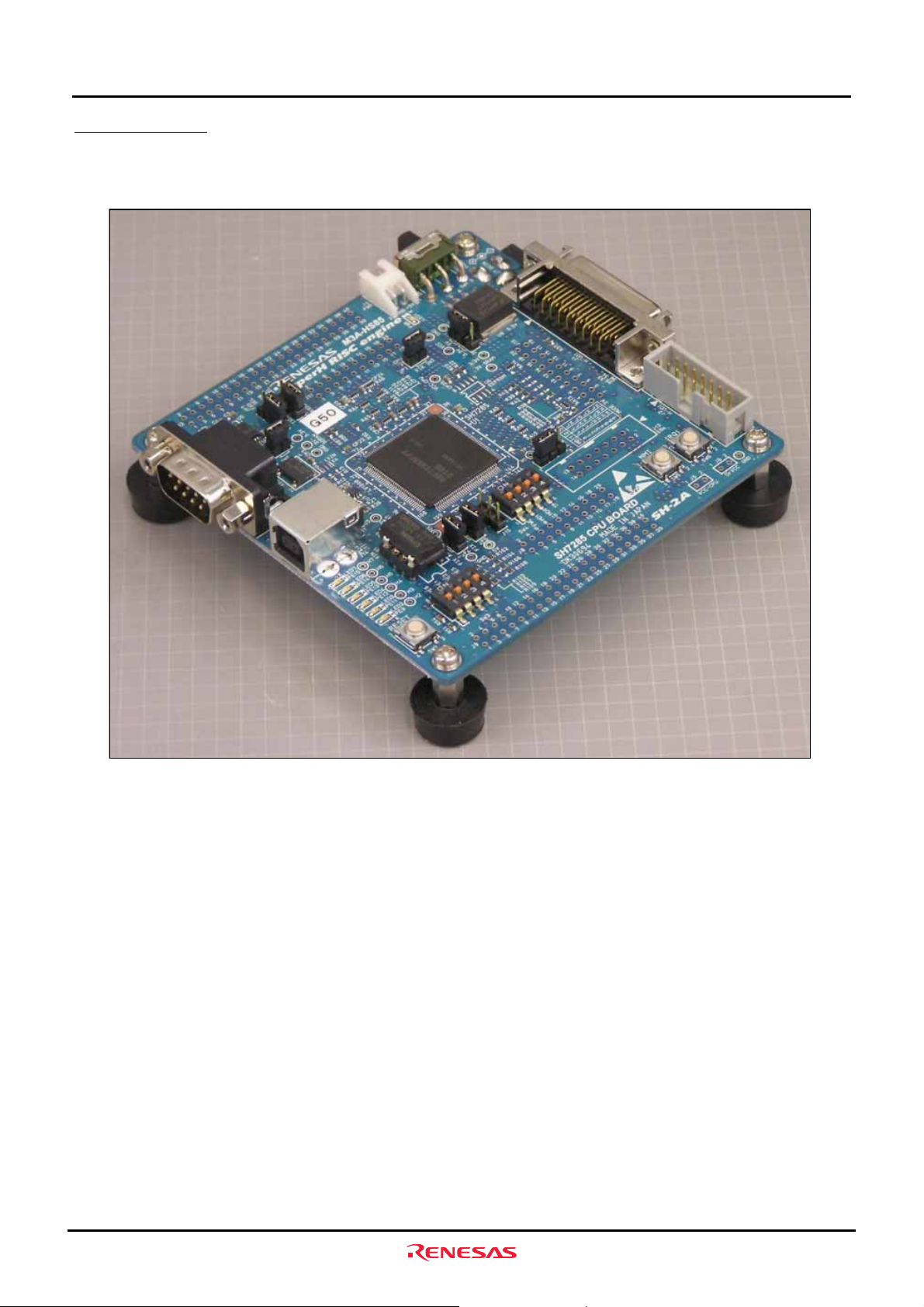

1.5 M3A-HS85 Block Diagram

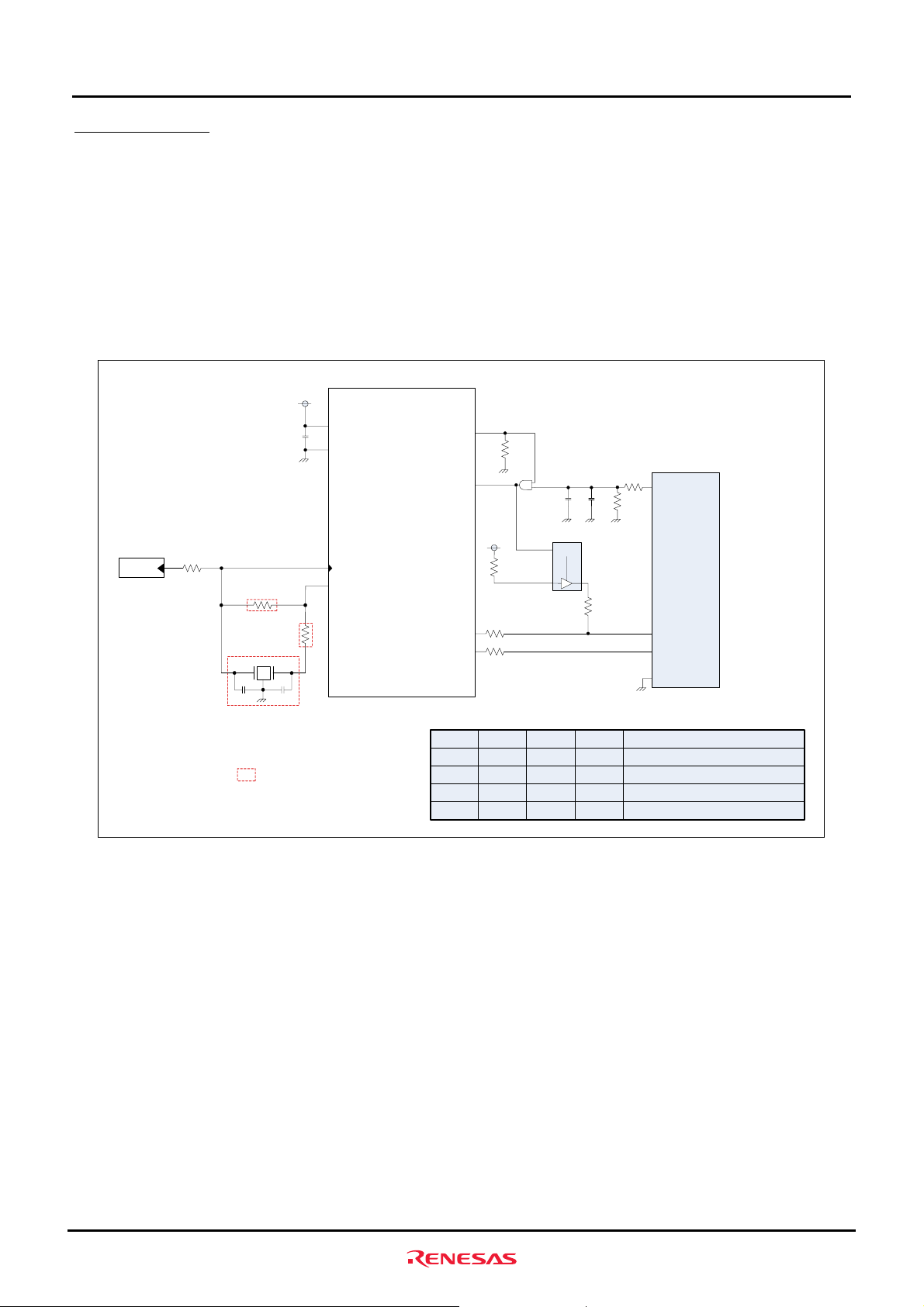

Figure 1.5.1 shows the system block diagram of M3A-HS85.

SRAM

2 MB

H-UDI connector

(36-pin)

EEPROM

(128 k-bit)

*

AUD

I2C

H-UDI connector

H-UDI

(14-pin)

SH7285

(100 MHz)

SCI0

(48 MHz)

(12.5 MHz)

Serial Port

Connector

USB

USBXIN

XIN

Overview

1.5 M3A-HS85 Block Diagram

USB

Connector

SDRAM

16 MB

*

16

16

16

SH7285 CPU Board

M3A-HS85

Extension Connectors

: It is not mounted.

* : It can be mounted only when SH7285 is used in 3.3V.

Figure 1.5.1 System Block Diagram of M3A-HS85

16

External bus: Maximum 50 MHz

Rev.1.04 2008.07.10

REJ10J1564-0104

1-5

Page 10

1

1.6 M3A-HS85 Board Overview

Figure 1.6.1 shows the M3A-HS85 board overview.

<Top view of the component side>

Overview

1.6 M3A-HS85 Board Overview

<Top view of the solder side>

Rev.1.04 2008.07.10

REJ10J1564-0104

Figure 1.6.1 M3A-HS85 Board Overview

1-6

Page 11

1

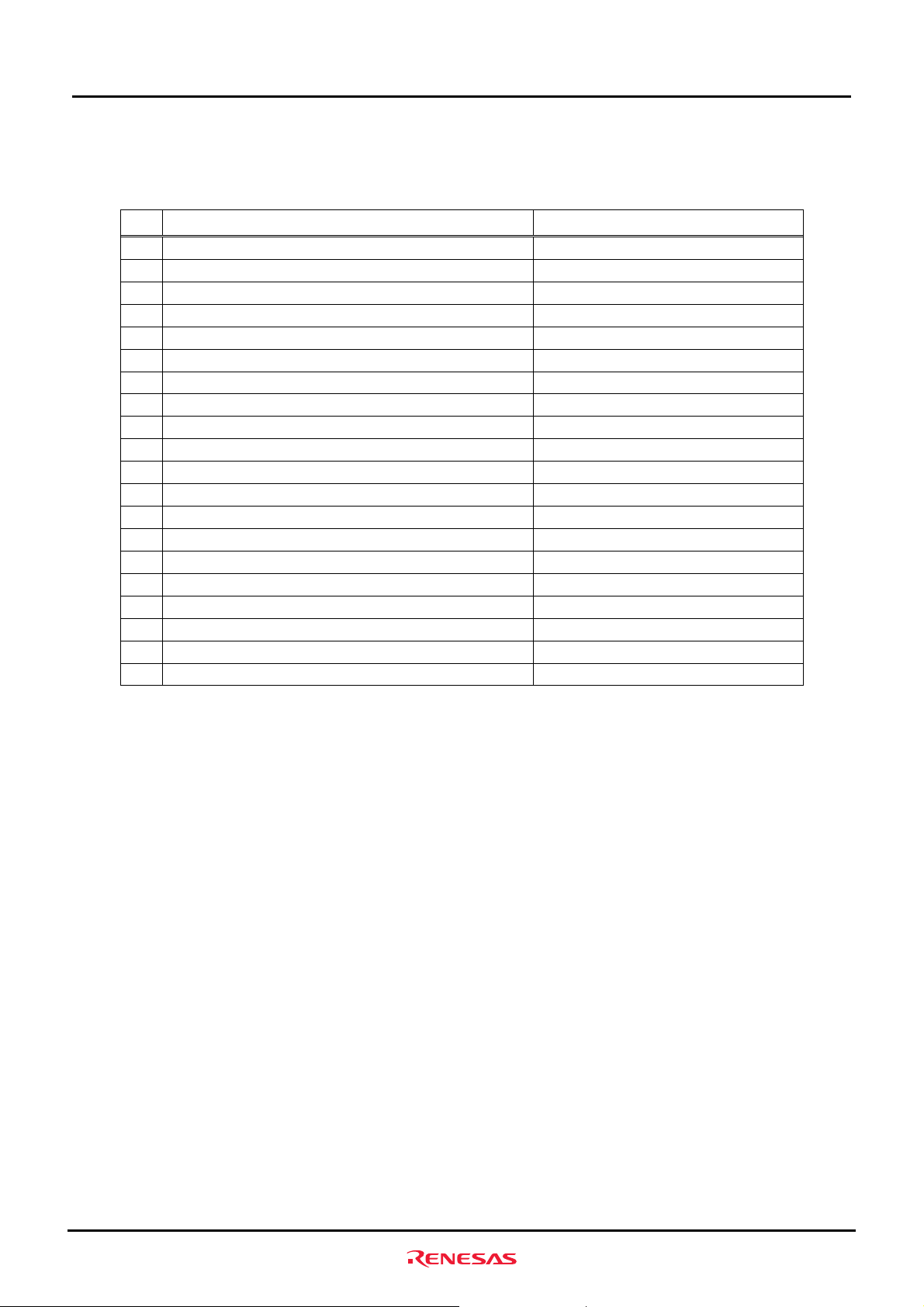

Table 1.6.1 lists the main components mounted on the M3A-HS85.

Table 1.6.1 Main Components Mounted in the M3A-HS85

Overview

1.6 M3A-HS85 Board Overview

Symbol Parts Name Remarks

U1 CPU SH7285 (Renesas)

U2 SRAM Not mounted R1LV1616RSA-7S (Renesas)

U3 SDRAM Not mounted EDS1216AATA-75E (Elpida)

U4 EEPROM Not mounted HN58X24128FPIE (Renesas)

U5 RS-232C driver SP3232ECA(Sipex)

U6 Reset IC

X1

X1

X2

X3

X4

J1 H-UDI connector (36pin) DX10M-36SE(50) (Hirose)

J2 H-UDI connector (14pin) 7614-6002BL(3M)

J3 Serial port connector XM2C-0942-132L(Omron)

J4

J5

J6

J7 DC power jack

J8,J10,J11

J9,J12

J13

J14 USB connector UBB-4R-D14T-4D(SN)(LF) (JST)

LED1

LED2-7

SW1

SW2

SW3

SW4

SW5 NMI switch Push switch B3SN-3012 (Omron)

SW6 IRQ1 switch Push switch B3SN-3012 (Omron)

Oscillator

Oscillator

Resonator

Oscillator

Resonator

Power supply connector

External power supply

connector

External power supply

connector

Extension connector

Extension connector

Extension connector

Power LED

User LED

Power switch

Reset switch

DIP switch for user

DIP switch for system setting

socket

(20pin)

(40pin)

(14pin)

M51957BFP

SG8002DC_12.5MHz (Epson)

R110-83-308(Preci-Dip)

Not mounted

SG8002JF_48MHz (Epson)

Not mounted

S2B-XH-A(JST)

Not mounted

Not mounted

Not mounted

Not mounted XG4C-2031 (Omron)

Not mounted XG4C-4031 (Omron)

Not mounted

Blue UB1111C (Stanley)

Green SML-310MT (Rohm)

MS-12AAH1 (Nihon Kaiheiki)

Push switch

B3SN-3012 (Omron)

4 poles A6S-4104 (Omron)

4 poles A6S-4104 (Omron)

(Renesas)

Recommended components

(Part number and manufacture)

CSTCE-G12M5 (Murata)

CSTCZ48M0X12R (Murata)

A2-2PA-2.54DSA (Hirose)

A2-2PA-2.54DSA (Hirose)

HEC0470-01-630 (HOSIDEN)

7614-6002 (Sumitomo 3M)

Rev.1.04 2008.07.10

REJ10J1564-0104

1-7

Page 12

1

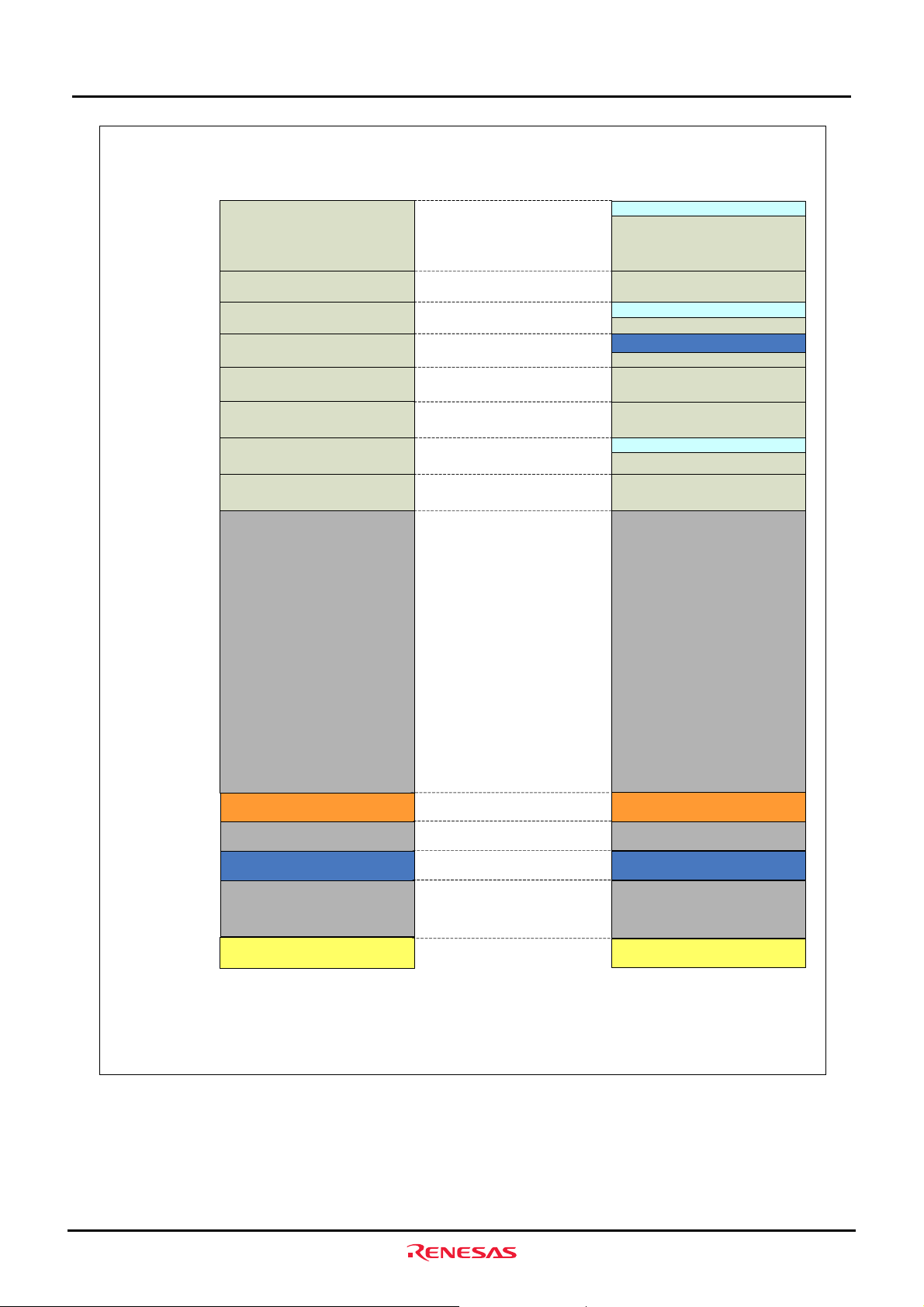

1.7 M3A-HS85 Memory Mapping

1.7 M3A-HS85 Memory Mapping

Figure 1.7.1, Figure 1.7.2, and Figure 1.7.3 show the memory mapping examples of SH7285 in the M3A- HS85.

Logical space of the SH7285

H'0000 0000

H'000B FFFF

H'000C 0000

MCU mode 3

(Single Chip Mode)

On-chip ROM(768KB)

H'0000 0000

H'000B FFFF

H'000C 0000

M3A-HS85 Memory Mapping

On-chip ROM(768KB)

Overview

H'801F FFFF

H'8020 0000

H'802F FFFF

H'8030 0000

Reserved

On-chip flash memory

writing/verify space

Reserved

H'801F FFFF

H'8020 0000

H'802F FFFF

H'8030 0000

Reserved

On-chip flash memory

writing/verify space

Reserved

H'FFF7 FFFF

H'FFF8 0000

H'FFF8 7FFF

H'FFF8 8000

H'FFFB FFFF

H'FFFC 0000

H'FFFC FFFF

H'FFFD 0000

H'FFFD FFFF

H'FFFE 0000

H'FFFF FFFF

Rev.1.04 2008.07.10

REJ10J1564-0104

H'FFF7 FFFF

On-chip RAM(32KB)

Reserved

SDRAM mode setting

H'FFF8 0000

H'FFF8 7FFF

H'FFF8 8000

H'FFFB FFFF

H'FFFC 0000

H'FFFC FFFF

On-chip RAM(32KB)

Reserved

SDRAM mode setting

H'FFFD 0000

Reserved

Reserved

H'FFFD FFFF

Peripheral I/O

Figure 1.7.1 Memory Mapping Example of SH7285 (MCU mode 3)

1-8

H'FFFE 0000

H'FFFF FFFF

Peripheral I/ O

Page 13

1

H'0000 0000

H'03FF FFFF

H'0400 0000

H'07FF FFFF

H'0800 0000

H'0BFF FFFF

H'0C00 0000

H'0FFF FFFF

H'1000 0000

H'13FF FFFF

H'1400 0000

H'17FF FFFF

H'1800 0000

H'1BFF FFFF

H'1C00 0000

H'1FFF FFFF

H'2000 0000

Logical space of the SH7285

MCU mode 0, 1

(On-chip ROM disabled mode)

CS0 space

CS1 space

CS2 space

CS3 space

CS4 space

CS5 space

CS6 space

CS7 space

H'0000 0000

H'03FF FFFF

H'0400 0000

H'07FF FFFF

H'0800 0000

H'0BFF FFFF

H'0C00 0000

H'0CFF FFFF

H'1000 0000

H'13FF FFFF

H'1400 0000

H'17FF FFFF

H'1800 0000

H'1BFF FFFF

H'1C00 0000

H'1FFF FFFF

H'2000 0000

Overview

1.7 M3A-HS85 Memory Mapping

M3A-HS85 Memory Mapping

SRAM(2MB) *1 *2 *3

User area *3

User area

SRAM(2MB) *1 *2

User area

SDRAM(16MB) *2

User area

User area

User area

SRAM(2MB) *1 *2

User area

User area

H'FFF8 7FFF

H'FFF8 8000

Reserved

H'FFF7 FFFF

H'FFF8 0000

H'FFFB FFFF

H'FFFC 0000

H'FFFC FFFF

H'FFFD 0000

On-chip RAM(32KB)

Reserved

SDRAM mode setting

Reserved

H'FFFD FFFF

H'FFFE 0000

Peripheral I/O

H'FFFF FFFF

[Notes] *1:CS space to assign is selected according to software. CS space which can be selected at a

time is only one.

*2:It is initially not mounted.

*3:ROM for program is necessary for CS0 space.

Figure 1.7.2 Example Memory Mapping of SH7285 (MCU mode 0,1)

H'FFF7 FFFF

H'FFF8 0000

H'FFF8 7FFF

H'FFF8 8000

H'FFFB FFFF

H'FFFC 0000

H'FFFC FFFF

H'FFFD 0000

H'FFFD FFFF

H'FFFE 0000

H'FFFF FFFF

Reserved

On-chip RAM(32KB)

Reserved

SDRAM mode setting

Reserved

Peripheral I/O

Rev.1.04 2008.07.10

REJ10J1564-0104

1-9

Page 14

1

H'000C 0000

H'0400 0000

H'0000 0000

H'000B FFFF

H'01FF FFFF

H'0200 0000

H'03FF FFFF

H'07FF FFFF

H'0800 0000

H'0BFF FFFF

H'0C00 0000

H'0FFF FFFF

H'1000 0000

H'13FF FFFF

H'1400 0000

H'17FF FFFF

H'1800 0000

H'1BFF FFFF

H'1C00 0000

H'1FFF FFFF

H'2000 0000

Logical space of the SH7285

MCU mode 2

(On-chip ROM enabled mode)

On-chip ROM(768KB)

Reserved

CS0 space

CS1 space

CS2 space

CS3 space

CS4 space

CS5 space

CS6 space

CS7 space

H'0000 0000

H'000B FFFF

H'000C 0000

H'01FF FFFF

H'0200 0000

H'03FF FFFF

H'0400 0000

H'07FF FFFF

H'0800 0000

H'0BFF FFFF

H'0C00 0000

H'0FFF FFFF

H'1000 0000

H'13FF FFFF

H'1400 0000

H'17FF FFFF

H'1800 0000

H'1BFF FFFF

H'1C00 0000

H'1FFF FFFF

H'2000 0000

Overview

1.7 M3A-HS85 Memory Mapping

M3A-HS85 Memory Mapping

On-chip ROM(768KB)

Reserved

SRAM(2MB) *1 *2

User area

User area

SRAM(2MB) *1 *2

User area

SDRAM(16MB) *2

User area

User area

User area

SRAM(2MB) *1 *2

User area

User area

H'801F FFFF

H'8020 F000

H'802F FFFF

H'8030 0000

H'FFF7 FFFF

H'FFF8 0000

H'FFF8 7FFF

H'FFF8 8000

H'FFFB FFFF

H'FFFC 0000

H'FFFC FFFF

H'FFFD 0000

H'FFFD FFFF

H'FFFE 0000

H'FFFF FFFF

Reserved

On-chip flash memory

writing/verify space

Reserved

On-chip RAM(32KB)

Reserved

SDRAM mode setting

Reserved

Peripheral I/O

H'801F FFFF

H'8020 F000

H'802F FFFF

H'8030 0000

H'FFF7 FFFF

H'FFF8 0000

H'FFF8 7FFF

H'FFF8 8000

H'FFFB FFFF

H'FFFC 0000

H'FFFC FFFF

H'FFFD 0000

H'FFFD FFFF

H'FFFE 0000

H'FFFF FFFF

Reserved

On-chip flash memory

writing/verify space

Reserved

On-chip RAM(32KB)

Reserved

SDRAM mode setting

Reserved

Peripheral I/O

[Notes] *1:CS space to assign is selected according to software. CS space which can be selected at a

time is only one.

*2:It is initially not mounted.

Rev.1.04 2008.07.10

REJ10J1564-0104

Figure 1.7.3 Example Memory Mapping of SH7285 (MCU mode 2)

1-10

Page 15

1

1.8 Absolute Maximum Ratings

1.8 Absolute Maximum Ratings

Table 1.8.1 lists the absolute maximum rating of M3A-HS85.

Table 1.8.1 Absolute Maximum Ratings of M3A-HS85

Symbol Parameter Rated Value Remarks

Overview

5VCC

3VCC 3.3V

Topr

Tstr

Note: The ambient temperature refers to the air temperature in places closest possible to the board.

5V System Power Supply Voltage

System Power Supply

Voltage

Operating Ambient Temperature

Storage Ambient T emperature

-0.3V to 6.0V Relative to VSS

-0.3V to 4.6V

0°C to 50°C

-10°C to 60°C

Relative to VSS

No dewdrops allowed.

Use in corrosive gas environment prohibited.

No dewdrops allowed.

Use in corrosive gas environment prohibited.

1.9 Recommended Operating Conditions

Table 1.9.1 lists the recommended operating conditions of M3A-HS85.

Table 1.9.1 Recommended Operating Conditions of M3A-HS85

Symbol Parameter Rated Value Remarks

5VCC

3VCC 3V

Topr

5V System Power Supply Voltage

Maximum Current Consumption in

the Board

Operating Ambient T emperature

System Power Supply Voltage

3.0V to 3.6V

4.5V to 5.5V

Within 1A

0°C to 50°C

Relative to VSS

Relative to VSS

No dewdrops allowed.

Use in corrosive gas environment prohibited.

Rev.1.04 2008.07.10

REJ10J1564-0104

1-11

Page 16

1

Overview

1.8 Absolute Maximum Ratings

*This is a blank page*

Rev.1.04 2008.07.10

REJ10J1564-0104

1-12

Page 17

Chapter2Functional Overview

Chapter2

Functional Overview

2-1

Page 18

2

2.1 Functional Overview

The M3A-HS85 is the SH7285 CPU board that has the functions listed in Table 2.1.1.

Table 2.1.1 lists the functional modules of M3A-HS85.

Table 2.1.1 Functional Modules of M3A-HS85

Section Function Content

Functional Overview

2.1 Functional Overview

2.2 CPU

SH7285

• Input(XIN) Clock: 12.5 MHz

• CPU Clock: Maximum 100 MHz

• Bus Clock: Maximum 50 MHz

• On-Chip Memory

- Flash Memory: 768 kBytes

- RAM: 32 kBytes

2.3 Memory

• SRAM : 2-Mbyte (16-bit bus width x 1pc.) (Not mounted)

*Can be mounted only when SH7285 is used in 3.3V.

• SDRAM : 16-Mbyte(16-bit bus width x 1pc.) (Not mounted)

*Can be mounted only when SH7285 is used in 3.3V.

• EEPROM : 128 kBits (Not mounted)

HN58X24128FPIE x 1 pc. (I2C bus connection)

2.4 Serial Port Interface Connects SCI0 or SCI3 of SH7285 to the serial port connector

2.5 I/O Ports Connects to the input/output ports of the SH7285

2.6 Power Supply Module Controls the system power supply of the M3A-HS85

2.7 USB Interface Connects USB pin of SH7285 to USB connector

2.8 Clock Module Controls the system clock

2.9 Reset Module Controls the device reset mounted on the M3A-HS85

2.10 Interrupt Switches Connect to the NMI pin, IRQ0 pin and test port

2.11 E10A-USB Interface SH7285 H-UDI/AUD interface

- Operational Specifications Connectors, Switches and LEDs

• SH7285 extension connector

• Switches and LEDs

• H-UDI connector

Detailed in Chapter 3.

Rev.1.04 2008.7.10

REJ10J1564-0104

2-2

Page 19

Functional Overview

2

2.2 CPU

The M3A-HS85 contains the 32-bit RISC microcomputer SH7285 that operates with a maximum 100MHz of CPU

clock frequency. The SH7285 includes 768-Kbyte flash memory, and 32-Kbyte RAM, making it useful in a wide range

of applications from data processing to equipment control.

The M3A-HS85 can be operated with a maximum 100MHz of CPU clock frequency (external bus maximum 50

MHz) using a 12.5 MHz input clock.

Figure 2.2.1 shows the SH7285 block diagram in the M3A-HS85.

SH7285

2.2 CPU

Clock

Mode

SW

System

control

LED for

user

DIP

switch

for user

EEPROM

USB

Serial

port

GPIO,

Control

signal,

MTU2/2S,

Interrupt,

etc

EXTAL

XTAL

PA15/CK

MD1

MD0

FWE/ASEBRKAK/ASEBRK

RES

NMI

WDTOVF

PE9/TIOC3B/FRAME

PE11/TIOC3D

PE12/TIOC4A

PE13/TIOC4B/MRES

PE14/DACK0/TIOC4C/AH

PE15/DACK1/TIOC4D/IRQOUT

PE0/TIOC0A/TIOC4AS/DREQ0

PE1/TIOC0B/TIOC4BS/TEND0

PE2/TIOC0C/TIOC4CS/DREQ1

PE3/TIOC0D/TIOC4DS/TEND1

PB2/SCL/POE1/IRQ0

PB3/SDA/POE2/IRQ1

USBXTAL

USBEXTAL

PB9/USPND

VBUS

USD+

USDPB10

PE4/TIOC1A/RXD3

PE5/TIOC1B/TIOC3BS/TXD3

PA5/SCK1/SSCK/CS5

PA6/TCLKA/RASL

PA7/TCLKB/SCK3/CASL

PA8/TCLKC/TXD3/RDWR

PA9/TCLKD/RXD3/CKE

PA12/WRH/DQMLU/POE8

PA13/WRL/DQMLL

PA14/RD

PA23/TIC5W/POE0/IRQ1/AH/CKE

PA22/TIC5V/CASU/POE4/IRQ2/CASL

PA21/TIC5U/RASU/POE8/IRQ3/RASL

PB11/RXD2/CS6/CS2/CS0/IRQ0

PB12/TXD2/CS7/CS3/CS1/IRQ1

PD20/IRQ4/TIC5WS/SCK4/POE8

PD21/IRQ5/TIC5VS/TXD4

PD25/TIOC4CS/DREQ1

PD26/TIOC3BS/DACK1

PD27/TIOC4AS/DACK0

PD28/TIOC3DS

PD29/TIOC3BS

PD30/TIOC3CS/IRQOUT

PD31/TIOC3AS/ADTRG

PE4/TIOC1A/RXD3

PE5/TIOC1B/TIOC3BS/TXD3

PE6/TIOC2A/TIOC3DS/SCK3

PE7/TIOC2B/RXD2/BS/UBCTRG

PE8/TIOC3A/SCK2

PE10/TIOC3C/TXD2

H-UDI

Figure 2.2.1 SH7285 Block Diagram

PC0/A0/POE0

PC1/A1

PC2/A2

PC3/A3

PC4/A4

PC5/A5

PC6/A6

PC7/A7

PC8/A8

PC9/A9

PC10/A10

PC11/A11

PC12/A12

PC13/A13/IRQ0

PC14/A14/IRQ1

PC15/A15/IRQ2

PB1/A17/REFOUT/ADTRG/IRQ4

PB6/A18/BACK/POE3/IRQ5/RXD0

PB7/A19/BREQ/POE4/IRQ6/TXD0

PB8/A20/WAIT/POE8/IRQ7/SCK0

Switch by JP7

and JP8

Serial port,

Extension connector

(J13)

Mode SW

PD17/IRQ1/POE5/SCK3/CS2/AUDATA1

PD18/IRQ2/POE6/TXD3/CS1/AUDATA2

PD19/IRQ3/POE7/RXD3/CS0/AUDATA3

PD22/IRQ6/TIC5US/RXD4/AUDSYNC

PA2/SCK0/SCS/CS2/TCK

PA3/RXD1/SSI/CS3/TMS

PA4/TXD1/SSO/CS4/TRST

FWE/ASEBRKAK/ASEBRK

PD16/IRQ0/CS3/AUDATA0

PD24/DREQ0/TIOC4DS/AUDCK

PB0/A16/IRQ3

PD0/D0

PD1/D1

PD2/D2/TIC5U

PD3/D3/TIC5V

PD4/D4/TIC5W

PD5/D5/TIC5US

PD6/D6/TIC5VS

PD7/D7/TIC5WS

PD8/D8/TIOC3AS

PD9/D9/TIOC3CS

PD10/D10/TIOC3BS

PD11/D11/TIOC3DS

PD12/D12/TIOC4AS

PD13/D13/TIOC4BS

PD14/D14/TIOC4CS

PD15/D15/TIOC4DS

PA0/RXD0/CS0/TDI

PA1/TXD0/CS1/TDO

ASEMD0

PF0/AN0

PF1/AN1

PF2/AN2

PF3/AN3

PF4/AN4

PF5/AN5

PF6/AN6

PF7/AN7

Address bus

Data bus

H-UDI

AUD

A/D

Rev.1.04 2008.7.10

REJ10J1564-0104

2-3

Page 20

Functional Overview

2

2.3 Memory

2.3.1 SH7285 On-Chip Memory

The SH7285 includes a 768-Kbytes flash memory and 32-Kbytes RAM.

2.3.2 SRAM

Two Mbytes of SRAM can be mounted on the M3A-HS85 (Not mounted). In the M3A-HS85 specification, 3.3V

power is supplied to SRAM so that SH7285 should be used in 3.3V when SRAM is mounted (CPU power supply

switch jumper (JP1) should be set to “2-3”). SRAM is controlled by the bus state controller built into SH7285. The

address spaces of SRAM can be switched to CS0 space, CS2 space, and CS6 space by the pin function controller

setting of SH7285.

Table 2.3.1 lists the SRAM specifications. Figure 2.3.1 shows the block diagram for the connection between

SH7285 and SRAM.

Table 2.3.1 SRAM Specifications

Part Number Bus size Capacity Package

2.3 Memory

R1LV1616RSA-7S 16 bit 2 Mbytes (16-bit x 1M word x 1 pc.) 48-pin TSOP (20 x 12mm)

SH7285

PB8/A20 - PC1/A1

PB11/CS0/CS2/CS6

PA14/RD

PA8/RDWR

PA12/WRH

PA13/WRL

Figure 2.3.1 Block Diagram for Connection Between SH7285 and SRAM

20

16

Reset

3.3V

R1LV1616RSA-7

16M-bit SRAM

(1M Word ×16bit)

A19 - A0

DQ15 - DQ0PD15/D15 - PD0/D0

BYTE

CS1

CS2

OE

WE

UB

LB

Rev.1.04 2008.7.10

REJ10J1564-0104

2-4

Page 21

Functional Overview

2

2.3.3 SDRAM

The M3A-HS85 can mount 16Mbytes of SDRAM (Not mounted). In the M3A-HS85 specification, 3.3V power is

supplied to SDRAM so that SH7285 should be used in 3.3V when SDRAM is mounted (CPU power supply switch

jumper (JP1) should be set to

Table 2.3.2 lists the SDRAM specifications. Figure 2.3.2 shows the block diagram for the connection between

SH7285 and SDRAM.

Specification Content

Configuration 2M words x 16 bits x 4 banks (1pc.)

Capacity 16 Mbytes

Access Time 5.4ns

CAS Latency 2 (at 40MHz bus clock)

Refresh Interval 4096 refresh cycle every 64ms

Low Address A11- A0

Column Address A8 - A0

Number of Banks 4-bank operation controlled by BA0 and BA1

“2-3”). The SDRAM is controlled by the bus state controller built into SH7285.

Table 2.3.2 SDRAM Specifications

2.3.3 SDRAM

SH7285

PC14/A14

PC13/A13

PC12/A12-PC1/A1

PA15/CK

PA9/CKE

PB12/CS3

PA6/RASL

PA7/CASL

PA8/RDWR

PA12/DQMLU

PA13/DQMLL

PD15/D15-PD0/D0

Figure 2.3.2 Block Diagram for the Connection Between SH7285 and SDRAM

BA1

11

16

BA1

BA0

BA0

A11-A0

A11-A0

CLK

CLK

CKE

CKE

CS#

CS

RAS#

RAS

CAS

CAS

WE#

WE

DQMU

DQMU

DQML

DQML

DQ15-DQ0

SDRAM

(8M Word x 16bit)

Rev.1.04 2008.7.10

REJ10J1564-0104

2-5

Page 22

Functional Overview

2

2.3.4 EEPROM

The M3A-HS85 can mount the 128k-bits of EEPROM (Not mounted). The EEPROM is controlled by the I2C bus

interface included in SH7285.

Table 2.3.3 lists the specification outline of EEPROM.

Figure 2.3.3 shows the connection circuit block diagram of SH7285 and EEPROM.

Table 2.3.3 EEPROM Specification Outline

Part Number I nt erf ace Capacity Package

HN58X24128FPIE 2-wire system serial (I2C bus)

*

128k bit (16k-word x 8-bit) 8-pin SOP

2.3.4 EEPROM

Figure 2.3.3 Block Diagram of SH7285 and EEPROM

Note*: I2C bus is a trademark of Koninklijke Philips Electronics N. V.

Rev.1.04 2008.7.10

REJ10J1564-0104

2-6

Page 23

Functional Overview

2

2.4 Serial Port Interface

2.4 Serial Port Interface

SCI channel 0 or SCI channel 3 of SH7285 can be connected with the serial port connector in the M3A-HS85 (SCI

channel 3 is connected to serial port connector (J3) in initial setting.). SCI channel to connect to a serial port

connector is switched by the serial port switch jumper (JP7 and JP8).

SCI channel 0 of SH7285 is connected to an H-UDI connector (14-pin and 36-pin). When SCI channel 0 of SH7285

is used as a serial port connector, note that it should not be double-used on the other connectors.

Figure 2.4.1 shows the block diagram of serial port interface in the M3A-HS85.

1

2

3

4

5

6

7

8

9

DCD

RxD

TxD

DTR

GND

DSR

RTS

CTS

RI

Serial port

connector

RS-232C

SH7285

JP

PE4/RXD3

PA0/RXD0

PE5/TXD3

PA1/TXD0

1

2

3

JP

1

2

3

H-UDI connector

PA0/RXD0/CS0/TDI

PA1/TXD0/CS1/TDO

Extension connector

PE4/RXD3

PE5/TXD3

Figure 2.4.1 Block Diagram of Serial Port Interface

driver

NC

GND

NC

Rev.1.04 2008.7.10

REJ10J1564-0104

2-7

Page 24

2

2.5 I/O Ports

In the M3A-HS85, all of the SH7285's I/O ports are connected to the extension bus connector.

Some I/O ports are connected to DIP switches and LEDs, and users are free to use these ports.

Figure 2.5.1 shows the block diagram of DIP Switch and LEDs.

Table 2.5.1 lists the functions of the SH7285.

Functional Overview

2.5 I/O Ports

Rev.1.04 2008.7.10

REJ10J1564-0104

Figure 2.5.1 Block Diagram of DIP Switch and LEDs

2-8

Page 25

2

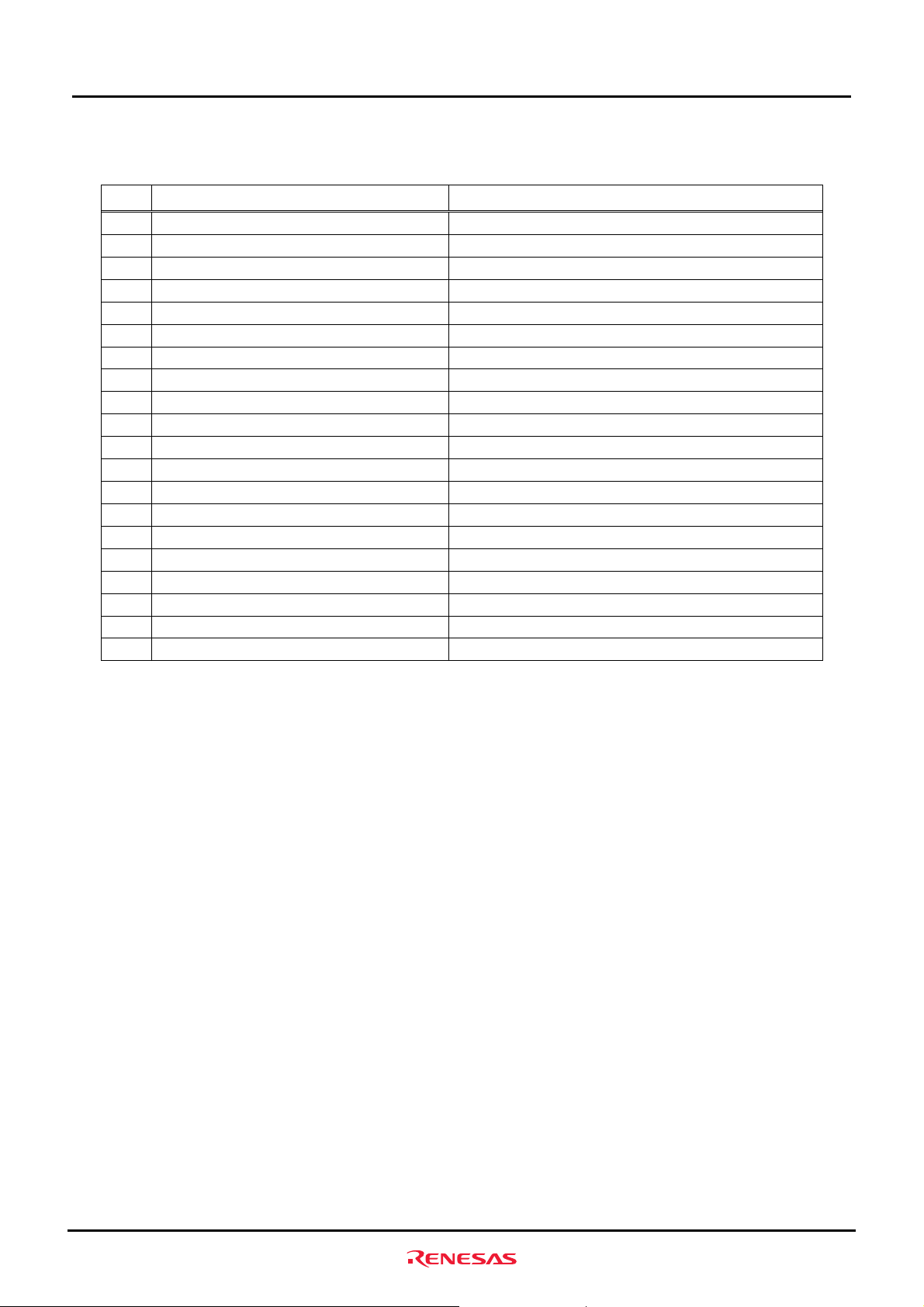

Table 2.5.1 Functions of I/O Ports

SH7285 Extension Connector

No Pin Name J8 J9 J10 J11 J12

1 PE14/DACK0/TIOC4C/AH

2 PE15/DACK1/TIOC4D/IRQOUT

6 PA23/TIC5W/POE0/IRQ1/AH/CKE

7 PA22/TIC5V/CASU/POE4/IRQ2/CASL

8 PA21/TIC5U/RASU/POE8/IRQ3/RASL

9 PC0/A0/POE0

10 PC1/A1

11 PC2/A2

12 PC3/A3

13 PC4/A4

14 PC5/A5

15 PC6/A6

16 PC7/A7

17 PC8/A8

18 PC9/A9

19 PC10/A10

20 PC11/A11

21 PC12/A12

24 PC13/A13/IRQ0

25 PC14/A14/IRQ1

26 PC15/A15/IRQ2

27 PB0/A16/IRQ3

28 PB1/A17/REFOUT/ADTRG/IRQ4

29 PB2/SCL/POE1/IRQ0

30 PB3/SDA/POE2/IRQ1

31 PB6/A18/BACK/POE3/IRQ5/RXD0

32 PB7/A19/BREQ/POE4/IRQ6/TXD0

33 PB8/A20/WAIT/POE8/IRQ7/SCK0

36 PD0/D0

37 PD1/D1

38 PD2/D2/TIC5U

39 PD3/D3/TIC5V

40 PD4/D4/TIC5W

41 PD5/D5/TIC5US

42 PD6/D6/TIC5VS

43 PD7/D7/TIC5WS

46 PD8/D8/TIOC3AS

47 PD9/D9/TIOC3CS

48 PD10/D10/TIOC3BS

49 PD11/D11/TIOC3DS

50 PD12/D12/TIOC4AS

51 PD13/D13/TIOC4BS

52 PD14/D14/TIOC4CS

53 PD15/D15/TIOC4DS

57 PD16/IRQ0/CS3/AUDATA0 *

58 PD17/IRQ1/POE5/SCK3/CS2/AUDATA1 *

59 PD18/IRQ2/POE6/TXD3/CS1/AUDATA2 *

60 PD19/IRQ3/POE7/RXD3/CS0/AUDATA3 *

61 PD20/IRQ4/TIC5WS/SCK4/POE8

62 PD21/IRQ5/TIC5VS/TXD4

63 PD22/IRQ6/TIC5US/RXD4/AUDSYNC *

64 PD24/DREQ0/TIOC4DS/AUDCK *

67 PD25/TIOC4CS/DREQ1

68 PD26/TIOC4BS/DACK1

69 PD27/TIOC4AS/DACK0

70 PD28/TIOC3DS

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

z

EEPROM

EEPROM

z z

z z

z z

z z

z z

z z

z z

z z

z z

z z

z z

z z

z z

z z

z z

z z

z

z

LED

z

LED

z

IRQ1 SW

z

z

z

z

z

Functional Overview

2.5 I/O Ports

Remarks

Rev.1.04 2008.7.10

REJ10J1564-0104

2-9

Page 26

2

Functional Overview

2.5 I/O Ports

SH7285 Extension Connector

No Pin Name J8 J9 J10 J11 J12

71 PD29/TIOC3BS

72 PD30/TIOC3CS/IRQOUT

73 PD31/TIOC3AS/ADTRG

76 PA15/CK

77 PA14/RD

78 PA13/WRL/DQMLL

79 PA12/WRH/DQMLU/POE8

80 PA9/TCLKD/RXD3/CKE

81 PA8/TCLKC/TXD3/RDWR

82 PA7/TCLKB/SCK3/CASL

83 PA6/TCLKA/RASL

87 PB9/USPND

93 PB10

102 PE0/TIOC0A/TIOC4AS/DREQ0

103 PE1/TIOC0B/TIOC4BS/TEND0

104 PE2/TIOC0C/TIOC4CS/DREQ1

105 PE3/TIOC0D/TIOC4DS/TEND1

106 PE4/TIOC1A/RXD3

107 PE5/TIOC1B/TIOC3BS/TXD3

108 PE6/TIOC2A/TIOC3DS/SCK3

111 PB11/RXD2/CS6/CS2/CS0/IRQ0

112 PB12/TXD2/CS7/CS3/CS1/IRQ1

118 PF0/AN0

119 PF1/AN1

120 PF2/AN2

121 PF3/AN3

122 PF4/AN4

123 PF5/AN5

124 PF6/AN6

125 PF7/AN7

131 PA0/RXD0/CS0/TDI J1,J2,J3,J13

132 PA1/TXD0/CS1/TDO J1,J2,J3,J13

133 PA2/SCK0/SCS/CS2/TCK *

134 PA3/RXD1/SSI/CS3/TMS *

135 PA4/TXD1/SSO/CS4/TRST *

136 PA5/SCK1/SSCK/CS5

137 PE7/TIOC2B/RXD2/BS/UBCTRG

139 PE8/TIOC3A/SCK2

140 PE10/TIOC3C/TXD2

141 PE9/TIOC3B/FRAME

142 PE11/TIOC3D

143 PE12/TIOC4A

144 PE13/TIOC4B/MRES

z

z

z

z

z

z

z

z

z z

z

z

Pin for analog input

z

Pin for analog input

z

Pin for analog input

z

Pin for analog input

z

Pin for analog input

z

Pin for analog input

z

Pin for analog input

z

Pin for analog input

z

z

z

z

z

z

z

z

DIP switch for user

DIP switch for user

DIP switch for user

DIP switch for user

z

z

z z

z

z

z

z

z

z

LED

z

LED

z

LED

z

LED

Remarks

Note *: Connected only when the 0Ω resistance is mounted.

Rev.1.04 2008.7.10

REJ10J1564-0104

2-10

Page 27

Functional Overview

2

2.6 Power Supply Module

2.6 Power Supply Module

In M3A-HS85, 5V power is input to the board and 3.3V is generated by using a regulator. The regulator used is

output voltage variable type and given voltage value can be generated by changing the resistance value.

5V power can be supplied from DC stabilized power supply (via power supply connector (J4)) and AC adapter (via

DC power supply jack (J7)).

SH7285 system power supply (VCC) can be switched to 3.3V/5V by setting 3V/5V select jumper (JP1)(Initially it is

set to 5V). When VCC is switched, please note the points shown as follows.

• When 5V is set in the state that SRAM or SDRAM is mounted, the voltage that exceeds the maximum rating is

supplied from the address line, data line, and control line to SDRAM or SRAM, and devices could be destroyed. Thus,

using like this must be avoided.

(3.3V is supplied to 3V system device such as SRAM and SDRAM even when 5V is set.)

By setting jumpers, system power (VSS), A/D power (AVCC), AVREF power, and USB power (DrVCC) of SH7285

can be individually supplied from external power supply.

Figure 2.6.1 shows the block diagram of M3A-HS85 power supply circuit.

Extension connector

AVCC

DC5V

input

J4

Power

connector

J7

DC power jack

Power switch

5VCC

5VCC

5VCC

5VCC

5V

3.3V

3VCC

J8 connector

JP4

J8 connector

JP5

3.3V/5V select

jumper (JP1)

1

2

3

JP

VCC

SRAM

AVREF

External

power supply

JP2

JP3

SDRAM

VCC_CPU

External

power supply

SH7285

AVCC

AVREF

VCC

DrVCC

(USB power supply)

Rev.1.04 2008.7.10

REJ10J1564-0104

Extension connector

It is not initially mounted.

Mountable only for 3.3V operation

Figure 2.6.1 Block Diagram of Power Supply Circuit

2-11

Page 28

Functional Overview

2

2.7 USB Interface

2.7 USB Interface

The M3A-HS85 contains a USB connector (Standard-B receptacle).

When a cable is connected to USB host/hub in the state that this CPU board is not turned on, the voltage is

impressed from USB host/hub to VBUS. Thus, the CPU board should be turned on before USB cable is connected.

When you want to delay a notification of connection to USB host/hub (the cases such as in the processing of high

priority or initialization), it can be controlled by PB10. The powered state is kept regardless of the states USD+ and

USD- when pin VBUS of SH7285 is set to low level.

Figure 2.7.1 shows the block diagram of M3A-HS85 USB interface.

Oscillator (48MH z )

3.3V

Ceralock

CSTCZ48M0X12R

(Murata)

:Not mounted

SH7285

DrVCC

DrVSS

USBEXTAL

USBXTAL

Figure 2.7.1 Block Diagram of USB Interface

PB10

VBUS

HD74LV1GT08ACME-E

USB

series B

connector

Vbus

3.3V

HD74LV1GT126ACME-E

OE

USD+

USD-

D+

D-

GND

Vbus PB10 VBUS D+ Remarks

0 0 0 Hi-Z Initial value

0 1 0 Hi-Z

1 0 0 Hi-Z

1 1 1 Pull-up When USB is connected

Rev.1.04 2008.7.10

REJ10J1564-0104

2-12

Page 29

Functional Overview

2

2.8 Clock Module

2.8 Clock Module

The clock module in the M3A-HS85 consists of the following two blocks:

•

Output from a oscillator connected to EXTAL of the SH7285

•

Ceramic resonator connected to EXTAL and XTAL

The M3A-HS85 has a 12.5MHz ceramic oscillator connected to it as standard specification. (The oscillator is

mounted via 8-pin IC socket.)

When the ceramic resonator is used, R7 should be removed.

Figure 2.8.1 shows the block diagram of clock module.

Oscillator

CLK

R7

*1

0

EXTAL

XTAL

SH7285

PA15/CK

Extension connector

SDRAM(U3)_CLK pin

Ceramic resonator

12.5MHz

*1: To mount the ceramic resonator, R7 should be removed.

: Not mounted component

Figure 2.8.1 Block Diagram of Clock Module

*1

Rev.1.04 2008.7.10

REJ10J1564-0104

2-13

Page 30

2

2.9 Reset Module

This circuit controls the reset signal of SH7285 mounted on the M3A-HS85.

Figure 2.9.1 shows the block diagram of reset module in the M3A-HS85.

Functional Overview

2.9 Reset Module

Figure 2.9.1 Block Diagram of Reset Module

2.10 Interrupt Switches

In the M3A-HS85, the push switches are connected with the pins NMI and IRQ1 of SH7285.

Figure 2.10.1 shows the block diagram of interrupt switch.

Rev.1.04 2008.7.10

REJ10J1564-0104

Figure 2.10.1 Block Diagram of Interrupt Switch

2-14

Page 31

2

2.11 E10A-USB Interface

The M3A-HS85 has the H-UDI connectors (J1 and J2) to connect with E10A-USB.

____________________

ASEBRKAK

M3A-HS85 is connected to E10A-USB, SW4-1 should be set to

When it is connected to E10A-USB in the state that SW4-1 is set to

Figure 2.11.1 shows the block diagram of E10A-USB interface.

________________

/ASEBRK

/FWE pin of SH7285 is connected to DIP switch for system setting (SW4-1). When the

“OFF” after FWE switch jumper (JP6) is set to “1-2”.

“ON”, it cannot be normally debugged.

Functional Overview

2.11 E10A-USB Interface

Rev.1.04 2008.7.10

REJ10J1564-0104

Figure 2.11.1 Block Diagram of E10A-USB Interface

2-15

Page 32

2

Functional Overview

2.11 E10A-USB Interface

*This is a blank page*

Rev.1.04 2008.7.10

REJ10J1564-0104

2-16

Page 33

Chapter3Operational Specifications

Chapter3

Operational Specifications

3-1

Page 34

3

3.1 M3A-HS85 Connectors Outline

Figure 3.1.1 shows the M3A-HS85 connector assignments.

<Top View of the Component Side >

Operational Specifications

3.1 M3A-HS85 Connectors Outline

< Top View of the Solder Side >

Figure 3.1.1 M3A-HS85 Connector Assignments

Rev.1.04 2008.7.10

REJ10J1564-0104

3-2

Page 35

Operational Specifications

3

3.1.1 H-UDI Connector (J1, J2)

The M3A-HS85 includes a 36-pin H-UDI (J1) connector and 14-pin H-UDI (J2) connector for a connection to the

E10A-USB emulator.

Figure 3.1.2 shows the pin assignments of H-UDI (J1) connector.

35

36

Board

edge

Board

edge

35

36

Figure 3.1.2 Pin Assignments of H-UDI (J1) Connector

Table 3.1.1 lists pin assignments of H-UDI connector (J1).

Table 3.1.1 Pin Assignments of H-UDI (J1) Connector

Pin Signal Name Pin Signal Name

1

2

1

2

3.1.1 H-UDI Connector (J1, J2)

Top view of the

component side

Side view

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

AUDCK

GND

AUDATA0

GND

AUDATA1

GND

AUDATA2

GND

AUDATA3

GND

________________

AUDSYNC

GND

NC

GND

NC

GND

TCK

GND

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

TMS

GND

_________

TRST

(GND)

TDI

GND

TDO

GND

___________________

ASEBRKAK

GND

UVCC

GND

_______

RES

GND

GND

GND

NC

GND

______________

/ASEBRK

Rev.1.04 2008.7.10

3-3

REJ10J1564-0104

Page 36

3

Figure 3.1.3 shows the pin assignments of H-UDI (J2) connector.

714613512411310291

Board

edge

Board

edge

[Note] Please note that the assignments of pin numbe r by Ren esas is different

from the assignments of pin number by the manufacturing company of con nector.

Figure 3.1.3 Pin Assignments of H-UDI (J2) Connector

Table 3.1.2 lists the pin assignments of H-UDI (J2) connector.

J2

Operational Specifications

3.1.1 H-UDI Connector (J1, J2)

8

Top view of the

component side

Side view

Table 3.1.2 Pin Assignments of H-UDI (J2) Connector

Pin Signal Name Pin Signal Name

1

TCK

_________

2

TRST

3

TDO

___________________

4

ASEBRKAK

5

TMS

6

TDI

_______

7

RES

______________

/ASEBRK

8

9

10

11

12

13

14

NC

(GND)

GND

UVCC

GND

GND

GND

Rev.1.04 2008.7.10

REJ10J1564-0104

3-4

Page 37

3

3.1.2 Serial Port Connector (J3)

The M3A-HS85 contains a serial port connector (J3).

Figure 3.1.4 shows the pin assignments of serial port connector.

Operational Specifications

3.1.2 Serial Port Connector (J3)

5

9

Board

edge

5

9

Board

edge

Figure 3.1.4 Pin Assignments of Serial Port Connector (J3)

Table 3.1.3 lists the pin assignments of serial port connector.

Table 3.1.3 Pin Assignments of Serial Port Connector (J3)

Pin Signal Name Pin Signal Name

1 NC 6 DSR

2 RXD 7 RTS

3 TXD 8 CTS

_______

4 DTR

5 GND

9 NC

1

6

Top view of the

component side

1

6

Side view

_______

_______

_______

Pins 4-6 and Pins 7-8 are loop back connected.

Rev.1.04 2008.7.10

3-5

REJ10J1564-0104

Page 38

3

3.1.3 Power Supply Connector (J4)

The M3A-HS85 includes a connector for power supply.

Figure 3.1.5 shows the pin assignments of power supply connector.

12

Board

edge

12

Board

edge

Figure 3.1.5 Pin Assignments of Power Supply Connector (J4)

Operational Specifications

3.1.3 Power Supply Connector (J4)

Top view of the

component side

Side view

Table 3.1.4 lists the pin assignments of power supply connector for M3A-HS85.

Table 3.1.4 Pin Assignments of Power Supply Connector (J4)

Pin Signal Name Pin Signal Name

1 +5V 2 GND

Rev.1.04 2008.7.10

REJ10J1564-0104

3-6

Page 39

Operational Specifications

3

3.1.4 External Power Supply Connector for SH7285 (J5, J6)

The M3A-HS85 contains a connector pin for external power supply to be supplied to the power for CPU and USB.

When the power is supplied by using this connector, remove the post heads of the external power switch jumpers

(JP2 and JP3) to be in the released state.

Figure 3.1.6 shows the pin assignments of power supply connector.

Top view of the

component side

3.1.4 External Power Supply Connector for SH7285 (J5, J6)

J6

1

DrVCC

2

Board

edge

J5

12

VCC-CPU

Figure 3.1.6 Pin Assignments of Power Supply Connector (J5, J6)

Table 3.1.5 lists the pin assignment of power supply connector (J5) for SH7285.

Table 3.1.5 Pin Assignments of Power Supply Connector for SH7285 (J5)

Pin Signal Name Pin Signal Name

1 VCC-CPU 2 GND

Table 3.1.6 lists the pin assignments of power supply connector (J6) for SH7285.

Table 3.1.6 Pin Assignments of Power Supply Connector for SH7285 (J6)

Pin Signal Name Pin Signal Name

1 DrVCC 2 GND

Rev.1.04 2008.7.10

REJ10J1564-0104

3-7

Page 40

Operational Specifications

3

3.1.5 DC Power Jack (J7)

A DC power jack can be mounted on the M3A-HS85. Figure 3.1.7 shows the pin assignments of DC power jack,

and Table 3.1.7 lists the pin assignments of DC power jack (J7).

Top view of the

solder side

2

1

3

J7

3.1.5 DC Power Jack (J7)

Board

edge

Figure 3.1.7 Pin Assignments of DC Power Jack (J7)

Table 3.1.7 Pin Assignments of DC Power Jack (J7)

Pin Signal Name

+5V

1

GND

2

GND

3

Rev.1.04 2008.7.10

REJ10J1564-0104

3-8

Page 41

Operational Specifications

3

3.1.6 Extension Connectors (J8-J12)

The M3A-HS85 includes the through-hole for mounting extension connectors to which the I/O pins of the SH7285

are connected.

MIL standard connectors can be connected to J8-J12, allowing users to connect with extension boards or monitor

the SH7285 bus signals.

Figure 3.1.8 shows the pin assignments of extension connector.

Board edge

40

39

19 20

20

19

J11

J10

2

1

3.1.6 Extension Connectors (J8-J12)

2

1

J12

Top view of the

solder side

Board edge

J8

J11

J8

2

1

J9

2

1

40

39

20

19

J10

20

19

40

39

1920

12

J12

J9

20

19

40

39

2

1

2

1

12

2

1

2

1

[Note]:The pin numbers on CPU board are defined base d on t he assumption that extension

connectors are installed in the component side. Thus, the assignments of pin number on the

extension connector side and the CPU board side are different when extension connectors

are installed in the solder side.

Figure 3.1.8 Pin Assignments of Extension Connectors

Board edge

Top view of the

component side

Board edge

Rev.1.04 2008.7.10

3-9

REJ10J1564-0104

Page 42

3

Table 3.1.8 lists the pin assignments of extension connector (J8).

Table 3.1.8 Pin Assignments of Extension Connectors (J8)

Pin Signal Name

1 AVCC 2 AVCC 3 AVREF 4 PF0/AN0 5 PF1/AN1 6 PF2/AN2 7 PF3/AN3 8 PF4/AN4 -

9 PF5/AN5 10 PF6/AN6 11 PF7/AN7 12 AVREFVSS 13 PE6/TIOC2A/TIOC3DS/SCK3 Extension Connector (J9)

14 AVSS 15 AVSS 16 NC 17 NC 18 NC 19 NC 20 GND -

Operational Specifications

3.1.6 Extension Connectors (J8-J12)

Other Connections

Rev.1.04 2008.7.10

REJ10J1564-0104

3-10

Page 43

3

Table 3.1.9 lists the pin assignments of extension connectors (J9).

Table 3.1.9 Pin Assignments of Extension Connectors (J9)

Pin Signal Name

1 5VCC 2 5VCC 3 WDTOVF# 4 PE6/TIOC2A/TIOC3DS/SCK3 Extension Connector (J8)

5 PE5/TIOC1B/TIOC3BS/TXD3 Serial Port Connector (J3) *When JP7 is ”2-3”

6 PE4/TIOC1A/RXD3 Serial Port Connector (J3) *When JP8 is ”2-3”

7 PE3/TIOC0D/TIOC4DS/TEND1 DIP Switch for User (SW3)

8 PE2/TIOC0C/TIOC4CS/DREQ1 DIP Switch for User (SW3)

9 PB8/A20/WAIT/POE8/IRQ7/SCK0 SRAM (U2)*

10 PB7/A19/BREQ/POE4/IRQ6/TXD0 SRAM (U2)*

11 PB6/A18/BACK/POE3/IRQ5/RXD0 SRAM (U2)*

12 PB1/A17/REFOUT/ADTRG/IRQ4 SRAM (U2)*

13 PB0/A16/IRQ3 SRAM (U2)*

14 PC15/A15/IRQ2 SRAM (U2)*

15 PC14/A14/IRQ1 SRAM (U2)*, SDRAM (U3)*

16 PC13/A13/IRQ0 SRAM (U2)*, SDRAM (U3)*

17 PC12/A12 SRAM (U2)*, SDRAM (U3)*

18 PC11/A11 SRAM (U2)*, SDRAM (U3)*

19 PC10/A10 SRAM (U2)*, SDRAM (U3)*

20 GND 21

PE1/TIOC0B/TIOC4BS/TEND0 DIP Switch for User (SW3)

22

PE0/TIOC0A/TIOC4AS/DREQ0 DIP Switch for User (SW3)

23

PA15/CK SDRAM (U3)*

24

PC9/A9 SRAM (U2)*

25

PC8/A8 SRAM (U2)*

26

PC7/A7 SRAM (U2)*

27

PC6/A6 SRAM (U2)*

28

PC5/A5 SRAM (U2)*

29

PC4/A4 SRAM (U2)*

30

PC3/A3 SRAM (U2)*

31

PC2/A2 SRAM (U2)*

32

PC1/A1 SRAM (U2)*

33

PC0/A0/POE0 -

34

PB11/RXD2/CS6#/CS2#/CS0#/IRQ0 SRAM (U2)*

35

PA5/SCK1/SSCK/CS5# -

36

PD20/IRQ4/TIC5WS/SCK4/POE8 -

37

PD21/IRQ5/TIC5VS/TXD4 -

38

PD30/TIOC3CS/IRQOUT -

39

RESET# Reset Module

40

GND -

Note *: Only when SRAM and SDRAM are mounted.

Operational Specifications

3.1.6 Extension Connectors (J8-J12)

Other Connections

,

SDRAM (U3)*

,

SDRAM (U3)*

,

SDRAM (U3)*

,

SDRAM (U3)*

,

SDRAM (U3)*

,

SDRAM (U3)*

,

SDRAM (U3)*

,

SDRAM (U3)*

,

SDRAM (U3)*

Rev.1.04 2008.7.10

3-11

REJ10J1564-0104

Page 44

3

Table 3.1.10 lists the pin assignments of extension connectors(J10).

Table 3.1.10 Pin Assignments of Extension Connectors (J10)

Pi Signal Name

1

PB3/SDA/POE2/IRQ1 EEPROM (U4)

2

PB2/SCL/POE1/IRQ0 EEPROM (U4)

3

PB12/TXD2/CS7#/CS3#/CS1#/IRQ1 SDRAM (U3)*

4

PA8/TCLKC/TXD3/RDWR# SRAM (U2)*, SDRAM (U3)*

5

PA13/WRL/DQMLL SRAM (U2)*, SDRAM (U3)*

6

PA12/WRH/DQMLU/POE8 SRAM (U2)*, SDRAM (U3)*

7

PD31/TIOC3AS/ADTRG -

8

NC (PA4/TXD1/SSO/CS4#/TRST when R93 is mounted) - (H-UDI connector (J1,J2) when R93 is mounted)

9

PA9/TCLKD/RXD3/CKE SDRAM (U3)*

10

PA6/TCLKA/RASL# SDRAM (U3)*

11

PA7/TCLKB/SCK3/CASL# SDRAM (U3)*

12

NC (PA2/SCK0/SCS/CS2#/TCK when R94 is mounted) - (H-UDI connector (J1,J2) when R94 is mounted)

13

NC (PA3/RXD1/SSI/CS3#/TMS when R95 is mounted) - (H-UDI connector (J1,J2) when R95 is mounted)

14

NC (PD16/IRQ0/CS3#/AUDATA0 when R96 is mounted) - (H-UDI connector (J1) when R96 is mounted)

NC

15

(PD17/IRQ1/POE5/SCK3/CS2#/AUDATA1 when R97 is mounted)

NC

16

(PD18/IRQ2/POE6/TXD3/CS1#/AUDATA2 when R98 is mounted)

NC

17

(PD19/IRQ3/POE7/RXD3/CS0#/AUDATA3 when R99 is mounted)

18

NC (PD22/IRQ6/TIC5US/RXD4/AUDSYNC when R100 is mounted) - (H-UDI connector (J1) when R100 is mounted)

19

NC (PD24/DREQ0/TIOC4DS/AUDCK when R101 is mounted) - (H-UDI connector (J1) when R101 is mounted)

20

GND

Note *: Only when SRAM and SDRAM are mounted.

Operational Specifications

3.1.6 Extension Connectors (J8-J12)

Other Connections

- (H-UDI connector (J1) when R97 is mounted)

- (H-UDI connector (J1) when R98 is mounted)

- (H-UDI connector (J1) when R99 is mounted)

Rev.1.04 2008.7.10

3-12

REJ10J1564-0104

Page 45

Operational Specifications

3

Table 3.1.11 lists the pin assignments of extension connectors (J11).

Table 3.1.11 Pin Assignments of Extension Connectors (J11)

Pin Signal Name

1 PD28/TIOC3DS -

2 PD29/TIOC3BS -

3 PA14/RD# SRAM (U2)*, Extension Connector (J12)

4 PD15/D15/TIOC4DS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

5 PD14/D14/TIOC4CS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

6 PD13/D13/TIOC4BS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

7 PD12/D12/TIOC4AS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

8 PD11/D11/TIOC3DS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

9 PD10/D10/TIOC3BS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

10 PD9/D9/TIOC3CS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

11 PD8/D8/TIOC3AS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

12 PD7/D7/TIC5WS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

13 PD6/D6/TIC5VS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

14 PD5/D5/TIC5US SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

15 PD4/D4/TIC5W SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

16 PD3/D3/TIC5V SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

17 PD2/D2/TIC5U SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

18 PD1/D1 SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

19 PD0/D0 SRAM (U2)*, SDRAM (U3)*, Extension Connector (J12)

20 GND -

Note *: Only when SRAM and SDRAM are mounted.

3.1.6 Extension Connectors (J8-J12)

Other Connections

Rev.1.04 2008.7.10

REJ10J1564-0104

3-13

Page 46

3

Table 3.1.12 lists the pin assignments of the extension connectors (J12).

Table 3.1.12 Pin Assignments of the Extension Connectors (J12)

Pin Signal Name

3VCC -

1

3VCC -

2

PA21/TIC5U/RASU/POE8/IRQ3/RASL -

3

PA22/TIC5V/CASU/POE4/IRQ2/CASL -

4

PA23/TIC5W/POE0/IRQ1/AH/CKE IRQ1 SW (SW6)

5

PB9/USPND -

6

PB10 USB module

7

PD25/TIOC4CS/DREQ1 -

8

PD26/TIOC4BS/DACK1 -

9

PD27/TIOC4AS/DACK0 -

10

PE7/TIOC2B/RXD2/BS/UBCTRG -

11

PE8/TIOC3A/SCK2 -

12

PE9/TIOC3B/FRAME User LED

13

PE10/TIOC3C/TXD2 -

14

PE11/TIOC3D User LED

15

PE12/TIOC4A User LED

16

PE13/TIOC4B/MRES# User LED

17

PE14/DACK0/TIOC4C/AH User LED

18

PE15/DACK1/TIOC4D/IRQOUT User LED

19

GND

20

NC -

21

NC -

22

PA14/RD# SRAM (U2)*, Extension Connector (J11)

23

PD15/D15/TIOC4DS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

24

PD14/D14/TIOC4CS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

25

PD13/D13/TIOC4BS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

26

PD12/D12/TIOC4AS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

27

PD11/D11/TIOC3DS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

28

PD10/D10/TIOC3BS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

29

PD9/D9/TIOC3CS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

30

PD8/D8/TIOC3AS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

31

PD7/D7/TIC5WS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

32

PD6/D6/TIC5VS SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

33

PD5/D5/TIC5US SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

34

PD4/D4/TIC5W SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

35

PD3/D3/TIC5V SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

36

PD2/D2/TIC5U SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

37

PD1/D1 SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

38

PD0/D0 SRAM (U2)*, SDRAM (U3)*, Extension Connector (J11)

39

GND

40

Note *: Only when SRAM and SDRAM are mounted.

-

-

Operational Specifications

3.1.6 Extension Connectors (J8-J12)

Other Connections

Rev.1.04 2008.7.10

3-14

REJ10J1564-0104

Page 47

Operational Specifications

3

3.1.7 Extension Connector (J13)

J13 is the one having installed it for the examination when this board is developed. Please do not use it.

Top view of the

component side

131411129107856341

Board

edge

Figure 3.1.9 Pin Assignments of the Extension Connectors (J13)

Connector mounting hole

2

J13

3.1.7 Extension Connector (J13)

Rev.1.04 2008.7.10

REJ10J1564-0104

3-15

Page 48

Operational Specifications

3

3.1.8 USB Connector (J14)

The M3A-HS85 has a connector for USB (series B plug).

Figure 3.1.10 shows the pin assignments of USB connector (J14), and Table 3.1.13 lists the pin assignments of

USB connector (J14).

Top view of the

component side

Board

edge

Side view

2

3

2

1

4

1

3.1.8 USB Connector (J14)

Board

edge

Figure 3.1.10 Pin Assignments of USB Connector (J14)

Table 3.1.13 Pin Assignments of USB Connector (J14)

Pin Signal Name

Vbus

1

D-

2

D+

3

GND

4

43

Rev.1.04 2008.7.10

REJ10J1564-0104

3-16

Page 49

Operational Specifications

3

3.1.9 GND Connector (J15)

The M3A-HS85 has a connector for GND. This is because GND such as measuring instruments can be easily

connected when debugging.

Figure 3.1.11 shows the pin assignments of GND connector (J15). Table 3.1.14 lists the pin assignments of GND

connector (J15).

Top view of the

component side

13

GND

J15

Board

edge

Figure 3.1.11 Pin Assignments of GND Connector (J15)

3.1.9 GND Connector (J15)

Table 3.1.14 Pin Assignments of GND Connector (J15)

Pin Signal Name

GND

1

GND

2

GND

3

Rev.1.04 2008.7.10

REJ10J1564-0104

3-17

Page 50

3

3.2 Outline of Switches and LEDs

The M3A-HS85 includes switches and LEDs as its operational components.

Figure 3.2.1 shows the M3A-HS85 operational component assignment.

<Top View of the Component Side >

Operational Specifications

3.2 Outline of Switches and LEDs

Figure 3.2.1 M3A-H85 Operational Component Assignment

Rev.1.04 2008.7.10

REJ10J1564-0104

3-18

Page 51

Operational Specifications

3

3.2.1 CPU Power Supply Select Jumpers (JP1)

The power voltage supplied to SH7285 can be switched to 3.3V supply or 5V supply by setting JP1.

The power voltage which can be switched in this jumper is only SH7285 (U1). The supply voltages for the

components such as external memories are not changed.

Figure 3.2.2 shows the pin assignments of select jumper for CPU power supply. Table 3.2.1 lists the pin

assignments of jumper for CPU power supply select jumper for CPU power supply.

Top view of the

component side

Board

edge

13

5V

3.3V

JP1 PWRSEL

3.2.1 CPU Power Supply Select Jumpers (JP1)

Jumper Setting Function

JP1

PWRSEL

: Initial Setting

Note: Do not change jumper settings during the operation of M3A-HS85. Ensure to turn off the power for the

M3A-HS85 before changing jumper settings.

Board

edge

Figure 3.2.2 Pin Assignments of Select Jumper for CPU Power Supply (JP1)

Table 3.2.1 Pin Assignments of Select Jumper for CPU Power Supply (JP1)

1-2

2-3

5V voltage is supplied to CPU

3.3V voltage is supplied to CPU

Rev.1.04 2008.7.10

REJ10J1564-0104

3-19

Page 52

Operational Specifications

3

3.2.2 External Power Supply Select Jumper (JP2, JP3, JP4, JP5)

By setting JP2 to JP5, the source of power voltage supplying to A/D reference power supply (AVREF), analog

power supply (AVCC), USB power supply (DrVCC), and system power supply of SH7285 can be switched.

Figure 3.2.3 shows the external power supply select jumper assignments. Table 3.2.2 lists the external power

supply select jumper setting.

Top view of the

component side

3.2.2 External Power Supply Select Jumper (JP2, JP3, JP4, JP5)

Jumper Setting Function

JP2

CPU-VCC SEL

JP3

DrVCC SEL

JP4

AVCCSEL

JP5

AVREFSEL

: Initial Setting

DrVCC SEL

JP3

FIX INT

AVCC SEL

FIX AVCC

2

1

JP4

12

AVREF SEL

2

FIX AVREF

1

JP5

CPU-VCC SEL

JP2

FIX INT

12

Figure 3.2.3 External Power Supply Select Jumper Assignments (JP2,JP3,JP4,JP5)

Table 3.2.2 External Power Supply Select Jumper Setting (JP2,JP3,JP4,JP5)

1-2

SH7285 power supply voltage (VCC) is supplied from J4 or J7

Open External power supply voltage (supplied from J5 or H13)

1-2

SH7285 USB power supply (DrVCC) is supplied from J4 or J7 (via regulator)

Open External power supply voltage (supplied from J6 or H14)

1-2

SH7285 AVCC is connected to 5V fixed power supply voltage.

Open External power supply voltage (supplied from J8 or H8)

1-2

SH7285 AVREF is connected to 5V fixed power supply voltage.

Open External power supply voltage (supplied from J8 or H9)

Note: Do not change jumper settings during the operation of M3A-HS85.

Ensure to turn off the power for the M3A-HS85 before changing jumper settings.

Rev.1.04 2008.7.10

3-20

REJ10J1564-0104

Page 53

Operational Specifications

3

3.2.3 FWE Pin Select Jumper (JP6)

By setting JP6, pin FWE/

connector, or the extension connector (J13). This jumper should be set only when you want the pin FWE/

________________

ASEBRK

to be controlled via the extension (J13).

Figure 3.2.4 shows FWE pin select jumper assignment. Table 3.2.3 lists jumper setting for selecting FWE pin.

_____________________

ASEBRKAK

________________

/ASEBRK

Top view of the

component side

of SH7285 can be switched if it is connected to SW4-3 and H-UDI

1

FWESEL

INT

Board

edge

E8a

3

JP6

3.2.3 FWE Pin Select Jumper (JP6)

_____________________

ASEBRKAK

/

Board

edge

Figure 3.2.4 FWE Pin Select Jumper (JP6) Assignment

Table 3.2.3 FWE Select Jumper Setting (JP6)

Jumper Setting Function

JP6

FWESEL

_____________________

1-2

Pin FWE/ASEBRKAK

connector (J1 and J2).

2-3 Pin FWE/ASEBRKAK

_____________________

________________

/ASEBRK

________________

/ASEBRK

of SH7285 is connected to SW4-3 and the H-UDI

of SH7285 is connected to the extension connector (J13).

: Initial Setting

Note: Do not change jumper settings during the operation of M3A-HS85.

Ensure to turn off the power for the M3A-HS85 before changing jumper settings.

Rev.1.04 2008.7.10

3-21

REJ10J1564-0104

Page 54

Operational Specifications

3

3.2.4 Serial Port Select Jumper (JP7, JP8)

SCI channel of SH7285 connecting to the serial port connector (J3) is changed by the setting of JP7 and JP8.

SCIF channel 3 is connected to the serial port connector (J3) as the initial setting. When SCI channel 0 is

connected to the serial port connector (J3), note that H-UDI connectors (J1 and J2) and the extension connector

(J13) cannot be used.

Figure 3.2.5 shows the serial port select jumper assignments. Table 3.2.4 lists the serial port select jumper setting.

Top view of the

component side

JP7

JP8

SEL

TXD

RXD

3

3

TXD0

1

TXD3

1

3.2.4 Serial Port Select Jumper (JP7, JP8)

Board

edge

SEL

RXD0

RXD3

Jumper Setting Function

JP7

TXDSEL

RXD SEL

: Initial Setting

Note: Do not change jumper settings during the operation of M3A-HS85.

Board

edge

Figure 3.2.5 Serial Port Select Jumper Assignments (JP7, JP8)

Table 3.2.4 Serial Port Select Jumper Setting (JP7, JP8)

1-2

2-3 Pin PA1/TXD0 of SH7285 is connected to

1-2 Pin PE4/RXD3 of SH7285 is connected to

2-3 Pin PA0/RXD0 of SH7285 is connected to

Pin PE5/TXD3 of SH7285 is connected to the serial port connector (J3).

serial port connector (J3).

the

serial port connector (J3). JP8

the

serial port connector (J3).

the

Ensure to turn off the power for the M3A-HS85 before changing jumper settings.

Rev.1.04 2008.7.10

3-22

REJ10J1564-0104

Page 55

Operational Specifications

3

3.2.5 Switch and LED Functions

The M3A-HS85 includes six switches and seven LEDs.

Table 3.2.5 lists switches mounted on M3A-HS85.

Table 3.2.5 Switches Mounted on M3A-HS85

No. Function Remarks

SW1 System power on/off switch SW2 System reset input switch See section 2.9 for details.

SW3 DIP switch for user (4-pole)

SW3-1 OFF : PE0=”H” ON : PE0=”L”

SW3-2 OFF : PE1=”H” ON : PE1=”L”

SW3-3 OFF : PE2=”H” ON : PE2=”L”

SW3-4 OFF : PE3=”H” ON : PE3=”L”

SW4 System setup DIP switch (4-pole) See Table 3.2.6 for the functions

SW5 NMI input switch See section 2.10 for details.

SW6 IRQ1 input switch See section 2.10 for details.

Table 3.2.6 lists the functions of switch SW4. The operation mode of SH7285 is set by the combination of the pins

FWE, MD0, and MD1. Table 3.2.7 lists the SH7285 operating mode setting.

FWE pin is multiplexed with the

to

“OFF”.

_______________

ASEBRK

___________________

/ASEBRKAK

signal. When E10A-USB is used, SW4-1(FWE) must be set

Table 3.2.6 Functions of Switch SW4

No. Setting Function

OFF FWE="H" (Releasing the writing/erasing protects of on-chip flash memory) SW4-1

FWE

MD1

MD0

TP

ON FWE="L" (Setting the writing erasing protects of on-chip flash memory)

OFF MD1 pin state "H" SW4-2

ON MD1 pin state "L"

OFF MD0 pin state "H" SW4-3

ON MD0 pin state "L"

OFF H1=”H” SW4-4

ON H1=”L”