Page 1

To our customers,

Old Company Name in Catalogs and Other Documents

On April 1st, 2010, NEC Electronics Corporation merged with Renesas Technology

Corporation, and Renesas Electronics Corporation took over all the business of both

companies. Therefore, although the old company name remains in this document, it is a valid

Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1

Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

st

, 2010

Send any inquiries to http://www.renesas.com/inquiry

.

Page 2

Notice

1. All information included in this document is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please

confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to

additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of

semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software,

and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by

you or third parties arising from the use of these circuits, software, or information.

5. When exporting the products or technology described in this document, you should comply with the applicable export control

laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas

Electronics products or the technology described in this document for any purpose relating to military applications or use by

the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and

technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited

under any applicable domestic or foreign laws or regulations.

6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics

does not warrant that such informatio n is error free. Renesas Electronics assumes no liability whatsoever for any damages

incurred by you resulting from errors in or omissions from the information included herein.

7. Renesas Electronics products are classified according to the following three quality grades: “Standard”, “High Quality”, and

“Specific”. The recommended applications for each Renesas Electronics product depends on the product’s quality grade, as

indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular

application. You may not use any Renesas Electronics product for any application categorized as “Specific” without the prior

written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for

which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way

liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an

application categorized as “Specific” or for which the product is not intended where you have failed to obtain the prior written

consent of Renesas Electronics. The quality grade of each Renesas Electronics product is “Standard” unless otherwise

expressly specified in a Ren esas E lectronics data sheets or dat a books, etc.

“Standard”: Computers; office equipment; communications equipment; test and measurement equipment; audio and visual

equipment; home electron ic appliances; machine tools; personal electronic equipment; and industrial robots.

“High Quality”: Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-

crime systems; safety equipment; and medical equipment not specifically designed for life support.

“Specific”: Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or

systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare

intervention (e.g. excision, etc.), and any other appl i cations or purposes that pose a d irect threat to human life.

8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics,

especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation

characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or

damages arising out of the use of Renesas Electronics products beyond such specified ranges.

9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have

specific characteristics such as t he occu rrence o f failure at a certai n rate an d malfunct io ns under cert ain u se con dition s. Further,

Renesas Electronics prod ucts are not subject to radiation resistance design. Please be sure to implement safety measures to

guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a

Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire

control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because

the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system

manufactured by you.

10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental

compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable

laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS

Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with

applicable laws and regulations.

11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas

Electronics.

12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this

document or Renesas Electronics products, or if you have any other inquiries.

(Note 1) “Renesas Electronics” as used in this document means Renesas Electronics Corporation an d also includes its majority-

owned subsidiaries.

(Note 2) “Renesas Electronics product(s)” means any product developed or manufactured by or for Renesas Electronics.

Page 3

User’s Manual

SH7619 CPU Board

M3A-HS19

User’s Manual

Renesas 32-Bit RISC Microcomputers

SuperH™ RISC engine Family/SH7619 Group

Rev.1.01 2008.10

Page 4

Notes regarding these materials

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate

Renesas products for their use. Renesas neither makes warranties or representations with respect to the

accuracy or completeness of the information contained in this document nor grants any license to any

intellectual property rights or any other rights of Renesas or any third party with respect to the information in

this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising

out of the use of any information in this document, including, but not limited to, product data, diagrams, charts,

programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military

applications such as the development of weapons of mass destruction or for the purpose of any other military

use. When exporting the products or technology described herein, you should follow the applicable export

control laws and regulations, and procedures required by such laws and regulations.

4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and

application circuit examples, is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas products listed in this

document, please confirm the latest product information with a Renesas sales office. Also, please pay regular

and careful attention to additional and different information to be disclosed by Renesas such as that disclosed

through our website. (http://www.renesas.com )

5. Renesas has used reasonable care in compiling the information included in this document, but Renesas

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information

included in this document.

6. When using or otherwise relying on the information in this document, you should evaluate the information in

light of the total system before deciding about the applicability of such information to the intended application.

Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any

particular application and specifically disclaims any liability arising out of the application and use of the

information in this document or Renesas products.

7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas

products are not designed, manufactured or tested for applications or otherwise in systems the failure or

malfunction of which may cause a direct threat to human life or create a risk of human injury or which require

especially high quality and reliability such as safety systems, or equipment or systems for transportation and

traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication

transmission. If you are considering the use of our products for such purposes, please contact a Renesas

sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

(1) artificial life support devices or systems

(2) surgical implantations

(3) healthcare intervention (e.g., excision, administration of medication, etc.)

(4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who

elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas

Technology Corp., its affiliated companies and their officers, directors, and employees against any and all

damages arising out of such applications.

9. You should use the products described herein within the range specified by Renesas, especially with respect

to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation

characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or

damages arising out of the use of Renesas products beyond such specified ranges.

10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific

characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use

conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and

injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for

hardware and software including but not limited to redundancy, fire control and malfunction prevention,

appropriate treatment for aging degradation or any other applicable measures. Among others, since the

evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or

system manufactured by you.

11. In case Renesas products listed in this document are detached from the products to which the Renesas

products are attached or affixed, the risk of accident such as swallowing by infants and small children is very

high. You should implement safety measures so that Renesas products may not be easily detached from your

products. Renesas shall have no liability for damages arising out of such detachment.

12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written

approval from Renesas.

13. Please contact a Renesas sales office if you have any questions regarding the information contained in this

document, Renesas semiconductor products, or if you have any other inquiries.

Page 5

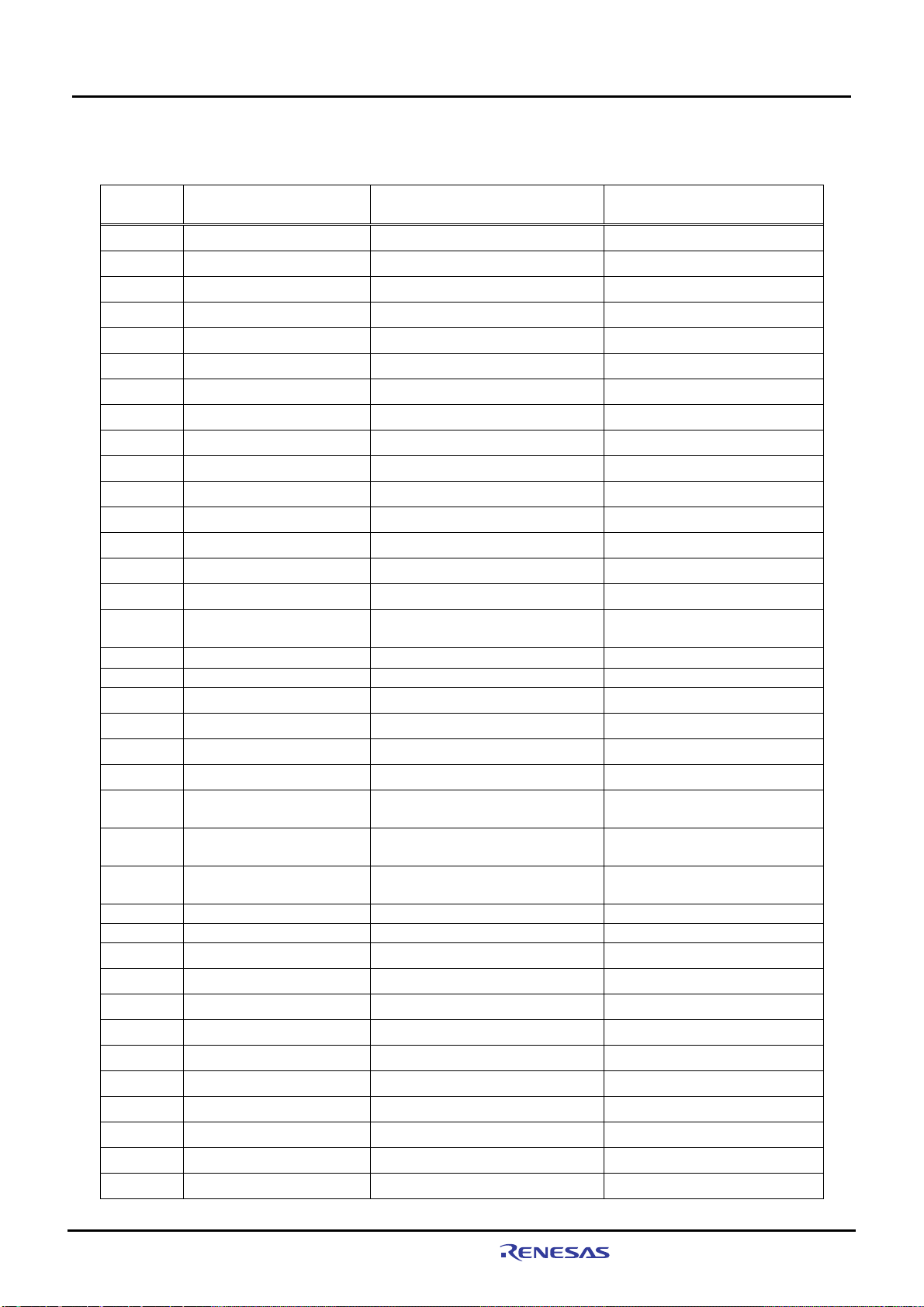

Table of Contents

Chapter1 Overview..............................................................................................................................1-1

1.1 Overview .................................................................................................................................................................... 1-2

1.2 Configuration.............................................................................................................................................................. 1-2

1.3 External Specifications...............................................................................................................................................1-3

1.4 Appearance................................................................................................................................................................ 1-4

1.5 M3A-HS19 Block Diagrams........................................................................................................................................ 1-5

1.6 M3A-HS19 Board Overview ....................................................................................................................................... 1-6

1.7 M3A-HS19 Memory Mapping.....................................................................................................................................1-9

1.8 Absolute Maximum Ratings...................................................................................................................................... 1-10

1.9 Recommended Operating Conditions ......................................................................................................................1-10

Chapter2 Features and Specifications.................................................................................................2-1

2.1 Features.....................................................................................................................................................................2-2

2.2 CPU............................................................................................................................................................................ 2-3

2.2.1 SH7619.............................................................................................................................................................2-3

2.3 Memory ......................................................................................................................................................................2-4

2.3.1 SH7619 U Memory and Cache Memory ........................................................................................................... 2-4

2.3.2 Flash Memory S29GL032A90TFIR4 (Standard component)............................................................................. 2-4

2.3.3 External Synchronous DRAM (SDRAM)...........................................................................................................2-6

2.3.4 External EEPROM .......................................................................................................................................... 2-11

2.4 Serial Port Interface.................................................................................................................................................. 2-13

2.5 PCMCIA Card Interface............................................................................................................................................ 2-14

2.6 LAN Port Interface.................................................................................................................................................... 2-15

2.7 I/O Port..................................................................................................................................................................... 2-16

2.8 Power Supply Circuit................................................................................................................................................ 2-19

2.9 Clock Module............................................................................................................................................................ 2-20

2.10 Reset Module.........................................................................................................................................................2-21

2.11 Interrupt Switch ...................................................................................................................................................... 2-22

2.12 E10A-USB Interface...............................................................................................................................................2-23

Chapter3 Operational Specifications...................................................................................................3-1

3.1 M3A-HS19 Connectors...............................................................................................................................................3-2

3.1.1 UART Connector Pin (J1).................................................................................................................................. 3-3

3.1.2 UART Connector (J2)........................................................................................................................................ 3-4

3.1.3 RS-422 Connector Pin (J3)...............................................................................................................................3-5

3.1.4 PCMCIA Connector (J4)....................................................................................................................................3-6

3.1.5 LAN Connector (J5) .......................................................................................................................................... 3-8

3.1.6 H-UDI Connector (J6) ....................................................................................................................................... 3-9

3.1.7 Power Supply Connector (J7) ......................................................................................................................... 3-10

3.1.8 External Power Supply Connector (J8)...........................................................................................................3-11

3.1.9 Expansion Connectors (J9-J13).................................................................. 3-12

3.2 Switches and LEDs ..................................................................................................................................................3-15

3.2.1 Jumpers (JP1 - JP9) ....................................................................................................................................... 3-16

Rev. 1.01 Oct 28, 2008

REJ10J1351-0101

(i)

Page 6

3.2.2 Features of Switches and LEDs...................................................................................................................... 3-18

3.3 Dimensions...............................................................................................................................................................3-20

Appendix..............................................................................................................................................A-1

M3A-HS19 SCHEMATICS

Rev. 1.01 Oct 28, 2008

REJ10J1351-0101

(ii)

Page 7

Chapter1 Overview

Chapter1

Overview

1-1

Page 8

1

1.1 Overview

1.1 Overview

The M3A-HS19 is a CPU board designed to evaluate the feature and performance of the SH7619 Group of Renesas Technology

original MCU, as well as developing and evaluating the application software for the MCUs.

SH7619 data bus, address bus and on-chip peripheral pins are all connected to expansion connectors and appropriate connectors

to allow for the timing evaluation with peripherals using measurement instruments, and the development of the optional boards

according to its application. Furthermore, it can be connected with an RS-232C connector and a LAN connector, and a PC card

can be mounted on the board.

Renesas Technology E10A-USB on-chip emulator can also be connected to the M3A-HS19.

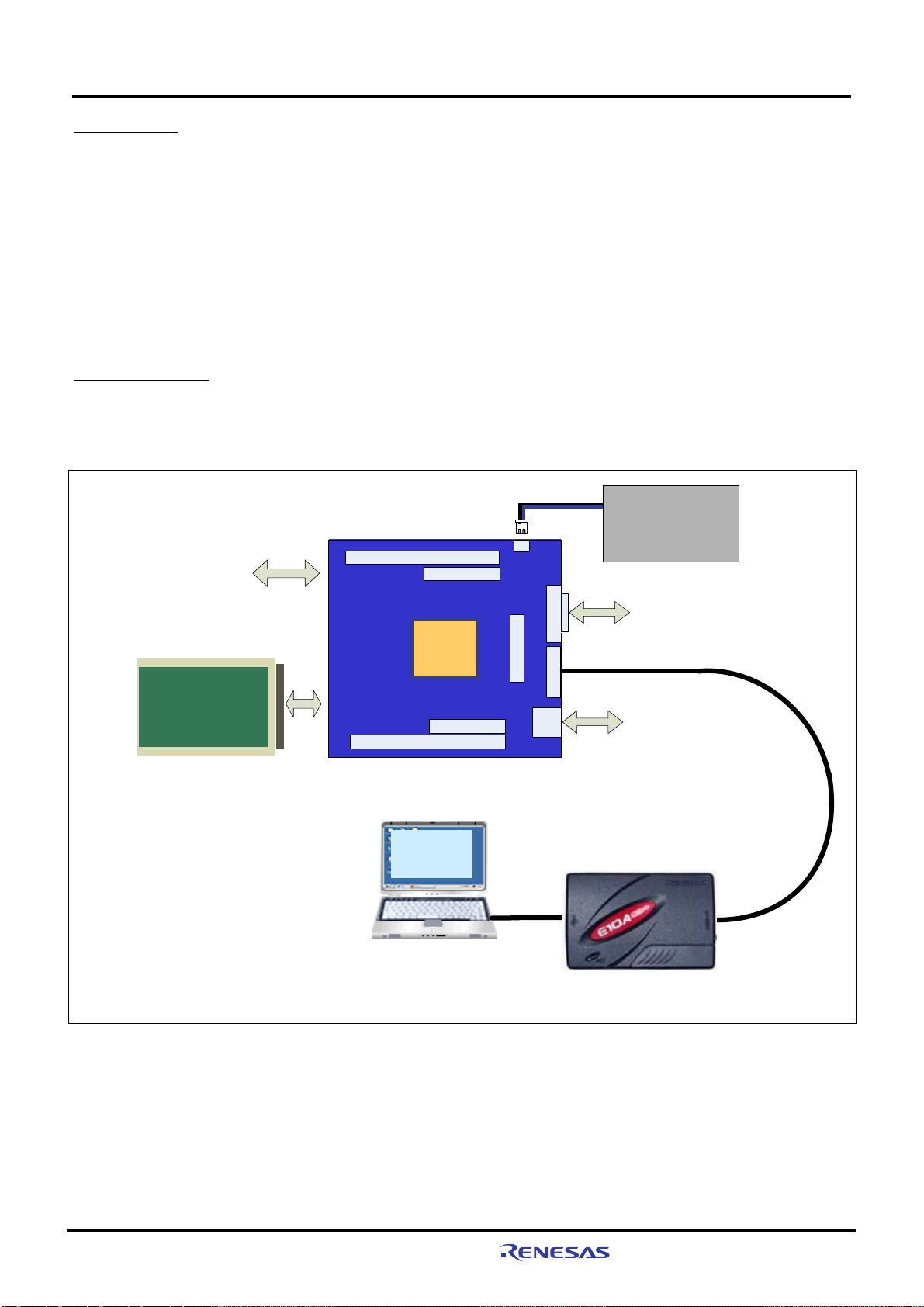

1.2 Configuration

Figure 1.2.1 shows an example of system configuration using the M3A-HS19.

Overview

PC card*

High-performance

Embedded Workshop

SuperHRISC engine

C/C++ CompilerPackage

*

Expansion

connector

PCMCIA

connector

*

SH7619 CPU board

M3A-HS19

SH7619

Debugger

Host computer*

USB

5V DC output

regulated PS

(1.5A min.)

Serial port connector

H-UDI connector

LAN port connector

E10A-U SB

*

These items should be prepared by user.

*

Figure 1.2.1 M3A-HS19 System Configuration

Rev.1.01 Oct 28, 2008 1-2

REJ10J1351-0101

Page 9

1

1.3 External Specifications

Table 1.3.1 lists external specifications.

Table 1.3.1 External Specifications

No. Items Description

1 CPU SH7619

1.3 External Specification

• Input (XIN) clock: 15.625 MHz

• Bus clock: 62.5 MHz at maximum

• CPU clock: 125 MHz at maximum

2 Memories • SDRAM (16-bit data bus)

• EDS1216AATA-75E: 1 (16 MB)

• Flash memory (16-bit data bus)

• S29GL032A90TFIR4: 1 (4 MB)

• EEPROM (Serial)

• S93C76AFT-V-G: 1 (8 KB, 512 x 16)

3 Connectors • Expansion Connector (Bus, I/O, VCC, GND: 140 pins in total: Through-hole)

• Channel 1 serial port connector (2-pin: Through-hole)

• Channel 2 serial port connector (D-sub 9-pin)

• RS-422 serial connector (4-pin: Through-hole)

• RJ-45 LAN connector (8-pin, RJ-45)

• PC card connector (68-pin)

• H-UDI connector (14-pin)

• Power connector (2-pin: 5 V)

• External power connector (2-pin: 1.8 V: Through-hole)

4 LEDs • Power LED: 1

• User LEDs: 4

5 Switches • Power switch: 1

• Reset push-button switch: 1

• NMI push-button switch: 1

• IRQ0 push-button switch: 1

• User DIP switches: 4/package

• Mode DIP switches: 4/package

• 1.8 V external switch jumper: 1

• PCMCIA power switch jumper: 1

• PCMCIA bus switch enable jumper: 1

• Expansion connector signal select jumpers: 5

6 Dimensions • Dimensions: 100 mm x 100 mm

• Mounting form:6 layers, double-sided

• Board configuration:1 board

Overview

Rev.1.01 Oct 28, 2008 1-3

REJ10J1351-0101

Page 10

1

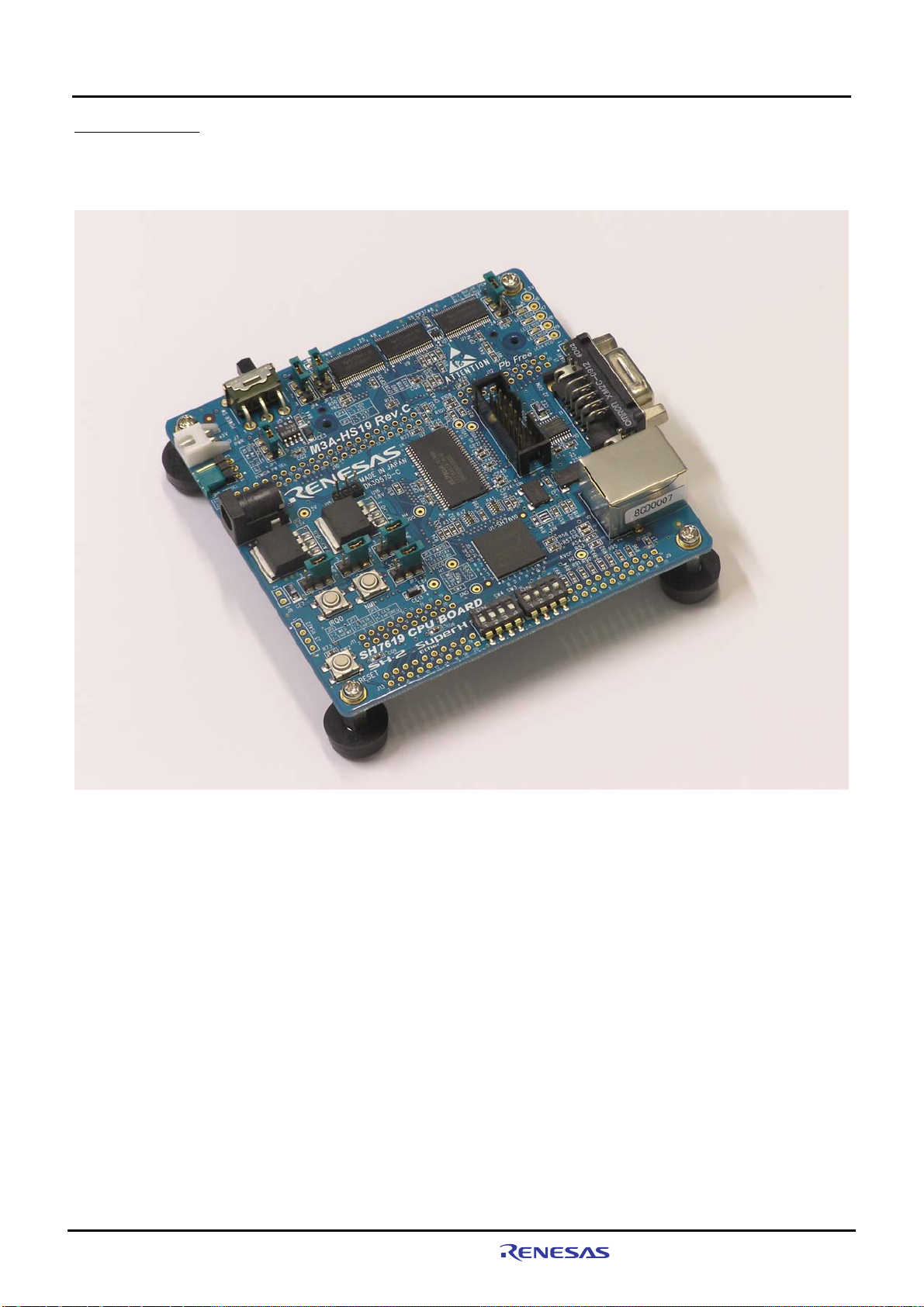

1.4 Appearance

Figure 1.4.1 shows the appearance of the M3A-HS19.

Overview

1.4

Figure 1.4.1 M3A-HS19 Appearance

Rev.1.01 Oct 28, 2008 1-4

REJ10J1351-0101

Page 11

1

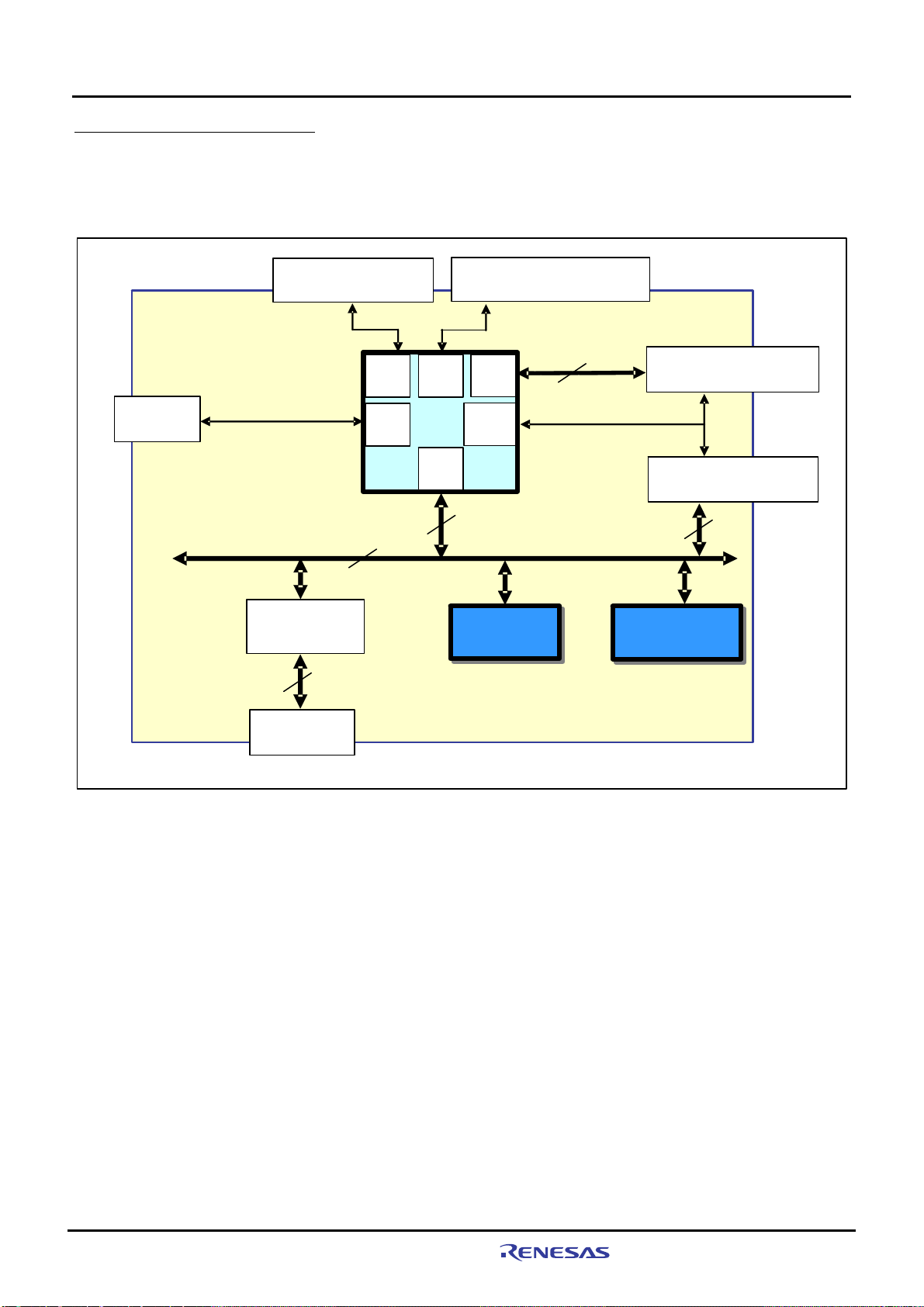

1.5 M3A-HS19 Block Diagrams

Figure 1.5.1 shows the system block diagram.

Overview

1.5 M3A-HS19 Block Diagram

LAN

connector

H-UDI (14-pin)

Bus switch

PCMCIA

connector

H-UDI

EtherC

16-bit

Serial port connector

(RS-232C x 2, RS-422 x 1)

SCIF

/SCI

SH7619

BSC

HIF

GPIO/

Other

Peripheral

Functions

16-bit

SDRAM

SDRAM

(16MB)

(16MB)

SH7619 CPU Board

16-bit

16-bit

Flash Memory

M3A-HS19

Expansion connector

(HIF bus)

Expansion connector

(CPU bus)

(4MB)

(4MB)

Figure 1.5.1 System Block Diagram

Rev.1.01 Oct 28, 2008 1-5

REJ10J1351-0101

Page 12

1

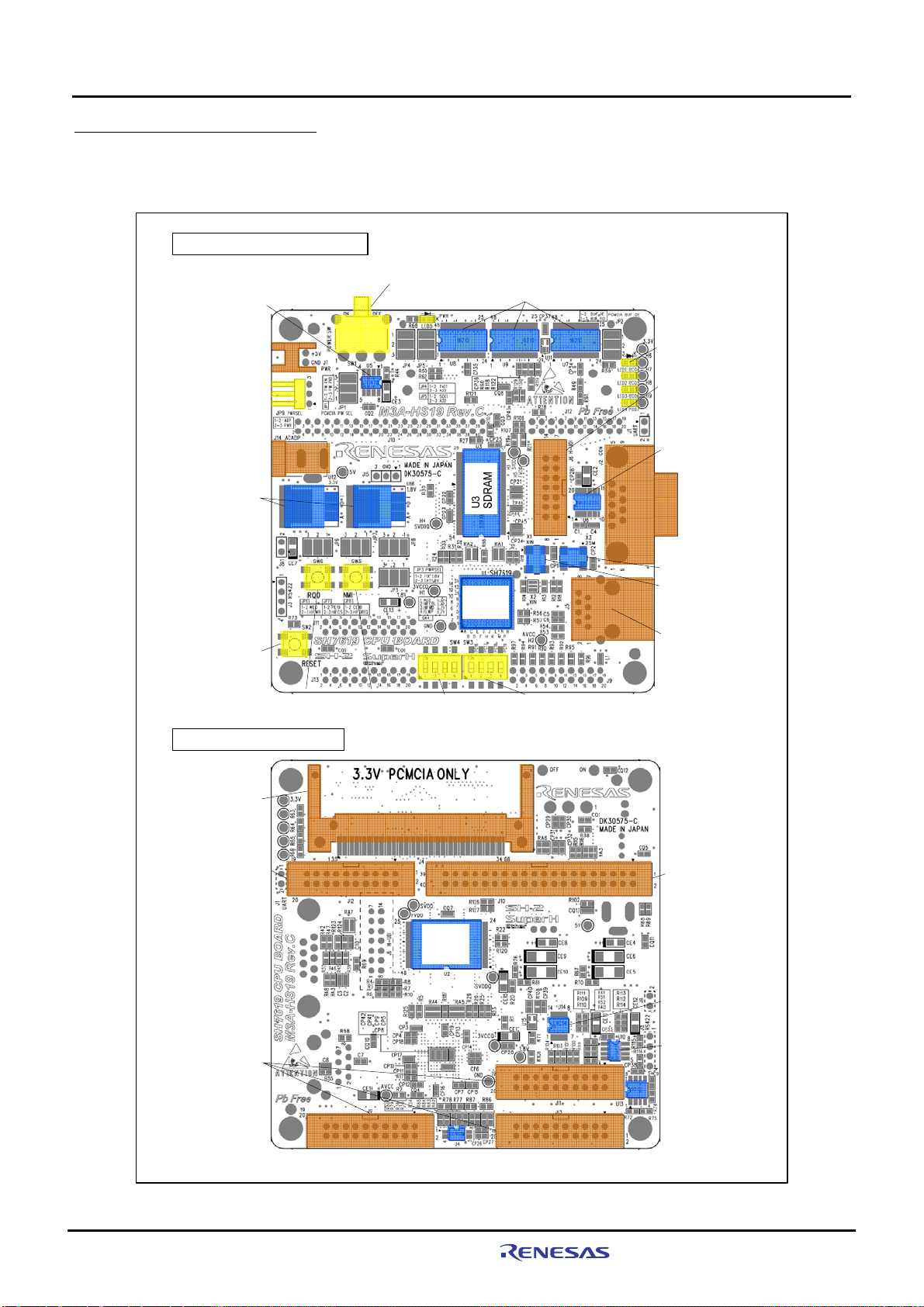

1.6 M3A-HS19 Board Overview

Figure 1.6.1 shows the M3A-HS19 board overview.

Top view of the component side

U5

PCMCIA

power control IC

J7

Power connector

JP9

Power switching

jumper

J14

AC adaptor jack

SW1

Power switch

LED5

Power LED

U7,U8,U9

Bus switch

Overview

1.6 M3A-HS19 Board Overview

LED1-4

User LED

J6

H-UDI connector

(14-pin)

U6

RS-232C

driver

U12, U16

3.3V/1.8V

regulator IC

SW2

Reset switch

SW6

IRQ0 switch

Top view of the solder side

J4

PC card

connector

(68-pin)

J12

Expansion

connector

SW5

NMI switch

SW4

Mode DIP

switch

U2

Flash

memory

U1

SH7619

SW3

User DIP switch

J2

RS-232C

serial connector

X3

25MHz oscillator

X1

15.625MHz oscillator

J5

RJ-45

LAN connector

J10

Extension

connector

U14

Logic IC

U10

J9, J11, J13

Expansion connector

U4

EEPROM

RS-422

driver

U13

Reset IC

Figure 1.6.1 M3A-HS19 Board External View

Rev.1.01 Oct 28, 2008 1-6

REJ10J1351-0101

Page 13

1

Table 1.6.1 lists major compo nents mounted on the M3A-HS19

Table 1.6.1 Major Components

Part

Number

U1 CPU R4S76190W125BGV (Renesas)

U2 Flash memory S29GL032A90TFIR4 (Spansion)

U3 SDRAM EDS1216AATA-75E (Elpida)

U4 EEPROM S93C76AFT-V-G (SII)

U5 PCMCIA power con trol IC LTC1470CS8#PBF (Linear)

U6 RS-232C driver SP3222ECY (Sipex)

U7,U8,U9 Bus switch SN74CBTLV16210GR (TI)

U10 RS-422 driver SP3077EEN-L (Sipex)

U11,U15 Logic IC TC7S08FU (TOSHIBA)

U12,U16 Regulator IC LMS1587CSX-ADJ (NS)

U13 Reset IC M51957BFP

U14 Logic IC SN74LVC14APWR (TI)

X1

X2

X3

J1

J2

J3 RS-422 serial connector

J4 PC card connector ICM-C68H-S112-400R1 (J.S.T.)

J5 RJ-45 LAN connector TLA-6T718 (TDK)

J6 H-UDI connector 7614-6002

J7 Power supply connector S2B-XH-A (J.S.T.)

J8

J9,J11-J13 Expansion connector

J10 Expansion connector

J14 AC adapter jack

J15 3-pin connector

JP1-8 Jumper HW-3P-G (MAC8)

JP9 Jumper XG8V-0334 (OMRON)

LED1-4 User LED Yellow, SML-3 11YT (ROHM)

LED5 Power LED Blue, UB1114C (STANLEY)

SW1 Power switch MS-12AAH1 (Nikkai)

SW2 Reset switch (MRES) B3SN-3012

SW3 User DIP switch A6S-4104-H

SW4 Mode DIP switch A6S-4101-H

SW5 NMI switch B3SN-3012

SW6 IRQ0 switch B3SN-3012

Oscillator

Ceramic resonator

Oscillator

Serial port connector (Ch1)

Serial port connector (Ch2)

1.8 V External power supply

connector

Name

SG-8002JF_15.625 MHz (Epson)

SG-8002JF_25.000 MHz (Epson)

Optional

Optional

2-pin MIL standard connector

XM2C-0912-112 (OMRON)

Optional

Optional

2-pin MIL standard connector

Optional,

20-pin MIL pitch connector

Optional,

40-pin MIL pitch connector

HEC0470-01-630 (Hoshiden)

XG8V-0331 (OMRON)

Remarks

(By manufacturer)

(Renesas)

, 15.625 MH z CSTCE15M7 (Murata)

,

A2-4PA-2.54DSA

(Sumitomo 3M)

,

(OMRON)

(OMRON)

(OMRON)

(OMRON)

(OMRON)

1.6 M3A-HS19 Board Overview

Recommended Optional Parts

(By manufacturer)

A2-2PA-2.54DSA

A2-2PA-2.54DSA

(Hirose)

XG4C-2031

XG4C-4031

(OMRON)

(OMRON)

(Hirose)

(Hirose)

Overview

Rev.1.01 Oct 28, 2008 1-7

REJ10J1351-0101

Page 14

1

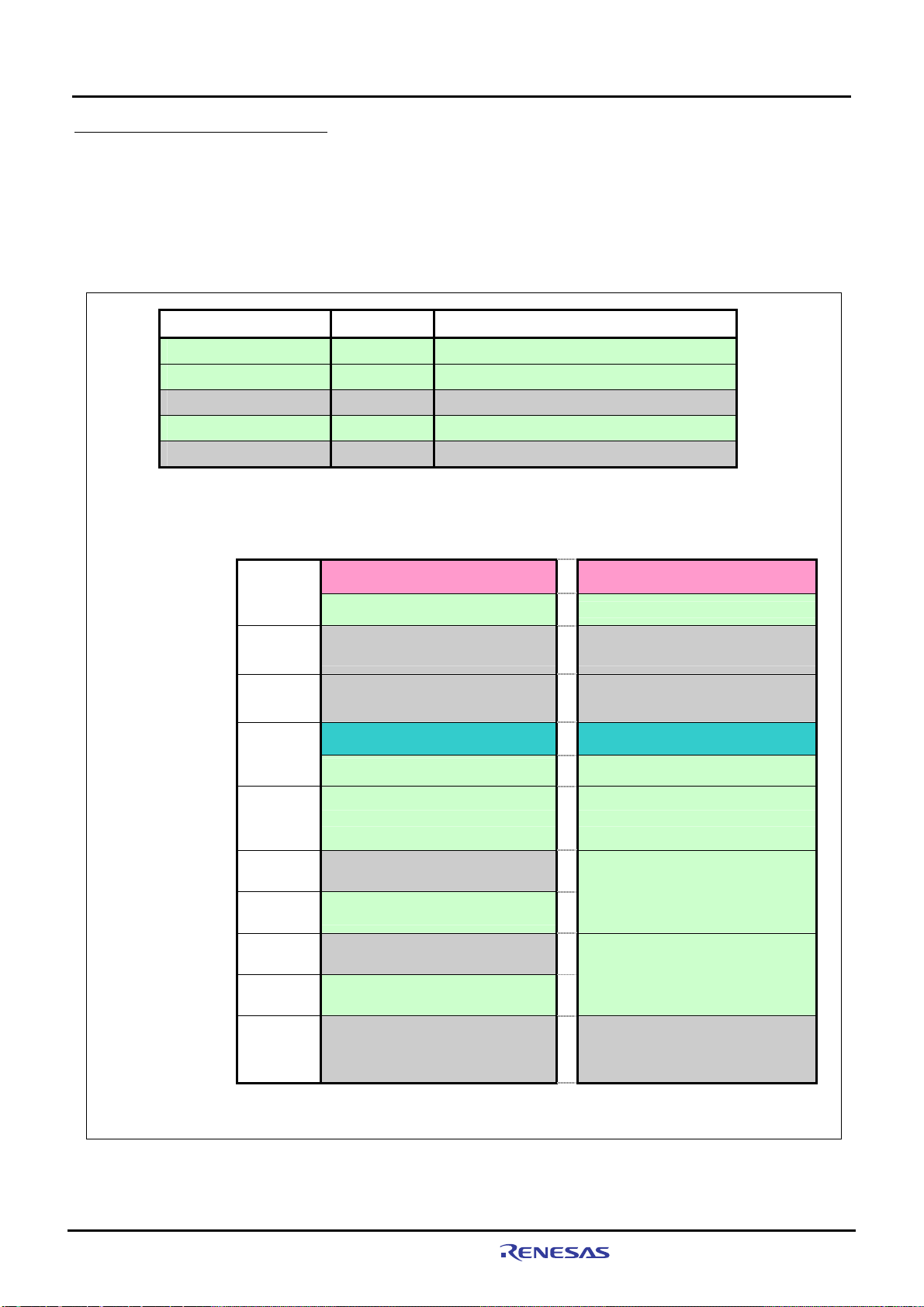

1.7 M3A-HS19 Memory Mapping

Area 0 bus width: (Default) MD3 = 0 •••16-bit

Data alignment: (SW4-1) MD5 = 0(ON) •••Big endian

MD5 = 1(OFF) •••Little endian

Figure 1.7.1 show the memory mapping examples of the SH7619 on the M3A-HS19.

Logical Address [31~29] Area Cacheable/Non-cacheable

000~011 P0 Cacheable

100~ P1 Cacheable

101~ P2 Non cacheable

110~ P3 Cacheable

111~ P4 Non-cacheable (on-chip I/O) etc.

(P0 and shadow area (P1, P2, P3))

Overview

1.7 M3A-HS19 Memory Mapping

Address [28~0] Area MAP = 0 MAP = 1

H'0000 0000

H'0400 0000

H'0800 0000

H'0C00 0000

H'1000 0000

H'1400 0000

H'1600 0000

H'1800 0000

H'1A00 0000

H'1C00 0000

H'1FFF FFFF

Area 0

64 MB

Area 1

64 MB

Area 2

64 MB

Area 3

64 MB

Area 4

64 MB

Area 5A

32 MB

Area 5B

32 MB

Area 6A

32 MB

Area 6B

32 MB

Area 7

64 MB

Flash Memory (4 MB)

H’0000 0000~H’003F FFFF

User Area

Reserved *

(Do not use)

Reserved *

(Do not use)

SDRAM (16 MB)

H’0C00 0000~H’0CFF FFFF

User Area

User Area User Area

Reserved

(Do not use)

User Area

Reserved

(Do not use)

User Area

Reserved *

(Do not use)

Flash Memory (4 MB)

H’0000 0000~H’003F FFFF

User Area

Reserved *

(Do not use)

Reserved *

(Do not use)

SDRAM (16 MB)

H’0C00 0000~H’0CFF FFFF

User Area

User Area

PCMCIA

User Area

PCMCIA

Reserved

(Do not use)

Note: H'0000 0000 to H'1FFF FFFF are the cache-enabled area.

Figure 1.7.1 SH7619 Memory Mapping Examples

Rev.1.01 Oct 28, 2008 1-8

REJ10J1351-0101

Page 15

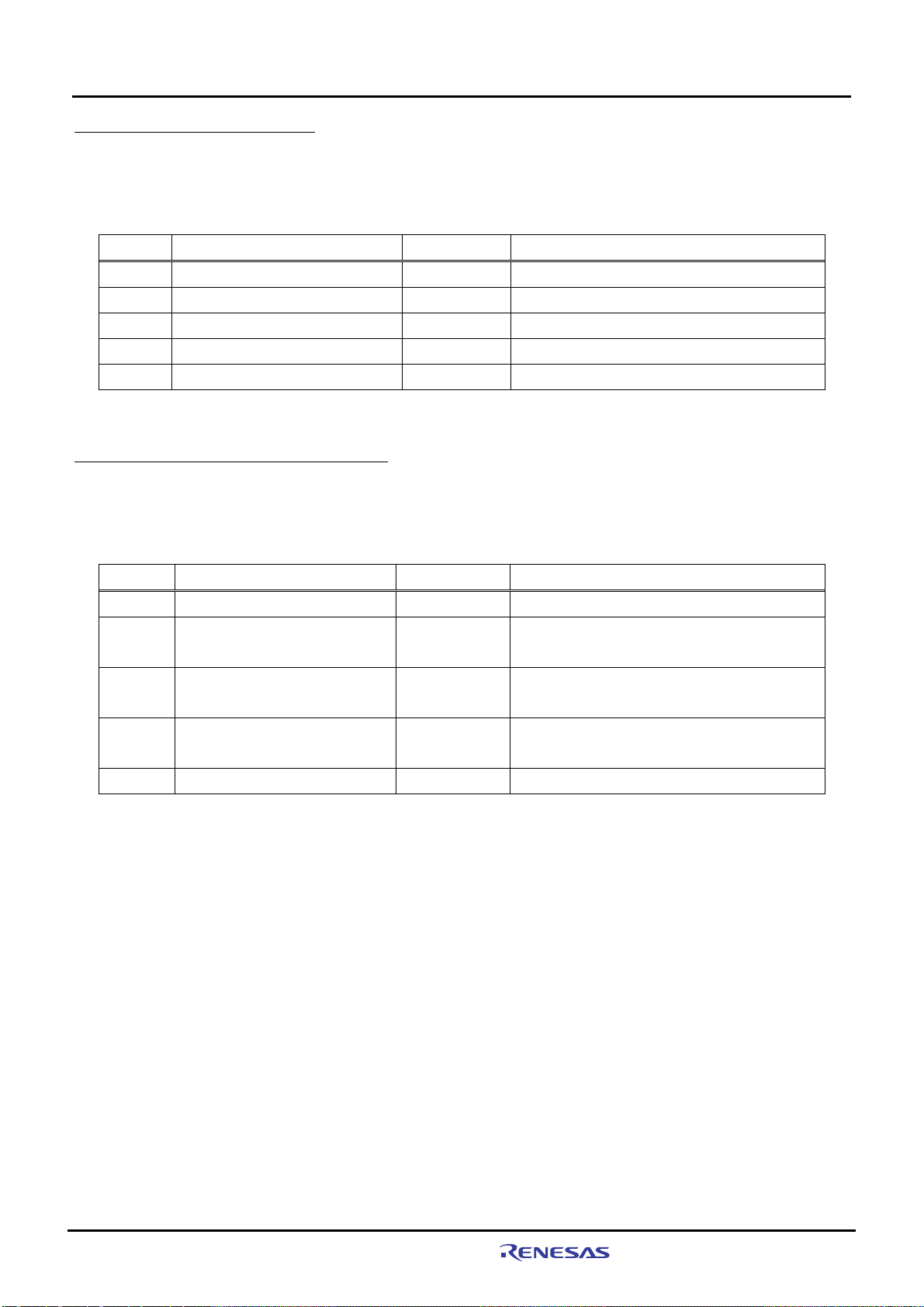

1

1.8 Absolute Maximum Ratings

1.8 Absolute Maximum Ratings

Table 1.8.1 lists the absolute maximum ratings.

Table 1.8.1 Absolute Maximum Ratings

Symbol Parameter Value Remarks

Overview

VCC

3VCC

1.8VCC 1.8 V

Topr

Tstr

Note: Temperature refers to the air temperature in the vicinity of the board.

5 V system power supply voltage

3.3 V system power supply voltage

system power supply voltage

Operating temperature

Storage temperature

-0.3 to 6.0 V

-0.3 to 3.8 V

-0.3 to 2.1 V

-5 to 55°C No condensation, no corrosion gas allowed.

-10 to 60°C No condensation, no corrosion gas allowed.

Relative to VSS

Relative to VSS

Relative to VSS

1.9 Recommended Operating Conditions

Table 1.9.1 lists the recomme nded operating conditions.

Table 1.9.1 Recommended Operating Conditions

Symbol Parameter Value Remarks

VCC

3VCC

1.8VCC

-

Topr

5 V power supply voltage

3.3 V power supply voltage

1.8 V power supply voltage

Maximum current consumption

on the board

Operating temperature 0 to 50°C

4.75 to 5.25 V

3.0 to 3.6 V

1.71 to 1.89 V

1 A max.

Relative to VSS

Relative to VSS

(Always supplied by regulator)

Relative to VSS

(Normally supplied by regulator)

No condensation, no corrosion gas allowed.

Rev.1.01 Oct 28, 2008 1-9

REJ10J1351-0101

Page 16

1

Overview

1.8 Absolute Maximum Ratings

This page intentionally left blank

Rev.1.01 Oct 28, 2008 1-10

REJ10J1351-0101

Page 17

Chapter2Features and Specifications

Chapter2

Features and Specifications

2-1

Page 18

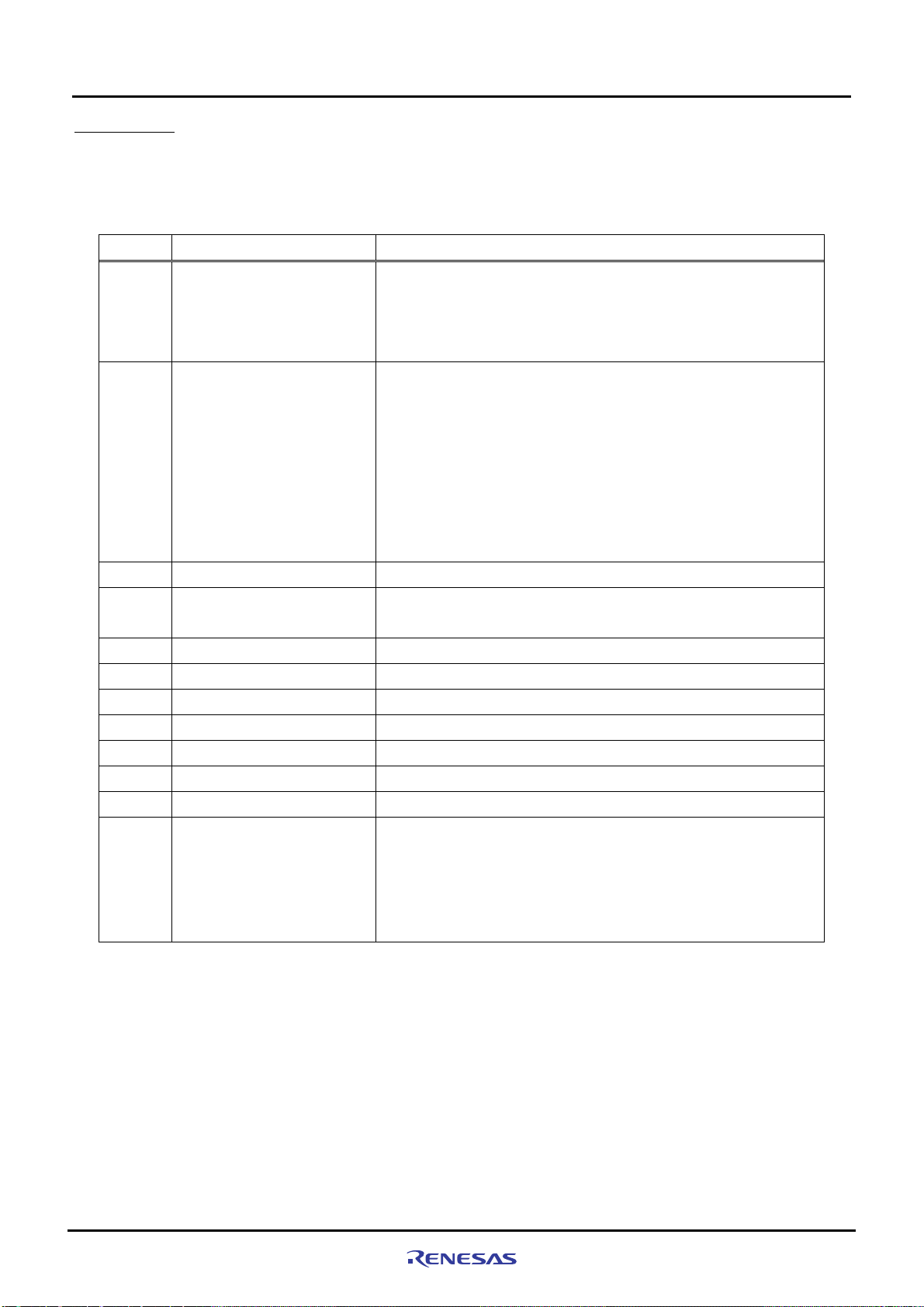

2

2.1 Features

Table 2.1.1 lists the functional modules.

Table 2.1.1 F unctional Modules

Section Features Description

Features and Specifications

2.1 Features

2.2 CPU

SH7619, clock mode 1

• Input (XIN) clock: 15.625 MHz

• Bus clock: 62.5 MHz, max.

• CPU clock: 125 MHz, max.

2.3

Memories

• U Memory (CPU)

• 16-KB memory

• Flash Memory

• S29GL032A90TFIR4: 1 (4 MB)

• SDRAM

• EDS1216AATA-75E: 1 (16 MB)

• EEPROM

• S-93C76AFT-V-G: 1 (8 KB, 512 x 16)

2.4 Serial Port Interface Connects SCIF2 of the SH7619 to a serial port connector

2.5 PCMCIA Card Interface Connects PCMCIA control signal and bus of the SH7619 to the

PCMCIA connector

2.6 LAN Port Interface Connects the SH7619 Ether I/O to an RJ-45 connector

2.7 I/O Ports Connects the SH7619 I/O port to an expansion connector

2.8 Power Supply Circuit Controls the system power supply of the M3A-HS19

2.9 Clock Module Controls the clock

2.10 Reset Module Reset control of device mounted on the M3A-HS19

2.11 Interrupt Switches Connects to the NMI pin and IRQ0 pin

2.12 E10A-USB Interface SH7619 H-UDI/AUD interface

- Operational specifications Connectors, switches, jumpers, LEDs

• Expansion connector, H-UDI connector

• PCMCIA, ETHER, RS-232C connector

• Switches and LEDs

Refer to Chapter 3 for details

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-2

Page 19

Features and Specifications

2

2.2 CPU

2.2 CPU

2.2.1 SH7619

The M3A-HS19 CPU board includes the SH7619, the 32-bit RISC MCU operates with a maximum frequency of 125 MHz.

The SH7619 is equipped with an Ethernet controller that includes an IEEE802.3u compliant Media Access Controller and

a Physical Layer Transceiver. Moreover, the SH7619 has both a 16-KB U memory (RAM) and a 16-KB instruction/data

unified cache memory. These on-chip modules enable the SH7619 to be used in a wide range of applications from data

processing to control equipments.

The M3A-HS19 can be operated at a maximum frequency of 125 MHz (external bus: 62.5 MHz, max) using a 15.625 MHz

input clock. The dedicated clock of 25.000 MHz input from CK_PHY pin is used as an on-chip PHY clock.

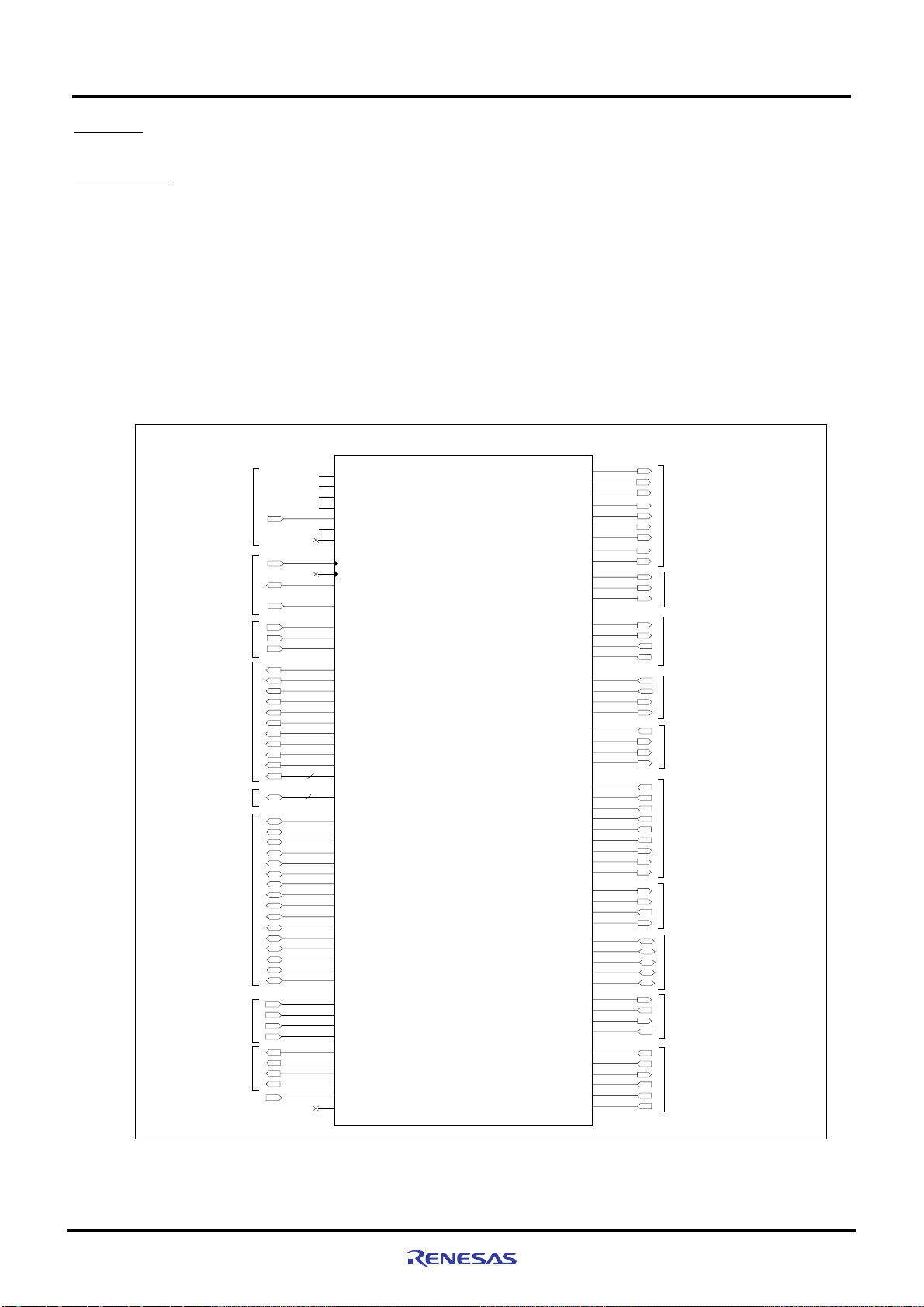

Figure 2.2.1 shows the SH7619 pin assignments.

SH7619

Mode

Clock

System

Control

CPU

Address Bus

Lower

Data Bus

HIF-D/Upper

Data bus

SW3

User port

(Ether)

LED

User port

(Ether)

Ether.ref

SW4-1

"H/L"

15.625MHz

25.000MHz

Serial Channel 0

"H"

MD0

"L"

MD1

"L"

MD2

"L"

MD3

MD5

"H"

TESTMD#

TESTOUT#

EXTAL

XTAL

CKI0

CK_PHY

RES#

NMI

PD0/IRQ0/-/TEND0

PA25/A25/SIOFSYNCO

PA24/A24/TXD_SIO0

PA23/A23/RXD_SIO0

PA22/A22/SIOMCLK0

PA21/A21/SCK_SIO0

PA20/A20

PA19/A19

PA18/A18

PA17/A17

PA16/A16

16

A15-A0

16

D15-D0

PE24/HIFD15/CTS1/D31

PE23/HIFD14/RTS1/D30

PE22/HIFD13/CTS1/D29

PE21/HIFD12/RTS0/D28

PE20/HIFD11/SCK0/D27

PE19/HIFD10/RXD0/D26

PE18/HIFD09/TXD1/D25

PE17/HIFD08/SCK0/D24

PE16/HIFD07/RXD0/D23

PE15/HIFD06/TXD0/D22

PE14/HIFD05/-/D21

PE13/HIFD04/-/D20

PE12/HIFD03/-/D19

PE11/HIFD02/-/D18

PE10/HIFD01/-/D17

PE09/HIFD00/-/D16

PC16/MDIO

PC17/MDC

PC18/LINKSTA

PC19/EXOUT

PC04/MII_TXD0/-/SPEED100#

PC05/MII_TXD1/-/LINK#

PC06/MII_TXD2/-/CRS#

PC07/MII_TXD3/-/DUPLEX#

EXRES1

TSTBUSA

PB13/BS#

RD/WR#

WE0#/DQMLL

PB05/WE2(BE2)#/DQMUL/ICIORD#

PB06/WE3(BE3)#/DQMUU/ICIOWR#

WE1#/DQMLU/WE#

PB12/CS3#

PB02/CKE

PB03/CAS#

PB04/RAS#

PB10/CS5B#/CE1A#

PB09/CE2A#

PB00/WAIT#

PB01/IOIS16#

PC00/MII_RXD0

PC01/MII_RXD1

PC02/MII_RXD2

PC03/MII_RXD3

PE08/HIFCS#

PE06/HIFWR#/SIOFSYNC0

PE02/HIFDREQ/RXD_SIO0

PE01/HIFRDY/SIOMCLK0

PE07/HIFRS

PE05/HIFRD

PE03/HIFMD

PE00/HIFEBL/SCK_SIO0

PE04/HIFINT#/TXD_SIO0

PC09/RX_ER

PC14/COL

PC15/CRS

PC20/WOL

PC08/RX_DV

PC10/RX_CLK

PC11/TX_ER

PC12/TX_EN

PC13/TX_CLK

PD2/IRQ2/TXD1/DREQ0

PD3/IRQ3/RXD1/DACK0

PD5/IRQ5/TXD2/DREQ1

PD6/IRQ6/RXD2/DACK1

ASEMD#

CS0#

TRST#

TMS

RD#

RXM

RXP

TXM

TXP

TDO

TDI

TCK

SW4-3

SW4-2

RESET#

REG#

CD#

EN#

Bus Control

(All,FLASH

SDRAM,PCMCIA)

Bus Control

(SDRAM)

Bus Control

(PCMCIA)

Ether

Interface

EEPROM

Extension

Connector

HIF

Interface

PCMCIA

Interface

Other Extension

Bus Interface

RS-422,RS-232C

Interface

H-UDI

Interface

Rev.1.01

Oct 28, .2008 2-3

REJ10J1351-0101

Figure 2.2.1 Pin Assignments by function

Page 20

Features and Specifications

2

2.3 Memory

2.3 Memory

The M3A-HS19 includes the SH7619 on-chip U memory, an external flash memory, external SDRAM and EEPROM.

Details are described below (Except the PC card).

2.3.1 SH7619 U Memory and Cache Memory

The SH7619 has a 16-KB (RAM) U memory module (address: H’E55FC000~H’E55FFFFF) and a 16-KB

instruction/data-unified cache memory.

2.3.2 Flash Memory S29GL032A90TFIR4 (Standard component)

The M3A-HS19 comes standard with a flash memory listed in Table 2.3.1 to store a user program.

The flash memory is an external bus 16-bit mode fixed and operates at 3.3 V single. The write-protection of flash memory

can be enabled or disabled by DIP switches (SW4-4).

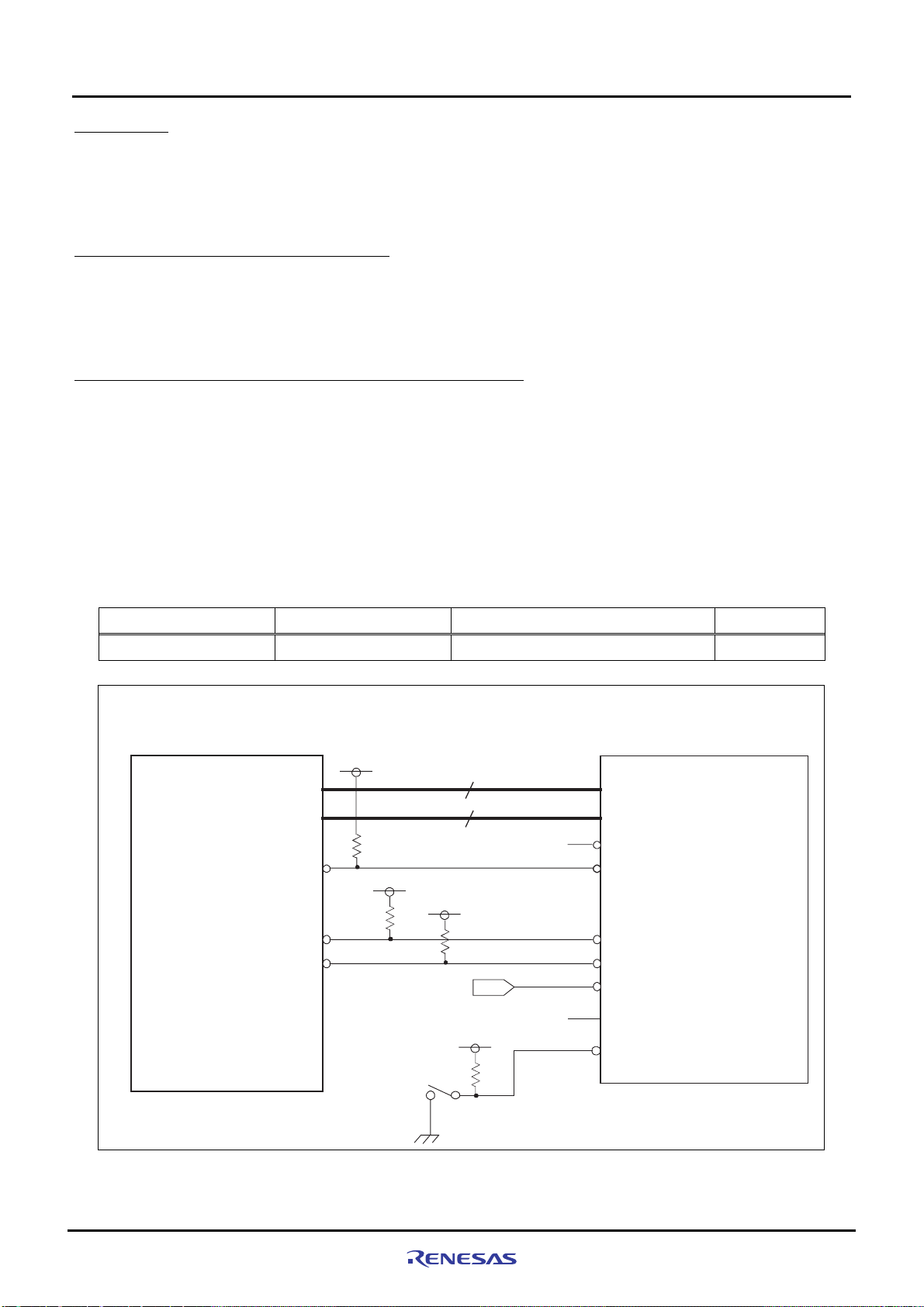

Figure 2.3.1 shows the Flash Memory Block Diagram. Table 2.3.2 lists setting examples of the bus state

controller(write/read) when the SH7619 bus clock operates at 62.5 MHz (clock mode 1), and Figure 2.3.2 shows read and

write access timing example.

Table 2.3.1 Flash Memory Specifications

Part Number Bus Size Capacity Access Time

S29GL032A90TFIR4 16-bit mode 4 MB (16 bits x 2 Mwords x 1) 90 ns

SH7619 (U1)

D15-D0

A21-A1

RD#

WE0#

CS0#

3.3 V

21

16

3.3 V

3.3 V

3.3 V

Reset Signal

NC

3.3 V

DIP Switch

(SW4-4)

S29GL032A90TFIR4 (U2)

(2 Mwords x 16 bits)

A20-A0

DQ15-DQ0

BYTE#

OE#

WE#

CE#

RESET#

RY/BY#

WP#

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-4

Figure 2.3.1 Flash Memory Block Diagram

Page 21

Features and Specifications

A

2

Table 2.3.2 Setting Example of Bus State Controller (Flash Memory Write and Read)

User Area Applicable Device Settings for Bus State Controller

CS0 S29GL032A90TFIR4 CS0 Space Bus Control Register: CS0BCR

2.3.2 Flash Memory S29GL032A90TFIR4 (Standard component)

Initial value: H'36DB 0400 (MD3 = "L")

Recommended value: H'1000 0400

• Idle Cycles between Write-Read Cycles and

Write-Write Cycles

IWW[1:0] = B'01: 1 idle cycle inserted

• Data bus width

BSZ[1:0] = B’10: *Shall be ignored.

CS0 space wait control register: CS0WCR

Initial value: H'0000 0500

Recommended value: H'0000 0AC1

• Number of Delay Cycles from address, CS0#

Assertion to RD#, WEn#

SW[1:0] = B'01; 1.5 cycles

• Number of Access Wait Cycles

WR[3:0] = B'0101; 5 cycles

• Ignore external WAIT input

WM = B’1;

• Number of Delay Cycles from RD#, WEn# negation

to address, CS0# negation

HW[1:0] = B'01; 1.5 cycles

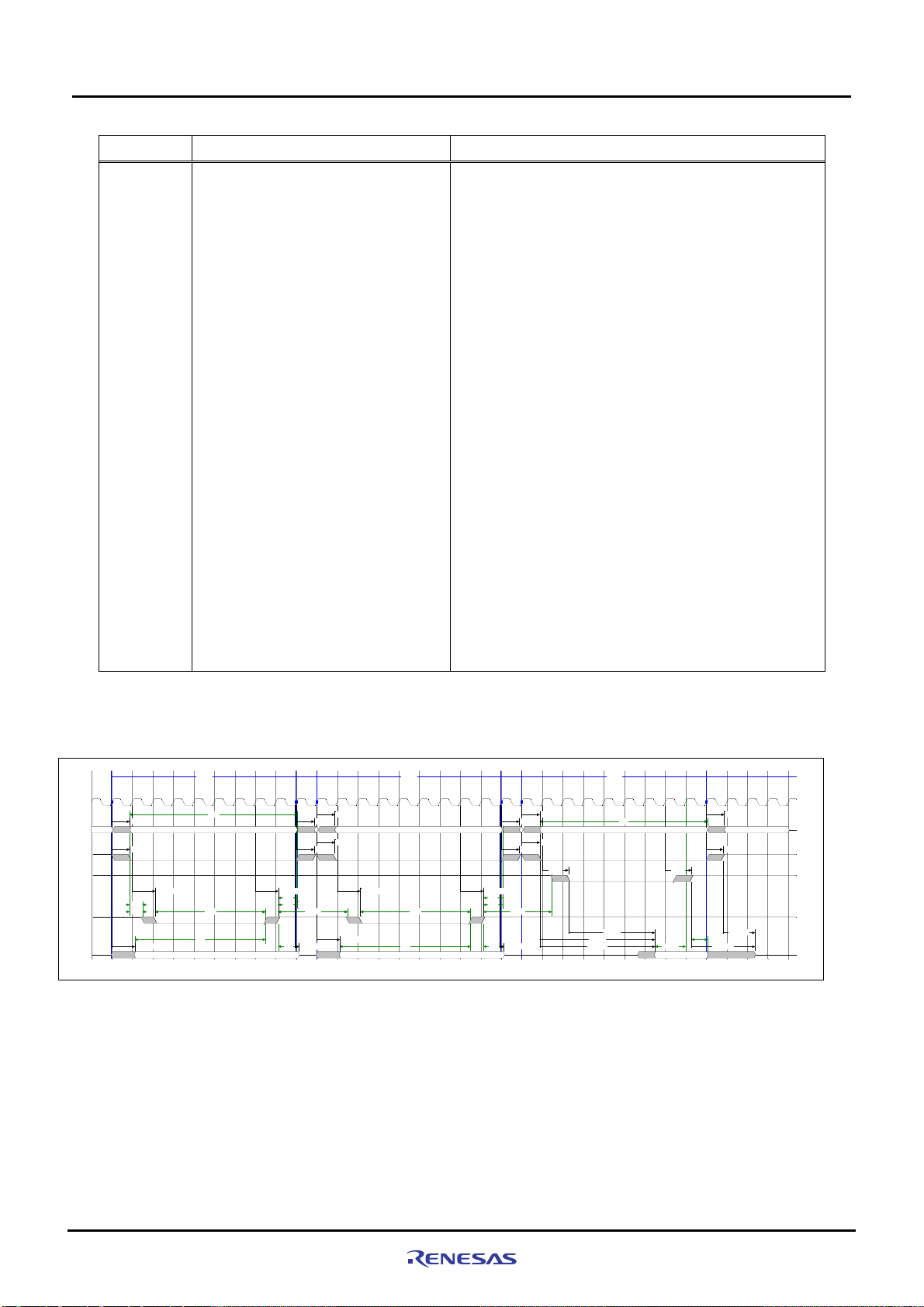

<Write/Read Timing>

CKIO

21-A1

CS0#

RD#

tCS

WE0#

D15-D0

Write1 Write2 Read1

tWCtWC

tCH

tWPtAS

tWP

tDS

DATA DATA DATA

tAH

T1T2Tw 4T1 Tw 1 Tw 2 Tw 1 Tw2 T2 T1 Tw1 Tw 2 Tw3 T2Tf Tf Taw1Taw 1Th Th Th TfTw 4Tw3 Tw 3 Tw4 Tw5Tw 5 Tw5

tAD1

tAD1tAD1

tCSD1

tCSD1tCSD1

tWPH

tWDD1

tWDH1tWDD1

ta(AD)

ta(CE1)

tRCtRC

ta(OE)

tAD1

tCSD1

tCSD1

tWED1tWED1tWED1tWED1

tCH

tAH

tWPtWPH tWP

tOEH

tWDH1

Figure 2.3.2 Flash Memory Read and Write Access Timing Example

tAD1tAD1

tCSD1

tRSDtRSD

tDF(CE)

tRDS1tDHtDStDH

tRDH1

tDF(OE)

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-5

Page 22

Features and Specifications

2

2.3.3 External Synchronous DRAM (SDRAM)

The M3A-HS19 is provided with a 16-MB synchronous DRAM (SDRAM) as an external main memory. T he SDRAM is

controlled by the SH7619 on-chip bus state controller. The SDRAM is accessed in 16-bit bus.

Table 2.3.3 lists SDRAM specifications used on the M3A-HS19, and Figure 2.3.3 shows its block diagram.

Table 2.3.3 SDRAM Specifications

Items Description

Part Number EDS1216AATA-75E

Configuration 16 MB (16-bit bus width) x 1

Capacity 16 MB

Access Time 5.4 ns

CAS Latency 2 (at 62.5 MHz bus clock)

Refresh Interval 4,096 refresh cycles in every 64 ms

Row Address A1 1- A0

Column Address A8 - A0

Number of Banks 4-banks controlled by BA0, BA1

2.3.3 External Synchronous DRAM

3.3V

EDS1216AATA-75(U3)

(

SH7619(U1)

A14-13 BA1-0

A12-1

CS3#

CKIO

CKE

RD/WR#

RAS#

CAS#

DQMLU

DQMLL

D15-0

x 16

2

11

16

2 M x 16 bits x 4-bank)

A11-0

CS#

CLK

CKE

WE#

RAS#

CAS#

DQMU

DQML

DQ15-DQ0

Figure 2.3.3 External SDRAM Block Diagram

Rev.1.01

Oct 28, .2008 2-6

REJ10J1351-0101

Page 23

Features and Specifications

2

A power-on sequence is required to use a SDRAM. Power-on sequence is to initialize the pin function controller (PFC),

set registers in the bus state controller and write data in the SDRAM mode register.

Table 2.3.4 lists the access address when writing in the SDRAM mode register on the CS3 space.

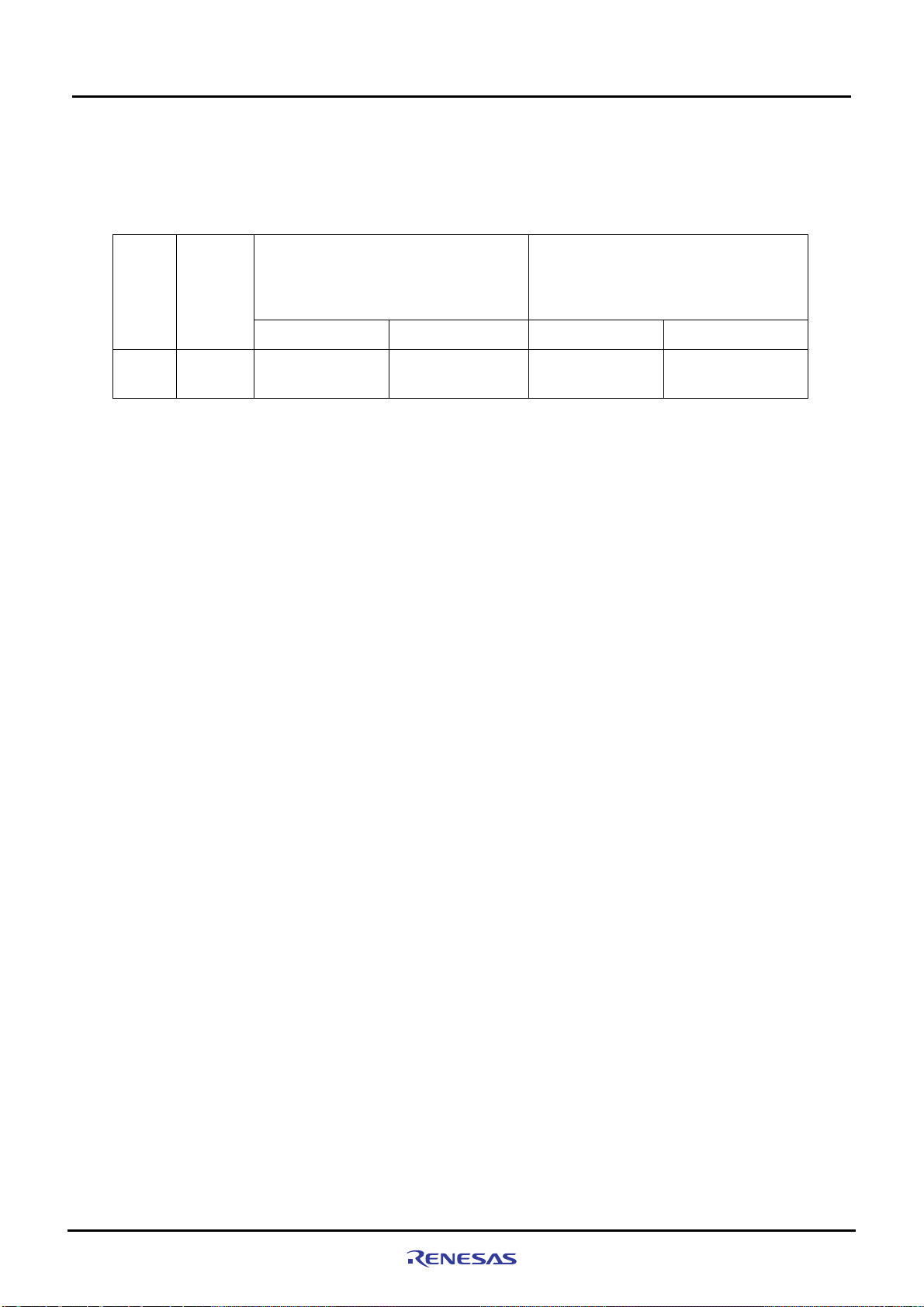

Table 2.3.4 Access Address for SDRAM Mode Register Write (CS3 Space)

2.3.3 External Synchronous DRAM

Data bus

width

16 bits 2 H'F8F D 5440 H'0000 0440 H'F8FD 5040 H'0000 0040

Execute following settings to the M3A-HS19 SDRAM mode register.

• Burst length: Burst read/single write (burst length 1)

• Wrap type: Sequential

• CAS latency: 2 cycles

To write data in the SDRAM mode register as shown in Table 2.3.4, write the arbitrary data in words to the address of

H'F8FD 5440 (the data in this case is ignored). Following commands are sequentially issued to the SDRAM by the word

writing.

1.All banks precharge command (PALL)

Idle cycles (Tpw), of which number is specified by bits WTRP1 and WTRP0 in CS3WCR, are inserted between the PALL

and the first REF commands.

2. Auto-refreshing command (REF) for eight times

Idle cycles (Trc), of which number is specified by bits WTRP1 and WTRP0 in CS3WCR are inserted after issuing REF

command

3. Mode register write command (MRS)

CAS

latency

Burst read/single write (burst length 1) Burst read/burst write (burst length 1)

Access Address External Address Pin Access Address External Address Pin

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-7

Page 24

2

Figure 2.3.4 shows a timing example of SDRAM mode register writing.

tRCtRP

CKIO

SDRAM

Command

A11-A1(A9-A0)

A12(A10/AP)

CS3#

RASL#

CASL#

RD/WR#

Tp

PALL

Tpw Trr

DESL

Trc Trc

Trc Trc

DESL DESL

REF

DESL

REF command is issued 8 times

DESL

Trr

Trc

DESL REF

Features and Specifications

2.3.3 External Synchronous DRAM

Tmw

REF

TrcTrr

DESL

MRS

Tnop

DESL

DQMUU-LL

D15-0

[Symbols Descriptions]

PALL

:All bank precharge command

REF :Auto-refreshing command

:Mode register write commamd

MRS

DESL

:Deselect command

(High)

Hi-Z

Figure 2.3.4 Timing Example of SDRAM Mode Register Writing

Rev.1.01

Oct 28, .2008 2-8

REJ10J1351-0101

Page 25

Features and Specifications

2

Table2.3.5 lists setting examples of the bus state controller with SH7619 bus clock at 62.5 MHz.

Figure 2.3.5 shows the SDRAM single read/write timing example.

Table2.3.5 Setting Example of Bus State Controller (SDRAM Read/Write)

User Area Applicable Device Settings for Bus State Controller

CS3 EDS1216AATA-75E CS3 Space Bus Control Register: CS3BCR

Initial value: H'36DB 0600

Recommended value: H'0000 4400 (in 16-bit bus width)

• Memory specification

TYPE[3:0] = B'0100; SDRAM

• Data bus specification

BSZ[1:0] = B'10; 16-bit bus width

CS3 Space Wait Control Register: CS3WCR

Initial value: H'0000 0500, recommended value: H'0000 2892

• Wait Cycle Number for Precharge Completion

WTRP[1:0] = B'01; 1 cycle

• Wait Cycle Number from ACTV command to READA WRITA

command

WTRCD[1:0] = B'10; 2 cycles

• Cas Latency for Area 3

A3CL[1:0] = B'01; 2 cycles

• Wait Cycle Number for Precharge Start Wait

TRWL[1:0] = B'10; 2 cycles

• Idle Cycle Number from REF/Self-Refreshing Release to

ACTV/REF/MRS Command

WTRC[1:0] = B'10; 5 cycles

SDRAM Control Register: SDCR

Initial value: H'0000 0000,

Recommended value: H'0000 0809

• Refresh Control

RFSH = B'1; Refreshing is performed

• Refresh Control

RMODE = B'0; Auto-Refreshing is not performed

• Bank active mode

BACTV = B'0; Auto-precharge mode

• Number of Bits of Row Address for Area 3

A3ROW[1:0] = B'01; 12 bits

• Number of Bits of Column Address for Area 3

A3COL[1:0] = B'01; 9 bits

Refresh Timer Control / Status Register: RTCSR

Initial value: H'0000 0000,

Recommended value: H'A55A 0010

• Clock Select

CKS[2:0] = B'010; Bφ/16

• Refresh Count

RRC[2:0] = B'000 ; Once

Refresh Time Constant Register: RTCOR

Initial value: H'0000 0000,

Recommended value: H'A55A 003D

*The refresh request interval when clock select is set to Bφ/16 is as

follows.

1 cycle: 256 nsec (62.5 MHz/16 = 3.90625 MHz)

Refresh request interval in this SDRAM: 15.625 μsec/time

15.625 usec/256 nsec = 61 (0x3D) cycles/refresh counts

2.3.3 External Synchronous DRAM

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-9

Page 26

2

A

CKIO

CKE

CS3#

RAS#

CAS#

RD/WR#

DQMUU-LL

A11-A1(A9-A0)

A12(A10/AP)

14,A13(BA1,0)

D15-0

ACT

Tr Trw1

tCSD1

tRASD1

tDQMD1

tAD1

tAD1

tAD1

SDRAM SINGLE READ

tRC

tHI

tSI

tCASD1

tRC

tCASD1

tLZ

tAC

Data

tHI

tRDS2

tRDH2

tOH

tRAS

READA ACT

Tc1 Tcw Td1 Tde Tr Trw1Tap

tSI

tRASD1

tHI

tSI

tOHZ

tRPtRAS tRP

Features and Specifications

2.3.3 External Synchronous DRAM

SDRAM SINGLE WRITE

tRC

tRC

tRAS

tRCD

WRITEA ACT

Tc1 Trwl1 Trwl2 TrTap

tSI

tCSD1tCSD1

tRASD1

tRASD1

tDQMD1tDQMD1

tAD1tAD1tAD1

tAD1tAD1tAD1

tAD1tAD1tAD1

tHI

tCASD1

tRWD1

tAD1tAD1

tAD1tAD1

tAD1tAD1

tHI

tSI

tWDD2

tWDH2

tDPL

tDPL

tCSD1

tCASD1

tRWD1

tDQMD1

tDAL

tDAL

tRP

tRPtRAS

Figure 2.3.5 SDRAM Single Read/Write Timing

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-10

Page 27

Features and Specifications

3.3 V

2

2.3.4 External EEPROM

The M3A-HS19 is provided with an EEPROM for storing MAC address.

Access to the EEPROM is enabled by using the SH7261 I/O ports (PC03, PC02, PC01 and PC00). A MAC address

consists of 48-bit numbers.

Table 2.3.6 lists instruction sets, and Figure 2.3.6 shows the block diagram of CPU and EEPROM connection.

Figure 2.3.7 shows the EEPROM-AC timing and Figure 2.3.8 shows EEPROM-read/write timing.

Settings for following instruction sets are not required;

- A7 to A0 for WRAL, ERAL, EWEN, and EWDS instructions

- Data for ERASE, ERAL, EWEN and EWDS instructions

Table 2.3.6 Instruction Sets (S-93C76AFT )

Start Bit Operation

Command SK

1 2 3 4 5 6~13 14~29

READ 1 1 0 - A8 A7~A0 D15~D0 (OUT)

WRITE 1 0 1 - A8 A7~A0 D15~D0 (IN)

ERASE 1 1 1 - A8 A7~A0 WRAL 1 0 0 0 1 - D15~D0(IN)

ERAL 1 0 0 1 0 - EWEN 1 0 0 1 1 - EWDS 1 0 0 0 0 - -

Code

Address Data

2.3.4 External EEPROM

SH7619 (U1)

PC03/MII_RXD3

PC01/MII_RXD1

PC00/MII_RXD0

Figure 2.3.6 CPU and EEPROM Connection

EEPROM

S-93C76AFT(U4)

CS

SKPC02/MII_RXD2

DI

DO GND

Vcc

TEST

NC

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-11

Page 28

2

READ

W

(Setting Address)Data0

2

A

Features and Specifications

2.3.4 External EEPROM

C characteristics

Clock pulse width

SK

1 μsec

or more

0 sec or more

Deselect

200 nsec or more

CS

1 μsec or more

Writing

Enabled Data

CS setup

400 nsec or more

DI

HoldSetup

200 nsec or more

DO

Hi-Z

Figure 2.3.7 EEPROM-AC Timing

200 nsec or more

Within 800 nsec

Output delay time

Output Enabled Data

Within

800 nsec

Hi-Z

Output disabled time

Within 500 nsec

SK

CS

DI

DO

RITE

SK

CS

DI

DO

Dummy SK

"0"

Dummy SK

"0"

3 4 5 6

1 2

"0""1"

"1""1"

Writing Instruction, Address, Writing Data Input

"1"

"x"

1 2 3 4 5 6

"0" "1"

"x"

A

Hi-Z

A8

Hi-Z

8

A7A

A7 A6

7 8 9 10

Setting Address

6

A5A

7 8 9 10

A5 A4

Figure 2.3.8 EEPROM-Read/Write Timing

4

A3A

A3 A2

11 12 13 14

2

A1A0"x"

"0"

11 12 13 14

A1 A0

D15 D14 D13

D15 D14 D13

(Setting Address)Data0

27 28 29 30 31 32 44 45 46 47 4815 16

D2 D1 D0 D15 D14 D13

(Setting Address+1)Data1 (Setting Address+2)Data

27 28 29 30 31 3215 16

D2 D1 D0

Start writing End of writing

43

D2 D1 D0

Verify Standby

"0"

D15 D14 D13

"1"

Hi-Z

Hi-Z

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-12

Page 29

Features and Specifications

2

2.4 Serial Port Interface

2.4 Serial Port Interface

The SH7619 MCU mounted on the M3A-HS19 is provided with a 3 channel’s of the Serial Communication Interface with

FIFO (SCIF).

SCIF channel 0 is connected to the 2-pin serial port connector, SCIF channel 2 is connected to the D-sub 9-pin serial port

connector, and SCIF channel 1 is connected to the 4-pin serial port connector.

Figure 2.4.1 shows the block diagram of the serial port interface.

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-13

Figure 2.4.1 Serial Port Interface

Page 30

Features and Specifications

2

2.5 PCMCIA Card Interface

2.5 PCMCIA Card Interface

The SH7619 MCU mounted on the M3A-HS19 is compliant with the JEIDA 4.2 (PCMCIA2.1 Rev.2.1). However, only

3.3 V interface PC card is supported. An on-chip bus state controller (BSC) and a PFC control the PC card.

High byte and low byte of the data is switched at the bus switch on the M3A-HS19. When the byte order of the SH7619 is

big-endian, the order of the PC card connector is little-endian (IOIS16#: ”L”).

The M3A-HS19 is provided with a PCMCIA card slot in area 5, allowing both IC memory card and I/O card to be mounted.

Figure 2.5.1 shows the block diagram of PCMCIA card interface.

PC card connector (J4)

20-bit bus switch

D15-D6

D5-D0

10

6

1B[9:0]

2B[9:0]

1A[9:0]

2A[9:0]

1OE#

2OE#

10

6

SH7619 (U1)

D7-D0, D15, D14

D13-D8

20-bit bus switch

A25-A16

A15-A6

A5-A0

RESET

CE1#

CE2#

REG#

OE#

WE#

IORD#

IOWR#

CD1#

CD2#

WAIT#

IOIS16#

IREQ#

VS1#

VS2#

INPACK#

SPKR#

STSCHG#

VCC

3.3 V

x3

PCVCC

10

10

6

1B[9:0]

2B[9:0]

20-bit bus switch

4

4

2

x5

1B[9:0]

2B[9:0]

PCMCIA

Power supply

circuit

PCVCC

1A[9:0]

2A[9:0]

1OE#

2OE#

10

10

A25-A16

A15-A6

A5-A0

6

PC09/RX_ER(GPIO)

CE2A#

1A[9:0]

2A[9:0]

10

8

4

4

CE1A#

PC14/COL

RD#

WE#

PB05/ICIORD#

1OE#

2OE#

4

PB06/ICIOWR#

PC15/CRS

PB0/WAIT#

PB1/IOIS16#

PD7/IRQ7

JP2

3.3 V5.0 V

PC20/WOL

PB13/BS#

JP1

Figure 2.5.1 PCMCIA Card Interface

Rev.1.01

Oct 28, .2008 2-14

REJ10J1351-0101

Page 31

Features and Specifications

2

2.6 LAN Port Interface

2.6 LAN Port Interface

An IEEE 802.3 compliant (MAC layer) Ethernet controller and an IEEE802.3/802.3u compliant (10/100 Mbps Ethernet

PHY) physical layer transceiver are embedded in the SH7619 MCU.

Figure 2.6.1 shows the block diagram of LAN port interface.

SH7619 (U1)

SPEED100#

LINK#

CRS#

DUPLEX#

(MII)

TxP

TxM

ETC

PHY

RxP

RxM

EXRES1

TSTBUSA

LED1

Yellow

3.3 V

LED2

Yellow

LED3

Yellow

LED4

Yellow

3.3 VA

1

2

3

4

5

6

7

8

RJ-45 (J5)

TX +

TX −

TCT

RX +

RX −

RCT

CK_PHY

25.000 MHz-OSC

MII-compliant signal

12.4 K(1%)

3 VAGND

Figure 2.6.1 LAN Port Interface

Rev.1.01

Oct 28, .2008 2-15

REJ10J1351-0101

Page 32

Features and Specifications

2

2.7 I/O Port

2.7 I/O Port

Following I/O ports on the M3A-HS19 can be configured by the SH7619 MCU. These ports are multiplexed pins with up to

four features. Some pins have several initial features for normal mode and HIF (Host Interface) boot mode. Features can

be controlled by PFC (pin function controller).

• PA16 - PA25

• PB00 - PB13

• PC00 - PC20

• PD0 - PD7

• PE00 - PE24

The M3A-HS19 is connected with a memory, expansion connectors, a PCMCIA connector, a LAN connector, an RS-232C

connector, an RS-422 connector and other control ICs. Some I/O ports are connected to DIP switches and LEDs, which

can be used in the port mode as intended use. LED shows status in the PHY mode.

Table 2.7.1 lists Mode DIP Switch (SW4) Features. The state will be loaded when the board is reset and started.

Table 2.7.1 Mode DIP Switch (SW4) Features

SW4-No.

1 ON: Big-endian OFF: Little-endian

2 ON: Host interface (HIF) is NOT operating OFF: Host interface (HIF) is operating

3 ON: Normal boot mode OFF: HIF boot mode

4 ON: Flash ROM is write-protected OFF: Write-enabled

Figure 2.7.1 shows the block diagram of I/O port connections to switches and LEDs.

Table 2.7.2 and Table 2.7.3 list I/O port features.

Description

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-16

Figure 2.7.1 I/O Port Connection to Switches and LEDs

Page 33

2

Table 2.7.2 I/O Port Features (1/2)

Port Name

(SH7619)

PA16~PA20 A16~A20: Flash ROM, PCMCIA, expansion connector

PB10 CS5B#/CE1A#: PCMCIA

PB12 CS3#: SDRAM, expansion connector

PB13 BS#: PCMCIA-PW control, expansion connector

PC0~PC3 MII_RxD0~MII_RxD3: EEPROM, expansion connector

PC10 RX_CLK: Expansion connector

PC12 TX_EN: Expansion connector

PC13 TX_CLK: Expansion connector

PC14 COL: PCMCIA

PC15 CRS: PCMCIA, expansion connector

PC16 MDIO: SW3-1 (Port IN)

PC17 MDC: SW3-2 (Port IN)

PC18 LNKSTA: SW3-3 (Port IN)

PC19 EXOUT: SW3-4 (Port IN)

PC20 WOL: PCMCIA (Bus DIR) , expansion connector

PA21 A21/SCK_SIO0: Flash ROM, PCMCIA, expansion connector

PA22 A22/SIOMCLK0: Flash ROM, PCMCIA, expansion connector

PA23 A23/RxD_SIO0: Flash ROM, PCMCIA, expansion connector

PA24 A24/TxD_SIO0: PCMCIA, expansion connector

PA25 A25/SIOFSYNC0: PCMCIA, expansion connector

PB0 WAIT#: PCMCIA

PB1 IOIS16#: PCMCIA

PB2 CKE: SDRAM

PB3 CAS#: SDRAM

PB4 RAS#: SDRAM

PB5 WE2#/DQMUL/ICIORD#: PCMCIA, expansion connector

PB6 WE3#/DQMUU/ICIOWR#: PCMCIA, expansion connector

PB7 CE2B#: Expansion connector

PB8 CS6B#/CE1B#: Expansion connector

PB9 CE2A#: PCMCIA

PB11 CS4#: Expansion connector

PC4 MII_TxD0/SPEED100#: LED1

PC5 MII_TxD1/LINK#: LED2

PC6 MII_TxD2/CRS#: LED3

PC7 MII_TxD3/DUPLEX#: LED4

PC8 RX_DV: Expansion connector

PC9 RX_ER: PCMCIA

PC11 TX_ER: Expansion connector

PD0 IRQ0/TEND0: SW6(IRQ0)

PD1 IRQ1/TEND1: Expansion connector

Signal Name and Connection (M3A-HS19)

Features and Specifications

2.7 I/O Port

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-17

Page 34

2

Table 2.7.3 I/O Port Features (2/2)

Port Name

(SH7619)

PD2 IRQ2/TxD1/DREQ0: RS-422

PD3 IRQ3/RxD1/DACK0: RS-422

PD4 IRQ4/SCK1: Expansion connector

PD5 IRQ5/TxD2/DREQ1: RS-232C

PD6 IRQ6/RxD2/DACK1: RS-232C

PD7 IRQ7/SCK2: PCMCIA, expansion connector

PE0 HIFEBL/SCK_SIO0: SW4-2, expansion connector

PE1 HIFRDY/SIOMCLK0: Expansion connector

PE2 HIFDREQ/RxD_SIO0: Expansion connector

PE3 HIFMD: SW4-3

PE4 HIFINT#/TxD_SIO0: Expansion connector

PE5 HIFRD#: Expansion connector

PE6 HIFWR#/SIOFSYNC: Expansion connector

PE7 HIFRS: Expansion connector

PE8 HIFCS#: Expansion connector

PE9~PE14 HIFD0~HIFD5/D16~D21: Expansion connector

PE15 HIFD6/TxD0/D22: Expansion connector, 3-wire RS-232C

PE16 HIFD7/RxD0/D23: Expansion connector, 3-wire RS-232C

PE17 HIFD8/SCK0/D24: Expansion connector

PE18 HIFD9/TxD1/D25: Expansion connector

PE19 HIFD10/RxD1/D26: Expansion connector

PE20 HIFD11/SCK1/D27: Expansion connector

PE21 HIFD12/RTS0/D28: Expansion connector

PE22 HIFD13/CTS0/D29: Expansion connector

PE23 HIFD14/RTS1/D30: Expansion connector

PE24 HIFD15/CTS1/D31: Expansion connector

Signal Name and Connection (M3A-HS19)

Features and Specifications

2.7 I/O Port

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-18

Page 35

Features and Specifications

1

2

2.8 Power Supply Circuit

2.8 Power Supply Circuit

The main power supply input 5 V DC to the M3A-HS19 and it generates 3.3 V and 1.8 V using a regulator.

It is an adjustable output voltage regulator to generate a desired voltage by changing resistance values.

A through-hole is provided with the M3A-HS19 to input 1.8 V DC from an external power supply. The PC card power

supply is controlled by software.

Figure 2.8.1 shows the schematic diagram of the power supply circuit.

5 V

Expansion connector (J12)

1

2

5 V-IN

(J7)

.8 V-IN

(J8)

Flash

Regulator (U12)

SW1

1

5 V

3.3 V

memory

(U2)

SH7619

2

GND

Regulator (U16)

5 V

1.8 V

(U1)

JP3

SDRAM

(U3)

PB13/BS#

1

Other

logic IC

JP1

EN1

EN0

Expansion connector

(J10)

LTC1470

PCMCIA connector

(U5)

(J4)

2

GND

Figure 2.8.1 Power Supply Circuit

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-19

Page 36

Features and Specifications

2

2.9 Clock Module

2.9 Clock Module

The clock module on the M3A-HS19 consists of following three blocks;

• A block connecting X1 (oscillator) output to SH7619 EXTAL

• A block connecting X2 (ceramic resonator) to EXTAL and XTAL (Optional)

• A block connecting X3 (oscillator) to CK-PHY

An on-chip oscillator (15.625 MHz) is connected to the SH7619 MCU to provide an operating clock. Another on-chip

oscillator (25.000 MHz) is also connected to the MCU to provide clock to physical layer. Bus clock output is connected to

a SDRAM and expansion connectors via damping resisters respectively.

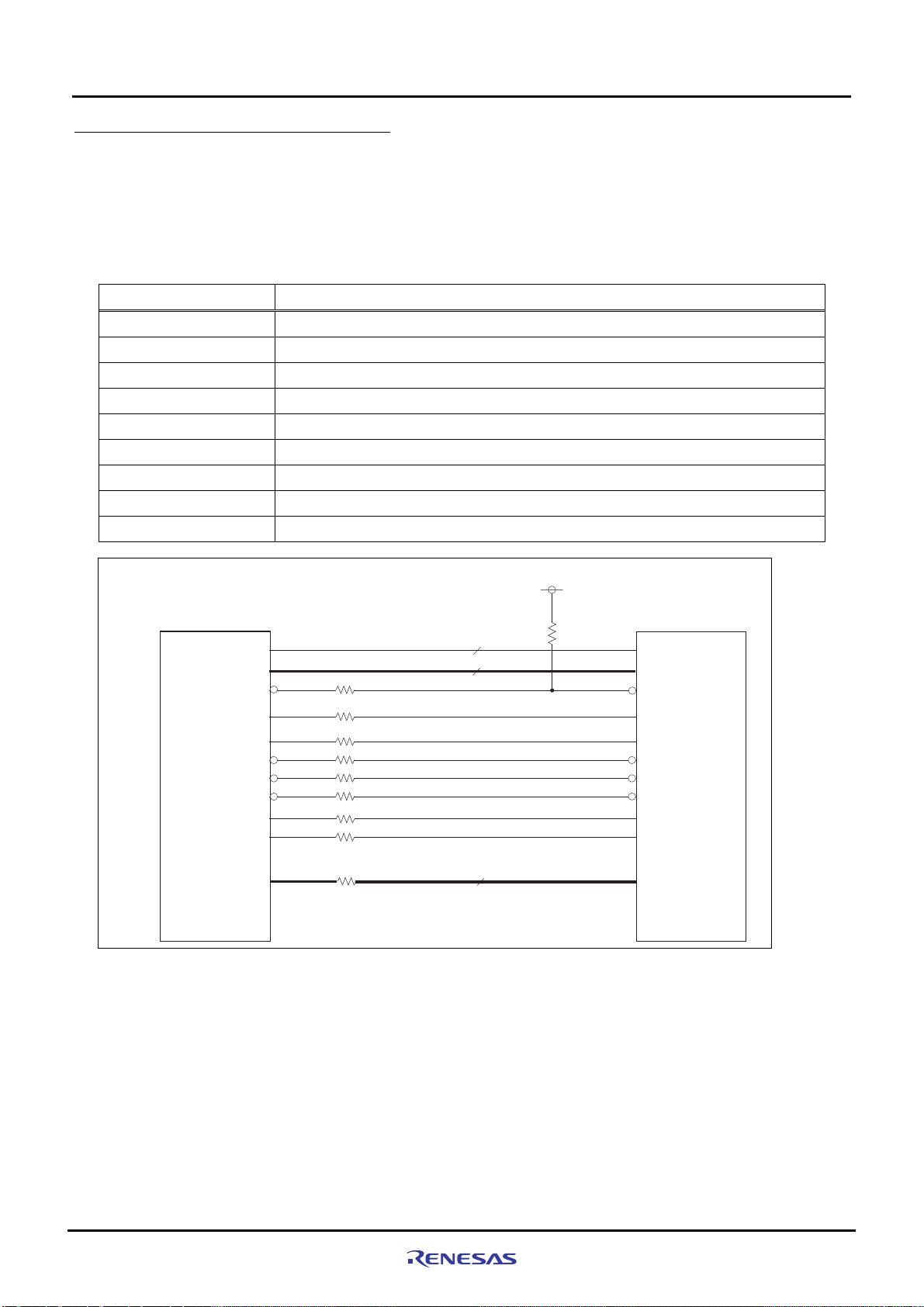

Figure 2.9.1 shows the block diagram of clock module.

* : To mount a ceramic resonator,remove the resistance R13 and mount the resistance R14.

:Optional

SH7619(U1)

CLK

Oscillator(X1)

15.625

MHz

R13

Optional

CSTCE-G15M7

(Murata)

R14

Ceramic

resonator*(X2)

EXTAL

XTAL

CKIO

R98

R117

EXCLK expansion

connector(J10-36)

CLK SDRAM(U3)

CLK

Oscillator(X3)

25.000

MHz

R18

CK-PHY

Figure 2.9.1 Clock Module

Rev.1.01

Oct 28, .2008 2-20

REJ10J1351-0101

Page 37

Features and Specifications

R

R

H-UDI connector

2

2.10 Reset Module

2.10 Reset Module

Reset module controls reset signals connected to the SH7619 MCU, a flash memory and connectors. Software controls to

reset PCMCIA connector.

Figure 2.10.1 shows the schematic diagram of resets.

Reset IC output delay time: td = 0.34×Cd(pF)µsec = 34 ms

3.3 V

0.1 µF

Ra+Rb

)

Rb

100 Ω

)

LVC14(U14)

SW2

Reset switch

Reset IC output detect voltage: Vs = 1.25× = 2.5 V

3.3 V

Open collector output

*

Reset

a

10 KΩ

M51957BFP(U13)

Input

K

Ω

Delay capacitor

10

b

IC

Output

*

Cd

RESET_IN(J9-1)

JP2

S08(U15)

1OE#

2OE#

RESET#

Expansion connector

RESET#

Flash memory

RESET#

SH7619

RES#

PC09/RX_ER

PC20/WOL

RESET

PCMCIA(J4)

Bus switch

Figure 2.10.1 M3A-HS19 Reset System

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-21

(U9)

Page 38

2

3.3 V

0

E

2.11 Interrupt Switch

Push-button switches are connected to the SH7619 NMI pin and IRQ0 pin.

Interrupts are connected to IRQ7 from an expansion connector and a PCMCIA connector.

Figure 2.11.1 shows the schematic diagram of interrupts.

Features and Specifications

2.11 Interrupt Switch

SH7619 (U1)

SW 5

NMI switch

SW 6

IRQ0 switch

IREQ#

PCMCIA(J4)

xpansion connector (J11)

16

NMI

LVC14(U14)

3.3 V

PD0/IRQ0/-/TEND

LVC14(U14)

PC20/WOL

PD7/IRQ7/SCK2

JP2

1OE#

2OE#

R106

18

Figure 2.11.1 Interrupts

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-22

Bus switch (U9)

Page 39

Features and Specifications

2

2.12 E10A-USB Interface

The M3A-HS19 is provided with a 14-pin H-UDI connector to embed the E10A-USB emulator.

Figure 2.12.1 shows the block diagram of the E10A-USB interface.

3.3 V

3.3 V

2.12 E10A-USB Interface

H-UDI connector (J6)

8

NC

10

GND

12

GND

13

GND

14

GND

Reset

UVCC

TCK

TRST#

TDO

NC

TMS

TDI

(GND)

RES#

11

1

3

4

5

6

9

7

TCK

TRST#

TDO

TMS

TDI

ASEMD#

RES#

SH7619 (U1)

Figure 2.12.1 E10A-USB Interface

Rev.1.01

Oct 28, .2008 2-23

REJ10J1351-0101

Page 40

2

Features and Specifications

2.12 E10A-USB Interface

This page intentionally left blank.

Rev.1.01

REJ10J1351-0101

Oct 28, .2008 2-24

Page 41

Chapter3Operational Specifications

Chapter3

Operational Specifications

3-1

Page 42

3

3.1 M3A-HS19 Connectors

Figure 3.1.1 shows the connector assignments on the M3A-HS19.

Top view of the component side

Operational Specifications

3.1 M3A-HS19 Connector

J7

Power

supply

connector

J14

AC adapter

jack

J15

GND pin

for test

J8

1.8 V External

power supply

connector (optional)

J3

RS-422

serial

connector

(optional)

Top view of the solder side

J6

H-UDI

connector

J1

RS-232C (ch1)

serial connector

(optional)

J2

RS-232C (ch2)

serial connector

J5

RJ-45 LAN

connector

J4

PC card

connector

J10, J12

Expansion

connectors

J9, J11, J13

Expansion

connectors

Figure 3.1.1 M3A-HS19 Connector Assignments

Rev.1.01

Oct.28.2008 3-2

REJ10J1351-0101

Page 43

3

3.1.1 UART Connector Pin (J1)

The M3A-HS19 is provided with an UART connector pin (J1).

Figure 3.1.2 shows the pin assignment for the UART connector (J1).

Top view of the component side

Operational Specifications

3.1.1 UART Connector Pin (J1)

J1

1

2

UART

Board Edge

Figure 3.1.2 Pin assignment for UART Connector (J1)

Table 3.1.1 lists the pin assignment for the UART connector (J1).

Table 3.1.1 Pin assignment for UART Connector (J1)

Pin no. Signal Name Pin no. Signal Name

1 RXD (PE16/HIFD07/RXD0/D23) 2 TXD (PE15/HIFD06/TXD0/D22)

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-3

Page 44

3

B

B

3.1.2 UART Connector (J2)

The M3A-HS19 is provided with an UART connector (J2).

Figure 3.1.3 shows the pin assignment for the UART connector (J2).

1

6

oard edge

J2

Operational Specifications

3.1.2 UART Connector (J2)

5

9

Top view of the

component side

1

6

oard edge

Figure 3.1.3 Pin assignment for UART Connector (J2)

Table 3.1.2 lists the pin assignment for the UART connector (J2).

Table 3.1.2 Pin assignment for UART Connector (J2)

Pin no. Signal Name Pin no. Signal Name

1 NC 6 DSR#

2 RXD (PD6/IRQ6/RXD2/DACK1) 7 RTS#

3 TXD (PD5/IRQ5/TXD2/DREQ1) 8 CTS#

4 DTR# 9 NC

5 GND

Pins 4-6 and 7-8 are loopback-connected, respectively.

5

9

Side view

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-4

Page 45

3

Top view of the

c

e

Top view of the

B

3.1.3 RS-422 Connector Pin (J3)

The M3A-HS19 is provided with an RS-422 connector pin (J3).

Figure 3.1.4 shows the pin assignment for the RS-422 connector pin (J3).

Operational Specifications

3.1.3 RS-422 Connector Pin (J3)

omponent side

solder side

J3

1

2

RS-422

3

4

oard edge

Figure 3.1.4 Pin assignment for RS-422 Connector Pin (J3)

Table 3.1.3 lists the pin assignment for the RS-422 connector pin (J3).

Table 3.1.3 Pin assignment for RS-422 Connector Pin (J3)

Pin no. Signal Name Pin no. Signal Name

1 RXD-a (PD3/IRQ3/RXD1/DACK0) 3 TXD-z (PD2/IRQ23/TXD1/DREQ0)

2 RXD-b (PD3/IRQ3/RXD1/DACK0) 4 TXD-y (PD2/IRQ23/TXD1/DREQ0)

1

2

3

4

Board edg

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-5

Page 46

3

3.1.4 PCMCIA Connector (J4)

The M3A-HS19 is provided with a PCMCIA connector (J4).

Figure 3.1.5 shows the pin assignment for the PCMCIA connector (J4).

Top view of

the solder side

J4

3.3V PCMCIA ONLY

68

34

35

Operational Specifications

3.1.4 PCMCIA Connector (J4)

1

Figure 3.1.5 Pin assignment for PCMCIA Connector (J4)

Board Edge

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-6

Page 47

Operational Specifications

3

Table 3.1.4 lists the pin assignment for the PCMCIA connector (J4).

Table 3.1.4 Pin assignment for PCMCIA Connector (J4)

Pin no. Signal Name Pin no. Signal Name

1 GND 35 GND

2 D3 36 CD1# (PC15/CRS)

3 D4 37 D11

4 D5 38 D12

5 D6 39 D13

6 D7 40 D14

7 CE1# (CE2A#) 41 D15

8 A10 42 CE2# (CE1A#)

9 OE# (RD#) 43 VS1# (Pulled up to the PCMCIA power supply)

10 A11 44 IORD# (PB05/WE2#/DQMUL/ICIORD#)

11 A9 45 IOWR# (PB06/WE3#/DQMUU/ICIOWR#)

12 A8 46 A17

13 A13 47 A18

14 A14 48 A19

15 WE# (WE1#/DQMLU/WE#) 49 A20

16 IREQ# (PD7/IRQ7/SCK2) 50 A21

17 VCC 51 VCC

18 VPP1 52 VPP2

19 A16 53 A22

20 A15 54 A23

21 A12 55 A24

22 A7 56 A25

23 A6 57 VS2# (Pulled up to the PCMCIA power supply)

24 A5 58 RESET (PC09/RX_ER)

25 A4 59 WAIT# (PB00/WAIT#)

26 A3 60 INPACK# (Pulled up to the PCMCIA power supply)

27 A2 61 REG# (PC14/COL)

28 A1 62 SPKR# (Pulled up to the PCMCIA power supply)

29 A0 63 STSCHG# (Pulled up to the PCMCIA power supply)

30 D0 64 D8

31 D1 65 D9

32 D2 66 D10

33 IOIS16#

34 GND 68 GND

(PB01/IOIS16#)

67 CD2# (PC15/CRS)

3.1.4 PCMCIA Connector (J4)

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-7

Page 48

3

2

4

6

8

3.1.5 LAN Connector (J5)

The M3A-HS19 is provided with a LAN connector (J5).

Figure 3.1.6 shows the pin assignment for the LAN connector (J5).

Operational Specifications

3.1.5 LAN Connector (J5)

Top view of the

component side

Top view of

the solder side

J5

8

6

4

2

7

5

3

1

Board Edge

Figure 3.1.6 Pin assignment for LAN Connector (J5)

Table 3.1.5 lists the pin assignment for the LAN connector (J5).

Table 3.1.5 Pin assignment for LAN Connector (J5)

Pin no. Signal Name Pin no. Signal Name

Board Edge

7

5

3

1

1 TD+ 5 RD2 TD- 6 RCT

3 TCT 7 NC

4 RD+ 8 NC

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-8

Page 49

3

Top view the

component side

J6

1

7

H-UDI

8

14

3.1.6 H-UDI Connector (J6)

The M3A-HS19 is provided with an H-UDI (J6) connector to connect the E10A-USB emulator.

Figure 3.1.7 shows the pin assignment for the H-UDI connector (J6).

Operational Specifications

3.1.6 H-UDI Connector (J6)

Figure 3.1.7 Pin assignment for H-UDI Connector (J6)

Table 3.1.6 lists the pin assignment for the H-UDI connector (J6).

Table 3.1.6 Pin assignment for H-UDI Connector (J6)

Pin no. Signal Name Pin no. Signal Name

1

TCK

2

TRST#

3

TDO

4

N.C.

5

TMS

6

TDI

7

RESET#

8

9

10

11

12

13

14

N.C.

(GND) ASEMD#

GND

UVCC

GND

GND

GND

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-9

Page 50

3

3.1.7 Power Supply Connector (J7)

The M3A-HS19 is provided with a connector for power supply.

Figure 3.1.8 shows the pin assignment for the power supply connector (J7).

Board Edge

J7

Operational Specifications

3.1.7 Power Supply Connector (J7)

Top view of the

component side

Board Edge

Figure 3.1.8 Pin assignment for Power Supply Connector (J7)

Table 3.1.7 lists the pin assignment for the power supply connector (J7).

Table 3.1.7 Pin assignment for Power Supply Connector (J7)

Pin no. Signal Name Pin no. Signal Name

1 +5 V 2 GND

Side view

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-10

Page 51

Operational Specifications

3

3.1.8 External Power Supply Connector (J8)

The M3A-HS19 is provided with a through-hole for the SH7619 external power supply connector (J8: Supplies 1.8 V).

Figure 3.1.9 shows the pin assignment for the external power supply connector (J8).

Top view of the

component side

Top view of

the solder side

3.1.8 External Power Supply Connector (J8)

1

2

1

2

J8

Board Edge

Figure 3.1.9 Pin assignment for External Power Supply Connector (J8)

Table 3.1.8 lists the pin assignment for the external power supply connector (J8).

Table 3.1.8 Pin assignment for External Power Supply Connector (J8)

Pin no. Signal Name Pin no. Signal Name

1 +1.8 V 2 GND

Board Edge

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-11

Page 52

Operational Specifications

3

3.1.9 Expansion Connectors (J9-J13)

The M3A-HS19 is provided with through-holes for expansion connectors. The Through-holes are connected to the

SH7619 I/O pins. Expansion connectors (J9 - J13) can be connected to the MIL STD connector to mount expansion

boards or to monitor the SH7619 bus signals.

Figure 3.1.10 shows the pin assignment for expansion connectors.

3.1.9 Expansion Connectors (J9-J13)

Figure 3.1.10 Pin assignment for Expansion Connectors

Table 3.1.9 lists the pin assignment for the expansion connector (J9).

Table 3.1.9 Pin assignment for Expansion Connector (J9)

Pin no. Signal Name Pin no. Signal Name

1

3

5

7

9

11

13

15

17

19

RESET_IN#

PB13/BS#

PC01/MII_RXD1

PC00/MII_RXD0

PC03/MII_RXD3

PC02/MII_RXD2

PC20/WOL

PC15/CRS

NC

GND

2

PB00/WAIT#

4

PA25/SIOFSYNC0

6

PD3/IRQ3/RXD1/DACK0

8

PD2/IRQ2/TXD1/DREQ0

10

PE07/HIFRS

12

PE01/HIFRDY

14

NC

16

PE04/HIFINT#

18

NC

20

GND

Rev.1.01

REJ10J1351-0101

Oct.28.2008 3-12

Page 53

3

3.1.9 Expansion Connectors (J9-J13)

Table 3.1.10 Pin assignment for Expansion Connector (J10)

Pin no. Signal Name Pin no. Signal Name

Operational Specifications

1

+3.3 V

3

GND

5

NC

7

PA22/A22/SIOMCLK0, PD4/IRQ4/SCK1

Jumper select