Page 1

OCO

R

S

REJ09B0202-0200

16

M16C/26A Group

(M16C/26A, M16C/26B, M16C/26T)

Hardware Manual

RENESAS 16-BIT SINGLE-CHIP MICR

M16C FAMILY / M16C/T iny SERIE

MPUTE

All information contained in these materials, including products and product specifications,

represents information on the product at the time of publication and is subject to change by

Renesas Technology Corp. without notice. Please review the latest information published

by Renesas Technology Corp. through various means, including the Renesas Technology

Corp. website (http://www.renesas.com).

Rev. 2.00

Revision Date: Feb.15, 2007

www.renesas.com

Page 2

Notes regarding these materials

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate

Renesas products for their use. Renesas neither makes warranties or representations with respect to the

accuracy or completeness of the information contained in this document nor grants any license to any

intellectual property rights or any other rights of Renesas or any third party with respect to the information in

this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising

out of the use of any information in this document, including, but not limited to, product data, diagrams, charts,

programs, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military

applications such as the development of weapons of mass destruction or for the purpose of any other military

use. When exporting the products or technology described herein, you should follow the applicable export

control laws and regulations, and procedures required by such laws and regulations.

4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and

application circuit examples, is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas products listed in this

document, please confirm the latest product information with a Renesas sales office. Also, please pay regular

and careful attention to additional and different information to be disclosed by Renesas such as that disclosed

through our website. (http://www.renesas.com )

5. Renesas has used reasonable care in compiling the information included in this document, but Renesas

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information

included in this document.

6. When using or otherwise relying on the information in this document, you should evaluate the information in

light of the total system before deciding about the applicability of such information to the intended application.

Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any

particular application and specifically disclaims any liability arising out of the application and use of the

information in this document or Renesas products.

7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas

products are not designed, manufactured or tested for applications or otherwise in systems the failure or

malfunction of which may cause a direct threat to human life or create a risk of human injury or which require

especially high quality and reliability such as safety systems, or equipment or systems for transportation and

traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication

transmission. If you are considering the use of our products for such purposes, please contact a Renesas

sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

(1) artificial life support devices or systems

(2) surgical implantations

(3) healthcare intervention (e.g., excision, administration of medication, etc.)

(4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who

elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas

Technology Corp., its affiliated companies and their officers, directors, and employees against any and all

damages arising out of such applications.

9. You should use the products described herein within the range specified by Renesas, especially with respect

to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation

characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or

damages arising out of the use of Renesas products beyond such specified ranges.

10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific

characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use

conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and

injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for

hardware and software including but not limited to redundancy, fire control and malfunction prevention,

appropriate treatment for aging degradation or any other applicable measures. Among others, since the

evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or

system manufactured by you.

11. In case Renesas products listed in this document are detached from the products to which the Renesas

products are attached or affixed, the risk of accident such as swallowing by infants and small children is very

high. You should implement safety measures so that Renesas products may not be easily detached from your

products. Renesas shall have no liability for damages arising out of such detachment.

12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written

approval from Renesas.

13. Please contact a Renesas sales office if you have any questions regarding the information contained in this

document, Renesas semiconductor products, or if you have any other inquiries.

Page 3

General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes

on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under

General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each

other, the description in the body of the manual takes precedence.

1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the

manual.

The input pins of CMOS products are generally in the high-impedance state. In operation

with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the

vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur

due to the false recognition of the pin state as an input signal become possible. Unused

pins should be handled as described under Handling of Unused Pins in the manual.

2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register

settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states

of pins are not guaranteed from the moment when power is supplied until the reset

process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset

function are not guaranteed from the moment when power is supplied until the power

reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do

not access these addresses; the correct operation of LSI is not guaranteed if they are

accessed.

4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become

stable. When switching the clock signal during program execution, wait until the target clock

signal has stabilized.

When the clock signal is generated with an external resonator (or from an external

oscillator) during a reset, ensure that the reset line is only released after full stabilization of

the clock signal. Moreover, when switching to a clock signal produced with an external

resonator (or by an external oscillator) while program execution is in progress, wait until

the target clock signal is stable.

5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm

that the change will not lead to problems.

The characteristics of MPU/MCU in the same group but having different part numbers may

differ because of the differences in internal memory capacity and layout pattern. When

changing to products of different part numbers, implement a system-evaluation test for

each of the products.

Page 4

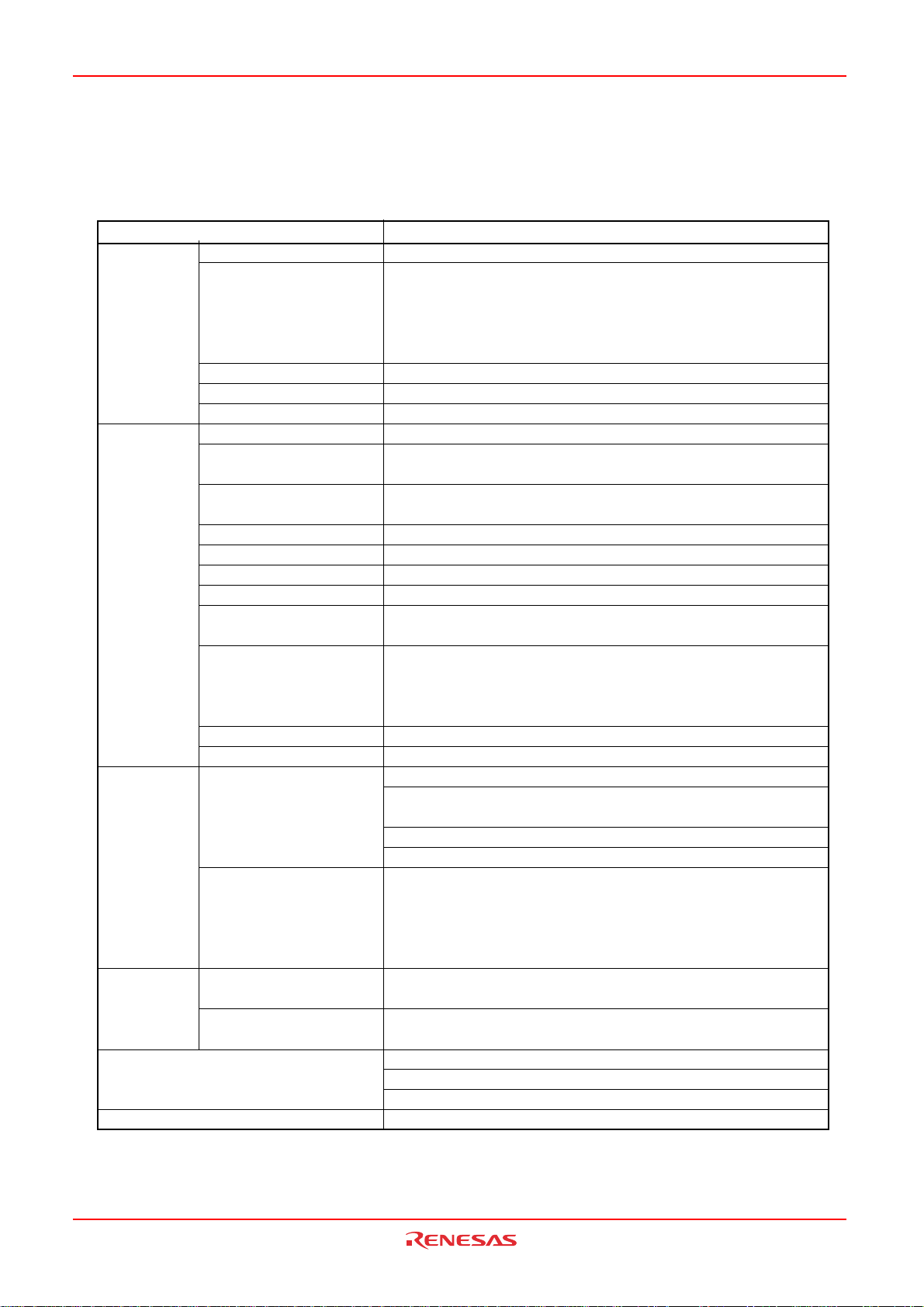

How to Use This Manual

1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical

characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic

knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual.

The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral

functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur

within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer

to the text of the manual for details.

The following documents apply to the M16C/26A Group (M16C/26A, M16C/26B, and M16C/26T). Make sure to

refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the

Renesas Technology Web site.

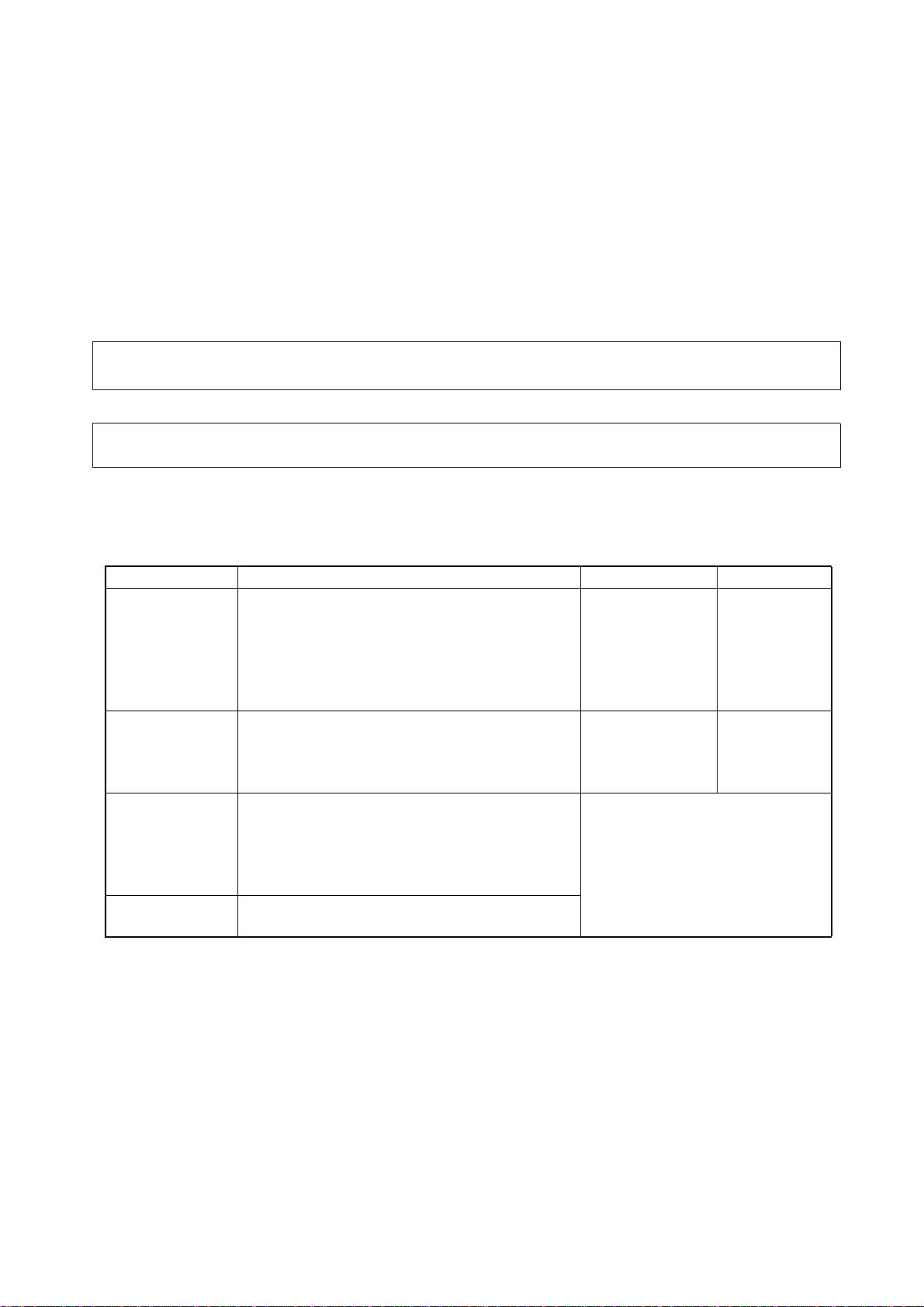

Document Type Description Document Title Document No.

Hardware manual Hardware specifications (pin assignments,

memory maps, peripheral function

specifications, electrical characteristics, timing

charts) and operation description

Note: Refer to the application notes for details on

using peripheral functions.

Software manual Description of CPU instruction set M16C/60,

Application note Information on using peripheral functions and

application examples

Sample programs

Information on writing programs in assembly

language and C

Renesas

technical update

Product specifications, updates on documents,

etc.

M16C/26A Group

(M16C/26A,

M16C/26B,

M16C/26T)

Hardware Manual

M16C/20,

M16C/Tiny Series

Software Manual

Available from Renesas

Technology Web site.

This hardware

manual

REJ09B0137

Page 5

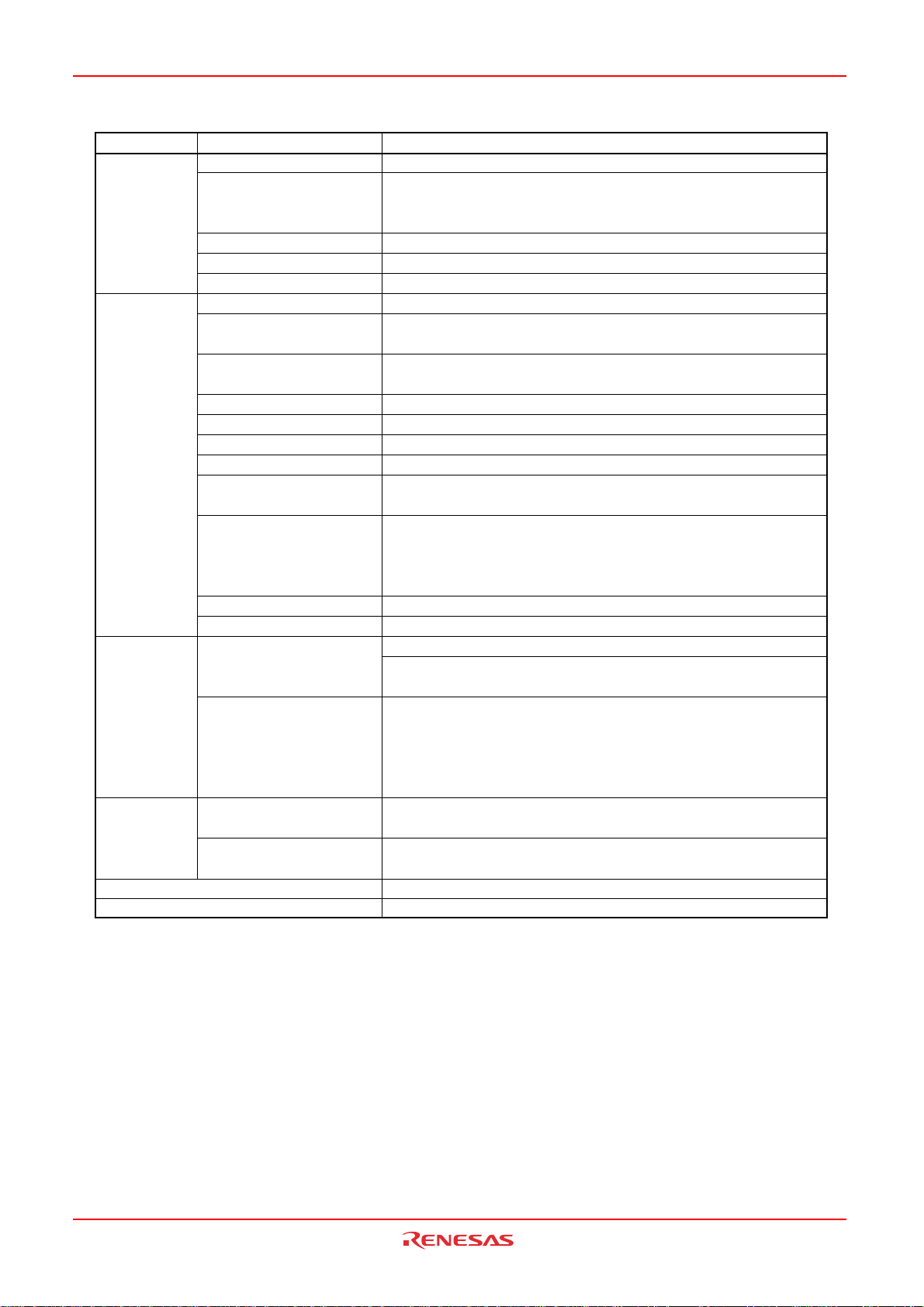

2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described

below.

(1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word

“register,” “bit,” or “pin” to distinguish the three categories.

Examples the PM03 bit in the PM0 register

P3_5 pin, VCC pin

(2) Notation of Numbers

The indication “

values of single bits. The indication “

is appended to numeric values given in decimal format.

Examples Binary: 11

2” is appended to numeric values given in binary format. However, nothing is appended to the

16” is appended to numeric values given in hexadecimal format. Nothing

2

Hexadecimal: EFA016

Decimal: 1234

Page 6

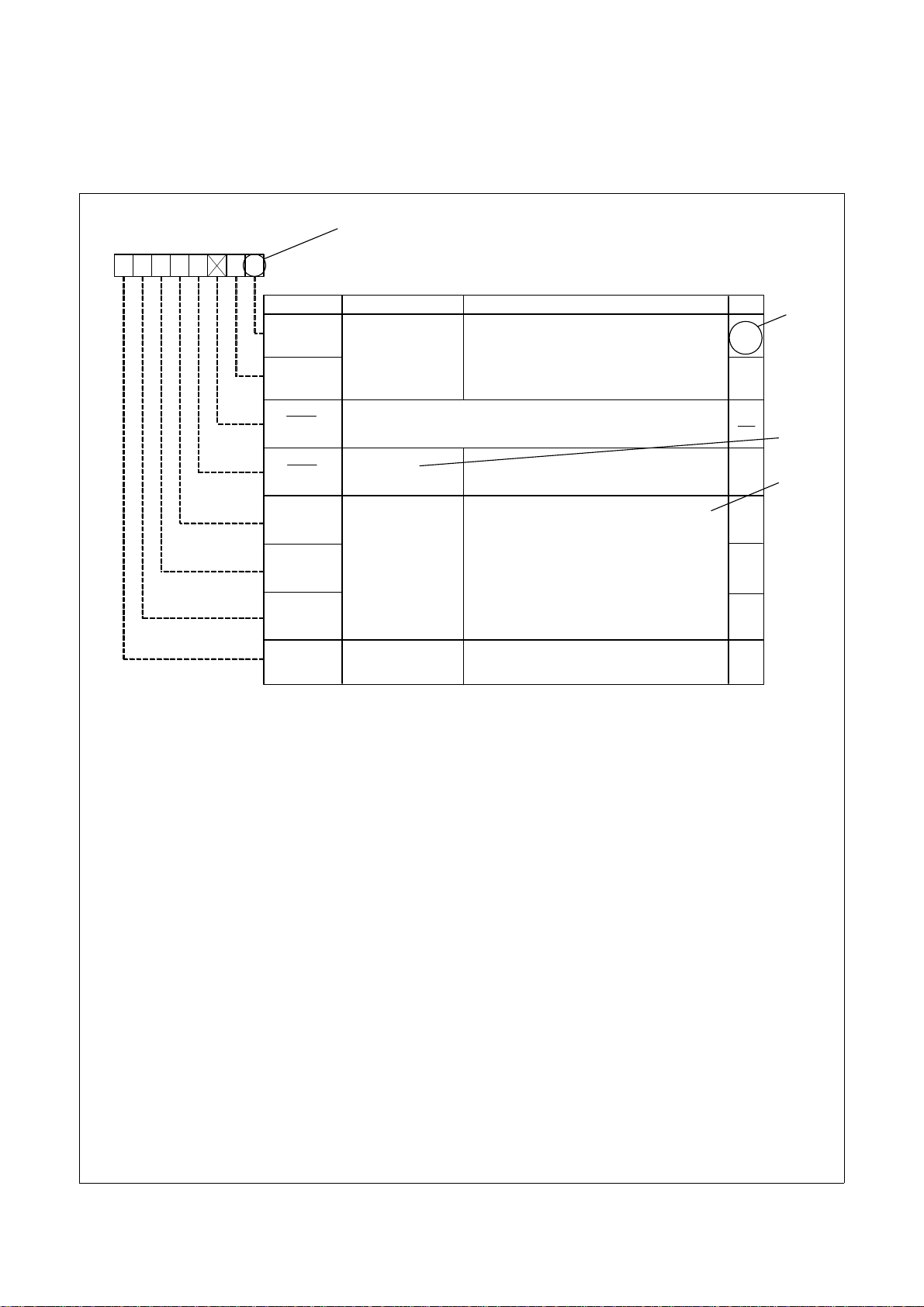

3. Register Notation

The symbols and terms used in register diagrams are described below.

XXX Register

b7 b6 b5 b4 b3 b2 b1 b0

0

XXX0

XXX1

(b2)

(b3)

XXX4

XXX5

XXX6

XXX7

*1

Symbol Address After Reset

XXX XXX 00

Bit NameBit Symbol

XXX bits

Nothing is assigned. If necessary, set to 0.

When read, the content is undefined.

Reserved bits

XXX bits

XXX bit

b1 b0

1 0: XXX

0 1: XXX

1 0: Do not set.

1 1: XXX

Set to 0.

Function varies according to the operating

mode.

0: XXX

1: XXX

Function

16

RW

RW

RW

*2

*3

RW

*4

RW

WO

RW

RO

*1

Blank: Set to 0 or 1 according to the application.

0: Set to 0.

1: Set to 1.

X: Nothing is assigned.

*2

RW: Read and write.

RO: Read only.

WO: Write only.

−: Nothing is assigned.

*3

• Reserved bit

Reserved bit. Set to specified value.

*4

• Nothing is assigned

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information

on the individual modes.

Page 7

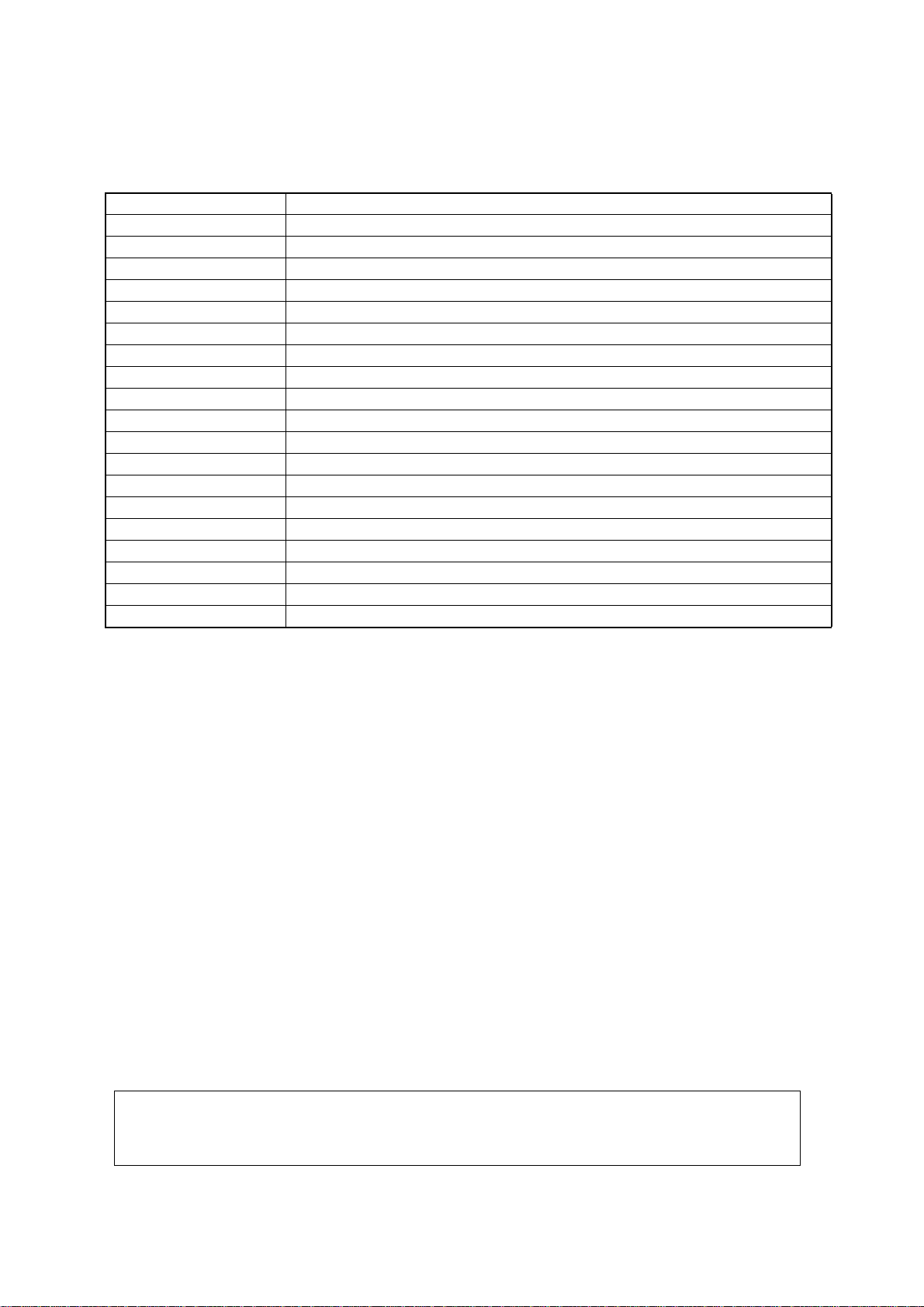

4. List of Abbreviations and Acronyms

Abbreviation Full Form

ACIA Asynchronous Communication Interface Adapter

bps bits per second

CRC Cyclic Redundancy Check

DMA Direct Memory Access

DMAC Direct Memory Access Controller

GSM Global System for Mobile Communications

Hi-Z High Impedance

IEBus Inter Equipment bus

I/O Input/Output

IrDA Infrared Data Association

LSB Least Significant Bit

MSB Most Significant Bit

NC Non-Connection

PLL Phase Locked Loop

PWM Pulse Width Modulation

SFR Special Function Registers

SIM Subscriber Identity Module

UART Universal Asynchronous Receiver/Transmitter

VCO Voltage Controlled Oscillator

All trademarks and registered trademarks are the property of their respective owners.

IEBus is a registered trademark of NEC Electronics Corporation.

Page 8

Table of Contents

Quick Reference by Address_______________________ B-1

1. Overview ______________________________________ 1

1.1 Applications ...................................................................................................................1

1.2 Performance Outline .....................................................................................................2

1.3 Block Diagram...............................................................................................................4

1.4 Product List ...................................................................................................................6

1.5 Pin Assignments..........................................................................................................11

1.6 Pin Description ............................................................................................................15

2. Central Processing Unit (CPU) ____________________ 17

2.1 Data Registers (R0, R1, R2 and R3)...........................................................................17

2.2 Address Registers (A0 and A1)...................................................................................17

2.3 Frame Base Register (FB) ..........................................................................................18

2.4 Interrupt Table Register (INTB) ...................................................................................18

2.5 Program Counter (PC) ................................................................................................18

2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) ......................................18

2.7 Static Base Register (SB) ...........................................................................................18

2.8 Flag Register (FLG) ....................................................................................................18

2.8.1 Carry Flag (C Flag) ..............................................................................................18

2.8.2 Debug Flag (D Flag) ............................................................................................18

2.8.3 Zero Flag (Z Flag) ...............................................................................................18

2.8.4 Sign Flag (S Flag) ................................................................................................18

2.8.5 Register Bank Select Flag (B Flag)...................................................................... 18

2.8.6 Overflow Flag (O Flag).........................................................................................18

2.8.7 Interrupt Enable Flag (I Flag) ...............................................................................18

2.8.8 Stack Pointer Select Flag (U Flag)....................................................................... 18

2.8.9 Processor Interrupt Priority Level (IPL)................................................................18

2.8.10 Reserved Area ...................................................................................................18

3. Memory ______________________________________ 19

4. Special Function Registers (SFRs) _________________ 20

A-1

Page 9

5. Reset________________________________________ 26

5.1 Hardware Reset ..........................................................................................................26

5.1.1 Hardware Reset 1 ................................................................................................26

5.1.2 Hardware Reset 2 ................................................................................................26

5.2 Software Reset............................................................................................................27

5.3 Watchdog Timer Reset................................................................................................27

5.4 Oscillation Stop Detection Reset.................................................................................27

5.5 Voltage Detection Circuit.............................................................................................29

5.5.1 Voltage Down Detection Interrupt .......................................................................32

5.5.2 Limitations on Exiting Stop Mode........................................................................ 34

5.5.3 Limitations on Exiting Wait Mode........................................................................34

6. Processor Mode _______________________________ 35

7. Clock Generation Circuit _________________________ 38

7.1 Main Clock ..................................................................................................................45

7.2 Sub Clock....................................................................................................................46

7.3 On-chip Oscillator Clock..............................................................................................47

7.4 PLL Clock ....................................................................................................................47

7.5 CPU Clock and Peripheral Function Clock .................................................................49

7.5.1 CPU Clock ...........................................................................................................49

7.5.2 Peripheral Function Clock (f1, f2, f8, f32, f1SIO, f2SIO, f8SIO, f32SIO, fAD, fC32) .......49

7.5.3 ClockOutput Function ..........................................................................................49

7.6 Power Control .............................................................................................................50

7.6.1 Normal Operation Mode.......................................................................................50

7.6.2 Wait Mode............................................................................................................51

7.6.3 Stop Mode...........................................................................................................53

7.7 System Clock Protective Function ..............................................................................57

7.8 Oscillation Stop and Re-oscillation Detect Function ...................................................57

7.8.1 Operation When the CM27 bit is set to "0" (Oscillation Stop Detection Reset) ...58

7.8.2 Operation When the CM27 bit is set to "1"

(Oscillation Stop and Re-oscillation Detect Interrupt) ..................58

7.8.3 How to Use Oscillation Stop and Re-oscillation Detect Function......................... 59

8. Protection ____________________________________ 60

9. Interrupt______________________________________ 61

9.1 Type of Interrupts ........................................................................................................61

9.1.1 Software Interrupts...............................................................................................62

9.1.2 Hardware Interrupts .............................................................................................63

A-2

Page 10

9.2 Interrupts and Interrupt Vector ....................................................................................64

9.2.1 Fixed Vector Tables..............................................................................................64

9.2.2 Relocatable Vector Tables ...................................................................................65

9.3 Interrupt Control ..........................................................................................................66

9.3.1 I Flag ....................................................................................................................69

9.3.2 IR Bit ....................................................................................................................69

9.3.3 ILVL2 to ILVL0 Bits and IPL .................................................................................69

9.4 Interrupt Sequence......................................................................................................70

9.4.1 Interrupt Response Time......................................................................................71

9.4.2 Variation of IPL when Interrupt Request is Accepted...........................................71

9.4.3 Saving Registers..................................................................................................72

9.4.4 Returning from an Interrupt Routine .................................................................... 74

9.5 Interrupt Priority...........................................................................................................74

9.5.1 Interrupt Priority Resolution Circuit ......................................................................74

______

9.6 INT Interrupt ................................................................................................................76

______

9.7 NMI Interrupt ...............................................................................................................77

9.8 Key Input Interrupt.......................................................................................................77

9.9 Address Match Interrupt..............................................................................................78

10. Watchdog Timer ______________________________ 80

10.1 Count Source Protective Mode .................................................................................81

11. DMAC ______________________________________ 82

11.1 Transfer Cycles.........................................................................................................87

11.2. DMA Transfer Cycles................................................................................................89

11.3 DMA Enable...............................................................................................................90

11.4 DMA Request ............................................................................................................90

11.5 Channel Priority and DMA Transfer Timing .............................................................. 91

12. T imer _______________________________________ 92

12.1 Timer A.....................................................................................................................94

12.1.1. Timer Mode.......................................................................................................97

12.1.2. Event Counter Mode.........................................................................................98

12.1.3. One-shot Timer Mode .....................................................................................103

12.1.4. Pulse Width Modulation (PWM) Mode............................................................105

12.2 Timer B...................................................................................................................108

12.2.1 Timer Mode ..................................................................................................... 111

12.2.2 Event Counter Mode........................................................................................ 112

12.2.3 Pulse Period and Pulse Width Measurement Mode .......................................113

12.2.4 A/D Trigger Mode............................................................................................ 115

A-3

Page 11

12.3 Three-phase Motor Control Timer Function ............................................................ 117

12.3.1 Position-data-retain Function ...........................................................................128

12.3.2 Three-phase/Port Output Switch Function....................................................... 130

13. Serial I/O ___________________________________ 132

13.1. UARTi (i=0 to 2)......................................................................................................132

13.1.1. Clock Synchronous serial I/O Mode................................................................ 142

13.1.2. Clock Asynchronous Serial I/O (UART) Mode ................................................150

13.1.3 Special Mode 1 (I2C bus mode)(UART2)......................................................... 158

13.1.4 Special Mode 2 (UART2) .................................................................................168

13.1.5 Special Mode 3 (IE Bus mode )(UART2) ........................................................173

13.1.6 Special Mode 4 (SIM Mode) (UART2) ............................................................175

14. A/D Converter _______________________________ 180

14.1 Operation Modes.....................................................................................................186

14.1.1 One-Shot Mode................................................................................................ 186

14.1.2 Repeat mode ...................................................................................................188

14.1.3 Single Sweep Mode ........................................................................................190

14.1.4 Repeat Sweep Mode 0 ....................................................................................192

14.1.5 Repeat Sweep Mode 1 ....................................................................................194

14.1.6 Simultaneous Sample Sweep Mode ................................................................196

14.1.7 Delayed Trigger Mode 0...................................................................................199

14.1.8 Delayed Trigger Mode 1...................................................................................205

14.2 Resolution Select Function .....................................................................................211

14.3 Sample and Hold..................................................................................................... 211

14.4 Power Consumption Reducing Function................................................................. 211

14.5 Output Impedance of Sensor under A/D Conversion.............................................. 212

15. CRC Calculation Circuit _______________________ 213

15.1. CRC Snoop ............................................................................................................ 213

16. Programmable I/O Ports _______________________ 216

16.1 Port Pi Direction Register (PDi Register, i = 1, 6 to 10)........................................... 216

16.2 Port Pi Register (Pi Register, i = 1, 6 to 10) ............................................................216

16.3 Pull-up Control Register 0 to Pull-up Control Register 2

16.4 Port Control Register...............................................................................................217

(PUR0 to PUR2 Registers)...

216

16.5 Pin Assignment Control register (PACR).................................................................217

16.6 Digital Debounce function .......................................................................................217

17. Flash Memory Version_________________________ 230

17.1 Flash Memory Performance....................................................................................230

17.1.1 Boot Mode....................................................................................................... 231

A-4

Page 12

17.2 Memory Map ...........................................................................................................232

17.3 Functions To Prevent Flash Memory from Rewriting...............................................235

17.3.1 ROM Code Protect Function............................................................................235

17.3.2 ID Code Check Function..................................................................................235

17.4 CPU Rewrite Mode .................................................................................................237

17.4.1 EW0 Mode .......................................................................................................238

17.4.2 EW1 Mode .......................................................................................................238

17.5 Register Description................................................................................................239

17.5.1 Flash memory control register 0 (FMR0) .........................................................239

17.5.2 Flash memory control register 1 (FMR1) .........................................................240

17.5.3 Flash memory control register 4 (FMR4) .........................................................240

17.6 Precautions in CPU Rewrite Mode..........................................................................245

17.6.1 Operation Speed..............................................................................................245

17.6.2 Prohibited Instructions .....................................................................................245

17.6.3 Interrupts..........................................................................................................245

17.6.4 How to Access .................................................................................................245

17.6.5 Writing in the User ROM Space.......................................................................245

17.6.6 DMA Transfer...................................................................................................246

17.6.7 Writing Command and Data.............................................................................246

17.6.8 Wait Mode........................................................................................................246

17.6.9 Stop Mode........................................................................................................246

17.6.10

Low Power Consumption Mode and On-chip Oscillator-Low Power Consumption Mode ...

246

17.7 Software Commands...............................................................................................247

17.7.1 Read Array Command (FF16) ..........................................................................247

17.7.2 Read Status Register Command (7016)...........................................................247

17.7.3 Clear Status Register Command (5016)...........................................................248

17.7.4 Program Command (4016) ...............................................................................248

17.7.5 Block Erase......................................................................................................249

17.8 Status Register........................................................................................................251

17.8.1 Sequence Status (SR7 and FMR00 Bits ) .......................................................251

17.8.2 Erase Status (SR5 and FMR07 Bits) ...............................................................251

17.8.3 Program Status (SR4 and FMR06 Bits)...........................................................251

17.8.4 Full Status Check.............................................................................................252

17.9 Standard Serial I/O Mode........................................................................................254

17.9.1 ID Code Check Function..................................................................................254

17.9.2 Example of Circuit Application in Standard Serial I/O Mode............................258

17.10 Parallel I/O Mode ..................................................................................................260

17.10.1 ROM Code Protect Function..........................................................................260

A-5

Page 13

18. Electrical Characteristics_______________________ 261

18.1. M16C/26A, M16C/26B (Normal version)................................................................261

18.2. M16C/26T (T version) ............................................................................................280

19. Usage Notes ________________________________ 299

19.1 SFR .........................................................................................................................299

19.1.1 Precaution for 48-pin package .........................................................................299

19.1.2 Precaution for 42-pin package .........................................................................299

19.1.3 Register Setting ...............................................................................................299

19.2 PLL Frequency Synthesizer ....................................................................................300

19.3 Power Control .........................................................................................................301

19.4 Protect.....................................................................................................................303

19.5 Interrupts ................................................................................................................. 304

19.5.1 Reading address 0000016....................................................................................................304

19.5.2 Setting the SP ..................................................................................................304

19.5.3 The NMI Interrupt.............................................................................................304

19.5.4 Changing the Interrupt Generation Factor .......................................................304

19.5.5 INT Interrupt.....................................................................................................305

19.5.6 Rewrite the Interrupt Control Register .............................................................306

19.5.7 Watchdog Timer Interrupt.................................................................................306

19.6 DMAC......................................................................................................................307

19.6.1 Write to DMAE Bit in DMiCON Register ..........................................................307

19.7 Timer .......................................................................................................................308

19.7.1 Timer A.............................................................................................................308

19.7.2 Timer B............................................................................................................. 311

19.7.3 Three-phase Motor Control Timer Function .....................................................312

19.8 Serial I/O .................................................................................................................313

19.8.1 Clock-Synchronous Serial I/O..........................................................................313

19.8.2 Serial I/O (UART Mode)...................................................................................314

19.9 A/D Converter..........................................................................................................315

19.10 Programmable I/O Ports .......................................................................................317

_______

______

19.11 Electric Characteristic Differences Between Mask ROM

and Flash Memory Version Microcomputers..................318

19.12 Mask ROM Version ............................................................................................... 319

19.12.1 Internal ROM area .........................................................................................319

19.12.2 Reserve bit.....................................................................................................319

A-6

Page 14

19.13 Flash Memory Version ..........................................................................................320

19.13.1 Functions to Inhibit Rewriting Flash Memory .................................................320

19.13.2 Stop mode......................................................................................................320

19.13.3 Wait mode......................................................................................................320

19.13.4

19.13.5 Writing command and data ............................................................................320

19.13.6 Program Command........................................................................................320

19.13.7 Operation speed ............................................................................................320

19.13.8 Instructions prohibited in EW0 Mode .............................................................320

19.13.9 Interrupts........................................................................................................321

19.13.10 How to access..............................................................................................321

19.13.11 Writing in the user ROM area.......................................................................321

19.13.12 DMA transfer ................................................................................................321

19.13.13 Regarding Programming/Erasure Times and Execution Time.....................321

19.13.14 Definition of Programming/Erasure Times ...................................................322

19.13.15

19.13.16 Boot Mode....................................................................................................322

19.14 Noise .....................................................................................................................323

19.15 Instruction for a Device Use ..................................................................................324

Low power dissipation mode, on-chip oscillator low power dissipation mode...

Flash Memory Version Electrical Characteristics 10,000 E/W cycle product ..

320

322

Appendix 1. Package Dimensions___________________ 325

Appendix 2. Functional Difference __________________ 326

Appendix 2.1 Differences between M16C/26A, M16C/26B, and M16C/26T...................326

Appendix 2.2 Differences between M16C/26A Group and M16C/26 Group ...................327

Register Index __________________________________ 328

A-7

Page 15

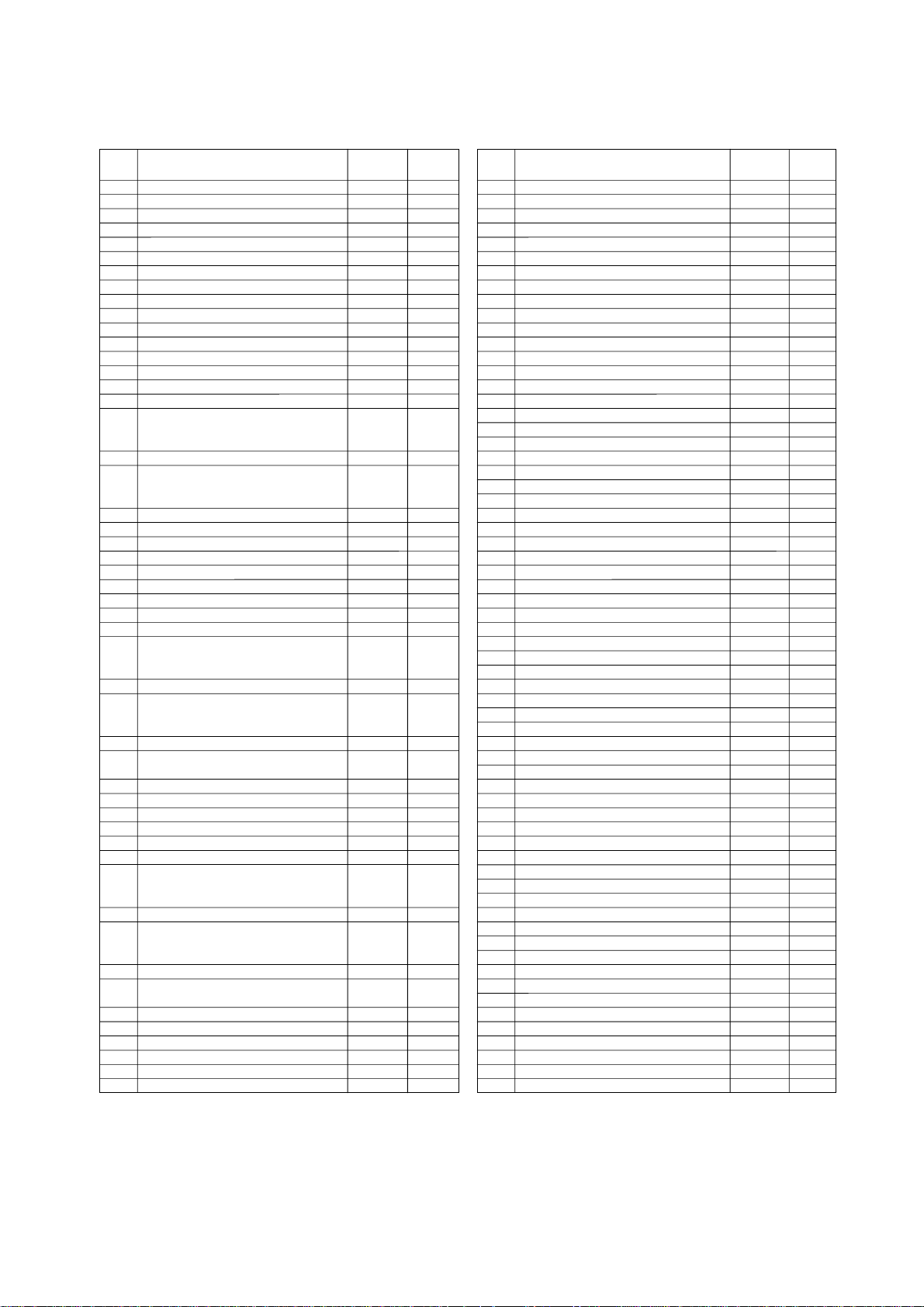

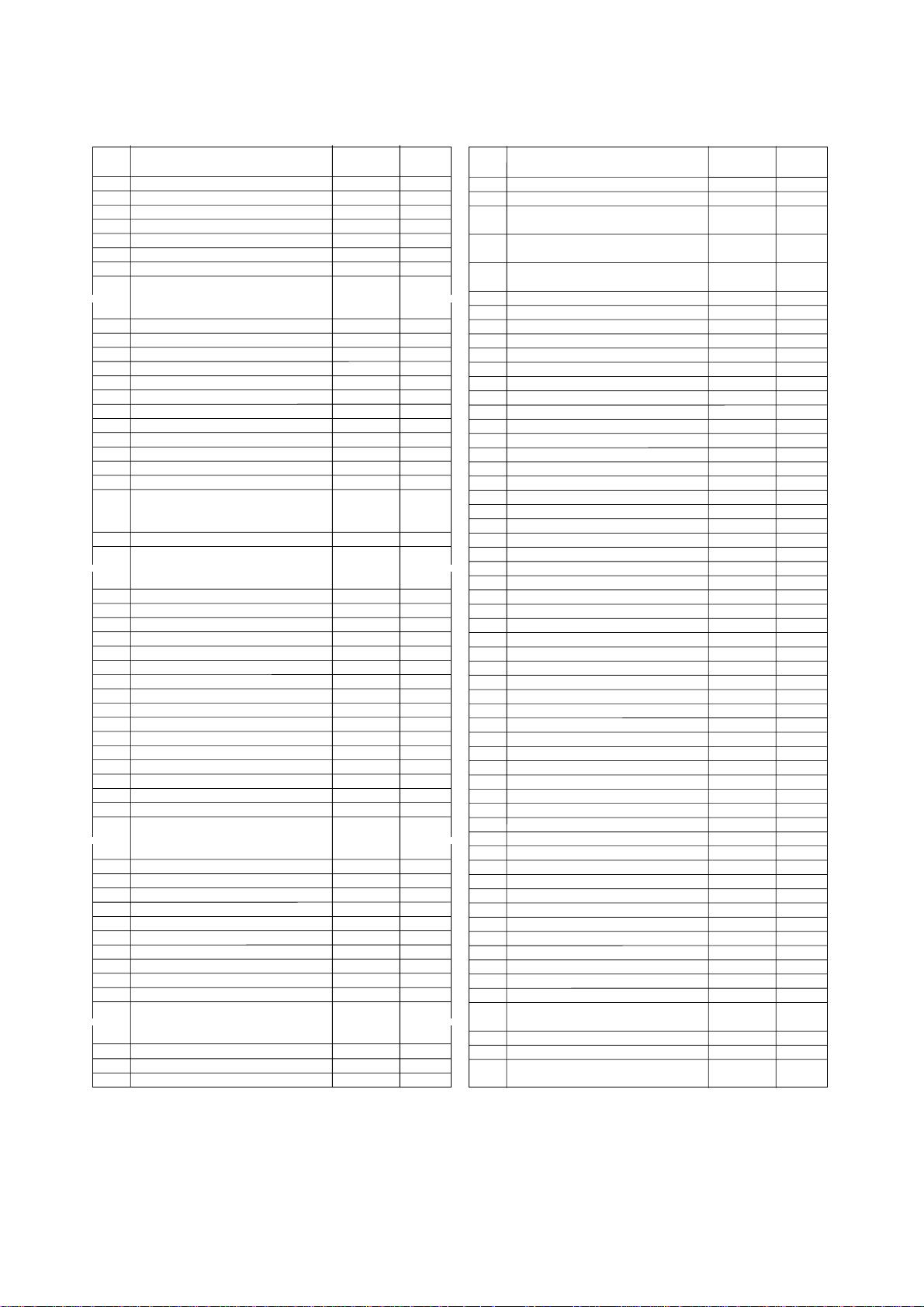

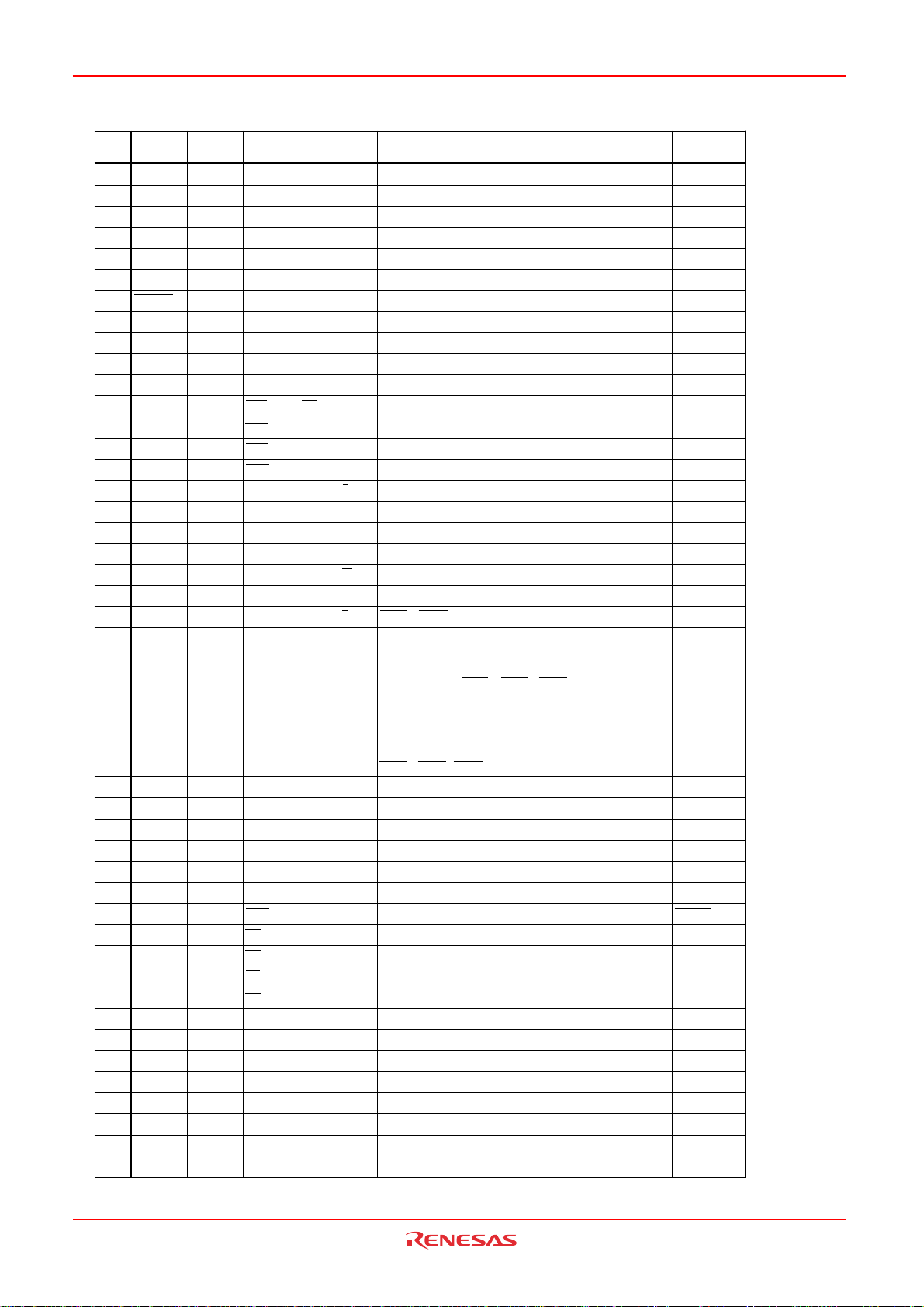

Quick Reference by Address

Address

000016

000116

000216

000316

Processor mode register 0 PM0

000416

Processor mode register 1 PM1

000516

System clock control register 0 CM0

000616

System clock control register 1 CM1

000716

000816

000916

Address match interrupt enable register AIER

000A16

Protect register PRCR

000B16

000C16

Oscillation stop detection register CM2

000D16

000E16

Watchdog timer start register WDTS

000F16

Watchdog timer control register WDC

001016

Address match interrupt register 0 RMAD0

001116

001216

001316

001416

Address match interrupt register 1 RMAD1

001516

001616

001716

001816

001916

Voltage detection register 1 VCR1

001A16

Voltage detection register 2 VCR2

001B16

001C16

PLL control register 0 PLC0

001D16

001E16

Processor mode register 2 PM2

001F16

Voltage down detection interrupt register D4INT

002016

002116

DMA0 source pointer SAR0

002216

002316

002416

DMA0 destination pointer DAR0

002516

002616

002716

002816

DMA0 transfer counter TCR0

002916

002A16

002B16

002C16

DMA0 control register DM0CON

002D16

002E16

002F16

003016

003116

DMA1 source pointer SAR1

003216

003316

003416

003516

DMA1 destination pointer DAR1

003616

003716

003816

DMA1 transfer counter TCR1

003916

003A16

003B16

003C16

DMA1 control register DM1CON

003D16

003E16

003F16

NOTE:

1. The blank areas are reserved and cannot be accessed by users.

Register Symbol Page

35

35

40

41

79

60

42

81

81

79

79

30

30

44

36, 43

30

81

86

86

85

86

86

86

85

Address

004016

004116

004216

004316

INT3 interrupt control register INT3IC

004416

004516

004616

004716

004816

INT5 interrupt control register INT5IC

004916

INT4 interrupt control register INT4IC

004A16

UART2 Bus collision detection interrupt control register

004B16

DMA0 interrupt control register DM0IC

004C16

DMA1 interrupt control register DM1IC

004D16

Key input interrupt control register KUPIC

004E16

A/D conversion interrupt control register ADIC

004F16

UART2 transmit interrupt control register

005016

UART2 receive interrupt control register

005116

UART0 transmit interrupt control register

005216

UART0 receive interrupt control register

005316

UART1 transmit interrupt control register

005416

UART1 receive interrupt control register

005516

Timer A0 interrupt control register TA0IC

005616

Timer A1 interrupt control register TA1IC

005716

Timer A2 interrupt control register TA2IC

005816

Timer A3 interrupt control register TA3IC

005916

Timer A4 interrupt control register TA4IC

005A16

Timer B0 interrupt control register TB0IC

005B16

Timer B1 interrupt control register TB1IC

005C16

Timer B2 interrupt control register TB2IC

005D16

INT0 interrupt control register INT0IC

005E16

INT1 interrupt control register INT1IC

005F16

INT2 interrupt control register INT2IC

006016

006116

006216

006316

006416

006516

006616

006716

006816

006916

006A16

006B16

006C16

006D16

006E16

006F16

007016

007116

007216

007316

007416

007516

007616

007716

007816

007916

007A16

007B16

007C16

007D16

007E16

007F16

Register Symbol Page

BCNIC

S2TIC

S2RIC

S0TIC

S0RIC

S1TIC

S1RIC

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

67

B-1

Page 16

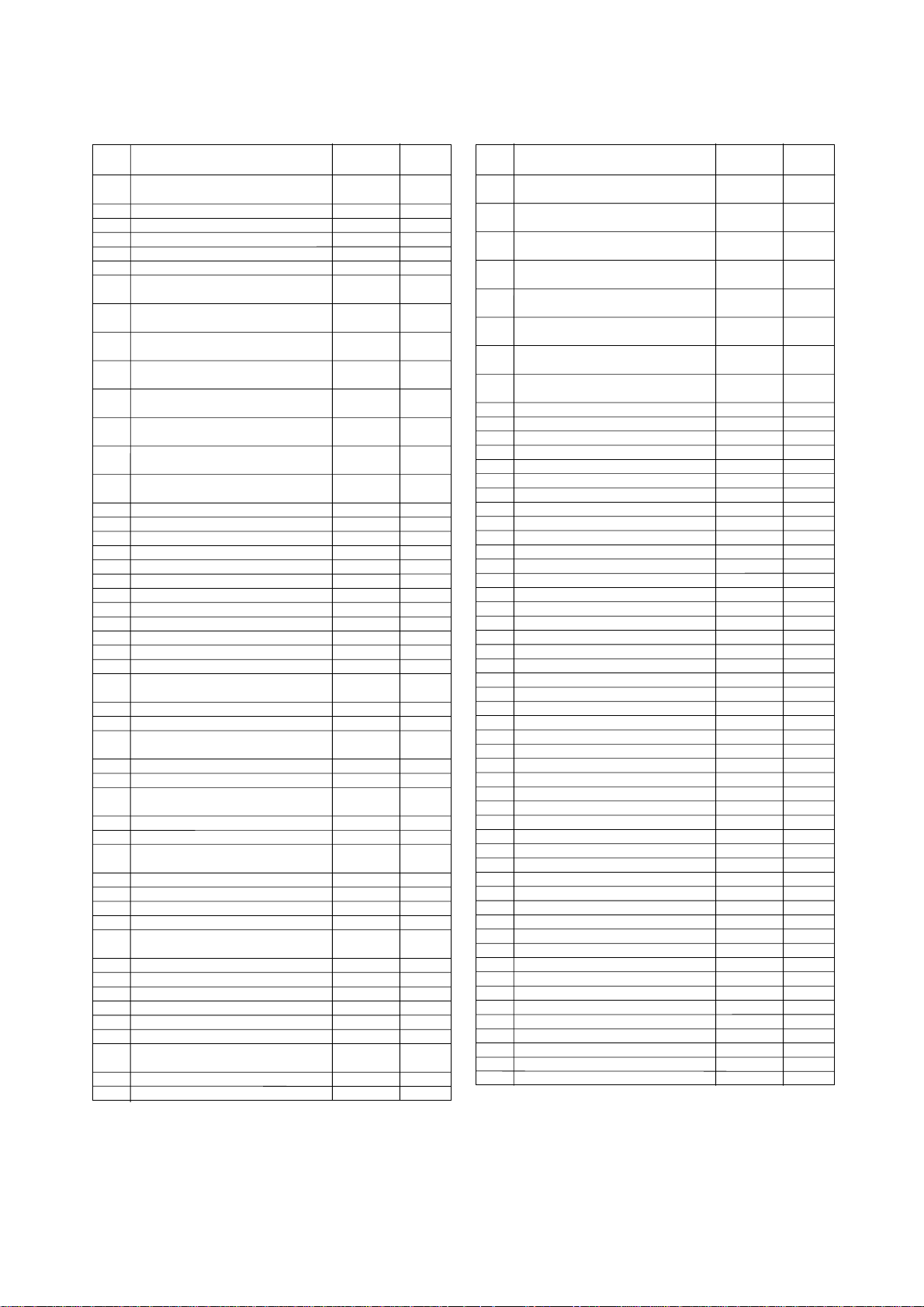

Quick Reference by Address

Address

0080

16

0081

16

0082

16

0083

16

0084

16

0085

16

0086

16

01B0

16

01B1

16

01B2

16

01B3

16

Flash memory control register 4 FMR4

01B4

16

01B5

16

Flash memory control register 1 FMR1

01B6

16

01B7

16

Flash memory control register 0 FMR0

01B8

16

01B9

16

01BA

16

01BB

16

01BC

16

01BD

16

01BE

16

01BF

16

0250

16

0251

16

0252

16

0253

16

0254

16

0255

16

0256

16

0257

16

0258

16

0259

16

025A

16

Three phase protect control register TPRC

025B

16

025C

16

On-chip oscillator control register ROCR

025D

16

Pin assignment control register PACR

025E

16

Peripheral clock select register PCLKR

025F

16

02E0

16

02E1

16

02E2

16

02E3

16

02E4

16

02E5

16

02E6

16

02E7

16

02E8

16

02E9

16

033D

16

033E

16

NMI digital debounce register NDDR

033F

16

7

digital debounce register P17DDR

P1

NOTES:

1. The blank areas are reserved and cannot be accessed by users.

2. This register is included in the flash memory version.

Register Symbol Page

(2)

(2)

(2)

242

241

241

131

41

139, 226

43

227

227

Address

0340

16

0341

16

0342

16

Timer A1-1 register TA11

0343

16

0344

16

Timer A2-1 register TA21

0345

16

0346

16

Timer A4-1 register TA41

0347

16

Three-phase PWM control register 0 INVC0

0348

16

Three-phase PWM control register 1 INVC1

0349

16

Three-phase output buffer register 0 IDB0

034A

16

Three-phase output buffer register 1 IDB1

034B

16

Dead time timer DTT

034C

16

Timer B2 interrupt occurrence frequency set counter

034D

16

034E

16

Position-data-retain function contol register

034F

16

0350

16

0351

16

0352

16

0353

16

0354

16

0355

16

0356

16

0357

16

0358

16

Port function contol register PFCR

0359

16

035A

16

035B

16

035C

16

035D

16

Interrupt request cause select register 2

035E

16

Interrupt request cause select register

035F

16

0360

16

0361

16

0362

16

0363

16

0364

16

0365

16

0366

16

0367

16

0368

16

0369

16

036A

16

036B

16

036C

16

036D

16

036E

16

036F

16

0370

16

0371

16

0372

16

0373

16

UART2 special mode register 4 U2SMR4

0374

16

UART2 special mode register 3 U2SMR3

0375

16

0376

16

UART2 special mode register 2 U2SMR2

0377

16

UART2 special mode register U2SMR

0378

16

UART2 transmit/receive mode register

UART2 bit rate generator

0379

16

037A

16

UART2 transmit buffer register

037B

16

UART2 transmit/receive control register 0

037C

16

UART2 transmit/receive control register 1

037D

16

037E

16

UART2 receive buffer register

037F

16

Register Symbol Page

ICTB2

PDRF

IFSR2A

IFSR

U2MR

U2BRG

U2TB

U2C0

U2C1

U2RB

122

122

122

119

120

121

121

121

122

129

131

68

68, 76

141

141

140

140

137

136

136

138

139

136

B-2

Page 17

Quick Reference by Address

Address

Count start flag TABSR

038016

Clock prescaler reset flag CPSRF

038116

One-shot start flag ONSF

038216

Trigger select register TRGSR

038316

Up-down flag UDF

038416

038516

038616

Timer A0 register TA0

038716

038816

Timer A1 register TA1

038916

038A16

Timer A2 register TA2

038B16

038C16

Timer A3 register TA3

038D16

038E16

Timer A4 register TA4

038F16

039016

Timer B0 register TB0

039116

039216

Timer B1 register TB1

039316

039416

Timer B2 register TB2

039516

039616

Timer A0 mode register TA0MR

Timer A1 mode register TA1MR

039716

Timer A2 mode register TA2MR

039816

039916

Timer A3 mode register TA3MR

039A16

Timer A4 mode register TA4MR

Timer B0 mode register TB0MR

039B16

039C16

Timer B1 mode register TB1MR

039D16

Timer B2 mode register TB2MR

039E16

Timer B2 special mode register TB2SC

039F16

03A016

UART0 transmit/receive mode register

03A116

UART0 bit rate generator U0BRG

03A216

UART0 transmit buffer register U0TB

03A316

03A416

UART0 transmit/receive control register 0

03A516

UART0 transmit/receive control register 1

03A616

UART0 receive buffer register U0RB

03A716

03A816

UART1 transmit/receive mode register

03A916

UART1 bit rate generator U1BRG

03AA16

UART1 transmit buffer register U1TB

03AB16

03AC16

UART1 transmit/receive control register 0

03AD16

UART1 transmit/receive control register 1

03AE16

UART1 receive buffer register U1RB

03AF16

03B016

UART transmit/receive control register 2

03B116

03B216

03B316

03B416

CRC snoop address register CRCSAR

03B516

03B616

CRC mode register CRCMR

03B716

DMA0 request cause select register DM0SL

03B816

03B916

03BA16

DMA1 request cause select register DM1SL

03BB16

03BC16

CRC data register CRCD

03BD16

03BE16

CRC input register CRCIN

03BF16

NOTE:

1. The blank areas are reserved and cannot be accessed by users.

Register Symbol Page

U0MR

U0C0

U0C1

U1MR

U1C0

U1C1

UCON

95, 110,

124

r0)

96

96, 124

95

95

95, 122

95, 122

95

95, 122

110

110

110, 124

94

94, 125

94, 125

94

94, 125

109

109

109, 125

123, 185

137

136

136

138

139

136

137

136

136

138

139

136

138

214

214

84

85

214

214

Address

03C016

A/D register 0 AD0

03C116

03C216

A/D register 1 AD1

03C316

03C416

A/D register 2 AD2

03C516

03C616

A/D register 3 AD3

03C716

03C816

A/D register 4 AD4

03C916

03CA16

A/D register 5 AD5

03CB16

03CC16

A/D register 6 AD6

03CD16

03CE16

A/D register 7 AD7

03CF16

03D016

03D116

03D216

A/D trigger control register ADTRGCON

03D316

A/D convert status register 0 ADSTAT0

A/D control register 2 ADCON2

03D416

03D516

03D616

A/D control register 0 ADCON0

03D716

A/D control register 1 ADCON1

03D816

03D916

03DA16

03DB16

03DC16

03DD16

03DE16

03DF16

03E016

03E116

Port P1 register P1

03E216

03E316

Port P1 direction register PD1

03E416

03E516

03E616

03E716

03E816

03E916

03EA16

03EB16

03EC16

Port P6 register P6

03ED16

Port P7 register P7

Port P6 direction register PD6

03EE16

Port P7 direction register PD7

03EF16

03F016

Port P8 register P8

03F116

Port P9 register P9

03F216

Port P8 direction register PD8

03F316

Port P9 direction register PD9

Port P10 register P10

03F416

03F516

03F616

Port P10 direction register PD10

03F716

03F816

03F916

03FA16

03FB16

03FC16

Pull-up control register 0 PUR0

03FD16

Pull-up control register 1 PUR1

03FE16

Pull-up control register 2 PUR2

03FF16

Port control register PCR

Register Symbol Page

184

184

184

184

184

184

184

184

183

184

182

182

182

224

223

224

224

223

223

224

224

223

223

224

223

225

225

225

226

B-3

Page 18

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

1. Overview

The M16C/26A Group (M16C/26A, M16C/26B, M16C/26T) is a single-chip control MCU, fabricated using

high-performance silicon gate CMOS technology, embedding the M16C/60 Series CPU core. The M16C/

26A Group (M16C/26A, M16C/26B, M16C/26T) is housed in 42-pin and 48-pin plastic molded packages.

This MCU combines advanced instruction manipulation capabilities to process complex instructions by less

bytes and execute instructions at higher speed. The M16C/26A Group (M16C/26A, M16C/26B, M16C/

26T) has a multiplier and DMAC adequate for office automation, communication devices and industrial

equipment, and other high-speed processing applications. The M16C/26A and M16C/26B have normal

version. The M16C/26T has T version and V version.

1.1 Applications

Audio, cameras, office/communications/portable/ equipment, air-conditioning equipment, home appliances, etc.

0020-2020B90JER

page 1

923fo7002,51.beF00.2.veR

Page 19

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

1. Overview

1.2 Performance Outline

Table 1.1 and 1.2 outline performance overview of the M16C/26A Group (M16C/26A, M16C/26B, M16C/

26T).

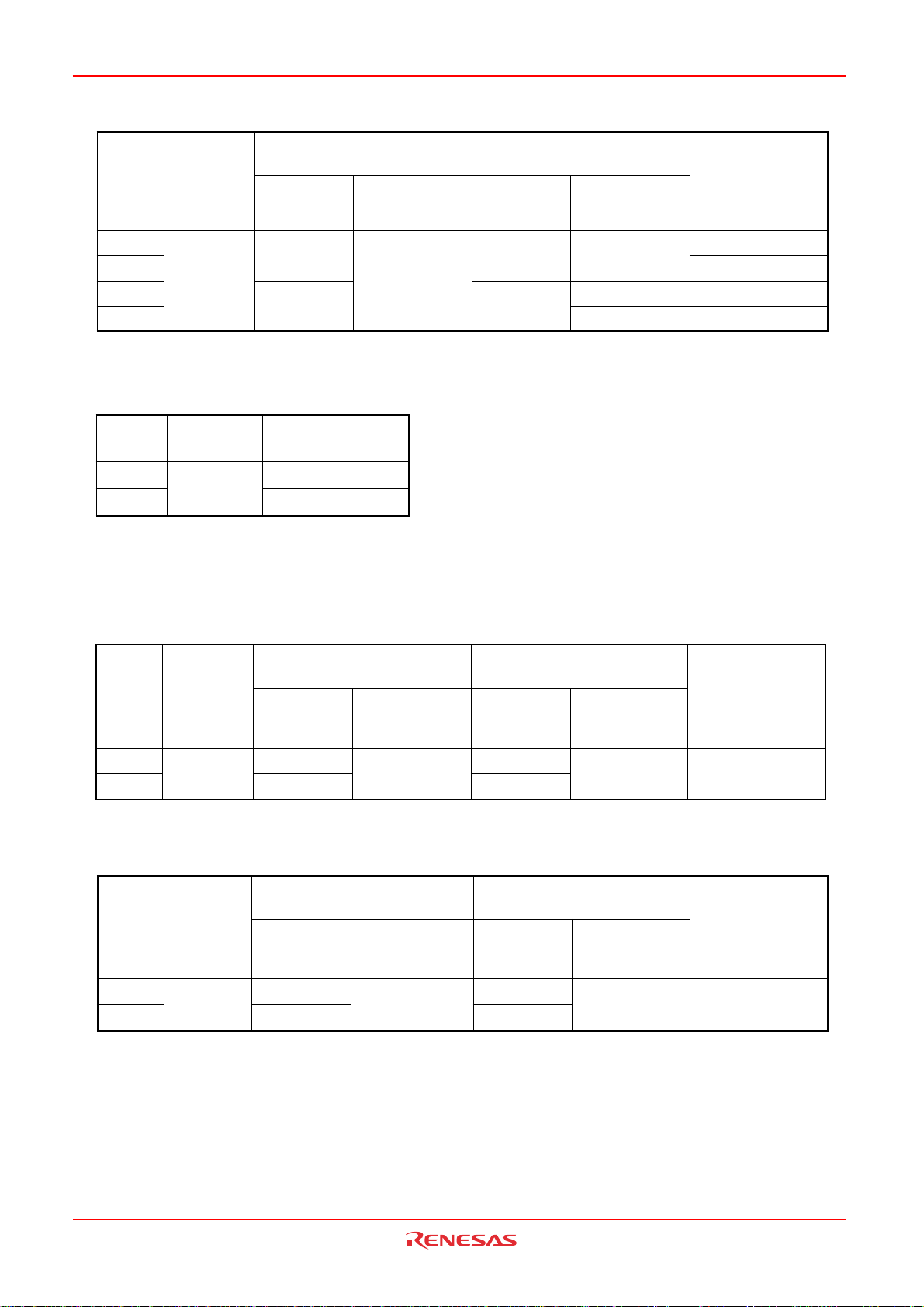

Table 1.1. M16C/26A Group(M16C/26A, M16C/26B, M16C/26T) Performance (48-Pin Package)

Item Specification

CPU Basic instructions 91 instructions

Minimun instruction

execution time

Operating mode Single-chip mode

Address space 1 Mbyte

Memory capacity ROM/RAM: See 1.4 Product Information

Peripheral I/O ports 39 I/O pins

Function Multifunction timers TimerA:16 bits x 5 channels, TimerB:16 bits x 3 channels

Serial I/O 2 channels (UART, clock synchronous serial I/O)

A/D converter 10 bit A/D Converter : 1 circuit, 12 channels

DMAC 2 channels

CRC calcuration circuit

Watchdog timer 15 bits x 1 channel (with prescaler)

Interrupts 20 internal and 8 external sources, 4 software sources,

Clock generation circuit 4 circuits

Oscillation stop detection Main clock oscillation stop, re-oscillation detection function

Voltage detection circuit On-chip (M16C/26A, M16C/26B), not on-chip (M16C/26T)

Electrical Power supply voltage VCC = 4.2 to 5.5 V (f(BCLK) = 24 MHZ)

Characteristics V

Power consumption 20 mA (Vcc = 5 V, f(BCLK) = 24 MHz) (M16C/26B)

Flash Memory Programming /erasure 2.7 to 5.5 V (M16C/26A, M16C/26B)

Version voltage 3.0 to 5.5 V (M16C/26T(T-ver.)) 4.2 to 5.5 V (M16C/26T(V-ver.))

Programming /erasure

endurance

Operating Ambient Temperature -20 to 85°C / -40 to 85°C

Package 48-pin plastic molded QFP

NOTES:

1. IEBus is a trademark of NEC Electronics Corporation.

2. See Tables 1.7 to 1.10 Product Code for the program and erase endurance, and operating ambient temperature.

3. The PLL frequency synthesizer is used to run the M16C/26B at f(BCLK) = 24 MHz.

41.7 ns (f(BCLK) = 24MHZ

50 ns (f(BCLK) = 20MHZ, VCC = 3.0 to 5.5 V)

100 ns (f(BCLK) = 10MHZ, VCC = 2.7 to 5.5 V)

50 ns (f(BCLK) = 20MHZ, VCC = 4.2 to 5.5 V -40 to 105°C)

62.5 ns (f(BCLK) = 16MHZ, VCC = 4.2 to 5.5 V -40 to 125°C)

Three-phase motor control timer

1 channel

1 circuit (CRC-CCITT and CRC-16) with MSB/LSB selectable

Interrupt priority level: 7

Main clock oscillation circuit(*), Sub-clock oscillation circuit(*)

On-chip oscillator, PLL frequency synthesizer

(*)Equipped with a built-in feedback resister.

CC = 3.0 to 5.5 V (f(BCLK) = 20 MHZ) (M16C/26A, M16C/26B)

VCC = 2.7 to 5.5 V (f(BCLK) = 10 MHZ)

VCC = 3.0 to 5.5 V (M16C/26T(T-ver.))

VCC = 4.2 to 5.5 V (M16C/26T(V-ver.))

16 mA (Vcc = 5 V, f(BCLK) = 20 MHz)

25 µA (f(XCIN) = 32 KHz on RAM)

3 µA (Vcc = 3 V, f(XCIN) = 32 KHz, in wait mode)

0.7 µA (Vcc = 3 V, in stop mode)

100 times (all area) or 1,000 times (block 0 to 3)

/ 10,000 times

-40 to 85°C (M16C/26T(T-ver.))

-40 to 105°C / -40 to 125°C (M16C/26T(V-ver.))

(UART, clock synchronous, I2C bus, or IEBus

(3)

, VCC = 4.2 to 5.5 V) (M16C/26B)

(block A, block B)

(2)

(M16C/26A, M16C/26B, M16C/26T(T-ver.))

(M16C/26A , M16C/26B)

(M16C/26T(V-ver.))

(M16C/26T(V-ver.))

(1)

)

(3)

(2)

(M16C/26A , M16C/26B)

(M16C/26B)

page 2

0020-2020B90JER

923fo7002,51.beF00.2.veR

Page 20

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

1. Overview

Table 1.2. Performance outline of M16C/26A group (M16C/26A, M16C/26B) (42-pin package)

Item Performance

CPU Basic instructions 91 instructions

Minimun instruction

execution time

41.7 ns (f(BCLK) = 24 MHz

50 ns (f(BCLK) = 20 MHZ, V

100 ns (f(BCLK) = 10 MHZ, V

Operation mode Single-chip mode

Address space 1M byte

Memory capacity ROM/RAM: See 1.4 Product Information

Peripheral Port 33 I/O pins

function Multifunction timer Timer A: 16 bits x 5 channels, Timer B: 16 bits x 3 channels

Three-phase motor control timer

Serial I/O 1 channel (UART, clock synchronous serial I/O)

1 channel (UART, clock synchronous, I2C bus, or IEBus

A/D converter 10 bit A/D converter: 1 circuit, 10 channels

DMAC 2 channels

CRC calcuration circuit 1 circuits (CRC-CCITT and CRC-16) with MSB/LSB selectable

Watchdog timer 15 bits x 1 channel (with prescaler)

Interrupt 18 internal and 8 external sources, 4 software sources,

Interrupt priority level: 7

Clock generation circuit 4 circuits

Main clock(*), Sub-clock(*)

On-chip oscillator, PLL frequency synthesizer

(*)Equipped with a built-in feedback resister.

Oscillation stop detection Main clock oscillation stop, re-oscillation detection function

Voltage detection circuit On-chip

Electrical Supply voltage VCC = 4.2 to 5.5 V (f(BCLK) = 24 MHZ)

Characteristics V

CC = 3.0 to 5.5 V (f(BCLK) = 20 MHZ) (M16C/26A, M16C/26B)

VCC = 2.7 to 5.5 V (f(BCLK) = 10 MHZ)

Power Consumption 20 mA (Vcc = 5 V, f(BCLK) = 24 MHz) (M16C/26B)

16 mA (Vcc = 5 V, f(BCLK) = 20 MHz)

25 µA (f(XCIN) = 32 KHz on RAM)

3 µA (Vcc = 3 V, f(XCIN) = 32 KHz, in wait mode)

0.7 µA (Vcc = 3 V, in stop mode)

Flash memory Programming/erasure 2.7 to 5.5 V

voltage

Programming/erasure 100 times (all area) or 1,000 times (block 0 to 3)

endurance / 10,000 times (block A, block B)

Operating Ambient Temperature -20 to 85°C / -40 to 85°C

Package 42-pin plastic molded SSOP

NOTES:

1. IEBus is a trademark of NEC Electronics Corporation.

2. See Tables 1.7 and 1.8 Product Code for the program and erase endurance, and operating ambient temperature.

3. The PLL frequency synthesizer is used to run the M16C/26B at f(BCLK) = 24 MHz.

(3)

, VCC = 4.2 to 5.5 V (M16C/26B)

CC

= 3.0 to 5.5 V) (M16C/26A, M16C/26B)

CC

= 2.7 to 5.5 V) (M16C/26A, M16C/26B)

(1)

)

(3)

(2)

(2)

(M16C/26B)

page 3

923fo7002,51.beF00.2.veR

0020-2020B90JER

Page 21

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

1. Overview

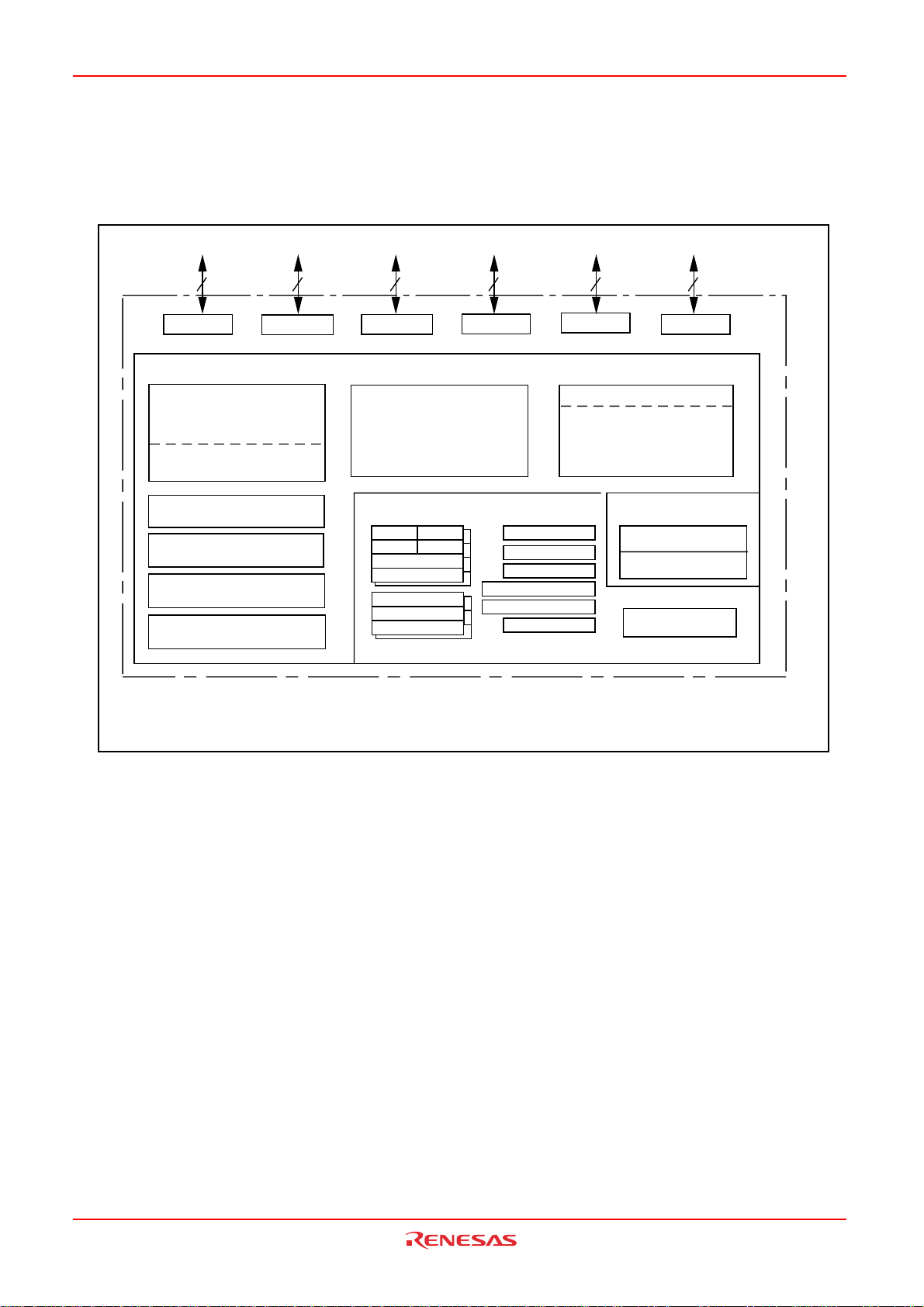

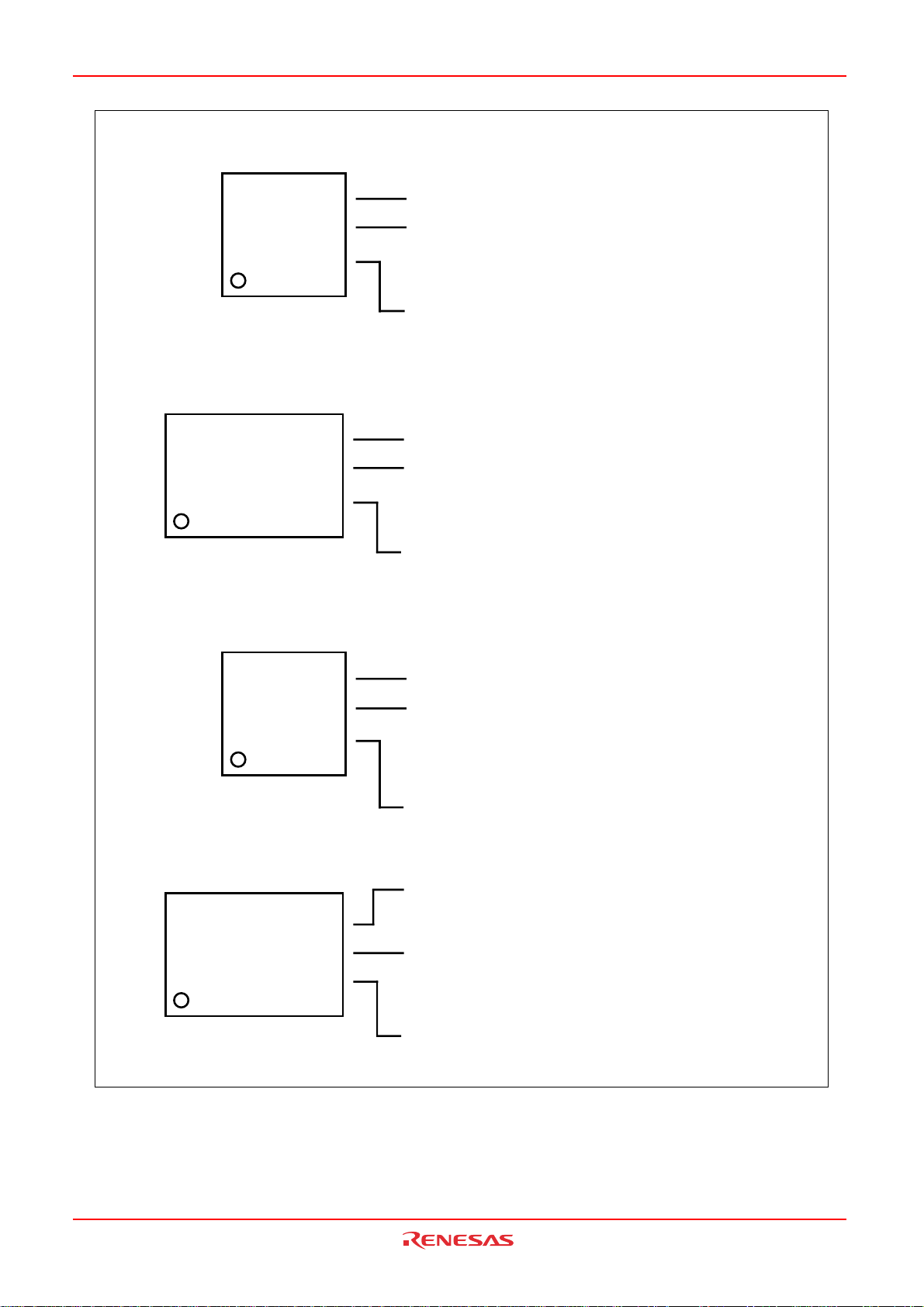

1.3 Block Diagram

Figure 1.1 and 1.2 show block diagrams of the M16C/26A Group (M16C/26A, M16C/26B, M16C/26T) 48-

pin package and 42-pin package.

3

Port P1

Peripheral functions

Timer (16-bit)

Output (timer A): 5channels

Input (timer B): 3 channels

Three-phase motor

control circuit

10-bit A/D converter

12 channels

Watchdog timer

(15 bits)

DMAC

(2 channels)

CRC calculation circuit

(CCITT, CRC-16 )

Port P6

Port P10

(1)

ROM

(2)

RAM

Multiplier

8

8

8

Port P7

UART or

clock synchronous serial I/O

(8 bits X 3 channels)

M16C/60 series CPU core

R0LR0H

R1H R1L

R2

R3

A0

A1

FB

8

Port P8

4

Port P9

Clock generation circuit

XIN-XOUT

XCIN-XCOUT

On-Chip Oscillator

PLL frequency synthesizer

Memory

SB

USP

ISP

INTB

PC

FLG

NOTES:

1: ROM size depends on the MCU type.

2: RAM size depends on the MCU type.

Figure 1.1 Block Diagram(48-pin Package)

page 4

923fo7002,51.beF00.2.veR

0020-2020B90JER

Page 22

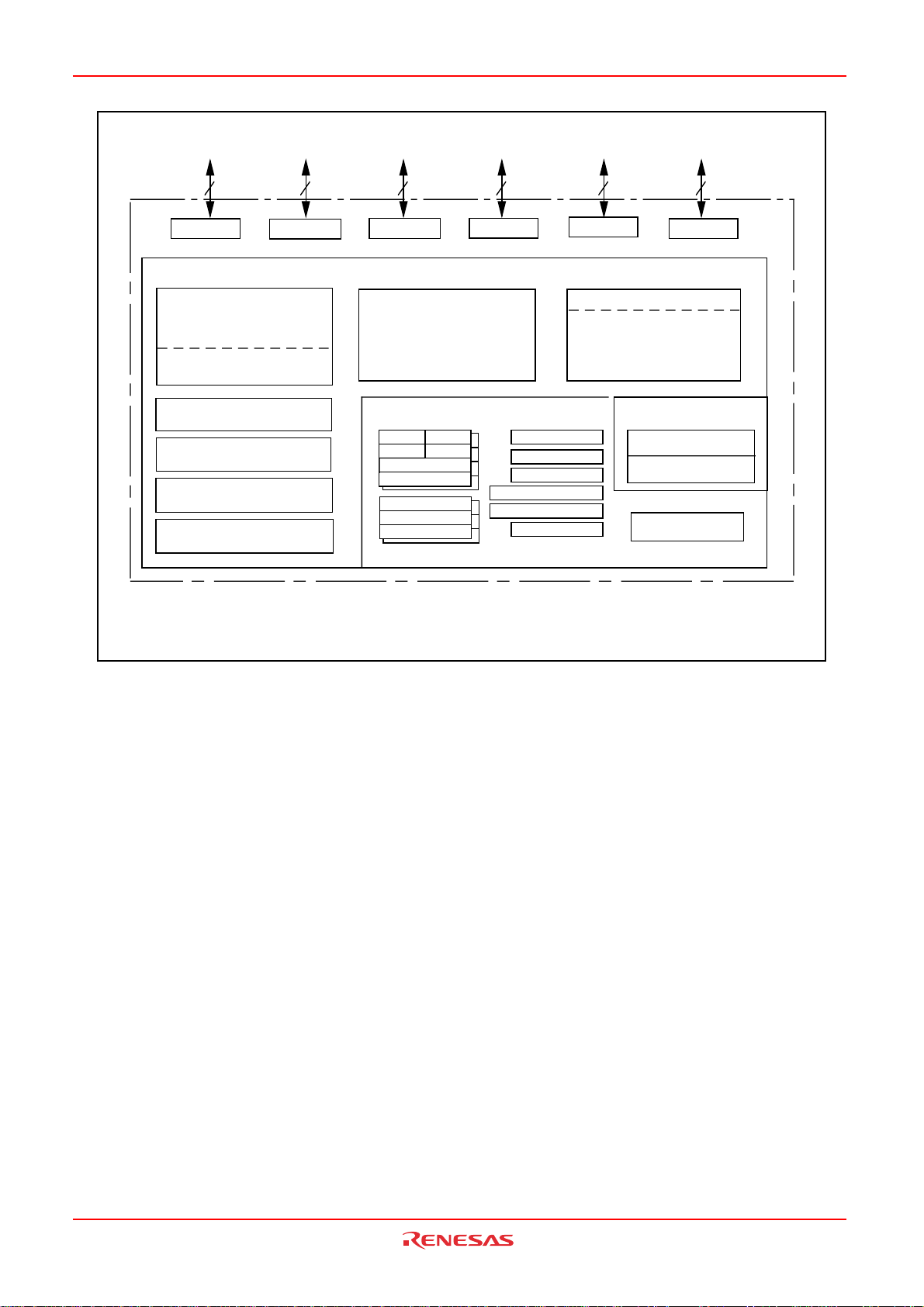

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

1. Overview

3

Port P1

Peripheral functions

Timer (16-bit)

Output (timer A): 5channels

Input (timer B): 3 channels

Three-phase motor

control circuit

10-bit A/D converter

10 channels

Watchdog timer

(15 bits)

DMAC

(2 channels)

CRC calculation circuit

(CCITT, CRC-16 )

Port P6

Port P10

(1)

ROM

(2)

RAM

Multiplier

8

4

8

Port P7

UART or

clock synchronous serial I/O

(8 bits X 2 channels)

M16C/60 series CPU core

R0LR0H

R1H R1L

R2

R3

A0

A1

FB

8

Port P8

2

Port P9

Clock generation circuit

XIN-XOUT

XCIN-XCOUT

On-Chip Oscillator

PLL frequency synthesizer

Memory

SB

USP

ISP

INTB

PC

FLG

NOTES:

1: ROM size depends on the MCU type.

2: RAM size depends on the MCU type.

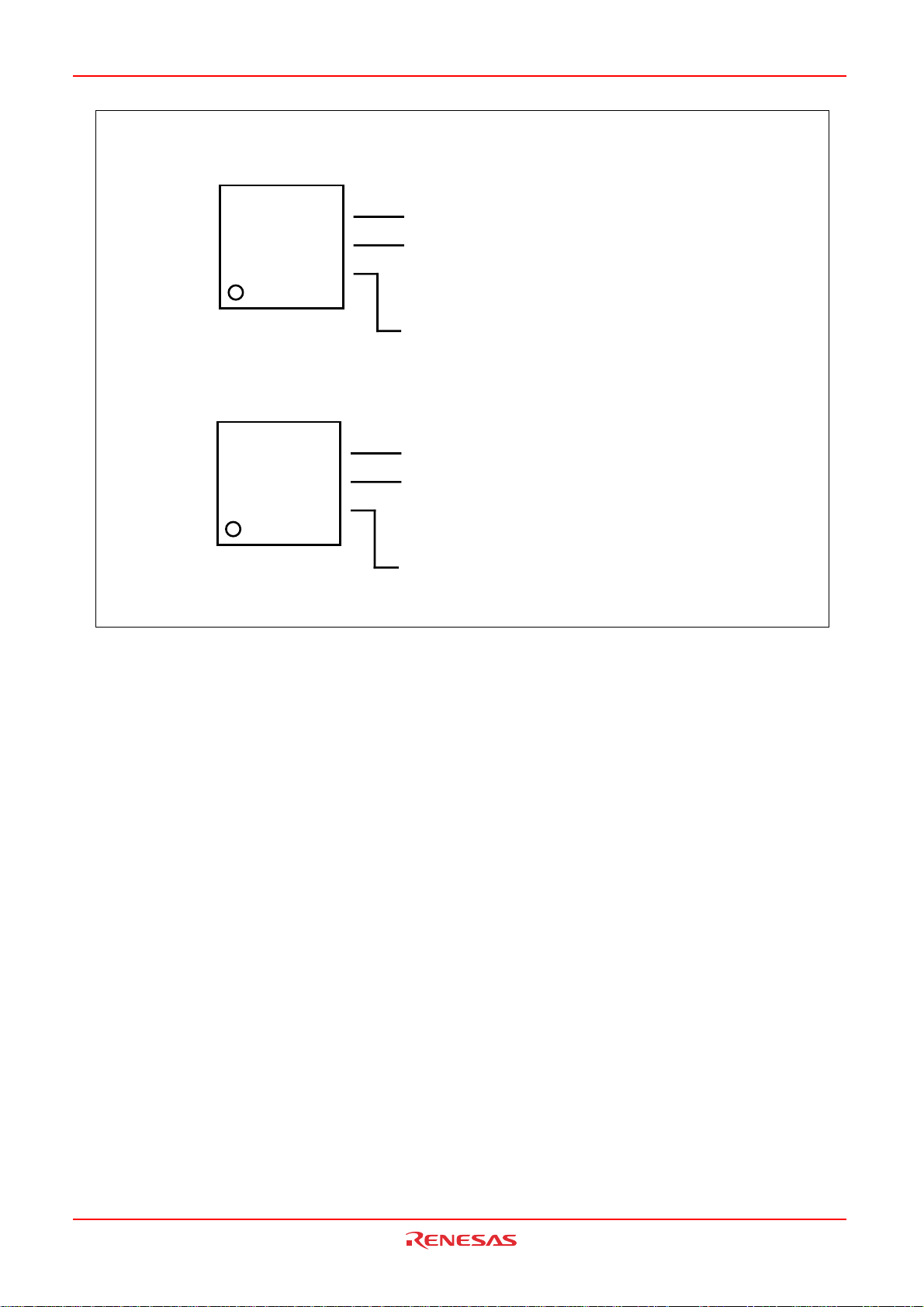

Figure 1.2 Block Diagram( 42-pin Package)

page 5

923fo7002,51.beF00.2.veR

0020-2020B90JER

Page 23

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

1. Overview

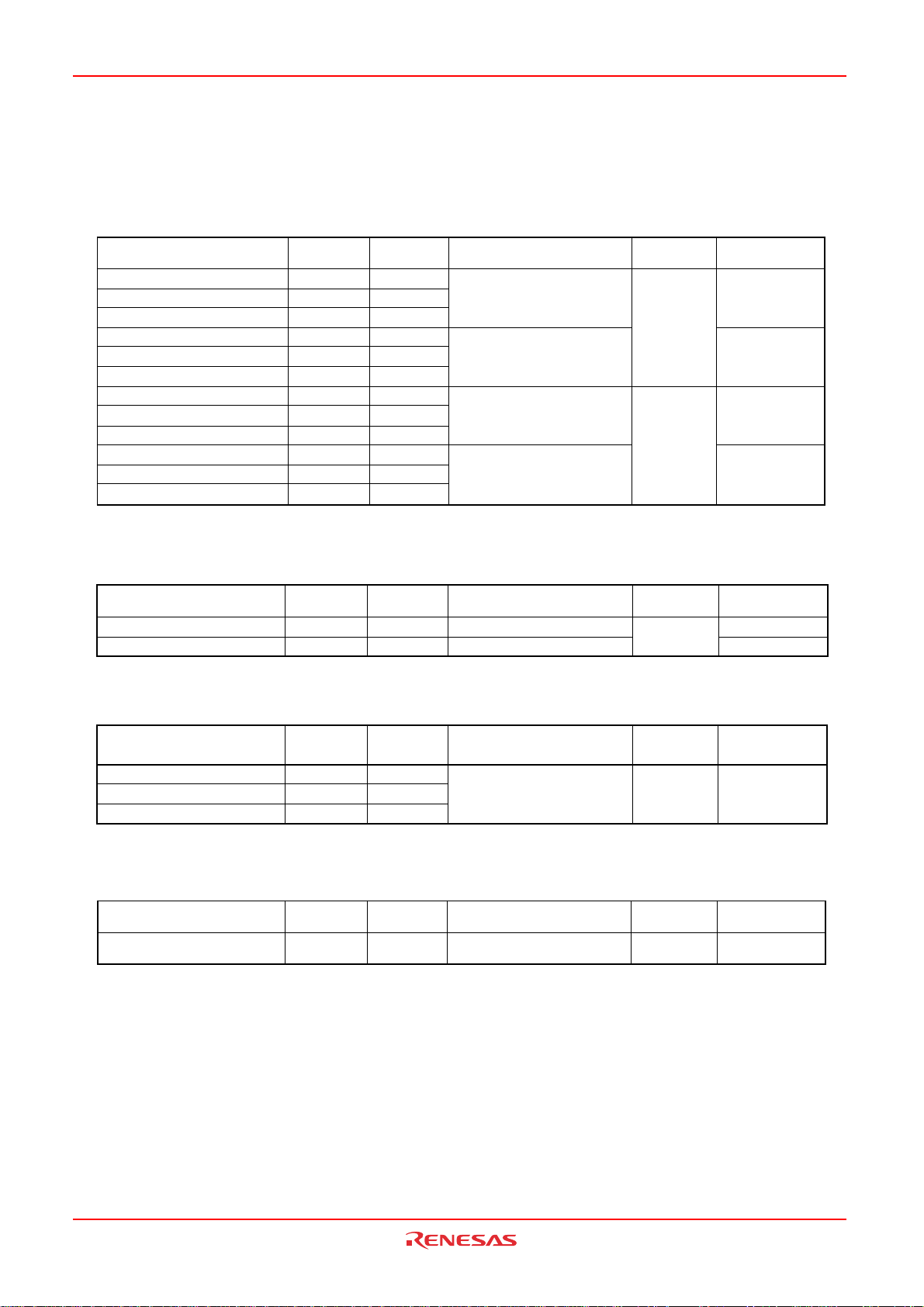

1.4 Product List

Tables 1.3 to 1.6 lists product information, Figure 1.3 shows a product numbering system, Table 1.7 lists

the product code, and Figure 1.4 shows the marking.

Table 1.3 M16C/26A Current as of Feb., 2007

rebmuNepyT

PGA3F06203M)N(K4+K42K1

PGA6F06203M)N(K4+K84K2

PGA8F06203M)N(K4+K46K2

PFA3F36203M)N(K4+K42K1

PFA6F36203M)N(K4+K84K2

PFA8F36203M)N(K4+K46K2

PGXXX-A3M06203M)N(K42K1

PGXXX-A6M06203M)N(K84K2

PGXXX-A8M06203M)N(K46K2

PFXXX-A3M36203M)N(K42K1

PFXXX-A6M36203M)N(K84K2

PFXXX-A8M36203M)N(K46K2

weN:)N(

MOR

yticapaC

MAR

yticapaC

epyTegakcaPskrameRedoCtcudorP

)A-Q6P84(A-BK8400PQLP

hsalF

yromem

)R2P24(B-AG2400PSRP9U,5U

)A-Q6P84(A-BK8400PQLP

MORksaM

)R2P24(B-AG2400PSRP5U

5U,3U

9U,7U,5U,3U

Table 1.4 M16C/26B Current as of Feb., 2007

rebmuNepyT

PGB8F06203M)N(K4+K46K2)A-Q6P84(A-BK8400PQLP

PFB8F36203M)N(K4+K46K2)R2P24(B-AG2400PSRP9U

weN:)N(

MOR

yticapaC

MAR

yticapaC

epyTegakcaPskrameRedoCtcudorP

hsalF

yromem

7U

Table 1.5 M16C/26T T-ver. Current as of Feb., 2007

rebmuNepyT

PGT3F06203MK4+K42K1

PGT6F06203MK4+K84K2

PGT8F06203MK4+K46K2

:ETON

MOR

yticapaC

.ylnonoisrevyromemhsalfnielbaliavA.1

MAR

yticapaC

epyTegakcaPskrameRedoCtcudorP

)A-Q6P84(A-BK8400PQLP

hsalF

yromem

7U,3U

Table 1.6 M16C/26T V-ver. Current as of Feb., 2007

rebmuNepyT

PGV8F06203MK4+K46K2)A-Q6P84(A-BK8400PQLP

:ETON

MOR

yticapaC

.ylnonoisrevyromemhsalfnielbaliavA.1

MAR

yticapaC

egakcaPskrameRedoCtcudorP

hsalF

yromem

7U,3U

page 6

923fo7002,51.beF00.2.veR

0020-2020B90JER

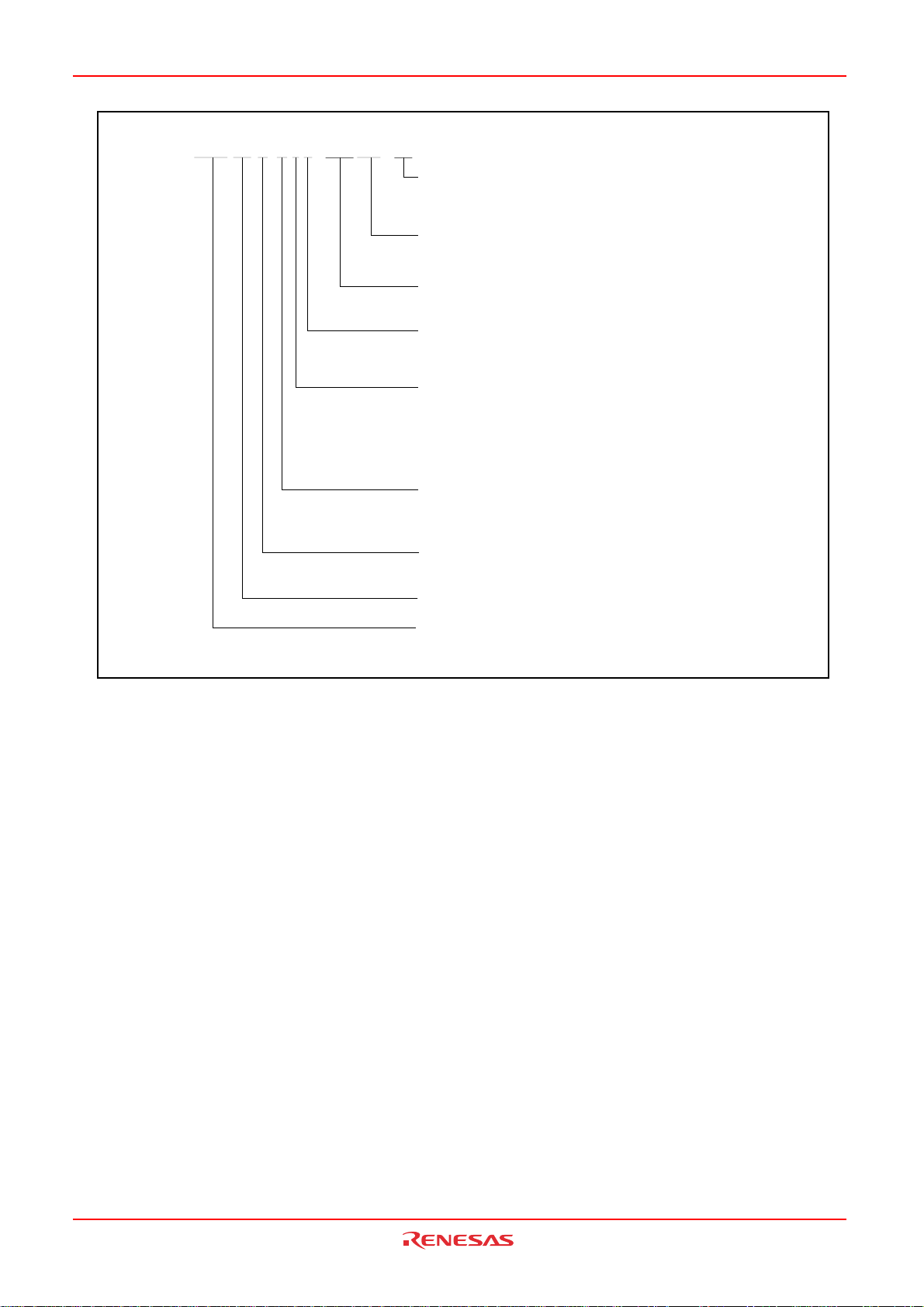

Page 24

Type No. M 3 0 2 6 0 M 8 A - XXX G P - U3

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

Product code:

See Tables 1.7 to 1.10

Package type:

GP: PLQP0048KB-A (48P6Q) (M16C/26A, M16C/26B, M16C/26T)

FP: PRSP0042GA-B (42P2R) (M16C/26A, M16C/26B)

ROM number:

ROM number is omitted in flash memory version

Version:

A : M16C/26A

B : M16C/26B

T : M16C/26T T-ver.

V : M16C/26T V-ver.

1. Overview

Figure 1.3 Product Numbering System

ROM / RAM capacity:

3: (24K+4K) bytes

6: (48K+4K) bytes

8: (64K+4K) bytes

NOTE:

1. Only flash memory version exists in "+4K bytes"

Memory type:

M: Mask ROM version

F: Flash memory version

Pin count (The value itself has no specific meaning)

M16C/26A Group

M16C Family

(1)

/ 1K bytes

(1)

/ 2K bytes

(1)

/ 2K bytes

page 7

923fo7002,51.beF00.2.veR

0020-2020B90JER

Page 25

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

Table 1.7 Product Code (Flash Memory Version) - M16C/26A, M16C/26B

MORlanretnI

tcudorP

edoC

3U

5U Cº58ot027U

9U Cº58ot02-Cº58ot02-

egakcaP

eerfdaeL

dnamargorP

esarE

ecnarudnE

001

000,1000,01

)3ot0skcolB:ecapSmargorP(

erutarepmeT

egnaR

Cº06ot0

dnamargorP

esarE

ecnarudnE

001Cº06ot0

MORlanretnI

)BdnaAskcolB:ecapSataD(

erutarepmeT

egnaR

Cº58ot04-Cº58ot04-

Table 1.8 Product Code (Mask ROM Version - M16C/26A)

1. Overview

tneibmAgnitarepO

erutarepmeT

Cº58ot04-

tcudorP

edoC

3U

egakcaP

Cº04-otCº58

tneibmAgnitarepO

erutarepmeT

eerfdaeL

5UCº02-otCº58

NOTE:

1. The lead contained products, D3, D5, D7, and D9 are put together with U3, U5, U7, and U9 respectively.

Lead-free products can be mounted by both conventional Sn-Pb paste and Lead-free paste (Sn-Ag-Cu

plating).

Table 1.9 Product Code (Flash Memory Version) - M16C/26T T-ver.

MORlanretnI

tcudorP

edoC

3U

7U000,1000,01

egakcaP

eerfdaeL

gnimmargorP

erusaredna

ecnarudne

001

)3ot0skcolB:ecapSmargorP(

erutarepmeT

egnar

Cº06otCº0

gnimmargorP

erusaredna

ecnarudne

001

MORlanretnI

)BdnaAskcolB:ecapSataD(

erutarepmeT

egnar

Cº58otCº04-Cº58otCº04-

tneibmAgnitarepO

erutaremeT

Table 1.10 Product Code (Flash Memory Version) - M16C/26T V-ver.

MORlanretnI

tcudorP

edoC

3U

7U000,1000,01

egakcaP

eerfdaeL

gnimmargorP

erusaredna

ecnarudne

001

)3ot0skcolB:ecapSmargorP(

erutarepmeT

egnar

Cº06otCº0

gnimmargorP

erusaredna

ecnarudne

001

MORlanretnI

)BdnaAskcolB:ecapSataD(

erutarepmeT

egnar

Cº521otCº04-Cº521otCº04-

tneibmAgnitarepO

erutaremeT

page 8

0020-2020B90JER

923fo7002,51.beF00.2.veR

Page 26

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

(1) Flash memory version, PLQP0048KB-A (48P6Q), M16C/26A, M16C/26B

1. Overview

0260F8A

A U3

XXXXX

(2) Flash memory version, PRSP0042GA-B (42P2R), M16C/26A, M16C/26B

M30263F8AFP

A U3

XXXXXXX

(3) MASK ROM version, PLQP0048KB-A (48P6Q), M16C/26A

Product Name : indicates M30260F8AGP

Chip Version and Product Code:

A : Indicates chip version

The first edition is shown to be blank and continues

with A and B.

U3 : Indicates Product code (see Table 1.7 Product Code)

Date Code (5 digits) fi indicates manufacturing management code

Product Name : indicates M30263F8AFP

Chip Version and Product Code:

A : Indicates chip version

The first edition is shown to be blank and continues

with A and B.

U3 : Indicates Product code (see Table 1.7 Product Code)

Date Code (7 digits) fi indicates manufacturing management code

0260M8A

001A U3

XXXXX

(4) MASK ROM version, PRSP0042GA-B (42P2R), M16C/26A

M30263M8A-001FP

A U3

Product Name : indicates M30260M8AGP

ROM number, Chip Version and Product Code:

001: Indicates ROM Number

A : Indicates chip version

U3 : Indicates Product code (see Table 1.8 Product Code)

Date Code (5 digits) fi indicates manufacturing management code

Product Name and ROM number

M30263M8A and FP are indicated of Produnct name

001 is indicated of ROM number

Chip Version and Product Code:

A : Indicates chip version

XXXXXXX

U3 : Indicates Product code (see Table 1.8 Product Code)

Date Code (7 digits) fi indicates manufacturing management code

Figure 1.4 Marking Diagram (M16C/26A , M16C/26B)

The first edition is shown to be blank and continues

with A and B.

The first edition is shown to be blank and continues

with A and B.

page 9

923fo7002,51.beF00.2.veR

0020-2020B90JER

Page 27

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

(1) Flash memory version, PLQP0048KB-A (48P6Q), M16C/26T T-ver.

1. Overview

0260F8T

A U3

Product Name : indicates M30260F8TGP

Chip Version and Product Code:

XXXXX

Date Code (5 digits) fi indicates manufacturing management code

(2) Flash memory version, PLQP0048KB-A (48P6Q), M16C/26T V-ver.

0260F8V

A U3

Product Name : indicates M30260F8VGP

Chip Version and Product Code:

XXXXX

Date Code (5 digits) fi indicates manufacturing management code

Figure 1.5 Marking Diagram (M16C/26T)

A : Indicates chip version

The first edition is shown to be blank and continues

with A and B.

U3 : Indicates product code (see Table 1.9 Product Code)

A : Indicates chip version

The first edition is shown to be blank and continues

with A and B.

U3 : Indicates product code (see Table 1.10 Product Code)

page 10

923fo7002,51.beF00.2.veR

0020-2020B90JER

Page 28

)T62/C61M,B62/C61M,A62/C61M(puorGA62/C61M

p

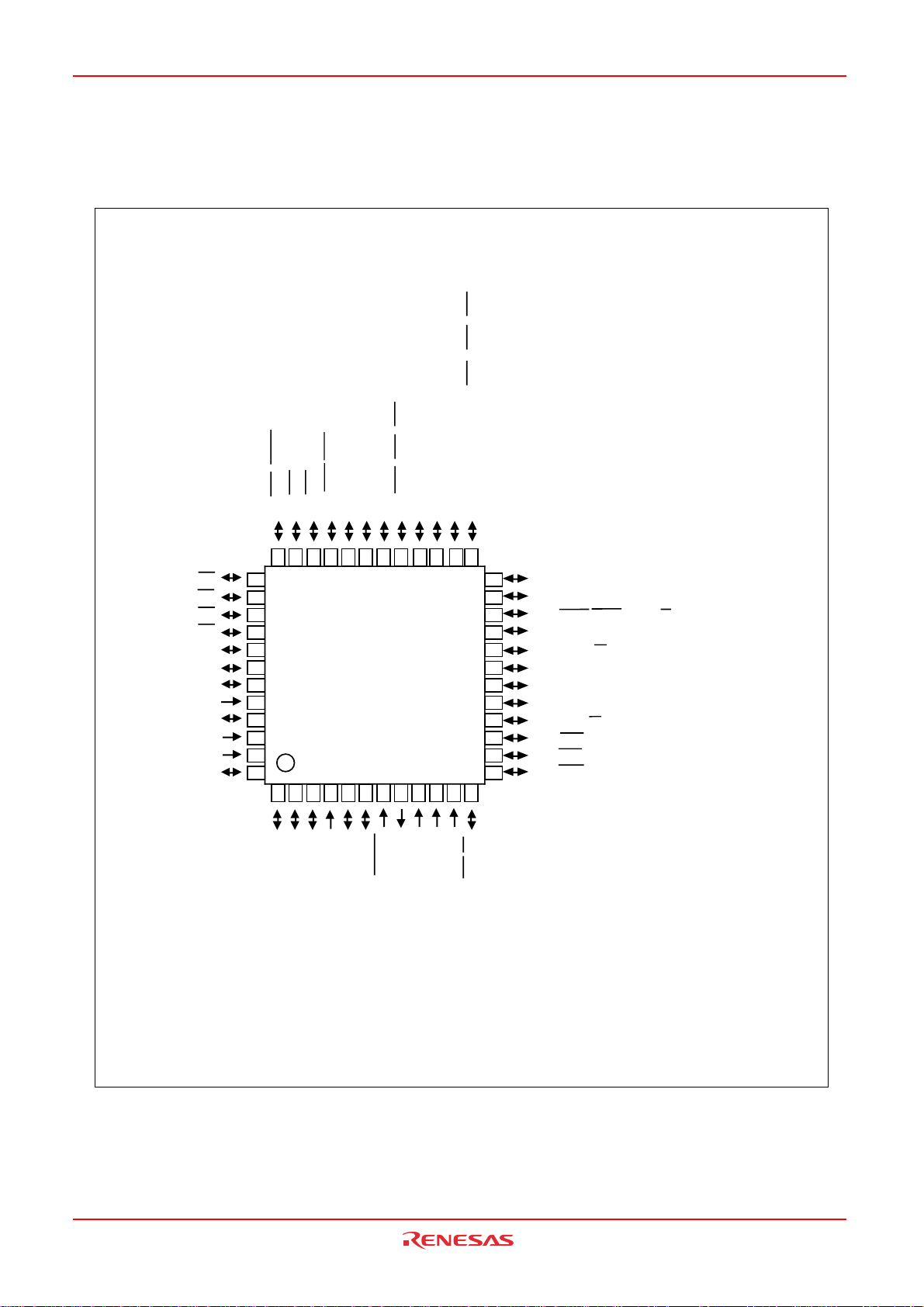

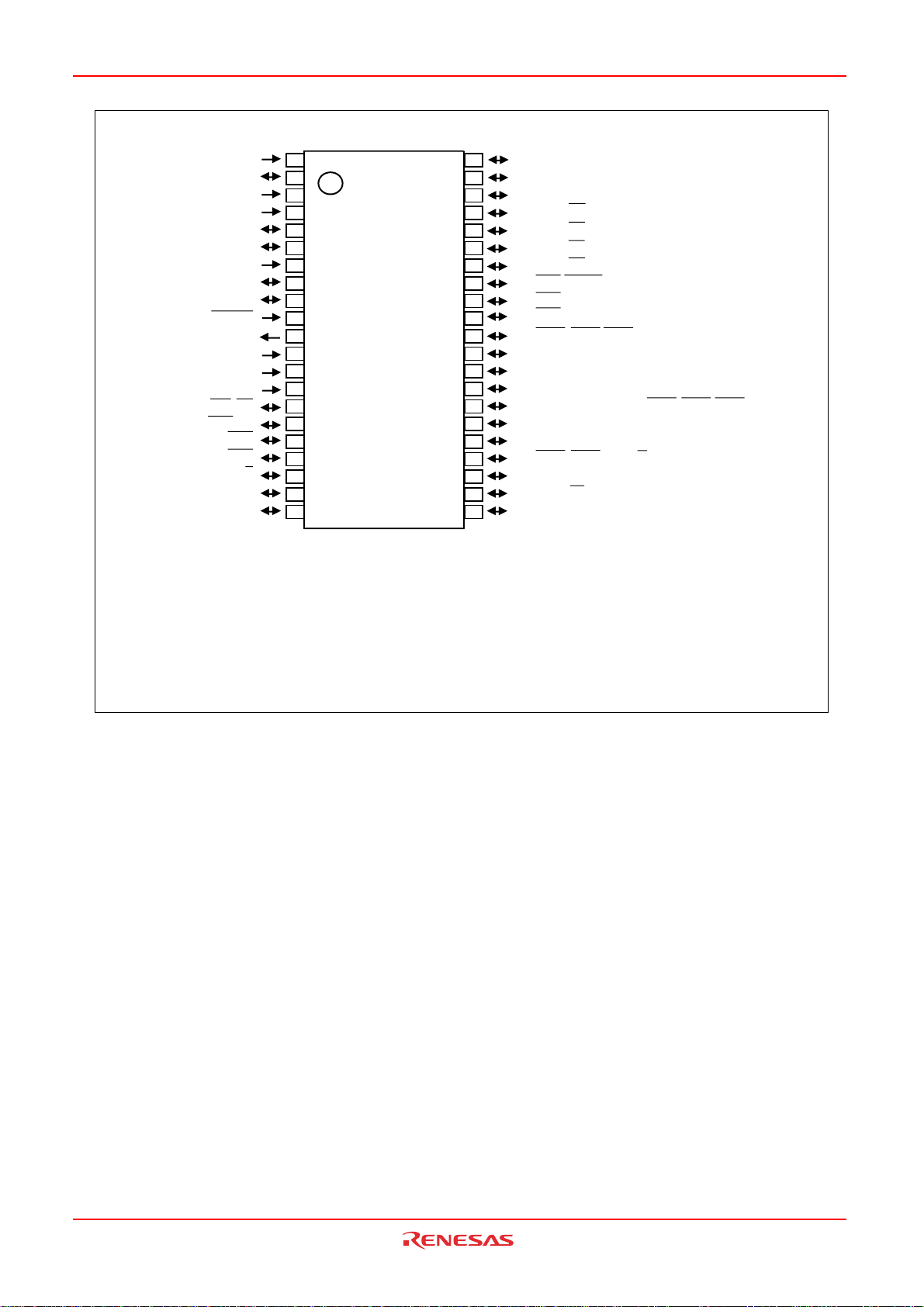

1.5 Pin Assignments

Figures 1.6 and 1.7 show the Pin Assignments (top view).

1

/CLKS

0

/IDV

TRG

/AD

3

/INT

5

P1

/IDW

4

/INT

6

P1

/IDU

5

/INT

7

P1

0

/RTS

0

/CTS

0

P6

0

/CLK

1

P6

0

/RxD

2

P6

0

/TxD

3

P6

/CTS

1

/RTS

1

/CTS

4

P6

1

/CLK

5

P6

1

/RxD

6

P6

1

/TxD

7

P6

1

/CLKS

0

/CTS

1

/RTS

1

/CTS

2

/SDA

0OUT

/TA

2

/TxD

0

P7

1. Overview

P107/AN7/KI

P106/AN6/KI

P105/AN5/KI

P104/AN4/KI

P103/AN

P102/AN

P101/AN

AV

P100/AN

V

REF

AV

P93/AN

35

2

31

/AN

IN

/TB1

1

P9

34

3

OUT

/CLK

30

/AN

IN

/TB0

0

33

4

SS

CNV

32

5

CIN

/X

7

P8

31

6

COUT

/X

6

P8

30

7

RESET

36

3

37

2

38

1

39

0

40

41

3

2

42

1

43

ss

44

0

45

46

cc

47

24

48

1

32

/AN

IN

/TB2

2

P9

P9

29

8

OUT

X

SS

V

27

28

9

25

26

24

P71/RxD2/TA0IN/SCL2/CLK1

P72/CLK2/TA1

23

22

P73/CTS2/RTS2/TA1IN/V/TxD

21

P74/TA2

20

19

18

17

16

15

14

13

11

10

12

IN

CC

X

V

/NMI/SD

5

5

/TA2IN/W

P7

P76/TA3

P77/TA3

P80/TA4

1

/TA4IN/U

P8

2

/INT

P8

P83/INT

P84/INT2/ZP

OUT

OUT

IN

OUT

0

1

/W

/U

OUT

/V/RxD

1

1

P8

NOTE:

1. Set PACR2 to PACR0 bit in the PACR register

2

to "100

" before you input and output it after

resetting to each pin. When the PACR register

isn't set up, the input and output function of

some of the

ins are disabled.

Figure 1.6 Pin Assignment for 48-Pin Package (Top View)