To all our customers

Regarding the change of names mentioned in the document, such as Mitsubishi

Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas

Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog

and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.)

Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi

Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names

have in fact all been changed to Renesas Technology Corp. Thank you for your understanding.

Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been

made to the contents of the document, and these changes do not constitute any alteration to the

contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices

and power devices.

Renesas Technology Corp.

Customer Support Dept.

April 1, 2003

Under

development

Description

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

Description

The M16C/80 group of single-chip microcomputers are built using the high-performance silicon gate CMOS

process using a M16C/80 Series CPU core and are packaged in a 100-pin and 144-pin plastic molded

QFP. The peripheral functions of 100-pin and 144-pin are common. These single-chip microcomputers

operate using sophisticated instructions featuring a high level of instruction efficiency. With 16M bytes of

address space, they are capable of executing instructions at high speed. They also feature a built-in multiplier and DMAC, making them ideal for controlling office, communications, industrial equipment, and other

high-speed processing applications.

Features

• Memory capacity..................................ROM (See ROM expansion figure.)

RAM 10 to 24 Kbytes

• Shortest instruction execution time......50ns (f(XIN)=20MHz)

• Supply voltage .....................................4.2 to 5.5V (f(XIN)=20MHz)

Mask ROM, external ROM and flash memory versions

2.7 to 5.5V (f(XIN)=10MHz)

Mask ROM, external ROM and flash memory versions

• Low power consumption ......................45mA (M30800MC-XXXFP)

(f(XIN) = 20MHz without software wait,Vcc=5V)

• Interrupts..............................................29 internal and 8 external interrupt sources, 5 software interrupt

sources; 7 levels (including key input interrupt)

• Multifunction 16-bit timer......................5 output timers + 6 input timers

• Serial I/O..............................................5 channels for UART or clock synchronous

• DMAC ..................................................4 channels (trigger: 31 sources)

• DRAMC................................................Used for EDO, FP, CAS before RAS refresh, self-refresh

• A-D converter.......................................10 bits X 8 channels (Expandable up to 10 channels)

• D-A converter.......................................8 bits X 2 channels

• CRC calculation circuit.........................1 circuit

• X-Y converter.......................................1 circuit

• Watchdog timer....................................1 line

• Programmable I/O ...............................87 lines:100-pin version, 123 lines:144-pin version

• Input port..............................................

1 line (P85 shared with NMI pin)

• Memory expansion ..............................Available (16M bytes)

• Chip select output ................................4 lines

• Clock generating circuit .......................2 built-in clock generation circuits

(built-in feedback resistance, and external ceramic or quartz oscillator)

Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free of error.

Specifications in this manual may be changed for functional or performance improvements. Please make sure

your manual is the latest edition.

_______

Applications

Audio, cameras, office equipment, communications equipment, portable equipment, etc.

------Table of Contents------

CPU ..............................................................13

Reset.............................................................18

Processor Mode............................................26

Clock Generating Circuit ............................... 43

Protection......................................................55

Interrupts.......................................................56

Watchdog Timer............................................78

DMAC ...........................................................80

Timer.............................................................91

Serial I/O ..................................................... 123

A-D Converter .............................................165

D-A Converter .............................................175

CRC Calculation Circuit ..............................177

X-Y converter .............................................. 179

DRAM controller..........................................182

Programmable I/O Ports .............................189

Usage Precaution .......................................207

Electric characteristics ................................219

Flash memory version.................................266

1

Under

Preliminary Specifications REV.D

development

Description

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

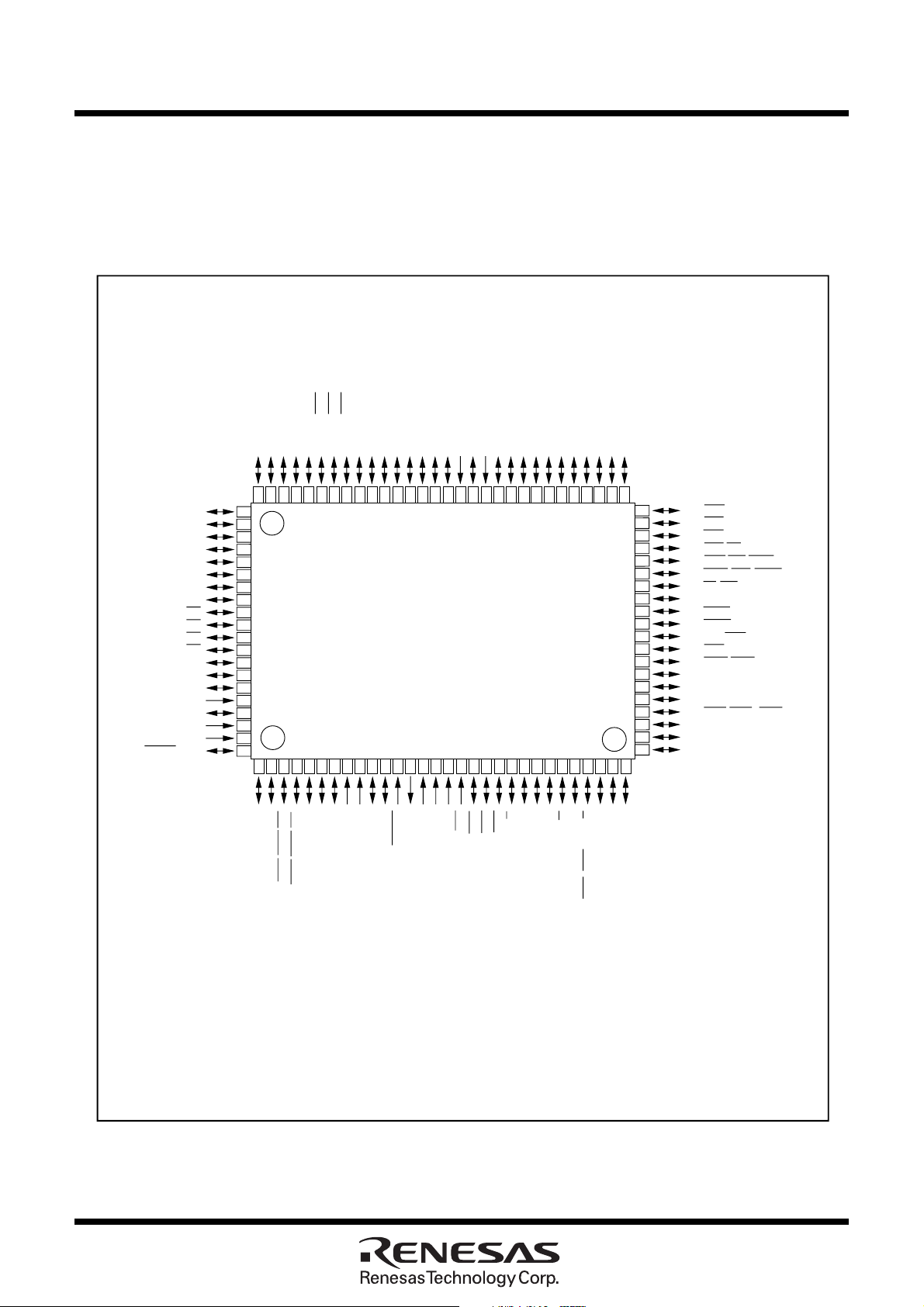

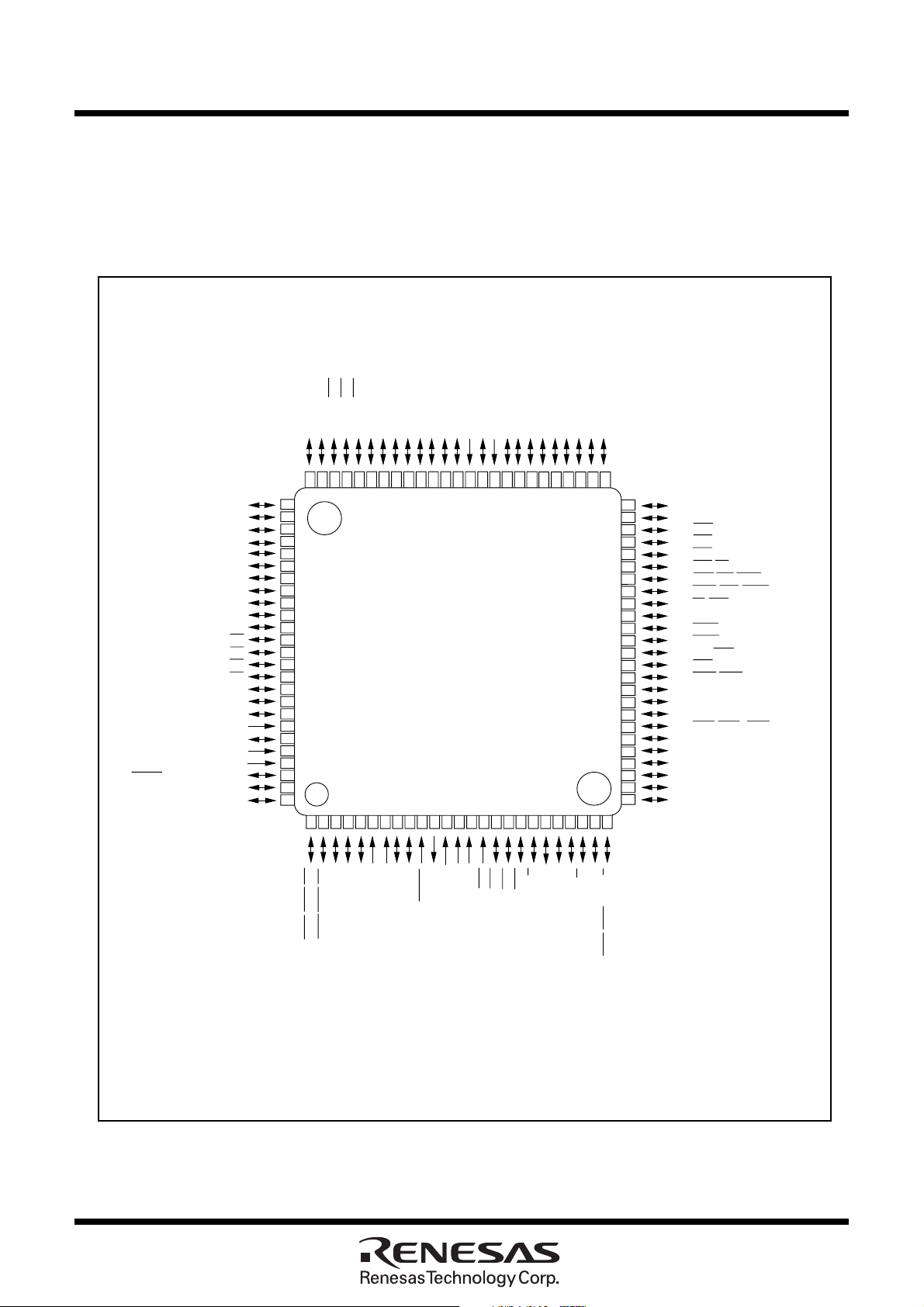

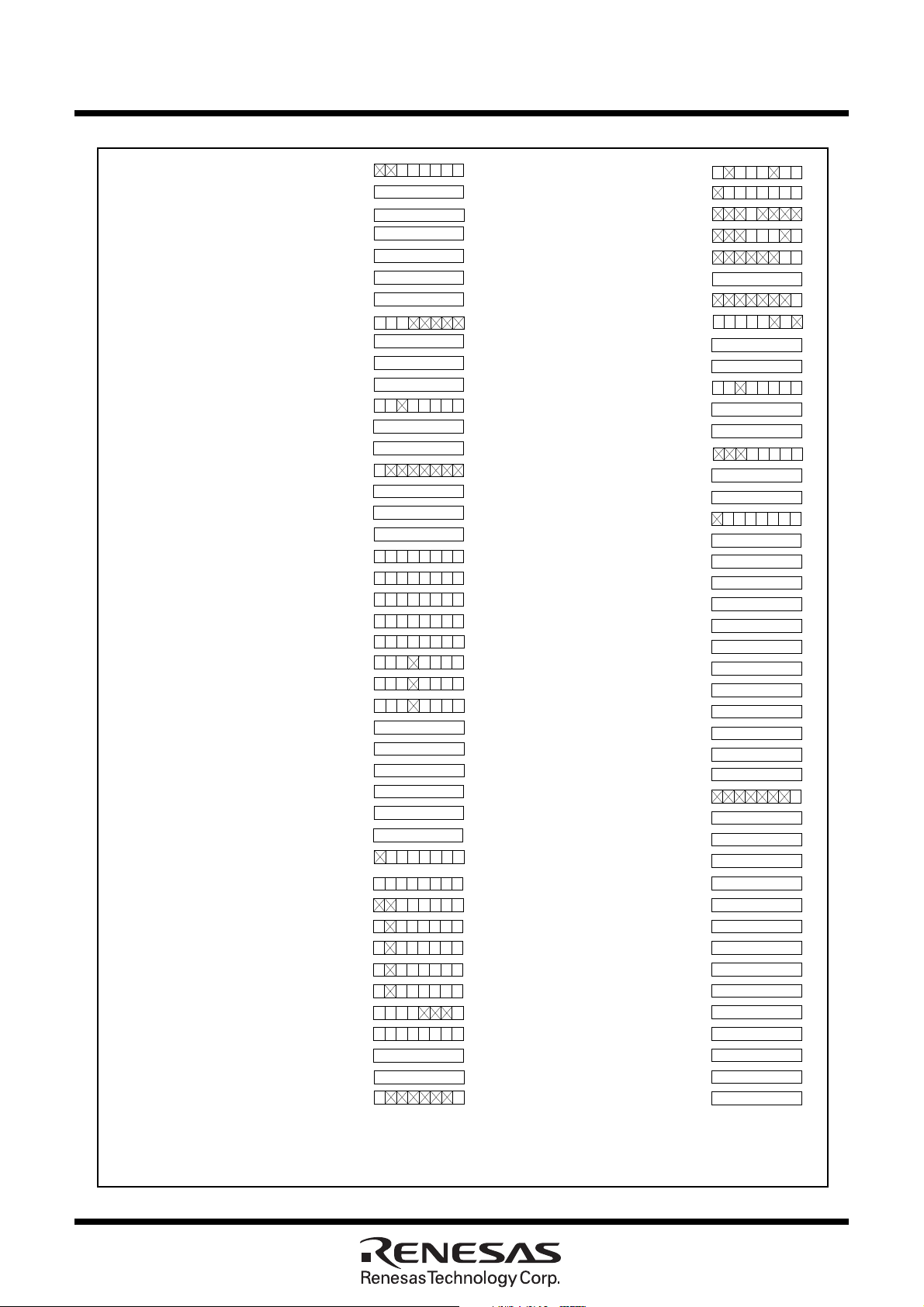

Pin Configuration

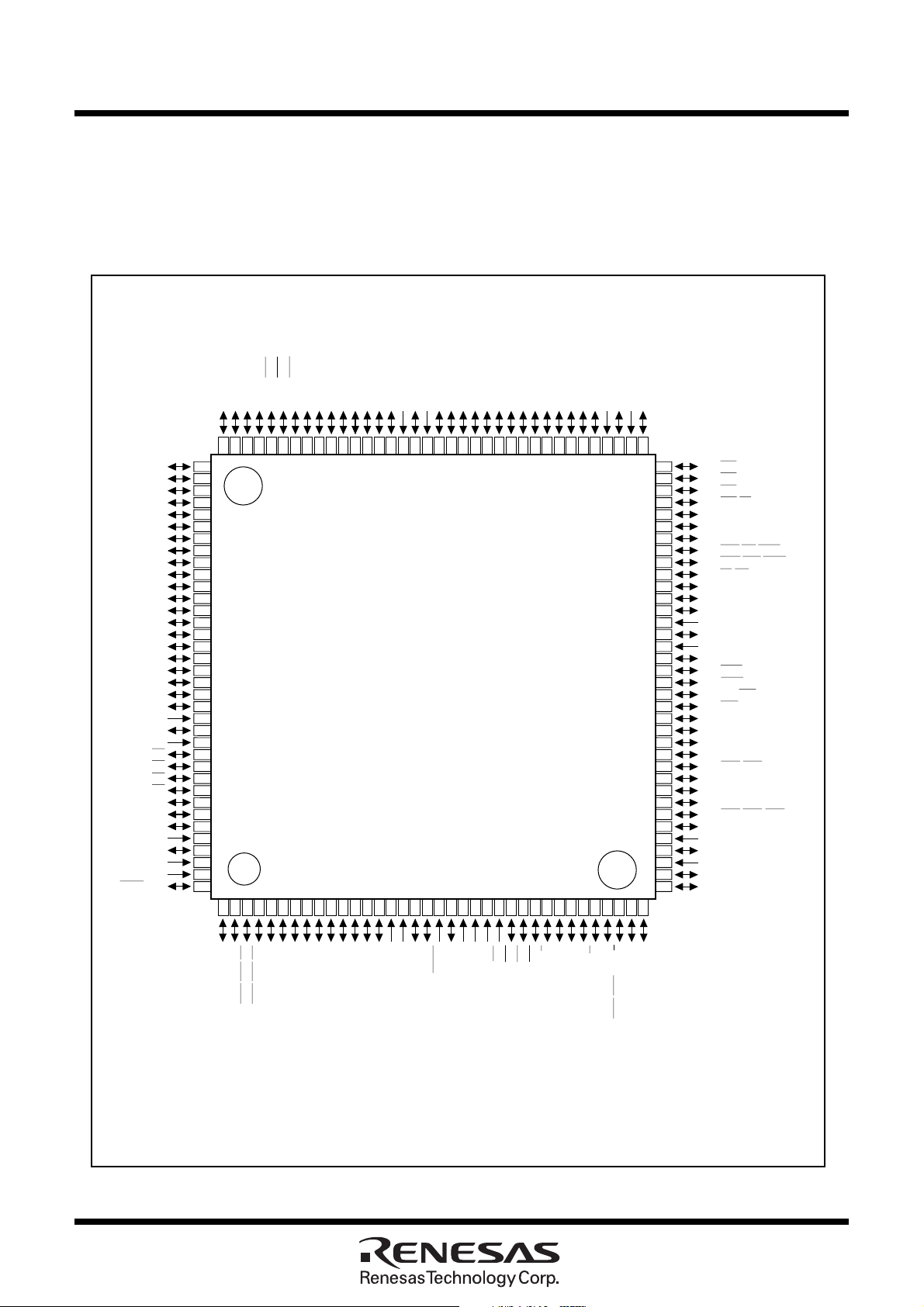

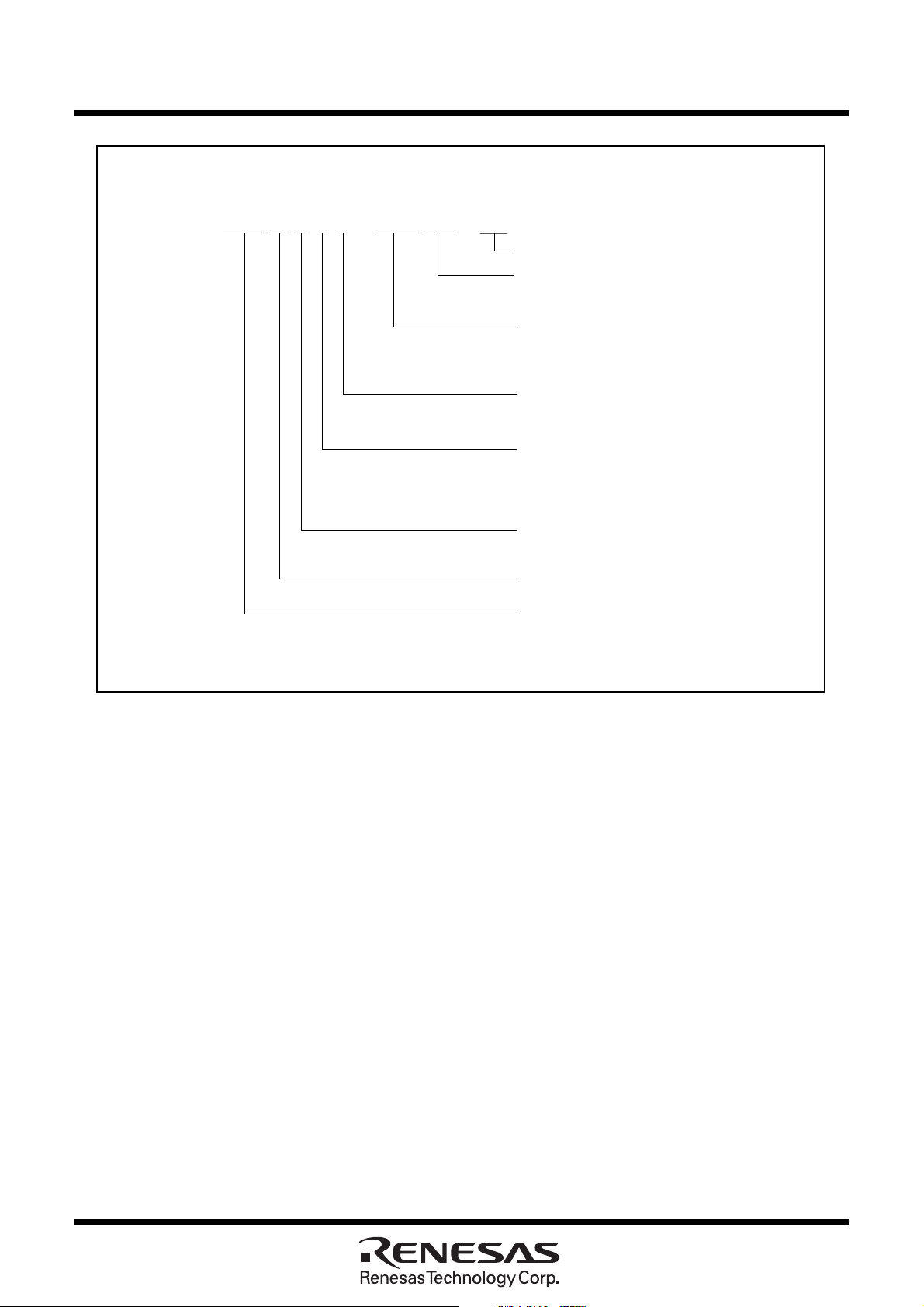

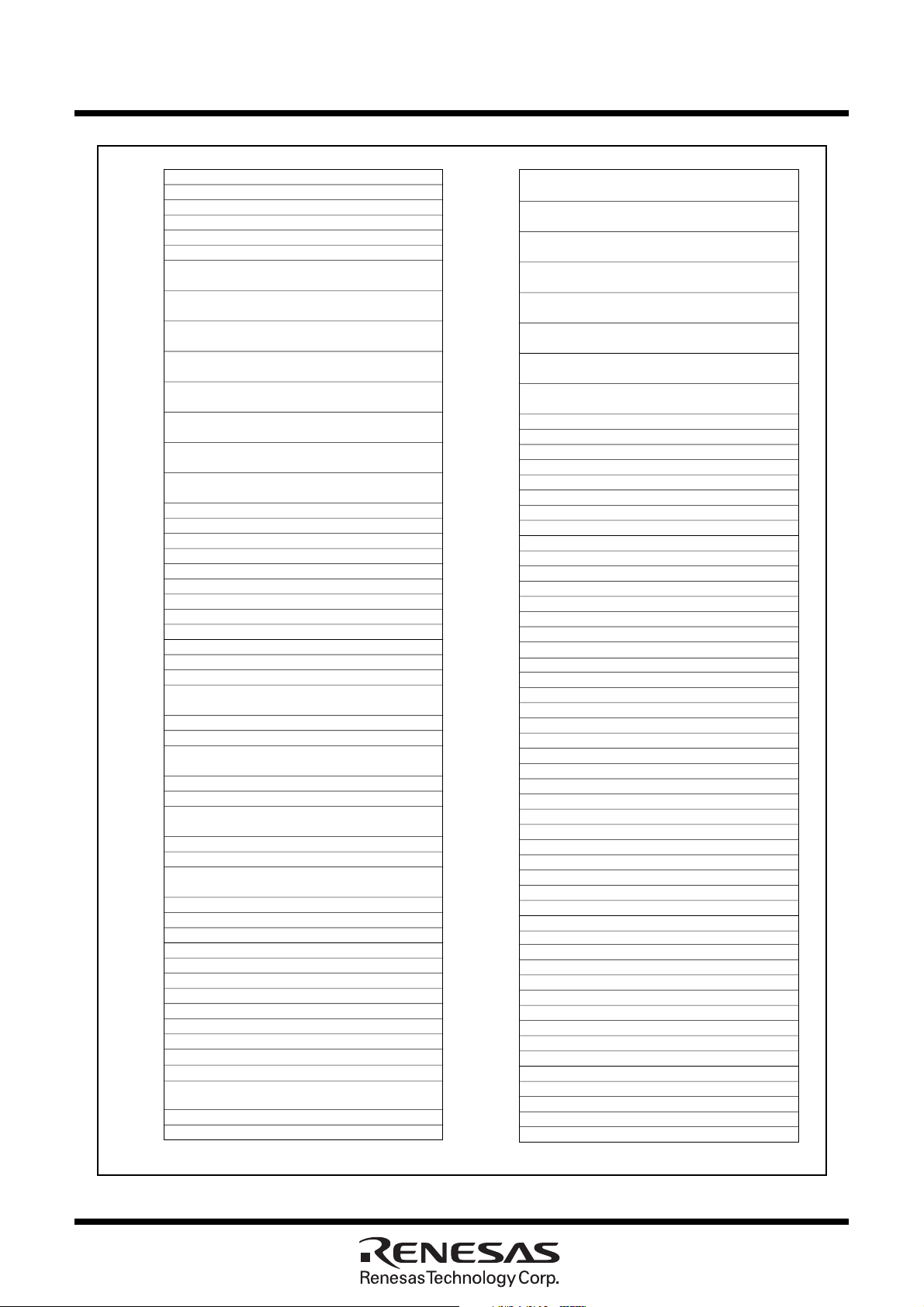

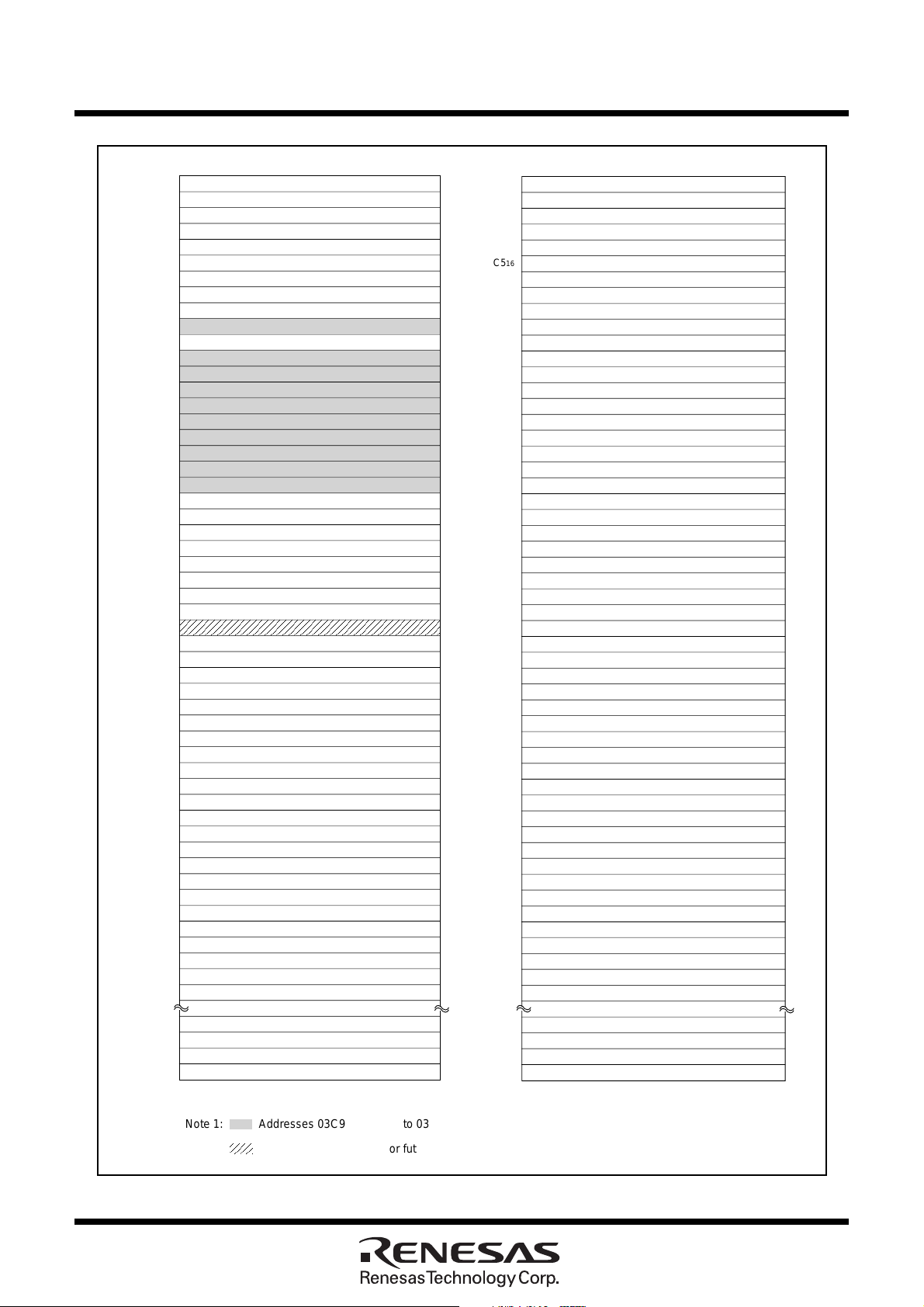

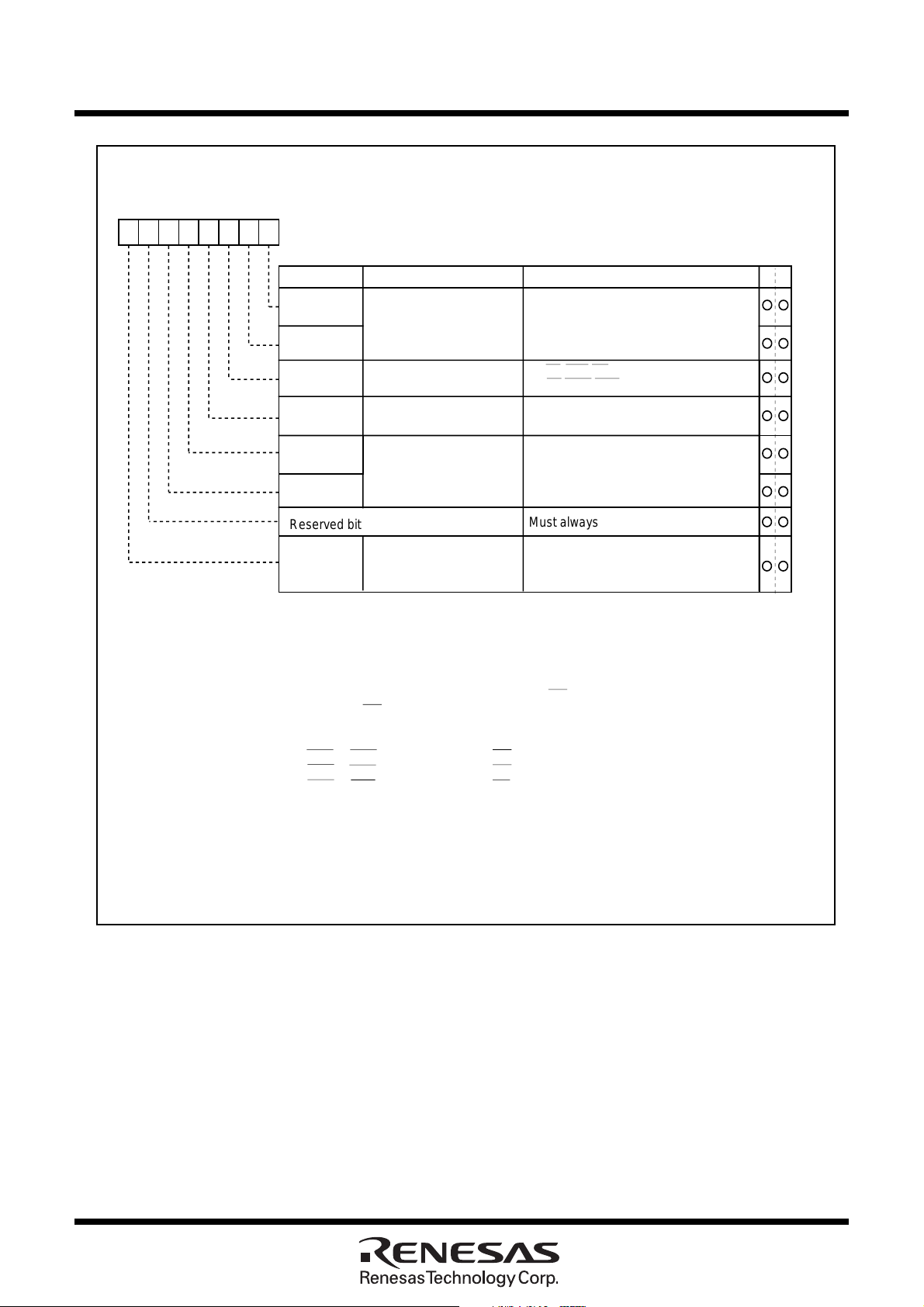

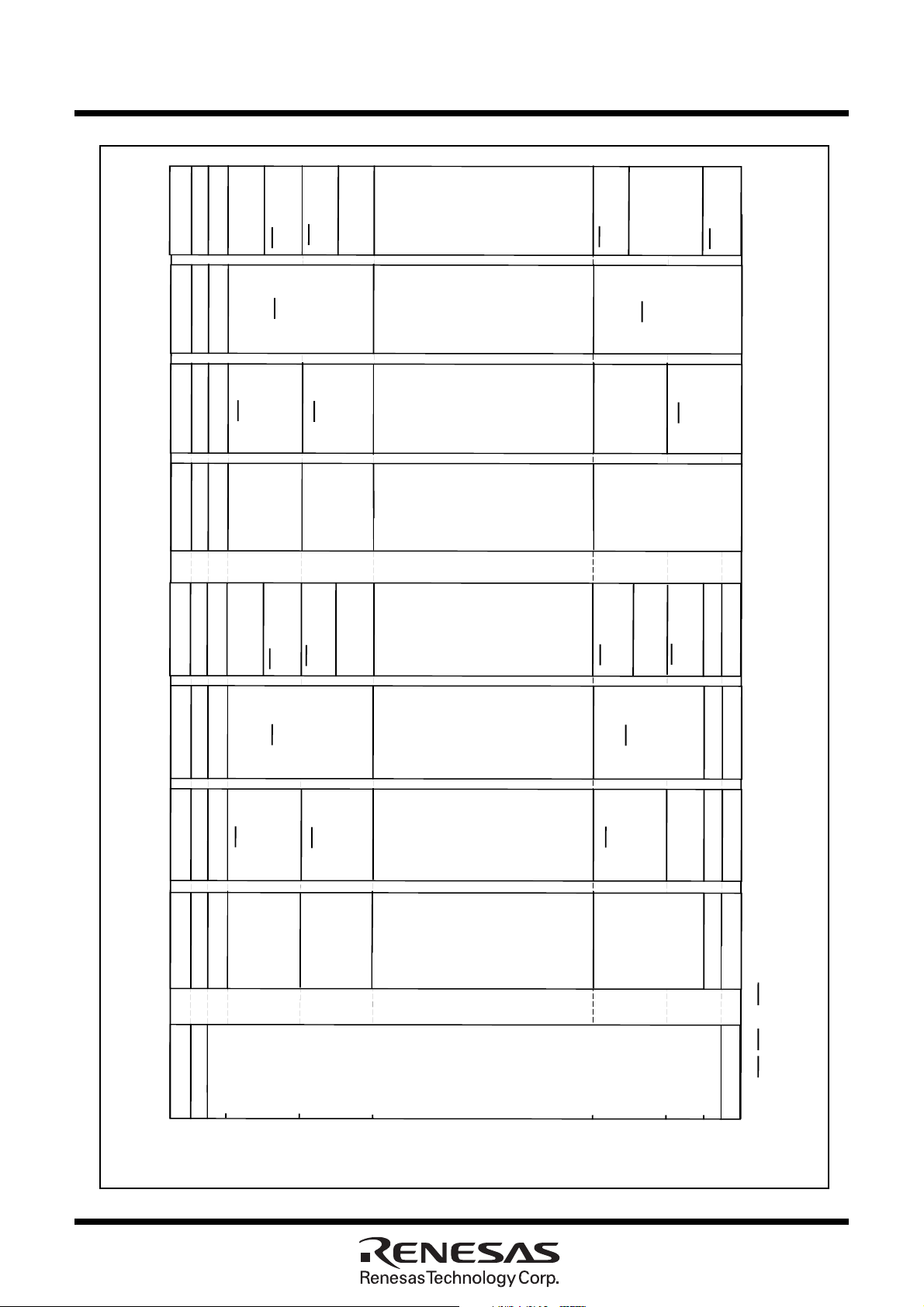

Figures 1.1.1 and 1.1.2 show the pin configuration (top view) for 100-pin and Figure 1.1.3 shows the pin

configuration (top view) for 144-pin.

PIN CONFIGURATION (top view)

)

)

)

)

11

12

13

(MA3)(/D

(MA4)(/D

(MA5)(/D

11

12

13

/A

/A

/A

3

4

5

P3

P3

P3

)

15

14

(MA7)(/D

(MA6)(/D

(MA8)

15

14

16

/A

/A

/A

7

6

0

P3

P3

P4

(MA9)

(MA10)

17

18

/A

/A

1

2

P4

P4

(MA11)

19

/A

3

P4

)

)

10

)

9

8

)

)

2

(/D

2

/A

2

P2

)

3

(/D

3

/A

3

P2

)

4

(/D

4

/A

4

P2

)

5

(/D

5

/A

5

P2

)

6

(/D

6

/A

6

P2

7

(/D

7

/A

7

P2

(MA0)(/D

8

/A

0

P3

Vss

(MA1)(/D

9

/A

1

Vcc

P3

(MA2)(/D

10

/A

2

P3

)

)

0

1

/INT5

/INT4

/INT3

(/D

(/D

8

9

10

11

/D

/D

/D

/D

0

1

2

3

P1

P1

P1

P1

15

14

13

12

/D

4

P1

0

1

/A

/D

/A

/D

/D

0

7

1

6

5

P2

P1

P2

P1

P1

515253545556575859606162636465666768697071727374757677787980

P0

7

/D

7

P0

6

/D

P0

5

/D

P0

4

/D

P0

3

/D

P0

2

/D

P0

1

/D

P0

0

/D

P10

7

/AN

7

/KI

P10

6

/AN

6

/KI

P10

5

/AN

5

/KI

P10

4

/AN

4/

KI

P10

3

/AN

P10

2

/AN

P10

1

/AN

AV

SS

P10

0

/AN

V

REF

7

/AD

/SCL

TRG

/R

4

/STxD

AVcc

X

D

P9

81

6

82

5

83

4

84

3

85

2

86

1

87

0

88

3

89

2

90

1

91

0

92

3

93

2

94

1

95

96

0

97

98

99

4

00

1

4

1 2 3 4 5 6 7 8 9 101112131415161718192021222324252627282930

4

4

4

/SS

4

/SRxD

4

/RTS

4

/SDA

/ANEX0/CLK

4

5

D

/CTS

X

P9

IN

/TB4

1

/ANEX1/T

/DA

6

4

P9

P9

M16C/80 Group

3

3

3

3

/SS

3

/RTS

3

/CTS

IN

/TB3

0

/DA

3

P9

/STxD

/SRxD

3

3

/SCL

/SDA

3

3

D

D

X

X

/R

/T

IN

IN

/TB1

/TB2

1

2

P9

P9

/CLK

IN

/TB0

0

P9

BYTE

CNVss

CIN

/X

7

P8

COUT

/X

6

P8

OUT

X

RESET

SS

V

IN

CC

X

V

/NMI

/INT

/INT

5

3

4

P8

P8

P8

/INT

2

P8

/U

IN

/TA4

1

P8

/U

OUT

/TA4

0

P8

IN

/TA3

7

P7

OUT

/TA3

6

P7

/W

IN

/TA2

5

P7

/W

OUT

/TA2

4

P7

/V

IN

/TA1

2

/RTS

2

/CTS

3

P7

/V

OUT

/TA1

2

/CLK

2

P7

(Note)

IN

/TB5

IN

/TA0

2

/SCL

2

/RxD

1

P7

(Note)

OUT

/TA0

2

/SDA

2

D

X

/T

0

P7

1

0

2

P4

4

/CS3/A

20

50

P4

49

48

P4

47

P4

46

P5

45

P5

44

P5

43

P5

42

P5

41

P5

40

P5

39

P5

38

P6

37

P6

36

P6

35

P6

34

P6

33

P6

32

P6

31

P6

(MA12)

5

/CS2/A

21

6

/CS1/A

22

7

/CS0/A

23

0

/WRL/WR/CASL

1

/WRH/BHE/CASH

2

/RD/DW

3

/BCLK/ALE/CLK

4

/HLDA/ALE

5

/HOLD

6

/ALE/RAS

7

/RDY

0

/CTS

0

/RTS

1

/CLK

2

/RxD

3

/T

4

/CTS

5

/CLK

6

/RxD

7

/T

0

0

0

X

D

0

1

/RTS

1

/CTS

1

1

X

D

1

OUT

0

/CLKS

1

Figure 1.1.1. Pin configuration for 100-pin version (top view) (1)

2

Note: This port is N-channel open drain output.

Package: 100P6S-A

Under

development

Description

PIN CONFIGURATION (top view)

P97/AD

TRG/RXD4

P96/ANEX1/TXD4/SDA4/SRxD

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

)

)

)

10

P12/D

P11/D

P10/D

P07/D

P06/D

P05/D

P04/D

P03/D

P02/D

P01/D

P00/D

P107/AN7/KI

P106/AN6/KI

P105/AN5/KI

P104/AN4/KI

P103/AN

P102/AN

P101/AN

AV

P100/AN

V

AVcc

/SCL4/STxD

P95/ANEX0/CLK

REF

)

8

3

4

5

)

)

0

/INT

11

12

13

/D

/D

/D

3

4

5

P1

P1

P1

10

SS

76

9

77

8

78

79

7

6

80

5

81

4

82

83

3

2

84

1

85

0

86

3

87

2

88

1

89

0

90

3

91

2

92

93

1

94

95

0

96

97

98

4

99

4

00

1

4

1 2 3 4 5 6 7 8 9 10111213141516171819202122232425

1

/INT

/INT

(/D

(/D

0

14

15

1

/A

/A

/D

/D

0

1

6

7

P2

P2

P1

P1

M16C/80 Group

)

2

(/D

2

/A

2

P2

)

3

(/D

3

/A

3

P2

)

4

(/D

4

/A

4

P2

)

5

(/D

5

/A

5

P2

)

6

(/D

6

/A

6

P2

)

7

(/D

7

/A

7

P2

(MA0)(/D

8

/A

0

P3

Vss

9

(MA1)(/D

9

/A

1

Vcc

P3

11

(MA2)(/D

(MA3)(/D

10

11

/A

/A

2

3

P3

P3

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

)

)

)

)

14

12

13

15

(MA6)(/D

(MA8)

(MA7)(/D

14

15

/A

/A

6

7

P3

P3

16

/A

0

P4

51525354555657585960616263646566676869707172737475

(MA9)

17

/A

1

P4

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

P42/A18(MA10)

P4

3/A19

(MA11)

P44/CS3/A20(MA12)

P45/CS2/A

P46/CS1/A

P47/CS0/A

21

22

23

P50/WRL/WR/CASL

P51/WRH/BHE/CASH

P52/RD/DW

P53/BCLK/ALE/CLK

P54/HLDA/ALE

P55/HOLD

P56/ALE/RAS

P57/RDY

P60/CTS0/RTS

P61/CLK

0

P62/RxD

0

P63/TXD

0

P64/CTS1/RTS1/CTS0/CLKS

P65/CLK

1

P66/RxD

1

P67/TXD

1

P70/TXD2/SDA2/TA0

1

/RxD2/SCL2/TA0IN/TB5

P7

P72/CLK2/TA1

0

OUT

OUT

OUT

(Note)

/V

(MA4)(/D

(MA5)(/D

12

13

/A

/A

4

5

P3

P3

IN

1

(Note)

3

3

3

4

/SS

4

/RTS

4

/CTS

IN

/TB4

1

/DA

4

P9

/SS

3

/RTS

3

/CTS

IN

/TB3

0

/DA

3

P9

/STxD

/SRxD

3

3

/SCL

/SDA

3

3

D

D

X

X

/R

/T

IN

IN

/TB1

/TB2

1

2

P9

P9

3

/CLK

IN

/TB0

0

P9

BYTE

CNVss

CIN

/X

7

P8

COUT

/X

6

P8

OUT

X

RESET

IN

SS

CC

X

V

V

/NMI

5

P8

0

1

2

/INT

4

P8

/INT

3

P8

/INT

2

P8

/U

IN

/TA4

1

P8

/U

OUT

/TA4

0

P8

Note: This port is N-channel open drain output.

Figure 1.1.2. Pin configuration for 100-pin version (top view) (2)

IN

/TA3

7

P7

/V

/W

/W

OUT

IN

IN

OUT

/TA3

/TA1

/TA2

6

2

5

/TA2

4

P7

P7

/RTS

P7

2

/CTS

3

P7

Package: 100P6Q-A

3

Under

1

)

)

Preliminary Specifications REV.D

development

Description

Specifications in this manual are tentative and subject to change.

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

PIN CONFIGURATION (top view)

)

0

/INT3

/INT5

/INT4

(/D

13

P10/D8

P07/D7

P06/D6

P05/D5

P04/D4

P114

P113

P112

P111

P110

P03/D3

P02/D2

P01/D1

P00/D0

P157

P156

P155

P154

P153

P152

P151

VSS

P150

VCC

P107/AN7/KI3

P106/AN6/KI2

P105/AN5/KI1

P104/AN4/KI0

P103/AN3

P102/AN2

P101/AN1

AVSS

P100/AN0

VREF

AVCC

P97/ADTRG/RXD4

/SCL4/STxD4

10

/D

/D12

/D9

/D11

2

4

1

3

P1

P1

P1

P1

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

123 4 76 8 9 101112 13141516 17181920212223 242526272829305 31 32 33 34 35 36

0

/D

/D15

/D14

/A

5

7

6

0

P1

P1

P1

P2

)

8

)

)

(/D1

(/D2

1

2

/A

/A

1

2

P2

P2

100101102103104105106107108

)

)

)

)

)

7

4

(/D6

(/D3

(/D5

(/D

(/D

3

5

4

/A

/A

/A

3

5

4

P2

P2

P2

(MA0)(/D

6

7

8

1

0

/A

/A

/A

6

7

0

SS

P2

V

P2

P3

2

CC

V

P12

P12

P12

M16C/80 Group

3

P12

4

P12

10

)

9

(MA2)(/D

(MA1)(/D

10

9

/A

/A

2

1

P3

P3

)

12

11

(MA4)(/D

(MA3)(/D

12

11

/A

/A

4

3

P3

P3

)

)

14

13

(MA6)(/D

(MA5)(/D

14

13

/A

/A

6

5

P3

P3

)

15

(MA8)

(MA7)(/D

16

15

/A

/A

0

7

P4

P3

78

(MA9)

17

/A

1

P4

SS

V

(MA10)

18

/A

2

CC

P4

V

(MA11)

19

/A

3

P4

7374757677798081828384858687888990919293949596979899

P44/CS3/A20(MA12)

72

P45/CS2/A21

71

P46/CS1/A22

70

P47/CS0/A23

69

P125

68

P126

67

P127

66

P50/WRL/WR/CASL

65

P51/WRH/BHE/CASH

64

P52/RD/DW

63

P53/BCLK/ALE/CLKOUT

62

P130

61

P131

60

VCC

59

P132

58

VSS

57

P133

56

P54/HLDA/ALE

55

P55/HOLD

54

P56/ALE/RAS

53

P57/RDY

52

P134

51

P135

50

P136

49

P137

48

P60/CTS0/RTS0

47

P61/CLK0

46

P62/RXD0

45

P63/TXD0

44

P64/CTS1/RTS1/CTS0/CLKS

43

P65/CLK1

42

VSS

41

40

P66/RXD1

VCC

39

38

P67/TXD1

P70/TXD2/SDA2/TA0OUT

37

4

2

4

4

/CLK

0

/SRxD

4

/SDA

/ANEX

4

5

D

X

P9

/T

/ANEX1

6

P9

4

/SS

4

/RTS

4

/CTS

4IN

/TB

/DA1

4

P9

3

/SS

3

/RTS

3

/CTS

3IN

/TB

/DA0

3

P9

3

3

/STxD

/SRxD

3

3

/SCL

/SDA

3

3

D

D

X

/RX

/T

1IN

2IN

/TB

/TB

1

2

P9

P9

/CLK3

0IN

/TB

0

P9

6

P14

5

P14

P14

3

P14

P14

1

P14

0

P14

BYTE

SS

CNV

CIN

COUT

/X

7

/X

6

P8

P8

XOUT

RESET

XIN

VSS

VCC

Figure 1.1.3. Pin configuration for 144-pin version (top view)

4

/NMI

5

P8

2

/INT

4

P8

1

/INT

3

P8

0

/INT

2

P8

/U

4IN

/TA

1

P8

/U

4OUT

/TA

0

P8

3IN

/TA

7

P7

3OUT

/TA

6

P7

/W

2IN

/TA

5

P7

/W

2OUT

/TA

4

P7

/V

1IN

/TA

2

/RTS

2

/CTS

3

P7

(Note)

/V

1OUT

/TA

2

/CLK

2

P7

(Note)

5IN

/TB

0IN

/TA

2

/SCL

2

D

X

/R

1

P7

Note: This port is N-channel open drain output.

Package: 144P6Q-A

Under

A

A

A

A

development

Description

Specifications in this manual are tentative and subject to change.

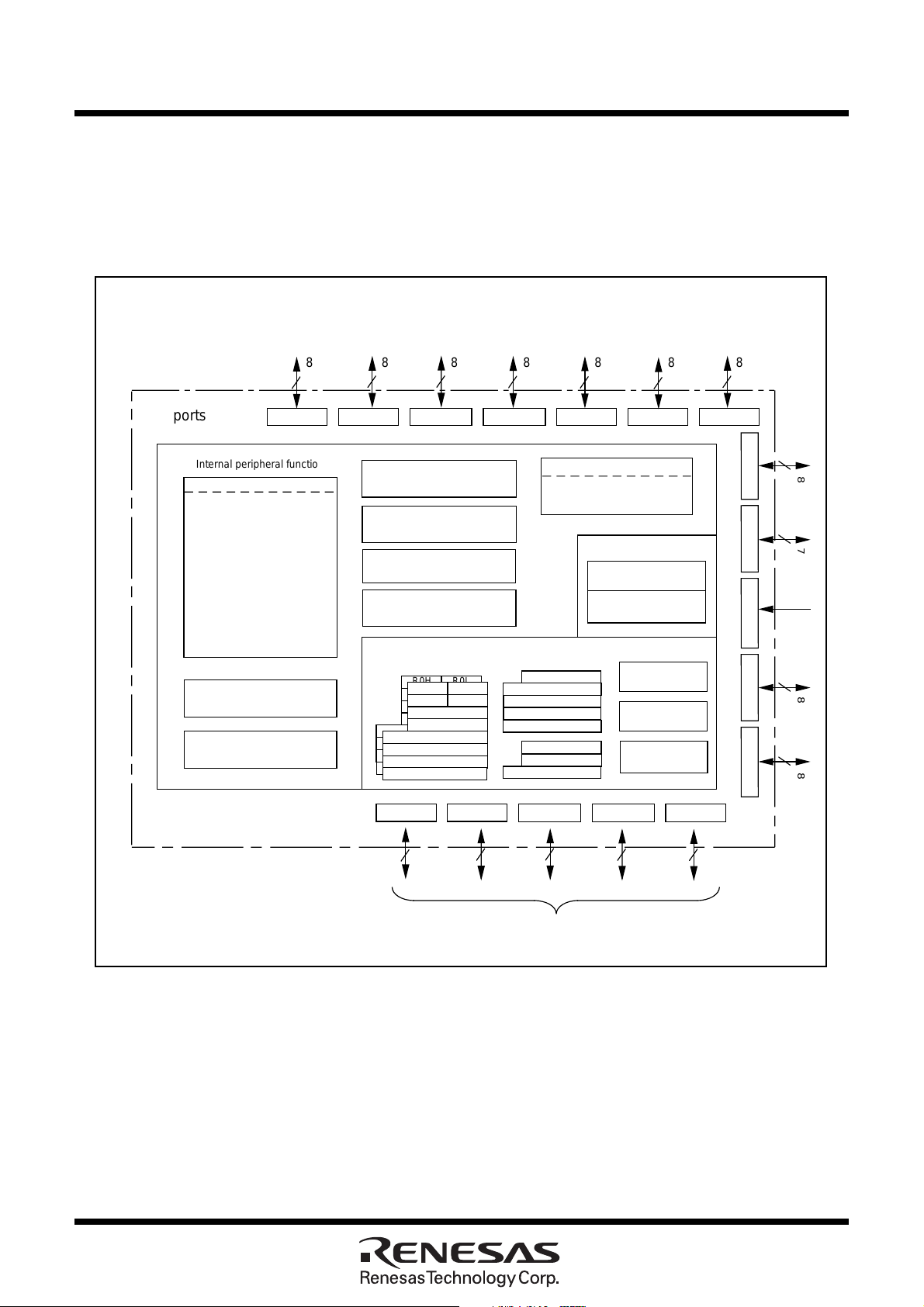

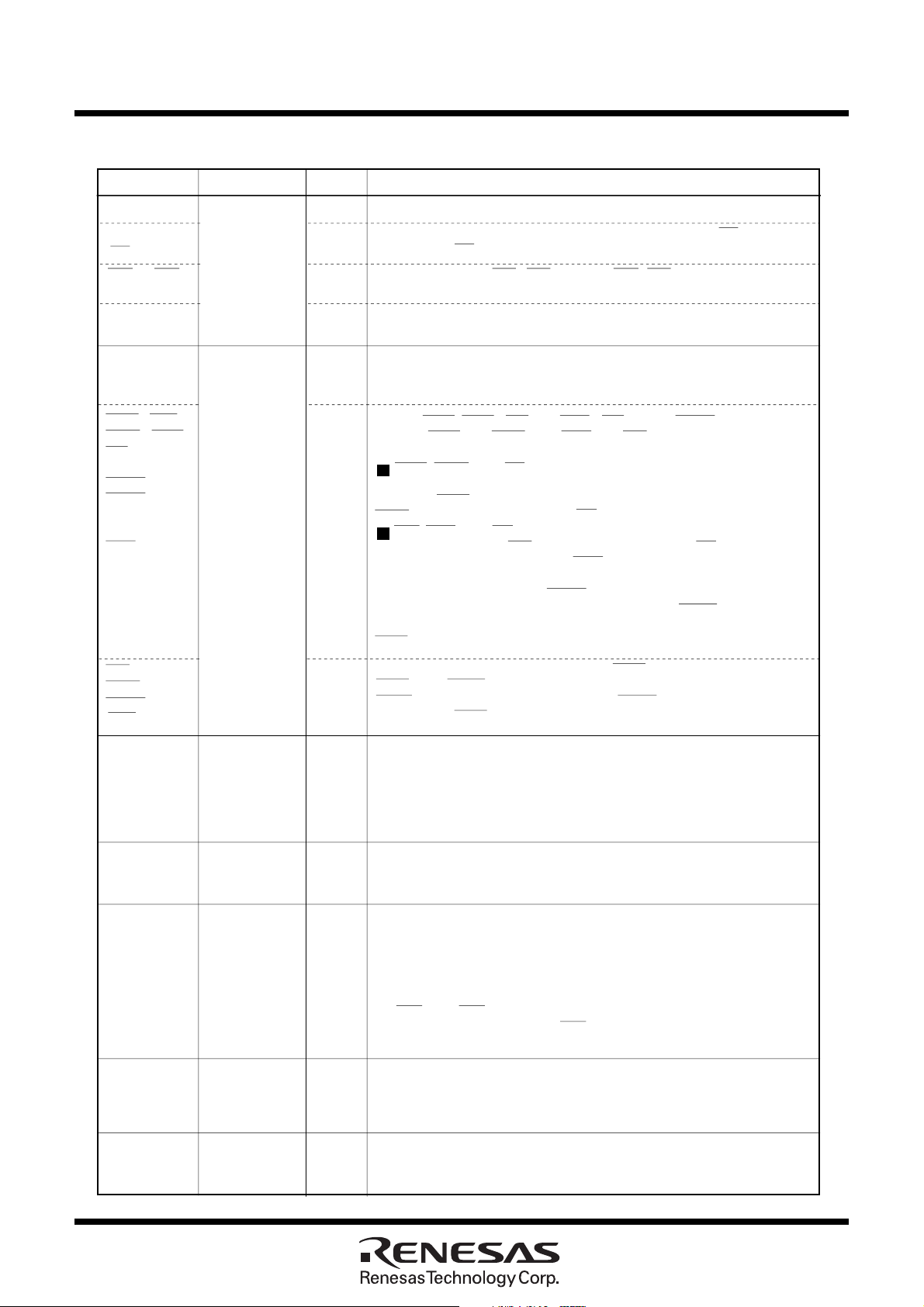

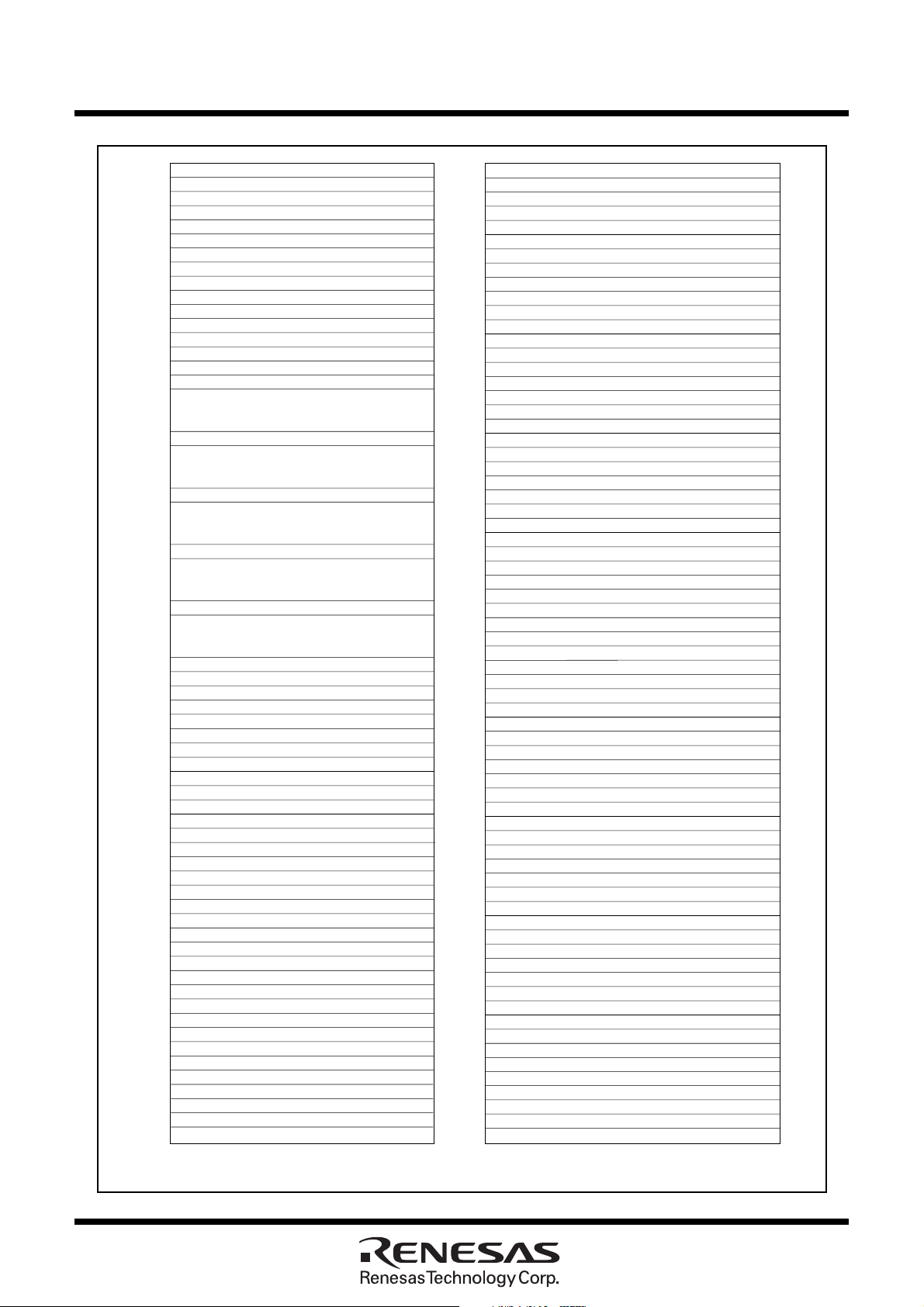

Block Diagram

Figure 1.1.4 is a block diagram of the M16C/80 group.

8888888

Preliminary Specifications REV.D

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

I/O ports

Port P0

Internal peripheral functions

Timer

Timer TA0 (16 bits)

Timer TA1 (16 bits)

Timer TA2 (16 bits)

Timer TA3 (16 bits)

Timer TA4 (16 bits)

Timer TB0 (16 bits)

Timer TB1 (16 bits)

Timer TB2 (16 bits)

Timer TB3 (16 bits)

Timer TB4 (16 bits)

Timer TB5 (16 bits)

Watchdog timer

(15 bits)

D-A converter

(8 bits X 2 channels)

Port P1

Expandable up to 10 channels)

UART /clock synchronous SI/O

CRC arithmetic circuit (CCITT)

Port P2

A-D converter

(10 bits X 8 channels

(8 bits X 5 channels)

X-Y converter

(16 bits X 16 bits)

Registers

R0LR0H

R0H R0L

R1H R1L

R2

R2

R3

A0

A1

FB

SB

Port P14

1216 5

(Polynomial : X +X +X +1)

M16C/80 series 16-bit CPU core

R1H R1L

Port P15

Port P3

Port P4

System clock generator

XIN - XOUT

XCIN - XCOUT

AAAAA

AAAAA

AAAAA

FLG

INTB

ISP

USP

PC

SVF

SVP

VCT

Port P13

Port P12

Port P5

Memory

ROM

(Note 1)

RAM

(Note 2)

DRAM

controller

DRAM

controller

Multiplier

AA

Port P6

Port P7

8

Port P8

7

Port P8

5

Port P9

8

Port P10

8

Port P11

Note 1: ROM size depends on MCU type.

Note 2: RAM size depends on MCU type.

Note 3: Ports P11 to P15 exist in 144-pin version.

Figure 1.1.4. Block diagram of the M16C/80 group

87885

(Note 3)

5

Under

development

Description

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

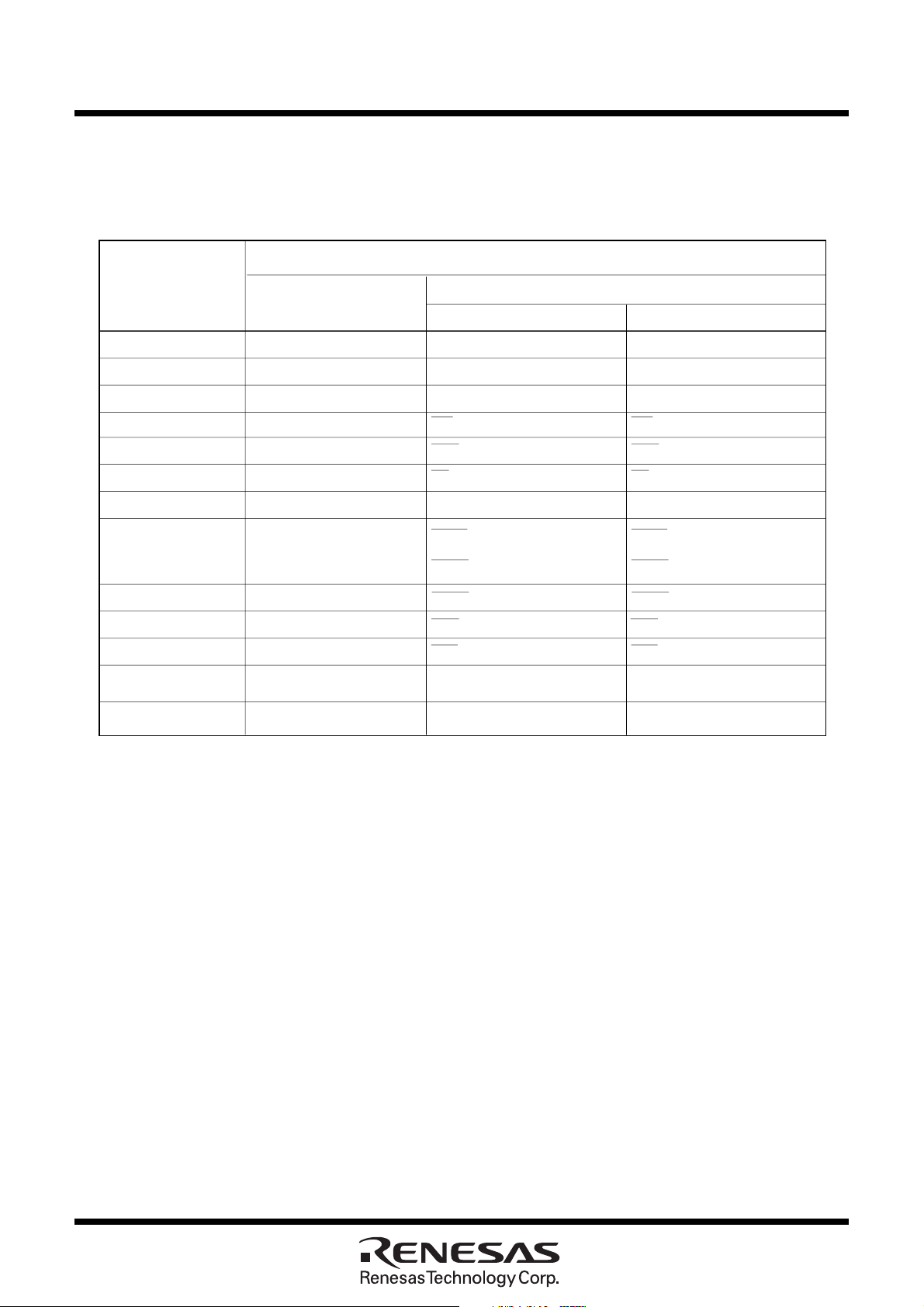

Performance Outline

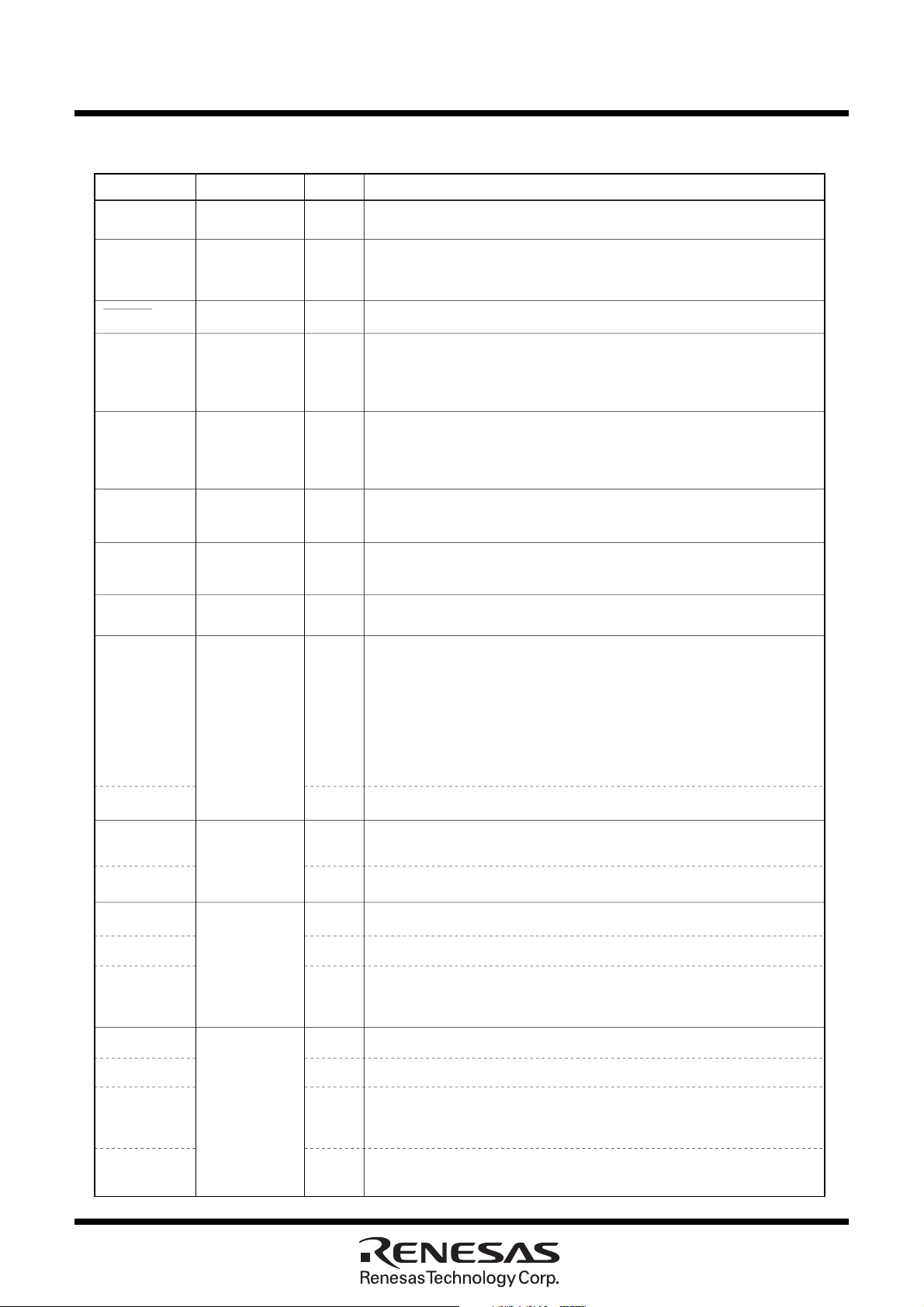

Table 1.1.1 is a performance outline of M16C/80 group.

Table 1.1.1. Performance outline of M16C/80 group

Item Performance

Number of basic instructions 106 instructions

Shortest instruction execution time 50ns(f(XIN)=20MHz)

Memory See ROM expansion figure.

capacity 10 to 24 K bytes

I/O port P0 to P10 (except P85) 8-bit x 10, 7-bit x 1

Input port 1 bit x 1

Multifunction 16 bits x 5

timer 16 bits x 6

Serial I/O (UART or clock synchronous) x 5

A-D converter 10 bits x (8 + 2) channels

D-A converter 8 bits x 2

DMAC 4 channels

DRAM controller CAS before RAS refresh, self-refresh, EDO, FP

CRC calculation circuit CRC-CCITT

X-Y converter 16 bits X 16 bits

Watchdog timer 15 bits x 1 (with prescaler)

Interrupt 29 internal and 8 external sources, 5 software sources, 7

Clock generating circuit 2 built-in clock generation circuits

Supply voltage 4.2 to 5.5V (f(XIN)=20MHz) Mask ROM, external ROM

Power consumption 45mA (f(XIN) = 20MHz without software wait,Vcc=5V)

I/O 5V

characteristics 5mA

Memory expansion Available (up to 16M bytes)

Operating ambient temperature –40 to 85oC

Device configuration CMOS high performance silicon gate

Package 100-pin and 144-pin plastic mold QFP

ROM

RAM

100-pin

144-pin

P85

TA0, TA1, TA2, TA3,TA4

TB0, TB1, TB2, TB3, TB4, TB5

UART0, UART1, UART2,

UART3, UART4

I/O withstand voltage

Output current

P0 to P15 (except P85) 8-bit x 13, 7-bit x 2, 5-bit x 1

levels

(built-in feedback resistance, and external ceramic or

quartz oscillator)

and flash memory versions

2.7 to 5.5V (f(XIN)=10MHz) Mask ROM, external ROM

and flash memory versions

Mask ROM 128 Kbytes version

6

Under

development

Description

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

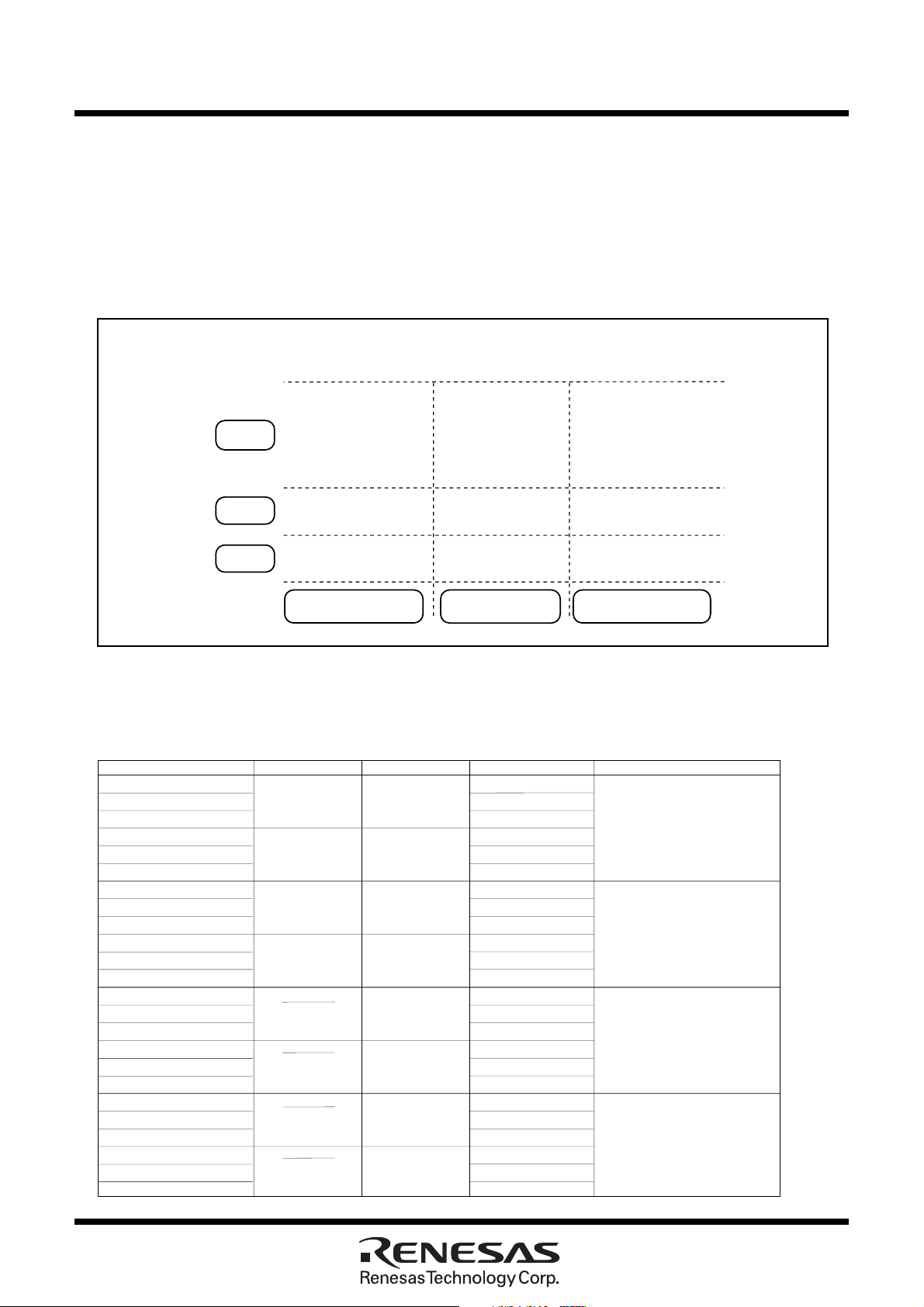

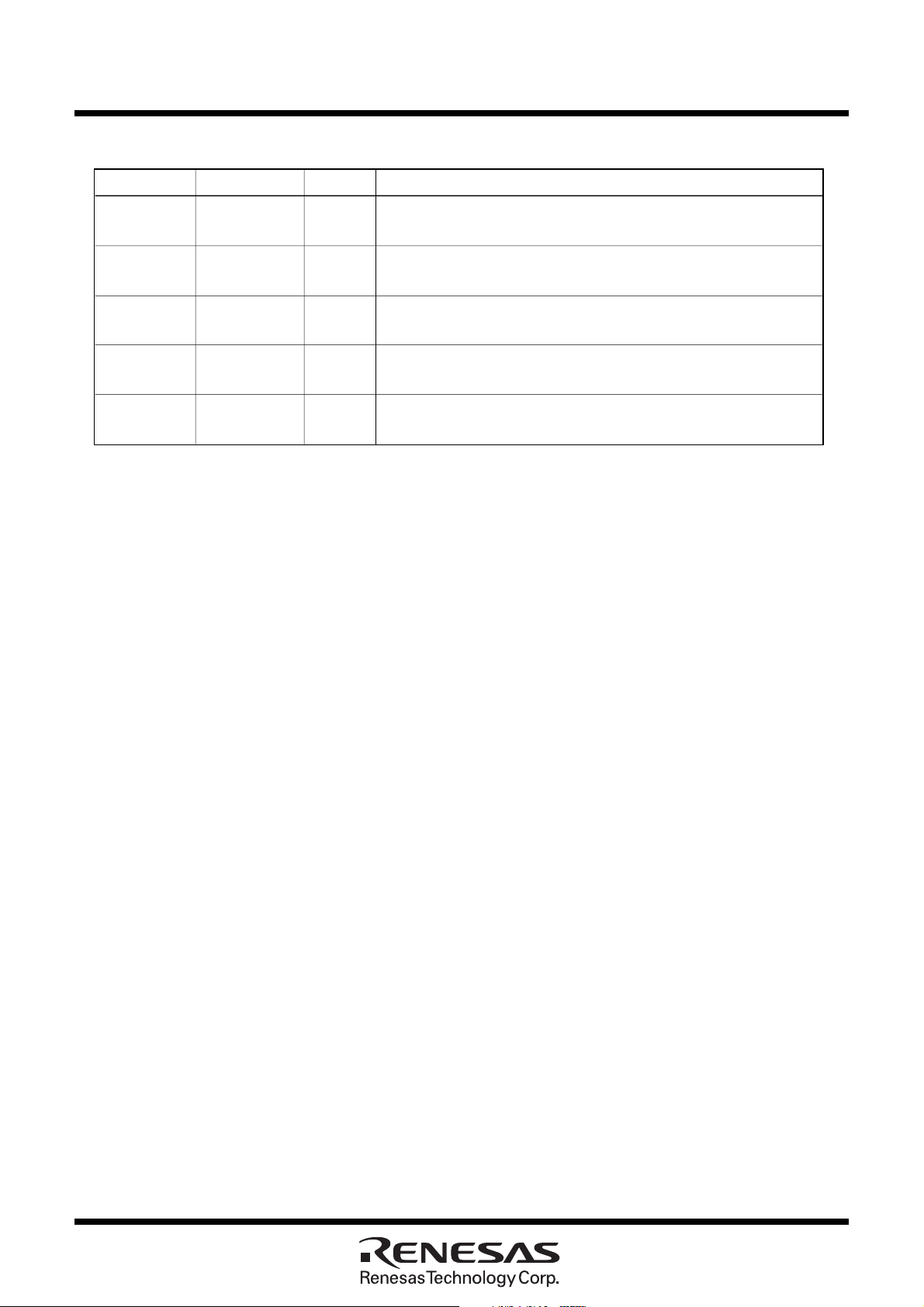

Mitsubishi plans to release the following products in the M16C/80 group:

(1) Support for mask ROM version, external ROM version and flash memory version

(2) ROM capacity

(3) Package

100P6S-A : Plastic molded QFP (mask ROM version and flash memory version)

100P6Q-A : Plastic molded QFP (mask ROM version and flash memory version)

144P6Q-A : Plastic molded QFP (mask ROM version and flash memory version)

ROM Size

(Byte)

M30805SGP-BL

M30803SFP/GP-BL

Preliminary Specifications REV.D

External

ROM

M30802SGP-BL

M30800SFP/GP-BL

M30805SGP

M30803SFP/GP

M30802SGP

M30800SFP/GP

Mitsubishi Microcomputers

M16C/80 group

256K

128K

M30803MG-XXXFP/GP

M30805MG-XXXGP

M30800MC-XXXFP/GP

M30802MC-XXXGP

Mask ROM version

M30803FGFP/GP

M30805FGGP

M30800FCFP/GP

M30802FCGP

Flash memory

version

External ROM version

Figure 1.1.5. ROM expansion

The M16C/80 group products currently supported are listed in Table 1.1.2.

Table 1.1.2. M16C/80 group

Type No

M30800MC-XXXFP

M30800MC-XXXGP

M30802MC-XXXGP

M30803MG-XXXFP

M30803MG-XXXGP

M30805MG-XXXGP

M30800FCFP

M30800FCGP

M30802FCGP

M30803FGFP

M30803FGGP

M30805FGGP

M30800SFP

M30800SGP

M30802SGP

M30803SFP

M30803SGP

M30805SGP

M30800SFP-BL

M30800SGP-BL

M30802SGP-BL

M30803SFP-BL

M30803SGP-BL

M30805SGP-BL

*

: New product

ROM capacity

128K bytes

256K bytes

128K bytes

256K bytes

*

RAM capacity

10K bytes 100P6S-A

20K bytes

10K bytes

20K bytes

10K bytes

*

*

24K bytes

*

*

10K bytes

*

*

*

24K bytes

*

*

Package type

100P6Q-A

144P6Q-A

100P6S-A

100P6Q-A

144P6Q-A

100P6S-A

100P6Q-A

144P6Q-A

100P6S-A

100P6Q-A

144P6Q-A

100P6S-A

100P6Q-A

144P6Q-A

100P6S-A

100P6Q-A

144P6Q-A

100P6S-A

100P6Q-A

144P6Q-A

100P6S-A

100P6Q-A

144P6Q-A

As of August, 2001

Remarks

Mask ROM version

Flash memory version

External ROM version

External ROM version

with built-in boot loader

7

Under

development

Description

Type No. M 3 0 8 0 2 M C – X X X G P – BL

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

Boot loader

Package type:

FP : Package 100P6S-A

GP : Package 100P6Q-A, 144P6Q-A

ROM No.

Omitted for blank external ROM version

and flash memory version

ROM capacity:

C : 128K bytes

G : 256K bytes

Memory type:

M : Mask ROM version

S : External ROM version

F : Flash memory version

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Figure 1.1.6. Type No., memory size, and package

Shows RAM capacity, pin count, etc

(The value itself has no specific meaning)

M16C/80 Group

M16C Family

8

Under

development

Pin Description

Specifications in this manual are tentative and subject to change.

Pin Description (1)

Preliminary Specifications REV.D

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Pin name

VCC, V

CNV

SS

RESET

X

IN

X

OUT

BYTE

AV

CC

AV

SS

V

REF

SS

Signal name

Power supply

input

CNV

SS

Reset input

Clock input

Clock output

External data

bus width

select input

Analog power

supply input

Analog power

supply input

Reference

voltage input

I/O type

I

I

I

O

I

I

Function

CC

Supply 4.2 (2.7) to 5.5 V to the V

This pin switches between processor modes. Connect it to the V

pin. Supply 0 V to the VSS pin.

SS

when operating in single-chip or memory expansion mode after reset.

Connect it to the V

CC

when in microprocessor mode after reset.

An “L” on this input resets the microcomputer.

These pins are provided for the main clock generating circuit. Connect

a ceramic resonator or crystal between the X

use an externally derived clock, input it to the X

X

OUT

pin open.

IN

and the X

IN

pin and leave the

OUT

pins. To

This pin selects the width of an data bus in the external area 3. A 16-

-bit width is selected when this input is “L”; an 8-bit width is selected

when this input is “H”. This input must be fixed to either “H” or “L”.

When not using the external bus, connect this pin to V

SS

.

This pin is a power supply input for the A-D converter. Connect this

pin to V

CC

.

This pin is a power supply input for the A-D converter. Connect this

pin to V

SS

.

This pin is a reference voltage input for the A-D converter.

P00 to P0

D0 to D

7

P10 to P1

D8 to D

15

P20 to P2

A0 to A

7

A0/D0 to

A

P30 to P3

A8 to A

15

A8/D8 to

A

15/D15

7

7

7

7/D7

7

I/O port P0

I/O port P1

I/O port P2

I/O port P3

I/O

This is an 8-bit CMOS I/O port. It has an input/output port direction

register that allows the user to set each pin for input or output

individually. When set for input in single chip mode, the user can

specify in units of four bits via software whether or not they are tied to

a pull-up resistance. In memory expansion and microprocessor

mode, an built-in pull-up resistance cannot be used. However, it is

possible to select pull-up resistance presence to the usable port as I/

O port by setting.

When set as a separate bus, these pins input and output data (D

I/O

This is an 8-bit I/O port equivalent to P0. P1

I/O

5

to P17 also function as

external interrupt pins as selected by software.

When set as a separate bus, these pins input and output data

I/O

This is an 8-bit I/O port equivalent to P0.

I/O

0–A7

O

These pins output 8 low-order address bits (A

If a multiplexed bus is set, these pins input and output data (D

I/O

and output 8 low-order address bits (A

0–A7

).

) separated in time by

multiplexing.

This is an 8-bit I/O port equivalent to P0.

I/O

These pins output 8 middle-order address bits (A

O

If the external bus is set as a 16-bit wide multiplexed bus, these pins

I/O

input and output data (D

bits (A

8–A15

) separated in time by multiplexing.

8–D15

) and output 8 middle-order address

8–A15

0–D7

).

(D8–D15).

0–D7

)

).

MA0 to MA7

If accessing to DRAM area, these pins output row address and

O

column address separated in time by multiplexing.

9

Under

development

Pin Description

Specifications in this manual are tentative and subject to change.

Pin Description (2)

Preliminary Specifications REV.D

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Signal name FunctionPin name I/O type

P40 to P4

7

A16 to A22,

23

A

0

to CS

CS

3

MA8 to MA12

P5

0

to P5

7

WRL / WR,

WRH / BHE,

RD,

BCLK,

HLDA,

HOLD,

ALE,

RDY

I/O port P4 This is an 8-bit I/O port equivalent to P0.I/O

O

O

O

I/O port P5 I/O

O

O

O

O

O

O

I

These pins output 8 high-order address bits (A

23

address bit (A

) outputs inversely.

16–A22

, A23). Highest

These pins output CS0–CS3 signals. CS0–CS3 are chip select

signals used to specify an access space.

If accessing to DRAM area, these pins output row address and

column address separated in time by multiplexing.

This is an 8-bit I/O port equivalent to P0. P53 in this port outputs a

IN

divide-by-8 or divide-by-32 clock of X

CIN

frequency as X

as selected by software.

or a clock of the same

Output WRL, WRH (WR and BHE), RD, BCLK, HLDA, and ALE

signals. WRL and WRH, and BHE and WR can be switched using

software control.

WRL, WRH, and RD selected

With a 16-bit external data bus, data is written to even addresses

I

when the WRL signal is “L” and to the odd addresses when the

WRH signal is “L”. Data is read when RD is “L”.

WR, BHE, and RD selected

Data is written when WR is “L”. Data is read when RD is “L”. Odd

addresses are accessed when BHE is “L”. Use this mode when

using an 8-bit external data bus.

While the input level at the HOLD pin is “L”, the microcomputer is

placed in the hold state. While in the hold state, HLDA outputs an “L”

level. ALE is used to latch the address. While the input level of the

RDY pin is “L”, the bus of microcomputer is in the wait state.

DW,

CASL,

CASH,

RAS

P60 to P6

P70 to P77

0

to P84,

P8

6

,

P8

7

,

P8

5

P8

P90 to P9

7

7

I/O port P6

I/O port P7

I/O port P8

I/O port P8

I/O port P9

O

O

O

O

I/O

When accessing to DRAM area while DW signal is “L”, write to DRAM.

CASL and CASH show timing when latching to line address. When

CASL accesses to even address, and CASH to odd, these two pins

become “L”. RAS signal shows timing when latching to row address.

This is an 8-bit I/O port equivalent to P0. When set for input in single

chip mode, microprocessor mode and memory expansion mode the

user can specify in units of four bits via software whether or not they

are tied to a pull-up resistance. Pins in this port also function as

UART0 and UART1 I/O pins as selected by software.

0

I/O

This is an 8-bit I/O port equivalent to P6 (P7

open drain output). Pins in this port also function as timer A

and P71 are N-channel

0–A3

,

timer B5 or UART2 I/O pins as selected by software.

I/O

I/O

I/O

5

P80 to P84, P86, and P87 are I/O ports with the same functions as P6.

Using software, they can be made to function as the I/O pins for timer

6

A4 and the input pins for external interrupts. P8

and P87 can be set

using software to function as the I/O pins for a sub clock generation

circuit. In this case, connect a quartz oscillator between P8

I

pin) and P8

7

(X

CIN

pin). P85 is an input-only port that also functions

6

(X

COUT

for NMI. The NMI interrupt is generated when the input at this pin

changes from “H” to “L”. The NMI function cannot be canceled using

software. The pull-up cannot be set for this pin.

I/O

This is an 8-bit I/O port equivalent to P6. Pins in this port also

function as UART3 and UART4 I/O pins, Timer B0–B4 input pins, D-A

converter output pins, A-D converter extended input pins, or A-D

trigger input pins as selected by software.

P100 to P10

10

7

I/O port P10

I/O

This is an 8-bit I/O port equivalent to P6. Pins in this port also

4

function as A-D converter input pins. Furthermore, P10

–P107 also

function as input pins for the key input interrupt function.

Under

development

Pin Description

Specifications in this manual are tentative and subject to change.

Pin Description (3)

(Note)

Preliminary Specifications REV.D

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Signal name FunctionPin name I/O type

II/OI/O port P11P110 to P114 This is an 5-bit I/O port equivalent to P6.

0

to P127 This is an 8-bit I/O port equivalent to P6.

(Note)

(Note)

0

to P146 This is an 7-bit I/O port equivalent to P6.

(Note)

(Note)

II/OI/O port P12P12

II/OI/O port P13P130 to P137 This is an 8-bit I/O port equivalent to P6.

II/OI/O port P14P14

II/OI/O port P15P150 to P157 This is an 8-bit I/O port equivalent to P6.

Note : Port P11 to P15 exist in 144-pin version.

11

Under

A

A

development

Memory

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

Operation of Functional Blocks

The M16C/80 group accommodates certain units in a single chip. These units include ROM and RAM to

store instructions and data and the central processing unit (CPU) to execute arithmetic/logic operations.

Also included are peripheral units such as timers, serial I/O, D-A converter, DMAC, CRC calculation circuit,

A-D converter, DRAM controller and I/O ports.

The following explains each unit.

Memory

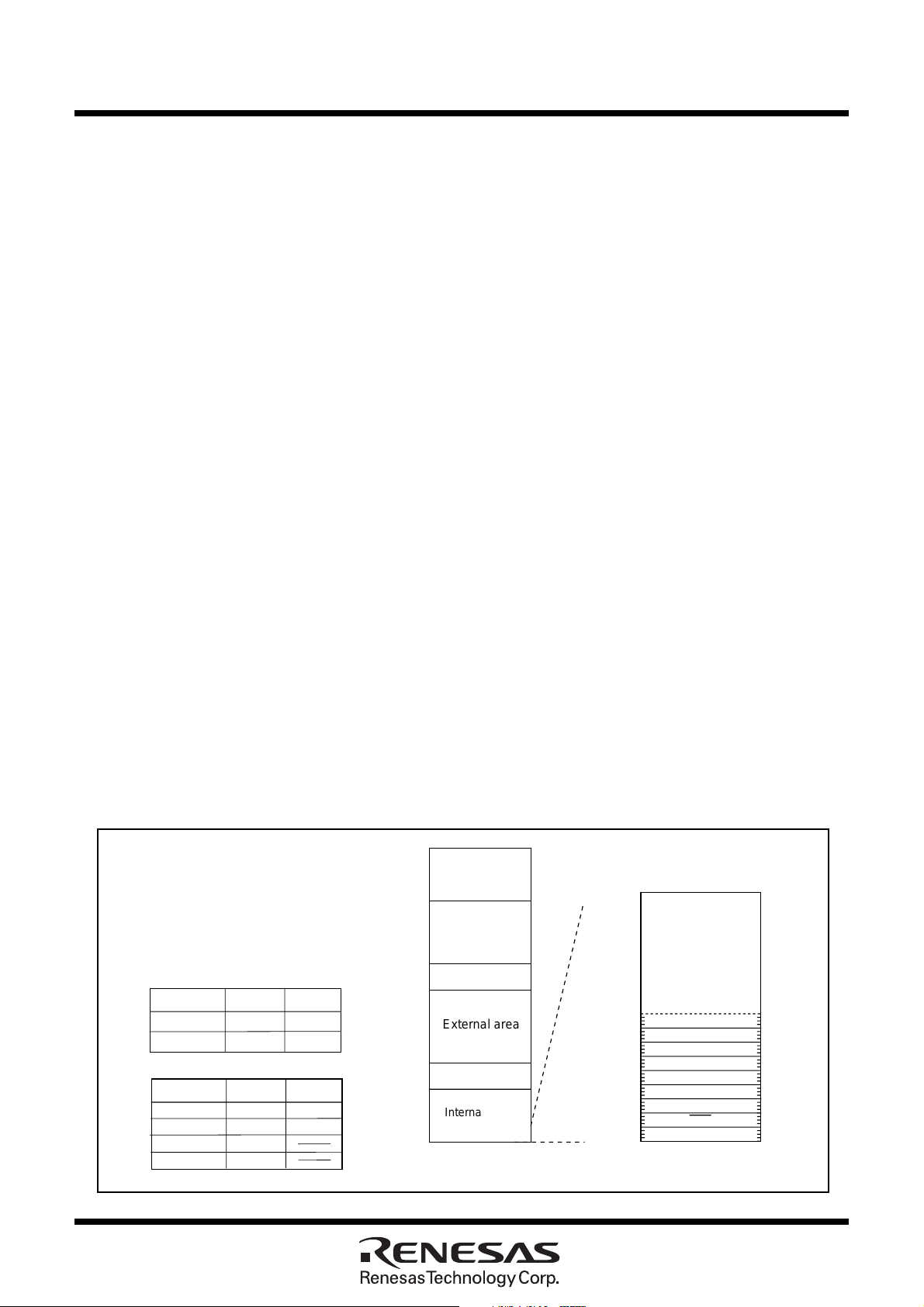

Figure 1.2.1 is a memory map of the M16C/80 group. The address space extends the 16 Mbytes from

address 00000016 to FFFFFF16. From FFFFFF16 down is ROM. For example, in the M30800MC-XXXFP,

there is 128K bytes of internal ROM from FE000016 to FFFFFF16. The vector table for fixed interrupts such

as the reset and NMI are mapped to FFFFDC16 to FFFFFF16. The starting address of the interrupt routine

is stored here. The address of the vector table for timer interrupts, etc., can be set as desired using the

internal register (INTB). See the section on interrupts for details.

From 00040016 up is RAM. For example, in the M30800MC-XXXFP, 10 Kbytes of internal RAM is mapped

to the space from 00040016 to 002BFF16. In addition to storing data, the RAM also stores the stack used

when calling subroutines and when interrupts are generated.

The SFR area is mapped to 00000016 to 0003FF16. This area accommodates the control registers for

peripheral devices such as I/O ports, A-D converter, serial I/O, and timers, etc. Figure 1.5.1 to 1.5.4 are

location of peripheral unit control registers. Any part of the SFR area that is not occupied is reserved and

cannot be used for other purposes.

The special page vector table is mapped to FFFE0016 to FFFFDB16. If the starting addresses of subroutines or the destination addresses of jumps are stored here, subroutine call instructions and jump instructions can be used as 2-byte instructions, reducing the number of program steps.

In memory expansion mode and microprocessor mode, a part of the spaces are reserved and cannot be

used. For example, in the M30800MC-XXXFP, the following spaces cannot be used.

• The space between 002C0016 and 00800016 (Memory expansion and microprocessor modes)

• The space between F0000016 and FDFFFF16 (Memory expansion mode)

_______

<100-pin version>

Type No.

M30800MC/FC

M30803MG/FG

<144-pin version>

Type No.

M30802MC/FC

M30805MG/FG

M30802S

M30805S

Address

XXXXX

002BFF

0053FF

Address

XXXXX

002BFF

0053FF

002BFF

0063FF

Figure 1.2.1. Memory map

12

000000

16

000400

16

XXXXXX

Address

YYYYY

FE0000

FC0000

Address

YYYYY

FE0000

FC0000

16

16

16

16

16

16

16

16

16

008000

16

16

16

F00000

16

YYYYYY

16

16

16

FFFFFF

Note 1: During memory expansion and microprocessor modes, can not be used.

Note 2: In memory expansion mode, can not be used.

SFR area

For details, see

Figures 1.5.1 to

Internal RAM

16

Internal reserved

area (Note 1)

AAA

External area

AAA

Internal reserved

area (Note 2)

16

Internal ROM

16

1.5.4

area

area

FFFE00

FFFFDC

FFFFFF

16

Special page

vector table

16

Undefined instruction

Overflow

BRK instruction

Address match

Watchdog timer

16

Reset

NMI

Under

development

CPU

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

Central Processing Unit (CPU)

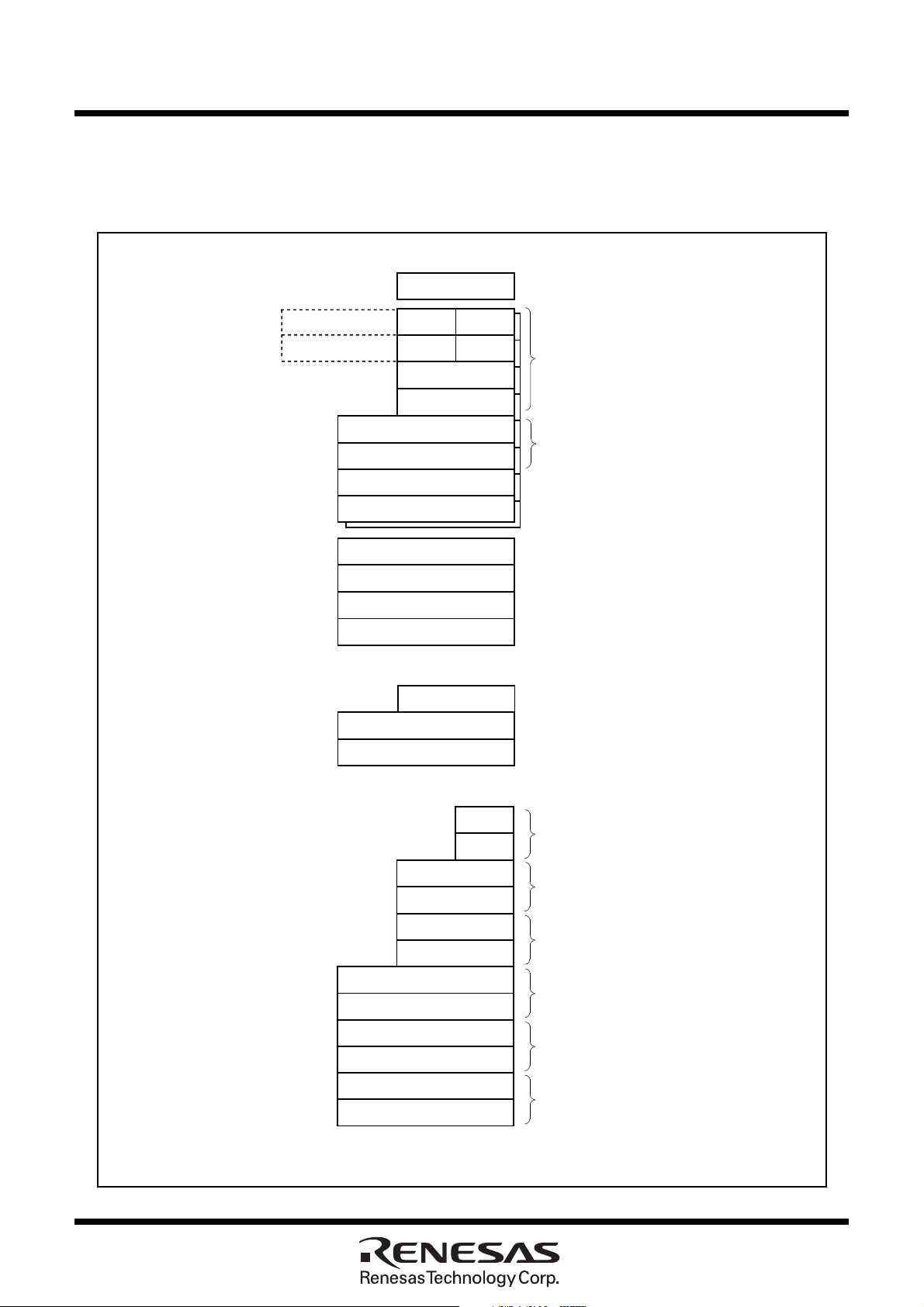

The CPU has a total of 28 registers shown in Figure 1.3.1. Eight of these registers (R0, R1, R2, R3, A0, A1,

SB and FB) come in two sets; therefore, these have two register banks.

General register

b31

R2

R3

b23

High-speed interrupt register

b23

b15 b0

FLG

R0H

R1H

A0

A1

SB

FB

USP

ISP

INTB

PC

b15 b0

SVP

R0L

R1L

R2

R3

SVF

Flag register

Data register (Note)

Address register (Note)

Static base register (Note)

Frame base register (Note)

User stack pointer

Interrupt stack pointer

Interrupt table register

Program counter

Flag save register

PC save register

VCT

DMAC related register

b15

b23

DMA0

DMA1

DSA0

DSA1

DRA0

DRA1

Note: These registers have two register banks.

Figure 1.3.1. Central processing unit register

b7 b0

DMD0

DMD1

DCT0

DCT1

DRC0

DRC1

Vector register

DMA mode register

DMA transfer count register

DMA transfer count reload register

DMA memory address register

DMA SFR address register

DMA memory address reload register

13

Under

development

CPU

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

(1) Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, R3, R2R0 and R3R1)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and

arithmetic/logic operations.

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H/R1H),

and low-order bits as (R0L/R1L). Registers R2 and R0, as well as R3 and R1 can use as 32-bit data

registers (R2R0/R3R1).

(2) Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 24 bits, and have functions equivalent to those of data

registers. These registers can also be used for address register indirect addressing and address register

relative addressing.

(3) Static base register (SB)

Static base register (SB) is configured with 24 bits, and is used for SB relative addressing.

(4) Frame base register (FB)

Frame base register (FB) is configured with 24 bits, and is used for FB relative addressing.

(5) Program counter (PC)

Program counter (PC) is configured with 24 bits, indicating the address of an instruction to be executed.

(6) Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 24 bits, indicating the start address of an interrupt vector

table.

(7) User stack pointer (USP), interrupt stack pointer (ISP)

Stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each configured with 24 bits.

Your desired type of stack pointer (USP or ISP) can be selected by a stack pointer select flag (U flag).

This flag is located at the position of bit 7 in the flag register (FLG).

Set USP and ISP to an even number so that execution efficiency is increased.

(8) Save flag register (SVF)

This register consists of 16 bits and is used to save the flag register when a high-speed interrupt is

generated.

14

Under

development

CPU

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

(9) Save PC register (SVP)

This register consists of 24 bits and is used to save the program counter when a high-speed interrupt is

generated.

(10) Vector register (VCT)

This register consists of 24 bits and is used to indicate the jump address when a high-speed interrupt is

generated.

(11) DMA mode registers (DMD0/DMD1)

These registers consist of 8 bits and are used to set the transfer mode, etc. for DMA.

(12) DMA transfer count registers (DCT0/DCT1)

These registers consist of 16 bits and are used to set the number of DMA transfers performed.

(13) DMA transfer count reload registers (DRC0/DRC1)

These registers consist of 16 bits and are used to reload the DMA transfer count registers.

(14) DMA memory address registers (DMA0/DMA1)

These registers consist of 24 bits and are used to set a memory address at the source or destination of

DMA transfer.

(15) DMA SFR address registers (DSA0/DSA1)

These registers consist of 24 bits and are used to set a fixed address at the source or destination of DMA

transfer.

(16) DMA memory address reload registers (DRA0/DRA1)

These registers consist of 24 bits and are used to reload the DMA memory address registers.

15

Under

development

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

CPU

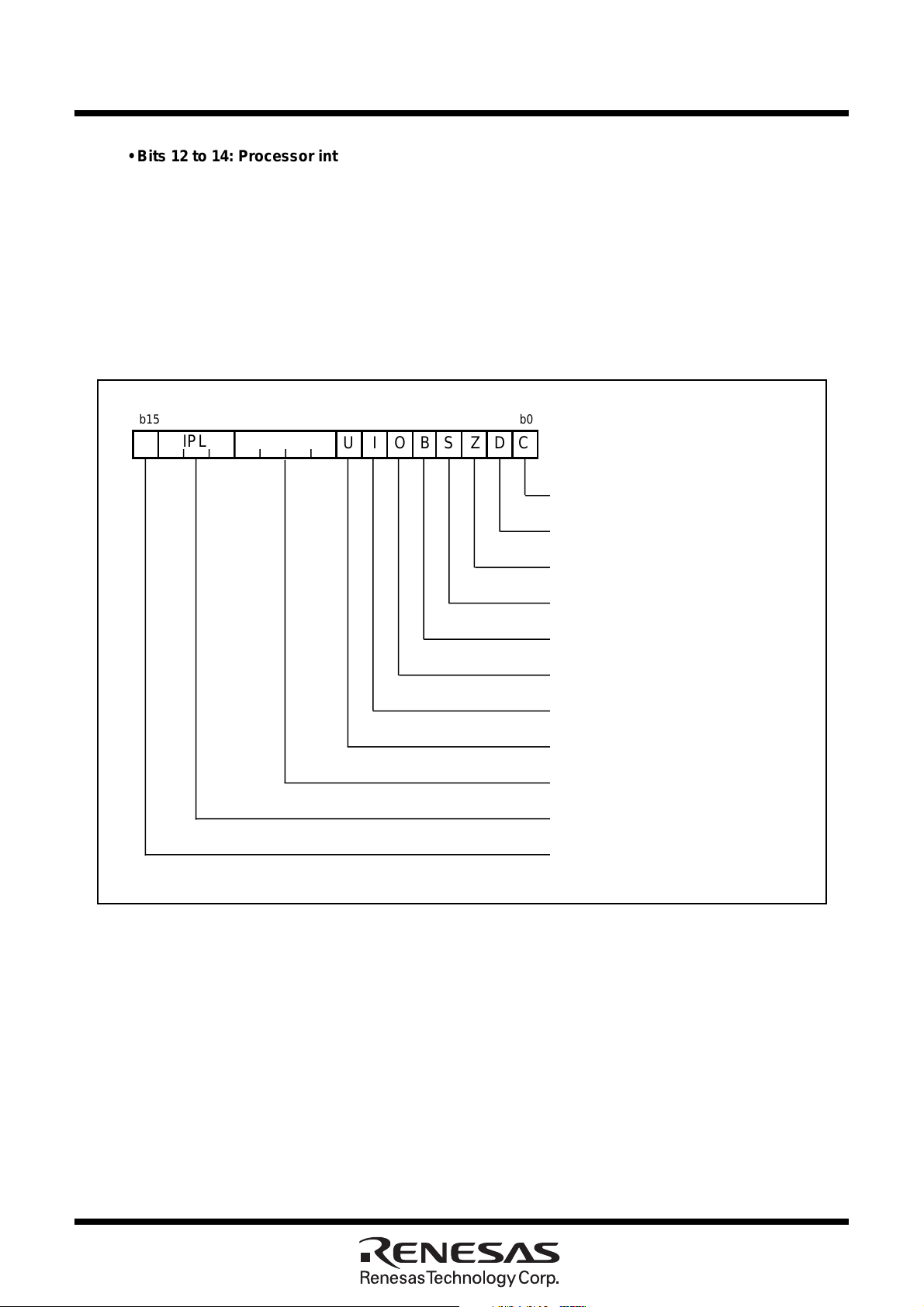

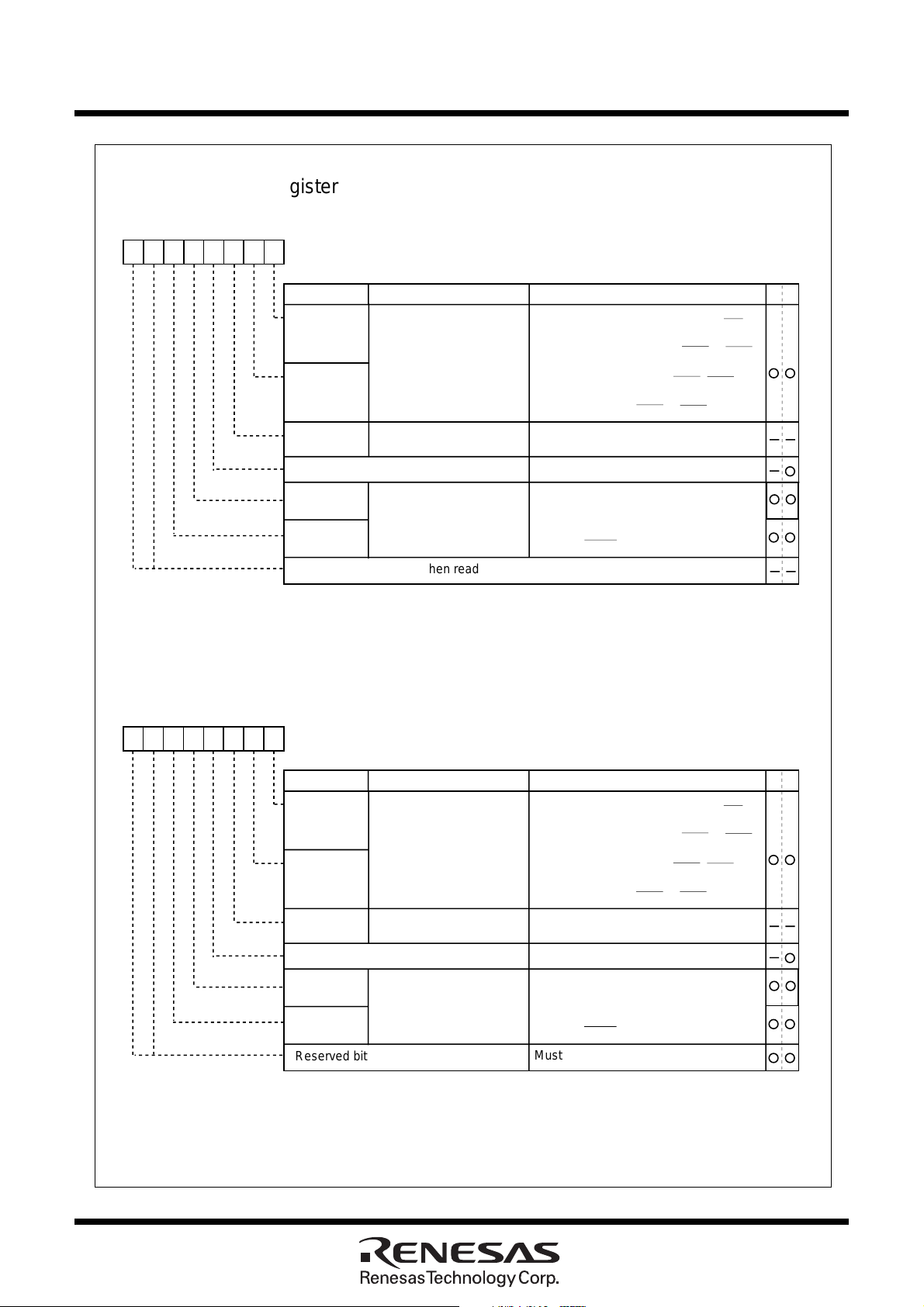

(17) Flag register (FLG)

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.3.2 shows the flag

register (FLG). The following explains the function of each flag:

• Bit 0: Carry flag (C flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

• Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is “1”, a single-step interrupt is generated after instruction execution. This flag is

cleared to “0” when the interrupt is acknowledged.

• Bit 2: Zero flag (Z flag)

This flag is set to “1” when an arithmetic operation resulted in 0; otherwise, cleared to “0”.

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

• Bit 3: Sign flag (S flag)

This flag is set to “1” when an arithmetic operation resulted in a negative value; otherwise, cleared

to “0”.

• Bit 4: Register bank select flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when this flag is “0” ; register bank

1 is selected when this flag is “1”.

• Bit 5: Overflow flag (O flag)

This flag is set to “1” when an arithmetic operation resulted in overflow; otherwise, cleared to “0”.

• Bit 6: Interrupt enable flag (I flag)

This flag enables a maskable interrupt.

An interrupt is disabled when this flag is “0”, and is enabled when this flag is “1”. This flag is

cleared to “0” when the interrupt is acknowledged.

• Bit 7: Stack pointer select flag (U flag)

Interrupt stack pointer (ISP) is selected when this flag is “0” ; user stack pointer (USP) is selected

when this flag is “1”.

This flag is cleared to “0” when a hardware interrupt is acknowledged or an INT instruction of

software interrupt Nos. 0 to 31 is executed.

16

• Bits 8 to 11: Reserved area

Under

development

CPU

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

• Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight

processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt

is enabled.

• Bit 15: Reserved area

b0b15

IPL

Flag register (FLG)

CDZSBOIU

Carry flag

Figure 1.3.2. Flag register (FLG)

Debug flag

Zero flag

Sign flag

Register bank select flag

Overflow flag

Interrupt enable flag

Stack pointer select flag

Reserved area

Processor interrupt priority level

Reserved area

17

Under

development

Reset

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Mitsubishi Microcomputers

M16C/80 group

Reset

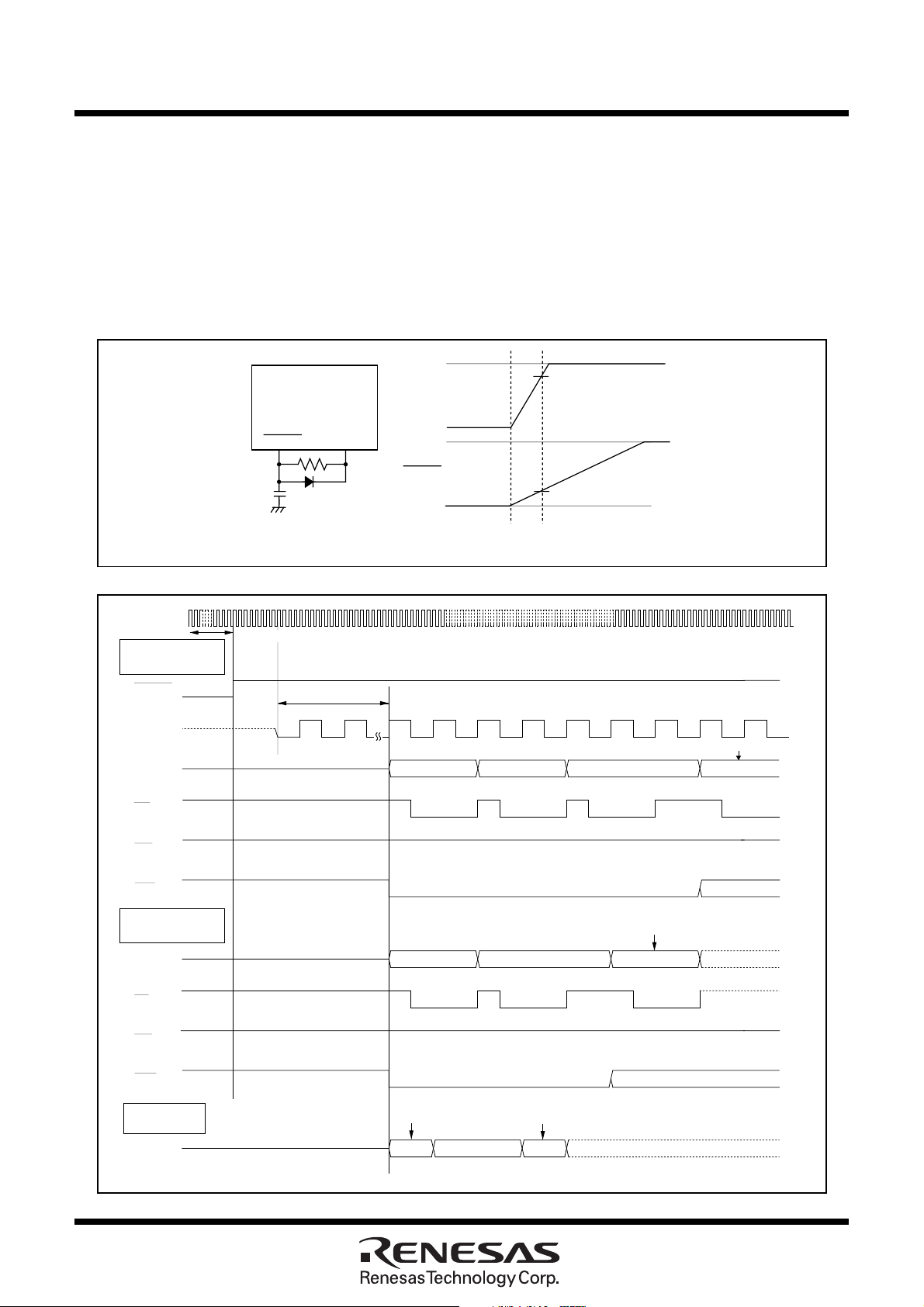

There are two kinds of resets; hardware and software. In both cases, operation is the same after the reset.

(See “Software Reset” for details of software resets.) This section explains on hardware resets.

When the supply voltage is in the range where operation is guaranteed, a reset is effected by holding the

reset pin level “L” (0.2VCC max.) for at least 20 cycles. When the reset pin level is then returned to the “H”

level while main clock is stable, the reset status is cancelled and program execution resumes from the

address in the reset vector table.

Figure 1.4.1 shows the example reset circuit. Figure 1.4.2 shows the reset sequence.

RESET

Example when f(XIN) = 10MHz and V

V

Figure 1.4.1. Example reset circuit

X

IN

More than 20 cycles are needed

Microprocessor

mode BYTE = “H”

RESET

BCLK

Address

RD

BCLK 24cycles

CC

5V

V

CC

0V

5V

RESET

0V

FFFFC

CC

= 5V

16

4.2V

0.8V

.

Content of reset vector

FFFFD

16

FFFFE

16

WR

CS0

Microprocessor

mode BYTE = “L”

Address

RD

WR

CS0

Single chip

mode

Address

Figure 1.4.2. Reset sequence

18

FFFFC

FFFFC

16

16

FFFFE

FFFFE

16

Content of reset vector

16

Content of reset vector

Under

development

Reset

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

Table 1.4.1 shows the statuses of the other pins while the RESET pin level is “L”. Figures 1.4.3 and 1.4.4

____________

show the internal status of the microcomputer immediately after the reset is cancelled.

Table 1.4.1. Pin status when RESET pin level is “L”

____________

Status

Pin name

P0

P1

P2, P3, P4

P5

0

P5

1

P5

2

P5

3

P5

4

CNVSS = V

Input port (floating)

Input port (floating)

Input port (floating)

Input port (floating)

Input port (floating)

Input port (floating)

Input port (floating)

Input port (floating)

SS

CNVSS = V

BYTE = V

SS

Data input (floating)

Data input (floating)

Address output (undefined)

WR output (“H” level is output)

BHE output (undefined)

RD output (“H” level is output)

BCLK output

HLDA output (The output value

depends on the input to the

HOLD pin)

CC

BYTE = V

CC

Data input (floating)

Input port (floating)

Address output (undefined)

WR output (“H” level is output)

BHE output (undefined)

RD output (“H” level is output)

BCLK output

HLDA output (The output value

depends on the input to the

HOLD pin)

P5

5

P5

6

P5

7

P6, P7, P80 to P84,

P8

6

, P87, P9, P10,

P11, P12, P13,

P14, P15 (Note)

Input port (floating)

Input port (floating)

Input port (floating)

Input port (floating)

Input port (floating) Input port (floating) Input port (floating)

Note :Port P11 to P15 exist in 144-pin vrsion.

HOLD input (floating)

RAS output

RDY input (floating)

HOLD input (floating)

RAS output

RDY input (floating)

Input port (floating) Input port (floating)

19

Under

development

Reset

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

(1) (0004

(2) (000516)···Processor mode register 1

(3) (0006

(4) (0007

(5) (0008

Address match interrupt

(6) (0009

enable register

(7) Protect register (000A

External data bus width control

(8)

register (Note 2)

(9)

(10)

(11)

(000B

(000C

(000F16)···Watchdog timer control register 00?0????

(0010

(0011

(0012

(12)

(0014

(0015

(001616)···

(13)

Address match interrupt register 2

(0018

(001916)···

(001A16)···

(14)

Address match interrupt register 3

(001C16)···

(001D16)···

(001E16)···

(15)

(16)

DMA0 interrupt control register

(17)

Timer B5 interrupt control register

(18)

DMA2 interrupt control register

UART2 receive/ACK interrupt control

(19)

register

(20)

Timer A0 interrupt control register

UART3 receive/ACK interrupt control

(21)

register

(22)

Timer A2 interrupt control register

UART4 receive/ACK interrupt control

(23)

register

(24)

Timer A4 interrupt control register

Bus collision detection(UART3)

(25)

interrupt control register

UART0 receive interrupt control

(26)

register

A-D conversion interrupt

(27)

control register

UART1 receive interrupt control

(28)

register

(29)

Timer B1 interrupt control register

The content of other registers and RAM is undefined when the microcomputer is reset. The initial values

must therefore be set.

Note 1: When the V

Note 2: When the BYTE pin is "L", the third bit is "1". When the BYTE pin is "H", the third bit is "0".

(004016)···DMAM control register

(0068

(0069

(006A

(006B

(006C

(006D

(006E

(006F

(0070

(0071

(0072

(0073

(0074

(0076

CC

level is applied to the CNVSS pin, it is 0316 at a reset.

16

)···Processor mode register 0 (Note1) 80

16

)···System clock control register 0

16

)···System clock control register 1

16

)···Wait control register

16

)···

16

)···

16

)···

16

)···Main clock divided register

16

)···Address match interrupt register 0

16

)···

16

)···

16

)···Address match interrupt register 1

16

)···

16

)···

00

08

20

FF

01

00

00

00

00

00

00

00

00

00

00

00

00

16

16

16

16

16

00

00

000

000

?

000

16

16

16

16

16

16

16

16

16

16

16

16

?????

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

x : Nothing is mapped to this bit

? : Undefined

?000

?000

?000

?000

?000

?000

?000

0 0 0?

? 0 0 0

? 0 0 0

? 0 0 0

? 0 0 0

? 0 0 0

? 0 0 0

(30)

Timer B3 interrupt control register

(31)

INT5 interrupt control register

(32)

INT3 interrupt control register

(33)

INT1 interrupt control register

(34)

DMA1 interrupt control register

UART2 transmit/NACK interrupt

(35)

control register

(36)

DMA3 interrupt control register

UART3 transmit/NACK interrupt

(37)

control register

(38)

Timer A1 interrupt control register

UART4 receive/NACK interrupt

(39)

control register

(40)

Timer A3 interrupt control register

Bus collision detection(UART2)

(41)

interrupt control register

UART0 transmit interrupt control register

(42)

Bus collision detection(UART4)

(43)

interrupt control register

(44)

UART1 transmit interrupt control register

(45)

Key input interrupt control register

(46)

Timer B0 interrupt control register

(47)

Timer B2 interrupt control register

Timer B4 interrupt control register

(48)

(49)

INT4 interrupt control register

(50)

INT2 interrupt control register

(51)

INT0 interrupt control register

(52)

Exit priority register

(53)

XY control register

(54)

UART4 special mode register 3

(55)

UART4 special mode register 2

(56)

UART4 special mode register

(57)

UART4 transmit/receive mode register

(58)

UART4 transmit/receive control register 0

UART4 transmit/receive control register 1

(59)

(60)

Timer B3,4,5 count start flag

(61)

Three-phase PWM control register 0

(62)

Three-phase PWM control register 1

(63)

Three-phase output buffer register 0

(64)

Three-phase output buffer register 1

(65)

Timer B3 mode register

(66)

Timer B4 mode register

(67)

Timer B5 mode register

(007816)···

(007A

(007C

(007E

(0088

(0089

(008A

(008B

(008C

(008D

(008E

(008F

(0090

(0091

(0092

16

16

16

16

16

16

16

16

16

16

16

16

16

16

00

)···

00

)···

00

)···

)···

)···

)···

)···

)··· ? 0 0 0

)··· ? 0 0 0

)···

)···

)···

)···

)···

(009316)···

16

)···

(0094

16

)···

(0096

16

)··· ? 0 0 0

(0098

16

)··· ? 000

(009A

(009C

(009E

(009F

(02E0

(02F5

(02F6

16

16

16

16

16

16

00

)···

00

)···

00

)···

)···

)···

)···

(02F716)···

(02F816)···

(02FC16)···

(02FD16)···

(030016)···

000

(030816)··· 00

(0309

16

)···

000 ?0000

16

)··· 00

(030A

(030B16)···

16

)···

(031B

(031C

(031D

00? 0000

16

)···

00? 0000

16

)···

00? 0000

? 0 0 0

? 000

? 000

? 000

? 0 0 0

? 0 0 0

? 0 0 0

? 0 0 0

? 0 0 0

? 0 0 0

? 000

? 000

? 000

? 0 0 0

? 0 0 0

? 0 0 0

? 000

? 000

0 000

00

16

00

16

00

16

00

16

08

16

02

16

16

16

00

16

00

Figure 1.4.3. Device's internal status after a reset is cleared

20

Under

development

Reset

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

Mitsubishi Microcomputers

M16C/80 group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

(68)

Interrupt cause select register

(69)

UART3 special mode register 3

(70)

UART3 special mode register 2

(71)

UART3 special mode register

(72)

UART3 transmit/receive mode register

(73)

UART3 transmit/receive control register 0

(74)

UART3 transmit/receive control register 1

(75)

UART2 special mode register 3

(76)

UART2 special mode register 2

(77)

UART2 special mode register

(78)

UART2 transmit/receive mode register

(79)

UART2 transmit/receive control register 0

(80)

UART2 transmit/receive control register 1

Count start flag

(81)

Clock prescaler reset flag

(82)

One-shot start flag

(83)

Trigger select flag

(84)

Up-down flag

(85)

Timer A0 mode register

(86)

Timer A1 mode register

(87)

Timer A2 mode register

(88)

Timer A3 mode register

(89)

Timer A4 mode register

(90)

Timer B0 mode register

(91)

Timer B1 mode register

(92)

Timer B2 mode register

(93)

UART0 transmit/receive mode register

(94)

UART0 transmit/receive control register 0

(95)

UART0 transmit/receive control register 1

(96)

UART1 transmit/receive mode register

(97)

UART1 transmit/receive control register 0

(98)

UART1 transmit/receive control register 1

(99)

UART transmit/receive control register 2

(100)

(101)

(102)

DMA0 cause select register

(103)

DMA1 cause select register

(104)

(105)

DMA2 cause select register

(106)

DMA3 cause select register

(107)

A-D control register 2

A-D control register 0

(108)

(109)

A-D control register 1

(110)

D-A control register

(111)

Function select register C

The content of other registers and RAM is undefined when the microcomputer is reset. The initial values

must therefore be set.

Note 1:This register exists in the flash memory version.

Note 2:This register exists in 144-pin version.

(Note 1)

(Note 1)

(031F16)···

16

(0325

16

(0326

(0327

16

16

(0328

(032C16)···

(032D

16

(0335

16

(0336

16

16

(0337

(033816)···

16

(033C

(033D

16

16

(0340

16

(0341

16

(0342

(034316)···

16

(0344

16

(0356

(0357

16

16

(0358

16

(0359

16

(035A

16

(035B

16

(035C

(035D16)···

16

(0360

16

(0364

(0365

16

16

(0368

16

(036C

(036D16)···

(037016)···

(0377

16

16

(0378

(037916)···

16

(037A

(037B16)···

16

(0394

16

(0396

16

(0397

(039C

16

(03AF

16

)···

)···

)···

)···

00

00

00

00

08

)···

)···

)···

)···

02

0 00

00

00

00

)···

0010000

)···

)···

)···

)···

02

00

0

00

00

)···

)···

)···

)···

)···

)···

)···

)···

00

000 0?000

000 0?000

000 0?000

000 0?000

000 0?000

00? 0000

00? 0000

00? 0000

)···

)···

)···

)···

)···

00

08

02

00

08

02

00 00000

?

?

)···Flash memory control register 0

000010

)··· 0

)··· 0

)···

)···

)···

)···

)···

00

00

0

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

00000

16

16

000000

0?????(037616)···Flash memory control register 1

000000

0000000

000000

0000000

???

(112)

Function select register A0

(113)

Function select register A1

(114)

Function select register B0

(115)

Function select register B1

(116)

Function select register A2

(117)

Function select register A3

(118)

Function select register B2

(119)

Function select register B3

(120)

Port P6 direction register

(121)

Port P7 direction register

(122)

Port P8 direction register

Port P9 direction register

(123)

Port P10 direction register

(124)

(125)

Port P11 direction register

(126)

Port P12 direction register

(127)

Port P13 direction register

(128)

Port P14 direction register

(129)

Port P15 direction register

(130)

Pull-up control register 2

(131)

Pull-up control register 3

(132)

Pull-up control register 4

(133)

Port P0 direction register

(132)

Port P1 direction register

(135)

Port P2 direction register

(136)

Port P3 direction register

(137)

Port P4 direction register

(138)

Port P5 direction register

(139)

Pull-up control register 0

(140)

Pull-up control register 1

(141)

Port control register

(142)

Data registers (R0/R1/R2/R3)

(143)

Address registers (A0/A1)

Static base register (SB)

(144)

Frame base register (FB)

(145)

Interrupt table register (INTB)

(146)

User stack pointer (USP)

(147)

(148)

Interrupt stack pointer (ISP)

Flag register (FLG)

(149)

(150)

DMA mode register (DMD0/DMD1)

(151)

00000

0

DMA transfer count register (DCT0/DCT1)

DMA transfer count reload register

(152)

(DRC0/DRC1)

(153)

DMA memory address register (DMA0/DMA1)

(154)

DMA SFR address register (DSA0/DSA1)

DMA memory address reload register

(155)

(DRA0/DRA1)

0000

16

)···

(03B0

(03B1

16

)···

(03B2

16

)···

16

)···

(03B3

16

)···

(03B4

16

)···

(03B5

16

)···

(03B6

(Note 2)

(Note 2)

(Note 2)

(Note 2)

(Note 2)

(Note 2)

(Note 2)

(03B716)···

(03C2

(03C3

(03C6

(03C7

(03CA

(03CB16)···

(03CE16)···

(03CF16)··· 00

(03D216)···

(03D316)···

(03DA

(03DB

(03DC

(03E2

(03E3

(03E6

(03E7

(03EA

(03EB

(03F0

00

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)··· X0

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

16

)···

(03F116)··· X0

(03FF

16

)···

x : Nothing is mapped to this bit

? : Undefined

0

00

0

0

00

0000

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

0000

000000

000000

000000

000000

000000

000000

0000

00

??

??

??

??

??

0

000000

00 0

16

16

16

00000

16

16

00000

16

16

00000

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

16

0

00

0

0

Figure 1.4.4. Device's internal status after a reset is cleared

21

Under

development

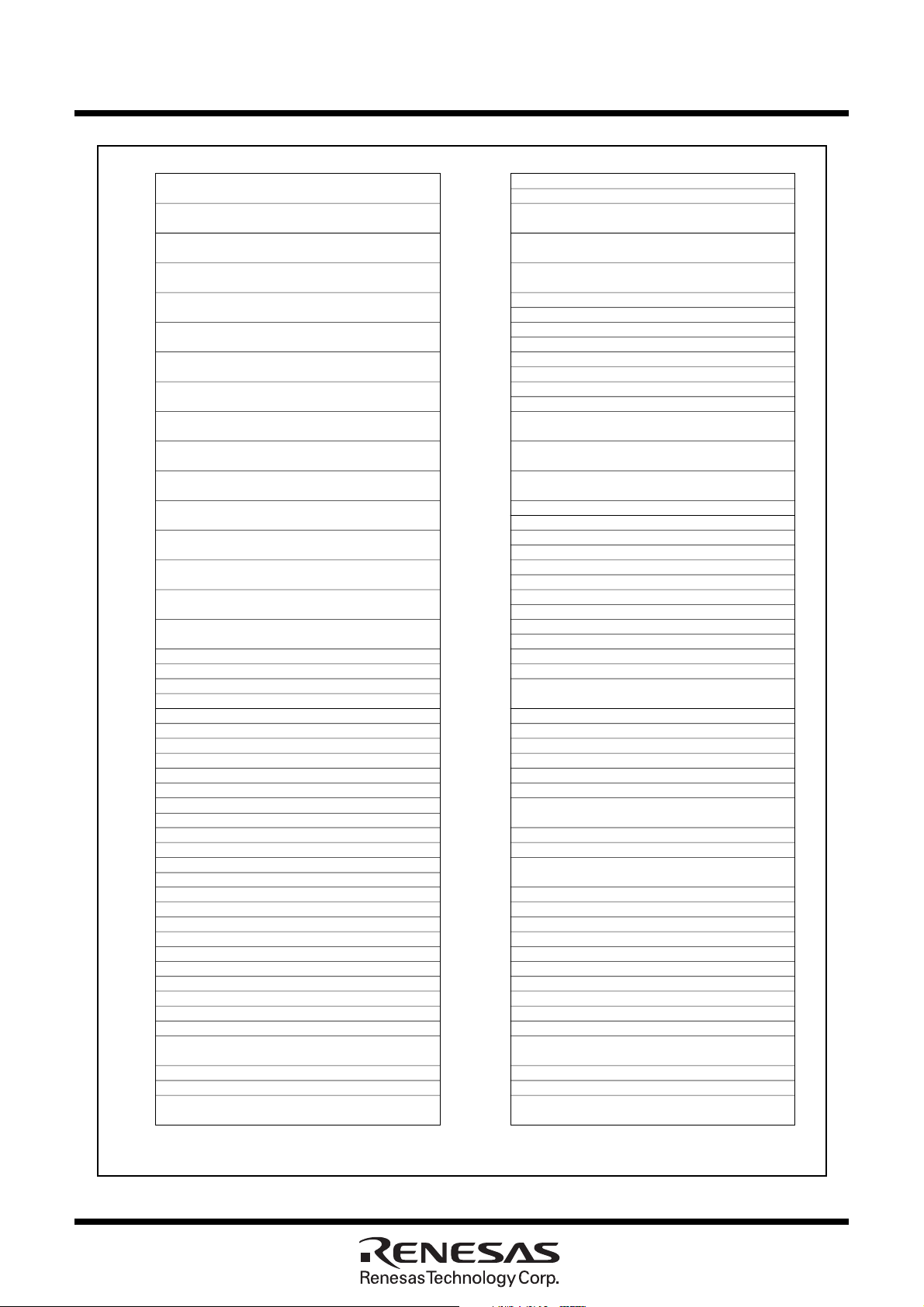

SFR

Preliminary Specifications REV.D

Specifications in this manual are tentative and subject to change.

0060

0000

16

0001

16

0002

16

0003

16

0004

16

Processor mode register 0 (PM0)

0005

16

Processor mode register 1(PM1)

0006

16

System clock control register 0 (CM0)

0007

16

System clock control register 1 (CM1)

0008

16

Wait control register (WCR)

0009

16

Address match interrupt enable register (AIER)

000A

16

Protect register (PRCR)

000B

16

External data bus width control register (DS)

000C

16

Main clock division register (MCD)

000D

16

000E

16

Watchdog timer start register (WDTS)

000F

16

Watchdog timer control register (WDC)

0010

16

0011

16

Address match interrupt register 0 (RMAD0)

0012

16

0013

16

0014

16

0015

16

Address match interrupt register 1 (RMAD1)

0016

16

0017

16

0018

16

0019

16

Address match interrupt register 2 (RMAD2)

001A

16

001B

16

001C

16

Address match interrupt register 3 (RMAD3)

001D

16

001E

16

001F

16

0020

16

Emulator interrupt vector table register (EIAD)

0021

16

0022

16

0023

16

Emulator interrupt detect register (EITD)

0024

16

Emulator protect register (EPRR)

0025

16

0026

16

0027

16

0028

16

0029

16

002A

16

002B

16

002C

16

002D

16

002E

16

002F

16

0030

16

ROM areaset register (ROA)

0031

16

Debug monitor area set register (DBA)

0032

16

Expansion area set register 0 (EXA0)

0033

16

Expansion area set register 1 (EXA1)

0034

16

Expansion area set register 2 (EXA2)

0035

16

Expansion area set register 3 (EXA3)

0036

16

0037

16

0038

16

0039

16

003A

16

003B

16

003C

16

003D

16

003E

16

003F

16

0040

16

DRAM control register (DRAMCONT)

0041

16

DRAM refresh interval set register (REFCNT)

0042

16

0043

16

0044

16

*

*

*

*

*

*

*

*

*

16

0061

16

0062

16

0063

16

0064

16

0065

16

0066

16

0067

16

0068

16

DMA0 interrupt control register (DM0IC)

0069

16

Timer B5 interrupt control register (TB5IC)

006A

16

DMA2 interrupt control register (DM1IC)

006B

16

UART2 receive/ACK interrupt control register (S2RIC)

006C

16

Timer A0 interrupt control register (TA0IC)

006D

16

UART3 receive/ACK interrupt control register (S3RIC)

006E

16

Timer A2 interrupt control register (TA2IC)

006F

16

UART4 receive/ACK interrupt control register (S4RIC)

0070

16

Timer A4 interrupt control register (TA4IC)

0071

16

Bus collision detection(UART3) interrupt control register (BCN3IC)

0072

16

UART0 receive interrupt control register (S0RIC)

0073

16

A-D conversion interrupt control register (ADIC)

0074

16

UART1 receive interrupt control register (S1RIC)

0075

16

0076

16

Timer B1 interrupt control register (TB1IC)

0077

16

0078

16

Timer B3 interrupt control register (TB3IC)

0079

16

007A

16

INT5 interrupt control register (INT5IC)

007B

16

007C

16

INT3 interrupt control register (INT3IC)

007D

16

007E

16

INT1 interrupt control register (INT1IC)

007F

16

0080

16

0081

16

0082

16

0083

16

0084

16

0085

16

0086

16

0087

16

0088

16

DMA1 interrupt control register (DM1IC)

0089

16