Page 1

To all our customers

Regarding the change of names mentioned in the document, such as Hitachi

Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas

Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog

and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.)

Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand

names are mentioned in the document, these names have in fact all been changed to Renesas

Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and

corporate statement, no changes whatsoever have been made to the contents of the document, and

these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp.

Customer Support Dept.

April 1, 2003

Page 2

Cautions

Keep safety first in your circuit designs!

1. Renesas Technology Corporation puts the maximum effort into making semiconductor products better

and more reliable, but there is al ways the possibility that t rouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in th e sel ection of the Renesas

Technology Corporation product best suited to the customer's application; they do not convey any

license under any intellectual property rights, or any other rights, belonging to Renesas Technology

Corporation or a third party.

2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any

third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or

circuit application examples contained in these materi als.

3. All information contained in these materials, including product data, diagrams, charts, programs and

algorithms represents information on products at the time of publication of these materials, and are

subject to change by Renesas Technology Corporation without notice due to product improvements or

other reasons. It is therefore recommended that customers contact Renesas Technology Corporation

or an authorized Renesas Technology Corporation product distributor for the latest product information

before purchasing a product listed herein.

The information described here may contain technical i naccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss

rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various

means, including the Renesas Technology Corporation Semiconductor home page

(http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams,

charts, programs, and algorithms, please be sure to evaluat e al l information as a total system before

making a final decision on the applicability of the information and products. Renesas Technology

Corporation assumes no responsibility for any damage, liability or other loss resulting from the

information contained herein.

5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device

or system that is used under circumstances in which human life is po t entially at stake. P l ease contact

Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor

when considering the use of a product contained herein for any specific purposes, such as apparatus or

systems for transportation, vehicular, medical, aerospace, n uclear, or undersea repeater use.

6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in

whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be

exported under a license from the Japanese government and cannot be imported into a country other

than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the

country of destination is prohibited.

8. Please contact Renesas Technology Corporation for further details on these materials or the products

contained therein.

Page 3

H8/3834 Series

H8/3837

HD6433837, HD6433837S, HD64473837

H8/3836

HD6433836, HD6433836S

H8/3835

HD6433835, HD6433835S

H8/3834

HD6433834, HD6433834S, HD6473834

H8/3833

HD6433833, HD6433833S

H8/3832

HD6433832S

ADE-602-054D

Rev. 5.0

3/5/03

Hitachi, Ltd.

MC-Setsu

Hardware Manual

Page 4

Notice

When using this document, keep the following in mind:

1. This document may, wholly or partially, be subject to change without notice.

2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole

or part of this document without Hitachi’s permission.

3. Hitachi will not be held responsible for any damage to the user that may result from accidents

or any other reasons during operation of the user’s unit according to this document.

4. Circuitry and other examples described herein are meant merely to indicate the characteristics

and performance of Hitachi’s semiconductor products. Hitachi assumes no responsibility for

any intellectual property claims or other problems that may result from applications based on

the examples described herein.

5. No license is granted by implication or otherwise under any patents or other rights of any third

party or Hitachi, Ltd.

6. MEDICAL APPLICATIONS: Hitachi’s products are not authorized for use in MEDICAL

APPLICATIONS without the written consent of the appropriate officer of Hitachi’s sales

company. Such use includes, but is not limited to, use in life support systems. Buyers of

Hitachi’s products are requested to notify the relevant Hitachi sales offices when planning to

use the products in MEDICAL APPLICATIONS.

Page 5

Preface

The H8/300L Series of single-chip microcomputers has the high-speed H8/300L CPU at its core,

with many necessary peripheral functions on-chip. The H8/300L CPU instruction set is compatible

with the H8/300 CPU.

The H8/3834 Series has a system-on-a-chip architecture that includes such peripheral functions as

an LCD controller/driver, five types of timers, a 14-bit PWM, a three-channel serial

communication interface, and an A/D converter. This makes it ideal for use in systems requiring

an LCD display.

This manual describes the hardware of the H8/3834 Series. For details on the H8/3834 Series

instruction set, refer to the H8/300L Series Programming Manual.

Note: The terms H8/3834, H8/3834S, and H8/3834 Series used in the text refer to the products

shown below.

1. H8/3834: HD6433837, HD6433836, HD6433835, HD6433834, HD6433833,

HD6473837, HD6473834

2. H8/3834S: HD6433837S, HD6433836S, HD6433835S, HD6433834S, HD6433833S,

HD6433832S

3. H8/3834 Series: All products, including the H8/3834 and H8/3834S

Page 6

Page 7

Contents

Section 1 Overview............................................................................................................ 1

1.1 Overview............................................................................................................................ 1

1.2 Internal Block Diagram...................................................................................................... 5

1.3 Pin Arrangement and Functions......................................................................................... 6

1.3.1 Pin Arrangement ................................................................................................... 6

1.3.2 Pin Functions......................................................................................................... 8

Section 2 CPU...................................................................................................................... 13

2.1 Overview............................................................................................................................ 13

2.1.1 Features ................................................................................................................. 13

2.1.2 Address Space ....................................................................................................... 14

2.1.3 Register Configuration.......................................................................................... 14

2.2 Register Descriptions.......................................................................................................... 15

2.2.1 General Registers.................................................................................................. 15

2.2.2 Control Registers................................................................................................... 15

2.2.3 Initial Register Values........................................................................................... 17

2.3 Data Formats...................................................................................................................... 17

2.3.1 Data Formats in General Registers........................................................................ 18

2.3.2 Memory Data Formats .......................................................................................... 19

2.4 Addressing Modes.............................................................................................................. 20

2.4.1 Addressing Modes................................................................................................. 20

2.4.2 Effective Address Calculation............................................................................... 22

2.5 Instruction Set .................................................................................................................... 26

2.5.1 Data Transfer Instructions..................................................................................... 28

2.5.2 Arithmetic Operations........................................................................................... 30

2.5.3 Logic Operations................................................................................................... 31

2.5.4 Shift Operations .................................................................................................... 31

2.5.5 Bit Manipulations.................................................................................................. 33

2.5.6 Branching Instructions.......................................................................................... 37

2.5.7 System Control Instructions.................................................................................. 39

2.5.8 Block Data Transfer Instruction............................................................................ 40

2.6 Basic Operational Timing.................................................................................................. 41

2.6.1 Access to On-Chip Memory (RAM, ROM).......................................................... 41

2.6.2 Access to On-Chip Peripheral Modules................................................................ 42

2.7 CPU States.......................................................................................................................... 43

2.7.1 Overview............................................................................................................... 43

2.7.2 Program Execution State....................................................................................... 45

2.7.3 Program Halt State................................................................................................ 45

2.7.4 Exception-Handling State ..................................................................................... 45

i

Page 8

2.8 Memory Map...................................................................................................................... 46

2.8.1 Memory Map......................................................................................................... 46

2.8.2 LCD RAM Address Relocation............................................................................ 52

2.9 Application Notes............................................................................................................... 53

2.9.1 Notes on Data Access............................................................................................ 53

2.9.2 Notes on Bit Manipulation.................................................................................... 55

2.9.3 Notes on Use of the EEPMOV Instruction ........................................................... 61

Section 3 Exception Handling........................................................................................ 63

3.1 Overview............................................................................................................................ 63

3.2 Reset................................................................................................................................... 63

3.2.1 Overview............................................................................................................... 63

3.2.2 Reset Sequence...................................................................................................... 63

3.2.3 Interrupt Immediately after Reset ......................................................................... 65

3.3 Interrupts............................................................................................................................ 66

3.3.1 Overview............................................................................................................... 66

3.3.2 Interrupt Control Registers.................................................................................... 67

3.3.3 External Interrupts................................................................................................. 75

3.3.4 Internal Interrupts.................................................................................................. 76

3.3.5 Interrupt Operations.............................................................................................. 76

3.3.6 Interrupt Response Time....................................................................................... 81

3.4 Application Notes............................................................................................................... 81

3.4.1 Notes on Stack Area Use ...................................................................................... 81

3.4.2 Notes on Rewriting Port Mode Registers.............................................................. 82

Section 4 Clock Pulse Generators.................................................................................. 85

4.1 Overview............................................................................................................................ 85

4.1.1 Block Diagram...................................................................................................... 85

4.1.2 System Clock and Subclock.................................................................................. 85

4.2 System Clock Generator..................................................................................................... 86

4.3 Subclock Generator............................................................................................................ 88

4.4 Prescalers............................................................................................................................ 91

4.5 Note on Oscillators............................................................................................................. 92

Section 5 Power-Down Modes....................................................................................... 93

5.1 Overview............................................................................................................................ 93

5.1.1 System Control Registers...................................................................................... 96

5.2 Sleep Mode......................................................................................................................... 99

5.2.1 Transition to Sleep Mode...................................................................................... 99

5.2.2 Clearing Sleep Mode............................................................................................. 99

5.3 Standby Mode .................................................................................................................... 99

5.3.1 Transition to Standby Mode.................................................................................. 99

5.3.2 Clearing Standby Mode ........................................................................................ 100

ii

Page 9

5.3.3 Oscillator Settling Time after Standby Mode is Cleared...................................... 100

5.3.4 Transition to Standby Mode and Port Pin States .................................................. 101

5.4 Watch Mode....................................................................................................................... 101

5.4.1 Transition to Watch Mode .................................................................................... 101

5.4.2 Clearing Watch Mode ........................................................................................... 102

5.4.3 Oscillator Settling Time after Watch Mode is Cleared......................................... 102

5.5 Subsleep Mode................................................................................................................... 102

5.5.1 Transition to Subsleep Mode ................................................................................ 102

5.5.2 Clearing Subsleep Mode ....................................................................................... 103

5.6 Subactive Mode.................................................................................................................. 103

5.6.1 Transition to Subactive Mode ............................................................................... 103

5.6.2 Clearing Subactive Mode...................................................................................... 103

5.6.3 Operating Frequency in Subactive Mode.............................................................. 103

5.7 Active (medium-speed) Mode............................................................................................ 104

5.7.1 Transition to Active (medium-speed) Mode......................................................... 104

5.7.2 Clearing Active (medium-speed) Mode................................................................ 104

5.7.3 Operating Frequency in Active (medium-speed) Mode........................................ 104

5.8 Direct Transfer.................................................................................................................... 104

5.8.1 Direct Transfer Overview...................................................................................... 104

5.8.2 Calculation of Direct Transfer Time before Transition ........................................ 106

Section 6 ROM.................................................................................................................... 109

6.1 Overview............................................................................................................................ 109

6.1.1 Block Diagram...................................................................................................... 109

6.2 H8/3834 PROM Mode ....................................................................................................... 110

6.2.1 Setting to PROM Mode......................................................................................... 110

6.2.2 Socket Adapter Pin Arrangement and Memory Map............................................ 110

6.3 H8/3834 Programming....................................................................................................... 113

6.3.1 Writing and Verifying........................................................................................... 113

6.3.2 Programming Precautions ..................................................................................... 117

6.4 H8/3837 PROM Mode ....................................................................................................... 118

6.4.1 Setting to PROM Mode......................................................................................... 118

6.4.2 Socket Adapter Pin Arrangement and Memory Map............................................ 118

6.5 H8/3837 Programming....................................................................................................... 121

6.5.1 Writing and Verifying........................................................................................... 121

6.5.2 Programming Precautions ..................................................................................... 126

6.6 Reliability of Programmed Data ........................................................................................ 127

Section 7 RAM.................................................................................................................... 129

7.1 Overview............................................................................................................................ 129

7.1.1 Block Diagram...................................................................................................... 129

Section 8 I/O Ports ............................................................................................................. 131

iii

Page 10

8.1 Overview............................................................................................................................ 131

8.2 Port 1.................................................................................................................................. 133

8.2.1 Overview............................................................................................................... 133

8.2.2 Register Configuration and Description................................................................ 133

8.2.3 Pin Functions......................................................................................................... 137

8.2.4 Pin States............................................................................................................... 139

8.3 Port 2.................................................................................................................................. 140

8.3.1 Overview............................................................................................................... 140

8.3.2 Register Configuration and Description................................................................ 140

8.3.3 Pin Functions......................................................................................................... 144

8.3.4 Pin States............................................................................................................... 144

8.4 Port 3.................................................................................................................................. 145

8.4.1 Overview............................................................................................................... 145

8.4.2 Register Configuration and Description................................................................ 145

8.4.3 Pin Functions......................................................................................................... 149

8.4.4 Pin States............................................................................................................... 151

8.4.5 MOS Input Pull-Up............................................................................................... 151

8.5 Port 4.................................................................................................................................. 152

8.5.1 Overview............................................................................................................... 152

8.5.2 Register Configuration and Description................................................................ 152

8.5.3 Pin Functions......................................................................................................... 154

8.5.4 Pin States............................................................................................................... 155

8.6 Port 5.................................................................................................................................. 155

8.6.1 Overview............................................................................................................... 155

8.6.2 Register Configuration and Description................................................................ 156

8.6.3 Pin Functions......................................................................................................... 158

8.6.4 Pin States............................................................................................................... 158

8.6.5 MOS Input Pull-Up............................................................................................... 159

8.7 Port 6.................................................................................................................................. 159

8.7.1 Overview............................................................................................................... 159

8.7.2 Register Configuration and Description................................................................ 160

8.7.3 Pin Functions......................................................................................................... 161

8.7.4 Pin States............................................................................................................... 162

8.7.5 MOS Input Pull-Up............................................................................................... 162

8.8 Port 7.................................................................................................................................. 163

8.8.1 Overview............................................................................................................... 163

8.8.2 Register Configuration and Description................................................................ 163

8.8.3 Pin Functions......................................................................................................... 164

8.8.4 Pin States............................................................................................................... 165

8.9 Port 8.................................................................................................................................. 165

8.9.1 Overview............................................................................................................... 165

8.9.2 Register Configuration and Description................................................................ 165

8.9.3 Pin Functions......................................................................................................... 167

iv

Page 11

8.9.4 Pin States............................................................................................................... 167

8.10 Port 9.................................................................................................................................. 168

8.10.1 Overview ............................................................................................................... 168

8.10.2 Register Configuration and Description................................................................ 168

8.10.3 Pin Functions......................................................................................................... 169

8.10.4 Pin States............................................................................................................... 171

8.11 Port A.................................................................................................................................. 171

8.11.1 Overview ............................................................................................................... 171

8.11.2 Register Configuration and Description................................................................ 172

8.11.3 Pin Functions......................................................................................................... 173

8.11.4 Pin States............................................................................................................... 174

8.12 Port B.................................................................................................................................. 175

8.12.1 Overview ............................................................................................................... 175

8.12.2 Register Configuration and Description................................................................ 175

8.13 Port C.................................................................................................................................. 176

8.13.1 Overview ............................................................................................................... 176

8.13.2 Register Configuration and Description................................................................ 176

Section 9 Timers................................................................................................................. 177

9.1 Overview............................................................................................................................ 177

9.2 Timer A.............................................................................................................................. 178

9.2.1 Overview............................................................................................................... 178

9.2.2 Register Descriptions............................................................................................ 180

9.2.3 Timer Operation.................................................................................................... 182

9.2.4 Timer A Operation States...................................................................................... 183

9.3 Timer B .............................................................................................................................. 183

9.3.1 Overview............................................................................................................... 183

9.3.2 Register Descriptions............................................................................................ 185

9.3.3 Timer Operation.................................................................................................... 187

9.3.4 Timer B Operation States...................................................................................... 188

9.4 Timer C .............................................................................................................................. 188

9.4.1 Overview............................................................................................................... 188

9.4.2 Register Descriptions............................................................................................ 190

9.4.3 Timer Operation.................................................................................................... 192

9.4.4 Timer C Operation States...................................................................................... 194

9.5 Timer F............................................................................................................................... 194

9.5.1 Overview............................................................................................................... 194

9.5.2 Register Descriptions............................................................................................ 197

9.5.3 Interface with the CPU.......................................................................................... 203

9.5.4 Timer Operation.................................................................................................... 206

9.5.5 Application Notes.................................................................................................. 208

9.6 Timer G.............................................................................................................................. 210

9.6.1 Overview............................................................................................................... 210

v

Page 12

9.6.2 Register Descriptions............................................................................................ 212

9.6.3 Noise Canceller Circuit......................................................................................... 215

9.6.4 Timer Operation.................................................................................................... 217

9.6.5 Application Notes.................................................................................................. 221

9.6.6 Sample Timer G Application................................................................................ 224

Section 10 Serial Communication Interface ................................................................. 225

10.1 Overview........................................................................................................................... 225

10.2 SCI1.................................................................................................................................... 225

10.2.1 Overview............................................................................................................... 225

10.2.2 Register Descriptions............................................................................................ 227

10.2.3 Operation............................................................................................................... 231

10.2.4 Interrupts ............................................................................................................... 234

10.2.5 Application Notes.................................................................................................. 234

10.3 SCI2.................................................................................................................................... 234

10.3.1 Overview............................................................................................................... 234

10.3.2 Register Descriptions ............................................................................................ 236

10.3.3 Operation............................................................................................................... 240

10.3.4 Interrupts ............................................................................................................... 247

10.3.5 Application Notes.................................................................................................. 247

10.4 SCI3.................................................................................................................................... 248

10.4.1 Overview............................................................................................................... 248

10.4.2 Register Descriptions............................................................................................ 250

10.4.3 Operation............................................................................................................... 266

10.4.4 Operation in Asynchronous Mode ........................................................................ 270

10.4.5 Operation in Synchronous Mode .......................................................................... 278

10.4.6 Multiprocessor Communication Function ............................................................ 285

10.4.7 Interrupts ............................................................................................................... 291

10.4.8 Application Notes.................................................................................................. 292

Section 11 14-Bit PWM...................................................................................................... 297

11.1 Overview............................................................................................................................ 297

11.1.1 Features ................................................................................................................. 297

11.1.2 Block Diagram...................................................................................................... 297

11.1.3 Pin Configuration.................................................................................................. 298

11.1.4 Register Configuration.......................................................................................... 298

11.2 Register Descriptions.......................................................................................................... 298

11.2.1 PWM Control Register (PWCR)........................................................................... 298

11.2.2 PWM Data Registers U and L (PWDRU, PWDRL)............................................. 299

11.3 Operation............................................................................................................................ 299

Section 12 A/D Converter.................................................................................................. 301

12.1 Overview............................................................................................................................ 301

vi

Page 13

12.1.1 Features ................................................................................................................. 301

12.1.2 Block Diagram...................................................................................................... 301

12.1.3 Pin Configuration.................................................................................................. 302

12.1.4 Register Configuration.......................................................................................... 302

12.2 Register Descriptions.......................................................................................................... 303

12.2.1 A/D Result Register (ADRR)................................................................................ 303

12.2.2 A/D Mode Register (AMR) .................................................................................. 303

12.2.3 A/D Start Register (ADSR)................................................................................... 305

12.3 Operation............................................................................................................................ 306

12.3.1 A/D Conversion Operation.................................................................................... 306

12.3.2 Start of A/D Conversion by External Trigger Input.............................................. 306

12.4 Interrupts ............................................................................................................................ 307

12.5 Typical Use ........................................................................................................................ 307

12.6 Application Notes............................................................................................................... 310

Section 13 LCD Controller/Driver .................................................................................. 311

13.1 Overview............................................................................................................................ 311

13.1.1 Features ................................................................................................................. 311

13.1.2 Block Diagram...................................................................................................... 312

13.1.3 Pin Configuration.................................................................................................. 313

13.1.4 Register Configuration.......................................................................................... 313

13.2 Register Descriptions.......................................................................................................... 314

13.2.1 LCD Port Control Register (LPCR)...................................................................... 314

13.2.2 LCD Control Register (LCR)................................................................................ 316

13.3 Operation............................................................................................................................ 318

13.3.1 Settings Prior to LCD Display .............................................................................. 318

13.3.2 Relation of LCD RAM to Display ........................................................................ 320

13.3.3 Connection to HD66100........................................................................................ 320

13.3.4 Operation in Power-Down Modes ........................................................................ 329

13.3.5 Boosting the LCD Driver Power Supply .............................................................. 330

Section 14 Electrical Characteristics............................................................................... 331

14.1 H8/3832S, H8/3833S, H8/3834S, H8/3835S, H8/3836S and H8/3837S

Absolute Maximum Ratings (Standard Specifications)..................................................... 331

14.2 H8/3832S, H8/3833S and H8/3834S Electrical Characteristics

(Standard Specifications).................................................................................................... 332

14.2.1 Power Supply Voltage and Operating Range........................................................ 332

14.2.2 DC Characteristics ................................................................................................ 334

14.2.3 AC Characteristics ................................................................................................ 339

14.2.4 A/D Converter Characteristics.............................................................................. 343

14.2.5 LCD Characteristics.............................................................................................. 344

14.3 H8/3835S, H8/3836S and H8/3837S Electrical Characteristics

(Standard Specifications).................................................................................................... 345

vii

Page 14

14.3.1 Power Supply Voltage and Operating Range........................................................ 345

14.3.2 DC Characteristics ................................................................................................ 347

14.3.3 AC Characteristics ................................................................................................ 352

14.3.4 A/D Converter Characteristics.............................................................................. 356

14.3.5 LCD Characteristics.............................................................................................. 357

14.4 H8/3832S, H8/3833S, H8/3834S, H8/3835S, H8/3836S and H8/3837S

Absolute Maximum Ratings (Wide Temperature Range (I-Spec) Version)...................... 358

14.5 H8/3832S, H8/3833S and H8/3834S Electrical Characteristics

(Wide Temperature Range (I-Spec) Version).................................................................... 359

14.5.1 Power Supply Voltage and Operating Range........................................................ 359

14.5.2 DC Characteristics ................................................................................................ 361

14.5.3 AC Characteristics ................................................................................................ 366

14.5.4 A/D Converter Characteristics.............................................................................. 370

14.5.5 LCD Characteristics.............................................................................................. 371

14.6 H8/3835S, H8/3836S and H8/3837S Electrical Characteristics

(Wide Temperature Range (I-Spec) Version).................................................................... 373

14.6.1 Power Supply Voltage and Operating Range........................................................ 373

14.6.2 DC Characteristics ................................................................................................ 375

14.6.3 AC Characteristics ................................................................................................ 380

14.6.4 A/D Converter Characteristics.............................................................................. 384

14.6.5 LCD Characteristics.............................................................................................. 385

14.7 H8/3833, H8/3834, H8/3835, H8/3836, and H8/3837 (Standard Specification)

Absolute Maximum Ratings............................................................................................... 387

14.8 H8/3833 and H8/3834 Electrical Characteristics (Standard Specifications)...................... 388

14.8.1 Power Supply Voltage and Operating Range........................................................388

14.8.2 DC Characteristics ................................................................................................ 390

14.8.3 AC Characteristics ................................................................................................ 395

14.8.4 A/D Converter Characteristics.............................................................................. 399

14.8.5 LCD Characteristics.............................................................................................. 400

14.9 H8/3835 and H8/3836 and H8/3837 (Standard Specifications)

Electrical Characteristics.................................................................................................... 401

14.9.1 Power Supply Voltage and Operating Range........................................................ 401

14.9.2 DC Characteristics ................................................................................................ 403

14.9.3 AC Characteristics ................................................................................................ 408

14.9.4 A/D Converter Characteristics.............................................................................. 412

14.9.5 LCD Characteristics.............................................................................................. 413

14.10 H8/3833, H8/3834, H8/3835, H8/3836, and H8/3837 Absolute Maximum Ratings

(Wide Temperature Range (I-Spec) Version).................................................................... 414

14.11 H8/3833 and H8/3834 Electrical Characteristics (Wide Temperature Range

(I-Spec) Version)................................................................................................................ 415

14.11.1 Power Supply Voltage and Operating Range........................................................ 415

14.11.2 DC Characteristics ................................................................................................ 417

14.11.3 AC Characteristics ................................................................................................ 422

viii

Page 15

14.11.4 A/D Converter Characteristics.............................................................................. 426

14.11.5 LCD Characteristics.............................................................................................. 427

14.12 H8/3835, H8/3836, and H8/3837 Electrical Characteristics

(Wide Temperature Range (I-Spec) Version).................................................................... 429

14.12.1 Power Supply Voltage and Operating Range........................................................ 429

14.12.2 DC Characteristics ................................................................................................ 431

14.12.3 AC Characteristics ................................................................................................ 436

14.12.4 A/D Converter Characteristics.............................................................................. 440

14.12.5 LCD Characteristics.............................................................................................. 441

14.13 Operation Timing ............................................................................................................... 443

14.14 Output Load Circuit............................................................................................................ 448

Appendix A CPU Instruction Set..................................................................................... 449

A.1 Instructions......................................................................................................................... 449

A.2 Operation Code Map.......................................................................................................... 457

A.3 Number of Execution States............................................................................................... 459

Appendix B On-Chip Registers........................................................................................ 466

B.1 I/O Registers (1) ................................................................................................................. 466

B.2 I/O Registers (2) ................................................................................................................. 470

Appendix C I/O Port Block Diagrams............................................................................ 513

C.1 Block Diagram of Port 1 .................................................................................................... 513

C.2 Block Diagram of Port 2 .................................................................................................... 518

C.3 Block Diagram of Port 3 .................................................................................................... 521

C.4 Block Diagram of Port 4 .................................................................................................... 527

C.5 Block Diagram of Port 5 .................................................................................................... 530

C.6 Block Diagram of Port 6 .................................................................................................... 531

C.7 Block Diagram of Port 7 .................................................................................................... 532

C.8 Block Diagram of Port 8 .................................................................................................... 533

C.9 Block Diagram of Port 9 .................................................................................................... 534

C.10 Block Diagram of Port A.................................................................................................... 535

C.11 Block Diagram of Port B.................................................................................................... 536

C.12 Block Diagram of Port C.................................................................................................... 536

Appendix D Port States in the Different Processing States....................................... 537

Appendix E List of Products Codes................................................................................. 538

Appendix F Package Dimensions..................................................................................... 542

ix

Page 16

Section 1 Overview

1.1 Overview

The H8/300L Series is a series of single-chip microcomputers (MCU: microcomputer unit), built

around the high-speed H8/300L CPU and equipped with peripheral system functions on-chip.

Within the H8/300L Series, the H8/3834 Series features an on-chip liquid crystal display (LCD)

controller/driver. Other on-chip peripheral functions include five timers, a 14-bit pulse width

modulator (PWM), three serial communication interface channels, and an analog-to-digital (A/D)

converter. Together these functions make the H8/3834 Series ideally suited for embedded control

of systems requiring an LCD display. On-chip memory is 16 kbytes of ROM and 1 kbyte of RAM

in the H8/3832S, 24 kbytes of ROM and 1 kbyte of RAM in the H8/3833(S), 32 kbytes of ROM

and 1 kbyte of RAM in the H8/3834(S), 40 kbytes of ROM and 2 kbytes of RAM in the

H8/3835(S), 48 kbytes of ROM and 2 kbytes of RAM in the H8/3836(S), and 60 kbytes of ROM

and 2 kbytes of RAM in the H8/3837(S).

The H8/3834 and H8/3837 both include a ZTAT™ version*, featuring a user-programmable onchip PROM.

Table 1.1 summarizes the features of the H8/3834 Series.

Note: * ZTAT is a trademark of Hitachi, Ltd.

Table 1.1 Features

Item Description

CPU High-speed H8/300L CPU

• General-register architecture

General registers: Sixteen 8-bit registers (can be used as eight 16-bit

registers)

• Operating speed

Max. operating speed: 5 MHz

Add/subtract: 0.4 µs (operating at 5 MHz)

Multiply/divide: 2.8 µs (operating at 5 MHz)

Can run on 32.768 kHz subclock

• Instruction set compatible with H8/300 CPU

Instruction length of 2 bytes or 4 bytes

Basic arithmetic operations between registers

MOV instruction for data transfer between memory and registers

1

Page 17

Table 1.1 Features (cont)

Item Description

CPU Typical instructions

• Multiply (8 bits × 8 bits)

• Divide (16 bits ÷ 8 bits)

• Bit accumulator

• Register-indirect designation of bit position

Interrupts 33 interrupt sources

• 13 external interrupt pins: IRQ

• 20 internal interrupt sources

Clock pulse generators Two on-chip clock pulse generators

• System clock pulse generator: 1 to 10 MHz

• Subclock pulse generator: 32.768 kHz

Power-down modes Six power-down modes

• Sleep mode

• Standby mode

• Watch mode

• Subsleep mode

• Subactive mode

• Active (medium-speed) mode

Memory Large on-chip memory

• H8/3832S: 16-kbyte ROM, 1-kbyte RAM

• H8/3833(S): 24-kbyte ROM, 1-kbyte RAM

• H8/3834(S): 32-kbyte ROM, 1-kbyte RAM

• H8/3835(S): 40-kbyte ROM, 2-kbyte RAM

• H8/3836(S): 48-kbyte ROM, 2-kbyte RAM

• H8/3837(S): 60-kbyte ROM, 2-kbyte RAM

I/O ports 84 I/O port pins

• I/O pins: 71

• Input pins: 13

Timers Five on-chip timers

• Timer A: 8-bit timer

Count-up timer with selection of eight internal clock signals divided

Note: *φ and

from the system clock (

watch clock (

φ

are defined in section 4, Clock Pulse Generators.

w

φ

)*

w

φ

)* and four clock signals divided from the

to IRQ0, WKP7 to WKP

4

0

2

Page 18

Table 1.1 Features (cont)

Item Description

Timers

Serial communication

interface

14-bit PWM Pulse-division PWM output for reduced ripple

A/D converter

LCD controller/driver Up to 40 segment pins and 4 common pins

• Timer B: 8-bit timer

Count-up timer with selection of seven internal clock signals or

event input from external pin

Auto-reloading

• Timer C: 8-bit timer

Count-up/count-down timer with selection of seven internal clock

signals or event input from external pin

Auto-reloading

• Timer F: 16-bit timer

Can be used as two independent 8-bit timers.

Count-up timer with selection of four internal clock signals or

event input from external pin

Compare-match function with toggle output

• Timer G: 8-bit timer

Count-up timer with selection of four internal clock signals

Input capture function with built-in noise canceller circuit

Three channels on chip

• SCI1: synchronous serial interface

Choice of 8-bit or 16-bit data transfer

• SCI2: 8-bit synchronous serial interface

Automatic transfer of 32-byte data segments

• SCI3: 8-bit synchronous or asynchronous serial interface

Built-in function for multiprocessor communication

• Can be used as a 14-bit D/A converter by connecting to an external

low-pass filter.

• Successive approximations using a resistance ladder resolution:

8 bits

• 12-channel analog input port

• Conversion time: 31/

• Choice of four duty cycles (static, 1/2, 1/3, 1/4)

• Segments can be expanded externally

• Segment pins can be switched to general-purpose ports in groups of

four

φ

or 62/φ per channel

3

Page 19

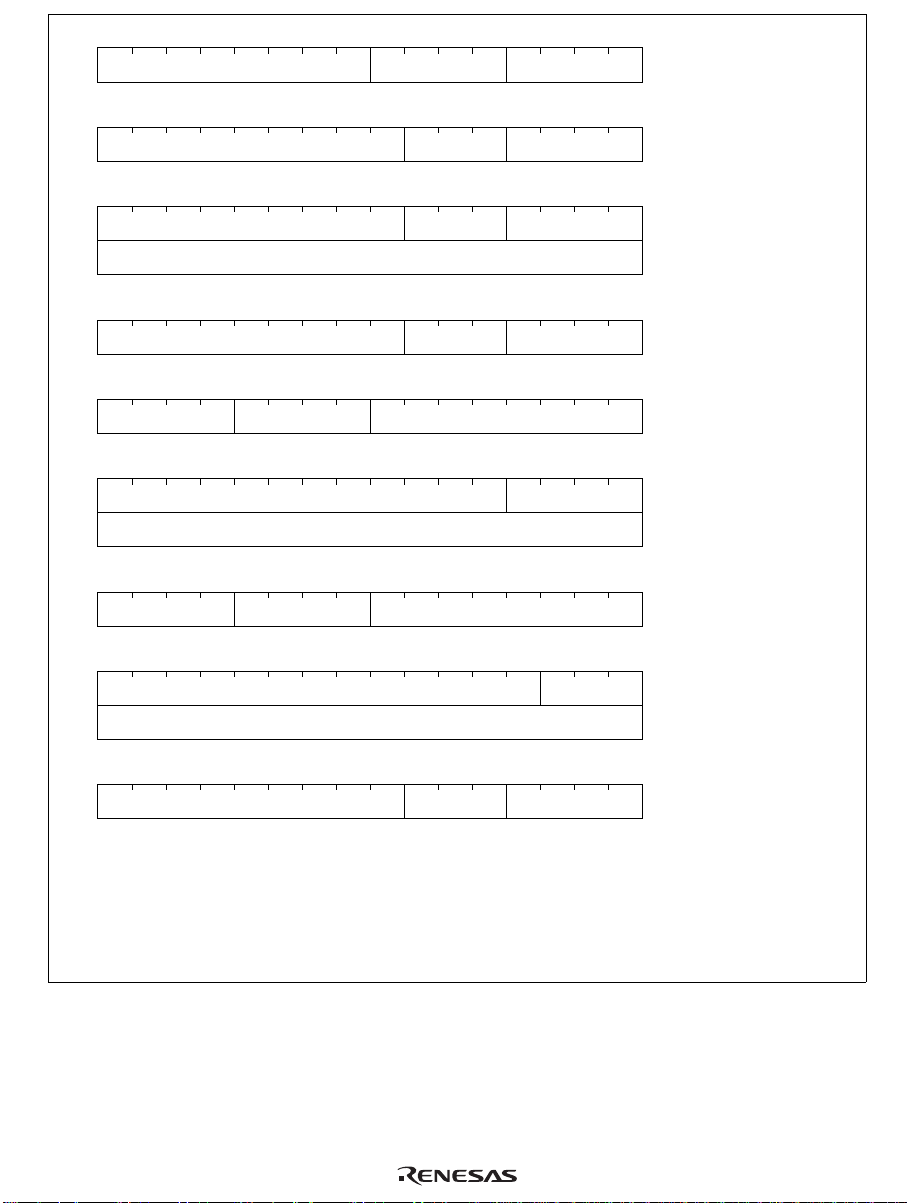

Table 1.1 Features (cont)

Item Description

Product lineup

Mask ROM Version ZTAT™ Version Package ROM/RAM Size

HD6433832SH

HD6433832SF

HD6433832SX

HD6433833H

HD6433833SH

HD6433833F

HD6433833SF

HD6433833X

HD6433833SX

HD6433834H

HD6433834SH

HD6433834F

HD6433834SF

HD6433834X

HD6433834SX

HD6433835H

HD6433835SH

HD6433835F

HD6433835SF

HD6433835X

HD6433835SX

HD6433836H

HD6433836SH

HD6433836F

HD6433836SF

HD6433836X

HD6433836SX

HD6433837H

HD6433837SH

HD6433837F

HD6433837SF

HD6433837X

HD6433837SX

HD6433832SD

HD6433832SE

HD6433832SL

HD6433833D

HD6433833SD

HD6433833E

HD6433833SE

HD6433833L

HD6433833SL

HD6433834D

HD6433834SD

HD6433834E

HD6433834SE

HD6433834L

HD6433834SL

HD6433835D

HD6433835SD

HD6433835E

HD6433835SE

HD6433835L

HD6433835SL

HD6433836D

HD6433836SD

HD6433836E

HD6433836SE

HD6433836L

HD6433836SL

HD6433837D

HD6433837SD

HD6433837E

HD6433837SE

HD6433837L

HD6433837SL

Product Code

—

—

—

—

—

—

HD6473834H

HD6473834F

HD6473834X

—

—

—

—

—

—

HD6473837H

HD6473837F

HD6473837X

—

—

—

—

—

—

HD6473834D

HD6473834E

—

—

—

—

—

—

—

HD6473837D

HD6473837E

HD6473837L

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

100-pin QFP (FP-100B)

100-pin QFP (FP-100A)

100-pin TQFP (TFP-100B)

ROM: 16 kbytes

RAM: 1 kbyte

ROM: 24 kbytes

RAM: 1 kbyte

ROM: 32 kbytes

RAM: 1 kbyte

ROM: 40 kbytes

RAM: 2 kbytes

ROM: 48 kbytes

RAM: 2 kbytes

ROM: 60 kbytes

RAM: 2 kbytes

ROM: 16 kbytes

RAM: 1 kbyte

WTR (I-spec)

ROM: 24 kbytes

RAM: 1 kbyte

WTR (I-spec)

ROM: 32 kbytes

RAM: 1 kbyte

WTR (I-spec)

ROM: 40 kbytes

RAM: 2 kbytes

WTR (I-spec)

ROM: 48 kbytes

RAM: 2 kbytes

WTR (I-spec)

ROM: 60 kbytes

RAM: 2 kbytes

WTR (I-spec)

4

Page 20

1.2 Internal Block Diagram

Figure 1.1 shows a block diagram of the H8/3834 Series.

P10/TMOW

/TMOFL

P1

1

/TMOFH

P1

2

/TMIG

P1

3

/PWM

P1

4

/IRQ1/TMIB

P1

5

/IRQ2/TMIC

P1

6

/IRQ3/TMIF

P1

7

/IRQ4/ADTRG

P2

0

P2

P30/SCK

P31/SI

P32/SO

P33/SCK

P34/SI

P35/SO

P36/STRB

P3

/SCK

P4

0

P41/RXD

P4

2

P4

3

P50/WKP0/SEG

P51/WKP1/SEG

P52/WKP2/SEG

P53/WKP3/SEG

P54/WKP4/SEG

P55/WKP5/SEG

P56/WKP6/SEG

P57/WKP7/SEG

/UD

1

P2

P2

P2

P2

P2

P2

/CS

7

/TXD

/IRQ

2

OSC1OSC2X1X

oscillator

oscillator

Subclock

System clock

Port 1Port 2Port 3Port 4Port 5

2

3

4

5

6

7

1

1

1

2

2

2

3

0

1

2

3

4

5

6

7

8

CC

VSSVSSVCCV

CPU

H8/300L

RES

Data bus (lower)

ROM RAM

Timer A

LCD

controller

Timer B SCI1

Timer C SCI2

Timer F SCI3

Timer G

14-bit

PWM

A/D

converter

TEST

MDO

Address bus

LCD driver

Data bus (upper)

V

1

V

2

V

3

power supply

PA3/COM

PA2/COM

PA1/COM

Port A

PA0/COM

P97/SEG40/CL

P96/SEG39/CL

P95/SEG38/DO

P9

P9

P92/SEG

P91/SEG

P90/SEG

P87/SEG

P86/SEG

P85/SEG

P84/SEG

P83/SEG

P82/SEG

P81/SEG

P80/SEG

P77/SEG

P76/SEG

P75/SEG

P74/SEG

P73/SEG

Port 7 Port 8 Port 9

P72/SEG

P71/SEG

P70/SEG

P67/SEG

P66/SEG

P65/SEG

P64/SEG

P63/SEG

Port 6

P62/SEG

P61/SEG

P60/SEG

/SEG37/M

4

/SEG

3

4

3

2

1

1

2

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

Port B Port C

8

AVCCAV

0

1

2

3

4

5

6

SS

/AN

/AN

/AN

0

1

2

PB

PB

PB

/AN

3

PB

/AN

4

PB

/AN

5

PB

/AN

6

PB

7

/AN

7

PB

/AN

0

PC

9

/AN

1

PC

10

/AN

2

PC

11

/AN

3

PC

Figure 1.1 Block Diagram

5

Page 21

1.3 Pin Arrangement and Functions

1.3.1 Pin Arrangement

The pin arrangement of the H8/3834 Series is shown in figures 1.2 and 1.3.

/TMIF

/TXD

2

P4

4

/SEG

3

/WKP

3

P5

/RXD

1

P4

5

/SEG

4

/WKP

4

P5

3

/SCK

0

P4

6

/SEG

5

/WKP

5

P5

3

/IRQ

7

P1

7

/SEG

6

/WKP

6

P5

/IRQ2/TMIC

6

P1

8

/SEG

7

/WKP

7

P5

/IRQ1/TMIB

5

P1

9

/SEG

0

P6

/PWM

4

P1

10

/SEG

1

P6

/TMIG

3

P1

11

/SEG

2

P6

P2

/IRQ4/ADTRG

0

PC3/AN

AV

TEST

V

OSC

OSC

RES

MDO

P2

/UD

1

P2

P2

P2

P2

P2

P2

P30/SCK

P31/SI

P32/SO

P33/SCK

P34/SI

P35/SO

P36/STRB

10

9

8

7

6

5

4

3

2

/AN

/AN

/AN

/AN

/AN

/AN

2

1

0

PC

PC

PC

PB

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81 80 79 78 77 76

1

11

2

SS

/AN

7

6

5

4

PB

PB

PB

/AN

3

PB

/AN

2

PB

1

/AN

1

PB

0

/AN

0

PB

AVCCP4

0

/IRQ

3

3

4

X

2

5

X

1

6

SS

7

1

8

2

9

10

11

12

13

2

14

3

15

4

16

5

17

6

18

7

19

1

20

1

21

1

22

2

23

2

24

2

25

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

1

2

/CS

P3

4

3

2

/COM

2

PA

/COM

1

PA

1

/COM

0

PA

V3V2V

1

CC

V

/COM

3

SS

V

7

PA

/SEG

0

/WKP

0

P5

/SEG

1

/WKP

1

P5

3

/SEG

2

/WKP

2

P5

/TMOFH

/TMOFL

2

1

P1

P1

12

13

/SEG

/SEG

3

4

P6

P6

/TMOW

0

CC

P1

V

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

14

15

/SEG

/SEG

5

6

P6

P6

P97/SEG40/CL

P96/SEG39/CL

P95/SEG38/DO

P9

/SEG37/M

4

P9

/SEG

3

36

P92/SEG

35

P91/SEG

34

P90/SEG

33

P87/SEG

32

P86/SEG

31

P85/SEG

30

P84/SEG

29

P83/SEG

28

P82/SEG

27

P81/SEG

26

P80/SEG

25

P77/SEG

24

P76/SEG

23

P75/SEG

22

P74/SEG

21

P73/SEG

20

P72/SEG

19

P71/SEG

18

P70/SEG

17

P67/SEG

16

1

2

Figure 1.2 Pin Arrangement (FP-100B, TFP-100B: Top View)

6

Page 22

7

/AN

7

PB

6

/AN

6

PB

5

/AN

5

PB

4

/AN

4

PB

3

/AN

3

PB

2

/AN

2

PB

1

/AN

1

PB

0

/AN

0

PB

/IRQ

AVCCP4

/TMIF

/TMIC

3

/IRQ

7

P1

2

/IRQ

6

P1

/TMIB

1

/IRQ

5

P1

/PWM

4

P1

/TMIG

3

P1

/TMOFH

/TMOFL

2

1

P1

P1

/TXD

2

P4

/RXD

1

P4

3

/SCK

0

P4

0

3

/IRQ4/ADTRG

P2

0

P36/STRB

PC0/AN

PC1/AN

PC2/AN

PC3/AN

AV

TEST

V

OSC

OSC

RES

MDO

/UD

P2

1

P2

P2

P2

P2

P2

P2

P30/SCK

P31/SI

P32/SO

P33/SCK

P34/SI

P35/SO

/CS

P3

7

V

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

1

8

2

9

3

10

4

11

5

SS

6

X

7

2

X

8

1

9

SS

10

1

11

2

12

13

14

15

16

2

17

3

18

4

19

5

20

6

21

7

22

1

23

1

24

1

25

2

26

2

27

2

28

29

30

SS

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

58

58

57

56

55

54

53

52

51

/TMOW

P1

0

V

CC

P97/SEG40/CL

P96/SEG39/CL

P95/SEG38/DO

/SEG37/M

P9

4

/SEG

P9

3

36

P92/SEG

35

P91/SEG

34

P90/SEG

33

P87/SEG

32

P86/SEG

31

P85/SEG

30

P84/SEG

29

P83/SEG

28

P82/SEG

27

P81/SEG

26

P80/SEG

25

P77/SEG

24

P76/SEG

23

P75/SEG

22

P74/SEG

21

P73/SEG

20

P72/SEG

19

P71/SEG

18

P70/SEG

17

P67/SEG

16

P66/SEG

15

P65/SEG

14

P64/SEG

13

1

2

1

2

3

4

5

6

7

/SEG

5

/WKP

5

P5

/SEG

6

/WKP

6

P5

8

/SEG

7

/WKP

7

P5

9

/SEG

0

P6

10

/SEG

1

P6

3V2V1

V

4

3

2

/COM

2

PA

/COM

1

PA

1

/COM

0

PA

/SEG

0

/WKP

0

P5

/SEG

1

/WKP

1

P5

/SEG

2

/WKP

2

P5

/SEG

3

/WKP

3

P5

/SEG

4

/WKP

4

P5

CC

V

/COM

3

PA

Figure 1.3 Pin Arrangement (FP-100A: Top View)

11

/SEG

2

P6

12

/SEG

3

P6

7

Page 23

1.3.2 Pin Functions

Table 1.2 outlines the pin functions of the H8/3834 Series.

Table 1.2 Pin Functions

Pin No.

FP-100B

Type Symbol

Power

V

CC

source pins

V

SS

AV

CC

AV

SS

V1,

V

,

2

V

3

Clock pins OSC

OSC

X

1

X

2

TFP-100B FP-100A I/O Name and Functions

31, 76 34, 79 Input Power supply: All VCC pins should be

6, 27 9, 30 Input Ground: All VSS pins should be

89 92 Input Analog power supply: This is the

2 5 Input Analog ground: This is the A/D

30,

29,

28

7 10 Input This pin connects to a crystal or

1

8 11 Output See section 4, Clock Pulse

2

33,

32,

31

Input LCD power supply: These are

5 8 Input This pin connects to a 32.768-kHz

4 7 Output See section 4, Clock Pulse

connected to the system power

supply (+5 V)

connected to the system power

supply (0 V)

power supply pin for the A/D

converter. When the A/D converter is

not used, connect this pin to the

system power supply (+5 V).

converter ground pin. It should be

connected to the system power

supply (0 V).

power supply pins for the LCD

controller/ driver. A built-in resistor

divider is provided for the power

supply, so these pins are normally left

open.

Power supply conditions are

V

≥ V1 ≥ V2 ≥ V3 ≥ VSS.

CC

ceramic oscillator, or can be used to

input an external clock.

Generators, for a typical connection

diagram.

crystal oscillator.

Generators, for a typical connection

diagram.

8

Page 24

Table 1.2 Pin Functions (cont)

Pin No.

FP-100B

Type Symbol

System

RES 9 12 Input Reset: When this pin is driven low,

control

MDO 10 13 Input Mode: This pin controls system clock

TEST 3 6 Input Test: This is a test pin, not for use in

Interrupt

pins

IRQ

IRQ

IRQ

IRQ

IRQ

0

1

2

3

4

WKP

WKP

Timer pins TMOW 77 80 Output Clock output: This is an output pin

TMIB 82 85 Input Timer B event counter input: This is

TMIC 83 86 Input Timer C event counter input: This is

UD 12 15 Input Timer C up/down select: This pin

TMIF 84 87 Input Timer F event counter input: This is

TMOFL 78 81 Output Timer FL output: This is an output

TFP-100B FP-100A I/O Name and Functions

the chip is reset

oscillation in the reset state

application systems. It should be

connected to V

88

82

83

84

11

to

43 to 36 46 to 39 Input Wakeup interrupt request 0 to 7:

7

0

91

85

86

87

14

Input External interrupt request 0 to 4:

These are input pins for external

interrupts for which there is a choice

between rising and falling edge

sensing

These are input pins for external

.

SS

interrupts that are detected at the

falling edge

for waveforms generated by the timer

A output circuit

an event input pin for input to the

timer B counter

an event input pin for input to the

timer C counter

selects whether the timer C counter

isused for up- or down-counting. At

high level it selects up-counting, and

at low level down-counting.

an event input pin for input to the

timer F counter

pin for waveforms generated by the

timer FL output compare function

9

Page 25

Table 1.2 Pin Functions (cont)

Pin No.

FP-100B

Type Symbol

Timer pins TMOFH 79 82 Output Timer FH output: This is an output

TMIG 80 83 Input Timer G capture input: This is an

14-bit PWM

PWM 81 84 Output 14-bit PWM output: This is an output

pin

I/O ports PB7 to PB097 to 90 100 to 93 Input Port B: This is an 8-bit input port

PC3 to PC01, 100 to984 to 1 Input Port C: This is a 4-bit input port

TFP-100B FP-100A I/O Name and Functions

pin for waveforms generated by the

timer FH output compare function

input pin for the timer G input capture

function

pin for waveforms generated by the

14-bit PWM

P4

3

88 91 Input Port 4 (bit 3): This is a 1-bit input

port

P42 to P4087 to 85 90 to 88 I/O Port 4 (bits 2 to 0): This is a 3-bit I/O

port. Input or output can be

designated for each bit by means of

port control register 4 (PCR4).

PA3 to PA032 to 35 35 to 38 I/O Port A: This is a 4-bit I/O port. Input

or output can be designated for each

bit by means of port control register A

(PCRA).

P17 to P1084 to 77 87 to 80 I/O Port 1: This is an 8-bit I/O port. Input