Page 1

REJ09B0023-0400

The revision list can be viewed directly by

clicking the title page.

The revision list summarizes the locations of

revisions and additions. Details should always

be checked by referring to the relevant text.

SH7641

32

Hardware Manual

Renesas 32-Bit RISC Microcomputer

SuperH™ RISC engine Family / SH7641 Series

SH7641 HD6417641

Rev.4.00

Revision Date: Sep. 14, 2005

Page 2

Rev. 4.00 Sep. 14, 2005 Page ii of l

Page 3

Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and

more reliable, but there is always the possibility that trouble may occur with them. Trouble with

semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate

measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or

(iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas

Technology Corp. product best suited to the customer's application; they do not convey any license

under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or

a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or

circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and

algorithms represents information on products at the time of publication of these materials, and are

subject to change by Renesas Technology Corp. without notice due to product improvements or

other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or

an authorized Renesas Technology Corp. product distributor for the latest product information

before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising

from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means,

including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data,

diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total

system before making a final decision on the applicability of the information and products. Renesas

Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the

information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or

system that is used under circumstances in which human life is potentially at stake. Please contact

Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when

considering the use of a product contained herein for any specific purposes, such as apparatus or

systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in

whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must

be exported under a license from the Japanese government and cannot be imported into a country

other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the

country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products

contained therein.

Rev. 4.00 Sep. 14, 2005 Page iii of l

Page 4

General Precautions on Handling of Product

1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are

used as test pins or to reduce noise. If something is connected to the NC pins, the

operation of the LSI is not guaranteed.

2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are hi g h-impedance input pins. If unused pins

are in their open states, intermediate levels are induced by noise in the vicinity, a passthrough current flows internally, and a malfun ction may occur.

3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the

chip and a low level is input on the reset pin. During the period where the states are

undefined, the register settings and the output state of each pin are also undefined. Design

your system so that it does not malfunction because of processing while it is in this

undefined state. For those products which have a reset function, reset the LSI immediately

after the power supply has been turned on.

4. Prohibition of Access to Undefined or Rese rved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers

may have been be allocated to these addresses. Do not access these registers; the system's

operation is not guaranteed if they are accessed.

5. Treatment of Power Supply (0 V) Pins

Note: There should be no voltage difference between the system ground pins (0 V power

supply), VssQ, Vss, Vss, Vss (PLL1), and Vss (PLL2).

If voltage difference is created between the system ground pi ns, malfunctions may occur or

excessive current flows during standby due to through current. Voltage difference should not

be created between the system ground pins, VssQ, Vss, Vss (PLL1), and Vss (PLL2).

Rev. 4.00 Sep. 14, 2005 Page iv of l

Page 5

Important Notice on the Quality Assurance for this LSI

Although the wafer process and assembly process of this LSI are entrusted to the external silicon

foundries, the quality of this LSI is guaranteed for the customers under the quality assurance

system of our company.

However, if it is clear that our company is responsible for a defective product, we will only offer,

after the agreement of both parties, to exchange it with a new product from stock.

The following shows the robustness (reference values) of the LSI against static-electricity-induced

breakdown.

Robustness (Reference Values) of the LSI against Static-electricity-induced Breakdown

Machine Model Method ± 200 V or more

Human Body Model Method ± 1500 V or more

Charged Device Model Method ± 1000 V or more

For the details on the quality assurance of this LSI, contact your nearest Renesas Technology sales

representative.

Rev. 4.00 Sep. 14, 2005 Page v of l

Page 6

Configuration of This Manual

This manual comprises the following items:

1. General Precautions on Handling of Product

2. Configuration of This Manual

3. Preface

4. Contents

5. Overview

6. Description of Functional Modules

• CPU and System-Control Modules

• On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the

module. However, the generic style includes the following items:

i) Feature

ii) Input/Output Pin

iii) Register Description

iv) Operation

v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section

includes notes in relation to the descriptions given, and usage notes are given, as required, as the

final part of each section.

7. List of Registers

8. Electrical Characteristics

9. Appendix

10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions.

This does not include all of the revised contents. For details, see the actual locations in this

manual.

11. Index

Rev. 4.00 Sep. 14, 2005 Page vi of l

Page 7

Rev. 4.00 Sep. 14, 2005 Page vii of l

Page 8

Preface

The SH7641 RISC (Reduced Instruction Set Comput er ) mi croc omputer includes a Renesas

Technology original RISC CPU as its core, and the peripheral functions required to configure a

system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Users of this manual are expected to understand the

fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

Refer to the SH-3/SH-3E/SH3-DSP Software Manual for a detailed description of

the instruction set.

Notes on reading this manual:

• Product names

The following products are covered in this manual.

Product Classifications and Abbreviations

Basic Classification Product Code

SH7641 HD6417641

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughl y categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU's functions

Read the SH-3/SH-3E/SH3-DSP Software Manual.

This product does not support the MMU functions. For example, the LDTLB instruction code

is executed as the NOP instruction.

Rev. 4.00 Sep. 14, 2005 Page viii of l

Page 9

Rules: Register name: The following notation is used for cases when the same or a

similar function, e.g. serial communication, is implemented

on more than one chann el:

XXX_N (XXX is the register name and N is the channel

number)

Bit order: The MSB (most significant bit) is on the left and the LSB

(least significant bit) is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx , decimal is xxxx.

Signal notation: An overbar is added to a low-active signal: xxxx

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/eng/

SH7641manuals:

Document Title Document No.

SuperH RISC engine SH7641Hardware Manual This manual

SH-3/SH-3E/SH3-DSP Software Manual REJ09B0171

Users manuals for development tools:

Document Title Document No.

SuperHTM RISC engine C/C++ Compiler,Assembler,Optimizing Linkage

Editor Compiler Package V.9.00 User's Manual

SuperHTM RISC engine High-performance Embedded Workshop 3

Users Manual

SuperH RISC engine High-Performance Embedded Workshop 3 Tutorial REJ10B0023

REJ10B0152

REJ10B0025

Application note:

Document Title Document No.

SuperH RISC engine C/C++ Compiler Package Application Note REJ05B0463

Rev. 4.00 Sep. 14, 2005 Page ix of l

Page 10

Abbreviations

ADC Analog to digital converter

ALU Arithmetic logic unit

bpp bits per pixel

bps bits per second

BSC Bus state controller

CODEC Coder-decoder

CPG Clock pulse generator

CPU Central processing unit

CRC Cyclic redund anc y check

DMAC Direct memory access controller

DSP Digital signal processor

ESD Electrostatic discharge

ECC Error checking and correction

etu Elementary time unit

FIFO First-in first-out

Hi-Z High impedance

H-UDI User debugging interface

INTC Interrupt controller

LSB Least significant bit

MSB Most significant bit

PC Program counter

PFC Pin function controller

PLL Phase locked loop

RAM Random access memory

RISC Reduced instruction set computer

ROM Read only memory

SCIF Serial communication interface with FIFO

SOF Start of frame

TAP Test access port

T.B.D To be determined

UBC User break controller

Rev. 4.00 Sep. 14, 2005 Page x of l

Page 11

USB Universal serial bus

WDT Watch dog timer

Rev. 4.00 Sep. 14, 2005 Page xi of l

Page 12

Rev. 4.00 Sep. 14, 2005 Page xii of l

Page 13

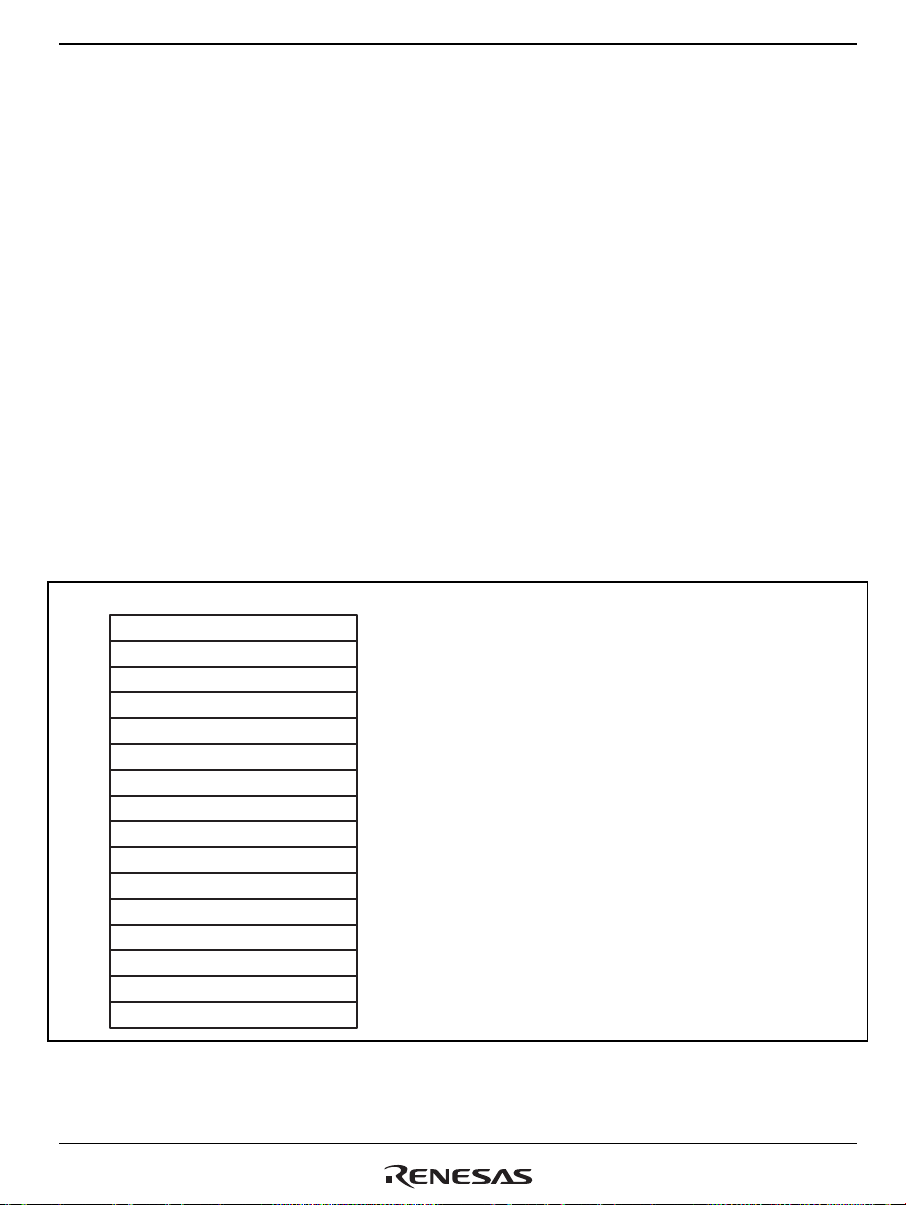

Contents

Section 1 Overview................................................................................................1

1.1 Features.................................................................................................................................. 1

1.2 Block Diagram....................................................................................................................... 7

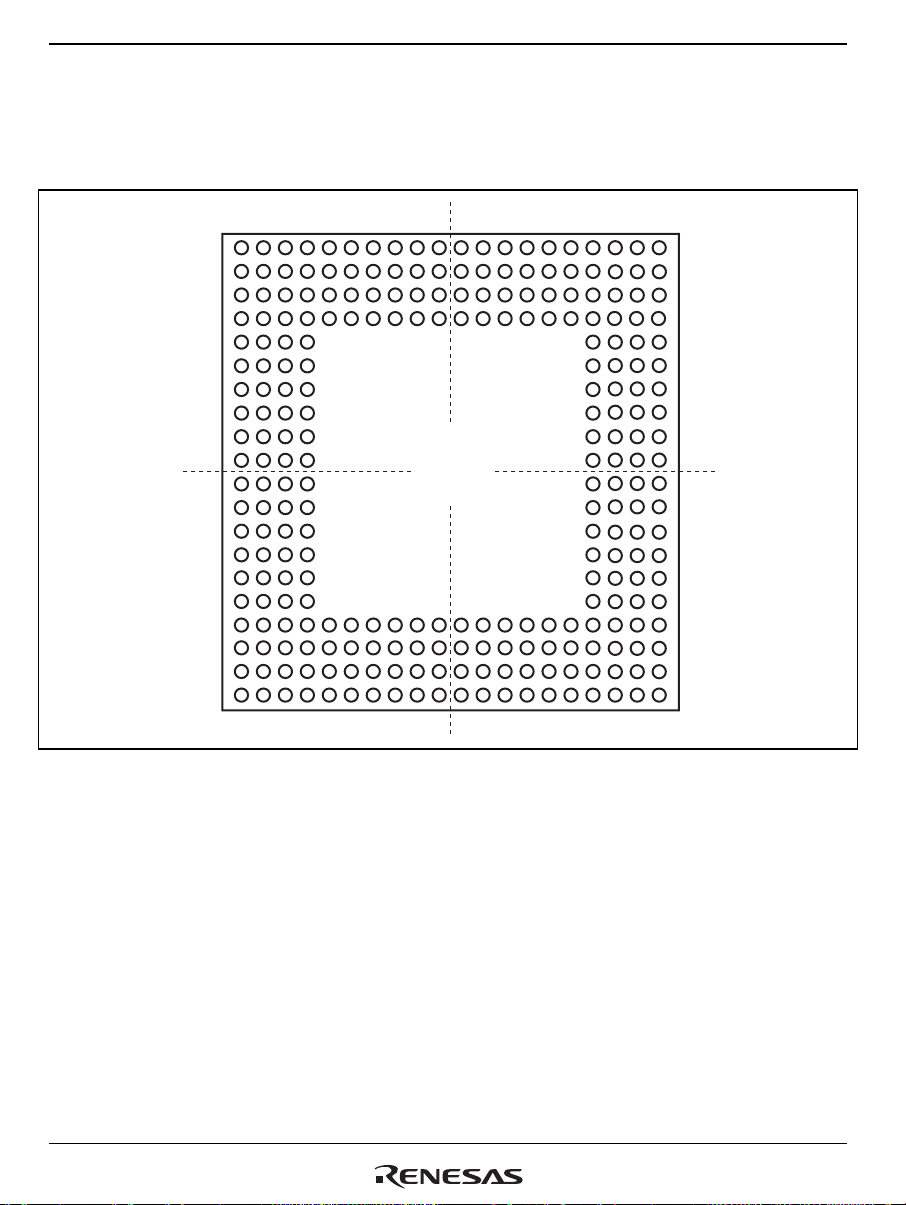

1.3 Pin Assignments.....................................................................................................................8

1.4 Pin functions.......................................................................................................................... 9

Section 2 CPU......................................................................................................25

2.1 Registers...............................................................................................................................25

2.1.1 General Registers....................................................................................................29

2.1.2 Control Registers ....................................................................................................31

2.1.3 System Registers..................................................................................................... 35

2.1.4 DSP Registers.........................................................................................................35

2.2 Data Formats........................................................................................................................42

2.2.1 Register Data Format (Non-DSP Type).................................................................. 42

2.2.2 DSP-Type Data Formats.........................................................................................42

2.2.3 Memory Data Formats............................................................................................ 44

2.3 Features of CPU Core Instructions ......................................................................................44

2.4 Instruction Formats..............................................................................................................48

2.4.1 CPU Instruction Addressing Modes ....................................................................... 48

2.4.2 DSP Data Addressing ............................................................................................. 51

2.4.3 CPU Instruction Formats ........................................................................................58

2.4.4 DSP Instruction Formats......................................................................................... 61

2.5 Instruction Set...................................................................................................................... 67

2.5.1 CPU Instruction Set................................................................................................67

2.6 DSP Extended-Function Instructions................................................................................... 81

2.6.1 Introduction.............................................................................................................81

2.6.2 Added CPU System Control Instructions...............................................................82

2.6.3 Single and Double Data Transfer for DSP Data Instructions..................................84

2.6.4 DSP Operation Instruction Set................................................................................ 88

Section 3 DSP Operation.....................................................................................99

3.1 Data Operations of DSP Unit...............................................................................................99

3.1.1 ALU Fixed-Point Operations .................................................................................. 99

3.1.2 ALU Integer Operations .......................................................................................104

3.1.3 ALU Logical Operations.......................................................................................105

3.1.4 Fixed-Point Multiply Operation............................................................................ 107

Rev. 4.00 Sep. 14, 2005 Page xiii of l

Page 14

3.1.5 Shift Operations.................................................................................................... 109

3.1.6 Most Significant Bit Detection Operation ............................................................ 112

3.1.7 Rounding Operation.............................................................................................. 115

3.1.8 Overflow Protection..............................................................................................117

3.1.9 Data Transfer Operation....................................................................................... 118

3.1.10 Local Data Move Instruction ................................................................................ 122

3.1.11 Operand Conflict .................................................................................................. 123

3.2 DSP Addressing................................................................................................................. 124

3.2.1 DSP Repeat Control.............................................................................................. 124

3.2.2 DSP Data Addressing........................................................................................... 132

Section 4 Clock Pulse Generator (CPG) ...........................................................143

4.1 Features.............................................................................................................................. 143

4.2 Input/Output Pins...............................................................................................................146

4.3 Clock Operating Modes..................................................................................................... 146

4.4 Register Descriptions......................................................................................................... 149

4.4.1 Frequency Control Register (FRQCR)................................................................. 149

4.5 Changing the Frequency....................................................................................................151

4.5.1 Changing the Multiplication Rate......................................................................... 151

4.5.2 Changing the Division Ratio................................................................................. 151

4.6 Notes on Board Design...................................................................................................... 152

Section 5 Watchdog Timer (WDT)...................................................................155

5.1 Features.............................................................................................................................. 155

5.2 Register Descriptions......................................................................................................... 156

5.2.1 Watchdog Timer Counter (WTCNT).................................................................... 156

5.2.2 Watchdog Timer Control/Status Register (WTCSR)............................................ 157

5.2.3 Notes on Register Access ..................................................................................... 159

5.3 Use of the WDT................................................................................................................. 159

5.3.1 Canceling Standbys .............................................................................................. 159

5.3.2 Changing the Frequency....................................................................................... 160

5.3.3 Using Watchdog Timer Mode .............................................................................. 160

5.3.4 Using Interval Timer Mode .................................................................................. 161

5.4 Precautions to Take when Using the WDT........................................................................ 161

Section 6 Power-Down Modes..........................................................................163

6.1 Features.............................................................................................................................. 163

6.1.1 Power-Down Modes.............................................................................................163

6.1.2 Reset ..................................................................................................................... 164

6.1.3 Input/Output Pins.................................................................................................. 165

Rev. 4.00 Sep. 14, 2005 Page xiv of l

Page 15

6.2 Register Descriptions......................................................................................................... 166

6.2.1 Standby Control Register (STBCR)...................................................................... 166

6.2.2 Standby Control Register 2 (STBCR2)................................................................. 167

6.2.3 Standby Control Register 3 (STBCR3)................................................................. 168

6.2.4 Standby Control Register 4 (STBCR4)................................................................. 170

6.3 Operation...........................................................................................................................171

6.3.1 Sleep Mode...........................................................................................................171

6.3.2 Standby Mode....................................................................................................... 172

6.3.3 Module Standby Function..................................................................................... 174

6.3.4 STATUS Pin Change Timings..............................................................................174

Section 7 Cache .................................................................................................179

7.1 Features.............................................................................................................................. 179

7.1.1 Cache Structure..................................................................................................... 180

7.2 Register Descriptions......................................................................................................... 182

7.2.1 Cache Control Register 1 (CCR1) ........................................................................ 182

7.2.2 Cache Control Register 2 (CCR2) ........................................................................ 183

7.3 Cache Operation.................................................................................................................186

7.3.1 Searching Cache ................................................................................................... 186

7.3.2 Read Access..........................................................................................................188

7.3.3 Prefetch Operation................................................................................................ 188

7.3.4 Write Access......................................................................................................... 188

7.3.5 Write-Back Buffer ................................................................................................189

7.3.6 Coherency of Cache and External Memory..........................................................189

7.4 Memory-Mapped Cache .................................................................................................... 190

7.4.1 Address Array....................................................................................................... 190

7.4.2 Data Array ............................................................................................................ 190

7.4.3 Usage Examples....................................................................................................192

Section 8 X/Y Memory......................................................................................193

8.1 Features.............................................................................................................................. 193

8.2 X/Y Memory Access from C PU........................................................................................ 194

8.3 X/Y Memory Access from DSP.........................................................................................194

8.4 X/Y Memory Access from DMAC.................................................................................... 195

8.5 Usage Note.........................................................................................................................195

8.6 Sleep Mode........................................................................................................................ 195

8.7 Address Error..................................................................................................................... 195

Section 9 Exception Handling ...........................................................................197

9.1 Register Descriptions......................................................................................................... 198

Rev. 4.00 Sep. 14, 2005 Page xv of l

Page 16

9.1.1 TRAPA Exception Register (TRA)...................................................................... 198

9.1.2 Exception Event Register (EXPEVT)................................................................... 199

9.1.3 Interrupt Event Register 2 (INTEVT2)................................................................. 199

9.2 Exception Handling Function ............................................................................................ 200

9.2.1 Exception Handling Flow.....................................................................................200

9.2.2 Exception Vector Addresses................................................................................. 201

9.2.3 Exception Codes...................................................................................................201

9.2.4 Exception Request and BL Bit (Multiple Exception Prevention)......................... 201

9.2.5 Exception Source Acceptance Timing and Priority.............................................. 202

9.3 Individual Exception Operations ....................................................................................... 205

9.3.1 Resets.................................................................................................................... 205

9.3.2 General Exceptions............................................................................................... 206

9.4 Exception Processing While DSP Extension Function is Valid.........................................210

9.4.1 Illegal Instruction Exception and Slot Illegal Instruction Exception....................210

9.4.2 Exception in Repeat Control Period ..................................................................... 210

9.5 Note on Initializing this LSI.............................................................................................. 216

9.6 Usage Notes....................................................................................................................... 218

Section 10 Interrupt Controller (INTC).............................................................219

10.1 Features.............................................................................................................................. 219

10.2 Input/Output Pins...............................................................................................................221

10.3 Register Descriptions......................................................................................................... 221

10.3.1 Interrupt Priority Registers B to J (IPRB to IPRJ)................................................ 223

10.3.2 Interrupt Control Register 0 (ICR0)...................................................................... 225

10.3.3 Interrupt Control Register 1 (ICR1)...................................................................... 226

10.3.4 Interrupt Control Register 3 (ICR3)...................................................................... 227

10.3.5 Interrupt Request Register 0 (IRR0).....................................................................228

10.3.6 Interrupt Mask Registers 0 to 10 (IMR0 to IMR10)............................................. 229

10.3.7 Interrupt Mask Clear Registers 0 to 10 (IMCR0 to IMCR10) .............................. 231

10.4 Interrupt Sources................................................................................................................ 233

10.4.1 NMI Interrupt........................................................................................................ 233

10.4.2 H-UDI Interrupt....................................................................................................233

10.4.3 IRQ Interrupts....................................................................................................... 233

10.4.4 On-Chip Peripheral Module Interrupts................................................................. 234

10.4.5 Interrupt Exception Handling and Priority............................................................ 235

10.5 INTC Operation................................................................................................................. 238

10.5.1 Interrupt Sequence................................................................................................238

10.5.2 Multiple Interrupts................................................................................................240

10.6 Notes on Use...................................................................................................................... 240

10.6.1 Notes on USB Bus Power Control........................................................................ 240

Rev. 4.00 Sep. 14, 2005 Page xvi of l

Page 17

10.6.2 Timing to Clear an Interrupt Source ..................................................................... 240

Section 11 User Break Controller (UBC)..........................................................241

11.1 Features..............................................................................................................................241

11.2 Register Descriptions......................................................................................................... 243

11.2.1 Break Address Register A (BARA)......................................................................243

11.2.2 Break Address Mask Register A (BAMRA)......................................................... 244

11.2.3 Break Bus Cycle Register A (BBRA)................................................................... 244

11.2.4 Break Address Register B (BARB) ......................................................................246

11.2.5 Break Address Mask Register B (BAMRB).........................................................247

11.2.6 Break Data Register B (BDRB)............................................................................247

11.2.7 Break Data Mask Register B (BDMRB)............................................................... 248

11.2.8 Break Bus Cycle Register B (BBRB) ................................................................... 249

11.2.9 Break Control Register (BRCR) ...........................................................................251

11.2.10 Execution Times Break Register (BETR).............................................................254

11.2.11 Branch Source Register (BRSR)........................................................................... 254

11.2.12 Branch Destination Register (BRDR)................................................................... 255

11.3 Operation ........................................................................................................................... 256

11.3.1 Flow of the User Break Operation........................................................................256

11.3.2 Break on Instruction Fetch Cycle.......................................................................... 257

11.3.3 Break on Data Access Cycle................................................................................. 258

11.3.4 Break on X/Y-Memory Bus Cycle........................................................................ 259

11.3.5 Sequential Break...................................................................................................260

11.3.6 Value of Saved Program Counter ......................................................................... 260

11.3.7 PC Trace ............................................................................................................... 261

11.3.8 Usage Examples.................................................................................................... 262

11.4 Usage Notes.......................................................................................................................266

Section 12 Bus State Controller (BSC)..............................................................269

12.1 Features..............................................................................................................................269

12.2 Input/Output Pins...............................................................................................................272

12.3 Area Overview...................................................................................................................273

12.3.1 Area Division........................................................................................................ 273

12.3.2 Shadow Area......................................................................................................... 274

12.3.3 Address Map.........................................................................................................275

12.3.4 Area 0 Memory Type and Memory Bus Width .................................................... 277

12.4 Register Descriptions......................................................................................................... 277

12.4.1 Common Control Register (CMNCR)..................................................................278

12.4.2 CSn Space Bus Control Register (CSnBCR) (n = 0, 2, 3, 4, 5A, 5B, 6A, 6B) ..... 281

12.4.3 CSn Space Wait Control Register (CSnWCR) (n = 0, 2, 3, 4, 5A, 5B, 6A, 6B)... 286

Rev. 4.00 Sep. 14, 2005 Page xvii of l

Page 18

12.4.4 SDRAM Control Register (SDCR)....................................................................... 314

12.4.5 Refresh Timer Control/Status Register (RTCSR)................................................. 317

12.4.6 Refresh Timer Counter (RTCNT)......................................................................... 319

12.4.7 Refresh Time Constant Register (RTCOR) .......................................................... 319

12.4.8 Reset Wait Counter (RWTCNT) .......................................................................... 320

12.5 Operating Description........................................................................................................ 321

12.5.1 Endian/Access Size and Data Alignment.............................................................. 321

12.5.2 Normal Space Interface ........................................................................................ 324

12.5.3 Access Wait Control.............................................................................................329

12.5.4 CSn Assert Period Expansion...............................................................................331

12.5.5 MPX-I/O Interface................................................................................................ 332

12.5.6 SDRAM Interface................................................................................................. 335

12.5.7 Burst ROM (Clock Asynchronous) Interface ....................................................... 376

12.5.8 Byte-Selection SRAM Interface ........................................................................... 377

12.5.9 Burst MPX-I/O Interface ...................................................................................... 382

12.5.10 Burst ROM Interface (Clock Synchronous).......................................................... 386

12.5.11 Wait between Access Cycles................................................................................ 387

12.5.12 Bus Arbitration ..................................................................................................... 399

12.5.13 Others....................................................................................................................401

Section 13 Direct Memory Access Controller (DMAC)...................................405

13.1 Features.............................................................................................................................. 405

13.2 Input/Output Pins...............................................................................................................407

13.3 Register Descriptions......................................................................................................... 408

13.3.1 DMA Source Address Registers (SAR)................................................................ 409

13.3.2 DMA Destination Address Registers (DAR)........................................................ 409

13.3.3 DMA Transfer Count Registers (DMATCR) ....................................................... 409

13.3.4 DMA Channel Control Registers (CHCR) ........................................................... 410

13.3.5 DMA Operation Register (DMAOR) ................................................................... 416

13.3.6 DMA Extension Resource Selector 0 and 1 (DMARS0, DMARS1).................... 421

13.4 Operation ........................................................................................................................... 424

13.4.1 DMA Transfer Flow ............................................................................................. 424

13.4.2 DMA Transfer Requests ....................................................................................... 426

13.4.3 Channel Priority.................................................................................................... 429

13.4.4 DMA Transfer Types............................................................................................ 432

13.4.5 Number of Bus Cycle States and DREQ Pin Sampling Timing ........................... 440

13.4.6 Completion of DMA Transfer .............................................................................. 444

13.4.7 Notes on Usage.....................................................................................................445

13.4.8 Notes On DREQ Sampling When DACK is Divided in External Access............ 446

Rev. 4.00 Sep. 14, 2005 Page xviii of l

Page 19

Section 14 U Memory........................................................................................451

14.1 Features..............................................................................................................................451

14.2 U Memory Access from CPU............................................................................................ 452

14.3 U Memory Access from DSP.............................................................................................452

14.4 U Memory Access from DMAC........................................................................................ 452

14.5 Usage Note......................................................................................................................... 453

14.6 Sleep Mode........................................................................................................................453

14.7 Address Error..................................................................................................................... 453

Section 15 User Debugging Interface (H-UDI).................................................455

15.1 Features..............................................................................................................................455

15.2 Input/Output Pins...............................................................................................................456

15.3 Register Descriptions......................................................................................................... 457

15.3.1 Bypass Register (SDBPR) .................................................................................... 457

15.3.2 Instruction Register (SDIR)..................................................................................457

15.3.3 Boundary Scan Register (SDBSR) ....................................................................... 458

15.3.4 ID Register (SDID)............................................................................................... 467

15.4 Operation ........................................................................................................................... 468

15.4.1 TAP Controller ..................................................................................................... 468

15.4.2 Reset Configuration .............................................................................................. 469

15.4.3 TDO Output Timing ............................................................................................. 469

15.4.4 H-UDI Reset ......................................................................................................... 470

15.4.5 H-UDI Interrupt ....................................................................................................470

15.5 Boundary Scan...................................................................................................................471

15.5.1 Supported Instructions .......................................................................................... 471

15.5.2 Points for Attention...............................................................................................472

15.6 Usage Notes.......................................................................................................................472

Section 16 I2C Bus Interface 2 (IIC2)................................................................473

16.1 Features..............................................................................................................................473

16.2 Input/Output Pins...............................................................................................................475

16.3 Register Descriptions......................................................................................................... 476

16.3.1 I2C Bus Control Register 1 (ICCR1)..................................................................... 476

16.3.2 I2C Bus Control Register 2 (ICCR2)..................................................................... 479

16.3.3 I2C Bus Mode Register (ICMR)............................................................................ 480

16.3.4 I2C Bus Interrupt Enable Register (ICIER)...........................................................482

16.3.5 I2C Bus Status Register (ICSR)............................................................................. 484

16.3.6 Slave Address Register (SAR).............................................................................. 486

16.3.7 I2C Bus Transmit Data Register (ICDRT).............................................................487

16.3.8 I2C Bus Receive Data Register (ICDRR).............................................................. 487

Rev. 4.00 Sep. 14, 2005 Page xix of l

Page 20

16.3.9 I2C Bus Shift Register (ICDRS)............................................................................ 487

16.3.10 NF2CYC Register (NF2CYC).............................................................................. 487

16.4 Operation ........................................................................................................................... 488

16.4.1 I2C Bus Format......................................................................................................488

16.4.2 Master Transmit Operation................................................................................... 489

16.4.3 Master Receive Operation .................................................................................... 491

16.4.4 Slave Transmit Operation ..................................................................................... 493

16.4.5 Slave Receive Operation....................................................................................... 496

16.4.6 Clocked Synchronous Serial Format .................................................................... 497

16.4.7 Noise Filter ........................................................................................................... 501

16.4.8 Example of Use..................................................................................................... 502

16.5 Interrupt Request................................................................................................................506

16.6 Bit Synchronous Circuit..................................................................................................... 507

16.7 Usage Note......................................................................................................................... 508

Section 17 Compare Match Timer (CMT)........................................................509

17.1 Features.............................................................................................................................. 509

17.2 Register Descriptions......................................................................................................... 510

17.2.1 Compare Match Timer Start Register (CMSTR).................................................. 510

17.2.2 Compare Match Timer Control/Status Register (CMCSR) .................................. 511

17.2.3 Compare Match Counter (CMCNT ).................................................................... 512

17.2.4 Compare Match Constant Register (CMCOR) ..................................................... 512

17.3 Operation ........................................................................................................................... 513

17.3.1 Interval Count Operation ...................................................................................... 513

17.3.2 CMCNT Count Timing......................................................................................... 513

17.4 Compare Matches..............................................................................................................514

17.4.1 Timing of Compare Match Flag Setting ............................................................... 514

17.4.2 DMA Transfer Requests and Interrupt Requests .................................................. 514

17.4.3 Timing of Compare Match Flag Clearing............................................................. 515

Section 18 Multi-Function Timer Pulse Unit (MTU)........................................517

18.1 Features.............................................................................................................................. 517

18.2 Input/Output Pins...............................................................................................................521

18.3 Register Descriptions......................................................................................................... 522

18.3.1 Timer Control Register (TCR).............................................................................. 524

18.3.2 Timer Mode Register (TMDR)............................................................................. 528

18.3.3 Timer I/O Control Register (TIOR)...................................................................... 530

18.3.4 Timer Interrupt Enable Register (TIER)............................................................... 548

18.3.5 Timer Status Register (TSR)................................................................................. 550

18.3.6 Timer Counter (TCNT)......................................................................................... 553

Rev. 4.00 Sep. 14, 2005 Page xx of l

Page 21

18.3.7 Timer General Register (TGR) .............................................................................553

18.3.8 Timer Start Register (TSTR) ................................................................................ 554

18.3.9 Timer Synchro Register (TSYR) .......................................................................... 554

18.3.10 Timer Output Master Enable Register (TOER)....................................................556

18.3.11 Timer Output Control Register (TOCR)...............................................................557

18.3.12 Timer Gate Control Register (TGCR) .................................................................. 559

18.3.13 Timer Subcounter (TCNTS).................................................................................561

18.3.14 Timer Dead Time Data Register (TDDR).............................................................561

18.3.15 Timer Period Data Register (TCDR)....................................................................561

18.3.16 Timer Period Buffer Register (TCBR)..................................................................561

18.3.17 Bus Master Interface............................................................................................. 562

18.4 Operation ........................................................................................................................... 562

18.4.1 Basic Functions..................................................................................................... 562

18.4.2 Synchronous Operation.........................................................................................568

18.4.3 Buffer Operation...................................................................................................571

18.4.4 Cascaded Operation .............................................................................................. 574

18.4.5 PWM Modes.........................................................................................................576

18.4.6 Phase Counting Mode........................................................................................... 581

18.4.7 Reset-Synchronized PWM Mode.......................................................................... 588

18.4.8 Complementary PWM Mode................................................................................ 591

18.5 Interrupts............................................................................................................................616

18.5.1 Interrupts and Priority........................................................................................... 616

18.5.2 DMA Activation ................................................................................................... 618

18.5.3 A/D Converter Activation..................................................................................... 618

18.6 Operation Timing............................................................................................................... 619

18.6.1 Input/Output Timing.............................................................................................619

18.6.2 Interrupt Signal Timing......................................................................................... 624

18.7 Usage Notes.......................................................................................................................627

18.7.1 Module Standby Mode Setting ............................................................................. 627

18.7.2 Input Clock Restrictions ....................................................................................... 627

18.7.3 Caution on Period Setting .....................................................................................628

18.7.4 Conflict between TCNT Write and Clear Operations .......................................... 628

18.7.5 Conflict between TCNT Write and Increment Operations ................................... 629

18.7.6 Conflict between TGR Write and Compare Match............................................... 630

18.7.7 Conflict between Buffer Register Write and Compare Match.............................. 630

18.7.8 Conflict between TGR Read and Input Capture ...................................................632

18.7.9 Conflict between TGR Write and Input Capture .................................................. 633

18.7.10 Conflict between Buffer Register Write and Input Capture..................................634

18.7.11 TCNT2 Write and Overflow/Underflow Conflict in Cascade Connection........... 634

18.7.12 Counter Value during Complementary PWM Mode Stop....................................636

Rev. 4.00 Sep. 14, 2005 Page xxi of l

Page 22

18.7.13 Buffer Operation Setting in Complementary PWM Mode...................................636

18.7.14 Reset Sync PWM Mode Buffer Operation and Compare Match Flag.................. 637

18.7.15 Overflow Flags in Reset Sync PWM Mode.......................................................... 638

18.7.16 Conflict between Overflow/Underflow and Counter Clearing.............................638

18.7.17 Conflict between TCNT Write and Overflow/Underflow .................................... 639

18.7.18 Cautions on Transition from Normal Operation or PWM Mode 1 to

Reset-Synchronous PWM Mode...........................................................................640

18.7.19 Output Level in Complementary PWM Mode and Reset-Synchronous

PWM Mode .......................................................................................................... 640

18.7.20 Interrupts in Module Standby Mode..................................................................... 640

18.7.21 Simultaneous Input Capture of TCNT_1 and TCNT_2 in

Cascade Connection.............................................................................................. 640

18.8 MTU Output Pin Initialization........................................................................................... 641

18.8.1 Operating Modes .................................................................................................. 641

18.8.2 Reset Start Operation............................................................................................641

18.8.3 Operation in Case of Re-Setting Due to Error During Operation, etc. ................. 642

18.8.4 Overview of Initialization Procedures and Mode Transitions in Case of

Error during Operation, Etc. ................................................................................. 643

18.9 Port Output Enable (POE) ................................................................................................. 673

18.9.1 Features................................................................................................................. 673

18.9.2 Pin Configuration.................................................................................................. 675

18.9.3 Register Configuration.......................................................................................... 675

18.9.4 Operation .............................................................................................................. 681

Section 19 Serial Communication Interface with FIFO (SCIF)........................685

19.1 Overview............................................................................................................................ 685

19.1.1 Features................................................................................................................. 685

19.2 Pin Configuration...............................................................................................................688

19.3 Register Description .......................................................................................................... 689

19.3.1 Receive Shift Register (SCRSR) .......................................................................... 690

19.3.2 Receive FIFO Data Register (SCFRDR) .............................................................. 690

19.3.3 Transmit Shift Register (SCTSR)......................................................................... 690

19.3.4 Transmit FIFO Data Register (SCFTDR)............................................................. 691

19.3.5 Serial Mode Register (SCSMR)............................................................................ 691

19.3.6 Serial Control Register (SCSCR).......................................................................... 695

19.3.7 Serial Status Register (SCFSR) ............................................................................ 699

19.3.8 Bit Rate Register (SCBRR) .................................................................................. 707

19.3.9 FIFO Control Register (SCFCR) .......................................................................... 714

19.3.10 FIFO Data Count Register (SCFDR).................................................................... 717

19.3.11 Serial Port Register (SCSPTR)............................................................................. 717

Rev. 4.00 Sep. 14, 2005 Page xxii of l

Page 23

19.3.12 Line Status Register (SCLSR)..............................................................................720

19.4 Operation ........................................................................................................................... 721

19.4.1 Overview............................................................................................................... 721

19.4.2 Operation in Asynchronous Mode........................................................................723

19.4.3 Synchronous Operation.........................................................................................733

19.5 SCIF Interrupts and DMAC...............................................................................................742

19.6 Usage Notes.......................................................................................................................743

Section 20 USB Function Module.....................................................................747

20.1 Features..............................................................................................................................747

20.1.1 Block Diagram...................................................................................................... 748

20.2 Pin Configuration...............................................................................................................748

20.3 Register Descriptions......................................................................................................... 749

20.3.1 USB Interrupt Flag Register 0 (USBIFR0)........................................................... 750

20.3.2 USB Interrupt Flag Register 1 (USBIFR1)........................................................... 751

20.3.3 USB Interrupt Flag Register 2 (USBIFR2)........................................................... 752

20.3.4 USB Interrupt Select Register 0 (USBISR0) ........................................................ 753

20.3.5 USB Interrupt Select Register 1 (USBISR1) ........................................................ 754

20.3.6 USB Interrupt Enable Register 0 (USBIER0)....................................................... 754

20.3.7 USB Interrupt Enable Register 1 (USBIER1)....................................................... 755

20.3.8 USB Interrupt Enable Register 2 (USBIER2)....................................................... 755

20.3.9 USBEP0i Data Register (USBEPDR0i) ............................................................... 756

20.3.10 USBEP0o Data Register (USBEPDR0o).............................................................. 756

20.3.11 USBEP0s Data Register (USBEPDR0s)...............................................................757

20.3.12 USBEP1 Data Register (USBEPDR1)..................................................................757

20.3.13 USBEP2 Data Register (USBEPDR2)..................................................................758

20.3.14 USBEP3 Data Register (USBEPDR3)..................................................................758

20.3.15 USBEP0o Receive Data Size Register (USBEPSZ0o).........................................758

20.3.16 USBEP1 Receive Data Size Register (USBEPSZ1).............................................759

20.3.17 USB Trigger Register (USBTRG)........................................................................ 759

20.3.18 USB Data Status Register (USBDASTS)............................................................. 760

20.3.19 USBFIFO Clear Register (USBFCLR)................................................................. 761

20.3.20 USBDMA Transfer Setting Register (USBDMAR)............................................. 762

20.3.21 USB Endpoint Stall Register (USBEPSTL) .........................................................763

20.3.22 USB Transceiver Control Register (USBXVERCR)............................................ 764

20.3.23 USB Bus Power Control Register (USBCTRL) ...................................................765

20.4 Operation ........................................................................................................................... 766

20.4.1 Cable Connection..................................................................................................766

20.4.2 Cable Disconnection.............................................................................................767

20.4.3 Control Transfer....................................................................................................768

Rev. 4.00 Sep. 14, 2005 Page xxiii of l

Page 24

20.4.4 EP1 Bulk-OUT Transfer (Dual FIFOs) ................................................................ 774

20.4.5 EP2 Bulk-IN Transfer (Dual FIFOs) .................................................................... 776

20.4.6 EP3 Interrupt-IN Transfer..................................................................................... 778

20.5 Processing of USB Standard Commands and Class/Vendor Commands .......................... 779

20.5.1 Processing of Commands Transmitted by Control Transfer................................. 779

20.6 Stall Operations.................................................................................................................. 780

20.6.1 Forcible Stall by Application................................................................................780

20.6.2 Automatic Stall by USB Function Module...........................................................782

20.7 DMA Transfer....................................................................................................................784

20.7.1 DMA Transfer for Endpoint 1 .............................................................................. 784

20.7.2 DMA Transfer for Endpoint 2 .............................................................................. 785

20.8 Example of USB External Circuitry .................................................................................. 786

20.9 USB Bus Power Control Method....................................................................................... 789

20.9.1 USB Bus Power Control Operation ...................................................................... 789

20.9.2 Usage Example of USB Bus Power Control Method ........................................... 790

20.10 Notes on Usage..................................................................................................................794

20.10.1 Receiving Setup Data ........................................................................................... 794

20.10.2 Clearing FIFO....................................................................................................... 794

20.10.3 Overreading or Overwriting Data Register........................................................... 794

20.10.4 Assigning Interrupt Source for EP0...................................................................... 795

20.10.5 Clearing FIFO when Setting DMA Transfer........................................................795

20.10.6 Manual Reset for DMA Transfer.......................................................................... 795

20.10.7 USB Clock............................................................................................................ 795

20.10.8 Using TR Interrupt................................................................................................ 795

Section 21 A/D Converter.................................................................................797

21.1 Features.............................................................................................................................. 797

21.1.1 Block Diagram...................................................................................................... 798

21.1.2 Input Pins..............................................................................................................799

21.1.3 Register Configuration.......................................................................................... 800

21.2 Register Descriptions......................................................................................................... 800

21.2.1 A/D Data Registers A to D (ADDRA0 to ADDRD0, ADDRA1 to ADDRD1)... 800

21.2.2 A/D Control/Status Registers (ADCSR0, ADCSR1)............................................ 801

21.2.3 A/D0, A/D1 Control Register (ADCR) ................................................................ 804

21.3 Operation ........................................................................................................................... 805

21.3.1 Single Mode.......................................................................................................... 805

21.3.2 Multi Mode........................................................................................................... 806

21.3.3 Scan Mode ............................................................................................................ 808

21.3.4 Simultaneous Sampling Operation ....................................................................... 809

21.3.5 A/D Converter Activation by MTU...................................................................... 810

Rev. 4.00 Sep. 14, 2005 Page xxiv of l

Page 25

21.3.6 Input Sampling and A/D Conversion Time .......................................................... 810

21.4 Interrupt and DMAC Transfer Request..............................................................................812

21.5 Definitions of A/D Conversion Accuracy.......................................................................... 813

21.6 Usage Notes.......................................................................................................................815

21.6.1 Setting Analog Input Voltage ............................................................................... 815

21.6.2 Processing of Analog Input Pins........................................................................... 815

21.6.3 Permissible Signal Source Impedance..................................................................815

21.6.4 Influences on Absolute Precision.......................................................................... 816

21.6.5 Stop during A/D Conversion ................................................................................816

Section 22 Pin Function Controller (PFC).........................................................819

22.1 Register Descriptions......................................................................................................... 823

22.1.1 Port A Control Register (PACR) ..........................................................................824

22.1.2 Port B Control Register (PBCR)........................................................................... 826

22.1.3 Port C Control Register (PCCR)........................................................................... 827

22.1.4 Port D Control Register (PDCR) ..........................................................................828

22.1.5 Port E Control Register (PECR) ........................................................................... 830

22.1.6 Port E I/O Register (PEIOR)................................................................................. 832

22.1.7 Port E MTU R/W Enable Register (PEMTURWER)...........................................833

22.1.8 Port F Control Register (PFCR)............................................................................ 834

22.1.9 Port G Control Register (PGCR) ..........................................................................836

22.1.10 Port H Control Register (PHCR) .......................................................................... 838

22.1.11 Port J Control Register (PJCR)............................................................................. 839

22.2 I/O Buffer Internal Block Diagram....................................................................................841

22.2.1 I/O Buffer with Weak Keeper............................................................................... 841

22.2.2 I/O Buffer with Open Drain Output...................................................................... 841

22.3 Notes on Usage..................................................................................................................842

Section 23 I/O Ports...........................................................................................843

23.1 Port A.................................................................................................................................843

23.1.1 Register Description ............................................................................................. 843

23.1.2 Port A Data Register (PADR)............................................................................... 844

23.2 Port B................................................................................................................................. 845

23.2.1 Register Description ............................................................................................. 845

23.2.2 Port B Data Register (PBDR) ............................................................................... 846

23.3 Port C................................................................................................................................. 847

23.3.1 Register Description ............................................................................................. 847

23.3.2 Port C Data Register (PCDR) ............................................................................... 848

23.4 Port D.................................................................................................................................849

23.4.1 Register Description ............................................................................................. 850

Rev. 4.00 Sep. 14, 2005 Page xxv of l

Page 26

23.4.2 Port D Data Register (PDDR)............................................................................... 850

23.5 Port E.................................................................................................................................851

23.5.1 Register Description ............................................................................................. 852

23.5.2 Port E Data Register (PEDR)................................................................................ 852

23.6 Port F ................................................................................................................................. 853

23.6.1 Register Description ............................................................................................. 854

23.6.2 Port F Data Register (PFDR)................................................................................854

23.7 Port G................................................................................................................................. 856

23.7.1 Register Description ............................................................................................. 856

23.7.2 Port G Data Register (PGDR)............................................................................... 857

23.7.3 Port G Internal Block Diagram.............................................................................859

23.8 Port H................................................................................................................................. 860

23.8.1 Register Description ............................................................................................. 860

23.8.2 Port H Data Register (PHDR)............................................................................... 861

23.9 Port J.................................................................................................................................. 862

23.9.1 Register Description ............................................................................................. 862

23.9.2 Port J Data Register (PJDR) ................................................................................. 863

Section 24 List of Registers...............................................................................865

24.1 Register Addresses

(by functional module, in order of the corresponding section numbers) ........................... 866

24.2 Register Bits....................................................................................................................... 876

24.3 Register States in Each Operating Mode........................................................................... 896

Section 25 Electrical Characteristics.................................................................907

25.1 Absolute Maximum Ratings..............................................................................................907

25.1.1 Power-On Sequence.............................................................................................. 908

25.2 DC Characteristics............................................................................................................. 910

25.3 AC Characteristics............................................................................................................. 915