Page 1

User’s Guide

A

s

D5086

October, 2007

CCOL Translator

ACCOL Translator User’s Guide

Remote Automa tion Solution

www.EmersonProcess.com/Remote

Page 2

BLANK PAGE

Page 3

SECTION 2 – ODD HEADER

Table of Contents

What is the ACCOL Translator? .................................................................................................... 1

How the Translation Works – An Overview .................................................................................. 1

Does everything get translated?.............................................................................................. 1

What happens when the ACCOL Translator encounters an unsupported structure? ............. 2

Tips for Simplifying the Translation Process................................................................................. 2

Consider the Complexity of What You Are Trying to Translate ........................................... 2

Reverse Compile Your ACCOL Load Prior to Translation ................................................... 2

Rename Signals which are IEC 61131-3 Reserved Words Prior to Translation.................... 3

Numerical Values Must Begin with a Whole Number........................................................... 3

Starting the ACCOL Translator...................................................................................................... 4

Starting the Translation................................................................................................................... 4

Choosing Translation Options................................................................................................ 5

Sections of the ACCOL Source File Which are NOT Translated.................................................. 6

Translation of Data Arrays ............................................................................................................. 7

Translation of Signals................................................................................................................... 11

Signal Names........................................................................................................................ 11

Signal Definition................................................................................................................... 12

System Signals...................................................................................................................... 14

Translation of Signal Lists............................................................................................................ 16

Translation of Process I/O ............................................................................................................ 17

Translation of Tasks, Modules, and Control Statements.............................................................. 18

Tasks..................................................................................................................................... 18

Control Statements................................................................................................................ 20

Modules ................................................................................................................................ 20

Syntax of ACCOL II Modules/Structures and Corresponding ACCOL III Structure.................. 22

Application Notes on Module Translations.................................................................................. 38

List of ACCOL II Modules / Structures NOT Translated............................................................ 54

Getting Help on Correcting Errors................................................................................................ 61

Page 4

SECTION 2 – EVEN HEADER

SECTION 2 – EVEN FOOTER

Page 5

Using the ACCOL Translator

What is the ACCOL Translator?

The ACCOL Translator is a Windows™

-based utility which translates an

ACCOL II source (*.ACC) file into a

ControlWave Designer project file

(*.MWT). This translation process

allows re-use of existing ACCOL II

logic during development of new IEC

61131 projects for the ControlWave controller.

How the Translation Works – An Overview

The ACCOL Translator parses the existing ACC file, and generates a new project file from it.

ACCOL II structures are converted to equivalent structures which can be used in ControlWave

Designer with ACCOL III. At the completion of the translation, the new project is automatically

opened within ControlWave Designer.

• Each ACCOL Task is converted to a program organization unit (POU). Each program POU

is defined in the structured text (ST) language of IEC-61131-3.

• Each ACCOL signal is converted to an IEC 61131-3 variable. Logical and logical alarm

signals become variables of type BOOL, and analog and analog alarm signals become

variables of type REAL or UINT (unsigned INTEGER). String signals are converted to

STRING variables.

• Any ACCOL II module which has a counterpart in the ControlWave Designer ACCOL III

firmware library is converted to the equivalent function block in structured text (ST).

Does everything get translated?

No. However, most ACCOL II modules are converted to IEC 61131-3 function blocks and

included in the ACCOL III Firmware Library.

Often, the functionality of the untranslated ACCOL II modules, can be re-created by the user, if

desired, using a combination of user-defined function blocks, and pre-defined ControlWave

Designer functions, function blocks, and keywords.

1

Page 6

Using the ACCOL Translator

What happens when the ACCOL Translator encounters an unsupported

structure?

Any ACCOL II module or structure which is unsupported in IEC 61131-3 is converted to a

comment, e.g. (* COMMENT *).

If an entire section of the ACCOL II source file cannot be converted, a WARNING message will

be displayed in the output window of the ACCOL Translator.

Tips for Simplifying the Translation Process

Consider the Complexity of What You Are Trying to Translate

The ACCOL Translator is best for translating small ACCOL source files, or task-sized segments

of them. Most users will obtain better results by stripping out modules that cannot be translated,

and excess sections of the ACCOL source file prior to attempting the translation.

Complex files containing many unsupported modules tend to result in considerable work in the

post-translation phase in order to remove large commented blocks of unusable code, as well as

corrections of errors.

Reverse Compile Your ACCOL Load Prior to Translation

We recommend that after you edit the ACCOL source file in ACCOL Workbench, and you have

compiled it, that you reverse compile it, prior to running the ACCOL Translator.

SECTION 2 – EVEN FOOTER

2

Page 7

Using the ACCOL Translator

Rename Signals which are IEC 61131-3 Reserved Words Prior to Translation

NOTE: Some valid ACCOL II signal names may be invalid in IEC 61131-3 or may be converted

to IEC 61131-3 keywords. You should rename these signals prior to translation. Particular

examples of this include single character basename signals with no extension or attribute such

as:

S..

R..

as well as other signal names such as:

DATE..

TIME..

CALC..

Some reserved words, such as ADD or SUB will automatically be changed by the ACCOL

Translator to “ADDRWORD’ or “SUBRWORD”. When this is done, it may be necessary to

modify any HMI packages that have been programmed to use the reserved words as variable

names, especially if the “_USE_ACCOL_NAME” system variable has been turned on.

As of this writing, ACCOL Translator does not convert the words TRUE and FALSE. If these

names are used for signals, the programmer will have to rename all usages of those names to

#ON and #OFF, or to other names, as appropriate, in the ACCOL source file, prior to running the

ACCOL Translator.

Numerical Values Must Begin with a Whole Number

If your code in ACCOL Workbench includes numerical values or calculator expressions that do

NOT begin with a whole number to the left of the decimal point, for example,

.5

.732

etc., you must add the leading whole number, before performing the translation i.e.

0.5

0.732

or else your code will NOT be translated correctly.

3

Page 8

Using the ACCOL Translator

anslatio

Starting the ACCOL Translator

Click on StartÆ Programs Æ OpenBSI Tools Æ Utility Programs Æ ACCOL Translator

Starting the Translation

Type the path and filename of the ACCOL source file (*.ACC) to be translated into the “Input

File” field, or use the [Browse] button to locate and specify the file. A name for the project will

be chosen based on that name, with an extension of *.MWT. You can change the path and

basename, but do not change the extension.

If desired, choose translation options by clicking on the [Options] button. (See ‘Choosing

Translation Options’ later in this section.)

Finally, click on the [Translate] button to start the translation. The progress bar shows the

amount of translation which is complete. Messages detailing the sections being translated will

also be displayed.

ControlWave Designer will automatically be opened with the new project when the translation is

complete. Click on [Exit] to close the ACCOL Translator.

Enter the path and filename

of the ACCOL source file to

be converted (or use the

[Browse]

button to select it.

Path and filename

of the resulting

ControlWave

project.

Messages detailing

the status of the

translation are

displayed here.

Progress of the

translation is

shown here.

SECTION 2 – EVEN FOOTER

Click here

to start the

tr

Click here to specify

translation options.

n.

4

Page 9

Using the ACCOL Translator

Choosing Translation Options

Click on the [Options] button in the Acctrans dialog box to specify translation options:

Signal Names Reserved for future use.

Remove Temp Files Causes temporary files created in the ACCOL directory during the

translation to be deleted after translation is complete. The default is to

leave the temporary files.

5

Page 10

Using the ACCOL Translator

Sections of the ACCOL Source File Which are NOT

Translated

Several sections common to all ACCOL loads are NOT translated into IEC 61131-3. Typically,

this is because the corresponding structures in IEC 61131-3 or the ControlWave controller are

handled differently. The table, below, outlines the sections which are not translated.

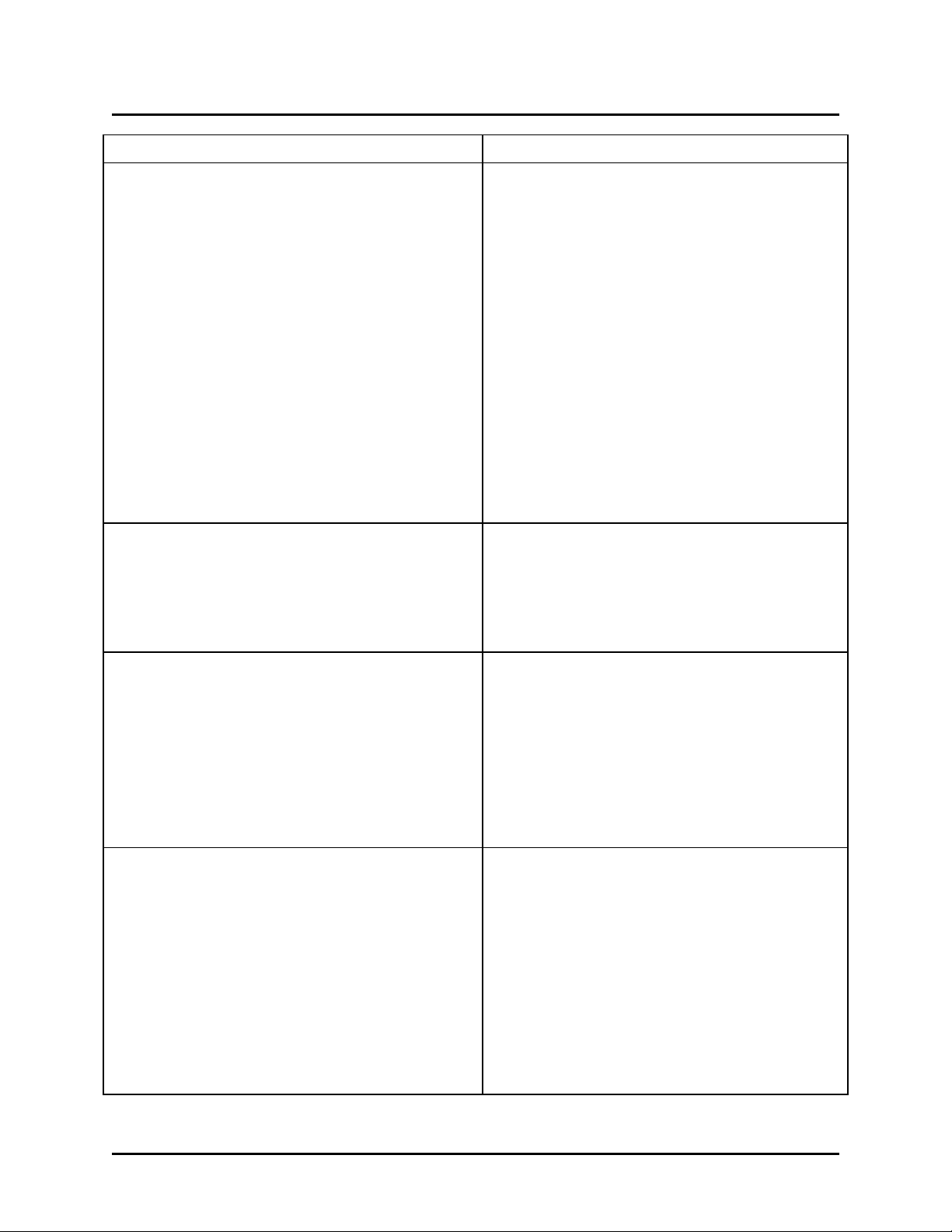

ACCOL Section Name Reason why the section is NOT translated into IEC 61131-3

structured text

*TARGET The target controller, by definition, must support IEC 61131-3.

The firmware libraries available determine which types of

controllers can be used; not any specific identifier.

*SECURITY-CODES Security is handled differently in the ControlWave controller;

security is configured via the Flash Configuration Utility.

*MEMORY Memory does NOT need to be explicitly allocated.

*BASENAMES IEC 61131-3 variables do not use basename descriptive text.

*LOW-LEVEL The Low-Level Analog Input board is supported for CW_10 and

CW_30 only.

*FORMAT Format codes are NOT supported in the ControlWave controller.

*COMMUNICATIONS Communication ports are configured via the Flash Configuration

Utility.

SECTION 2 – EVEN FOOTER

6

Page 11

Using the ACCOL Translator

Translation of Data Arrays

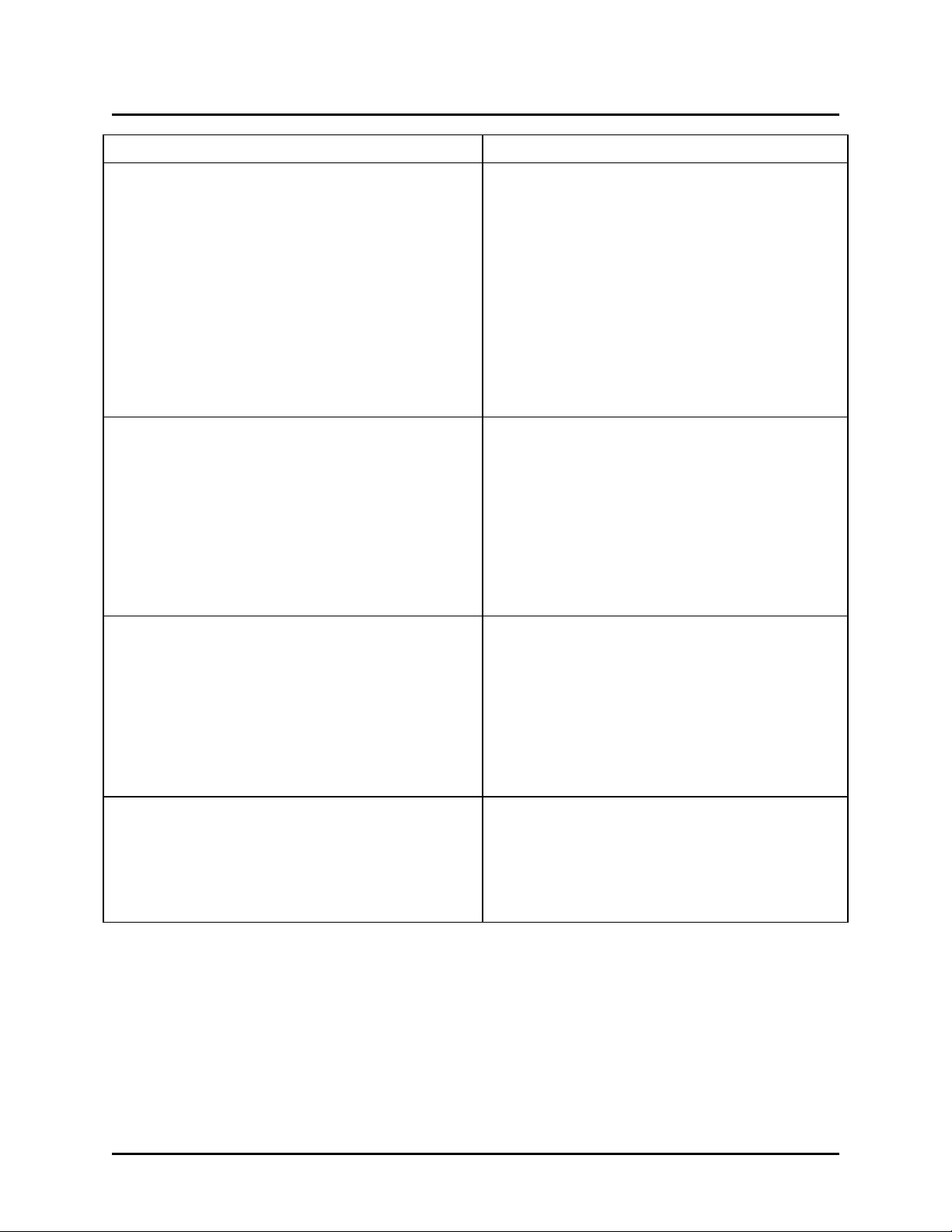

Analog Data Array Declaration (both Read Only RO and Read Write RW)

Each analog data array is defined in the DATATYPE section as a new data type. The new data

type consists of a one dimensional array of one dimensional arrays. This allows an equivalent set

of row, column elements to be defined.

ACCOL Workbench (.ACC) File

Structure

*A-ARRAY x Rt (r,c)

where x = array number

r = number of rows

c= number of columns

t = O – read only

= W – read write

Example:

*A-ARRAY 1 RO (5,7)

NOTE: The actual array variables (which are of the type defined in the DATATYPE section)

appear in the Global_Variables section.

Equivalent Construct in ControlWave

Designer

DATATYPE section

TYPE

ANAx_C : ARRAY[1..c] OF REAL; (or

UINT)

ANAx_R : ARRAY[1..r] OF ANAx_C;

END_TYPE

Where x = array number

r = number of rows

c= number of columns

Equivalent Example:

TYPE

ANA1_C : ARRAY[1..7] OF REAL;

ANA1_R : ARRAY[1..5] OF ANA1_C;

END_TYPE

7

Page 12

Using the ACCOL Translator

Analog Array Initialization (Read-Only Arrays)

Each read-only array is initialized in the system task called Inittsk. Inittsk runs once, on cold

start.

NOTE: The same general syntax for initialization in ControlWave Designer is also valid for

setting array values after initialization in read-write arrays.

ACCOL Workbench (.ACC) File

Structure

*A-ARRAY x RO (m,n)

r1c1 r1c2 r1c3 …. r1cm

r2c1 r2c2..r2c3… r2cm

: : : :

rnc1 rnc2 rnc3… rncm

where x = array number

m = number of rows

n= number of columns

r1c1 through rncm = initial values

Example:

*A-ARRAY 1 RO (2,3)

17.5 3.4 8.2

8.3 7.3 4.1

Equivalent Construct in ControlWave

Designer

(* Beginning of Array Section *)

Ana_x_Array[r1] [c1] := r1c1

Ana_x_Array[r1] [c2] := r1c2

: : : :

Ana_x_Array[rn] [cm] := rncm

where x = array number

r = number of rows

c= number of columns

r1c1 through rncm = initial values

Equivalent Example:

Ana_1_Array[1] [1] := 17.5000000;

Ana_1_Array[1] [2] := 3.4000000;

Ana_1_Array[1] [3] := 8.2000000;

Ana_1_Array[2] [1] := 8.3000000;

Ana_1_Array[2] [2] := 7.3000000;

Ana_1_Array[2] [3] := 4.1000000;

SECTION 2 – EVEN FOOTER

8

Page 13

Using the ACCOL Translator

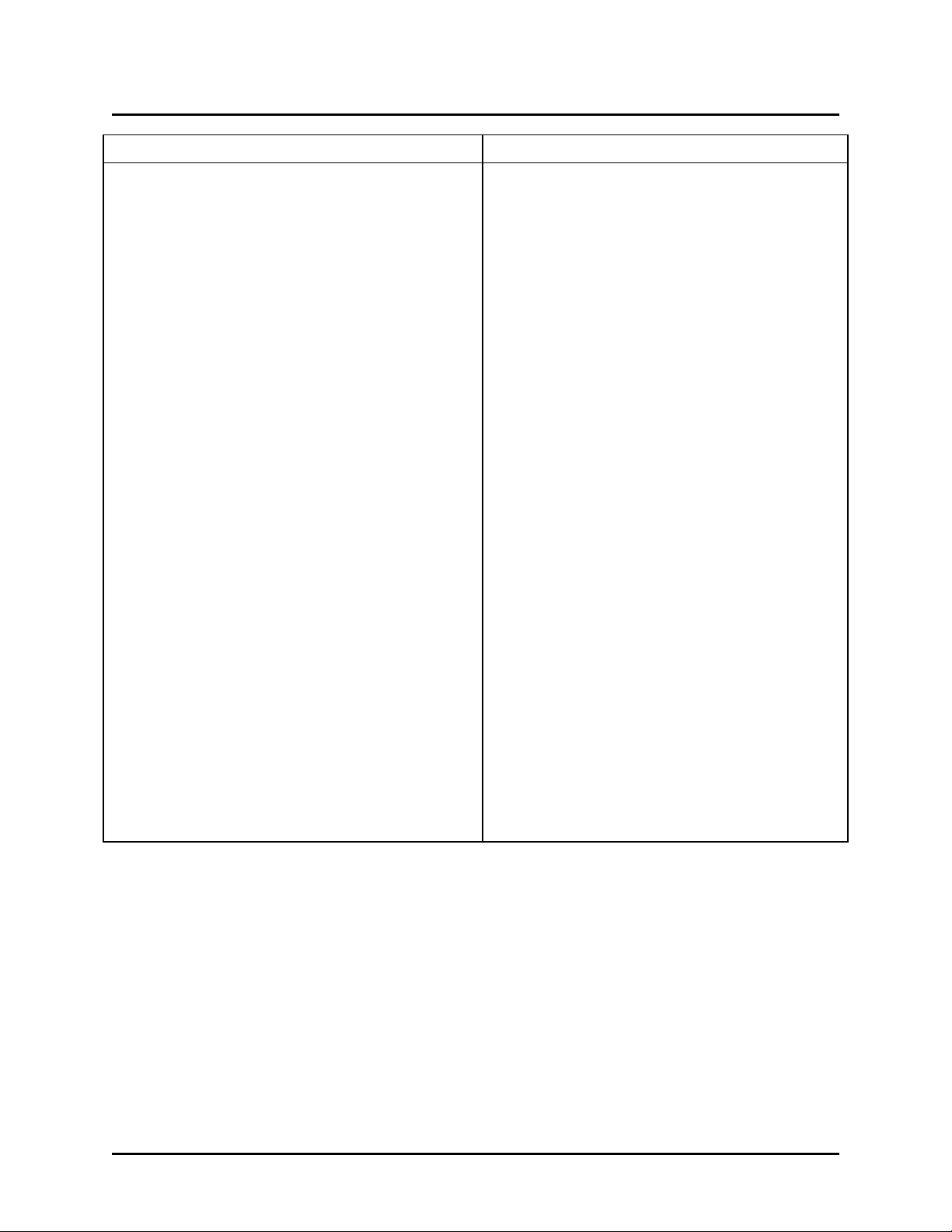

Logical Data Array Declaration (both Read Only RO and Read Write RW)

Each logical data array is defined in the DATATYPE section as a new data type. The new data

type consists of a one dimensional array of one dimensional arrays. This allows an equivalent set

of row, column elements to be defined.

ACCOL Workbench (.ACC) File

Structure

*L-ARRAY x Rt (r,c)

where x = array number

r = number of rows

c= number of columns

t = O – read only

= W – read write

Example:

*L-ARRAY 1 RW (12,16)

NOTE: The actual array variables (which are of the type defined in the DATATYPE section)

appear in the Global_Variables section.

Equivalent Construct in ControlWave

Designer

DATATYPE section

TYPE

LOGx_C : ARRAY[1..c] OF BOOL;

LOGx_R : ARRAY[1..r] OF LOGx_C;

END_TYPE

Where x = array number

r = number of rows

c= number of columns

Equivalent Example:

TYPE

LOG1_C : ARRAY[1..16] OF BOOL;

LOG1_R : ARRAY[1..12] OF LOG1_C;

END_TYPE

9

Page 14

Using the ACCOL Translator

Logical Array Initialization (Read-Only Arrays)

Each read-write array is initialized in the system task called Inittsk. Inittsk runs once, on cold

start.

NOTE: The same general syntax for initialization in ControlWave Designer is also valid for

setting array values after initialization in read-write arrays.

ACCOL Workbench (.ACC) File

Structure

*L-ARRAY x RO (m,n)

r1c1 r1c2 r1c3 …. r1cm

r2c1 r2c2..r2c3… r2cm

: : : :

rnc1 rnc2 rnc3… rncm

where x = array number

m = number of rows

n= number of columns

r1c1 through rncm = initial values

Example:

*L-ARRAY 1 RO (4,3)

1 0 0

1 1 0

0 0 1

1 0 1

Equivalent Construct in ControlWave

Designer

(* Beginning of Array Section *)

Log_x_Array[r1] [c1] := r1c1

Log_x_Array[r1] [c2] := r1c2

: : : :

Log_x_Array[rn] [cm] := rncm

where x = array number

r = number of rows

c= number of columns

r1c1 through rncm = initial values

Equivalent Example:

Log_1_Array[1] [1] := TRUE;

Log_1_Array[1] [2] := FALSE;

Log_1_Array[1] [3] := FALSE;

Log_1_Array[2] [1] := TRUE;

Log_1_Array[2] [2] := TRUE;

Log_1_Array[2] [3] := FALSE;

Log_1_Array[3] [1] := FALSE;

Log_1_Array[3] [2] := FALSE;

Log_1_Array[3] [3] := TRUE;

Log_1_Array[4] [1] := TRUE;

Log_1_Array[4] [2] := FALSE;

Log_1_Array[4] [3] := TRUE;

SECTION 2 – EVEN FOOTER

10

Page 15

Using the ACCOL Translator

Translation of Signals

Signal Names

Signals are converted to IEC 61131-3 variables. IEC 61131-3 does NOT support periods

embedded in variable names, therefore, the periods separating the basename and extension, and

the extension and the attribute of an ACCOL signal name are converted to underscores.

ACCOL Workbench (.ACC) File

Structure

basename.extension.attribute

where:

basename= up to 8 characters

extension = up to 6 characters

attribute = up to 4 characters

Example:

COMPRSR3.FLOW.TOT

NOTE: ControlWave Designer allows variable names up to 30 characters in length. If, however,

you will be using a version of Open BSI Utilities older than Version 4.1 to collect data, you

should limit your variable names to no more than 20 characters.

NOTE: If you have an ACCOL II signal with a basename and attribute, but no extension, the

extension will be replaced with the word ‘dot’. For example:

COMPRSR3..TOT will be translated to COMPRSR3_dot_TOT

Equivalent Construct in ControlWave

Designer

basename_extension_attribute

where:

basename= up to 8 characters

extension = up to 6 characters

attribute = up to 4 characters

Example:

COMPRSR3_FLOW_TOT

11

Page 16

Using the ACCOL Translator

Signal Definition

All ACCOL logical and logical alarm signals are converted to IEC 61131-3 variables of type

BOOL. All ACCOL analog and analog alarm signals are converted to IEC 61131-3 variables of

type REAL or UINT (unsigned Integer). By default, the variables are stored in the

Global_Variables section of the project. When ACCOL signals are converted to IEC 61131-3

variables, certain characteristics of the signal are NOT translated, because they have no direct

counterpart in IEC 61131-3.

The following characteristics of ACCOL signals are NOT translated to IEC 61131-3:

• Basename descriptive text (except in the case of alarms)

• Questionable data flag.

• Initial values for manual inhibit/enable, alarm inhibit/enable, control inhibit/enable flags.

However, CALCULATOR statements making use of these flags are translated. See VARATTRIB_GET, VAR_ATTRIB_SET, and VAR_CI_PROC.

• Units text for analog signals. Will be supported for analog alarms, however.

• ON/OFF text for logical signals (other than TRUE or FALSE) which are NOT alarms.

ACCOL Workbench (.ACC) File

Structure

Logical Signals, Logical Alarm Signals

name type read_sec write_sec mi ci

[ai] initial onoff [alarmtype] priority

where:

name= signal name

type = L for logical or LA for logical alarm

read_sec = security level for read access

write_sec = security level for write access

mi = manual inhibit/enable flag

ci = control inhibit/enable flag

[ai] = alarm inhibit/enable flag (alarm

signals only)

initial = initial value of signal 0 = OFF 1 =

ON.

onoff = ON and OFF text

[alarmtype] = condition which generates

Equivalent Construct in ControlWave

Designer

variable declaration section

Boolean Variables

name : BOOL := initial;

where

name = the variable name

initial = the initial value of the variable

SECTION 2 – EVEN FOOTER

12

Page 17

Using the ACCOL Translator

ACCOL Workbench (.ACC) File

Structure

alarm (either TRUE or FALSE or

CHANGE). (alarm signals only)

priority = C – Critical (alarm signals only)

N – Non-critical

O – Operator Guide

E – Event

Example:

PUMP1.START.CMD LA R1 W3 ME

CE AE 0 RUN HALT TRUE C

ACCOL Workbench (.ACC) File

Structure

Analog Signals, Analog Alarm Signals

name type read_sec write_sec mi ci

[ai] initial units [deadband] [limits]

priority

where:

name= signal name

type = A for analog or AA for analog alarm

read_sec = security level for read access

write_sec = security level for write access

mi = manual inhibit/enable flag

ci = control inhibit/enable flag

[ai] = alarm inhibit/enable flag (alarm

signals only)

initial = initial value of signal.

units = units text e.g. HOURS

[deadband] = alarm deadband value (alarm

signals only)

[limits] = alarm limit value(s) (alarms

signals only)

priority = C – Critical (alarm signals only)

N – Non-critical

O – Operator Guide

Equivalent Construct in ControlWave

Designer

variable declaration section

Example:

PUMP1_START_CMD : BOOL := FALSE;

Equivalent Construct in ControlWave

Designer

variable declaration section

REAL Variables

name : REAL := initial;

- orname : UINT := initial;

where

name = the variable name

initial = the initial value of the variable

13

Page 18

Using the ACCOL Translator

ACCOL Workbench (.ACC) File

Structure

E – Event

Example:

F101.FLOW.TOT AA R1 W3 ME CE

AE 0.0000000 GPM HDB: 20 LDB: 5

HALM: 100 LALM: 10 C

System Signals

Many ACCOL II system signals do NOT have counterparts in ControlWave Designer with

ACCOL III.

Certain similar variables, for example, for measuring time like #TIME.00x ACCOL signals, etc.

are created in the SYS_VAR_WZ_DATA section of the Global_Variables, when you run the

System Variable Wizard in ControlWave Designer. These system variables are distinguished

from other variables by an underscore at the front of the variable name. For example,

_TIME_005. A list of these appears below:

Equivalent Construct in ControlWave

Designer

variable declaration section

Example:

F101_FLOW_TOT : REAL := 0.0000000;

VAR_GLOBAL

_TS_INHIB AT %MX 3.0.3 : BOOL;

_TS_REQ AT %MX 3.0.2 : BOOL;

_TIME_000 AT %MD 3.4 : DWORD;

_TIME_001 AT %MD 3.8 : DINT;

_TIME_002 AT %MW 3.12 : INT;

_TIME_003 AT %MB 3.14 : SINT;

_DAY_OF_WEEK AT %MB 3.15 : SINT;

_TIME_004 AT %MB 3.16 : SINT;

_TIME_005 AT %MB 3.17 : SINT;

_TIME_006 AT %MB 3.18 : SINT;

_TIME_007 AT %MB 3.19 : SINT;

_TIME_008 AT %MW 3.4 : INT;

_CPU_OUT_ERR AT %MD 3.24 : DINT;

SECTION 2 – EVEN FOOTER

14

Page 19

Using the ACCOL Translator

_T0_SLIP AT %MD 3.1000 : DINT;

_T1_SLIP AT %MD 3.1032 : DINT;

_T1_FPERR AT %MD 3.1036 : DINT;

_T2_SLIP AT %MD 3.1064 : DINT;

_T2_FPERR AT %MD 3.1068 : DINT;

_P1_TYPE AT %MB 3.3000 : SINT;

_P1_RECEIVES AT %MD 3.3004 : DINT;

_P1_TRANSMIT AT %MD 3.3008 : DINT;

_P1_POLLS AT %MD 3.3012 : DINT;

END_VAR

Certain other ACCOL II system signals are translated to system variables with similar names in

ACCOL III, and stored in the SYSTEM_VARIABLES group in the Global Variables worksheet

(as opposed to the SYS_VAR_WIZ_DATA group.) If there are counterpart system signals with

different names, the translated names based on the original name will be mapped to point to

memory location for the actual system variable.

If there is no corresponding system variable, the translated variable will only be a variable, NOT

a system variable.

They do NOT, however, have the same functionality of the ACCOL II equivalents; they are

simply variables. Users can choose to rename them or otherwise change the logic they are used

with.

15

Page 20

Using the ACCOL Translator

Translation of Signal Lists

ACCOL signal lists are converted into lists in the Inittsk section of the project. The Inittsk

section only executes once.

ACCOL Workbench (.ACC) File

Structure

*LIST listnumber

listlinenum1 signal1

listlinenum2 signal2

listlinenum3 signal3

: :

listlinenumn signaln

where:

listnumber = the number identifying this

signal list

listlinenum1… n = line numbers for the list

signal1 … signaln = ACCOL signals

Example:

*LIST 5

10 PUMP1.RUN.

20 PUMP2.RUN.

30 PUMP3.RUN.

Equivalent Construct in ControlWave

Designer

Structured Text (ST)

(* Beginning of Lists Section *)

LIST_size_id ( iiListnumber := number,

ianyElement1 := variable1,

ianyElement2 := variable2,

ianyElement3 := variable3,

: :

ianyElementn := variablen;

(* * INT * :=LIST_id.odiStatus; *)

where:

size = maximum number of items in the list. Can

be 10, 20, 30, 50, or 100.

id = a number identifying this list

number = a number identifying the iilistnumber.

variable1…variablen = the variable name

Example:

(* Beginning of Lists Section *)

LIST_10_5 ( iiListNumber := number,

ianyElement1 := PUMP1_RUN,

ianyElement2 := PUMP2_RUN,

ianyElement3 := PUMP3_RUN);

(* * INT * := LIST_10_5.odiStatus; *)

SECTION 2 – EVEN FOOTER

16

Page 21

Using the ACCOL Translator

Translation of Process I/O

Because of direct access to I/O through variables, process I/O modules such as ANIN, DIGIN,

DIGOUT are not converted.

The ANOUT module is converted, since it has a special usage with some function blocks, e.g.

PID3TERM.

I/O points associated with process I/O boards are converted to global variables in the

IO_GLOBAL_VARIABLES section of the Global_Variables page in the project tree.

Once you have opened the project in ControlWave Designer, you must make I/O assignments

using the I/O Configurator (accessible in ControlWave Designer through ViewÆIO

Configurator).

17

Page 22

Using the ACCOL Translator

Translation of Tasks, Modules, and Control

Statements

Tasks

Each ACCOL task is converted into a

logical program POU of the same

name. For example, ACCOL Task 1, is

converted to a logical POU called

‘Task1’.This logical POU is then

automatically inserted within an IEC

61131-3 task which handles the

execution rate and priority.

Certain ACCOL task characteristics are

converted into settings for the

corresponding IEC 61131-3 task. For

example, the ACCOL task rate

becomes the “Interval” for the IEC

61131-3 cyclic task.

Task line numbers are automatically converted into (* Comment *) statements.

IMPORTANT

If there are 14 or fewer ACCOL tasks to be translated, the IEC 61131-3 task name will be

the same as the newly created POU it contains. ControlWave Designer, however, can only

have a maximum of 16 IEC 61131-3 tasks. Therefore, if your ACCOL source file contains

more than 14 ACCOL tasks (including Task 0), all the ACCOL tasks will be converted to

POUs, but those POUs will automatically be distributed among a maximum of 14 IEC

61131-3 tasks in ControlWave Designer. Two additional tasks (system tasks) are

automatically created by the ACCOL Translator. The system tasks are used for initializing

lists, and other special purposes.

For example, if your ACCOL source file contains 20 ACCOL tasks, the ACCOL Translator

will generate 20 program POUs (1 for each of the ACCOL tasks), but only 16 IEC 61131-3

tasks (2 of which are System Tasks). The 20 POUs will be distributed among the 14 IEC

61131-3 non-system tasks. You can manually reassign the POUs, as desired, if you want

them in different tasks. When deciding whether to reassign a particular POU, you need to

consider whether another IEC 61131-3 task already has an identical execution rate and

priority. You only need one task for a given rate / priority, since multiple program POUs

can run in the same task.

SECTION 2 – EVEN FOOTER

18

Page 23

Using the ACCOL Translator

ACCOL Workbench (.ACC) File Structure Equivalent Construct in ControlWave

Designer

*TASK tasknumber RATE: rate PRI: priority

linenum1 control_statement, comment or

module

linenum2 control_statement, comment or

module

linenum3 control_statement, comment or

module

: : :

linenumn control_statement, comment or

module

where:

tasknumber = the number of the task

rate = the execution rate of the task

priority = the priority of the task

linenum1 linenumn = task line numbers

control_statement = ACCOL control statements

comment = a comment

module = ACCOL module

Example:

*TASK 1 RATE: 10.000000 PRI: 1

10 * IF (START.TASK<15)

20 * CALCULATOR

10 START.TASK=START.TASK+1

30 * ELSE

40 * C ** TWO DIMENSION FUNCTION MODULE

50 * C ** FUN.TEST1.HLT IS CTRL INHIBITED *

60 * IF (~FUN.TEST1.HLT)

70 * CALCULATOR

10 FUN1.TEST.CNT=FUN1.TEST.CNT+1

20 LINE.CNT.001=LINE.CNT.001+1

30 :IF(LINE.CNT.001>16)

40 LINE.CNT.001=1

50 :ENDIF

60 FUN.ROW.001=#ADATA 2[LINE.CNT.001]

70 FUN.COL.001=#ADATA 3[LINE.CNT.001]

80 * FUNCTION

ARRAY FUN.ARRAY.001

ROW FUN.ROW.001

COLUMN FUN.COL.001

linenum1

control_statement, comment or fcnblock

linenum2

control_statement, comment or fcnblock

linenum3

control_statement, comment or fcnblock

: : :

linenumn

control_statement, comment or fcnblock

where:

linenum1..n = comment identifying the

ACCOL task line number

from the source ACC file

control_statement = IEC 61131-3 control

statements

comment = a comment

module = function block from Bbifsb library

Example:

(* *TASK 1 RATE: 10.000000 PRI: 1 *)

(* Line: 10 *)

IF (START_TASK<15.0) THEN

(* Line: 20 *)

START_TASK:=START_TASK+1.0;

(* Line: 30 *)

ELSE

(* Line: 40 *)

(** TWO DIMENSION FUNCTION MODULE*)

(* Line: 50 *)

(* *FUN.TEST1.HLT IS CTRL INHIBITED *)

(* Line: 60 *)

IF ( NOT FUN_TEST1_HLT) THEN

(* Line: 70 *)

FUN1_TEST_CNT:=FUN1_TEST_CNT+1.0;

LINE_CNT_001:=LINE_CNT_001+1.0;

IF (LINE_CNT_001>16.0) THEN

LINE_CNT_001:=1.0;

END_IF;

FUN_ROW_001:=Ana_2_Array[LINE_CNT_001];

19

Page 24

Using the ACCOL Translator

OUTPUT FUN.OUT.001

FUN_COL_001:=Ana_3_Array[LINE_CNT_001];

(* Line: 80 *)

(*FUNCTION *)

FUNCTION_80(

irFunctionArray := FUN_ARRAY_001,

irRow := FUN_ROW_001,

irColumn := FUN_COL_001);

FUN_OUT_001 := FUNCTION_80.orOutput;

(* * REAL * := FUNCTION_80.orStatus;*)

Control Statements

• IF, ENDIF, ELSE, ELSEIF are converted to IF, THEN, and

ELSE statements in structured text.

• FOR statements are converted to FOR keywords in structured

text.

• Most other ACCOL control statements (ABORT, GOTO,

SUSPEND, RESUME, WAIT) are not supported, and so are

converted into (* Comment *) statements.

Modules

• When parsing the ACCOL task, any ACCOL module encountered

which exists in the ACCOL III library is declared as an IEC 61131-3

function block.

• Function block parameters are treated as assignment statements.

• The function blocks may have slightly different parameter names than

the module terminals in the original module. Most parameter names are

preceded by a prefix which identifies whether the parameter is an input

variable to the function block, or an output variable from the function

block, and also the variable type (e.g. BOOL, REAL, or UINT). For

example, a module terminal named Setpoint, would become a function

block parameter named irSetpoint.

SECTION 2 – EVEN FOOTER

20

Page 25

Using the ACCOL Translator

The table, below, summarizes the meaning of the letters in the parameter name prefix.

Parameter Name

Prefix

ia, iany INPUT REAL, SINT, INT, DINT

iab INPUT BOOL variable - NO constants allowed.

iais INPUT STRING or INT variable. No constants.

iar INPUT REAL variable - NO constants allowed.

iarb INPUT REAL or BOOL variable. NO constants allowed.

iaus INPUT USINT variable or array of USINT. No constants.

ib INPUT BOOL variable or constant

idi INPUT DINT variable or constant

ii INPUT INT variable or constant

ioab INPUT & OUTPUT BOOL variable - NO constants allowed.

ioar INPUT & OUTPUT REAL variable - NO constants allowed.

ir INPUT REAL variable or constant

is, isi INPUT SINT variable or constant

is, istr INPUT STRING (must be surrounded by single quotes)

iudi INPUT UDINT variable or constant

iui INPUT UINT variable or constant

ius INPUT USINT variable or constant

ob OUTPUT BOOL variable or constant

odi OUTPUT DINT variable or constant

oi OUTPUT INT variable or constant

or OUTPUT REAL variable or constant

oud OUTPUT UDINT variable or constant

oui OUTPUT UINT variable or constant

ous OUTPUT USINT variable or constant

Input or Output Valid Data Types:

NOTE: You CANNOT use constants on parameters

with the 'ia' or 'iany' prefix; only variables may be

used.

21

Page 26

Using the ACCOL Translator

Syntax of ACCOL II Modules/Structures and

Corresponding ACCOL III Structure

NOTE: In the table below, ACCOL II modules appear in the left column, and the corresponding

ACCOL III translated fuction block or keyword in structured text (ST) is shown in the right

column. For details on how the various function blocks work, please consult the online help files

in ControlWave Designer.

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

10 * AAT

FREQ_1 ANALOG.SIGNAL.

FREQ_2 ANALOG.SIGNAL.

COUNT_1 ANALOG.SIGNAL.

COUNT_2 ANALOG.SIGNAL.

LIST_1 ANALOG.SIGNAL.

LIST_2 ANALOG.SIGNAL.

LIST_3 ANALOG.SIGNAL.

STATUS_1 ANALOG.SIGNAL.

STATUS_2 ANALOG.SIGNAL.

STATUS_3 ANALOG.SIGNAL.

STATUS_4 ANALOG.SIGNAL.

20 * AGA3

DIFF_PRESS ANALOG.SIGNAL.

STAT_PRESS ANALOG.SIGNAL.

ADJ_PRESS ANALOG.SIGNAL.

ORIF_DIAM ANALOG.SIGNAL.

PIPE_DIAM ANALOG.SIGNAL.

ORIF_CONST ANALOG.SIGNAL.

BASE_PRESS ANALOG.SIGNAL.

BASE_TEMP ANALOG.SIGNAL.

FLOW_TEMP ANALOG.SIGNAL.

FPV_IN ANALOG.SIGNAL.

POINT ANALOG.SIGNAL.

SPEC_GRAV ANALOG.SIGNAL.

TRACK ANALOG.OR.LOG

OUTPUT ANALOG.SIGNAL.

AUTOADJUST_10(

(* iiOutListData := * INT * *));

(* FREQ_2 ANALOG.SIGNAL. *)

iudiCntMain := REAL_TO_INT(ANALOG_SIGNAL),

iudiCntSens := REAL_TO_INT(ANALOG_SIGNAL),

iiInList := REAL_TO_INT(ANALOG_SIGNAL),

iiOutListFactr := REAL_TO_INT(ANALOG_SIGNAL),

(* LIST_3 ANALOG.SIGNAL. *)

);

ANALOG_SIGNAL :=

DINT_TO_REAL(AUTOADJUST_10.odiStatus1);

ANALOG_SIGNAL :=

DINT_TO_REAL(AUTOADJUST_10.odiStatus2);

ANALOG_SIGNAL :=

DINT_TO_REAL(AUTOADJUST_10.odiStatus3);

ANALOG_SIGNAL :=

DINT_TO_REAL(AUTOADJUST_10.odiStatus4);

AGA3_20

iarDiffPress := ANALOG_SIGNAL,

iarStatPress := ANALOG_SIGNAL,

iarAdjPress := ANALOG_SIGNAL,

iarOrifDiam:= ANALOG_SIGNAL,

iarPipeDiam := ANALOG_SIGNAL,

iarOrifCon:= ANALOG_SIGNAL,

iarBasePress := ANALOG_SIGNAL,

iarBaseTemp := ANALOG_SIGNAL,

iarFlowTemp := ANALOG_SIGNAL,

iarFPV := ANALOG_SIGNAL,

iiPoint := ANALOG_SIGNAL,

iarSpecGrav := ANALOG_SIGNAL,

iarbTrack := ANALOG_OR_LOG,

);

(* * DINT * := AGA3_20.odiStatus; *)

ANALOG_SIGNAL := AGA3_20.orOutput;

(

SECTION 2 – EVEN FOOTER

22

Page 27

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

30 * AGA3DENS

DIFF_PRESS ANALOG.SIGNAL

STAT_PRESS ANALOG.SIGNAL

FLOW_TEMP ANALOG.SIGNAL

TAP_LOC LOGICAL.SIGNAL

ORIF_DIAM ANALOG.SIGNAL

PIPE_DIAM ANALOG.SIGNAL

ORIF_COEF ANALOG.SIGNAL

PIPE_COEF ANALOG.SIGNAL

ORIF_RTEMP ANALOG.SIGNAL

PIPE_RTEMP ANALOG.SIGNAL

VISCOSITY ANALOG.SIGNAL

ISEN_COEF ANALOG.SIGNAL

FLOW_DENS ANALOG.SIGNAL

BASE_DENS ANALOG.SIGNAL

REL_DENS ANALOG.SIGNAL

TRACK LOGICAL.SIGNAL

MASS_FLOW ANALOG.SIGNAL

VOL_FLOW ANALOG.SIGNAL

BASE_FLOW ANALOG.SIGNAL

LIST ANALOG.SIGNAL

40 * AGA3ITER

DIFF_PRESS ANALOG.SIGNAL.

STAT_PRESS ANALOG.SIGNAL.

TAP_LOC ANALOG.SIGNAL.

ADJ_PRESS ANALOG.SIGNAL.

ORIF_DIAM ANALOG.SIGNAL.

PIPE_DIAM ANALOG.SIGNAL.

THERM_COEF1 ANALOG.SIGNAL.

THERM_COEF2 ANALOG.SIGNAL.

BASE_PRESS ANALOG.SIGNAL.

BASE_TEMP ANALOG.SIGNAL.

FLOW_TEMP ANALOG.SIGNAL.

VISCOSITY ANALOG.SIGNAL.

SPEC_GRAV ANALOG.SIGNAL.

ISEN_COEF ANALOG.SIGNAL.

Z_FLOWING ANALOG.SIGNAL.

Z_BASE ANALOG.SIGNAL.

POINT ANALOG.SIGNAL.

TRACK ANALOG.OR.LOG

OUTPUT ANALOG.SIGNAL.

LIST ANALOG.SIGNAL.

INPUT 1 ANALOG.SIGNAL.

AGA3DENS_30(

irDiffPress := ANALOG_SIGNAL,

irStatPress := ANALOG_SIGNAL,

iarFlowTemp := ANALOG_SIGNAL,

ibTapLoc := LOGICAL_SIGNAL,

irOrifDiam:= ANALOG_SIGNAL,

irPipeDiam := ANALOG_SIGNAL,

iarOrifCoef:= ANALOG_SIGNAL,

iarPipeCoef := ANALOG_SIGNAL,

iarOrifRefTemp:= ANALOG_SIGNAL,

iarPipeRefTemp := ANALOG_SIGNAL,

iarViscosity := ANALOG_SIGNAL,

irIsenCoef := ANALOG_SIGNAL,

irFlowDens := ANALOG_SIGNAL,

iarBaseDens := ANALOG_SIGNAL,

irRelDens := ANALOG_SIGNAL,

irCutOff := LOGICAL_SIGNAL,

iiList := REAL_TO_INT(ANALOG_SIGNAL));

ANALOG_SIGNAL := AGA3DENS_30.orMassFlow;

ANALOG_SIGNAL := AGA3DENS_30.orVolFlow;

ANALOG_SIGNAL := AGA3DENS_30.orBaseFlow;

AGA3I_40(

irDiffPress := ANALOG_SIGNAL,

iarStatPress := ANALOG_SIGNAL,

irTapLoc := ANALOG_SIGNAL,

iarAdjPress := ANALOG_SIGNAL,

irOrifDiam:= ANALOG_SIGNAL,

irPipeDiam := ANALOG_SIGNAL,

iarOrifTCoef := ANALOG_SIGNAL,

iarPipeTCoef := ANALOG_SIGNAL,

iarBasePress := ANALOG_SIGNAL,

iarBaseTemp := ANALOG_SIGNAL,

iarFlowTemp := ANALOG_SIGNAL,

iarViscosity := ANALOG_SIGNAL,

iarSpecGrav := ANALOG_SIGNAL,

iarIsenCoef := ANALOG_SIGNAL,

iarZFlow := ANALOG_SIGNAL,

iarZBase := ANALOG_SIGNAL,

iarPoint := REAL_TO_INT(ANALOG_SIGNAL),

iarbTrack := ANALOG_OR_LOG,

(* * DINT * := AGA3I_40.odiStatus; *)

iiOutList := REAL_TO_INT(ANALOG_SIGNAL),

iarInput1 := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := AGA3I_40.orOutput;

.

23

Page 28

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

50 * AGA3TERM

DIFF_PRESS ANALOG.SIGNAL.

STAT_PRESS ANALOG.SIGNAL.

ADJ_PRESS ANALOG.SIGNAL.

ORIF_DIAM ANALOG.SIGNAL.

PIPE_DIAM ANALOG.SIGNAL.

ORIF_CONST ANALOG.SIGNAL.

BASE_PRESS ANALOG.SIGNAL.

BASE_TEMP ANALOG.SIGNAL.

FLOW_TEMP ANALOG.SIGNAL.

FPV_IN ANALOG.SIGNAL.

POINT ANALOG.SIGNAL.

SPEC_GRAV ANALOG.SIGNAL.

TRACK ANALOG.OR.LOG

OUTPUT ANALOG.SIGNAL.

LIST ANALOG.SIGNAL.

INPUT 1 ANALOG.SIGNAL.

60 * AGA5

VOLUME ANALOG.SIGNAL.

BASE_PRESS ANALOG.SIGNAL.

BASE_TEMP ANALOG.SIGNAL.

FPV_IN ANALOG.SIGNAL.

SPEC_GRAV ANALOG.SIGNAL.

VOL_%_CO2 ANALOG.SIGNAL.

VOL_%_N2 ANALOG.SIGNAL.

VOL_%_O2 ANALOG.SIGNAL.

VOL_%_HE ANALOG.SIGNAL.

VOL_%_CO ANALOG.SIGNAL.

VOL_%_H2S ANALOG.SIGNAL.

VOL_%_H2O ANALOG.SIGNAL.

VOL_%_H2 ANALOG.SIGNAL.

VOL_CONVERS ANALOG.SIGNAL.

ENERGY_CONV ANALOG.SIGNAL.

OUTPUT ANALOG.SIGNAL.

AGA3TERM_50(

iarDiffPress := ANALOG_SIGNAL,

iarStatPress := ANALOG_SIGNAL,

iarAdjPress := ANALOG_SIGNAL,

iarOrifDiam:= ANALOG_SIGNAL,

iarPipeDiam := ANALOG_SIGNAL,

iarOrifCon:= ANALOG_SIGNAL,

iarBasePress := ANALOG_SIGNAL,

iarBaseTemp := ANALOG_SIGNAL,

iarFlowTemp := ANALOG_SIGNAL,

iarFPV := ANALOG_SIGNAL,

iiPoint := REAL_TO_INT(ANALOG_SIGNAL),

iarSpecGrav := ANALOG_SIGNAL,

iarbTrack := ANALOG_OR_LOG,

(* iarCPrime := * ANY * *)

(* iarFb := * ANY * *)

(* iarFr := * ANY * *)

(* iarY := * ANY * *)

(* iarFpb := * ANY * *)

(* iarFtb := * ANY * *)

(* iarFtf := * ANY * *)

(* iarFg := * ANY * *)

(* iarExt := * ANY * *)

(* * DINT * := AGA3TERM_50.odiStatus; *)

iiOutList := REAL_TO_INT(ANALOG_SIGNAL),

);

(* INPUT 1 ANALOG.SIGNAL. *)

ANALOG_SIGNAL := AGA3TERM_50.orOutput;

AGA5_60

iarVolume := ANALOG_SIGNAL,

iarBasePress := ANALOG_SIGNAL,

iarBaseTemp := ANALOG_SIGNAL,

iarFPV := ANALOG_SIGNAL,

iarSpecGrav := ANALOG_SIGNAL,

irCO2 := ANALOG_SIGNAL,

irN2 := ANALOG_SIGNAL,

irO2 := ANALOG_SIGNAL,

irHE := ANALOG_SIGNAL,

irCO := ANALOG_SIGNAL,

irH2S := ANALOG_SIGNAL,

irH2O := ANALOG_SIGNAL,

irH2 := ANALOG_SIGNAL,

iarVolConvers := ANALOG_SIGNAL,

iarEnergyConv := ANALOG_SIGNAL,

);

(* * DINT * := AGA5_60.odiStatus; *)

ANALOG_SIGNAL := AGA5_60.orOutput;

(

SECTION 2 – EVEN FOOTER

24

Page 29

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

70 * AGA7

FLOW_SWITCH LOGICAL.SIGNAL.

DENS_SWITCH LOGICAL.SIGNAL.

FLOW_TEMP ANALOG.SIGNAL.

FLOW_PRESS ANALOG.SIGNAL.

RATE ANALOG.SIGNAL.

BASE_TEMP ANALOG.SIGNAL.

BASE_PRESS ANALOG.SIGNAL.

FPV_IN ANALOG.SIGNAL.

ADJ_PRESS ANALOG.SIGNAL.

FLOW_DENS ANALOG.SIGNAL.

BASE_DENS ANALOG.SIGNAL.

SPEC_GRAV ANALOG.SIGNAL.

GRAV_TEMP ANALOG.SIGNAL.

GRAV_PRESS ANALOG.SIGNAL.

CALIB_FACTR ANALOG.SIGNAL.

SPAN ANALOG.SIGNAL.

OUTPUT ANALOG.SIGNAL.

80 * AGA8DETAIL

ENABLE LOGICAL.SIGNAL.

PRIORITY ANALOG.SIGNAL.

FLOW_TEMP ANALOG.SIGNAL.

STAT_PRESS ANALOG.SIGNAL.

BASE_TEMP ANALOG.SIGNAL.

BASE_PRESS ANALOG.SIGNAL.

LIST ANALOG.SIGNAL.

ARRAY ANALOG.SIGNAL.

COLUMN ANALOG.SIGNAL.

ERROR ANALOG.SIGNAL.

STATUS ANALOG.SIGNAL.

Z_FLOWING ANALOG.SIGNAL.

Z_BASE ANALOG.SIGNAL.

FPV ANALOG.SIGNAL.

90 *AGA8GROSS

ENABLE LOGICAL.SIGNAL.

PRIORITY ANALOG.SIGNAL.

FLOW_TEMP ANALOG.SIGNAL.

STAT_PRESS ANALOG.SIGNAL.

BASE_TEMP ANALOG.SIGNAL.

BASE_PRESS ANALOG.SIGNAL.

MODE ANALOG.SIGNAL.

HEAT_VALUE ANALOG.SIGNAL.

REF_T_HV ANALOG.SIGNAL.

REF_P_HV ANALOG.SIGNAL.

REL_DENS ANALOG.SIGNAL.

REF_T_RD ANALOG.SIGNAL.

REF_P_RD ANALOG.SIGNAL.

MOLE_%_N2 ANALOG.SIGNAL.

MOLE_%_CO2 ANALOG.SIGNAL.

MOLE_%_H2 ANALOG.SIGNAL.

MOLE_%_CO ANALOG.SIGNAL.

ERROR ANALOG.SIGNAL.

STATUS ANALOG.SIGNAL.

Z_FLOWING ANALOG.SIGNAL.

Z_BASE ANALOG.SIGNAL.

FPV ANALOG.SIGNAL.

AGA7_70(

ibFlowSwitch := LOGICAL7SIGNAL,

ibDensSwitch := LOGICAL_SIGNAL,

iarFlowTemp := ANALOG_SIGNAL,

iarFlowPress := ANALOG_SIGNAL,

iarRate := ANALOG_SIGNAL,

iarBaseTemp := ANALOG_SIGNAL,

iarBasePress := ANALOG_SIGNAL,

iarFPV := ANALOG_SIGNAL,

iarAdjPress := ANALOG_SIGNAL,

iarFlowDens := ANALOG_SIGNAL,

iarBaseDens := ANALOG_SIGNAL,

iarSpecGrav := ANALOG_SIGNAL,

iarGravTemp := ANALOG_SIGNAL,

iarGravPress := ANALOG_SIGNAL,

iarCalibFactr := ANALOG_SIGNAL,

iarSpan := ANALOG_SIGNAL,

);

(* * DINT * := AGA7_70.odiStatus; *)

ANALOG_SIGNAL := AGA7_70.orOutput;

AGA8DETAIL_80(

(* ENABLE LOGICAL.SIGNAL. *)

(* PRIORITY ANALOG.SIGNAL. *)

iarFlowTemp := ANALOG_SIGNAL,

iarStatPress := ANALOG_SIGNAL,

iarBaseTemp := ANALOG_SIGNAL,

iarBasePress := ANALOG_SIGNAL,

iiList := REAL_TO_INT(ANALOG_SIGNAL),

iarArray := ANALOG_SIGNAL,

iiRowSel := * INT * *)

iiRowSel := REAL_TO_INT(ANALOG_SIGNAL),

(* ERROR ANALOG.SIGNAL. *)

);

ANALOG_SIGNAL :=

DINT_TO_REAL(AGA8DETAIL_80.odiStatus);

ANALOG_SIGNAL := AGA8DETAIL_80.orZFlowing;

ANALOG_SIGNAL := AGA8DETAIL_80.orZBase;

ANALOG_SIGNAL := AGA8DETAIL_80.orFPV;

AGA8GROS_90(

(* ENABLE LOGICAL.SIGNAL. *)

(* PRIORITY ANALOG.SIGNAL. *)

iarFlowTemp := ANALOG_SIGNAL,

iarStatPress := ANALOG_SIGNAL,

iarBaseTemp := ANALOG_SIGNAL,

iarBasePress := ANALOG_SIGNAL,

iusMode := REAL_TO_USINT(ANALOG_SIGNAL),

iarHeatValue := ANALOG_SIGNAL,

iarRefTHV := ANALOG_SIGNAL,

iarRefPHV := ANALOG_SIGNAL,

iarRelDens := ANALOG_SIGNAL,

iarRefTRD := ANALOG_SIGNAL,

iarRefPRD := ANALOG_SIGNAL,

irMoleN2 := ANALOG_SIGNAL,

irMolCO2 := ANALOG_SIGNAL,

irMoleH2 := ANALOG_SIGNAL,

irMoleCO := ANALOG_SIGNAL,

(* ERROR ANALOG.SIGNAL. *)

);

ANALOG_SIGNAL :=

DINT_TO_REAL(AGA8GROS_90.odiStatus);

ANALOG_SIGNAL := AGA8GROS_90.orZFlowing;

ANALOG_SIGNAL := AGA8GROS_90.orZBase;

ANALOG_SIGNAL := AGA8GROS_90.orFPV;

25

Page 30

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

100 *ANOUT

DEVICE ;DEVICE_ID

INITIAL ;CHANNEL

OUTPUT 1 ;ANALOG_SIGNAL_OR_VALUE

ZERO 1 ;ANALOG_SIGNAL_OR_VALUE

SPAN \ 1 ;ANALOG_SIGNAL_OR_VALUE

TRACK 1 ;LOGICAL_SIGNAL

RESET 1 ;ANALOG_SIGNAL

110 * ARC_STORE

ARCHIVE ARCH.FILE.ID

MODE ARCH.MODE.

STATUS ARCH.STATUS.

PARAMETER 1 ARCH.PARAM.

120 * AUDIT

MODE AUDIT.MODE.

LIST AUDIT.LIST.

STATUS AUDIT.STATUS.

130 * AVERAGER

INPUT ANALOG.OR.LOG

RESET LOGICAL.SIGNAL.

TRACK LOGICAL.SIGNAL.

SPAN ANALOG.SIGNAL.

OUTPUT_1 ANALOG.SIGNAL.

OUTPUT_2 ANALOG.SIGNAL.

TIME ANALOG.SIGNAL.

_0_1_ZERO := ;ANALOG_SIGNAL_OR_VALUE;

_0_1_SPAN := ;ANALOG_SIGNAL_OR_VALUE;

ANOUT_100(

irInput :=(*;ANALOG_SIGNAL_OR_VALUE*)_0.0_1.0,

irZero := _0.0_1.0_ZERO,

irSpan :=

_0.0_1.0_SPAN(*;LOGICAL_SIGNAL*)(*;ANALOG_SIGNAL*));

:= ANOUT_100.orOutput;

:= ANOUT_100.obTrack;

:= ANOUT_100.orOutput;

ARCHIVE_110(

iiArchiveNumber := REAL_TO_INT(ARCH_FILE_ID ) ,

isiMode := REAL_TO_SINT(ARCH_MODE )(*

iiArchiveList := * INT * *)

(* iiOutList := * INT * *)

(* isiContractHour := * SINT * *)

(* irwFactor1 := * REAL * *)

(* irwFactor2 := * REAL * *)

(* idiSequenceIndex := * DINT * *)

);

(* * UINT * := ARCHIVE_110.ouiNumRecords; *)

(* * UINT * := ARCHIVE_110.ouiOldestRecord; *)

(* * UINT * := ARCHIVE_110.ouiNewestRecord; *)

(* PARAMETER 1 ARCH.PARAM. *)

ARCH_STATUS := DINT_TO_REAL(ARCHIVE_110.odiStatus);

AUDIT_120(

(* MODE AUDIT.MODE. *)

(* ibDisable := * BOOL8 * *)

iiAuditList := REAL_TO_INT(AUDIT_LIST )(*

ianyEventVar := * ANY * *));

(* * UINT * := AUDIT_120.ouiNumEvents; *)

(* * UINT * := AUDIT_120.ouiOldestEvent; *)

(* * UINT * := AUDIT_120.ouiNewestEvent; *)

(* * UINT * := AUDIT_120.ouiNumAlarms; *)

(* * UINT * := AUDIT_120.ouiOldestAlarm; *)

(* * UINT * := AUDIT_120.ouiNewestAlarm; *)

AUDIT_STATUS := DINT_TO_REAL(AUDIT_120.odiStatus);

AVERAGER_130(

IarInput := ANALOG_OR_LOG,

IbReset := LOGICAL_SIGNAL,

IbTrack := LOGICAL_SIGNAL,

IrSpan := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := AVERAGER_130.orOutput_1;

ANALOG_SIGNAL := AVERAGER_130.orOutput_2;

ANALOG_SIGNAL := AVERAGER_130.orTime;

SECTION 2 – EVEN FOOTER

26

Page 31

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

140 * CALCULATOR

calculator expression(s)

150 * COMMAND

COMMAND LOGICAL.SIGNAL.

OUTPUT LOGICAL.SIGNAL.

DELAY ANALOG.SIGNAL.

TRANSITION ANALOG.SIGNAL.

ON_LIM_SW LOGICAL.SIGNAL.

OFF_LIM_SW LOGICAL.SIGNAL.

STATUS LOGICAL.SIGNAL.

RUN_TIME ANALOG.SIGNAL.

RESET LOGICAL.SIGNAL.

160 * COMPARATOR

MODE LOGICAL.SIGNAL.

INPUT ANALOG.SIGNAL.

SETPOINT ANALOG.SIGNAL.

DEADBAND ANALOG.SIGNAL.

OUTPUT_1 ANALOG.OR.LOG

OUTPUT_2 ANALOG.OR.LOG

OUTPUT_3 ANALOG.OR.LOG

calculator expression(s)

TRANSLATION NOTES:

• Most calculator expressions are directly

translated without difficulty to IEC 611313 expressions in structured text.

Two ACCOL III functions have also been

•

added for calculation functions not

present in IEC 61131-3: R_INT for

truncating a REAL to an INT, and

R_RND for rounding a REAL to the

nearest INT.

COMMAND_150(

IbCommand := LOGICAL_SIGNAL,

IrDelay := ANALOG_SIGNAL,

IrTransition := ANALOG_SIGNAL,

IbOn_Lim_Sw := LOGICAL_SIGNAL,

IbOFF_Lim_Sw := LOGICAL_SIGNAL,

IbReset := LOGICAL_SIGNAL,

);

LOGICAL_SIGNAL := COMMAND_150.obOutput;

LOGICAL_SIGNAL := COMMAND_150.obStatus;

ANALOG_SIGNAL := COMMAND_150.orRun_time;

COMPARATOR_160(

IbMode := LOGICAL_SIGNAL,

IrInput := ANALOG_SIGNAL,

IrSetpoint := ANALOG_SIGNAL,

IrDeadband := ANALOG_SIGNAL,

);

ANALOG_OR_LOG := COMPARATOR_160.orOutput_1;

ANALOG_OR_LOG := COMPARATOR_160.orOutput_2;

ANALOG_OR_LOG := COMPARATOR_160.orOutput_3;

(* * BOOL * := COMPARATOR_160.obOutput_1;*)

(* * BOOL * := COMPARATOR_160.obOutput_2;*)

(* * BOOL * := COMPARATOR_160.obOutput_3;*)

170 * CUSTOM

MODE CUSTOM.MODE.

LIST CUSTOM.LIST.

STATUS CUSTOM.STATUS.

CUSTOM_170(

(* ioabInit := * ANY * *)

(* idiRepeat := * DINT * *)

iiMode := REAL_TO_INT(CUSTOM_MODE ),

iiCustomlist := REAL_TO_INT(CUSTOM_LIST )(*

iiComPort := * INT * *)

(* iiSlaveAddress := * INT * *)

(* idiTimeout := * DINT * *)

(* isIPAddress := * ANY * *));

(* * UDINT * := CUSTOM_170.oudDoneCount; *)

(* * BOOL8 * := CUSTOM_170.obDoneFlag; *)

CUSTOM_STATUS :=

DINT_TO_REAL(CUSTOM_170.odiStatus);

27

Page 32

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

180 * DACCUMULATOR

MODE ANALOG.SIGNAL.

SCALE ANALOG.SIGNAL.

INPUT_HIGH ANALOG.SIGNAL.

INPUT_LOW ANALOG.SIGNAL.

OUTPUT_HIGH ANALOG.SIGNAL.

OUTPUT_LOW ANALOG.SIGNAL.

190 * DEMUX

INPUT ANY.SIGNAL.

SELECT ANALOG.OR.LOG

OUTLIST ANALOG.SIGNAL.

200 * DIFFERENTIATOR

INPUT ANALOG.SIGNAL.

RESET LOGICAL.SIGNAL.

SPAN ANALOG.SIGNAL.

OUTPUT ANALOG.SIGNAL.

210 * ENCODE

SELECT ANALOG.SIGNAL.

LIST ANALOG.SIGNAL.

ARRAY ANALOG.SIGNAL.

TYPE LOGICAL.SIGNAL.

MODE LOGICAL.SIGNAL.

INDEX ANALOG.SIGNAL.

STATUS ANALOG.SIGNAL.

INPUT 1 ANY.SIGNAL.

DACCUMULATOR_180(

IoarMode := ANALOG_SIGNAL,

IarScale := ANALOG_SIGNAL,

IoarInput_High := ANALOG_SIGNAL,

IoarInput_Low := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := DACCUMULATOR_180.orOutput_High;

ANALOG_SIGNAL := DACCUMULATOR_180.orOutput_Low;

DEMUX_190(

ianyInput := ANY_SIGNAL ,

iiSelect := REAL_TO_INT(ANALOG_OR_LOG ),

iiOutlist := REAL_TO_INT(ANALOG_SIGNAL ));

(* * DINT * := DEMUX_190.odiStatus; *)

ANALOG_SIGNAL := DEMUX_190.orOutput;

DIFFERENTIATOR_200(

irInput := ANALOG_SIGNAL,

ibReset := LOGICAL_SIGNAL,

irSpan := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := DIFFERENTIATOR_200.orOutput;

ENCODE_210(

isSelect := REAL_TO_SINT(ANALOG_SIGNAL ),

iiList := REAL_TO_INT(ANALOG_SIGNAL ));

(* ARRAY ANALOG.SIGNAL. *)

(* TYPE LOGICAL.SIGNAL. *)

(* MODE LOGICAL.SIGNAL. *)

(* INDEX ANALOG.SIGNAL. *)

(* * REAL * := ENCODE_210.orOutput1; *),

irInput1 := ANALOG_SIGNAL );

ANALOG_SIGNAL := DINT_TO_REAL(ENCODE_210.odiStatus);

TRANSLATION NOTES:

220 * FOR startat, endat, increment,

action(s)

230 * ENDFOR

SECTION 2 – EVEN FOOTER

• Only functions 3, 4, 5, and 6 are

supported.

• Julian Date/Time Stamp output for

function 4 is sent to parameter Output1,

instead of Input 1.

In function 6, missing values in the list

•

will default to 0.

FOR iLOOP_30 := startat TO endat BY increment

DO

action(s)

END_FOR;

TRANSLATION NOTES:

• This is a KEYWORD, not a function block.

28

Page 33

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

240 * FPV

FLOW_TEMP ANALOG.SIGNAL.

STAT_PRESS ANALOG.SIGNAL.

SPEC_GRAV ANALOG.SIGNAL.

CO2_MOLE ANALOG.SIGNAL.

NMOLE ANALOG.SIGNAL.

OUTPUT ANALOG.SIGNAL.

250 * FUNCTION

ARRAY ANALOG.SIGNAL.

ROW ANALOG.SIGNAL.

COLUMN ANALOG.SIGNAL.

OUTPUT ANALOG.SIGNAL.

260 * HILOLIMITER

INPUT ANALOG.SIGNAL.

HIGH_LIMIT ANALOG.SIGNAL.

LOW_LIMIT ANALOG.SIGNAL.

OUTPUT_1 ANALOG.SIGNAL.

OUTPUT_2 LOGICAL.SIGNAL.

OUTPUT_3 LOGICAL.SIGNAL.

FPV_240(

iarFlowTemp := ANALOG_SIGNAL,

iarStatPress := ANALOG_SIGNAL,

iarSpecGrav := ANALOG_SIGNAL,

irCO2Mole := ANALOG_SIGNAL,

irNMole := ANALOG_SIGNAL,

);

(* * DINT * := FPV_240.odiStatus; *)

ANALOG_SIGNAL := FPV_240.orOutput;

FUNCTION_250(

iarFunctionArray := ANALOG_SIGNAL,

irRow := ANALOG_SIGNAL,

irColumn := ANALOG_SIGNAL,

);

(* * DINT * := FUNCTION_250.odiStatus; *)

ANALOG_SIGNAL := FUNCTION_250.orOutput;

HILOLIMITER_260(

irInput := ANALOG_SIGNAL,

iarHighLimit := ANALOG_SIGNAL,

iarLowLimit := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := HILOLIMITER_260.orOutput_1;

LOGICAL_SIGNAL := HILOLIMITER_260.obOutput_2;

LOGICAL_SIGNAL := HILOLIMITER_260.obOutput_3;

(* * BOOL * := HILOLIMITER_260.obError;*)

270 * HILOSELECT

OUTPUT_1 ANALOG.SIGNAL.

OUTPUT_2 ANALOG.SIGNAL.

SELECT_1 ANALOG.OR.LOG

SELECT_2 ANALOG.OR.LOG

INLIST ANALOG.SIGNAL.

INPUT 1 ANALOG.SIGNAL.

280 * HSCOUNT

DEVICE 2

INITIAL 1

COUNT 1 ANALOG.SIGNAL.

COUNT_ZERO 1 ANALOG.SIGNAL.

COUNT_SPAN 1 ANALOG.SIGNAL.

RESET 1 LOGICAL.SIGNAL.

FREQUENCY 1 ANALOG.SIGNAL.

FREQ_ZERO 1 ANALOG.SIGNAL.

FREQ_SPAN 1 ANALOG.SIGNAL.

HILOSELECT_270(

(* * DINT * := HILOSELECT_270.odiStatus; *)

iiInlist := REAL_TO_INT(ANALOG_SIGNAL),

(* INPUT 1 ANALOG.SIGNAL. *)

);

ANALOG_SIGNAL := HILOSELECT_270.orOutput_1;

ANALOG_SIGNAL := HILOSELECT_270.orOutput_2;

ANALOG := INT_TO_REAL(HILOSELECT_270.oiSelect_1);

ANALOG := INT_TO_REAL(HILOSELECT_270.oiSelect_2);

(* * REAL * := HILOSELECT_270.orStatus;*)

HSCOUNT_280(

(* DEVICE 2 *)

(* INITIAL 1 *)

irCountZero := ANALOG_SIGNAL,

irCountSpan := ANALOG_SIGNAL,

ibReset := LOGICAL_SIGNAL,

irFreqZero := ANALOG_SIGNAL,

irFreqSpan := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := HSCOUNT_280.orCount;

ANALOG_SIGNAL := HSCOUNT_280.orFrequency;

29

Page 34

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

290 * HWSTI

DEVICE ;DEVICE_ID

CHANNEL ;CHANNEL_ID

COMMAND ANALOG.SIGNAL.

DONE LOGICAL.SIGNAL.

STATUS ANALOG.SIGNAL.

PV ANALOG.SIGNAL.

STIEU ANALOG.SIGNAL.

SECVAR ANALOG.SIGNAL.

MISMATCH LOGICAL.SIGNAL.

CFGSTAT STRING.SIGNAL.

SENSRTYP ANALOG.SIGNAL.

DECONF ANALOG.SIGNAL.

DAMPING ANALOG.SIGNAL.

PVCHAR ANALOG.SIGNAL.

CJTACT LOGICAL.SIGNAL.

PIUOTDCF LOGICAL.SIGNAL.

STITAG STRING.SIGNAL.

FREQ6050 LOGICAL.SIGNAL.

URV ANALOG.SIGNAL.

LRV ANALOG.SIGNAL.

URL ANALOG.SIGNAL.

LRL ANALOG.SIGNAL.

SERIALNO STRING.SIGNAL.

STISWVER STRING.SIGNAL.

SCRATCHPAD STRING.SIGNAL.

XMITSTAT STRING.SIGNAL.

COMERRS ANALOG.SIGNAL.

POWERFAIL ANALOG.SIGNAL.

300 * IF (condition)

310 * executable statement(s) or module(s)

320 * ENDIF

HWSTI_290(

iiDevice := REAL_TO_INT(1.0),

iiChannel := REAL_TO_INT(1.0),

iiCommand := REAL_TO_INT(ANALOG_SIGNAL),

ioaiStiEngUnits := ANALOG_SIGNAL,

ioaiSensrTyp := ANALOG_SIGNAL,

ioaiDeconf := ANALOG_SIGNAL,

ioaiDamping := ANALOG_SIGNAL,

ioaiPVChar := ANALOG_SIGNAL,

ioabCJTAct := LOGICAL_SIGNAL,

ioabPIUOTDCF := LOGICAL_SIGNAL,

ioastrStiTag := STRING_SIGNAL,

ioabFreq6050:= LOGICAL_SIGNAL,

ioarURV:= ANALOG_SIGNAL,

ioarLRV:= ANALOG_SIGNAL,

ioarURL:= ANALOG_SIGNAL,

iaiPwrFail := ANALOG_SIGNAL);

LOGICAL_SIGNAL := HWSTI_290.obDoneFlag;

ANALOG_SIGNAL := HWSTI_290.ostrCfgStat;

ANALOG_SIGNAL := HWSTI_290.orPV;

ANALOG_SIGNAL := HWSTI_290.orSecVar;

LOGICAL_SIGNAL := HWSTI_290.obMismatch;

ANALOG_SIGNAL := HWSTI_290.orLRL;

STRING_SIGNAL := HWSTI_290.ostrSerialNo;

STRING_SIGNAL := HWSTI_290.ostrSTISWVer;

STRING_SIGNAL := HWSTI_290.ostrScratchPad;

STRING_SIGNAL := HWSTI_290.ostrXmitStat;

ANALOG_SIGNAL := HWSTI_290.ousCommErrs;

IF (condition) THEN

executable statement(s), function(s), or function

block(s)

END_IF;

TRANSLATION NOTES:

330 * IF (condition)

340 * executable statement(s) or module(s)

350 * ELSE

360 * executable statement(s) or module(s)

370 * ENDIF

SECTION 2 – EVEN FOOTER

This are KEYWORDs, not a function block

IF (condition) THEN

executable statement(s), function(s), or function

block(s)

ELSE

executable statement(s), function(s), or function

block(s)

END_IF;

TRANSLATION NOTES:

These are KEYWORDs, not a function block

30

Page 35

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

380 * IF (condition1)

390 * executable statement(s) or module(s)

400 * ELSEIF (condition2)

410 * executable statement(s) or module(s)

420 * ENDIF

430 * IF (condition1)

440 * executable statement(s) or module(s)

450 * ELSEIF (condition2)

460 * executable statement(s) or module(s)

470 * ELSE

480 * executable statement(s) or module(s)

490 * ENDIF

IF (condition1) THEN

executable statement(s), function(s), or function

block(s)

ELSEIF (condition2)

executable statement(s), function(s), or function

block(s)

END_IF;

TRANSLATION NOTES:

These are KEYWORDs, not a function block

IF (condition1) THEN

executable statement(s), function(s), or function

block(s)

ELSEIF (condition2)

executable statement(s), function(s), or function

block(s)

ELSE

Executable statement(s), function(s), or function

block(s)

END_IF;

TRANSLATION NOTES:

These are KEYWORDs, not a function block

500 * INTEGRATOR

INPUT ANALOG.SIGNAL.

RESET LOGICAL.SIGNAL.

ZERO ANALOG.SIGNAL.

SPAN ANALOG.SIGNAL.

OUTPUT ANALOG.SIGNAL.

510 * IP_CLIENT

REMOTE STRING.SIGNAL.

RESOLV_NAME ANALOG.SIGNAL.

SERVR_ID ANALOG.SIGNAL.

ACCESS_MODE ANALOG.SIGNAL.

RESP_TMO ANALOG.SIGNAL.

STRUCT_TYPE ANALOG.SIGNAL.

SERVR_STRUCT_NO ANALOG.SIGNAL.

SERVR_INDEX ANALOG.SIGNAL.

ACCESS_TYPE ANALOG.SIGNAL.

SERVR_SELECT ANALOG.SIGNAL.

CLNT_STRCT_NO ANALOG.SIGNAL.

CLNT_INDEX ANALOG.SIGNAL.

CLNT_SELECT ANALOG.SIGNAL.

CLNT_COUNT ANALOG.SIGNAL.

STATUS_1 ANALOG.OR.LOG

STATUS_2 ANALOG.SIGNAL.

INTEGRATOR_500(

irInput := ANALOG_SIGNAL,

ibReset := LOGICAL_SIGNAL,

irZero := ANALOG_SIGNAL,

irSpan := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := INTEGRATOR_500.orOutput;

CLIENT_510(

(* ioabInit := * ANY * *)

(* iiProtocol := * INT * *)

iaisRemoteNode := STRING_SIGNAL,

(* RESOLV_NAME ANALOG.SIGNAL. *)

iiServerID := REAL_TO_INT(ANALOG_SIGNAL),

iiAccessMode := REAL_TO_INT(ANALOG_SIGNAL),

idiTimeout := REAL_TO_DINT(ANALOG_SIGNAL),

iiStructType := REAL_TO_INT(ANALOG_SIGNAL),

iiServerStructNum := REAL_TO_INT(ANALOG_SIGNAL),

iiServerStructIndex := REAL_TO_INT(ANALOG_SIGNAL),

(* ACCESS_TYPE ANALOG.SIGNAL. *)

iiServerStructSelect := REAL_TO_INT(ANALOG_SIGNAL),

iiClientStructNum := REAL_TO_INT(ANALOG_SIGNAL),

iiClientStructIndex := REAL_TO_INT(ANALOG_SIGNAL),

iiClientStructSelect := REAL_TO_INT(ANALOG_SIGNAL),

idiCount := REAL_TO_DINT(ANALOG_SIGNAL),

);

(* * BOOL8 * := CLIENT_510.obDoneFlag; *)

(* * UDINT * := CLIENT_510.oudDoneCount; *)

(* STATUS_2 ANALOG.SIGNAL. *)

ANALOG _SIGNAL:= DINT_TO_REAL(CLIENT_510.odiStatus);

31

Page 36

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

520 * IP_SERVER

SERVR_ID ANALOG.SIGNAL.

LIST_DB ANALOG.SIGNAL.

AARRAY_DB ANALOG.SIGNAL.

LARRAY_DB ANALOG.SIGNAL.

ARCHIVE_DB ANALOG.SIGNAL.

KNOWN_IP_NODES ANALOG.SIGNAL.

RESOLV_NAME ANALOG.SIGNAL.

STATUS_1 ANALOG.OR.LOG

STATUS_2 ANALOG.SIGNAL.

SERVER_520(

(* ioabInit := * ANY * *)

(* iiProtocol := * INT * *)

iiServerID := REAL_TO_INT(ANALOG_SIGNAL),

iiListDB := REAL_TO_INT(ANALOG_SIGNAL),

iiRealArrayDB := REAL_TO_INT(ANALOG_SIGNAL),

iiBoolArrayDB := REAL_TO_INT(ANALOG_SIGNAL),

(* iiAuthorizedNodes := * INT * *)

(* iiStructType := * INT * *)

(* iiClientStructNum := * INT * *)

(* iiServerStructNum := * INT * *)

(* ARCHIVE_DB ANALOG.SIGNAL. *)

(* KNOWN_IP_NODES ANALOG.SIGNAL. *)

(* RESOLV_NAME ANALOG.SIGNAL. *)

);

(* * BOOL8 * := SERVER_520.obDoneFlag; *)

(* * UDINT * := SERVER_520.oudDoneCount; *)

(* STATUS_2 ANALOG.SIGNAL. *)

ANALOG_SIGNAL := DINT_TO_REAL(SERVER_520.odiStatus);

530 * ISO5167

DIFF_PRESS ANALOG.SIGNAL.

STAT_PRESS ANALOG.SIGNAL.

ADJ_PRESS ANALOG.SIGNAL.

ORIF_DIAM ANALOG.SIGNAL.

PIPE_DIAM ANALOG.SIGNAL.

THERM_COEF1 ANALOG.SIGNAL.

THERM_COEF2 ANALOG.SIGNAL.

DEVICE ANALOG.SIGNAL.

DEVICE2 ANALOG.SIGNAL.

FLOW_TEMP ANALOG.SIGNAL.

VISCOSITY ANALOG.SIGNAL.

ISEN_COEF ANALOG.SIGNAL.

DENSITY ANALOG.SIGNAL.

BASE_DENS ANALOG.SIGNAL.

STAT_P2 ANALOG.SIGNAL.

POINT ANALOG.SIGNAL.

TRACK ANALOG.OR.LOG

OUTPUT ANALOG.SIGNAL.

LIST ANALOG.SIGNAL.

ISO5167_530(

iarDiffPress := ANALOG_SIGNAL,

iarStatPress := ANALOG_SIGNAL,

iarAdjPress := ANALOG_SIGNAL,

iarOrifDiam:= ANALOG_SIGNAL,

iarPipeDiam := ANALOG_SIGNAL,

iarOrifCoef := ANALOG_SIGNAL,

iarPipeCoef := ANALOG_SIGNAL,

iiDevice := REAL_TO_INT(ANALOG_SIGNAL),

iiDevice2 := REAL_TO_INT(ANALOG_SIGNAL),

iarFlowTemp := ANALOG_SIGNAL,

iarViscosity := ANALOG_SIGNAL,

iarIsenCoef := ANALOG_SIGNAL,

iarFlowDens := ANALOG_SIGNAL,

iarBaseDens := ANALOG_SIGNAL,

irStat_P2 := ANALOG_SIGNAL,

iarScaleFact := REAL_TO_INT(ANALOG_SIGNAL),

iarbTrack := LOGICAL_SIGNAL,

(* * DINT * := ISO5167_530.odiStatus; *)

iiOutList := REAL_TO_INT(ANALOG_SIGNAL),

);

ANALOG_SIGNAL := ISO5167_530.orOutput;

SECTION 2 – EVEN FOOTER

32

Page 37

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

540 * LBBTI

DEVICE ;DEVICE_ID

CHANNEL ;CHANNEL

MODE ANALOG.SIGNAL

DGP ANALOG.SIGNAL

DGPU ANALOG.SIGNAL

DGPSUB ANALOG.SIGNAL

SP ANALOG.SIGNAL

SPU ANALOG.SIGNAL

SPSUB ANALOG.SIGNAL

RTDT ANALOG.SIGNAL

RTDTU LOGICAL.SIGNAL

RTDTSUB ANALOG.SIGNAL

EST ANALOG.SIGNAL

ESTU LOGICAL.SIGNAL

ESTSUB ANALOG.SIGNAL

TAG STRING.SIGNAL

OUTPUT ANALOG.SIGNAL

TRACK LOGICAL.SIGNAL

ALARM LOGICAL.SIGNAL

STATUS ANALOG.SIGNAL

CFGSTAT STRING.SIGNAL

ERRORCNT ANALOG_SIGNAL

550 * LEAD/LAG

INPUT ANALOG.SIGNAL.

DERIVATIVE ANALOG.SIGNAL.

INTEGRAL ANALOG.SIGNAL.

RESET LOGICAL.SIGNAL.

OUTPUT ANALOG.SIGNAL.

560 * MASTER

REMOTE ANALOG.SIGNAL.

POINT ANALOG.SIGNAL.

MODE ANALOG.SIGNAL.

INTYPE ANALOG.SIGNAL.

OUTTYPE ANALOG.SIGNAL.

INDEX ANALOG.SIGNAL.

INLIST ANALOG.SIGNAL.

OUTLIST ANALOG.SIGNAL.

STATUS_1 ANALOG.SIGNAL.

STATUS_2 ANALOG.SIGNAL.

570 * MUX

INLIST ANALOG.SIGNAL.

SELECT ANALOG.OR.LOG

OUTPUT ANY.SIGNAL.

LBTI_540(

iiDevice := REAL_TO_INT(1.0),

iiChannel := REAL_TO_INT(1.0),

ioaiMode := ANALOG_SIGNAL,

iorDGP := ANALOG_SIGNAL,

iarDGPUnits := ANALOG_SIGNAL,

iarDGPSUB := ANALOG_SIGNAL,

iorSP := ANALOG_SIGNAL,

iarSPUnits := ANALOG_SIGNAL,

iarSPSUB := ANALOG_SIGNAL,

iorRTDT := ANALOG_SIGNAL,

iarRTDTUnits := LOGICAL_SIGNAL,

iarRTDTSUB := ANALOG_SIGNAL,

iorEST := ANALOG_SIGNAL,

iarESTUnits := LOGICAL_SIGNAL,

iarESTSUB := ANALOG_SIGNAL,

iasTAG := STRING_SIGNAL,

(*;ANALOG_SIGNAL_OR_VALUE*),

iaiErrorCnt := ANALOG_SIGNAL);

LOGICAL_SIGNAL := LBTI_540.obTrack;

LOGICAL_SIGNAL := LBTI_540.obAlarm;

ANALOG_SIGNAL := LBTI_540.odiStatus;

STRING_SIGNAL_ := LBTI_540.ostrCfgStat;

LEAD_LAG_550(

irInput := ANALOG_SIGNAL,

irDerivative := ANALOG_SIGNAL,

irIntegral := ANALOG_SIGNAL,

ibReset := LOGICAL_SIGNAL,

);

ANALOG_SIGNAL := LEAD_LAG_550.orOutput;

MASTER_TO_CLIENT_560(

iaisRemoteNode := ANALOG_SIGNAL,

iiServerID := REAL_TO_INT(ANALOG_SIGNAL),

irAccessMode := ANALOG_SIGNAL(* INTYPE

ANALOG.SIGNAL. *)

(* OUTTYPE ANALOG.SIGNAL. *)

,

iiClientStructNum := REAL_TO_INT(ANALOG_SIGNAL),

iiServerStructNum := REAL_TO_INT(ANALOG_SIGNAL)(* *

BOOL8 * := MASTER_TO_CLIENT_560.obDoneFlag; *)

(* * UDINT * := MASTER_TO_CLIENT_560.oudDoneCount; *)

);

ANALOG_SIGNAL := MASTER_TO_CLIENT_560.orStatus;

MUX_570(

iiInlist := REAL_TO_INT(ANALOG_SIGNAL),

iiSelect := REAL_TO_INT(ANALOG_OR_LOG),

);

(* * DINT * := MUX_570.odiOutput; *)

(* * DINT * := MUX_570.odiStatus; *)

ANALOG_SIGNAL := MUX_570.orOutput;

TRANSLATION NOTES:

• Signals in a list may be of type REAL,

BOOL, or BYTE.

• The irSelect terminal must be UINT.

33

Page 38

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

580 * PDO

DEVICE 4

INITIAL 1

RESOLUTION 1

MODE 1 ANALOG.SIGNAL.

OUTPUT 1 ANALOG.SIGNAL.

ENABLE 1 LOGICAL.SIGNAL.

MIN_TIME 1 ANALOG.SIGNAL.

MAX_TIME 1 ANALOG.SIGNAL.

SPAN 1 ANALOG.SIGNAL.

INPUT 1 ANALOG.SIGNAL.

HIGH_LIMIT 1 LOGICAL.SIGNAL.

LOW_LIMIT 1 LOGICAL.SIGNAL.

TRACK 1 LOGICAL.SIGNAL.

RESET 1 ANALOG.SIGNAL.

PDO_580(

(* DEVICE 4 *)

(* INITIAL 1 *)

(* ioabRecalculate := * ANY * ,*)

iiResolution := REAL_TO_INT(1.0),

iiMode := REAL_TO_INT(ANALOG_SIGNAL),

iarOutput:= ANALOG_SIGNAL,

iabEnable := LOGICAL_SIGNAL,

irMin_time := ANALOG_SIGNAL,

irMax_time := ANALOG_SIGNAL,

iarInput := ANALOG_SIGNAL,

ibHigh_limit := LOGICAL_SIGNAL,

ibLow_limit := LOGICAL_SIGNAL,

);

LOGICAL_SIGNAL := PDO_580.obTrack;

ANALOG_SIGNAL := PDO_580.orReset;

(* * BOOL * := PDO_580.obRaise_output;*)

(* * BOOL * := PDO_580.obLower_output;*)

(* * REAL * := PDO_580.orStatus;*)

590 * PID3TERM

INPUT ANALOG.SIGNAL.

SETPOINT ANALOG.SIGNAL.

DEADBAND ANALOG.SIGNAL.

PROPORTION ANALOG.SIGNAL.

INTEGRAL ANALOG.SIGNAL.

DERIVATIVE ANALOG.SIGNAL.

RESET ANALOG.SIGNAL.

TRACK LOGICAL.SIGNAL.

OUTPUT ANALOG.SIGNAL.

ERROR ANALOG.SIGNAL.

600 * SCHEDULER

STROBE LOGICAL.SIGNAL.

STATE LOGICAL.SIGNAL.

RESET LOGICAL.SIGNAL.

MODE ANALOG.SIGNAL.

TRACK LOGICAL.SIGNAL.

UNAVAILABLE 1 LOGICAL.SIGNAL.

FAIL_STATE 1 LOGICAL.SIGNAL.

RANK 1 ANALOG.SIGNAL.

OUTPUT 1 LOGICAL.SIGNAL.

610 * SEQUENCER

STROBE LOGICAL.SIGNAL.

STATE ANALOG.SIGNAL.

INPUT 1 LOGICAL.SIGNAL.

OUTPUT 1 LOGICAL.SIGNAL.

PID3TERM_590(

irInput := ANALOG_SIGNAL,

irSetpoint := ANALOG_SIGNAL,

irDeadband := ANALOG_SIGNAL,

irProportion := ANALOG_SIGNAL,

irIntegral := ANALOG_SIGNAL,

irDerivative := ANALOG_SIGNAL,

irReset := ANALOG_SIGNAL,

ibTrack := LOGICAL_SIGNAL,

);

ANALOG_SIGNAL := PID3TERM_590.orOutput;

ANALOG_SIGNAL := PID3TERM_590.orError;

SCHEDULER_600(

ibStrobe := LOGICAL_SIGNAL,

ibState := LOGICAL_SIGNAL,

ibReset := LOGICAL_SIGNAL,

iiMode := REAL_TO_INT(ANALOG_SIGNAL)(* iaibDeviceInfo :=

* ANY * *)

);

(* * DINT * := SCHEDULER_600.odiStatus; *)

(* UNAVAILABLE 1 LOGICAL.SIGNAL. *)

(* FAIL_STATE 1 LOGICAL.SIGNAL. *)

(* RANK 1 ANALOG.SIGNAL. *)

1.0 LOGICAL_SIGNAL := SCHEDULER_600.obTrack;

ANALOG_SIGNAL := SCHEDULER_600.orOutput;

SEQUENCER_610(

ibStrobe := LOGICAL_SIGNAL,

(* STATE ANALOG.SIGNAL. *)

iiInputList := REAL_TO_INT(LOGICAL_SIGNAL),

iiOutputlist := REAL_TO_INT(LOGICAL_SIGNAL),

);

(* * INT * := SEQUENCER_610.oiStatus; *)

(* * DINT * := SEQUENCER_610.odiStatus; *)

SECTION 2 – EVEN FOOTER

34

Page 39

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

620 * STEPPER

STROBE LOGICAL.SIGNAL.

HOLD_OFF LOGICAL.SIGNAL.

DIRECTION LOGICAL.SIGNAL.

INDEX ANALOG.SIGNAL.

RESET LOGICAL.SIGNAL.

RESET_INDEX ANALOG.SIGNAL.

TRACK LOGICAL.SIGNAL.

TRACK_INDEX ANALOG.SIGNAL.

STEP ANALOG.SIGNAL.

ARRAY ANALOG.SIGNAL.

TIME ANALOG.SIGNAL.

OUTPUT 1 ANALOG.OR.LOG

630 * STORAGE

RESET LOGICAL.SIGNAL.

READ LOGICAL.SIGNAL.

WRITE LOGICAL.SIGNAL.

COLUMN LOGICAL.SIGNAL.

INDEX ANALOG.SIGNAL.

ARRAY ANALOG.SIGNAL.

TYPE LOGICAL.SIGNAL.

STATUS ANALOG.SIGNAL.

LIST ANALOG.SIGNAL.

INPUT 1 ANALOG.SIGNAL.

640 * TCHECK

INLIST ;ANALOG_SIGNAL_OR_VALUE

OUTLIST ;ANALOG_SIGNAL_OR_VALUE

STATUS ;ANALOG_SIGNAL

DGPSUB ;ANALOG_SIGNAL_OR_VALUE

SPSUB ;ANALOG_SIGNAL_OR_VALUE

RTDTSUB ;ANALOG_SIGNAL_OR_VALUE

ESTSUB ;ANALOG_SIGNAL_OR_VALUE

ERRORCNT ;ANALOG_SIGNAL_OR_VALUE

650 * TIMER

INPUT LOGICAL.SIGNAL.

SETPOINT ANALOG.SIGNAL.

RESET LOGICAL.SIGNAL.

TIME ANALOG.SIGNAL.

OUTPUT_1 LOGICAL.SIGNAL.

OUTPUT_2 LOGICAL.SIGNAL.

STEPPER_620(

ibStrobe := LOGICAL_SIGNAL,

ibHold_off := LOGICAL_SIGNAL,

ibDirection := LOGICAL_SIGNAL,

irIndex := ANALOG_SIGNAL,

ibReset := LOGICAL_SIGNAL,

irReset_index := ANALOG_SIGNAL,

(* iiOutputList := * INT * *)

irTrack_index := ANALOG_SIGNAL,

iarbDataArray := ANALOG_SIGNAL),

);

(* OUTPUT 1 ANALOG.OR.LOG *)

LOGICAL_SIGNAL := STEPPER_620.obTrack;

ANALOG_SIGNAL := STEPPER_620.orStep;

ANALOG_SIGNAL := STEPPER_620.orTime;

(* * REAL * := STEPPER_620.orStatus;*)

STORAGE_630(

ibReset := LOGICAL_SIGNAL,

ibRead := LOGICAL_SIGNAL,

ibWrite := LOGICAL_SIGNAL,

ibColumn := LOGICAL_SIGNAL,

iuiIndex := REAL_TO_UINT(ANALOG_SIGNAL),

iiArray := REAL_TO_INT(ANALOG_SIGNAL)(* TYPE

LOGICAL.SIGNAL. *)

,

iiList := REAL_TO_INT(ANALOG_SIGNAL));

ANALOG_SIGNAL :=

DINT_TO_REAL(STORAGE_630.OdiStatus);

TCHECK_640(

iiInlist := REAL_TO_INT((*;ANALOG_SIGNAL_OR_VALUE*)),

iiOutlist :=

REAL_TO_INT((*;ANALOG_SIGNAL_OR_VALUE*))(*;ANALO

G_SIGNAL*),

iarDGPSUB := (*;ANALOG_SIGNAL_OR_VALUE*),

iarSPSUB := (*;ANALOG_SIGNAL_OR_VALUE*),

iarRTDTSUB := (*;ANALOG_SIGNAL_OR_VALUE*),

iarESTSUB := (*;ANALOG_SIGNAL_OR_VALUE*),

iaiErrorCnt :=

REAL_TO_INT((*;ANALOG_SIGNAL_OR_VALUE*)));

:= DINT_TO_REAL(TCHECK_640.OdiStatus);

TIMER_650(

ibInput := LOGICAL_SIGNAL,

irSetpoint := ANALOG_SIGNAL,

ibReset := LOGICAL_SIGNAL);

ANALOG_SIGNAL := TIMER_650.orTime;

LOGICAL_SIGNAL := TIMER_650.obOutput_1;

LOGICAL_SIGNAL := TIMER_650.obOutput_2;

35

Page 40

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

660 * TOT/TRND

INPUT ANALOG.OR.LOG

START_HOUR ANALOG.SIGNAL.

START_MIN ANALOG.SIGNAL.

TIME ANALOG.SIGNAL.

HOUR_SPAN ANALOG.SIGNAL.

SHIFT_SPAN ANALOG.SIGNAL.

DAY_SPAN ANALOG.SIGNAL.

MONTH_SPAN ANALOG.SIGNAL.

PREV_HOUR ANALOG.SIGNAL.

PREV_SHIFT ANALOG.SIGNAL.

PREV_DAY ANALOG.SIGNAL.

PREV_MONTH ANALOG.SIGNAL.

CUR_T_HOUR ANALOG.SIGNAL.

CUR_T_SHIFT ANALOG.SIGNAL.

CUR_T_DAY ANALOG.SIGNAL.

CUR_T_MONTH ANALOG.SIGNAL.

DERIVATIVE ANALOG.SIGNAL.

670 * VLIMITER

INPUT ANALOG.SIGNAL.

TRACK LOGICAL.SIGNAL.

RATE_UP ANALOG.SIGNAL.

RATE_DOWN ANALOG.SIGNAL.

OUTPUT_1 ANALOG.SIGNAL.

OUTPUT_2 LOGICAL.SIGNAL.

680 * VMUX

TRACK LOGICAL.SIGNAL.

RATE ANALOG.SIGNAL.

OUTPUT ANALOG.SIGNAL.

SELECT ANALOG.SIGNAL.

INLIST ANALOG.SIGNAL.

INPUT 1 ANALOG.SIGNAL

TOT_TRND_660(

iarbInput := ANALOG_OR_LOG,

irStart_Hour := ANALOG_SIGNAL,

irStart_Min := ANALOG_SIGNAL,

iarTime := ANALOG_SIGNAL,

irHour_Span := ANALOG_SIGNAL,

irShift_Span := ANALOG_SIGNAL,

irDay_Span := ANALOG_SIGNAL,

irMonth_Span := ANALOG_SIGNAL,

(* irReset_Hour := * REAL * *)

(* irReset_Shift := * REAL * *)

(* irReset_Day := * REAL * *)

(* irReset_Month := * REAL * *)

);

ANALOG_SIGNAL := TOT_TRND_660.orPrev_Hour;

ANALOG_SIGNAL := TOT_TRND_660.orPrev_Shift;

ANALOG_SIGNAL := TOT_TRND_660.orPrev_Day;

ANALOG_SIGNAL := TOT_TRND_660.orPrev_Month;

ANALOG_SIGNAL := TOT_TRND_660.orCur_T_Hour;

ANALOG_SIGNAL := TOT_TRND_660.orCur_T_Shift;

ANALOG_SIGNAL := TOT_TRND_660.orCur_T_Day;

ANALOG_SIGNAL := TOT_TRND_660.orCur_T_Month;

ANALOG_SIGNAL := TOT_TRND_660 .orDerivative;

VLIMIT_670(

irInput := ANALOG_SIGNAL,

ibTrack := LOGICAL_SIGNAL,

irRateUp := ANALOG_SIGNAL,

irRateDown := ANALOG_SIGNAL,

);

ANALOG_SIGNAL := VLIMIT_670.orOutput1;

LOGICAL_SIGNAL := VLIMIT_670.obOutput2;

VMUX_680(

ibTrack := LOGICAL_SIGNAL,

irRate := ANALOG_SIGNAL,

iiSelect := REAL_TO_INT(ANALOG_SIGNAL),

irInlist := ANALOG_SIGNAL,

irInput := ANALOG_SIGNAL);

ANALOG_SIGNAL := VMUX_680.orOutput;

SECTION 2 – EVEN FOOTER

36

Page 41

Using the ACCOL Translator

ACCOL II Module / Statement ACCOL III Fuction Block / Keyword

690 * XMTR_INTERFACE

DEVICE ;ANALOG_SIGNAL_OR_VALUE

CHANNEL ;ANALOG_SIGNAL_OR_VALUE

REMOTE ;ANALOG_SIGNAL_OR_VALUE

MODE ;ANALOG_SIGNAL

FORMAT ;ANALOG_SIGNAL_OR_VALUE

ADDRESS ;ANALOG_SIGNAL_OR_VALUE

COUNT ;ANALOG_SIGNAL_OR_VALUE

LIST ;ANALOG_SIGNAL_OR_VALUE

INDEX ;ANALOG_SIGNAL_OR_VALUE

STATUS_1 ;ANALOG/LOGICAL_SIGNAL_OR_VALUE

STATUS_2 ;ANALOG_SIGNAL

XMTR_690(

iiDevice := REAL_TO_INT(1.0),

iiChannel := REAL_TO_INT(2.0),

iiChannel := REAL_TO_INT(ANALOG_SIGNAL_REM),

ioaiMode := ANALOG_SIGNAL_MODE,

iiFormat := REAL_TO_INT(ANALOG_SIGNAL_FRMT),

iuiAddress := REAL_TO_UINT(ANALOG_SIGNAL_ADDR),

iiCount := REAL_TO_INT(ANALOG_SIGNAL_CNT),

iiList := REAL_TO_INT(ANALOG_SIGNAL_LIST),

iiIndex := REAL_TO_INT(ANALOG_SIGNAL_INDX));

ANALOG_SIGNAL_STA1 :=