ADL}OO/ADAI2OO

Userts Manual

Real

IISSOO99000011 aanndd AASS99110000 CCeerrttiiffiieedd

Time

"Accessing

Devices,

the Analog

Inc.

World',,

ADLaOO/ADA12OO

Userts

Manual

ffi

REAL

State

TIME

820 North

Post

College, Pennsylvania

Phone: (8141234A087

FAX:

University Drive

Office Box

(81a)

DEVICES,

234-5218

INC.

906

16804

USA

Published

Real

Time Devices,Inc.

820 N.

University Dr.

P.O.

Box

State College,

by

906

PA 16804

USA

Copyright @ 1992

by Real Time

All rights

Printed

in

Devices,Inc.

reserved

U.S.A.

Rev.A 9234

Table

of

Contents

INTRODUCTION

Digital-to-Analog

What Comes

Applications

CHAPTER 1

Factory-Configured

P3 - Analog

-

P4

Analog

-

P5

DMA

P6 - DMA

-8254

P7

-

P8

Intemrpt

-

P9

DAC

-

P10

Pl I

Plz

Sl - Base

Pull-up/Pull-down

-

-

DAC

A/D

A/D

Conversion

With Your

Software

-

BOARD

Input

Input

Request

Acknowledge

Timer/Counrer

Source

I

Output Voltage Range

2

Output Volrage

Data

Converter

Address

Resistors

(ADA1200

Toolkit

and

SBTTINGS

Switch and Jumper

Voltage Range

Voltage Polarity

Channel

Channel

Clock Sources

and Channel

Word Bit

State Set

Status,/External

(Facory

on

(Facrory

(Factory

(Factory

Range

Setting:

Digital

I/O

(Factory

(Facory

(Facory

Only)...........

Settings

Setring: t0

(Facory

(Factory

Gate

300 hex

Seuing:

Setting:

Lines.....

Disabled).....

Sening: Disabled)

@acory

Setting:

Seuing:

Sening: +5

Setting: +/-)

2 Monitor

(268

Volrs)......

+/-)

..............

Serings:

Jumpers

-5

+5

to

o

.............

@actory

decimal)

CLKI-XTAL,

on OT2

volts)

-5

volts)............

Setting: EOC

.................

& G;

..........

CLK2-OT1,

Inremrpt

(A/D

Chs

Converter

..........................t-3

............i4

...............1-3

.......................

.....................14

pCK)

...................1-5

Disabled)

.....................

Status))

..............1_9

14

........... 14

......14

......... l-6

.........1_7

......1_g

l_g

....... l-9

.......1_10

i-l

CHAPTER 2

Connecting

Connecting

Connecting

Connecting

Running

CHAPTER

D/A

Converte

Di$tal I/O, Programmable

_

BOARD

Analog

the

Trigger

the

the Analog

Timer/Counters

the

the 1200DIAG

-

3

HARDWARE

INSTALLATION

Input Pins

In

Trigger

and

Outpurs

Diagnostics

Peripheral Interface

Out

(ADAI200

and Digital

Prrogram

DESCRIPTION

pins,

Cascading

Only)...........

...............

VO

...........

8oards.........

2-l

............24

..............24

..................2-s

..................2_5

...................2_s

.............3-1

.................3_5

CHAPTER 4 - BOARD

OPERATION AND

PROGRAMMING

BA +

0: Read

BA + l:

BA + 2:

BA + 4:

BA +

5: PPI

BA +

6: PPI Port

BA +

7:

BA +

8:

BA +

9:

BA+

l0:

BA+

11:

BA + 12:

BA

+ 13:

BA +

14:

BA +

15:

Clearing

Initializing

Enabling

Enabling

Conversion Modes/Triggering

Starting

Monitoring

Reading

Programming

Sntus/Srart

Read A/D Data/Update DAC

(Write

Reset

PPI Port A - Digital

Port

B

C

PPI

8255

SZl4TimerlCounrer0

8254 Timer/Countor I

8254Timer/Counr€r2(ReadAMrite)

S254ConrolWord(WriteOnly)...........

D/A

D/A

D/A

D/A

and Setting Bits

an A/D

the

Conrol Word

Converter 1 LSB: ADA1200

Converter 1 MSB: ADAI200

Converter

Converter

Disabling

and

Disabling

and

Conversion

Conversion

Converted Data

the Pacer

Convert

Only) ..........

-

Channel8oard

-

Digital

2 LSB: ADAI200

2 MSB: ADA12200

in

the

Intemrprs

Status

Clock

(Readl'\Mrire)

Outputs

(ReadAMrire)

VO

Functions

(Readflilrire)

VO

(Write

Only) ...........

(ReadAMrite)

(Read/lMri9

Extemal

............

Trigger

............

Done

@MA

..................

(Read/Write)

................

(Readflilrite)

Select

................

(Wrire

Only) ..........

(Wrire

Only) ...........

(Wrire

Only)

..........

(Write

Only) ...........

.....

or End-of-Convert)

.........44

...........44

...........44

...............4-5

..................4-5

................4-5

.......................4-5

...............4-7

...............4-7

.............4-7

.......4-7

......4-g

.........................4-g

......4-g

.......................4-g

....................4-12

......4-12

.....................4-12

..........,.....4-13

......................4-13

...4-13

...............4-14

8259 Programmable

Intemrpt

End-of-Interrupt

What

Using

Writing

Saving

Restoring

Common

Choosing

Allocating

Calculating

Setting

The

DMA

Programming

Programming

Mask Register

Exactly

Intemrpts in Your

Interrupt

an

the startup

the

Interrupt Mistakes

DMA

a

DMA Buffer

a

the

the DMA Page Register...................

DMA

Mask

Single

Intemrpt

(IMR)

(EOI)

Command

llappens When

Programs..........

Service

Intemrpt

Startup

Channel

Page

Register

DMA

the

the 1200 for DMA.....

Mask Register (IMR)

IMR

and Interrupt

and Offset

Controller

Controller

..........

Intemrpt

an

Routine (ISR)

of a Buffer

Occurs?

Vector

and

Intemrpt

vector

.................4-16

......................4-16

......4-16

.....................4-16

................4-16

.............4-17

..........4-tg

.....4-lg

...............4-19

..................4-19

...................4-19

............4-20

............4-2t

................4-Zz

.....4-23

.,4-23

Monitoring for DMA Done............

Common

D/A

Conversions

DMA Problems

(ADA1200

...............

Only)

.....4-23

....4-24

........4-2,4

Example Programs

Single Convert

DMA Flow Diagram

Interrupts Flow Diagram

D/A

Conversion

Flow Diagrams

and

Flow Diagram

(Figure

(Figure

Flow Diagram

4-5)..............

CHAPTER 5 _ CALIBRATION

APPENDIX A - 12OO

APPENDIX B - P2

APPENDIX

APPENDIX D

APPENDIX E

APPENDIX F

C - COMPONENT

_

_

-

SPECIFICATIONS

CONNECTOR PIN ASSIGNMENTS

CONFIGURING THE

CONFIGURING

WARRANTY

(Figure

44)

4-6)

.............

(Figure

4-7).

......

DATA

SHEETS

12OO FOR

THE 12OO

.............

....

SIGNAL

MATH

FOR ATLANTIS.........

......4-27

.....................4-29

..............4-30

........4-3I

..........4-32

A-l

.........8-1

D-1

.......E.T.

F-1

ul

iv

LIST

ILLUSTRATIONS

OF

l-l

t-2

t-3

T4

1-5

r-6

r-7

t-8

r-9

l-10

l-l I

t-12

l-13

l-t4

l-15

1-16

t-17

l-18

2-r

2-2

2-3

3-1

3-2

4-I

4-2

4-3

4-4

4-5

4-6

+-t

5-1

Board Layout

Analog Input

Analog Input

DMA Request

DMA

Acknowledge

&254Timer/Counter

8254 Timer/Counter

Intemrpt

Pulling Down

DAC

I

DAC 2

A/D Data

A/D

Converter

Base Address

Pull-up/Pull-down

Adding Pull-ups

Gain Circuiny

Diagram

n

Connector Pin Assignmens

UO

Analog Input

Cascading

ADI200/ADA1200

S2l4TimerlCounter

A/D

Conversion Timing

Pacer

Clock

8254Timer/Counter

Single Conversion Flow Diagram

DMA Flow Diagram

Interrupts Flow

D/A

Conversion Flow

Showing Factory-Configured

Voltage Range

Voltage Polarity

Channel Jumper, P5

Channel Jumper, P6................

Clock Source

Circuit Block Diagram

Channel Jumper,

Intemrpt Request

the

Voltage

Output

Output Voltage Range

Word Bit

for Removal

Two

Block

State Set Jumper, Pll

StatuslExternal

Switch, Sl ................

Resistor

Pull-downs

and

Formulas

and

Connections

Boards for

Block

Circuit

Diagram

Circuit Block Diagram

Diagram

Jumper, P3

Jumper, P4

P8

...............

Range

Jumper,

Jumper, P10

Gate

Circuitry....

for

Calculating

of Solder Short

............

Simultaneous

Diagram

Block

Diagram, All

.................

Diagram

(ADA1200

to

Settings...................

...............

................

Jumpers, P7................

.....................

Line

............

P9

................

..............

2 Monitor

Digital

...........

.............

Diagram

Modes....

Jumper, P12..............

Lines

VO

Gain

and f ............

Sampling

Only)...........

..................

...................14

................14

.....................14

..................1-5

................1-6

......................1-z

................1-8

................1-8

........... l-9

...........1-9

......................1-9

.............. l-l

.............1-12

..................1-13

........................24

.................2-6

.....................3-3

.....................4-12

...........4-15

.......................4-Zg

....................4-31

1-3

........1-5

........1-6

I

..... 1-14

.........2-3

........34

......4-25

.......4-32

INTRODUCTION

The ADl200

high-speed, high-performance

a

computer, each

.

16

single-ended analog input

.

l2-bit,5 microsecond

.

15, tl0,

.

Resistor

.

Three

.

.

.

'

.

.

.

The following

functions

board

conversion

DMA

transfer,

Trigger

16 TTL/CMOS

Three l6-bit

Two 12-bit

+5, +10,

Turtro Pascal,

setup

in

is included in

is

described in

ADA1200

and

1200

series

board features:

analog+o-digital

+10 volt

or 0 to

configurable

and trigger out for

timer/counters

digital-to-analog

+5,

0 to

Turbo

paragraphs

gain,

modes,

8255-based

or 0 to

C, and BASIC

Chapter

Chapter

Advanced

data

acquisition

channels,

input

range,

external

digital

(two

cascaded

output

+10

volt

analog output range

briefly

describe

3, Hardware

l, Board

Indusrial

converter

triggering or cascading

I/O

lines which

channels

source code; diagnostics

Operation,and

Settings.

Contol

and control

pacer

for

with

major

the

boards turn

system.

with 125 kl{z

can

be configured with

clock),

dedicated

(ADA1200

functions

Chapter 4 , Board

your

IBM

PC/XT/AT

Installed

boards,

grounds (ADA1200

program.

of the

within a

throughput,

pull-up

only),

A more

board.

Operation

single

pull-down

or

only),

detailed

and

or compatible into

expansion

Programming.Tlte

slot in

resisrors,

discussion

the

of board

Analog-to-Di

The

analog-to-digital

into

l2-bit

The

analog

unipolar range

provided

can

customize the

A,/D

are controlled

through

microprocessor

channel

memory.

through the

the

The

converted data

is

gital

digital data words which

input voltage

+ l0 volts.

of 0 to

inputs.

at the

input

conversions are

through software,

I/O

connector.

or by using

DMA

jumper

transfer

chosen by

In

the

processor.

Digital-to-Analog

The

digiral-to-analog

with individually

programmed

Data is

write

single

jumper-selectable

into

operation. Access

Conversion

(AlD)

circuitry

range

The

The high-perforrnance

gain.

performed

by an

can be Eansferred

direct memory

settings

mode,

Conversion

(D/A)

circuitry

D/A

the

converter

ttrrough

receives

can tien be

jumper-selectable

is

is

board

in

on

you

factory

A,/D

5 microseconds,

on-board

through

access

the board. The

make

can

(ADA1200

on the ADA1200

ranges

oulput

and a conversion

DMA is not

up to 16

read

converter

pacer

ttre

@MA).

continuous

single-ended

and/or transferred

for

bipolar

-5

set for

supports

and the maximum

clock,

or by an external

PC

data bus to PC memory in

The mode

PC

data bus is

Onty)

features

-5

of

+5

to

available.

volts,

is

analog

pc

to

ranges

of

+5 volts.

to

transfers

-10

automatically

Overvoltage

resistor

throughput rate

of transfer is

used to

directly o

independent

two

+10 volts,

to

inputs

and

converts

memory.

-5

+5 volts

to

configurable

trigger brought

software-selectable

read

and/or

PC

0 to +5 volts,

triggered for

or

protection

gain

is

125 kllz.

one

of two ways:

transfer

memory

l2-bit

analog

a

channel

onto the

-10

to

to

circuiry

data

wittrout

output

or 0

inpus

these

+10

volts,

or a

+35

volts

is

so that

Conversions

board

by using

and the DMA

pC

o

going

channels

+10 volts.

to

through

a

you

the

8254 Timer/Counter

An

timing and

clock. The

programmable

8254

counting

third is

functions.

available

interval

Two

for

counting

of the timerrcounters

timer

contains

applications,

three l6-bit,

are cascaded

or it can

i-3

8-MHz

be cascaded

timer/counters

and

can be used internally

to

the other

to

support

two

a wide range

for

timer/counters.

the

of

pacer

Digital

or

the on-board

resistors

VO

The

1200 has 16 TTL/CMOS-compatible

signals

to sense switch closures, trigger digital

included

are

programmable peripheral

8255

on the board.

digital I/O lines which

interface

Installation

events, or

procedures

activate

chip. Pads for installing

given

are

can be directly interfaced

solid-state

near

relays.

and activating

end

the

ofChapter l,Board

These lines

with external

provided

are

pull-up

pull-down

or

Settings.

devices

by

What

(814)

Board

hardware

for help

Application

SIGNAL*MATH

ATLANTIS

high level

NOTEBOOK/XE,

Programmer's

Hardware

Comes With

You

receive

.

ADl200

.

Software

.

User's

If

any item is missing

234-8087. If

the following items in

or

and diagnostics diskette

manual

Accessories

In

addition

in

Our

to

accessories.

choosing the

Software

custom application software

for real-time monitoring and

interfaces

Toolkit

Accessories

Your Board

ADAI200 interface

or damaged,

you

require

the items included in

Call

and Drivers

for integrated

between the 1200

LTICONTROL. rtdlinx

and

provides

service outside

your

items to

best

local

distributor

support

packages

dara acquisition

routines with

your

board

with

please

your

data

and

package:

1200

Turbo Pascal, Turbo

call Real Time Devices'

the U.S., contact

package,

1200

or our

your

board's application.

provide

and sophisticated

acquisition. rtdlinx

custom or third

source

documented source

and BASIC

C,

Customer

your

local disnibutor.

Real Time Devices

main

office for more information

excellent data acquisition

digital signal

rtdlinx/ablinx

and

party

software,

code

is

available

code

for

for

offers a

including

a one-time fee.

cuslom

source

code

Service Department

full line

about these

and analysis

processing

drivers

LABTECH

progrcmming.

of software

support.

and analysis,

provide

NOTEBOOK,

Our Pascal

at

and

accessories and

Use

or

full-featured

and C

Hardware

input

channel

boards,

prototype/terminal

XB50

boards

for simplified

assembly for

OP

series

accessories

your

on

extemal

1200

optoisolated digiual

testing and debugging

interfacing.

Using This Manual

This

manual is intended

enough

complex

can customize

When You

information

contact,

eastern

include

problem.

detail about the board and

applications.

the example software or

Need

This

manual and the example

properly

to

Technical

our

daylight time, or send a

your

company's

We

Help

Support

for

1200 include

the

16

to

differential

input

boards,

for

board

assume that

use all of the board's features.

name and address,

easy signal

you

help

to

Department,

FAX requesting

install your

its functions

you

write your

programs

already have

(814)

your

MX32

the

or

32 single-ended

the

access and

prototype

of

new

so

that

own

in

the software

234-8087,

assistance to

name,

analog input

input

channels,

T516

temperature sensor

prototype

circuitry, and

board and

you

can

an understanding

applications

package

you

If

during

your

telephone

development,

get

enjoy

programs.

have

any

regular

(814)

234-52L8.

maximum

included

problems

expansion

MR

board,

XP50

twisted

it

running

use of

of data

acquisition

with

installing

business hours,

When

number,

and

which

board

series

the

EX-XT

ttre

pair

quickly,

its

your

sending a

a brief description

can

mechanical

TB50

terminal

and EX-AT

wire flat ribbon

while

also

features

board

or

even

principles

provide

using ttris board,

eastern

FAX

expand a single

relay

output

board and

extender

cable

providing

in

most

the

and that

enough

sandard

request,

of the

you

time or

please

CHAPTER

1

The AD1200

settings

1200 is

factory

of this

easy-to-follow

computer.

the

associated

lines

near

C36,

circuiuy is

you

can change

factory-configured

settings are

chapter. Should you

Note

that by installing

PPI

8255

to be

the

Also

you

and

pads,

pulled

end of this

note

that

can add your

described

and

ADA1200

if

necessary

with

listed

and

instructions

resistor

soldering

you

can

up

or

chapter.

by

jumpers

configure

pulled

installing

own

at the

boards have

for

the most

shown

need

before

down. This

resistor

end

on

to

change these

you

packs

in

the

components

configurable

of this chapter.

jumper

your

application.

often

a diagram in

install

the

16

the board

at three locations

desired

available

procedure

RL,

at

and

used settings.

the

settings,

locations

digital

is

R2,

gain.

BOARD

switch

The

The

beginning

use

these

in your

around

in

the

VO

explained

TR4,

and

gain

The

SETTINGS

Fa

bo:

exl

avl

P3 - Analog

This header

jumper

the

15,110,

is installed

and 0 to

Input

Voltage

connector,

on

+10

volts.

(Factory

Range

shown in Figure

20V,

then

P4

can only be

Fig.1-2 - Analog

Setting:

1-2,

sets

10 Votts)

the analog input voltage

for

set

l-l

taol

t-l

cro

N

Input

bipolar

P3

Voltage

(+/-).

Range

range

for 10

The inpur ranges

Jumper, P3

or 20 volts.

allowed

by the 1200

Note

that if

are

P4 - Analog

This header

(+/-).

Note

that

allowed

P5 - DMA

DMA

disabled

DMA

by the 1200

This header

request

(umper

channel,

Input

connector,

if

the

are

Request

connector,

(DRQ),

line

in

a sored

channel

Voltage Polarity

shown in Figure

jumper

on P3 is installed

+10,

15,

Fig. 1-3

Channel

contention will result,

(Factory

shown in Figure

must

be set

position).

(Factory

and 0 to

-Analog

to the same

Note

Setting: +/-)

1-3,

sets the

on 20V,

+10

volts.

Input Voltage

Setting: Disabled)

14,

lets

that if

causing

analog

then P4

you

select

channel

any other

as

erratic

input voltage

can only

Polarity

channel 1 or 3 for DMA

DACK

the

device in

operation.

your

DRQl

polarity

for

be set

Jumper,

line

on

system is

DR03

for

bipolar

p4

P6.

The factory

already

unipolar

(+/).

The

transfers.

setting is

using

(+)

or bipolar

inpur

ranges

This line,

DMA

your

selected

the

Fig. 1-4

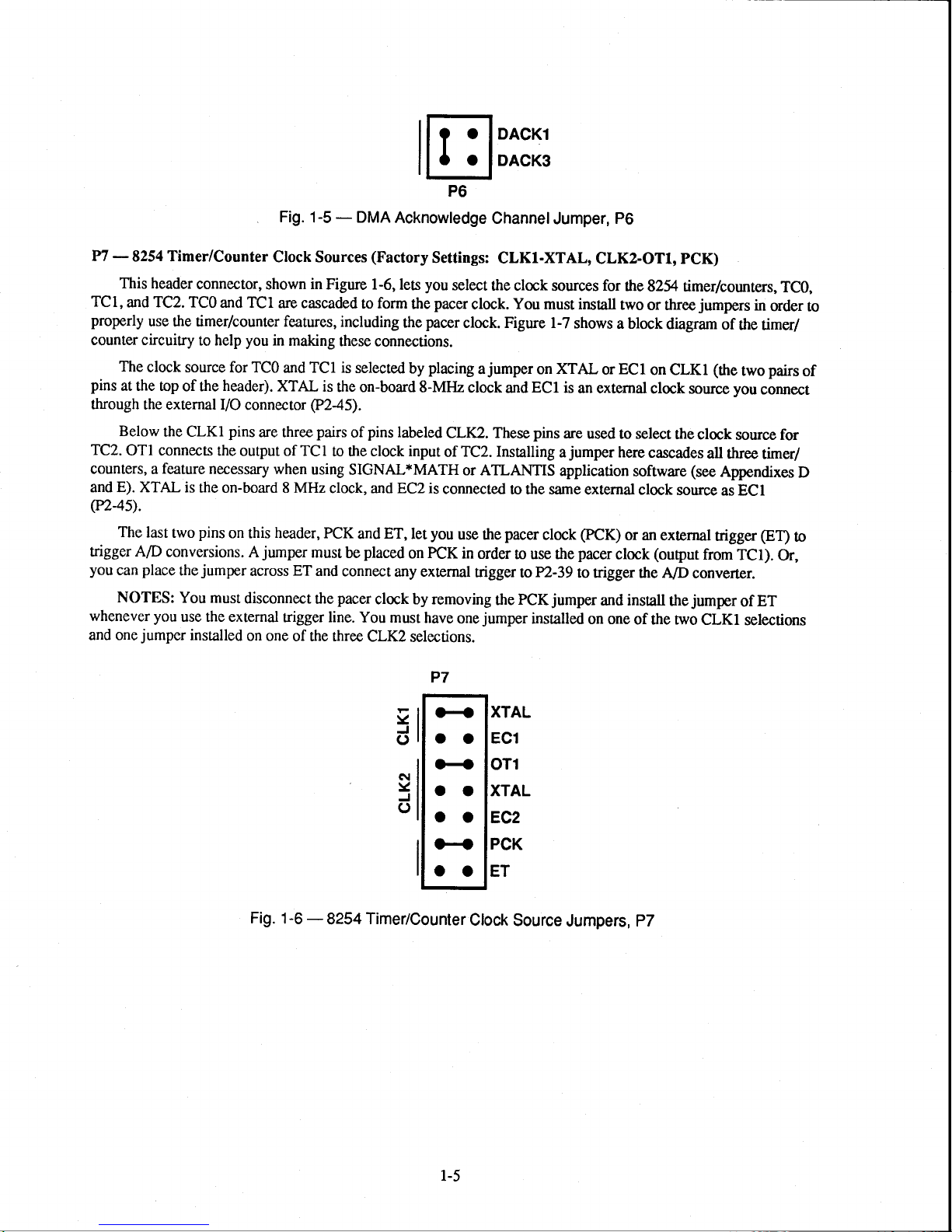

P6 - DMA

This

DMA

DMA

selected

Acknowledge

header

connector,

acknowledge

disabled

DMA

line

(umper

channel,

Channel

shown

(DACK),

in

a stored

channel

in

must

position).

contention will

-

DMA

(Factory

Figure

l-5, lets

be

set to the

Note

P5

Request

Setting:

you

same

that if

result,

causing

ChannelJumper,

Disabled)

select

channel

any

other

erratic

T4

channel I

or 3

as the DRQ

device in

operation.

for

line

your

p5

DMA

transfers.

p5.

on

system is

The

factory

already

This

setting

using

line,

your

the

is

DACKl

-8254

YI

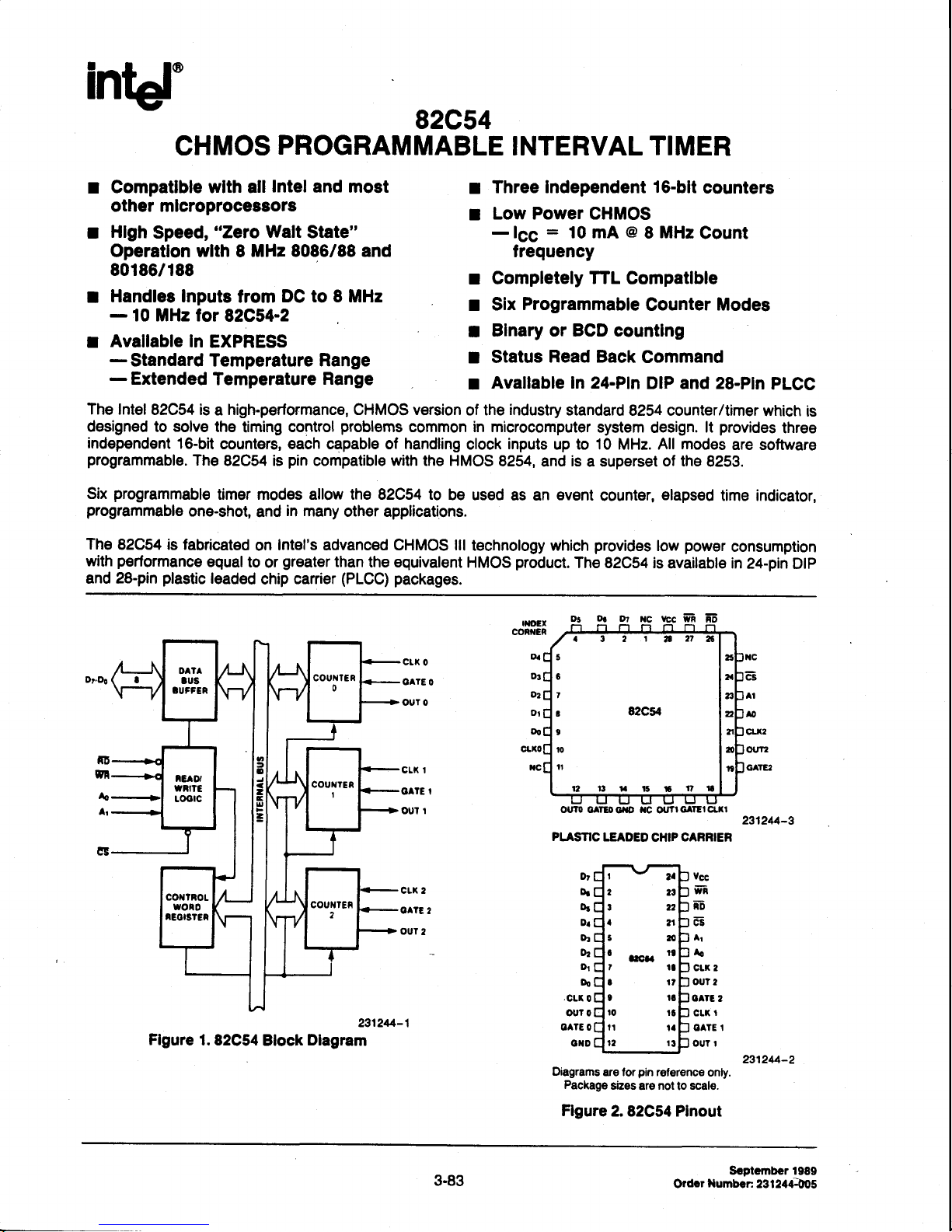

This

TCl,

properly

counter circuitry

The

pins

through

Below

TC2.

counters, a feature necessary

and E). XTAL

Timer/Counter

header

connector,

and TC2. TCO

use the timer/counter

clock source for TCO

at the top

the external I/O

the CLKI

OTI connects

and TCI

to help

header).

of the

pins

the output of TCI

is

the on-board 8 MHz

Clock Sources

shown

you

in

connector

are three

(n4r.

The

last

trigger AID

you

whenever you

and one

place

can

NOTES:

jumper

pins

two

conversions.

the

You

use the external

on this header, PCK

A

jumper

must

disconnect

installed

on one

jumper

across ET and

Fig.

1-5 - DMA

(Factory

in

Figure l-6,

are cascaded

features, including

making

TCI is

and

XTAL

e245).

when

using

must

the

trigger line.

of the three

to form

these connections.

selected

is

the on-board

pairs

pins

of

to the clock input

SIGNAL*MATH

clock, and EC2 is

and

placed

be

connect

pacer

clock by removing

You must

CLK2

tr

P6

Acknowledge

Settings:

you

lets

the

labeled

ET,

any external

select

pacer

the

by

8-MIIZ

let

on

selections.

clock.

pacer

clock. Figure l-7

placing

clock and

CLK2. These

TC2. Installing

of

or ATLANTIS

connected

you

use the

PCK

in order

have

one

DACK3

ChannelJumper, P6

CLKI-XTAL,

the clock

jumper

a

pacer

trigger toY2-39

the

jumper

sources

You

must install

shows

on XTAL

ECI

is

an external

pins

are

jumper

a

application

to the same

clock

to use the

PCK

installed

pacer

to trigger

jumper

used to select

external clock

(PCK)

on one

CLK2-OTI, PCK)

for

the

8254 timerlcounters,

diagram

the

(see

source

external

(output

A/D

converter.

jumper

the

jumpers

clock

all three

from

CLKI

two

or three

a block

ECI

or

and install

on CLK1

clock source

here

cascades

software

or an

clock

the

of the npo

TC0,

in

order to

of

the

timer/

(the

Appendixes

as ECI

trigger

pairs

two

you

connect

source for

timer/

(ET)

TCI).

Or,

ET

of

selections

of

D

to

Fig.

1-6

-8254

P7

Y

o

(\|

Y

o

IH

Timer/Counter

Clock

XTAL

EC1

oTl

XTAL

EC2

PCK

ET

Source

Jumpers,

p7

l-5

t-;;;------'l

8254

TO A/D

TRIGG

ER

1 200

I/O

CONNECTOR

P8 - Interrupt

This

header

interrupt

you

1-8b shows

channels,

must install

intenupt

TIMER/

COUNTER

2

Source

and

connector,

(highest

IRQ2

jumper

a

vertically

source

P8

CLK

GATE

Ar ri

Fig.

1-7

Channet

shown in

priority

OT2

connected

-8254

(Factory

Figure

channel)

across

Timer/Counter

Setting:

1-8, lets

you

through

the desired

IRQ

tro IRQ3.

XTAL

EC1

oTl

XTAL

EC2

F8

o-_8

Circuit Block

Jumpers

connect

IRQT

any one

(lowest

channel. Figure

on

P8

MHz

MHz

OT2 &

four

of

priority

1-8a

ptt{ ggl1pl66gp

PIN

Diagram

Interrupt

G;

intemrpt

channel).

shows

the

EXT CLK

EXT GATE

I

I

ozl

T/C

EXT

T/C

sources

To

facory

1

1x

OUT

I

GATE

2

OUT

2

Channels

to

any

activate

a channel,

setting;

Disabled)

of six

Figure

Fig.

Factory Setting

On

the

intemtpt

A/D

source

end-of-convert

1-8a:

right

side

of the header,

is

chosen

(EOC),

placing

by

DMA

or2

ET

EOC

DMA

IRQT

IRQ6

IRQ5

IRQ4

IRQ3

IRQ2

G

Fig.

you

done

1-8

can

jumper

a

(DMA),

Fig.

OT2

-

Interrupt

select

across

extemal

1-8b:

Interrupt

Connected

ChannelJumper,

any

one

of four

the

desired

rigger

l-6

Source

to lRe3

signal

pair

of.pins.

@T),

sources

and

rhe outpur

or2

ET

EOC

DMA

IRQT

IRQ6

IRQ5

lR04

IRQ3

IRQ2

G

pg

generate

to

The intemrpt

of timer/counter 2 (OT2).

an intemrpt.

sources

available

An

are

the

jumpered,

When

high-impedance

of a

intemrpt request

buffer is

bit 2 in

returns

circuit. Because

boards

board's

installed.

enabled,

the status word

IRQ

the

which

share the same

IRQ

status bit.

NOTE:

The

When

rest

line

the bottom

tri-state

low

line

forcing

(I/O

low,

disabling

intemrpt

the

you

use multiple

should be disconnected.

pair

of

driver which

whenever

the output high

address location

intemrpts

the

request

IRQ

channel. You

tri-state

line is

boards that

pins

on P8, labeled

carries

are not

generating

and

BA +

buffer,

driven low

can tell

share

Whenever

G, connects

the intemrpt

active.

0). After

and

the same interrupt,

you

request

Whenever

an intemrpL

the

pulling

only

by the

which

board issued

operate

a I kilohm

signal. This

intemrpt

an

You

can monitor

intemrpt

has

the ouput low

pull-down

only

a

single board,

pull-down

pull-down

request

been

serviced,

again. Figure

resistor, you

the intemlpt

one board

the

G

resistor

resistor

is

made,

the interupt

the reset

l-9 shows

can have

request

jumper

by

should

have

should be installed-

to the

output

drives

tle

the tri-state

strtus

through

command

this

two

or more

monitoring

jumper

the G

each

-

P9

DAC

This

+10

volts.

or

rightmost

or Xl.

When

possible

four

to be

set the

1

Output Voltage

header

connector,

jumpers

Two

jumpers

select the range,

jumper

a

combinations of

same

as

INT

SOURGE

Fig.

1-9

Range

shown in

must

be installed,

is on

the X2 multiplier pins,

jumper

Pl0.

-

(Factory

Figure

bipolar

settings,

Pulling

Setting:

l-10,

one

to select

(15)

or unipolar

and

Down

sets

the

the

Interrupt

the

-5

+5

to

the output voltage

the range

(5).

The

range

values

diagram

shows

g"

Request

volts)

range for

and one

twoleftmost

become

the factory

IRO STATUS

INTERRUPT

Line

DAC

to select

jumpers

+10

and 10. The

setting.

1

at 0 to +5,

the multiplier.

select

the multiplier,

table

below shows

This header

+5,

0 to

The

two

does not

+10,

X2

the

have

Voltage Range

-5

to

+5 volts

0 to

+5 volts

-1

0 to

+10 volts

0 to

+10 volts

x2

OFF

OFF

ON

ON

Jumpers (Left

x1

ON

ON

OFF

OFF

t-7

to Blght)

r5

ON

OFF

ON

OFF

5

OFF

ON

OFF

ON

P9

:II:

DACl

P10 - DAC

This header

+10

volts.

or

rightmost

or

four

to be set

jumpers

Xl.

When

possible

the same as P9.

2

Output Voltage

connector, shown

jumpers

Two

select

jumper

a

combinations of

must

the range,

is on the X2 multiplier

Voltage Range

and

-5

to +5 volts

to

0

-1

to

0

0 to +10 volts

Fig.

1-10

Range

in Figure

be installed,

brpolar

jumper

Polarity

+5 volts

volls

+10

-

DAC 1

(Factory

l-l

one

(15)

pins,

settings,

OFF

OFF

x2x1+5

Output Voltage

Setting:

l,

sets the

to select

or unipolar

the

and

the diagram

+5

output

the

(5).

range

Jumpers

x2

ON

ON

P10

OFF

OFF

-5

to

range

The

values

shows

x1

ON

ON

DAC2

5

Range

volts)

voltage

(Left

Jumper, P9

range for

and one to select

leftmost

two

become

+10

factory

the

to Right)

r5

ON

OFF

ON

OFF

DAC 2

jumpers

and

setting. This

at 0 to

multiplier.

the

select the multiplier,

10.

The table

5

OFF

ON

OFF

ON

+5,

The

below

header

+5,

0

+10,

to

two

X2

shows

the

does not have

-

Pll

AID

state

explains

A/D Data

This header

data

as the most,

word.

this

Word

connector,

This

significant

in more

Fig. 1-11

Bit State

header ensures

detail. NOTE:

Set P4

Set

in Figure

shown

bit of the

to

the same

Fig.1-12

-

DAC

2

Output Vottage

(Factory

that ttrese four

12-bit

Pll

and

polarityl

-AlD

Setting:

l-12,

A/D

converted

P4

must

Data

:II:

x2x1r5

+/-)

sets

the state

topmost

be set

Word

Bit

5

Range

of the

bits

are set at 0 for

data for

bipolar

the same for

+l-

Pl1

State

Set Jumper,

Jumper,

unused four

unipolar

conversions.

proper

pl0

bits in

the 8-bit

conversions and

Chapter

board

operation.

p11

MSB

4,

BA +

of ttre l6-bit

at

the same

1,

l-8

-

Plz

input

provides

conversion stafis,

of this status signal.

A/D

Converter

This

header

connector,

of timer/counter

a direct read

then

StatudExternal

shown

in Figure

2

to be

available for monitoring

of

t"1D

the

goes

converter's

high

when

Gate 2 Monitor

l-13, les

availability

the

conversion

(Factory

you

select either

at bit

3 of ttre

for

starting

is

completed.

Oor

o(,

ut uJ

Setting: EOC

the A,/D

status word

convenions.

Chapter

converter

(BA

This

provides

4

(A/D

+

0).

line

a

Converter

status

or

the

The

A/D

goes

low

more

detailed

Status))

external

converter

when

a

explanation

gate

status

-

Base

S1

One of

your

computer's

to use I/O

To

one of

32 starting

your

for

in Table

values.

When

you

DIP

Make

the switches

set

the

switch set for

Fig. 1-13

Address

the

address locations

avoid

system,

l-2.The

sure that

base address for

(Factory

most

common

I/O

space is

problem,

tttis

addresses

you

can select

table

are

a base address

-

already

already

the 1200 has

in

shows

ttre swirch

you

verify

pulled

forward,

your

A/D

Converter

Setting:

causes

used

the computer's

a different

the

board, record

of

300 hex

hex

300

failure

of

occupied

by another

an easily

base

settings

order

of the

they

are OPEN,

(768

Status/External

(768

decimat))

you

when

by internal

VO.

address

and

switch numbers

the

decimal).

are flust

I/O

device,

accessible

Should

value

contention results

five-position

the

simply

their

corresponding

or set

in

the

and

facory

by

logic

to

rable

Gate 2 Monitor

your

rying

other

sening

setting

on

ttre swirch

1,

inside

board is

peripherals.

and the

DIP

swirch,

of

300

the switches

decimal

as

and hexadecimal (in parentheses)

(l

through

labeled

ttre

on

back cover.

Jumper,

When

hex

the DIp

P12

address

the 1200

board

does not

51, which

(76g

decimal)

to

any one

5) before

swirch

Figure

contention.

board

work.

you

lets

of

l-14

select

be

unsuitabie

values

the

setting

package.

shows

Some

of

attempts

any

listed

*rem.

When

the

Fig. 1-14

-

Base

l-9

Address

Switch,

51

Base Address

sn

s28

su

s60

576

s92

608

6U

640

6s6

672

(Hex)

tQ00)

(2ro)

|

t(220)

tQ30)

(240)

|

tQs0)

tQ60)

tQ70)

(280)

|

(290)

|

t

QA0)

(2B0)

/

tQC0)

tQm)

t(2E0)

(2F0)

|

1=open

Decimal/

688

704

720

736

7s2

0=closed,

Table 1-2-

Swltch

54321

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

0ltll

Base Address

Setting

Decimal/

Swltch Settlngs,

Base Address

(Hex)

(300)

768

/

784

tQr0)

(320)

8oo

/

-816

(330)

/

(340)

832

|

(350)

848

/

(360)

864

/

(370)

880

/

(380)

896

/

en

tQn)

(3A0)

928

/

9M

t(380)

(3C0)

960

/

976

tQrn)

9e2

t(3E0)

(3F0)

1008

/

S1

Switch Settlng

5432'l

10000

10001

10010

10011

10100

10101

10110

10111

11000

ll00l

11010

ll0ll

11100

11101

11110

11111

Pull-up/Pull-down

The

interfaced

lines,

and

and

connect

up for

connection

lines

down for connection

lines

controlling

during

lines

to

motors

To

locations

Figure

After

the

three-hole

+5V)

on the other end.

C

Upper. Figure l-15

(middle

and

the G

no

resistors.

programmable

8255

with

external devices. These lines

four Port

the few moments

operate erratically.

not

will

use the

near

1- l5

shows a blowup

the

pin

of tlre three) and the V

pin.

C Upper

pull-up

pull-up/pull-down

the 8255, labeled PA, PCL,

resistor

pads

Figure l-16

pull-down

or

to switches.

them are

switch

on before the

packs

on ttre board

The

shows ttrese

Resistors

lines.

relays

to

high. The Port

before the board

By

of the

are installed,

middle hole is

shows

on

peripheral

(The

resistors

This

will

which

pulling

these lines

8255 is initialized.

feature, you

PA, PCL,

below the resistor

pads.

pin.

For

Port

A

Digital

inrerface provides

eight lines

pull

control urning motors

A line.s

is first initialized.

and PCH.

you

common. PA

To

lines with

VO Lines

are divided

Port

of

for

any or all

line

the

operate

pull-downs,

high

of the

down, when

must first

PA

PCH

and

must

connect

packs.

as

pull-ups,

pull-ups,

16 TTI/CMOS

into

B

of these three

when

8255 automatically

ins0all

akes a lGpin

resistor

They

is for Port

solder

compatible

groups:

three

are used

the switch

on

This

can cause the external

the data acquisition

10 kilohm resistor packs

pack

into

them

are labeled

A, PCL is for

solder

jumper

a

Port C lower

eight

for internal

groups

and off.

locations.

ttre circuit

a

of lines.

is

disconnected.

These

power

pack,

and

(for

G

jumper

wire

berween

with pull-downs,

wire

digiral

VO

Port A lines,

board functions.)

You may

motors

up as inputs,

system is first

PCL

and

pull-ups

as

ground)

Port

C

between

tlre common

four

you

Or,

turn on when

which

devices connected

in

any

or all of

PCH

pull-downs.

or

on one

Lower,

and

the

and

lines

which

port

C

You

can insall

want

hrned

take 6-pin

Port

pull

to

may

want

the digitat

can

on, the

the three

end and V

pCH

is for

common

pin

(middle

C Upper with

can

Lower

lines

to

float

high

to these

packs.

Locate

(for

port

pin

pin)

be

pull

l-10

i5ffieEiEggstr

S$FE;EEEHH

:E:

H

"lJ"f

oooo

oooooo

oor oo

oo*

oo

oooooo

oooo

Fig. 1-15

-

ffiL,L

gfrlgg

;ffi];E,f,sp

ffi:-*:WI

oooooo

oooooooo

oo

oo.

33

oooooooo

Pull-up/Pull-down

Resistor

*'

oooooo

oo

oo

33

Circuitry

8255

PORT

A

J

(PA0-7)

1

(

PoRT

c

(PAo.3)

C

r

1

[

T

LOWER

PORT

l'l^::;

1

(

Resistor

Thel200

i:l,Hr[[

The

resisror

located

in

your

capacitor

formula

::l#:ffled

the

formula

input

As

shown

in

at

for

Fig.

Configurable

has

resitor

H#:,T,fr:"

configurable

the

upper

tt'"*

in

Figure

signal

c36

in

setting

in

Figure

on

is

a

slowly

order

the

frequencv

the

bottom

1-17'

1'77

-

1-16

Gain

configurable

up

gain

-o'tiehi;;'#,i;

ca;;ilor

crranging

,oredu":

asolder

'

side

the

boaio

is

n""

is given

of

Adding

gain

derived

one

itp*

short

ne

puil-ups

b

c11om1ze.

ror

gain

a

by

cii

p-"lo"a

i.

;;;""

il;qu€ncy

in

ttre

must

boarJ

uno

putt_downs

and

gain

the

or

on.ifi-'ffi;r

adding

resislors

board:The;e;i;r^

,o

do

nor

range

oiagram.

be

Hg*

removed

errJ7r

sening

Rl

n"iv""

need

,;;;;*

and

in

i-rirn"*,

from

a'D;i;ic1. rig*

to

Digitat

for

a

,n"

ro

and-R2,

-o

Jrr

turn

trre

trimpot

trimpotiombin"

low-pass

"oo

it

at

reduce

lJ;;;;l#itry

board

to

t/O

-lpecific

input

.r,i,inrri

TR4,

filrering

a.higher

ttre

noise

activate

l-18

shows

Lines

apprication.

and

to

B@, you

on'your

the gain

rie

Note

w'r

operate

capacibr

,"t

rhe

in

the

may

input

is

circuiry.

rocation

that

when

onry

c36,

gain,

gain

wanr

configured.

all

as

shown

circuit.

to

signar.

This

or

*re

add

The

at

If

a

ol

lo

OI IO

Remove Solder Short

Between These 2 Pads

Bottom Slde of

Board

on

'{:1"

El

lFl ^

oHo

lf l

-.olJ:id6615-ooo#gj

ooooooooooo

iooooooooooq*

oooo

oooooo

OOr

oo.B

oooooo

oooo

*r*(f,

OO

oo

Fig.

1-18 - Diagram

HEtr;EiEiESEi

@

k&,ffF'EP

oooooo

oooooooo

oo oo

oor oo

*.

33

oooooooo

lor Rernovalof

33

oooooo

Solder Short

CHAPTER

2

The 12ffi

ible

computer. It

chapter

After you

nections, you

board

diagnostics

verify

to

tells

that

you

is

easy to install

can

step-by-step how

have

can

your

placed

be

installed

your

turn

program

board is

in your

in

any

to install

the board

system

included

working.

on and run

IBM

PC/XT/AT

slot,

short or

and connect

and made

your

on

BOARD

full-size.

all

of

1200DIAG

the

example

INSTALLATION

or

compat-

This

the

board.

your

con-

software

disk

Board Installation

Keep

the board

hold

bag,

the board at the edges and do

Before installing

factory

settings and

Chapter l. Note that

To install

1. Turn

2. Remove

how

to do

in its

the board

how

incompatible

the board:

OFF the

power

the top cover of the computer housing

this).

3. Select any unused short or

4. Touch

the

metal

antistatic bag.

Holding

5.

the board

connector in the

After

6.

computer's

carefully

positioning

bus connector,

NOTE: Do not force

Wiggling

7. After

The

the board

the board is installed,

board is now ready

antistatic bag until

your

in

change

to

them.

jumper

your

to

computer.

you

are

not

touch the

computer,

you

If

need

settings can

ready

components or connectors.

check the

to

change any settings,

result

(refer

housing

its

by

full-size

of the computer to discharge

edges, orient

expansion

it

so that its

slot and remove

bottom of the selected expansion

the board

gently

the board

exerting

or

secure the slot

to be connected

in

and evenly

into

the

much

too

the expansion

press

If

slot.

the board

pressure

bracket

via

the external

install

to

jumper

in

unpredictable board operation and

your

m

your

in

il

computer.

and swirch settings. Chapter 1 reviews

owner's

slot bracket.

the

refer to

the appropriate insEuctions

manual

any static buildup and then

card edge

connector lines

@us)

slot.

slot, so that the card edge

down

on the board until

does

can resultln

place

inlo

back

connector at the rear

VO

not

slide

damage to the board or to

and

into

put

the cover

it is

place,

When removing

erratic

you

if

not

do

remove

up with

already know

ttre board from

the expansion

connector is resting

secured in

remove

ttre slot.

it

and try again.

the computer.

of

your

your

computer.

back on

panel

it from

the

the

in

response.

its

slot

on

the

computer.

External

Figure 2-l

VO

Connections

shows the 1200's P2UO

connector

AOUTT

AOUT2

Ail

LOG GI{O

TRIGGER IN

EXT GATE

TRIGGEB OUT

EXT CLK

+12

VOLTS

.r2

volTs

pinout.

AINI

AIN2

AIN3

AIN'

atil5

atil6

AINT

AIN8

PA7

PA5

PA5

PA'

PA3

PA2

PAI

PAO

1

Refer

to this diagram as

AIN9

AINlO

AINIl

AINl2

AINI3

AINl'

AINIs

AINl6

AIIALOG GND

ANALOG OND

ANALOO GND

PC7

PC6

PC5

POI

PC3

PC2

PCt

PC0

OIGITAL GND

T/C OUT r

T/C

OUT 2

EXT GATE 2

+5

VOLTS

DIOITAL

OND

you

make

your

I/O

connections.

Fig.2-1 - PZ

VO

Connector Pin

2-3

Assignments

Connecting

the Analog Input Pins

Connect the high

connect

the

side

low

made.

NOTE: It is

good

Failure to do so may

SIGNAL

souRcE

1

SIGNAL

jouRcE

1 5

side of the

o an

practice

analog

ANALOG

to connect

GND

affect the accuracy

7

'

|

our(

Inno

I

a

a

ourJ

I

'

[

(GNc

a

a

a

input

to

(pins

all unused

your

of

I 200

I'O

CONNECTOR

P2

I

I

PIN,I

one of

the analog input

18

and 2A-22

channels to

results.

channels, AINI

onP2). Figure 2-2

ground,

as shown in

AIN

I

a

.

a

AtN t5

ilux

OUT

OUT

+

.

through

shows how

following

the

+

AIN16,

rhese

connections

diagrams.

and

are

Connecting the

1200

The

Trigger

board

has

based on external events,

configuration. By

conversion

to set each board for

NOTE: When

tainty is

too

configuration,

sampling

(see

uncertainty is reduced

you

If

Chapter

cascading

at the same

a different

cascading

geat

for

your

the boards

apply

an external

1). The

board is

time

nanoseconds.

In

and Trigger

an external

or

so that two

(or

two

(sampling

base

boards, the

application,

not

are

cascaded,

to less

trigger

triggered on

PIN

16

PIN

22

Fig.2-2

trigger input

more)

uncertainty

address

you

-

Pins,

Out

more

or

boards

(see

sampling

can connect

rather

but

Analog

Cascading

(P2-39)

boards

as shown

is

less

Chapter l),

uncertainty

driven

than 5 nanoseconds.

to the

board's

the

nigger in

positive

Input

and

output

can

be cascaded

in Figure

ttran

or system

the trigger

by the same

pin,

edge

of the

AIN I5

Connections

Boards

(Y243)

and run

2-3,

they

nanoseconds).

50

contention

is

less

than

signal to

trigger

note

that

a

pulse

and

so

that conversions

synchronously

can

be triggered

you

When

will result.

nanoseconds.

50

the rigger input

pulse

at the same

jumper

the

should

pulse

duration

can

in

to

cascade

If

this

of each

instaued

be

should

be started

"master/slave"

a

start an A/D

boards,

level

time,

be sure

of

uncer-

board. In

and

the

on ET

this

on

be at least

p7

100

24

BOARD T1

(MASTER)

BOARO T2

(SLAVE)

Connecting

For

each of the two D/A

orP2-19)

F2-17

Connecting

For

all

of these connections,

appropriate

signal

2-3

-

the Analog

Fig.

Outputs

outputs,

and connect

the

the Timer/Counters

the

pin

on the P2 I/O

Cascading Two

(ADA1200

connect

low

side of the

and Digital

high

connector

Only)

the high

UO

side

of an

and the low

Boards

side

device

external

to

of the

an

side

TRIGGER

TRIGGER

OUT

IN

for

Simultaneous

device

ANALOG

signal

source or

is

connected to

receiving

(P2-tS

GND

destination

any

Sampling

the

output

orp2-20).

device is

DIGITAL

to the AOUT

connected

GND.

channel

to

the

Running

Now

that

program,

also use

1200DIAG,

this

the I200DIAG

your

board is ready

is included

program

to make

Diagnostics

you

to

use,

your

with

sure

that

your

example

curent

Program

will want

software

base

to try it

out. An

help

to

address setting

2-5

easy-to-use,

you

verify

does not

menu-driven

your

board's

contend

operation.

with

another

diagnostics

you

device.

can

CHAPTER

3

This

major

digital

intemrpts.

able

chapter

circuits

lines. This

VO

describes

are the A/D,

chapter

the features

the D/A,

also

the timer/counters,

describes the hardware-select-

HARDWARE

of the 1200 hardware.

The

and the

DESCRIPTION

The 1200

I/O lines. Figure

major circuits

board

and

has four major

3-1 shows the

hardware-selectable

circuits,

block diagtam

the

of ttre board. This

intemrpts.

A/D,

the

(ADA1200

D/A

chapter describes the hardware

only),

the timer/counters,

and

which

rhe digitat

makes

up the

A/D

Conversion

The1200

channels. The following

Analog Inputs

The

configurable

circiutry is

A/D

Converter

The

microseconds,

5

and-hold

A/D

conversion function

design

Conversions are initiated

board

through

modes

performs

input

gain

described in

AD678

amplifier, a 72-bit

give you

are described in

Circuitry

voltage

lets

12-bit

for

a maximum

accurate results.

I/O

the

conneclor. An

Fig.

3-1 - AD1200/ADA1

analog-to-digital

paragraphs

range is

you

amplify lower level

Chapter 1.

successive

A/D

on a single

Chapter 4, Board

describe

jumper-selectable

Overvoltage

approximation A/D

throughput rate

converter,

chip. Irs low-power

through

software

on-board

conversions

ttre A/D

a 5-volt reference,

Operation

on up to 16

circuitry.

-5

for

signals

(internally

pacer

to

protection

convert€r

200

of

clock

and

to

more

kHz

CMOS logic

Programming.

200

single-ended

+5 volts,

closely match

+35

to

volts

accurately

for

the

a clock,

riggered)

can be

used to control

Block Diagram

software-selectable

-10

+10 volts,

to

provided

is

digitizes

converter alone. The

and a

digitat

combined

or by using

or 0 to +10 volts.

the board's input

at the inputs.

dynamic

interface

with a high-precision,

an extemal

the conversion

ranges.

input voltages

AD678

contains

provide

to

trigger

rate.

analog input

Resistor

gain

This

in

a

sample-

a complete

low-noise

brought

onto

Conversion

the

3-3

Data

Transfer

The

converted

microprocessor

They

da0a

managed

The maximum

polling

use

directly

by

into

the

throughput

data

can be tansfened through

or

by using

and intemtpts

the PC's

DMA

memory,

controller as a background

rate

memory

direct

determine

to

the 1200 is 125

of

access

one byte

the PC

(DMA).

when

data has

at a time,

function

kHz.

data bus

Data

to

bus

transfers

been acquired

with minimal

of

PC, letting

the

PC

memory in

take

and is ready for

processor

use of

you

one of

processor

more

time. DMA

operate at

two ways:

transfer.

higher

by using

time to

e*ecute.

places

DMA

transfers

are

throughput

the

rates.

D/A

Converters

Two

independent

ated by two l2-bit

volts.

The

110 volt

2.44 millivolts,

D/A

range has

and

Timer/Counters

An8254

timing

pacer

the

counting

circuiry.

Each

programmed

Chapter

Mode

Mode

Mode

Mode

programmable

and

counting functions.

clock. The

applications,

timer/counter

as binary

4.

The

command

0 Event

I

Hardware-Retriggerable

2

Rate

3

Square Wave

!-trui------l

(ADA1200

l2-bitanalog

Only)

output

channels

converters with independent

resolution

a

of

4.88

the 0 to +5 volt range has

interval

Two of

pacer

is described

clock

or cascade it to TCO

has

two inputs,

BCD

or

down counten

word

also

Counter

(Intemrpt

provides

timer

the timer/counters,

in

and TCI

in

CLK

you

lets

set

on Terminal

One-Shot

Generator

Mode

TRIGGER

TITER/

COUI{TER

CLK

0

GATE

OUT

are included

jumper-selectable

millivolts,

a resolution

of 1.22

three 16-bit,

TCO

Chapter

and

by writing

4. You

for

timing

GATE

the

up the mode

Count)

TO

A/D

XTAL

EC1

on the ADAI200. The

output ranges

+5

the

and 0 to

millivolts.

MHz

8

and TCl,

can use

timer/counters

are cascaded

the

applications.

in,

and

one output,

appropriate

of operation.

F-

datato

The

8 MHz

of

+10

volt ranges

remaining

Figure

3-2 shows

timer/counter

the command

programmable

six

1200

I/O CONNECTOR

?2

I

I

I

analog

outputs

+5,

+10,

0 to +5,

have

resolution

a

to support

so that

timer/counter,

a wide range

they

can

TC2,

the timer/counter

OUT.

They

word,

modes

EXT CLK

gener-

are

orb to +10

be

used for

for

can be

as

described

are:

of

of

in

L----__-__.;

Fig.

3-2 - 8254 Timer/Gounter

CLK

2

Circuit

Block

Diagram

prr{

gglrnrecen

rt*

o11116

EXT GATE

er1l

1

rN

.,

Mode 4

Mode

These modes

Software-Triggered

5 Hardware Triggered

are

detailed

in

*re

Strobe

Strobe

8254

(Retriggerable)

Data

Sheet, reprinted from Intel

in Appendix

C.

Digital

The

CMOS compatible

Group A - Port A

Group B

Port

is not

available for

Mode

read from

Mode

shaking

Mode

through Port

These

Programmable

VO,

programmable

----

Port

A

Port

and

0 - Basic input/output.

the specified

-

I

Strobed input/output.

signals.

-

2

Strobed

modes

Interrupts

The

1200

has four

output

of timer/counter

is

completed.

completed. The

changes

reaches

how

to

The DMA

external

states from

0. Chapter 1

program

intemrpts.

Peripheral

peripheral

has

chip

(8

lines)

(8

B

lines)

are

C

available

your

use. You

bidirectional input/output.

A. Handshaking

are detailed in

jumper-selectable

2. The

done is

trigger at

low

high.

to

you

tells

interface

24 digital

port.

end-of+onvert

how

I/O

Port

and

Port

and

at the external I/O

can use

Lets

I-es

is

the 8255 Data

used in

the

VO

Or, the

to set the

Interface

is

@PI)

lines

C

Upper

C Lower

the

you

use

you

similar

intemrpt

the DMA mode

connector

output of

jumpers

used for

divided into

(4

(4

16 lines

simple input

transfer IIO

I*ts

Mode

to

Sheet, reprinted

sources:

signal

can

can

timer/counter

digital

goups

two

lines);

lines).

connector,

Ports

of

you

1.

be used

to

be used

on the intemrpt

p2. port

A

and C in

and

output operation for

data from Port A in

communicate

from Intel

end-of-convert,

interrupt

to

generate

an

generate

to

2

cangenerate

functions.

VO

12 lines

of

B is

one of these

bidirectionally

in Appendix

DMA

the computer

intemtpt

an

header

connector P7,

This high-performanceTlLl

each:

dedicated

conjunction

whenever

intemrpt

an intemrpt

to on-board

three

porL

a

wittr

C.

done, the

when

a DMA

whenever

PPI

operating

Data

is

wittr

strobes

an external

external

whenever

and

trigger,

an A/D

transfer is

the

Chapter 4

written

rhe count

functions

modes:

to or

or hand-

device

and

convenion

nigger line

describes

and

the

3-5

CHAPTER

4

This

chapter shows

board. It

description

flow

included

this chapter. These

and BASIC, include

programming.

provides

of

diagrams to aid

on the disk in

a complete

programming

programs,

BOARD

you

how

operations

you

source

programming.

in

your

board

code

OPERATION AND

program

to

description

package

written in Turbo

to simplify

and use

of the

and

operating

The

are

your

VO

example

listed

Turbo

C,

PROGRAMMING

your

1200

map,

a detailed

modes,

at the end

applications

and

programs

Pascal,

of

4-l

Defining

the

VO Map

The I/O map

consecutive

scribed in

Chapter l, Board

S 1 is factory

in

I/O map.

the

Reglster

Read

for

I/O port

set

at 300

Description

Status/Start

Read Data/Update

Reset

Reserved

8255 PPI

8255

PPI

Port A

Port

B

(Ghannel/Board

8255

PPI

Port

C

8255 PPlControlWord

S2S4TimerlCounter

(Used

for

pacer

8254Timer/Counter

(Used

8254

(Available

pacer

for

Timer/Counter

for external

S254TimerlCounter

ControlWord

D/A Converter

(ADA1200

D/A

Converter

(ADA1200

D/A Converter

(ADA1200

D/A

Converter

(ADA1200

*

=

BA

Base

1

only)

1 MSB

only)

2

only)

2 MSB

only)

Address

the ADl200

locations. The

Settings.

(768

hex

Convert

DACs

decimal). The following

Read

Read converted

first, then MSB

Not used

Not used

Read

Functions)

Read

Read Port

Not used

0

clock)

Read count

1

clock)

Read

2

use)

Read count

Not

LSB

Not

Nol

LSB

Not

Not used

ADA1200

and

base address

This

switch can

."Table

/t-1

Read

slatus word

Port A dighal

Port B bits

C digital

count value

value

used

used

used

used

is

shown in Table 4-1

(designated

as

BA)

can

be accessed without removing

sections describe

--ADl200/ADA1200

Function