Topaz, Stratus, Tropos,

Garnet, and Duros

PMC Graphics Boards

User’s Manual

Rastergraf

Rastergraf, Inc.

1810-J SE First St.

Redmond, OR 97756

(541) 923-5530

web: http://www.rastergraf.com

Release 3.7

May 7, 2017

Table of Contents

INTRODUCTION.......................................................................................................... 0-1

GETTING HELP .......................................................................................................................................... 0-2

BOARD REVISIONS .................................................................................................................................... 0-2

NOTICES .................................................................................................................................................... 0-3

CONVENTIONS USED IN THIS MANUAL ..................................................................................................... 0-4

CHAPTER 1 GENERAL INFORMATION .............................................................. 1-1

1.1 INTRODUCTION ................................................................................................................................... 1-2

1.2 SM731 GRAPHICS CONTROLLER ........................................................................................................ 1-9

1.2.1 Overview ................................................................................................................................. 1-9

1.2.2 Detailed Description.............................................................................................................. 1-10

1.2.3 SM731 Features..................................................................................................................... 1-11

1.3 VIDEO CAPTURE AND PLAYBACK ..................................................................................................... 1-13

1.4 BT835 NTSC/PAL/SECAM DIGITIZER ........................................................................................... 1-16

1.5 AD9882 RGBHV/DVI DIGITIZER .................................................................................................... 1-17

1.6 FLEXIBLE DISPLAY SUPPORT ............................................................................................................ 1-18

1.6.1 TV Display ............................................................................................................................ 1-19

1.6.2 Analog RGB Displays ........................................................................................................... 1-19

1.6.3 STANAG 3350 A-C (Topaz/Duros)...................................................................................... 1-19

1.6.4 Flat Panel Displays................................................................................................................ 1-20

1.7 FRONT AND REAR PANEL I/O OPTIONS............................................................................................. 1-22

1.8 SOFTWARE SUPPORT......................................................................................................................... 1-25

1.9 ADDITIONAL DETAILS ABOUT SDL .................................................................................................. 1-25

1.10 ADDITIONAL REFERENCES .............................................................................................................. 1-27

CHAPTER 2 SPECIFICATIONS ................................................................................ 2-1

2.1 GENERAL ............................................................................................................................................ 2-2

2.2 SPECIFICATIONS UNIQUE TO TOPAZ, STRATUS, AND GARNET ............................................................ 2-8

2.3 DISPLAY TIMING...............................................................................................................................2-10

2.4 MONITOR REQUIREMENTS ................................................................................................................ 2-12

2.5 VERIFIED DISPLAY AND CAPTURE MODES ....................................................................................... 2-13

2.5.1 Basic Format Evaluations...................................................................................................... 2-13

2.5.2 Maximum Display/Capture Performance.............................................................................. 2-15

2.6 CONFIGURATION INFORMATION ....................................................................................................... 2-17

2.6 SOFTWARE SUPPORT......................................................................................................................... 2-20

CHAPTER 3 CONNECTOR PINOUTS AND CABLE INFORMATION .............. 3-1

3.1 INTRODUCTION ................................................................................................................................... 3-2

3.2 VGA CONNECTOR .............................................................................................................................. 3-5

3.3 DVI-I CONNECTOR ............................................................................................................................. 3-7

3.4 MDR20 CONNECTOR.......................................................................................................................... 3-9

3.4.1 MDR20 Pinout 20A – NTSC/PAL or RGBHV In, NTSC/PAL Out....................................... 3-9

3.4.2 MDR20 Pinout 20B – DVI Input........................................................................................... 3-10

3.5 MDR26 CONNECTOR........................................................................................................................ 3-11

3.5.1 MDR26 Pinout 26A – Video In, Video Out, Ch 1 LVDS Out.............................................. 3-11

3.5.2 MDR26 Pinout 26B – DVI Input, Ch 1 LVDS Out............................................................... 3-12

3.5.3 MDR26 Pinout 26C – Ch 1 and CH 2 LVDS Out................................................................. 3-12

3.6 MDSM CONNECTOR......................................................................................................................... 3-13

3.6.1 Pinout MDSMA – NTSC/PAL or RGBHV In, NTSC/PAL Out........................................... 3-13

3.6.2 Pinout MDSMB – DVI Input ................................................................................................3-14

3.7 S-VIDEO CONNECTOR....................................................................................................................... 3-15

3.8 VGA TO VGA CABLE....................................................................................................................... 3-16

3.9 S-VIDEO ADAPTER CABLES .............................................................................................................. 3-17

3.10 DVI-I MULTIFUNCTION BREAKOUT CABLE .................................................................................... 3-19

3.10.1 C1 – Primary VGA.............................................................................................................. 3-20

3.10.2 C2 – Secondary VGA.......................................................................................................... 3-20

3.10.3 C3 – DVI ............................................................................................................................. 3-21

3.11 DVI-I TO VGA ADAPTERS.............................................................................................................. 3-22

3.12 TOPAZPMC VGA BREAKOUT CABLE............................................................................................. 3-24

3.13 TOPAZPMC VIDEO I/O BREAKOUT CABLE..................................................................................... 3-25

3.14 TOPAZPMC DVI IN ADAPTER CABLE ............................................................................................ 3-26

3.15 TOPAZPMC VIDEO I/O + LVDS BREAKOUT CABLE ...................................................................... 3-27

3.16 TOPAZPMC DVI IN + LVDS BREAKOUT CABLE............................................................................ 3-28

3.17 TOPAZPMC LVDS EXTENSION CABLE .......................................................................................... 3-29

3.18 STRATUSPMC VIDEO I/O BREAKOUT CABLE................................................................................. 3-31

3.19 STRATUSPMC DVI IN ADAPTER CABLE ........................................................................................ 3-32

3.20 CONNECTIONS TO PMC PN1, PN2, AND PN4................................................................................... 3-33

Pn4 Connectors................................................................................................................................ 3-33

3.20.1 Pn1 Connector (all boards).................................................................................................. 3-35

3.20.2 Pn2 Connector (all boards).................................................................................................. 3-36

3.20.3 Pn4 – Dual LVDS Only....................................................................................................... 3-37

3.20.4 Pn4 – Dual LVDS and DVI (In or Out)............................................................................... 3-38

3.20.5 Pn4 - Dual LVDS, DVI (In or Out), Analog Video I/O, VGA............................................ 3-39

3.20.6 Pn4 - Dual LVDS, Dual VGA, Analog Video I/O .............................................................. 3-40

3.20.7 Pn4 - Dual LVDS, VGA, DVI In, DVI Out ........................................................................ 3-41

3.20.8 Pn4 - Dual LVDS, Dual VGA, DVI In................................................................................ 3-42

3.20.9 Pn4 - Dual LVDS, Single VGA........................................................................................... 3-43

3.20.10 Pn4 – RG-101 Compatible VGA Pinout............................................................................ 3-44

CHAPTER 4 INSTALLING YOUR RASTERGRAF GRAPHICS BOARD.......... 4-1

4.1 INTRODUCTION ................................................................................................................................... 4-2

4.2 UNPACKING YOUR BOARD ................................................................................................................. 4-2

4.3 PREPARING FOR INSTALLATION .......................................................................................................... 4-3

4.3.1 Interrupt Settings ..................................................................................................................... 4-3

4.3.2 Address Settings...................................................................................................................... 4-3

4.3.3 Changing the Jumpers ............................................................................................................. 4-3

4.4 GRAPHICS BOARD INSTALLATION.................................................................................................... 4-10

4.5 INSTALLING IN A PCI BACKPLANE USING A CARRIER ....................................................................... 4-14

4.6 INSTALLING IN A COMPACTPCI BACKPLANE USING A CARRIER ....................................................... 4-17

4.7 FINISHING THE INSTALLATION .......................................................................................................... 4-21

4.7.1 Connecting to the Monitor..................................................................................................... 4-21

4.7.2 Checking your Display.......................................................................................................... 4-22

4.8 USING A RASTERGRAF BOARD IN A PC............................................................................................. 4-23

4.8.1 Single Graphics Board........................................................................................................... 4-23

4.8.2 Multiboard Operation ............................................................................................................ 4-23

4.9 USING A RASTERGRAF BOARD IN A POWERPC ................................................................................. 4-28

4.10 FINAL CHECKS................................................................................................................................ 4-28

CHAPTER 5 PROGRAMMING ON-BOARD DEVICES AND MEMORIES...... 5-1

5.1 INTRODUCTION ................................................................................................................................... 5-2

5.2 SM731 GRAPHICS ACCELERATOR ...................................................................................................... 5-3

5.3 CLOCKS............................................................................................................................................ 5-12

5.3.1 CY22150 Reference Clock.................................................................................................... 5-12

5.4 VIDEO TIMING PARAMETERS ............................................................................................................ 5-13

5.4.1 Application Note: Adjusting the Timing Parameters............................................................. 5-14

5.4.2 Pan and Scroll........................................................................................................................ 5-17

Request for Assistance in Determining Video Timing Parameters ................................................. 5-18

5.5 SYSTEM MANAGEMENT DEVICES AND FUNCTIONS........................................................................... 5-19

5.6 TALK TO ME THROUGH I2C.............................................................................................................. 5-20

5.7 TOPAZ/STRATUS/GARNET AUXILIARY REGISTER ............................................................................. 5-21

5.8 DVI DIGITAL VIDEO OUTPUT ........................................................................................................... 5-22

5.9 ADV7123 AND ADV7120 VGA DACS............................................................................................ 5-24

5.10 AD9882 HIGH SPEED DIGITIZER (STRATUS/GARNET) .................................................................... 5-25

5.11 BT835 NTSC/PAL/SECAM VIDEO DECODER ............................................................................... 5-26

5.12 FLASH EEPROM ............................................................................................................................ 5-30

5.13 SERIAL EEPROM........................................................................................................................... 5-31

5.14 INTERRUPTS .................................................................................................................................... 5-31

CHAPTER 6 TROUBLESHOOTING........................................................................ 6-1

6.1 GENERAL PROCEDURES ...................................................................................................................... 6-2

6.2 DEALING WITH THE PCI BUS .............................................................................................................. 6-3

6.3 MAINTENANCE, WARRANTY, AND SERVICE ....................................................................................... 6-3

Tables

Table 1-1 Board Feature Summary................................................................................. 1-3

Table 1-2 SDL Functional Summary............................................................................1-26

Table 2-1 Rastergraf Ruggedization Levels Chart.......................................................... 2-7

Table 2-2 BIOS Display Timing Specifications ........................................................... 2-10

Table 2-3 VGA/Windows Platform Display Timing Specifications ........................... 2-10

Table 2-4 SDL Platform Display Timing Specifications............................................. 2-11

Table 2-5 Basic Display/Capture Format Capabilities ................................................ 2-14

Table 2-6 Maximum Display/Capture Format Capabilities.........................................2-16

Table 2-7 Standard Front Panel Board Configurations and Connector Utilization..... 2-18

Table 2-8 Standard Rear Panel Board Configurations and I/O Assignments..............2-19

Table 2-9 Front Panel Board Model Compatibility ..................................................... 2-19

Table 2-10 Software...................................................................................................... 2-20

Table 3-1 Front Panel Signal Definitions ....................................................................... 3-3

Table 3-2 Front and Rear Panel Connector Usage.......................................................... 3-4

Table 3-3 Analog (VGA) Video Connector Pinout ........................................................ 3-6

Table 3-4 Tropos DVI-I Connector (Pinout D1) ............................................................ 3-7

Table 3-5 TopazPMC/2 and StratusPMC DVI-I Connector (Pinout D2)....................... 3-8

Table 3-6 Video I/O (VI/O) Front Panel Connector (Pinouts 20A & 20B).................... 3-9

Table 3-7 Video I/O (VI/O) Front Panel Connector (Pinouts 26A-26C) .....................3-11

Table 3-8 Video I/O (VI/O) Front Panel Connector (Pinouts MDSMA & MDSMB) . 3-13

Table 3-9 VGA to VGA Cable (A31-00599-1012) ...................................................... 3-16

Table 3-10 TopazPMC S-Video to BNC adapter cable (A31-00709-1003)................. 3-17

Table 3-11 StratusPMC BNC to S-Video Adapter Cable (VAD44) ............................ 3-18

Table 3-12 C1 - Primary VGA Connector....................................................................3-20

Table 3-13 C2 - Secondary VGA Connector................................................................3-20

Table 3-14 C3 - DVI-D Connector ............................................................................... 3-21

Table 3-15 DVI-I to VGA Adapter............................................................................... 3-22

Table 3-16 TopazPMC VGA Breakout Connector....................................................... 3-24

Table 3-17 TopazPMC Video I/O Breakout Cable....................................................... 3-25

Table 3-18 TopazPMC DVI In Adapter Cable ............................................................. 3-26

Table 3-19 TopazPMC Video I/O + LVDS Breakout Cable........................................3-27

Table 3-20 TopazPMC DVI In + LVDS Breakout Cable ............................................3-28

Table 3-21 TopazPMC LVDS Extension Cable (A31-00735-4012)............................ 3-30

Table 3-22 StratusPMC Video I/O Breakout Cable (A31-00735-0036) ...................... 3-31

Table 3-23 StratusPMC DVI In Adapter Cable............................................................3-32

Table 3-24 Rear Panel Signal Definitions ....................................................................3-34

Table 4-1 x86 Supported Video Modes........................................................................ 4-24

Table 5-1 Standard Graphics Display Formats.............................................................5-13

Table 5-2 Video Timing Parameter Request Form...................................................... 5-18

Table 5-3 I2C Device Addresses................................................................................... 5-20

Figures

Figure 1-1 Topaz Block Diagram ................................................................................... 1-4

Figure 1-2 Stratus Block Diagram .................................................................................. 1-5

Figure 1-3 Tropos Block Diagram..................................................................................1-6

Figure 1-4 Garnet Block Diagram .................................................................................. 1-7

Figure 1-5 Duros Block Diagram ..................................................................................1-8

Figure 1-6 SM731 Application Block Diagram.............................................................. 1-9

Figure 1-7 SM731 Detail Block Diagram..................................................................... 1-12

Figure 1-8 Video Capture and Playback Support ......................................................... 1-13

Figure 1-9 Capture Buffer and Display Memory.......................................................... 1-14

Figure 1-10 Video Processing Data Path...................................................................... 1-15

Figure 1-11 Bt835 Video Digitizer Block Diagram .....................................................1-16

Figure 1-12 AD9882 High Speed Digitizer Block Diagram ........................................1-17

Figure 1-13 Display Channels ......................................................................................1-18

Figure 1-14 DVI Flat Panel Output Block Diagram.....................................................1-20

Figure 1-15 LVDS Flat Panel Output Block Diagram.................................................. 1-21

Figure 1-16 Front and Rear Panel I/O Options for Topaz ............................................ 1-22

Figure 1-17 Front and Rear Panel I/O Options for Stratus ........................................... 1-23

Figure 1-18 Front and Rear Panel Output Options for Tropos ..................................... 1-23

Figure 1-19 Rear Panel I/O Options for Garnet............................................................ 1-24

Figure 1-20 Rear Panel Output Options for Duros ....................................................... 1-24

Figure 3-1 S-Video Connector...................................................................................... 3-15

Figure 3-2 VGA to VGA Extension Cable (A31-00599-1012)....................................3-16

Figure 3-3 S-Video to BNC Adapter (A31-00709-1003)............................................. 3-17

Figure 3-4 BNC to S-Video Adapter Cable (VAD44).................................................. 3-18

Figure 3-5 DVI-I Multifunction Breakout Cable (A31-00735-1012)........................... 3-19

Figure 3-6 Molex 88741-8700 DVI-I to VGA Adapter................................................ 3-22

Figure 3-7 DVI to VGA Adapter Cable (A31-00599-5012) ........................................3-23

Figure 3-8 TopazPMC VGA Breakput Cable (A31-00735-2012) ...............................3-24

Figure 3-9 TopazPMC LVDS Extension Cable (A31-00735-4012) ............................3-29

Figure 3-10 MDSM to BNC Breakout Cable (A31-00735-0036)................................ 3-31

Figure 4-1 Jumper Locations for the Fab Rev 0 TopazPMC Board............................... 4-5

Figure 4-2 Jumper Locations for the Fab Rev 1 TopazPMC Board............................... 4-5

Figure 4-2 Jumper Locations for the Fab Rev 1 TopazPMC Board............................... 4-6

Figure 4-3 Jumper Locations for the Fab Rev 2 TopazPMC Board............................... 4-7

Figure 4-4 Jumper Locations for the Fab Rev 1 StratusPMC and TroposPMC Boards. 4-7

Figure 4-4 Jumper Locations for the Fab Rev 1 StratusPMC and TroposPMC Boards. 4-8

Figure 4-5 Jumper Locations for the Fab Rev 1 Garnet and Duros Boards ...................4-9

Figure 4-6 Installation of a PMC Module into an Emerson MVME2604 .................... 4-12

Figure 4-7 Installation of the PMC Module into an Emerson CPV3060...................... 4-13

Figure 4-8 Installation of a PMC Module onto a PCI-PMC Carrier............................. 4-15

Figure 4-9 Installation of a PCI Module into an Emerson MTX..................................4-16

Figure 4-10 Installation of a PMC Module onto a 3U CPCI- PMC Carrier................. 4-18

Figure 4-11 Installation of a PMC Module into a 6U CPCI- PMC Carrier..................4-19

Figure 4-12 Installing a CompactPCI Board ................................................................4-20

Figure 5-1 CY22150 Block Diagram............................................................................ 5-12

Figure 5-2 Video Display Timing Fields......................................................................5-15

Figure 5-3 THC63DV164 Block Diagram ...................................................................5-22

Figure 5-4 THC63DV164 RGB to 24-bit TMDS Mapping Diagram........................... 5-23

Figure 5-5 Bt835 Detailed Block Diagram...................................................................5-27

Rastergraf

Introduction

This manual provides information about how to configure, install, and

program the Rastergraf Silicon Motion SM731-based Topaz, Stratus,

Tropos, Garnet, and Duros PMC graphics display controllers. When used

with appropriate PMC-to-host adapters, PCI and CompactPCI compatible

computers can also be supported.

This manual is broken down into six chapters:

Chapter 1: General Information

Chapter 2: Specifications

Chapter 3: Connector Pinouts and Cable Information

Chapter 4: Installing Your Graphics Board

Chapter 5: Programming Devices and Memories

Chapter 6: Troubleshooting

Chapters 1-3 provide background material about the graphics boards.

Understanding the information in the chapters, however, is not essential

for the hardware or software installation. If you want to perform the

installation as quickly as possible, start with Chapter 4. If you have

problems installing the hardware, refer to Chapter 6 for help.

Introduction - 1

Rastergraf

Getting Help

This installation manual gives specific steps to take to install your

Rastergraf board. There are, however, variables specific to your computer

configuration and monitor that this manual cannot address. Normally, the

default values given in this manual will work. If you have trouble

installing or configuring your system, first read Chapter 6,

“Troubleshooting”. If this information does not enable you to solve your

problems, do one of the following:

1) call Rastergraf technical support at: (541) 923-5530

2) send E-mail to: support@rastergraf.com

If your problem is monitor related, Rastergraf technical support will need

detailed information about your monitor.

Board Revisions

This manual applies to the following board revision levels:

Tropos/Stratus Fab Rev 1

Duros/Garnet Fab Rev 1

Topaz Fab Rev 0, 1, 2

Manual Revisions

Revision 3.1 April 2007 Rastergraf version

Revision 3.2 September 2007 Update RIO info

Revision 3.3 February 12, 2008 Fix part numbers, add

Revision 3.4 December 6, 2013 Changes for Topaz Rev 1.

Revision 3.5 January 6, 2014 clean up some text in Ch. 3

Revision 3.6 February 7, 2017 clean up and correct tables in

Revision 3.7 May 5, 2017 Changes for Topaz Rev 2.

.

LVDS info, change cable info.

Remove fax, update address, add

RG-101 pinout

Section 3.20.

Moved jumpers, added option for

VGA Ch 2 on Ch 1 on DVI-I

Introduction - 2

Notices

Rastergraf

Information contained in this manual is disclosed in confidence and may

not be duplicated in full or in part by any person without prior approval of

Rastergraf. Its sole purpose is to provide the user with adequately detailed

documentation to effectively install and operate the equipment supplied.

The use of this document for any other purpose is specifically prohibited

The information in this document is subject to change without notice. The

specifications of the graphics boards and other components described in

this manual are subject to change without notice. Although it regrets them,

Rastergraf, Inc. assumes no responsibility for any errors or omissions that

may occur in this manual. Customers are advised to verify all information

contained in this document

The electronic equipment described herein generates, uses, and may

radiate radio frequency energy, which can cause radio interference.

Rastergraf, Inc. assumes no liability for any damages caused by such

interference.

Rastergraf, Inc.’s products are not authorized for any use as critical

components in flight safety or life support equipment without the express

consent of the president of Rastergraf, Inc.

These products have been designed to operate in user-provided PMCcompatible computers. Connection of incompatible hardware is likely to

cause serious damage. Rastergraf assumes no liability for any damages

caused by such incompatibility.

Rastergraf assumes no responsibility for the use or reliability of software

or hardware that is not supplied by Rastergraf, or which has not been

installed in accordance with this manual.

The TopazPMC, StratusPMC, TroposPMC, GarnetPMC, and DurosPMC

graphics boards are manufactured and sold under license from

Curtiss-Wright Controls Embedded Computing (CWCEC). Contact

Rastergraf, Inc. for additional information.

Rastergraf is a trademark of Rastergraf, Inc.

All other trademarks and copyrights are the property of their respective

owners.

Copyright © 2017 by Rastergraf, Inc.

Introduction - 3

Rastergraf

Conventions Used In This Manual

The following list summarizes the conventions used throughout this

manual.

Code

fragments

Commands or

program names

System prompts

and commands

Keyboard usage

Note

Caution

Code fragments, file, directory or path names and

user/computer dialogs in the manual are presented

in the courier typeface.

Commands, or the names of executable programs,

except those in code fragments, are in bold.

Commands in code fragments are preceded by the

system prompt, a percentage sign (%), the standard

prompt in UNIX’s C shell, or the hash mark (#),

the standard UNIX prompt for the Super-User.

<CR> stands for the key on your keyboard labeled

“RETURN” or “ENTER”

Note boxes contain information either specific to

one or more platforms, or interesting, background

information that is not essential to the installation.

Caution boxes warn you about actions that can

cause damage to your computer or its software.

Warning!

Introduction - 4

Warning! boxes warn you about actions that can

cause bodily or emotional harm.

Chapter 1

General Information

Rastergraf

General Information 1-1

Rastergraf

1.1 Introduction

The Topaz, Stratus, Tropos, Garnet, and Duros comprise a set of closely

related designs that have been tuned to address a variety of requirements.

Originally starting with the Stratus as the fully configured version and

Tropos as the low parts count version, the line was expanded into the

analogous Garnet and Duros which are rugged, conduction cooled

versions adding 2 thermal layers and, on the Duros, the ability to produce

STANAG 3350 A-C output modes.

The final iteration is the Topaz, a non-conduction cooled design, which is

intended to subsume the Stratus and Tropos. It:

a) includes the new features added in the Garnet and Duros,

b) using an MDR26 connector, adds the optional capability to provide

LVDS on the front panel,

c) replaces the Stratus front panel MDSM Video I/O connector with an

MDR20 for easier cable construction,

d) adds a dual front panel VGA connector option,

e) adds the 3.3V local regulator option that was dropped on Garnet and

Duros.

The following page shows a table of the features of the boards in a

comparative format to ease understanding what each version provides.

Following that are block diagrams of each board, and then some

explanatory sections covering the board functions.

1-2 General Information

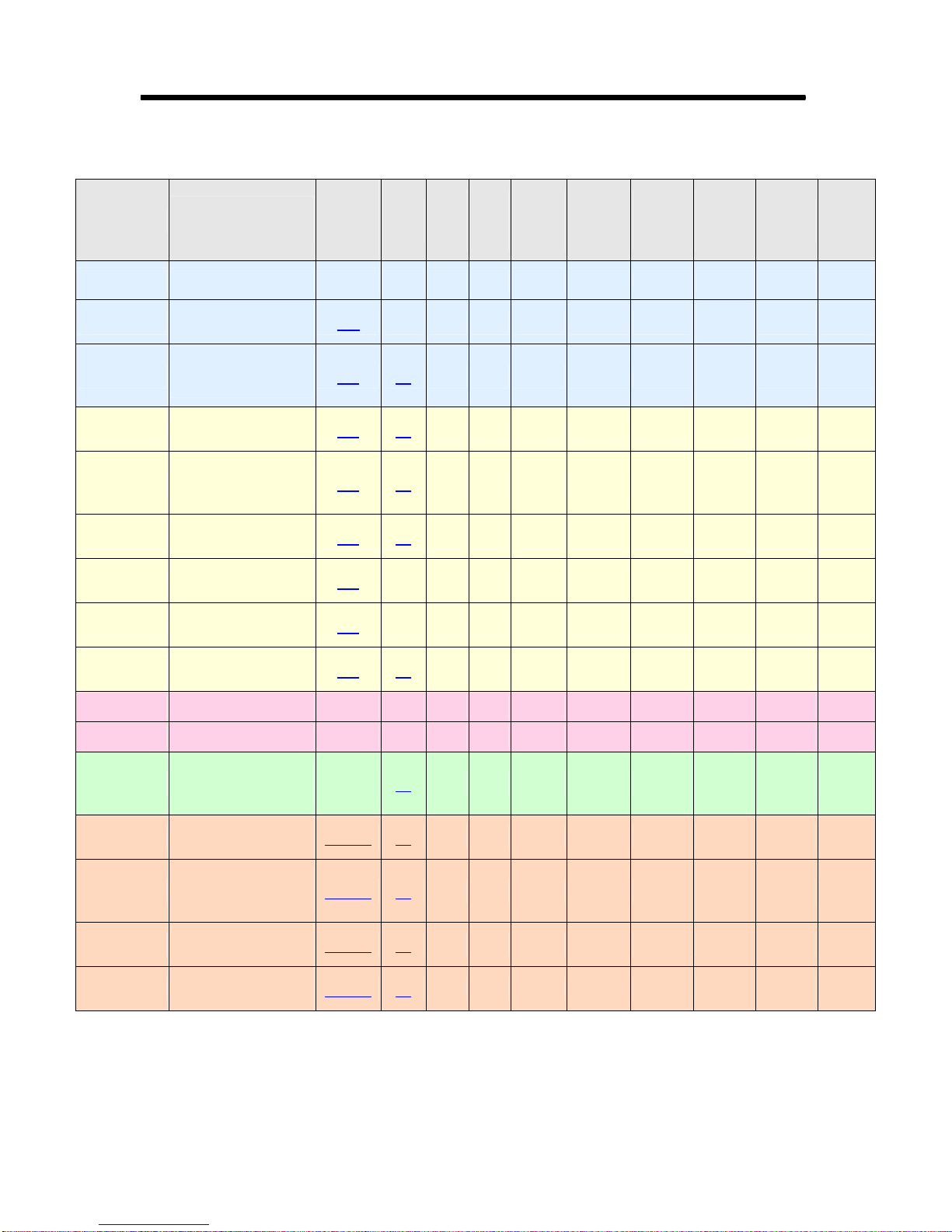

Table 1-1 Board Feature Summary

Rastergraf

Topaz

Stratus/

Garnet

Tropos/

Duros

Silicon Motion SM731 2D/3D engine with 16MB SDRAM yes yes yes

1600x1200 single VGA

1024x768 dual VGA

1280x1024 single/1024x768 dual LVDS

1600x1200 single DVI

yes yes yes

yes

yes

no

yes yes yes

yes yes option

S-Video/NTSC/PAL/SECAM single output yes yes Duros

Interlaced/non-interlaced, Sync-On-Green

STANAG 3350 A-C output option

DVI Input mode yes

RGBHV, RGB, and STANAG Input modes yes

S-Video/NTSC/PAL/SECAM Input modes yes

yes yes Duros

yes

no Duros

yes no

yes no

yes no

Dual front panel VGA connector option yes no no

Dual VGA via DVI b/o cable option yes

Dual VGA rear panel option yes yes

Stratus

no

no

LVDS options – front/rear yes rear only rear only

MDR26 LVDS front panel connector option yes

n/a n/a

Single DVI options – front/rear yes yes yes

Composite/S-Video output

MDSM-16 Video I/O connector no

yes yes yes

Stratus

no

MDR20 Video I/O connector yes no no

2 Kb serial EEPROM and LM75 thermal sensor

yes yes yes

3.3V & 5V PCI Bus Signaling yes yes yes

33/66 MHz PCI Bus Speed yes yes yes

CCPMC form factor compatible yes yes yes

Full CCPMC version with thermal layers no

Local 3.3V regulator yes

Garnet Duros

Stratus Tropos

Side 1 only component loading yes yes yes

Field reprogrammable VGA BIOS yes yes yes

SDL Graphics Subroutine Package

SDL-based WindML and BIT

Windows 2K/XP graphics drivers

Windows 2K/XP video input drivers

Xfree86 Version 4.3 for Linux and VxWorks

X video in extensions for Linux and VxWorks

RG-101 Rear I/O compatible version (PCB Rev 1)

yes yes yes

yes yes yes

yes yes yes

yes yes no

yes yes yes

yes yes no

yes no no

General Information 1-3

Rastergraf

Figure 1-1 Topaz Block Diagram

Front

Front

Front

Front

Panel

Panel

Panel

Panel

Version

Version

Version

Version

Rear

4

3

2

1

Panel

RGB In

Analog Devices

Out

VGA

VGA Ch 1

Connector

Out

VGA

VGA Ch 1

Connector

Out

VGA

VGA Ch 1

Connector

Out

DVI-I

VGA Ch 1

Connector

Out

Graphics

VGA Ch 1

DVI In

Select

Conexant Bt835

RGB/DVI Digitizer

AD9882 High Speed

Video In

Processor

Video Input

VGA

Connector

Graphics

VGA Ch 1 Out

Out

VGA Ch 2

Out

VGA Ch 2

Out

Graphics

VGA Ch 2

DVI Out

Analog Devices

THine THC63DV164

DVI Output Encoder

ADV7120 DAC (STANAG)

LVDS

Single

MDR-26

Channel

Connector

Dual

Channel

Connector

Dual

Graphics

LVDS

Channel

MDR-26

DVI Out

DVI

I/O Resource Manager

Video Out

VGA Ch 2 Out

ADV7123 DAC

Analog Devices

LVDS

MDR-20

Connector

LVDS Out

Video

Input/

Output/

Video

Input/

Output/

Video

Input/

Important Note

Topaz can support

or

DVI In

RGBHV

or

DVI In

RGBHV

or

Output/

DVI In

RGBHV

OR

Video Input

STANAG Out

RGB/DVI/NTSC/PAL

but not at the same time

Figure 1-1 Topaz Block Diagram

Ch 1

Ch 2

C

2

I

Controller

SM731

Motion

Silicon

Graphics

1-4 General Information

Input

Video

Processor

On-Chip

Accelerator

YUV/RGB Multiplexer

PLD for STANAG or

235 MHz

RAMDAC

Video

Display

Memory

Output

Processor

Drivers

Flat Panel

PCI Bus

32 bit

33/66 MHz

Interface

PMC (PCI) Bus

Video

NTSC/PAL

2D/3D

Drawing

Encoder

Engines

Dual

Channel

DMA

LVDS

Encoder

Engine

PLD Controller

BIOS EEPROM

BIOS

Memory

Interface

3.3V

Local

Regulator

Option

Rastergraf

Figure 1-2 Stratus Block Diagram

Front

Panel

Rear

Panel

Option

Option

RGB In

Analog Devices

AD9882 High Speed

Out

DVI-I

VGA Ch 1

Connector

Out

Graphics

VGA Ch 1

DVI In

Select

Video In

Video Input

RGB/DVI Digitizer

Conexant Bt835

Graphics

VGA Ch 1 Out

Processor

Out

VGA Ch 2

Out

Graphics

VGA Ch 2

DVI Out

THine THC63DV164

DVI Output Encoder

DVI Out

DVI

Dual

Graphics

LVDS

Channel

I/O Resource Manager

Video Out

VGA Ch 2 Out

ADV7123 DAC

Analog Devices

MDSM

Connector

LVDS Out

Video

Video

Input/

Output/

Input/

Output/

or

RGBHV

or

RGBHV

DVI In

DVI In

Ch 1

Ch 2

C

2

I

Motion

Silicon

Controller

SM731

Graphics

Accelerator

Video

Input

Multiplexer

PLD for YUV/RGB

Processor

Display

Memory

On-Chip

235 MHz

RAMDAC

Video

Output

Processor

Drivers

Flat Panel

PCI Bus

Interface

32 bit

33/66 MHz

Video

Encoder

NTSC/PAL

2D/3D

Engines

Drawing

PMC (PCI) Bus

Dual

LVDS

Channel

DMA

Encoder

Engine

PLD Controller

BIOS

Memory

Local

BIOS EEPROM

Interface

3.3V

Regulator

Figure 1-2 Stratus Block Diagram

Option

General Information 1-5

Rastergraf

Figure 1-3 Tropos Block Diagram

Front

Panel

Rear

Panel

Option

Option

DVI-I

Connector

Graphics

Out

VGA Ch 1

Out

VGA Ch 1

Graphics

VGA Ch 1 Out

Out

VGA Ch 2

Out

VGA Ch 2

Graphics

DVI Out

THine THC63DV164

DVI Output Encoder

DVI Out

DVI

Dual

Channel

Graphics

LVDS

I/O Resource Manager

Video Out

VGA Ch 2 Out

ADV7123 DAC

Analog Devices

LVDS Out

Ch 1

Ch 2

C

2

I

Controller

SM731

Motion

Silicon

Graphics

Accelerator

1-6 General Information

Video

Input

Processor

Display

Memory

On-Chip

235 MHz

RAMDAC

Video

Output

Processor

Drivers

Flat Panel

PCI Bus

32 bit

33/66 MHz

NTSC/PAL

2D/3D

Interface

PMC (PCI) Bus

Video

Encoder

Engines

Drawing

Dual

LVDS

Channel

DMA

Encoder

Engine

PLD Controller

BIOS

Memory

Local

BIOS EEPROM

Interface

3.3V

Regulator

Figure 1-3 Tropos Block Diagram

Option

Rastergraf

Figure 1-4 Garnet Block Diagram

Ch 1

Rear

Ch 2

Panel

Graphics

DVI In

RGB In

Select

Analog Devices

RGB/DVI Digitizer

AD9882 High Speed

Out

VGA Ch 1

Video In

VGA Ch 1 Out

Processor

Video Input

Conexant Bt835

YUV/RGB Multiplexer

PLD for

Graphics

VGA Ch 2

Out

DVI

Graphics

DVI Out

VGA Ch 2 Out

Analog Devices

THine THC63DV164

DVI Output Encoder

Dual

LVDS

Channel

Graphics

I/O Resource Manager

Video Out

ADV7120 DAC

LVDS Out

Video

Input/

Output/

RGBHV

PLD Controller

or

DVI In

BIOS EEPROM

Figure 1-4 Garnet Block Diagram

C

2

I

Controller

SM731

Motion

Silicon

Video

Graphics

Accelerator

Input

Processor

Display

On-Chip

235 MHz

Memory

RAMDAC

Video

Output

Processor

Drivers

Flat Panel

PCI Bus

Interface

32 bit

33/66 MHz

Video

Encoder

NTSC/PAL

2D/3D

Engines

Drawing

PMC (PCI) Bus

Dual

LVDS

Channel

DMA

Encoder

Engine

BIOS

Memory

Interface

General Information 1-7

Rastergraf

Rear

Panel

Out

Graphics

VGA Ch 1

Figure 1-5 Duros Block Diagram

Out

Graphics

VGA Ch 2

DVI

Graphics

Dual

Graphics

LVDS

Channel

I/O Resource Manager

DVI Out

VGA Ch 1 Out

VGA Ch 2 Out

or

ADV7120 DAC

Analog Devices

STANAG >> VGA Ch 1

Second VGA >> VGA Ch 2

Video Out

THine THC63DV164

DVI Output Encoder

LVDS Out

Ch 1

Ch 2

C

2

I

Motion

Silicon

Controller

SM731

Graphics

Accelerator

Video

Input

PLD for STANAG

Processor

Display

Memory

On-Chip

235 MHz

RAMDAC

Video

Output

Processor

Drivers

Flat Panel

PCI Bus

32 bit

33/66 MHz

NTSC/PAL

2D/3D

Interface

PMC (PCI) Bus

Video

Encoder

Engines

Drawing

Dual

LVDS

Channel

DMA

Encoder

Engine

PLD Controller

BIOS

Memory

BIOS EEPROM

Interface

Figure 1-5 Duros Block Diagram

1-8 General Information

ZV Port

LaserDisc

NTSC/PAL

Decoder

TV Tuner

NTSC/PAL Camera

CRT Monitor

Flat Panel

PCI/AGP2X/4X

SM731

16/32MB

VCR or

MEMORY

DDR/SGRAM

8/16/32MB

TV

Optional

ZV Port

LaserDisc

NTSC/PAL

Decoder

TV Tuner

NTSC/PAL Camera

CRT Monitor

Flat Panel

PCI/AGP2X/4XPCI/AGP2X/4X

SM731

16/32MB

SM731

16/32MB

VCR or

MEMORY

DDR/SGRAM

8/16/32MB

MEMORY

DDR/SGRAM

8/16/32MB

MEMORY

DDR/SGRAM

8/16/32MB

MEMORY

DDR/SGRAM

8/16/32MB

TV

Optional

33/66 MHz, 32-bit PCI Bus

1.2 SM731 Graphics Controller

1.2.1 Overview

The SM731 is a low power 2D/3D display controller with 90, 180, and

270 degree hardware rotation. Silicon Motion's ReduceOn™ technology

for the SM731 implements functions in hardware that were previously

performed in software, allowing easier driver development. ReduceOn

technology intelligently monitors the activity on the device and optimizes

the power as necessary to maximize performance and power consumption.

This level of power management is possible since each functional block

and engine clock can be dynamically controlled to actively reduce the

overall power consumption.

Figure 1-6 SM731 Application Block Diagram

Rastergraf

33/66 MHz, 32-bit PCI Bus

16 MB

General Information 1-9

Rastergraf

1.2.2 Detailed Description

The SM731 delivers full-featured 3D, a unique memory architecture

designed to enhance 3D/2D performance, enhanced multi-display

capabilities, and Motion Compensation for DVD. Software support is

available under Windows 2K/XP and Linux/XFree86.

A robust 128-bit Drawing Engine provides excellent 2D performance. The

Drawing Engine supports 3 ROPs, BitBLT, transparent BLT, pattern BLT,

color expansion, line draw and Alpha blending. The Host interface Unit

allows support for PCI up to 66 MHz.

The SM731 incorporates an IEEE Floating Point Setup engine as well as a

full-featured 3D rendering engine. The 3D engine pipeline was designed

to operate in a balanced manner, allowing setup of 6 million triangles per

second (125MHz core frequency) and rasterization of 125 Mpix/s. The

dual pipe Texture engine can output 250 million Texels per second.

Among other features, SM731 natively supports MIP mapping, Alpha

blend, Specular highlights and Fog, Stencil planes, W buffer and fog,

Bump Mapping, and Z engine.

The SM731 integrates 16 Mbytes of on-board SGRAM (SDR) over a 64bit memory bus operating at up to 150 MHz. The 1.2 GB/sec peak

bandwidth available allows concurrent support of large displays and other

processing functions at optimum performance.

SM731 can drive two independent digital displays or simultaneously drive

LCD, CRT and TV displays. It also incorporates two 112 MHz Max pix

clock LVDS channels that can drive two separate panels or a single

high-resolution panel (up to UXGA). Support for all ACPI power states is

provided. A high quality TV encoder, VGA Core, LCD Backend

Controller and 235 MHz RAMDAC are incorporated as well.

The SM731's Motion Compensation block, Video Processor block, and

Video Capture Unit provide superior video quality for real-time video

playback and capture. When combined with performance CPUs, the

Motion Compensation block allows full frame playback of DVD video

content without the need for additional hardware. The Video Processor

supports multiple independent full screen, full motion video windows with

overlay. Each motion video window uses hardware YUV-to-RGB

conversion, scaling, and color interpolation. When combined with multiview capabilities of the chip, these independent video streams can be

output to each of two display devices and bilinear scaled to support

applications such as full screen display of local and remote images.

1-10 General Information

1.2.3 SM731 Features

High Performance Hardware Graphics Support

• 128-bit single-cycle graphics engine

• 16MB on-chip frame buffer memory with 128-bit interface

• IEEE Floating point setup engine

• Bi-linear/Tri-linear filtering, MIP-mapping, vertex and global fog

• Multi-texture, bump mapping, texture compression

• Source/destination alpha blending, Specular highlights

• Z-buffering, dual-texture pipelines

• BitBLT, line draw, Polygon/rectangle fill

• Hardware cursor and pop-up icons

Analog RGB Display Support

• 640 x 480 to 1600 x 1200 non-interlaced at 8, 16 or 24 bits/pixel

• Integrated NTSC/PAL video formats

• Composite and S-Video (Y/C) signal interfaces

Panel Support

• Integrated Dual Channel LVDS transmitters with DualMon support

• QuickRotate feature for instantaneous rotation

On-Chip Dual Display Support

• RGB+VIDEO (NTSC/PAL). LVDS+RGB (VGA)

LVDS+LVDS, and LVDS+VIDEO

Rastergraf

Video Capture and Playback Support

• Zoom video port with live video display or single-frame capture

• Full-screen video or in a window with or without graphics overlay

• Video window may be of arbitrary size and on any pixel boundary

• Multiple independent hardware video windows

• Independent video capture and display subsystems

• Arbitrary XY scaling and up to 8x zoom on video input stream

• YUV capture data directly from host using on-chip DMA controller

• Motion compensation for full-speed DVD playback

PCI Bus

• 32-bit 33/66 MHz PCI 2.1 interface with burst-mode capability

• 264 Mbytes/sec peak data transfer rate at 66 MHz

• DMA bus-master capability

• Enhanced ReduceOn™ power management

• ACPI compliant

General Information 1-11

Rastergraf

p

YUV Data Control

33/66 MHz

32-bit

PCI bus

Video Input Port

Capture Engine

Memory

Controller

2D/3D 128-bit

Graphics Engine

16 MB

On-Chip

Memory for

Capture Buffer

and

Frame Buffer

Graphics Outputs

24-bit Digital to DAC/DVI

Video Encoder

Display Engine

R G B

RGB

to

YUV

Encoding

Matrix

Clock Generation

& Timing Control

Y

U

V

Modulators

HsyncVsync

Luma-trap

Figure 1-7 SM731 Detail Block Diagram

2 x Digital Output (LVDS)

Analog RGB Output (VGA)

NTSC/PAL

Video Out

C omposite

S-Video

uts

1-12 General Information

e

1.3 Video Capture and Playback

The Topaz, Stratus, and Garnet are ideal solutions for industrial graphics

applications. They combine a powerful hardware graphics engine with

support for multiple display devices including VGA, DVI, and LVDS

displays, and NTSC/PAL video monitors.

They also provide video capture support from NTSC/PAL rate and

RGBHV or DVI up to SXGA enabling real-time full-frame-rate display of

live video as well as “frame-grabber” functionality that can upload images

to the host.

Video input may be easily included in a wide variety of applications. The

use of video input can greatly benefit control and monitoring applications

as a fundamental component of the user interface.

Figure 1-8 Video Capture and Playback Support

Rastergraf

Video Input Sourc

(camera)

Station 1

Display

PMC Host CPU

Stratus

VMEbus or

CompactPCI

System

General Information 1-13

Rastergraf

y

Window

The display controller implements independent capture and playback

subsystems. The capture system receives digitized video data through its

16 bit Video Input Port, which is driven by a multiplexer that selects

between the on-board Bt835 NTSC/PAL video decoder (see Section 1.4

and the AD9882 RGBHV/DVI decoder (see Section 1.5

). It places it in a

)

capture buffer in display memory. The playback system retrieves the video

data from the buffer and inserts it into a window in the display stream

(screen image). The output display resolution and timing is not related to

the incoming video resolution and timing so live interlaced video input

may be incorporated into the graphics display without introducing videorelated artifacts.

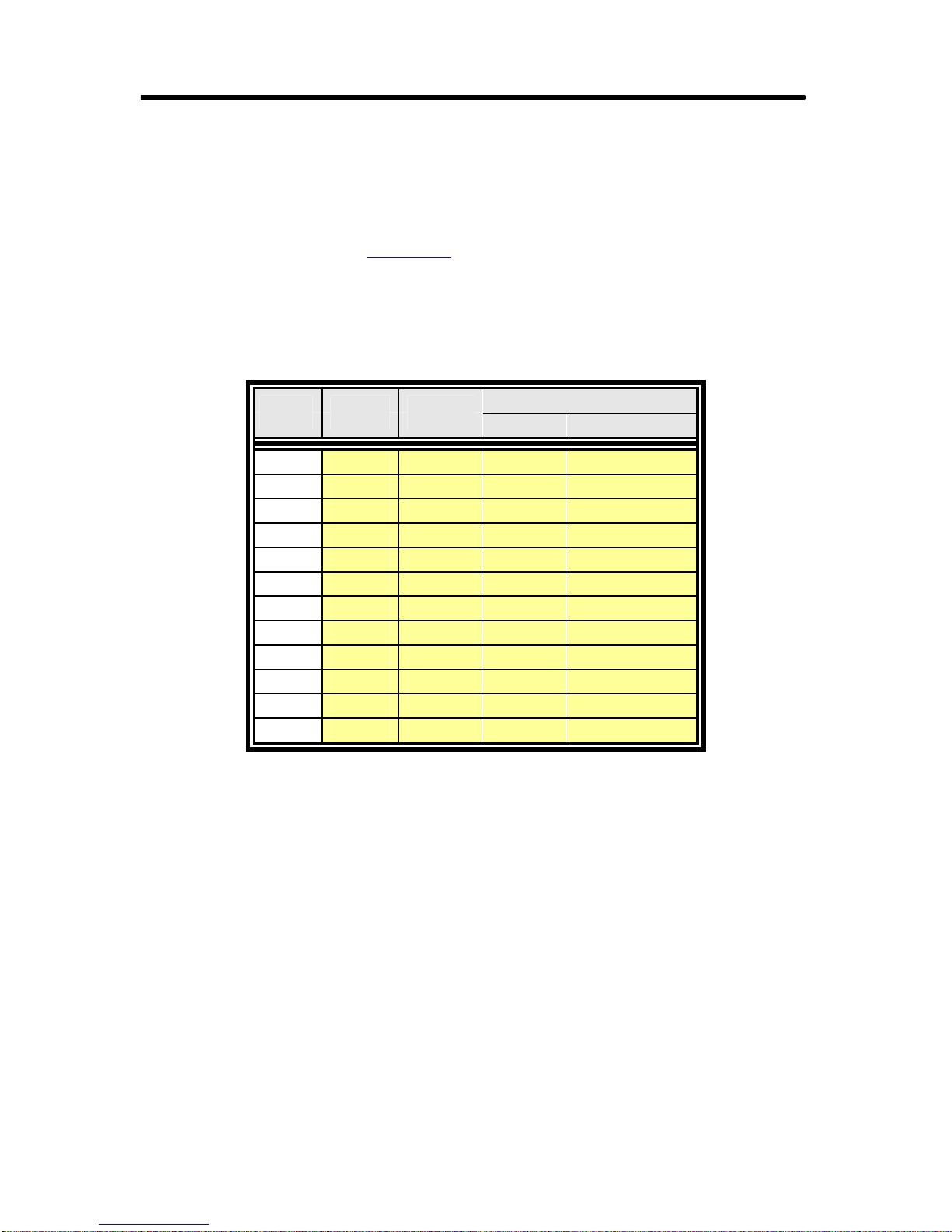

Figure 1-9 Capture Buffer and Display Memory

Video Image

(Input)

Source

Rectangle

Video Playback

Once the incoming digitized video data has been placed into the capture

buffer, the playback engine can retrieve it and incorporate it into the

display output stream. The playback engine can up-scale (zoom) the

contents of the video capture buffer before incorporating the capture

image into the output stream. The image may either be made to fill the

entire screen at the current resolution, or occupy a “window” within the

larger output display. The window may be of arbitrary size and located on

any pixel boundary. Color keying may be used to create non-rectangular

windows, and/or to superimpose a graphics overlay on the video image.

Display

Memor

Crop

&

Scale

Capture

Buffer

Scale

&

Pan

Screen Display

(Output)

Video

1-14 General Information

Rastergraf

Video Processing

Digitized video images in YUV format may be transferred from the

capture buffer to host memory by the Topaz/Stratus/Garnet acting as a

DMA PCI bus master. Once in host memory, the video data may be

archived for retrieval and display at a later time. Alternatively, the host

CPU can perform a color space transform on the YUV data or extract the

luminance in order to generate an 8-bit gray-scale image. Image

enhancement algorithms may be applied in surveillance or monitoring

applications, or edge-detection algorithms in automated (robotic) process

control applications.

Figure 1-10 Video Processing Data Path

NTSC/PAL/SECAM

Video Source

(Camera, VCR, etc.)

Host Processor

Stratus

PCI bus

Video Data

Host

Storage

Processing Task

General Information 1-15

Rastergraf

1.4 Bt835 NTSC/PAL/SECAM Digitizer

The Topaz/Stratus/Garnet provides a Conexant Bt835 video-capture

processor, a single-chip decoding and filtered scaling solution for VCRs,

cameras, and other sources of composite or component (S-Video or Y/C)

video. It integrates video digitization, auto NTSC/PAL format detect and

gain control, synchronization, 2H adaptive Y/C separation (comb filter),

horizontal and vertical filtered down-scaling, user programmable peaking

filter, and VBI data pass-through functions. An internal loopback can be

enabled by software to connect the Composite Video Output to a

Composite Video Input for testing

Using mixed signal and DSP circuitry, the Bt835 converts square pixel

and CCIR601 resolution analog S-Video, NTSC, PAL, and SECAM baseband signals composite video into a scaled to YCrCb digital video stream

An input multiplexer allows the user to select between four composite

input channels or an S-Video input. Hue, saturation, brightness and

contrast controls provide added flexibility to enhance the appearance of

the decoded image. Cropping and scaling can shrink the input image to no

more than is needed for display. This reduces the bandwidth requirement

of the capture and playback engines, leaving more time for graphics

drawing and display refresh. A minimum scale factor of 0.071 allows a

full-resolution video image to be reduced to icon size.

Figure 1-11 Bt835 Video Digitizer Block Diagram

Chroma

Demod

OE

PWRDN

CIN

C

A/D

C Interface

2

I

Clock Interface

Output Interface

LVT TL

MUX0

MUX1

MUX2

MUX3

RST

SDA

C

2

I

I2CCS

SCL

CLKx1

CLKx2

Clocking

CCVALID

QCLK

HRESET

VRESET

ACTIVE

VACTI VE

FIELD

CBFLAG

Video Timing Control

VALI D

GPIO[7:0]

DIG_CLK

VD[7:0]

DIG_V

DIG_H

AGC and

Sync Detect

Input Interface

Y/C Separation and

Chroma Demodulation

Video

Video Scaling

and Cropping Adjustments

JTAG Interface

TRST

REFOUT

AGCCAP

Y

A/D

Oversampling

Low-Pass Filter

Y/C

GPIO Port

Digital Video

Input Formatting

JTAG

TDI

TCK

TMS

Separation

Contrast, Saturation,

and Brightness

Adjust

Horizontal and

Vertical Filtering

and Scaling

Digital Video

Output Formatting

TDO

VD[7:0]

VD[15:8]

1-16 General Information

1.5 AD9882 RGBHV/DVI Digitizer

The AD9882 is a complete 8-bit 140 MSPS monolithic analog interface

optimized for capturing RGB graphics signals. Its 140 MSPS encode rate

capability and full-power analog bandwidth of 300 MHz supports

resolutions up to SXGA (1280 x 1024 at 75 Hz).

The AD9882’s on-chip PLL generates a pixel clock from HSYNC. Pixel

clock output frequencies range from 12 to 140 MHz. PLL clock jitter is

500ps p-p typical at 140 MSPS. The AD9882 also offers full sync

processing for composite sync and sync-on-green (SOG) applications.

The AD9882 also contains a DVI 1.0 compatible receiver and supports

display resolutions up to SXGA (1280 x 1024 at 60 Hz). The receiver

operates with true color (24 bit) panels and also features an intrapair skew

tolerance of up to one full clock cycle.

Figure 1-12 AD9882 High Speed Digitizer Block Diagram

Rastergraf

R

AIN

G

AIN

B

AIN

SOGIN

HSYNC

FILT

VSYNC

SCL

SDA

A

R

X0+

R

X0–

R

X1+

R

X1–

R

X2+

R

X2–

R

XC+

R

XC–

R

TERM

DDCSCL

DDCSDA

MCL

MDA

ANALOG INTERFACE

CLAMP

CLAMP

CLAMP

PROCESSING AND

SERIAL REGISTER AND

0

POWER MANAGEMENT

DIGITAL INTERFACE

RECEIVER

SYNC

CLOCK

GENERATION

DVI

HDCP

AD9882A

REF

R

8

A/D

A/D

A/D

8

8

8

OUT

G

8

OUT

B

8

OUT

DATACK

HSOUT

VSOUT

SOGOUT

R

OUT

G

OUT

B

OUT

DATACK

DE

HSYNC

VSYNC

MUXES

8

8

8

REFBYPASS

R

OUT

G

OUT

B

OUT

DATACK

HSOUT

CSOUT

SOGOUT

DE

05123-001

General Information 1-17

Rastergraf

1.6 Flexible Display Support

The graphics boards support a variety of displays, including LVDS and

DVI Flat Panels, Analog RGB (VGA) Monitors and Video Monitors. This

enables it to be easily incorporated into a wide variety of applications. .

Although at a reduced display size, the graphics boards can drive two

independent displays. One path is dedicated to RGB/DVI/LVDS displays

and the other to RGB/TV/LVDS displays. Remember that performance

will be compromised because there is only one drawing engine.

Figure 1-13 Display Channels

Panel Controller

Display

Display

Processor 1

Processor 1

Panel Controller

LVDS1

LVDS1

LVDS2

LVDS2

CRT Controller

Display

Display

Processor 2

Processor 2

CRT Controller

DAC

DAC

TV

TV

Encoder

Encoder

Digital out

Digital out

RGB

RGB

TV Out

TV Out

There are two independent display controllers inside SM731: The Panel

Controller also referenced as the Primary Controller and the CRT

Controller also referred to as the Secondary Controller. Because of this,

SM731 is able to drive two screens with different images, from separate

frame buffers and at independently programmable timing and resolution.

Furthermore, the LCD panels can be programmed to display images from

either controller, with some restrictions. The Digital Interface can drive

data from either the Panel Controller or the CRT Controller, just like the

LVDS2 interface. The LVDS1 interface is hardwired to drive data from

the Panel Controller (primary display). If the digital interface (which goes

to the external DVI encoder and the external Ch 2 VGA DAC) and

LVDS2 interface are both turned on to drive the single pixel panels, their

data source has to be the same either from the Panel controller or CRT

controller. There will be no restriction if only one interface is on for single

pixel panel or LVDS2 is used for double pixel panel.

See Section 5.2

combinations. There are several pages of diagrams that illustrate the

amazing flexibility of the SM731 display modes.

1-18 General Information

for more information about the possible display

1.6.1 TV Display

The Topaz/Stratus/Garnet supports base-band TV display output in either

NTSC or PAL video formats. Both composite and S-Video (Y/C) are

available.

The SM731 TV Encoder is somewhat limited in that it only allows 480

line output in NTSC mode. If your image is different from that, then you

have to use the scaler to down- or up-size the image accordingly. Use of

the scaler will affect the overall throughput of the chip and can limit the

display size and video input pixel rates.

1.6.2 Analog RGB Displays

The boards are able to support display resolutions from 640 x 480 (VGA)

up to 1600 x 1200 at up to 24 bpp. The Topaz/Stratus/Garnet can support a

secondary VGA port, in which case both ports should be limited to 1024 x

768. The Secondary VGA output uses the spare pins on the DVI-I front

panel connector or can be specified at order time to use the rear panel DVI

output pins.

Rastergraf

The secondary VGA DAC port is driven by the “Flat Panel” display

controller section of the SM731. Displays ranging up to 1024 x 768 are

practical when both channels are active. Some screen refresh-related

artifacts may appear when a larger display format is used due to

bandwidth limitations in the SM731.

1.6.3 STANAG 3350 A-C (Topaz/Duros)

STANAG Class A 875 Line, Interlaced

STANAG Class B 625 Line, Interlaced

STANAG Class B 525 Line, Interlaced

In the case of STANAG output, the video input multiplexer PLD is

“stolen” in order to generate the special timing modes required for

STANAG. For this reason, STANAG output automatically disables video

input. In addition, the secondary VGA DAC is also “stolen”. It is wireOR’d as an additional current source into the primary VGA output to

generate the sync and blanking levels required by STANAG. Thus, you

also lose the second VGA port. However, the STANAG implementation is

extremely good, even including negative (below ground) sync. Properly

programmed (using Rastergraf software) TopazPMC/1 and Duros boards

are highly compliant to STANAG 3350 A-C in all aspects.

General Information 1-19

Rastergraf

1.6.4 Flat Panel Displays

The graphics boards support 24-bit-per-pixel Flat Panel displays with

either dual LVDS channels (1024 x 768 max) or using an external encoder

connected to the Digital Out (see figure above), a single DVI channel

(optional on Tropos and Duros). LVDS is available only via the PMC Pn4

rear panel I/O connector for all boards except Topaz, which has a front

panel connector option as well.

1.6.4.1 DVI

The Topaz/Stratus/Garnet (optional on Tropos/Duros) is supplied with a

DVI compliant transmitter. It provides high quality 24-bit true color

digital output over twisted pair cables up to 3 meters in length. This length

may be increased by using shielded twin-ax or fiber-optic cables. Displays

ranging up to 1600 x 1200 are supported when best quality cables are

used.

The DVI serializer is driven by the “Flat Panel” display controller section

of the SM731. Three TMDS data channels send data at 1.65 Gbps per

channel. Connections are made either through the front panel DVI-I

connector or the rear panel I/O (PMC Pn4) as specified at order time.

Figure 1-14 DVI Flat Panel Output Block Diagram

1.6.4.2 LVDS

The LVDS interfaces can be used to drive two independent panels, one

displaying data from the Primary controller and the other displaying data

from the Secondary controller. They can also be combined to drive a

single, two pixels per clock, high-resolution panel. Each LVDS block

compresses 24 bits of RGB data and 4 bits of LCD timing into four

differential wire pairs, up to 392 MB per second at a maximum clock rate

of 112 MHz. A fifth differential pair transmits the interface clock. This

1-20 General Information

Rastergraf

way, each LVDS block can drive one SXGA+ panel (1400x1050x24

@60Hz). The LVDS1 Interface is hardwired to Panel Controller

(Primary). It can be programmed to drive 18 or 24 bpp panels, and, if used

in conjunction with the LVDS2 Interface, it can be used to drive a two

channel, two pixels per clock panel of up to QXGA size (2048x1536).

Figure 1-15 LVDS Flat Panel Output Block Diagram

4

Data

TxOut0+

TxOut1+

TxOut2+

TxOut3+

TxCLKOu

Pairs

-

-

-

-

LVDS

+

clock

-

Rxln0+

-

Rxln1+

-

Rxln2+

-

Rxln3+

1

-

RxCLKl

+

RxCLKOu

-

RxOut

RxOut

RxOut

RxOut

RxOut

RxOut

R[7:0]

G[7:0]

B[7:0]

HYSNC

VSYNC

DE

FPSC

TFT LVDS Panel

General Information 1-21

Rastergraf

1.7 Front and Rear Panel I/O Options

The Topaz/Stratus/Garnet boards support front-panel I/O as well as rearpanel I/O via PMC Pn4. Not all hosts support rear-panel I/O. Those that

do oftentimes have poorly routed traces from the PMC Pn4 connector to

the host backplane connector, which makes them unsuitable for high

frequency applications, especially LVDS and DVI. Check the host

(carrier) documentation to determine what support is provided before

considering rear panel I/O as an option.

Depending on the board, several input and output streams and connections

are possible both to front panel connectors as well as the rear panel I/O

(Pn4) connector.

Figure 1-16 Front and Rear Panel I/O Options for Topaz

SM731

LVDS

Outputs

Bt835/

AD9882

Analog

Video In

and SM731

Video Out

THine

THC63DV164

DVI Encoder

Jumper

Networks

RP11/13/15/19

0 - ohm Network

RP10/12/14

0 - ohm Network

RP16/18 0 - ohm

Network

RP51 0 - ohm

Network

RP54 0 - ohm

Network

RP55 0 - ohm

Network

Connectors

VGA and DVI Connectors

VGA pins

P4 Pin Group 3

P4 Pin Group 1

MDR Connectors

P4 Pin Groups 4 & 5

DVI Connector

Spare pins

DVI Connector

DVI pins

P4 Pin Group 2

Jumper

Networks

RP61 0 - ohm

Network

RP62 0 - ohm

Network

RP53 0 - ohm

Network

RP52 0 - ohm

Network

RP60 0 - ohm

Network

RP57 0 - ohm

Network

RP56 0 - ohm

Network

RP63 0 - ohm

Network

SM731

RGB DAC

Primary

VGA

AD9882

DVI

Digitizer

ADV7120/3

RGB DAC

Secondary

VGA

1-22 General Information

Figure 1-17 Front and Rear Panel I/O Options for Stratus

Rastergraf

Bt835/

AD9882

Analog

Video In

and SM731

Video Out

THine

THC63DV164

DVI Encoder

Jumper

Networks

RP50 0 - ohm

Network

RP51 0 - ohm

Network

RP51 0 - ohm

Network

RP55 0 - ohm

Network

Connectors

VGA and DVI Connectors

VGA pins

Rear Panel VGA pins

MDSM Connector

Rear Panel Video I/O pins

DVI Connector

Spare pins

DVI Connector

DVI pins

Rear Panel DVI pins

Jumper

Networks

RP61 0 - ohm

Network

RP62 0 - ohm

Network

RP53 0 - ohm

Network

RP52 0 - ohm

Network

RP60 0 - ohm

Network

RP57 0 - ohm

Network

RP56 0 - ohm

Network

RP63 0 - ohm

Network

SM731

RGB DAC

Primary

VGA

AD9882

DVI

Digitizer

ADV7123

RGB DAC

Secondary

VGA

Figure 1-18 Front and Rear Panel Output Options for Tropos

Jumper

Networks

RP61 0 - ohm

Network

RP62 0 - ohm

Network

SM731

RGB DAC

Primary

THine

THC63DV164

DVI Encoder

Jumper

Networks

RP51 0 - ohm

Network

RP55 0 - ohm

Network

Connectors

VGA and DVI Connectors

VGA pins

Rear Panel VGA pins

DVI Connector

DVI pins

Rear Panel DVI pins

VGA

General Information 1-23

Rastergraf

Figure 1-19 Rear Panel I/O Options for Garnet

Jumper

Networks

RP62 0 - ohm

Network

RP52 0 - ohm

Network

RP56 0 - ohm

Network

RP63 0 - ohm

Network

Bt835/

AD9882

Analog

Video In

and SM731

Video Out

THine

THC63DV164

DVI Encoder

Jumper

Networks

RP51 0 - ohm

Network

RP55 0 - ohm

Network

Connectors

Rear Panel VGA pins

Rear Panel Video I/O pins

Rear Panel DVI pins

Figure 1-20 Rear Panel Output Options for Duros

SM731

RGB DAC

Primary

VGA

AD9882

DVI

Digitizer

ADV7120

RGB DAC

Secondary

VGA

THine

THC63DV164

DVI Encoder

Jumper

Networks

RP55 0 - ohm

Network

Connectors

Rear Panel VGA pins

Rear Panel DVI pins

Jumper

Networks

RP62 0 - ohm

Network

SM731

RGB DAC

Primary

VGA

1-24 General Information

1.8 Software Support

Rastergraf software support is available for Linux, VxWorks, and

Windows. Please consult Rastergraf for specifics, as all packages are not

available on all systems. In general, we have:

• Windows 2K/XP Graphics Drivers with DirectX 8

• X Windows X11R6 (XFree86 Version 4.3) for Linux

• VGA BIOS

• SDL Graphics Subroutine Library for VxWorks and Linux

• VxWorks WindML (layered on top of SDL)

• Built-in Test (BIT) routines callable by CPU (layered on top of SDL)

1.9 Additional Details About SDL

Rastergraf

SDL is a graphics library designed to be a device-independent

programming interface. SDL is ideally suited to demanding board level

and embedded systems applications. Drivers are available for selected host

CPU boards and operating systems. SDL is supplied in object library

format, which means that its target code size can be controlled by limiting

the number of functions used in a given application. SDL has been

General Information 1-25

Rastergraf

designed to run on any CPU and operating system that uses linear

addressing and is supported by the GNU C compiler and linker. SDL is

available in source for an additional cost – please contact Rastergraf sales.

SDL is easy to use. It includes a complete set of graphics primitives that

interface to the SM731 graphics controller’s accelerated functions. SDL

also supports Stratus’ video capture capabilities. All graphics primitives

are drawn as single pixel lines. Rectangles, polygons, circles, ellipses, and

chords can be filled with a solid color or stipple patterns.

Complete information about

Library C Reference Manual that is available for download from our

web site at http://www.rastergraf.com.

SDL Feature Summary

• Solid (thin and wide) and dashed lines, polylines, and rectangles

• Pixblits to/from the display and host memory

• Filled and hollow polygons, ellipses, circles, sectors, and chords

• Solid and Pattern Fills – Pixel Processing

• Proportional and Fixed Width Fonts

• Clipping Rectangle and Logical Origin

• Video Capture Extensions

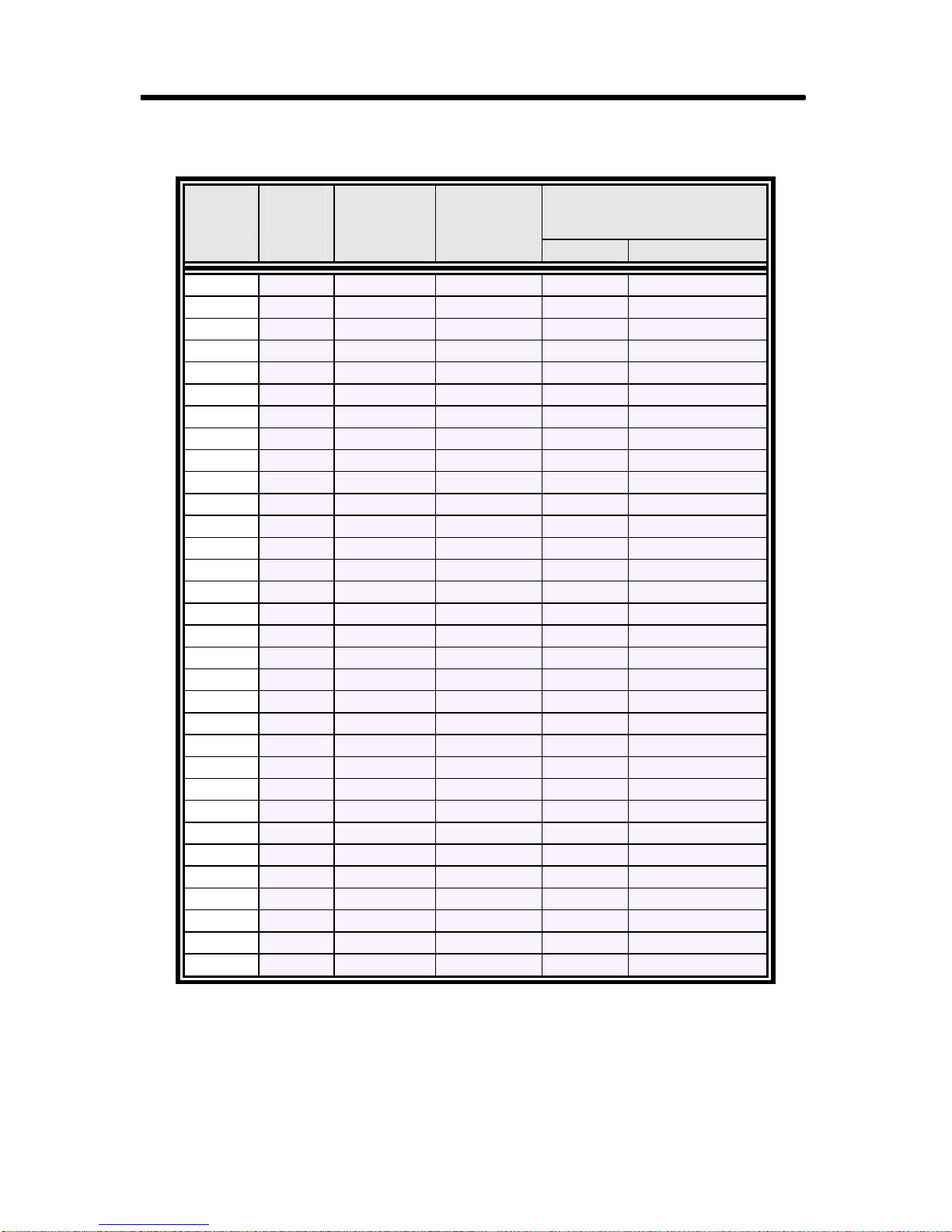

Table 1-2 SDL Functional Summary

Feature Supported

VGA 640x480 to 1600x1200

8/16/24 bpp

DVI Output

SDL is contained in the Standard Drawing

Yes

Yes

Yes

Sync On Green

Video Capture - NTSC/PAL

Video Capture - (RGB) via AD9882

Video Capture - (mono) via AD9882

TV Out - NTSC/PAL

STANAG-A Timing

1-26 General Information

Yes

Yes

Yes

Yes

Yes

Yes

1.10 Additional References

Rastergraf documentation includes (hardware) User’s Manuals and

Standard Drawing Library (SDL) Manual. You can obtain some technical

literature from the Rastergraf web page (http://www.rastergraf.com

that web links do change, so if the links given below are broken, just go

the manufacturer’s main web page and start your way in.

Silicon Motion SM731 Graphics Accelerator:

Contact Rastergraf (support@rastergraf.com)

Conexant Bt835 Audio/Video Decoder (now called CX25835):

http://www.conexant.com/products/entry.jsp?id=54

THine THC63DV164 DVIencoder:

Contact Rastergraf (support@rastergraf.com)

Analog Devices AD9882 RGB/YUV/DVI Digitizer and ADV7123 DAC:

AD9882: http://www.analog.com/en/prod/0,,765_806_AD9882A%2C00.html

Rastergraf

). Note

ADV7123: http://www.analog.com/en/prod/0%2C2877%2CADV7123%2C00.html

1386-2001 and 1386.1-2001:

IEEE Standard for a Common Mezzanine Card Family: CMC and IEEE

Standard Physical and Environmental Layers for PCI Mezzanine Cards

http://shop.ieee.org/ieeestore/Product.aspx?product_no=WE94922

The PCI Local Bus 2.3 Specification:

http://www.pcisig.com/specifications/conventional/conventional_pci_23/

Graphics Textbooks

Fundamentals of Interactive Computer Graphics

Addison Wesley, 1993. Foley and Van Dam

Principles of Interactive Computer Graphics

McGraw-Hill, 1979 Newman and Sproull

General Information 1-27

Chapter 2

Specifications

Rastergraf

Specifications 2-1

Rastergraf

2.1 General

Graphics Processor: Silicon Motion SM731 2D/3D High Performance 128-Bit

Graphics Processors. Integrated on the same Multi-Chip

Module (MCM) are the memory, LVDS encoders, and TV

encoder.

The SM731 features an internal 235 MHz RAMDAC. It

has a 256 entry Look Up Table (LUT), which is most

commonly used for conversion of 8-bit pixels into full 24bit RGB pixels. The RAMDAC has a programmable

four-color bit-mapped 64 x 64 cursor. It supports VGA and

common non-interlaced displays ranging from 640 x 480

up to better than 1600 x 1200. Signature registers enable

display analysis for end-to-end testing.

The pixel size can be 8, 15, 16, or 24 bits. For 15 and 16

bpp, the pixel is divided into Red, Green, and Blue: 5:5:5 or

5:6:5. For 24 bpp, pixel is divided into Red, Green, and

Blue and the data is ordered as packed pixels in memory.

Scroll, Pan, and Zoom: Scroll - single line (smooth scroll).

Pan - anywhere on 16 byte boundaries

Zoom: horizontal: 2, 4, 8, 16, vertical: 2, 3 ,...,15, 16

Display Memory: Display memory is 16 MB of 64-bits/word, byte

addressable, no-wait state SDRAM provides eight pages of

1600 x 1200 using 8-bit pixels, four pages using 16-bit

pixels, or two pages using 24 bpp packed pixel mode.

EEPROM Memory: Flash EEPROM contains the VGA BIOS.

Digital Output: Digital (DVI) output uses a THine (THC63DV164 DVI

(Optional on Tropos) encoder connected to the SM731 flat panel output, which

supplies 24-bit TTL level RGB plus HV. It samples and

multiplexes the data and drives four differential pairs.

Because of the high frequency nature of the TMDS signals,

it is vital that matched length, shielded pair cable be used

for DVI connections.

2-2 Specifications

Rastergraf

DVI-I Connector: The DVI-I connector supplies both the digital DVI signals

and dual analog VGA. Rastergraf can supply an adapter

that allows a standard VGA cable to be connected to the

DVI-I connector. A breakout cable can split out the DVI

and the two VGA channels.

Composite Video Signal: A jumper can be installed to select Sync-On-Green

operation on boot-up. The signal has the following

approximate values:

1 Volt peak to peak consisting of:

660 mV Reference White +

54 mV Reference Black +

286 mV Sync Level

Power-management: With the proper software, the SM731 can power-down

unused functions.

Fuse Element: The +5V supplied to the front panel connectors is protected

by a Positive Temperature Coefficient (PTC) resistor. It

resets automatically when an overload is removed.

PCI Bus Access: Programmable Bus Address Registers (BARs) in the

SM731 map control and drawing engine registers, and