RAMTRON FM6124-QG, FM6124 Datasheet

Preliminary

This is a product that has fixed target specifications but are subject Ramtron International Corporation

to change pending characterization results. 1850 Ramtron Drive, Colorado Springs, CO 80921

(800) 545-FRAM, (719) 481-7000

Rev. 1.0 http://www.ramtron.com

April 2008 Page 1 of 53

FM6124

Event Data Recorder with F-RAM

OVERVIEW

The FM6124 is an Event Data Recorder with F-RAM

memory that provides an integrated solution for digital

events monitoring. Li ke P LC d evices, the F M6124 p rovid es

simple device settings and data retrieval allowing easy

system integration to short design-in cycle.

Access to the device is performed through an I2C interface

able to sustain communication speed up to 100kbps. The I2C

interface also provides the ability to place the FM6124 away

from the host system and closer to the equipment and/or

sensors it is intended to monitor. It also allows multiple

devices to share the same I2C bus.

The FM6124 features 12 digital inputs that can be

individually configured to trigger event recording on either a

rising or a falling edge. An on-chip Real Time Clock (RTC)

with calendar provides a timestamp for each event recorded

and can also be used as system clock and calendar. The

event timestamp resolution is one second.

The on-chip 32KBytes F-RAM memory provides

nonvolatile storage for event recording and a portion of it

can also be used for nonvolatile User Data storage. Access

to the User Data is performed like any other I2C memory

device. Up to 32KB F-RAM can be reserved for Events

recording.

F-RAM can be treated as RAM and

reads/writes at the speed of the I2C bus. It also offe rs

effectively unlimited write endurance unlike other

nonvolatile memory technologies.

Recorded events consist of 8 bytes. One byte defines the

event code and the 7 remaining bytes contain timestamp

data. The events are recorded in a circular buffer fashion

and they are retrieved through I2C accessible registers.

The FM6124 can capture and record up to 10K Events every

second if no I

2

C communication in taking place on the I2C

bus. In that case, the Events must last 15µs. During I

2

C

transac ti ons, the de vi c e c an st il l ca p tu r e an d re co rd up to 5K

Events per second having a minimum duration of 25µs.

Other features of the FM6124 include a 16-bit battery

backed-up event counter, an early power fail monitoring

input, and a user programmable 64-bit serial number.

The FM6124 is powered b y a 3.0 to 3.6V supply, can

function over the industrial temperature range, and is

available in a QFP-44 package.

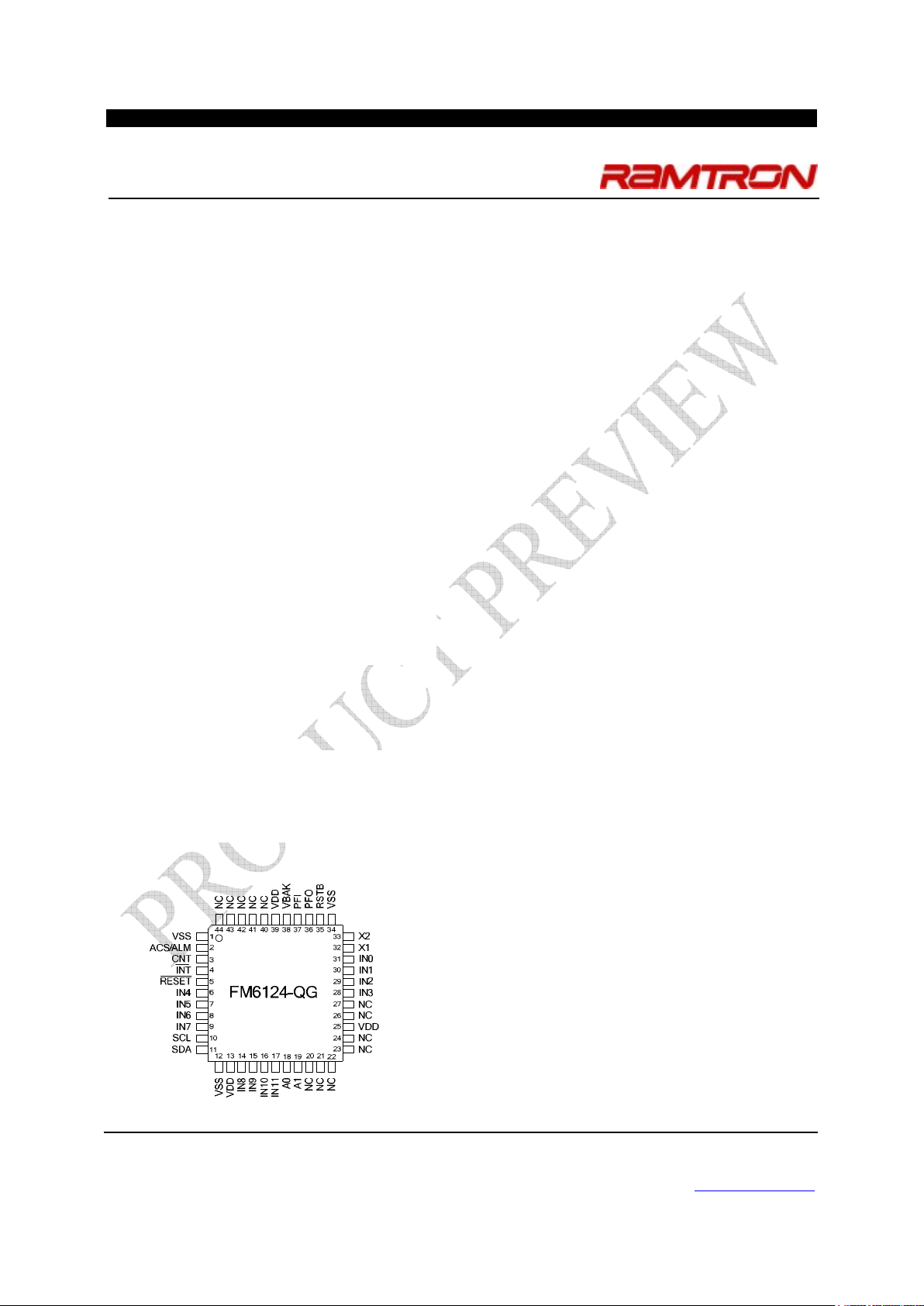

QFP-44

PRELIMINARY PACKAGE PINOUT

FEATURES

Event Monitoring Features

• Continuously Monitor Input State Change

• 12 Digital Events Inputs Pins

• Configurable Events Trigger on Rising/Falling Edge

• Up to 10K Events per second Capture/Record rate

• Event durati on can be as short as 15µS

• RTC Timestamp for each Recorded Event

• I

2

C Interface for Configuration and Data Read/Write

• Configurable F-RAM Segment Size for Event Recording

High Integration Device Replaces Multiple Parts

• Serial Nonvolatile M em ory

• Real-time Clock (RTC) with Alarm

• Low V

DD

Detection Drives Reset

• Watchdog Window Timer

• Early Power-Fail Warning/NMI

• 16-bit Nonvolatile Event Counter

• Serial Number with Write-lock for Secu rity

Ferroelectric Nonvolati l e RAM

• Configurable Size (Up to 24KB) F-RAM for User Data

• Dedicated I

2

C ID for User F-RAM

• Unlimited Read/Write Endurance

• 10 year Data Retention

• NoDelay™ Writes

Real-time Clock/Calendar

• Backup Curre nt u nder 1 µA

• Seconds through Centuries in BCD format

• Tracks Leap Years through 2099

• Uses Standard 32.768 kHz Crystal

• Software Calibration

• Supports Battery or Capacitor Backup

Processor Companion

• Active-low Reset Output for VDD and Watchdog

• Programmable Low-V

DD

Reset Thresholds

• Manual Reset Filtered and Debounced

• Programmable Watchdog Wi ndow Timer

• Nonvolatile Event Counter

• Comparator for Power-Fail Interrupt or Oth er Use

• 64-bit Programmable Serial Number with Lock

Easy to Use Configurations

• Operates from 3.0 to 3.6V

• QFP-44 10x10mm “Green”/RoHS Package

• Industrial Temperature Range -40°C to +85°C

APPLICATIONS

o Activity Monitoring

o Industrial Automation Event Recording

o Environmental Monitoring

o Vehicle & Pedestrian Traffic Counting

o Equipment Use monitoring

o Maintenance scheduling

FM6124 Event Data Recorder

Rev. 1.1

Dec. 2007 Page 2 of 28

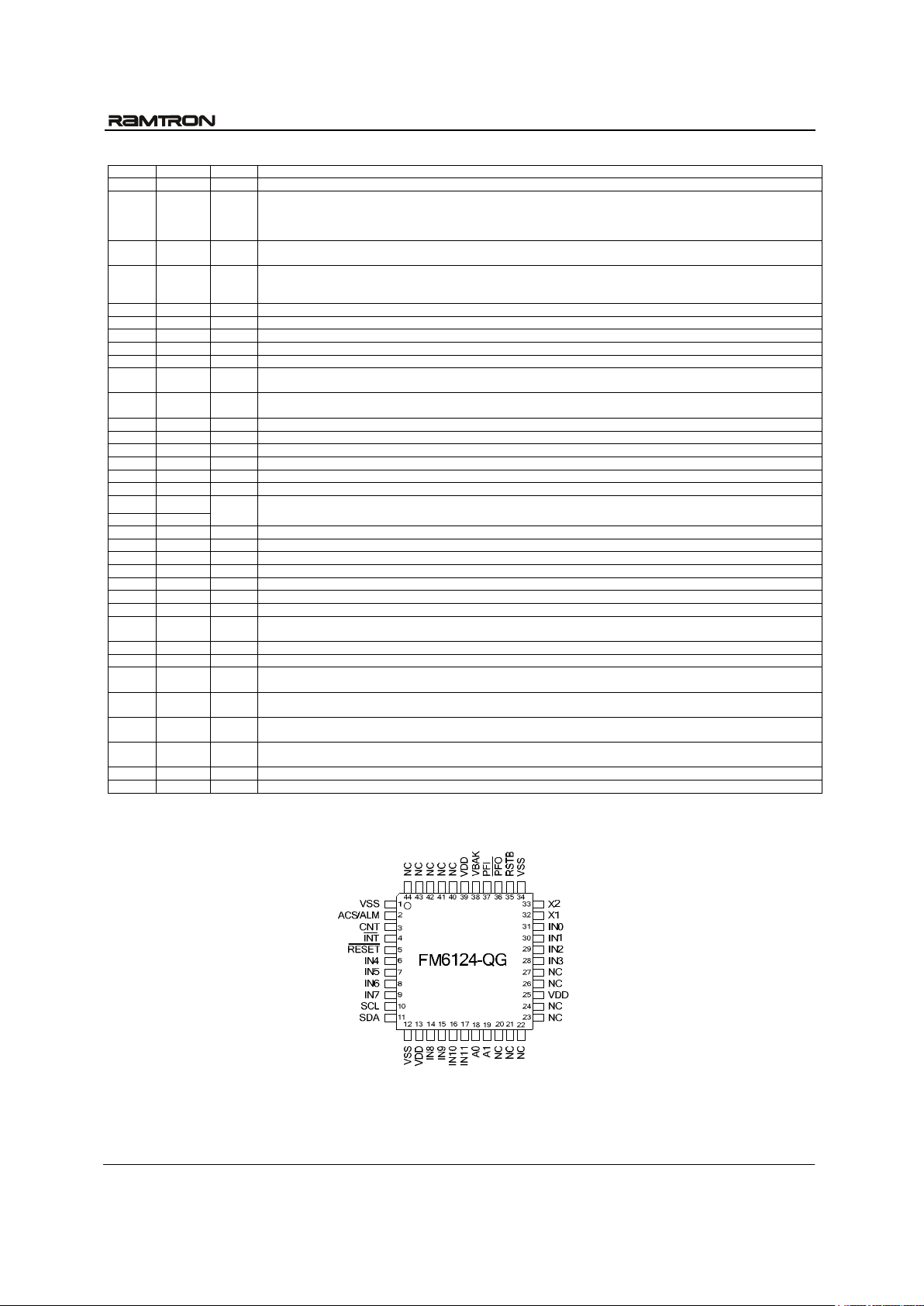

PIN DESCRIPTION

Pin Name I/O Function

1 VSS VSS Ground

2 ACS O

Alarm/Calibration/SquareWave: This is an open-drain output that requires an external pull-up resistor. In normal operation, this

pin acts as the active-low alarm output. In Calibration mode, a 512 Hz square-wave is driven out. In SquareWave mode, the user

may select a frequency of 1, 512, 4096, or 32768 Hz to be used as a continuous output. The SquareWave mode is e ntered by

clearing the AL/SW and CAL bits in register 18h.

3 CNT I

Event Counter Input: This input increments the counter when an edge is detected on this pin. The polarity is programmable and

the counter value is nonvolatile or battery-backed, depending on the mode. This pin should be tied to ground if unused.

4 INT O

Active Low output that can be configured to generate a low level when:

-Event buffer is full

-Activity on event input

5 RESET I Device Reset Input. This active-low input clears all volatile registers. Leave unconnected if not used, pin has internal pull-up.

6 IN4 Event Input Pin 4

7 IN5 Event Input Pin 5

8 IN6 Event Input Pin 6

9 IN7 Event Input Pin 7

10 SCL

Serial Clock: The serial clock input for the two-wire interface. Data is clocked out o f the device on the SCL falling ed ge, and

clocked in on the SCL rising edge. A pull-up resistor is required.

11 SDA

Serial Data/Address: This is a bi-directional pin used to shift serial data and addresses for the two-wire interface. It employs an

open-drain output and is intended to be wire-OR’d with other devices on the two-wire bus. A pull-up resistor is required.

12 VSS VSS Ground

13 VDD Supply Supply voltage

14 IN8 I Event Input Pin 8

15 IN9 I Event Input Pin 9

16 IN10 I Event Input Pin 10

17 IN11 I Event Input Pin 11

18 A0

19 A1

I

Address 1-0: These pins are used to select one of up to 4 devices of the same type on the same two-wire bus. To select the

device, the address value on the three pins must match the corresponding bits contained in the device address.

20-24 NC NC Leave these pins unconnected

25 VDD Supply Supply voltage

26, 27 NC NC Leave these pins unconnected

28 IN3 I Event Input Pin 3

29 IN2 I Event Input Pin 2

30 IN1 I Event Input Pin 1

31 IN0 I Event Input Pin 0

32 X1

32.768 kHz crystal connection. When us ing an externa l oscillator, apply the c lock to X1 a nd a DC mid-leve l to X2 (see Cr ystal

Type section for suggestions).

33 X2 32.768 kHz crystal connection

34 VSS Ground

35 RSTB NC

Reset Out: This active-low output is open dra in with weak pull-up. It is also an input w hen used as a manual reset. This pin

should be left floating if unused.

36 PFO

Early Power-fail Output : This pin is the e arly power-fail outp ut and is typica lly used to drive a microcontroller NMI p in. PFO

drives low when the PFI voltage is <1.5V.

37 PFI

Early Power-fail Input: Typically connected to an unregulated po wer supply to detect an early power failure. This p in must be

tied to ground if unused.

38 VBAK

Backup supply voltage: A 3V battery or a large value capac itor. I f no backup s upply is used, this p in should be tied to V SS a nd

the VBC bit should be cleared.

39 VDD Supply Supply voltage

40-44 NC NC Leave these pins unconnected

QFP-44 PACKAGE PINOUT

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 3 of 53

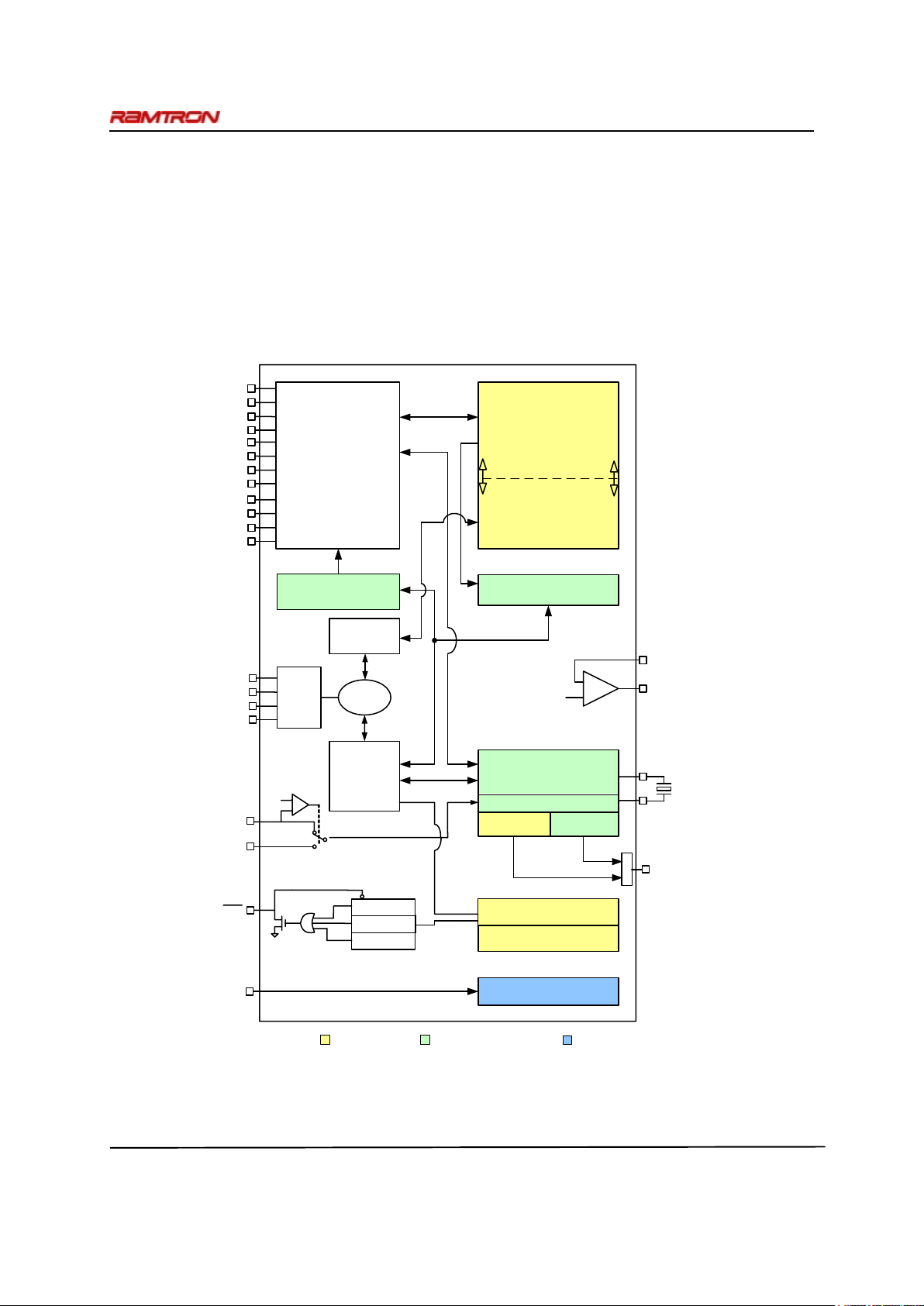

FUNCTIONAL BLOCKS

The functional block diagram of the FM6124 is represented in the figure below. The FM6124 combines the

following:

• 12 input pins individually configurable for Event recording

• Event Buffer memory for event storage implemented as F-RAM

• User accessible F-RAM memory

• User Accessible Real time clock (RTC) with alarm

• MCU co mpanion features such as Eve nt counter, Watchdog T imer, Power Fails Input/Outp ut and

programmable serial number

• I

2

C communication interface supporting two device IDs: one for User-F-RAM (0xA0) and one for

Event Recorder/MCU Companion (0xD0)

I2C

Interface

SDA

A1

RSTB

SCL

VDD

RTC

-

+

RTC Registers

X1

X2

Watchdog

LV Detect

Switched

Power

512Hz/SqW

Battery Backed

Nonvolatile

A0

Battery Backed Event Counter

Alarm

V

SW

NV/BB User Programmable

ManualReset

VBAK

IN4

IN5

IN6

IN7

IN0

IN1

IN2

IN3

IN8

IN9

IN10

IN11

Events Detection and Time

Stamping Unit

Event Recorder Comfiguration

Registers

User Data

F-RAM Zone

F-RAM based

Events Recording

Buffer

0KB

32KB

Adjustable boundary 0KB – 24KB

Event Retrieval Registers

F-RAM Access

Event Recorder

Functions

+

RTC & MCU

companion

Features

I2C ID

Sorting Unit

Serial Number

MCU Companion Features

Registers

AlarmRTC Calibration

CNT

+

-

PFO

PFI

1.5V

External,

User

supplied

32.768KHz

Crystal

ACS

F

IGURE 1.

FM6124 B

LOCK DIAGRAM

FM6124 Event Data Recorder

Rev. 1.1

Dec. 2007 Page 4 of 28

Two-wire (I2C) Interface

The FM6124 employs an industry standard two-wire

(I

2

C) bus that is familiar to man y users. This p roduct

is unique since it incorporates two logical devices in

one chip. Each logical device can be accessed

individually and appear to the system software to be

two separate products. One is the nonvolatile FRAM memory device. It has a Slave Address (Slave

ID = 1010b) that operates the same as a stand-alone

memory device. The second device is Event Data

Recorder and Companion which has a different

Slave Address (Slave ID = 1101b).

By convention, any device that is sending data onto

the bus is the transmitter while the tar get device for

this data is the receiver. The device that is

controlling the bus is the master. The master is

responsible for generating the clock signal for all

operations. Any device on the bus that is being

controlled is a slave. The FM6124 is always a slave

device.

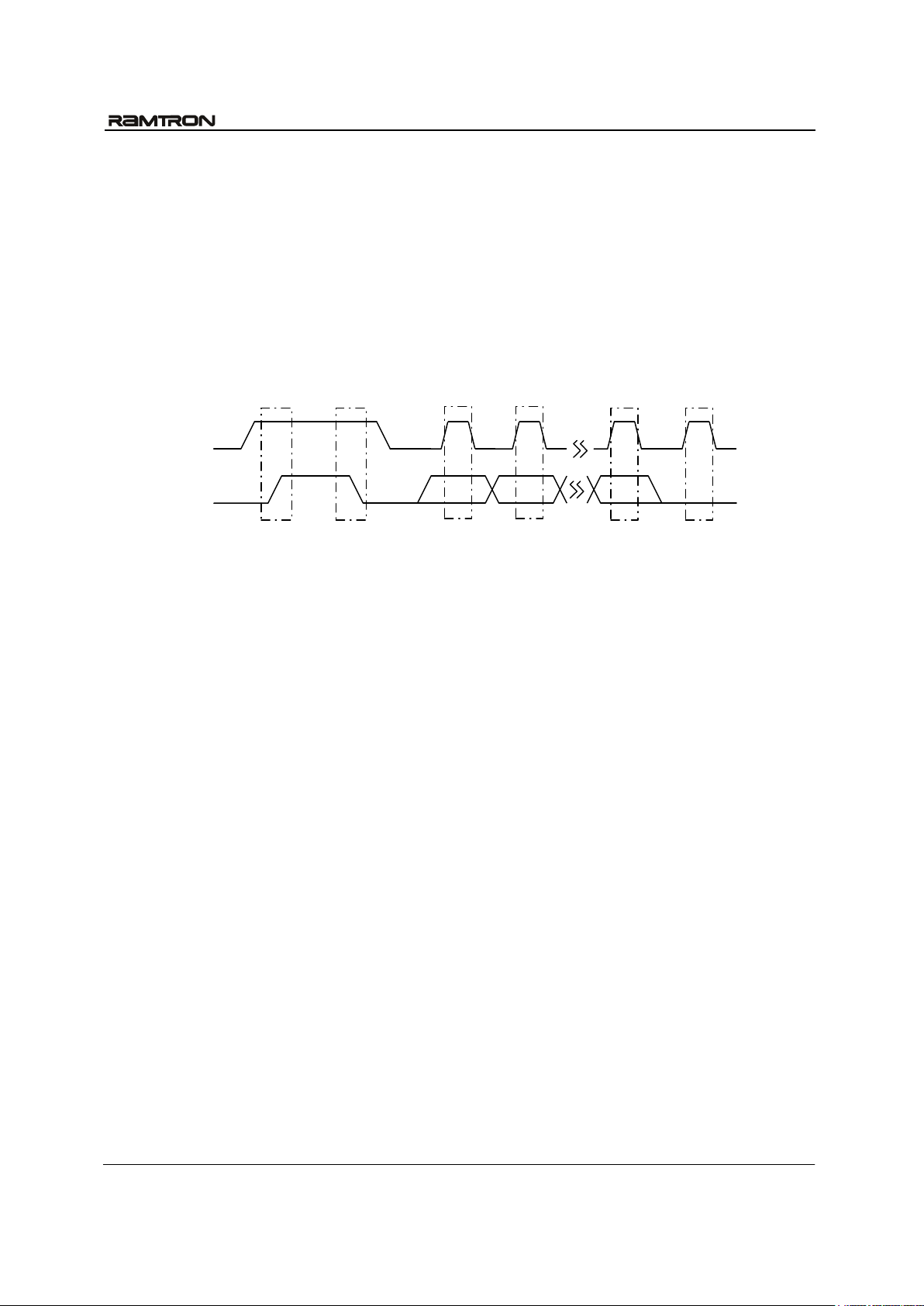

The bus protocol is controlled by transition states in

the SDA and SCL signals. There are four co nditions:

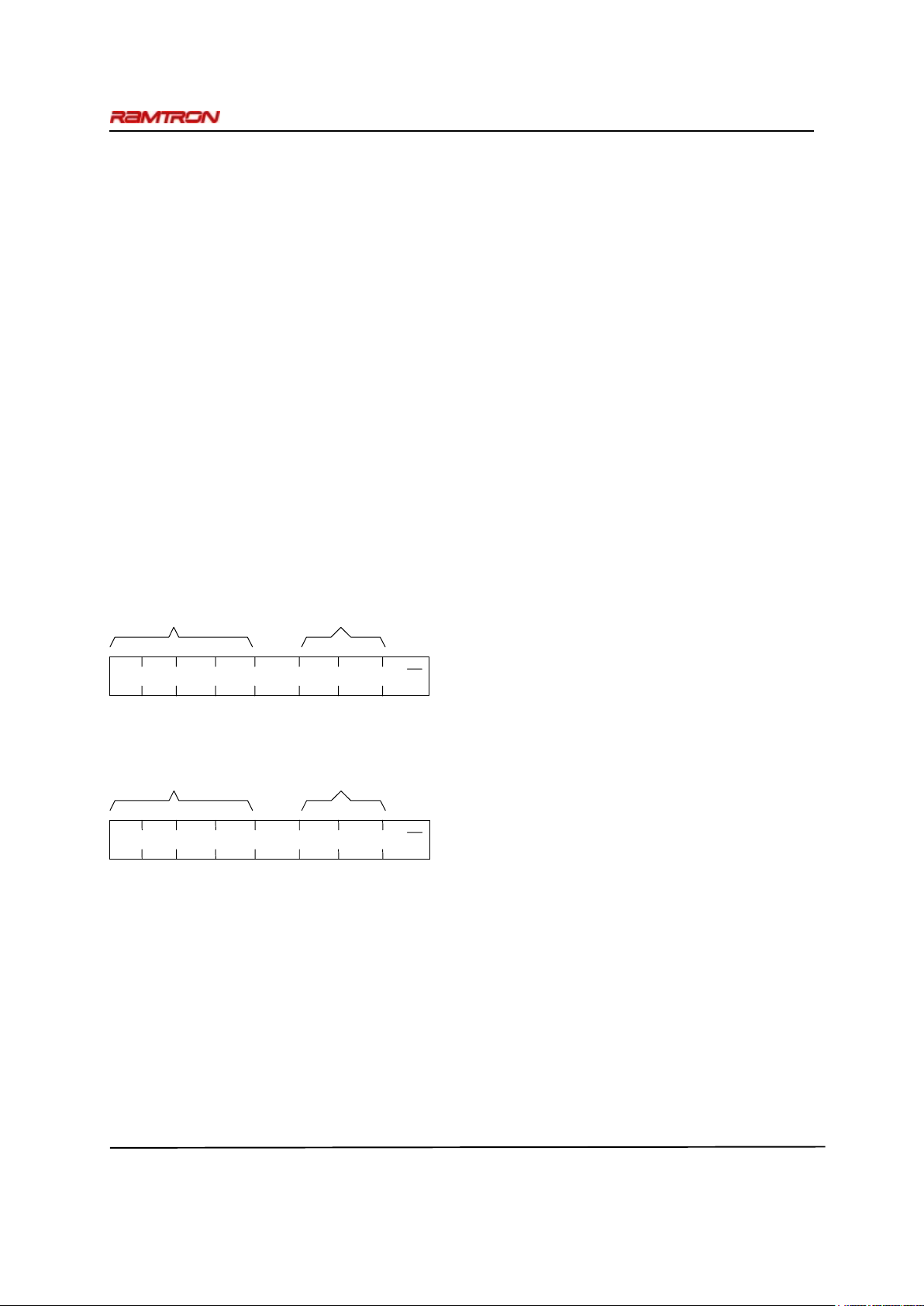

Start, Stop, Data bit, and Acknowledge. The figure

below illustrates the signal conditions that specify

the four states.

Stop

(Master)

Start

(Master)

7

Data bits

(Transmitter)

6

0

Data bit

(Transmitter)

Acknowledge

(Receiver)

SCL

SDA

F

IGURE 2.

I2C B

US CONDITIONS AND TERMINOLOGY

Start Condition

A Start condition is indicated when the bus master

drives SDA from high to lo w while the SCL signal is

high. All read and write transactions begin with a

Start condition. An operation in progress can be

aborted by asserting a Start condition at any time.

Aborting an operatio n using the Start condition will

ready the FM6124 for a new operation.

If the power supply drops below the specified VTP

during operation, any 2-wire transaction in progress

will be aborted and the system must issue a Start

condition prior to performing another operation.

Stop Condition

A Stop condition is indicated when the bus master

drives SDA from low to high while the SC L signal is

high. All operations must end with a Stop condition.

If an operation is pending when a stop is asserted,

the operation will be aborted . The master must have

control of SDA (not a memory read) in order to

assert a Stop condition.

Data/Address Transfer

All data transfers (including addresses) take place

while the SCL signal is high. Except unde r the two

conditions described above, the SDA signal should

not change while SCL is high.

Acknowledge

The Acknowledge (ACK) takes place after the 8

th

data bit has been transferred in any transaction.

During this state the transmitter must release the

SDA bus to allow the receiver to drive it. The

receiver drives the SDA signal low to acknowledge

receipt of the byte. If the receiver does not drive

SDA low, the condition is a No-Acknowledge

(NACK) and the operation is aborted.

The receiver might NACK for two distinct reasons.

First is that a byte transfer fails. In this case, the

NACK ends the current operation so that the part can

be addressed again. This allows the last byte to be

recovered in the event of a communication error.

Second and most common, the receiver does not

send an ACK to deliberately terminate an operation.

For example, during a read operation, the FM6124

will continue to place data onto the bus as long as the

receiver sends ACKs (and clocks). When a read

operation is complete and no more data is needed,

the receiver must NACK the last byte. If the receiver

ACKs the last byte, this will cause the FM6124 to

attempt to drive the bus o n the next clock while the

master is sending a new command such as a Stop.

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 5 of 53

Slave Address

The first byte that the FM6124 expects after a Start

condition is the slave address. As shown in figures

below, the slave address contains the Slave ID,

Device Select address, and a bit that specifies if the

transaction is a read or a write.

The FM6124 has two Slave Addresses (Slave IDs)

associated with two logical devices. To access the

memory device, bits 7-4 should be set to 1010b. The

other logical device within the FM6124 is the Event

Recorder configuration and data access, the real-time

clock and MCU companion. To access this device,

bits 7-4 of the slave address should be set to 1101b.

A bus transaction with this slave address will not

affect the memory in any way. The figures below

illustrate the two Slave Addresses.

The Device Select bits allow multiple device s of the

same type to reside on the 2-wire bus. The device

select bits (bits 2-1) select one of four parts on a twowire bus. They must match the corresponding value

on the external address pins in order to select the

device. Bit 0 is the read/write bit. A “1” indicates a

read operation, and a “0” indicates a write operatio n.

1010XA1A0R/W

Slave ID

Device

Select

76543 21 0

F

IGURE 3. SLAVE ADDRESS - MEMORY

F

IGURE 4. SLAVE ADDRESS –

EDR/C

OMPANION

Addressing Overview – Memory

After the FM6124 acknowledges the Slave Address,

the master can place the memory address on the bus

for a write operation. The address requires two bytes.

The first is the MSB (upper byte). Following the

MSB is the LSB (lower byte) which contains the

remaining eight address b its. The address is latched

internally. Each access causes the latched address to

be incremented automatically. The current address is

the value that is held in the latch, either a newly

written value or the address following the last access.

The current address will be held as long as VDD >

VTP or until a new value is written. Accesses to the

clock do not affect the current memory address.

Reads always use the current address. A random read

address can be loaded by beginning a write operation

as explained below.

After transmission of each data byte, just prior to the

Acknowledge, the FM6124 increments the internal

address. This allows the next sequential byte to be

accessed with no additional addressing externally.

After the last address is reached, the address latch

will roll over to 0000h. There is no limit to the

number of bytes that can be accessed with a single

read or write operation.

Addressing Overview – EDR, RTC & Companion

The Event Recorder, RTC, and Processor

Companion operate in a similar manner to the

memory, except that it uses only one byte of address.

Addresses 00h to 33h corresponds to special function

registers. Attempting to load addresses above 33h is

an illegal condition; the FM6124 will return a

NACK and abort the 2-wire transaction.

Data Transfer

After the address information has been transmitted,

data transfer between the bus master and the

FM6124 begins. For a read, the FM6124 will place 8

data bits on the bus then wait for an ACK from the

master. If the ACK occurs, the FM6124 will transfer

the next byte. If the ACK is not sent, the FM6124

will end the read operation. For a write operation, the

FM6124 will accept 8 data bits from the master then

send an Acknowledge. All data transfer occurs MSB

(most significant bit) first.

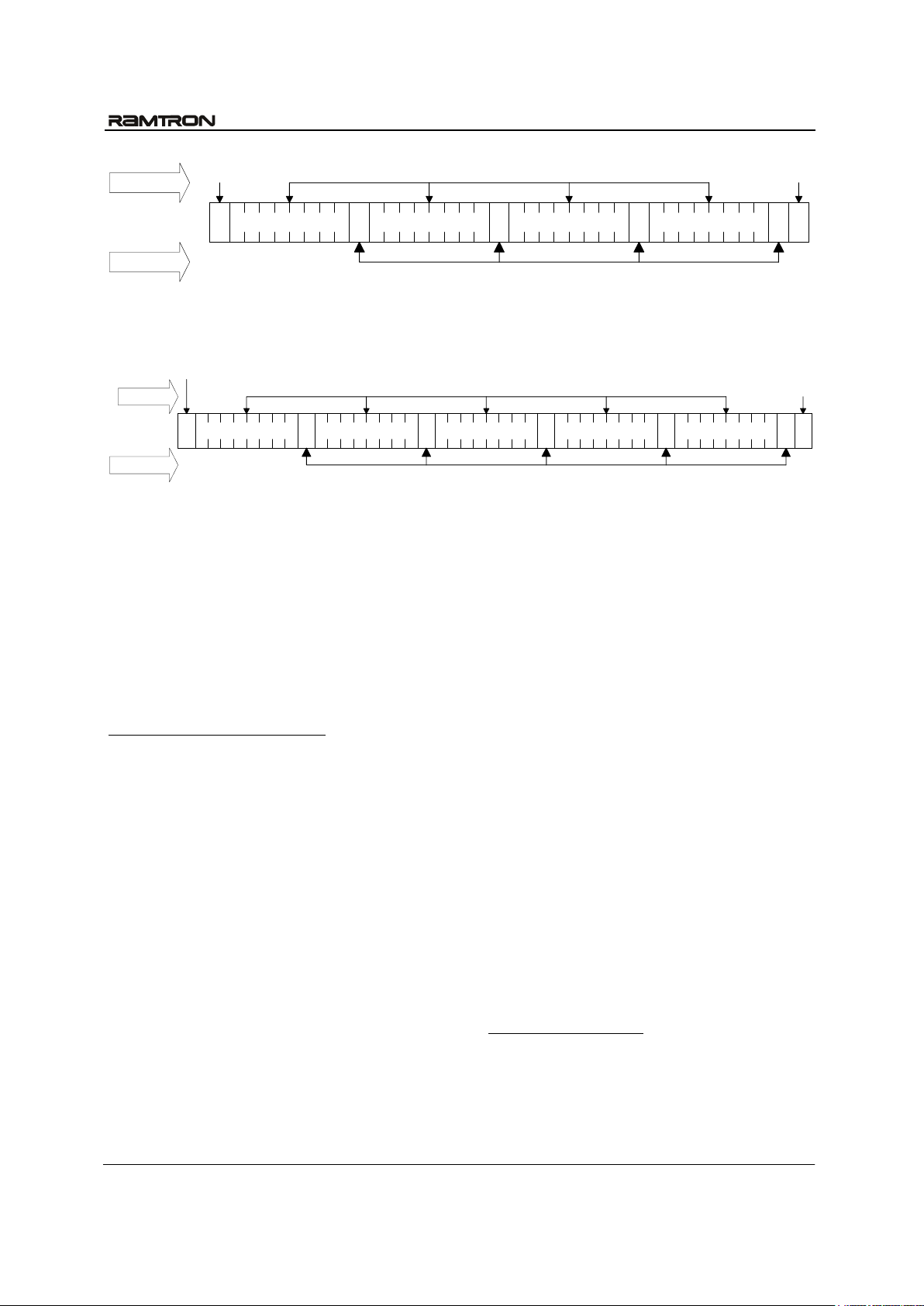

Memory Write Operation

All memory writes begin with a Slave Address, then

a memory address. The bus master indicates a write

operation by setting the slave address LSB to a 0.

After addressing, the bus master sends each byte of

data to the memory and the memory generates an

Acknowledge condition. Any number of sequential

bytes may be written. If t he end of the add ress range

is reached internally, the address counter will wrap

to 0000h. Internally, the actual memory write occurs

after the 8

th

data bit is transferred. It will be complete

before the Acknowledge is sent. Therefore, if the

user desires to abort a write without altering the

memory contents, this sho uld be done using a Start

or Stop condition pr ior to the 8

th

data bit. The figures

that follow illustrate a single - and multiple-writes to

memory.

1

1

0

1

X

A1 A0 R/W

Slave ID

7

6 5

4

3

2

1

0

Device

Select

FM6124 Event Data Recorder

Rev. 1.1

Dec. 2007 Page 6 of 28

F

IGURE 5. SINGLE BYTE MEMORY WRITE

F

IGURE 6. MULTIPLE BYTE MEMORY WRITE

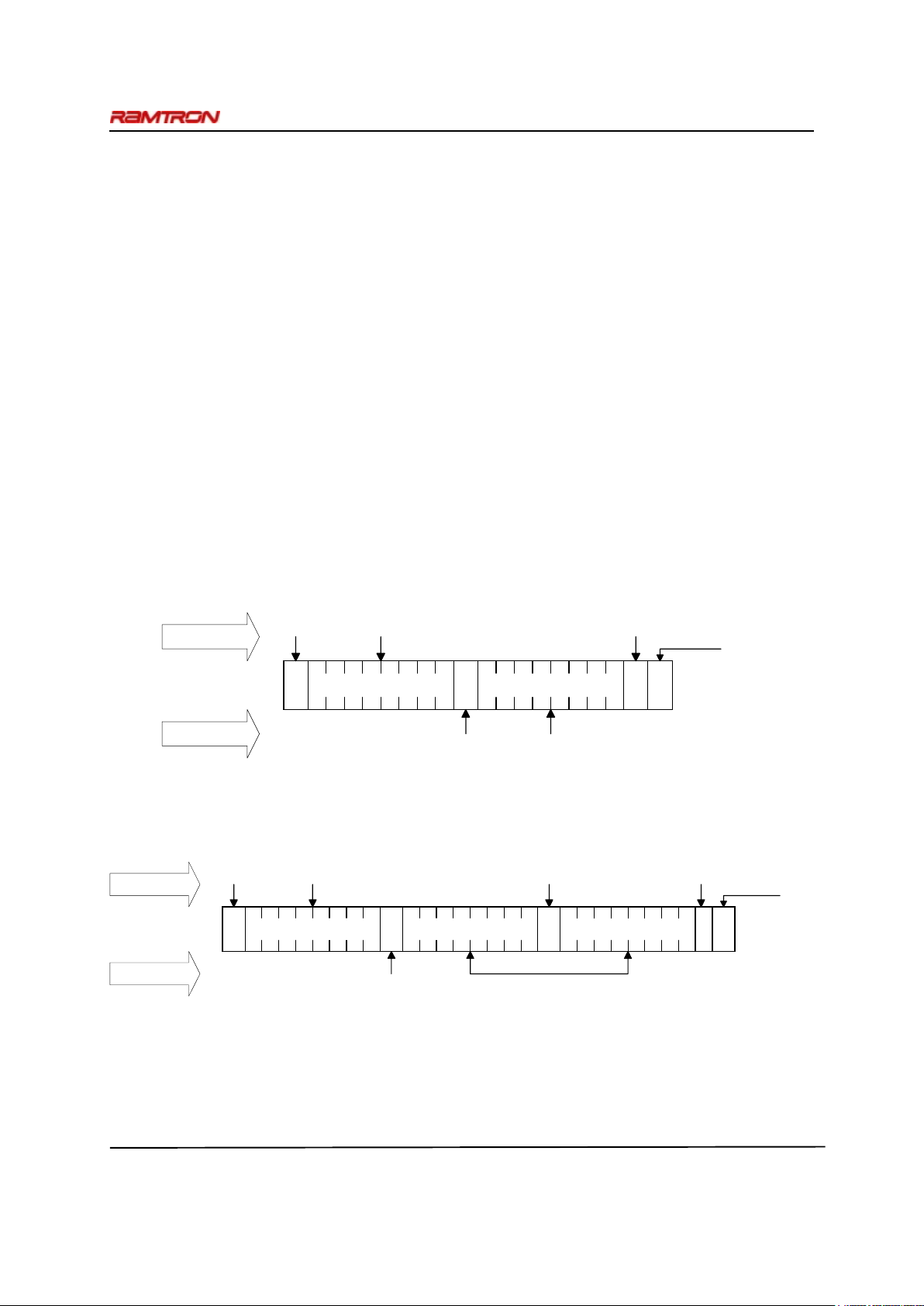

Memory Read Operation

There are two types of memory read operations. They

are current address read and selective address read. In

a current address read, the FM6124 uses the internal

address latch to supply the address. In a selective

read, the user performs a procedure to first set the

address to a specific value.

Current Address & Sequential Read

As mentioned above the FM6124 uses an internal

latch to supply the address for a read operation. A

current address read uses the existing value in the

address latch as a starting place for the read

operation. The system reads from the address

immediately following that of the last ope r a tion.

To perform a current address read, the bus master

supplies a slave addr ess with the LSB set to 1. This

indicates that a read operation is requested. After

receiving the complete device address, the FM6124

will begin shifting data out from the current address

on the next clock. The current address is the value

held in the internal address latch.

Beginning with the current address, the bus master

can read any number of bytes. Thus, a sequential read

is simply a current address read with multiple byte

transfers. After each byte the internal address counter

will be incremented.

Each time the bus master acknowledges a byte,

this indicates that the FM6124 should read out

the next sequential byte.

There are four ways to terminate a read operation.

Failing to properly terminate the read will most like l y

create a bus contention as the FM6124 attempts to

read out additional data onto the bus. The four valid

methods follow.

1. The bus master issues a NACK in the 9

th

clock

cycle and a Stop in the 10

th

clock cycle. This is

illustrated in the diagrams below and is

preferred.

2. The bus master issues a NACK in the 9

th

clock

cycle and a Start in the 10

th

.

3. The bus master issues a Stop in the 9

th

clock

cycle.

4. The bus master issues a Start in the 9

th

clock

cycle.

If the internal address reaches the top of me mory, it

will wrap around to 0000h on the next read cycle.

The figures below show the proper operation for

current address reads.

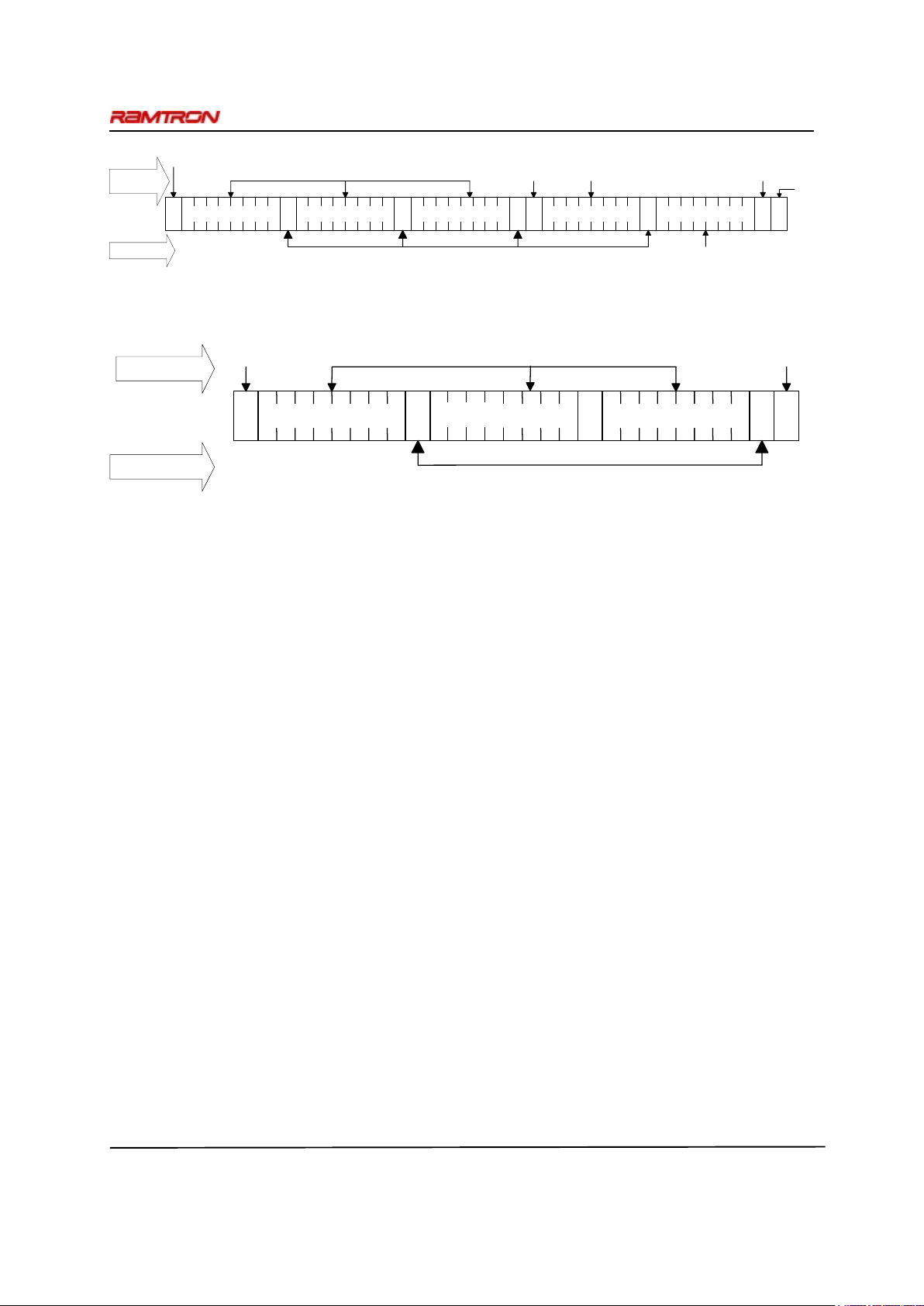

Selective (Random) Read

There is a simple technique that allows a user to

select a random address location as the starting point

for a read operation. This involves using the first

three bytes of a write operation to set the internal

address followed by subsequent read operations.

S

A

Slave Address 0

Address MSB

A

Data Byte

A

P

By Master

By FM6124

Start

A

ddress & Data

Stop

A

cknowledge

A

ddress LSB

A

S

A

Slave Address

0

Address MSB

A

Data Byte

A

P

By Master

By FM6124

Start

Address & Data

Stop

Acknowledge

Address LSB

A

Data Byte

A

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 7 of 53

To perform a selective read, the bus master sends out

the slave address with the LSB set to 0. This specifies

a write operation. According to the write protocol,

the bus master then sends the address bytes that are

loaded into the internal address latch. After the

FM6124 acknowledges the address, the bus master

issues a Start condition. This simultaneously aborts

the write operation and allows the read command to

be issued with the slave address LSB set to a 1. The

operation is now a read from the current address.

Read operations are illustrated below.

RTC/Companion Write Operation

All RTC and Companio n writes operate in a similar

manner to memory writes. The distinction is that a

different device ID is used and only one byte address

is needed instead of two. Figure 1 0 illustr ates a si ngle

byte write to this device.

RTC/Companion Read Operation

As with writes, a read operation begins with the

Slave Address. To perform a register read, the bus

master supplies a Slave Address with the LSB set to

1. This indicates that a read operation is requested.

After receiving the complete Slave Address, the

FM6124 will begin shifting data out fro m the current

register address on the next clock. Auto-increment

operates for the special function registers as with the

memory address. A current address read for the

registers look exactly like the memory except that the

device ID is different.

The FM6124 contains two separate address registers,

one for the memory address and the other for the

register address. This allows the contents of one

address register to be modifie d without affecting the

current address of the other register. For example,

this would allow an interrupted read to the memory

while still providing fast access to an RTC register. A

subsequent memory re ad will the n continue from the

memory address where it previously left off, without

requiring the load of a new memory address.

However, a write sequence always requires an

address to be supplied.

F

IGURE 7. CURRENT ADDRESS MEMORY READ

F

IGURE 8. SEQUENTIAL MEMORY READ

S

A

Slave Address

1

Data Byte

1 P

By Master

By FM6124

Start

Address

Stop

Acknowledge

No

Acknowledge

Data

S ASlave Address 1 Data Byte 1 P

By Master

By FM6124

Start

A

ddress

Stop

A

cknowledge

No

A

cknowledge

Data

Data Byte

A

A

cknowledge

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 8 of 53

F

IGURE 9. SELECTIVE (RANDOM) MEMORY READ

F

IGURE

10.

BYTE REGISTER WRITE

Delay When Switching from EDR/Companion ID

to User F-RAM ID

When switching from FM6124 EDR/Companion ID

to the User F-RAM ID, there will be a delay of

~100µs during which the FM6124 may not

acknowledge to I

2

C ID sent to it. This delay is

required for the internal logic of the FM6124 to

perform the switchover from one ID to another.

If the host attempts to initiate a transaction to the

FM6124 with a different slave address within this

100µs period, it is recommended that the host i nitiate

a read command to the FM6124 with the ID projected

to be used with the R/W bit set to 1 and then send a

STOP if the FM6124 fails to respond.

At 100 kHz I

2

C communication speed a 100µS delay

correspond to approximately one I

2

C read command.

This means that if the FM6124 fails to respond to the

first read operation, it will respond on the second one.

S

A

Slave Address

0 A

Data Byte

A P

By Master

Start

Address & Data

Stop

Acknowledge

By FM6124

Register Address

S A

Slave Address

1

Data Byte

1 P

By Master

By FM6124

Start Address

Stop

No

Acknowledge

Data

S

A

Slave Address

0

Address MSB

A

Start

Address

Acknowledge

Address LSB

A

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 9 of 53

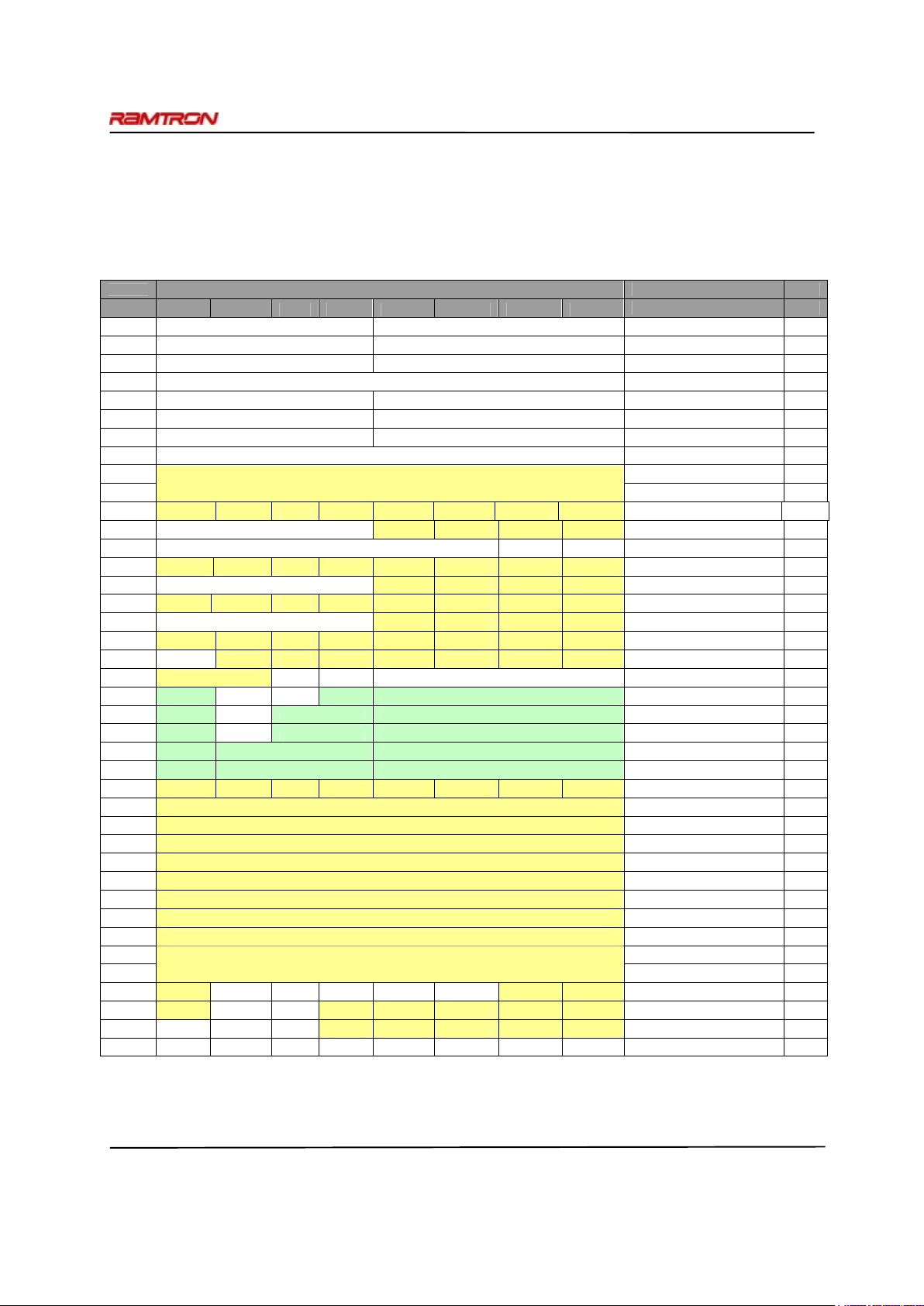

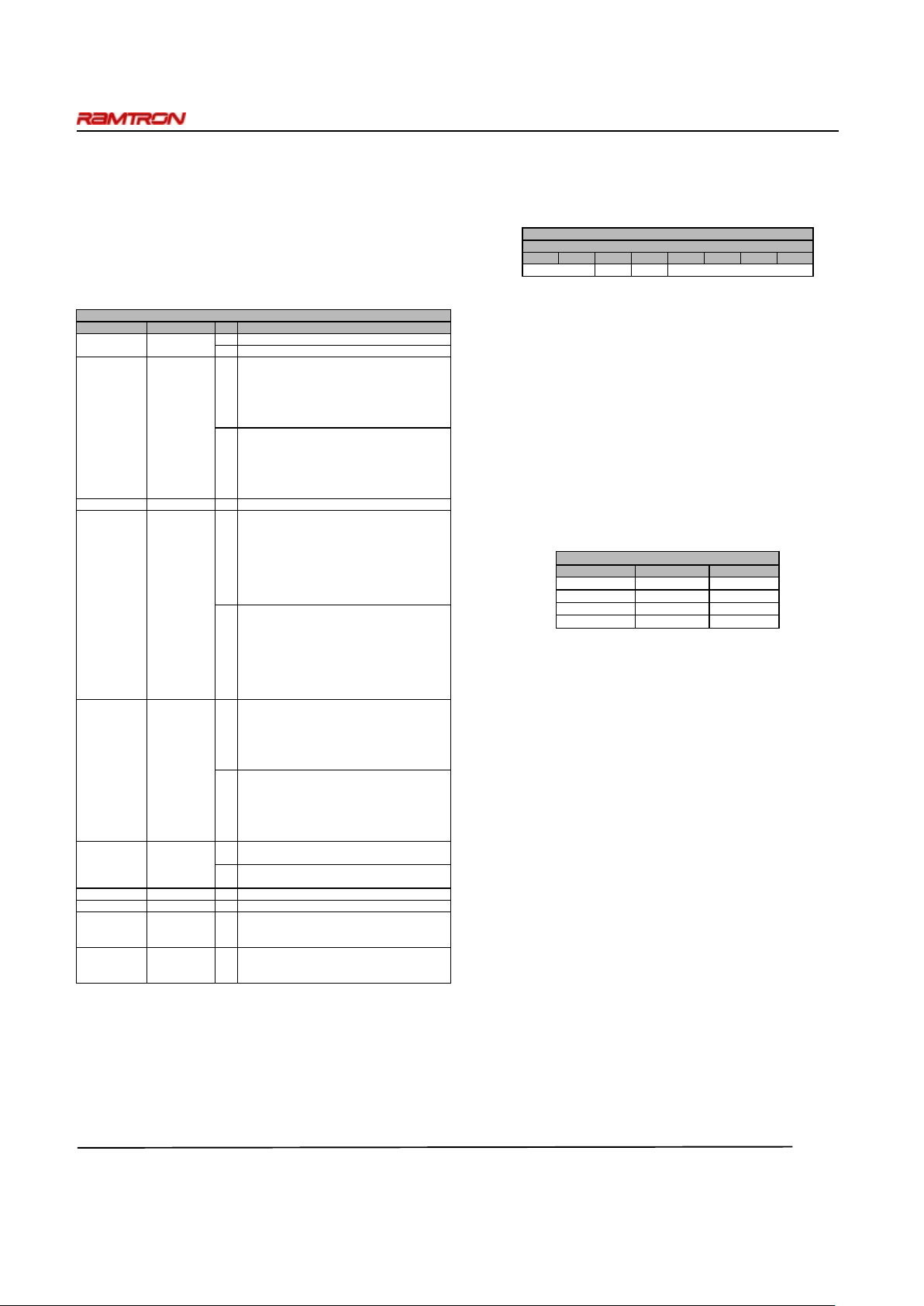

Register Map

The FM6124 Event Recorder, RTC, and processor companion functions are accessed via 51 special function

registers, which are mapped to unique commands. The interface protocol is described in details in the following

pages. The registers contain timekeeping data, alarm settings, control bits, and information flags. A description of

each register follows the summary table.

T

ABLE 1.

FM6124 R

EGISTER MAP OVERVIEW

Address

Data Function Type

7 6 5 4 3 2 1 0

0x33 10 Years Year Event BCD Year RO

0x32 10 Months Month Event BCD Month RO

0x31 10 Date Date Event BCD Dat e RO

0x30 Day of week Event BCD Day of Week RO

0x2F 10 Hours Hours Event BCD Hours RO

0x2E 10 Minutes Minutes Event BCD Minutes RO

0x2D 10 Seconds Seconds Event BCD Seconds RO

0x2C Event Code Event Code RO

0x2B Unread Events Counter MSB RO

0x2A

Number of Unr ead Events Recorded

Unread Events Counter LSB RO

0x29 P11 P10 P9 P8 P7 P6 P5 P4 Pin Pass-through B RO

0x28 Reserved P3 P2 P1 P0 Pin Pass-through A RO

0x27

Reserved

NBEV SNAP

Pin State– #Events snapshot WO

0x26 P11 P10 P9 P8 P7 P6 P5 P4 Pin Event Enable B R/W

0x25 Reserved P3 P2 P1 P0 Pin Event Enable A R/W

0x24 P11 P10 P9 P8 P7 P6 P5 P4 Pin Event Rise/Fall B R/W

0x23 Reserved P3 P2 P1 P0 Pin Event Rise/Fall A R/W

0x22 P11 P10 P9 P8 P7 P6 P5 P4 Pin Event Interrupt B R/W

0x21

CLEAR

BF B75F BHF

P3

P2 P1 P0 Pin Event Interrupt A R/W

0x20 EBUFSIZE[1:0] ERR DIR EDRCMD[3:0] Event Recorder Control R/W

0x1D ~M 0 0 10 mo Month Alarm BCD Month R/W

0x1C ~M 0 10 date Date Alarm BCD Date R/W

0x1B ~M 0 10 hours Hours Alarm BCD Hours R/W

0x1A ~M 10 minutes Minutes Alarm BCD Minutes R/W

0x19 ~M 10 seconds Seconds Alarm BCD Seconds R/W

0x18 SNL

AL/SW

F1 F0 VBC FC VTP1 VTP0 Companion Control R/W

0x17 Serial Number Byte 7 Serial number 7 R/W

0x16 Serial Number Byte 6 Serial number 6 R/W

0x15 Serial Number Byte 5 Serial number 5 R/W

0x14 Serial Number Byte 4 Serial number 4 R/W

0x13 Serial Number Byte 3 Serial number 3 R/W

0x12 Serial Number Byte 2 Serial number 2 R/W

0x11 Serial Number Byte 1 Serial number 1 R/W

0x10 Serial Number Byte 0 Serial number 0 R/W

0x0F Edge Count MSB RO

0x0E

16-bit “CNT Pin” Edge Count

Edge Count LSB RO

0x0D NVC - - - RC WC POLL CP Edge Count Control R/W

0x0C WDE - -

WDET4 WDET3 WDET2 WDET1 WDET0

Watchdog flags R/W

0x0B - - -

WDST4 WDST3 WDST2 WDST1 WDST0

Watchdog flags R/W

0x0A - - - - WR3 WR2 WR1 WR0 Watchdog Restart R/W

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 10 of 53

0x09 EWDF LWDF POR LB - - - Watchdog flags R/W

0x08 10 year Year BCD Year R/W

0x07 10 month Month BCD Month R/W

0x06 10 date Date BCD Date R/W

0x05 Day of week BCD Day of Week R/W

0x04 10 hours Hours BCD Hours R/W

0x03 10 minutes Minutes BCD Minutes R/W

0x02 10 seconds Seconds BCD Seconds R/W

0x01 CALS CAL4 CAL3 CAL2 CAL1 CAL0 CAL Control R/W

0x00 ~OSCEN AF CF AEN reserved CAL W R RTC Control R/W

Battery-backed = Nonvolatile = BB/NV User Programmable =

Note: When the device is first powered up and programmed, all timekeeping registers must be written because the battery-backed

register values cannot be guaranteed. The table below shows the default values of the nonvolatile registers and some of the

battery-backed bits. All other register values should be treated as unknown

.

Default Register Values

Address Hex Value Address Hex Value

33h 0x00 1Dh 0x81

32h 0x00 1Ch 0x81

31h 0x00 1Bh 0x80

30h 0x00 1Ah 0x80

2Fh 0x00 19h 0x80

2Eh 0x00 18h 0x40

2Dh 0x00 17h 0x00

2Ch 0x00 16h 0x00

2Bh 0x00 15h 0x00

2Ah 0x00 14h 0x00

29h 0x00 13h 0x00

28h 0x00 12h 0x00

27h 0x00 11h 0x00

26h 0x00 10h 0x00

25h 0x00 0Fh 0x00

24h 0x00 0Eh 0x00

23h 0x00 0Dh 0x01

22h 0x00 0Ch 0x00

21h 0x00 0Bh 0x00

20h 0x00 01h 0x00

1Eh-1Fh undefined 00h 0x80

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 11 of 53

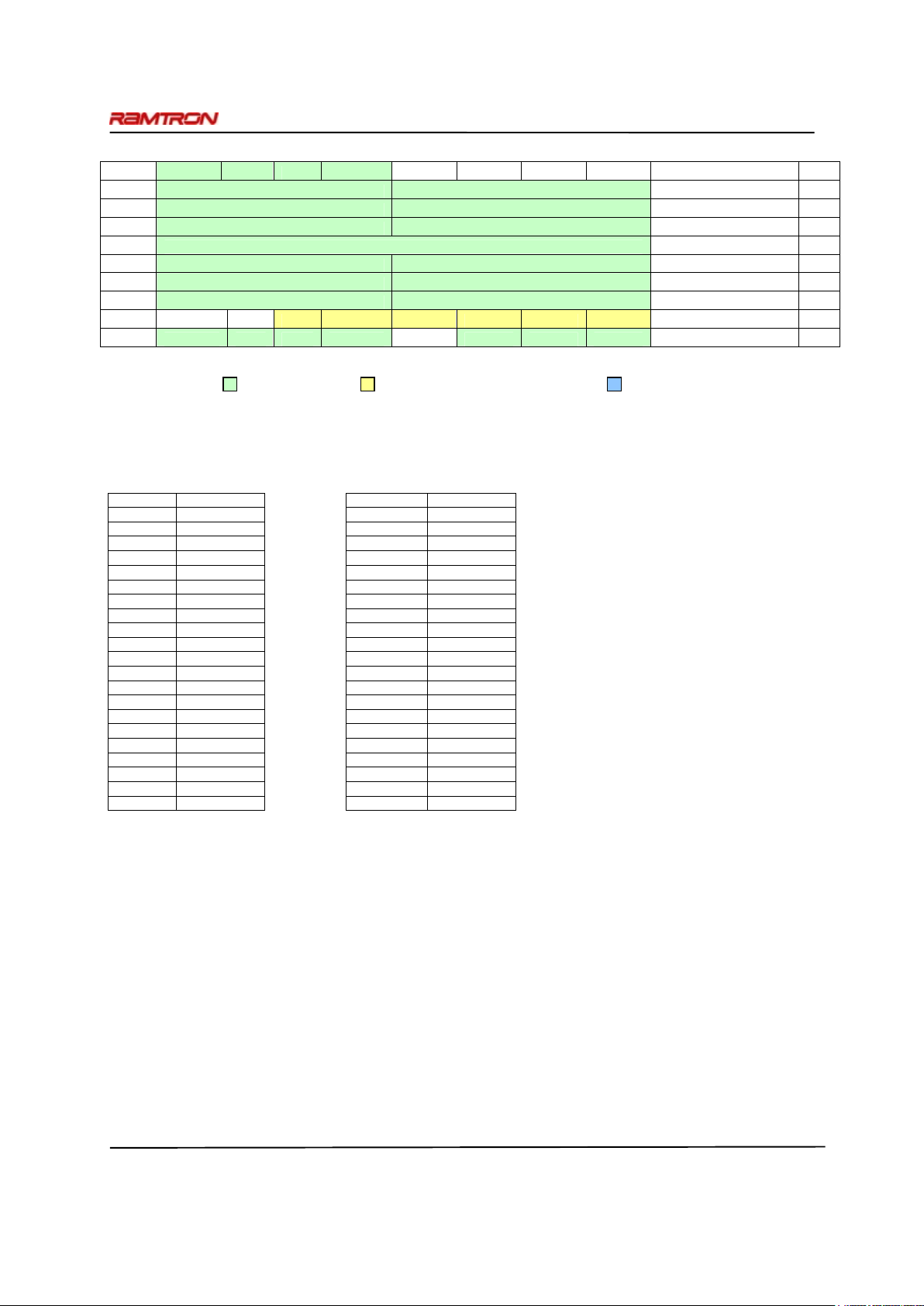

Event Recorder with Timestamp

The main feature of the FM6124 is its event recording

capability. The FM6124 can monitor events occurring on

each of its 12 digital input pins. When an event occurs the

Event is recorded into the Event Buffer F-RAM memory

along with current the timestamp. The recorded event data

is retrieved through I

2

C mapped registers.

The FM6124 is a highly integrated part able to operate in

standalone mode and requiring a few external components

to operate.

Dedicated F-RAM for Event Recording

Based on profiles set by the user, Events are recorded in

nonvolatile F-RAM memory. Each event is timestamped

automatically. A programmable amount of nonvolatile

storage is available to record events (25%, 50%, 75% or

100%). Event recording is triggered by pin state changes.

Events will be recorded in a circular buffer unless emptied

by the host.

A host processor can download the Event log at any time

via the I

2

C interface. In addition the various resources such

as the input pins and the RTC can be read directly through

the serial interface.

Event Definition

An Event is defined as either a rising or a falling tra nsitio n

occurring on any given input pin. Each one of the input

pin can be individually configured to react on a rising edge

or a falling edge.

Two registers located at addresses 0x23 and 0x24 allow

one to individually configure each one of the FM6124

Input pin to trigger an event record ing on either a Low to

High or a High to Low transitio n

• Setting t he corresponding bit to 1 will trigger an

Event recording on a Low to High transition

• Setting t he corresponding bit to 0 will trigger an

Event recording on a High to Low transition

F

IGURE

11. E

VENT TYPE SUPPORTED

Simultaneous transitions on distinct input pins configured

to react to these transitions will be considered as distinct

events and they will be recorded as such.

F

IGURE

12. E

VENT DETECTION AND STORAGE INTO

F-RAM

The recording order of simultaneous events will be related

to the input numbering. For example, if events occur

simultaneously on IN0, IN1, IN7 and IN10, the first event

recorded will be the one occurring on IN0 followed by the

one on IN1 then IN7 and IN10.

When simultaneous events occur, it is possible that the

timestamp recorded varies by 1 second.

Event Timestamp Content

Each time an event is recorded, the following parameters

are saved in the nonvolatile Event buffer:

F

IGURE

13. E

VENT TIMESTAMP CONTENT

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 12 of 53

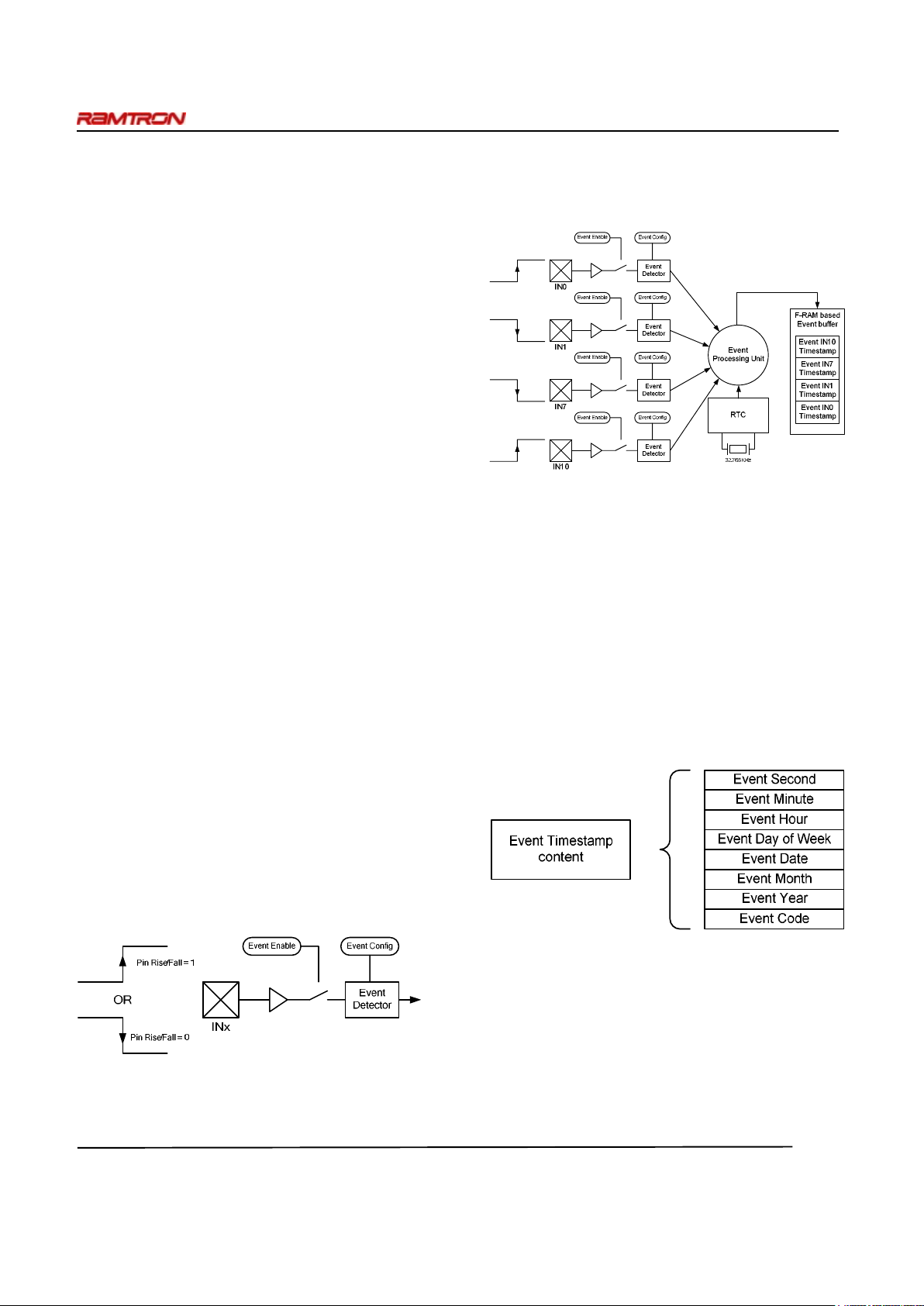

Event Memory/User F-RAM Memory Size

Configuration

The FM6124 contains a total of 32KBytes (256Kb) of FRAM memory on chip. The F-RAM memory can be

configured to serve for both Event Recording and for User

Data saving. The portion of the memory reserved for User

Data is defined through register and occupies the lower

portion of the address range.

The upper portion of the F-RAM addresses is used to store

Event type and timestamp information. The data associated

with Event is accessible only through I

2

C Mapped

registers.

The boundary between User FRAM and Event Recording

FRAM is adjusted through configuration register in the

Event recording portion of the device. The memory

boundary can be changed at any time, however each time it

is changed the entire F-RAM memory (Event Recording/

User Data) will be erased.

The portion of the F-RAM defined as User Memory Data

memory use consistent two-byte addressing for the

memory device rendering it code compatible to the

standalone memory counterparts, such as the FM24xx but

with the ability to be configured up to 24KB in size.

Up to 4000 events can be saved in the FM6124 Event

buffer F-RAM memory. A percentage of the F-RAM can

also be configured as User F-RAM that is accessed like

standard I

2

C based F-RAM and using a dedicated I2C

device ID for User F-RAM access.

The EBUFSIZE[1:0] portion of the Event Data Recorder

control register (address 0x20) defines the portion of

memory reserved for Event recording and User F-RAM

size as shown in the table below:

EBUFSIZE[1:0] Max number of Events User F-RAM size

00 4000 0

01 3000 64 Kb

10 2000 128 Kb

11 1000 192 Kb

When the entire F-RAM memory is reserved for Event

recording, there will be no User F-RAM available and the

FM6124 will stop acknowledging on any I

2

C transactions

initiated with F-RAM / EEPROM device ID.

This allows one to share the I

2

C bus between up to four

FM6124 and up to eight I

2

C based memory devices.

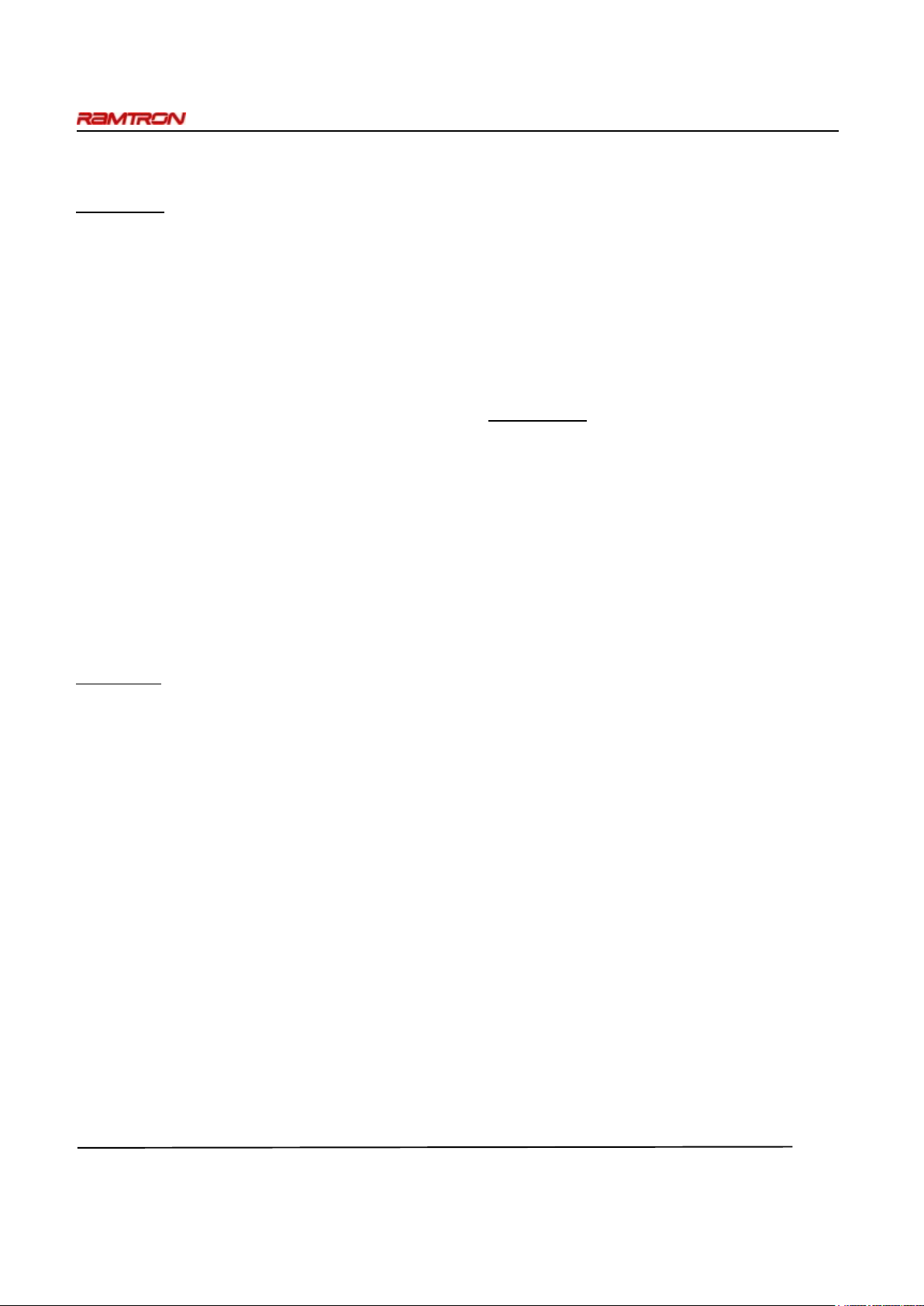

Event Buffer Architecture

The structure of the Event Buffer memory is analogue to a

Circular buffer: Initially the Event data will be stored

from a base address that we will call FP, for First pointer

and up to the maximum number of Event that the FM6124

have been configured to hold. We will call this address

Nmax.

Initially the FP pointer is likel y to be at lowest possible FRAM address. However, when the event buffer is full the

address of the FP pointer will be incremented for each ne w

event recorded.

F

IGURE

14. E

VENT BUFFER OVERVIEW

Event Buffer Pointers

The management of Event recording and retrieval is

handled using nonvolatile F-RAM based virtual pointers.

The addresses where these pointers point to are not directly

accessible through the I

2

C interface however the FM6124

provides commands to control the way those pointers

behave.

Four Pointers are defined:

FP: First pointer

RP: Read Pointer

SP: Stream Pointer

WP: Write pointer

First pointer

The FP pointer is the reference pointer which is fixed for a

given Event recorder configuration.

The first pointer actually indicates the position of oldest

event recorded and it is used as a reference. The

movements of the RP and WP pointers are referenced to

the FP pointer.

Each time the FM6124 configuration is changed through

EBUFSIZE[1:0] register, the p osition o f FP will be reset to

the lowest F-RAM ad dress and it will not move until the

Event buffer is filled.

When the number of event recorded exceeds the buffer

capacity, the FP pointer address will be incremented each

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 13 of 53

time a new event is recorded in o rder to point to the oldest

event.

Write pointer

The Write pointer is used by the Event recorder to indicate

where the next Event will be recorded in the event buffer.

The WP pointer can only move in one direction: up from

the FP address. For this reason the Eve nt storing can be

seen as a stack: more recent events being stored on top of

older ones.

Eventually the WP pointer can roll over the maximum

address. When this situation occur s the FP pointer will be

incremented for each new event recorded. In applications

where the EDR is placed close to the Host processor it is

possible to configure the Event recorder to activate the

INT output for the follo wi ng situations:

• Buffer Full

• Buffer full at 75%

• Buffer full at 50%

This is done by setting the BF, B75F, B50F bit

respectively in the PINEVENTA register

For situations where the FM6124 is remote from the host

processor, it is always possible for the host processor to

retrieve the number of e vent present in the event buffer b y

reading the Event buffer counter 16-bit register.

Read Pointer

The read pointer RP points to the next event to be read.

This pointer is used to load the next (or previous) event

data into the Event data read back registers (addresses

0x2C to 0x33) whenever the GET command

(EDRCMD[3:0] = 0001 is sent to the FM6124.

Contrary to WP, the Read pointer can be configured to

move from older to newer events but also from newer

event toward older ones.

The direction of the RP pointer depends on:

• The amount of events stored into the Event

memory buffer

• T he value of the READDIR bit

When the READDIR bit is cleared, the RP will fetch e vent

from FP toward WP. However RP cannot move farther

than WP-1. In situation where FP has reached WP-1 any

attempt to read extra events will make the Event data

recorder to fill the Event data read back registers with

0xFF, set the ERR bit of the Event Data recorder

configuration register and the RP address will not be

incremented.

When the READDIR bit is set and the GET co mmand is

initiated, the RP will fetch the data associated with the next

events toward FP and place its content into the Event Data

Read back registers. This provided that the RP pointer is

“away” and up from FP address.

In the case where the GET command is sent to the Event

Recorder while the RP = FP, if there is one event recorded

at FP position its content will be placed in the Event Data

register.

However if from that point a second attempt is made to

read Event Data, the Event Data Recorder will fill the

Event data readback registers with 0xFF, set the ERR bit

of the Event Data recorder configuration register and the

RP address will not be incremented ( decremented).

Stream Pointer

The stream pointer is a dedicated read pointer that is used

for event reading in stream operations. From a functional

point of view the SP pointer is independent of the RP.

However, like the RP po inter, the direction into whic h the

SP pointer will mode, de pend on configur ation of the DIR

bit of the Event Buffer Control register: W hen the DIR bit

is configured as 0, the SP pointer will mode from oldest

event toward newer event. In the situatio n where the DIR

bit is set to 1, the SP pointer moves from newer events

towards older ones.

The value of SP is i nitialized at the moment the ST REAM

command (EDRCMD[3:0] = 0011 is initiated.

The SP pointer is used to automatically load the next event

data into the Event data read back registers (addresses

0x2C to 0x33) after the last register (0x33) of the previous

event content is read and the STREAM Event data

recorder command is maintained.

As other pointers, the SP pointer address is not accessible

to the user.

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 14 of 53

Retrieving the Number of Unread Events

The FM6124 features a 16-bit register that indicate the

number of unread event present in the Event Buffer

memory. This 16-bit number actually corresponds to the

number of events between WP and RP pointers. It is

accessible through I

2

C registers addresses 0x2A and 0x2B.

Before accessing the Unread Event counter, the host

processor must latch a internal registers content into the

16-bit register.

This is performed by writing 0x02 into the Pin/Event

Snapshot register.

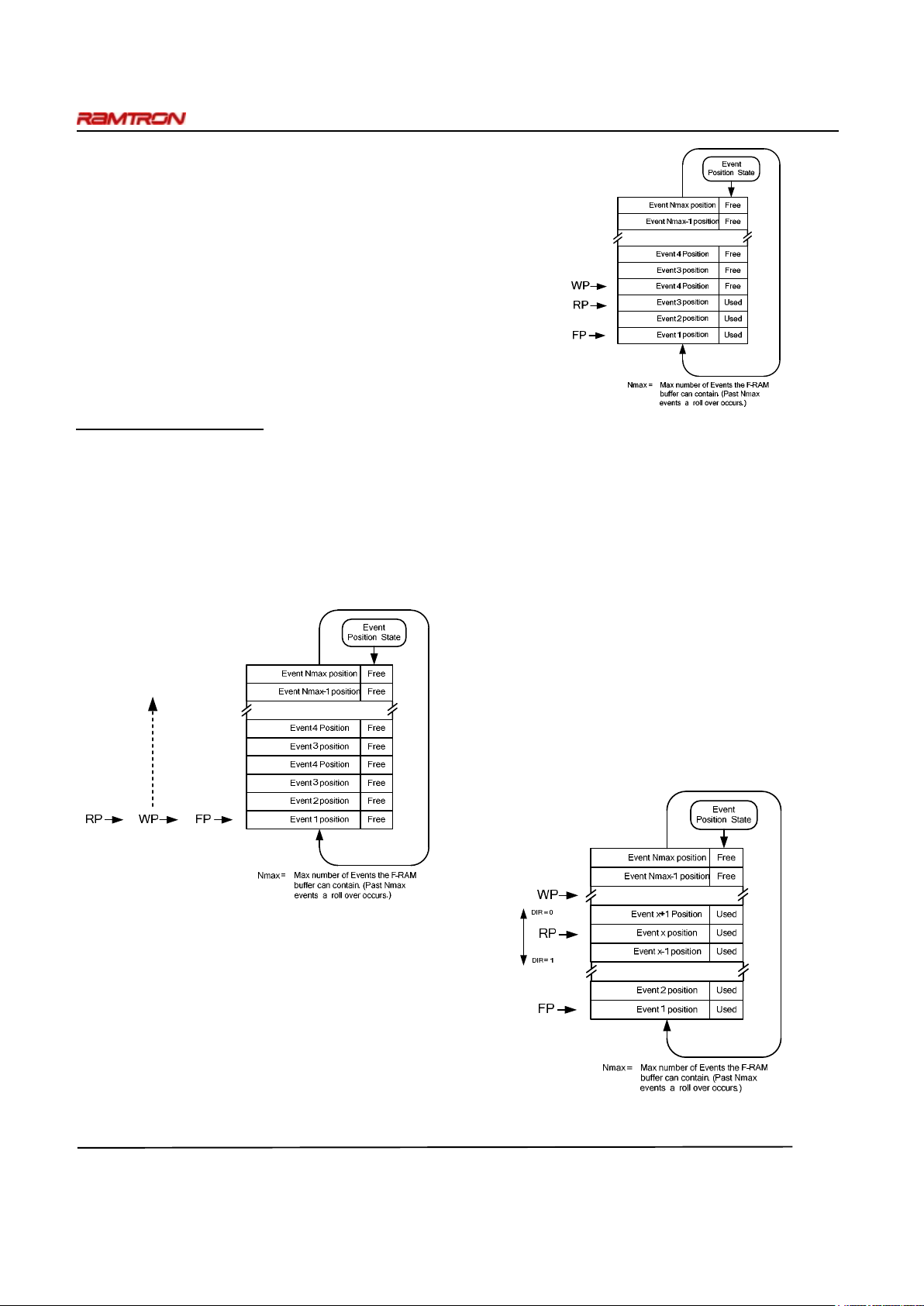

Event buffer initial condition

Every time the FM6124 Event Buffer memory size

configuratio n is c ha nged , b y Eve nt B uffe r M emor y will b e

reinitialized the events records that may still be present

into the F-RAM will be erased. This re-initialization

process takes ~100µs and during that time no eve nts will

be recorded and I

2

C communication should be stopped.

After initialization, the RP, WP, and FP pointer s will all be

pointing at the base memory address as shown in the

diagram below.

WP has only one direction

F

IGURE

15. I

NITIAL CONDITION OF EVENT BUFFER

The following example demonstrates the state of the

pointers after 3 events have been captured and stored in FRAM based Event buffer; the pointers wil l be positioned

as shown in the figure below:

F

IGURE

16. I

NTERNAL POINTERS AFTER 3 EVENTS

The FP, WP, and RP pointers will be set as follow:

• WP will point to the next free position

• RP point to the next Event to be read

• FP is fix

Each time a new Event is recorded the WP address is

incremented. When WP increments beyond the Nmax

position, it will roll-over to FP and so on. If FP reached

WP, an error condition will occur .

As mentioned earlier, after a number of events have been

recorded and a number of events have been read, the RP

pointer will be away from FP and the WP pointer. In that

situation the Event data recor der make s po ssible to retr ieve

either newer or older events by configuring the DIR bit

accordingly. The following diagram illustrates the impact

on the DIR register on the RP operation.

RP direction

depends on DIR bit

F

IGURE

17. RP P

OINTER DIRECTION

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 15 of 53

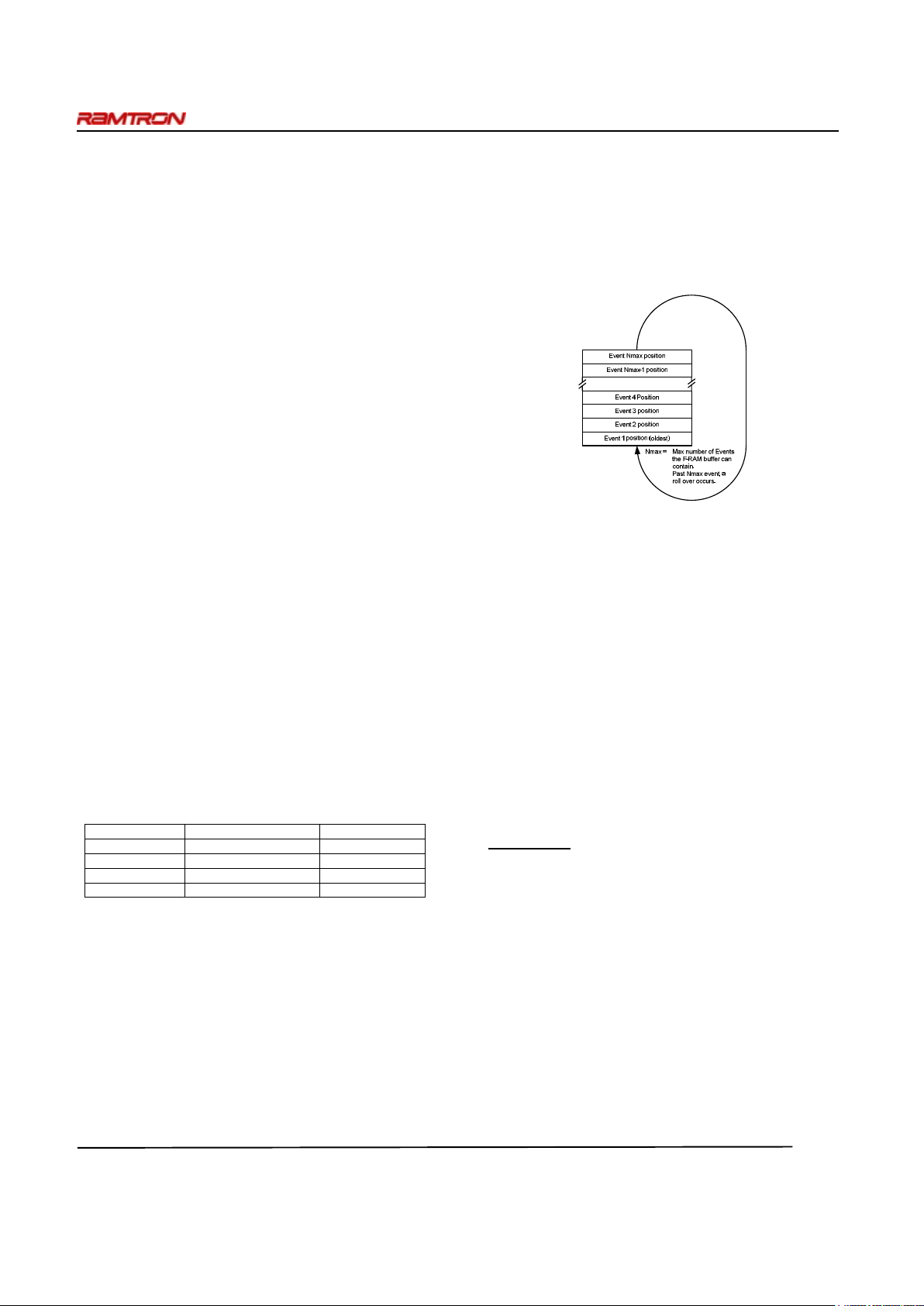

EDR COMMAND SET

The FM6124 responds to commands written to address

0x20, through the I

2

C serial port. There are nine unique

commands, eight of which ar e used to retrieve event data,

the remaining one is used to set the partitio n between User

Memory and Event Memory. The commands and their

effect are listed below.

Command EDRCMD[0:3] DIR EFFECT

0 set direction dirrection to increment

1 set p ointer d irrection to decrem ent

0

IF RP ≠ WP THEN

read_bu ffer = event_buffer[RP ]

increment RP

ELSE

read_buffer = [FF,FF,FF,FF,FF,FF,FF,FF]

ERR = 0x01

1

IF RP ≠ FP THEN

read_bu ffer = event_buffer[RP ]

decrement RP

ELSE

read_buffer = [FF,FF,FF,FF,FF,FF,FF,FF]

ERR = 0x01

GET KEEP 0010 x read_buffer = event_buffer[RP]

0

IF RP ≠ WP THEN

read_bu ffer = event_buffer[SP]

increment RP

ELSE

read_buffer = [FF,FF,FF,FF,FF,FF,FF,FF]

ERR = 1

ENDIF

SP = RP

1

IF RP ≠ FP THEN

read_bu ffer = event_buffer[SP]

decrement RP

ELSE

read_buffer = [FF,FF,FF,FF,FF,FF,FF,FF]

ERR = 1

ENDIF

SP = RP

0

IF SP ≠ WP THEN

read_bu ffer = event_buffer[SP]

increment SP

ELSE

read_buffer = [FF,FF,FF,FF,FF,FF,FF,FF]

ERR = 0x01

1

IF SP ≠ FP THEN

read_bu ffer = event_buffer[SP]

decrement SP

ELSE

read_buffer = [FF,FF,FF,FF,FF,FF,FF,FF]

ERR = 0x01

0

IF (WP - RP ) > 1 THEN

increment RP

1

IF RP > FP THEN

decrement RP

FIRS

T

0110 x RP = FP

LAST 0111 x RP = WP - 1

SET EVENT

BUFFER SIZE

1000 x

IF COMMAND[7 :6] ≠ EBUFSIZE[1:0 ] THEN

SP = RP = FP = WP = 0x00

event_buffer = [00,00,00,…,00,00,00]

RESERV ED

1001

to

1111

x No A ction

Table of Comm ands

STREAMING

GET

0011

SET DIR 0000

GET 0001

STREAMING

GET KEEP

0100

SKIP 0101

Each command is an eight bit assemblage of lesser

registers EBUFSIZE[1:0], ERR, DIR & EDRCMD[3:0]

The sequence of concatenation is shown in the table

below.

76543210

ERR DIR

Bit

EBUFSI ZE[1 :0] EDRCMD[3:0]

COMMAND STRUCTURE: Address 0x20

The EDRCMD[3:0] register specifies which of the nine

unique commands should be executed.

The DIR register specifies whether the event pointer used

by the command, should be incremented or decremented

after the successful completion of the command.

The ERR register is used to signal the host, that the event

pointer used dur ing the last co mmand ca n move no furt her

in the direction specified by DIR.

The EBUFSIZE[1:0] register specifies the partitioning of

User memory and Event Memory as indicated in the table

below.

EBUFSIZE[1:0] Event Memory User Memory

00 4000 events 0kB

01 3000 events 8kB

10 2000 events 16kB

11 1000 events 24kB

PARTITION SIZE:

ISSUING A COMMAND

When the host is ready to issue a command, the following

procedure should be used.

Start I

2

C

Send the EDR ID & [R/W] = 0 or write

Send the command register start address "0x20"

Send the EBUFSIZE[1:0]& ERR & DIR & EDRCMD[3:0]

Stop I

2

C

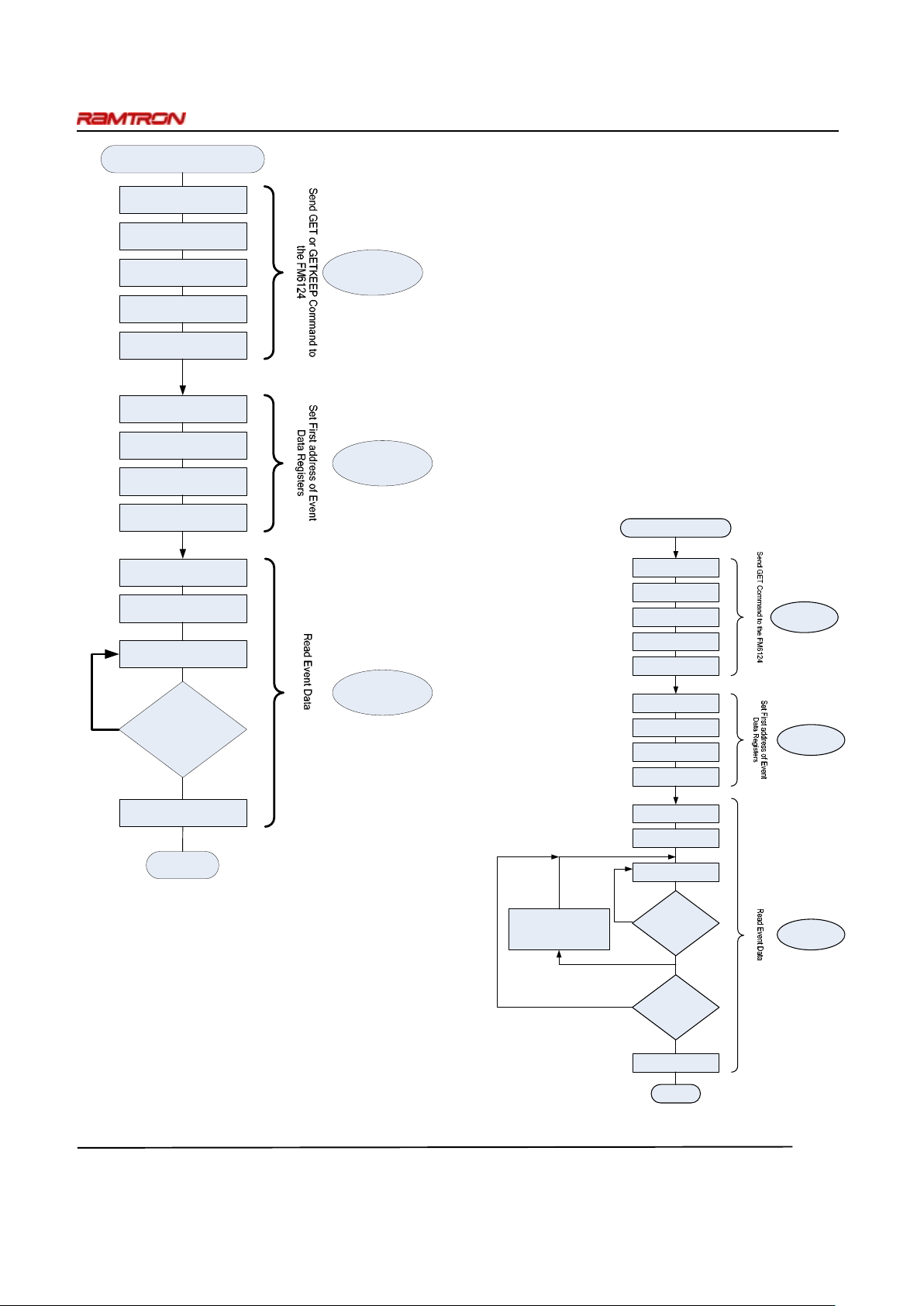

RETRIEVING SINGLE EVENTS

After a GET or KEEP command has been issued, the EDR

will place the event pointed to by RP into the read buffer.

The eight byte wide read buffer can be read through the

I

2

C serial port, starting at address 0x2C and finishing at

address 0x33. To retrieve an event from the buffer, the

following procedure should be followed.

Start I2C

Send the EDR ID & R/W bit = 0 (write)

Send the event buffer start ad dress "0x2C"

Stop I

2

C

Start I

2

C

Send the EDR ID & R/W = 1 (read)

Send seven addition read requests

Stop I

2

C

FM6124 Event Data Recorder

Rev. 1.0

April 2008 Page 16 of 53

Single Event Read

Send I2C EDR ID

+ R/W = 0 (write)

I2C Start

Send Reg Address = 0x20

I2C Stop

I2C Start

Send I2C EDR ID

+ R/W = 0 (write)

Send Command: GET or

GETKEEP + set DIR

Send Reg Address = 0x2C

I2C Stop

I2C Start

Send I2C EDR ID

+ R/W = 1 (read)

All 8 Bytes of event

data Read?

Event Data byte Read

I2C Stop

Step 1

Step 2

Step 3

End

F

IGURE

18. S

INGLE EVENT DATA RETRIEVAL PROCESS

Since the EDR's address register is auto-incrementing, it is

unnecessary to send the register address for each byte to be

read from the buffer. It is also unnecessary to begin

reading at address 0x2C or to finish reading at address

0x33. The user is free to retrieve event data from the read

buffer as best suits their application.

If the single event read command issued was a GET, then

RP will be incremented or decremented as indicated by

DIR.

If the single event command issued was a GET KEEP,

then RP will remain unchanged.

RETRIEVING MULTIPLE EVENTS

After a STREAMING GET or STREAMING GET KEEP

command has been issued, the EDR will place the event

pointed to by the SP pointer, into the read buffer. The

eight byte wide read buffer can be read through the I

2

C

serial port, starting at address 0x2C and finishing at

address 0x33.

To retrieve an event from the buffer, the

following procedure should be followed.

Start I

2

C

Send the EDR ID & [R/W] = 0 or write

Send the event buffer start address "0x2C"

Stop I

2

C

Start I

2

C

Send the EDR ID & [R/W] = 1 or read

Send seven addition read requests

Stop I

2

C

Repeat until the desired nu mber of events has been retrieved.

Multiple Events Read

Send I2C EDR ID

+ R/W = 0 (write)

I2C Start

Send Reg Address = 0x20

I2C Stop

I2C Start

Send I2C EDR ID

+ R/W = 0 (write)

Send Command: STREAM

+ set DIR

Send Reg Address = 0x2C

I2C Stop

I2C Start

Send I2C EDR ID

+ R/W = 1 (read)

Event Data Register

0x33 Read?

Event Data byte Read

I2C Stop

Step 1

Step 2

Step 3

Keep Reading Event?

No

Yes

Reload Event Data Registers

with Next/Previous Event data

(This operation is automatically

performed by the FM6124)

End

F

IGURE

19. M

ULTIPLE EVENTS RETRIEVAL

Loading...

Loading...