RAMTRON FM4005-G, FM4005 Datasheet

Pre-Production

This is a product in pre-production phas e of development. Devi ce Ramtron International Corporation

characterization is complete and Ramtron does not expect to change 1850 Ramtron Drive, Colorado Springs, CO 80921

the specifications. Ramtron will issue a Product Change Notice if (800) 545-FRAM, (719) 481-7000

any specification changes are made. www.ramtron.com

Rev. 2.3

Oct. 2006 Page 1 of 23

FM4005

Integrated Processor Companion

Features

High Integration Device Replaces Multiple Parts

• Real-time Clock (RTC)

• Low Voltage Reset

• Watchdog Timer

• Early Power-Fail Warning/NMI

• Two 16-bit Event Counters

• Serial Number with Write-lock for Security

Real-Time Clock/Calendar

• Backup Current under 1 µA

• Seconds through Centuries in BCD format

• Tracks Leap Years through 2099

• Uses Standard 32.768 kHz Crystal (6pF)

• Software Calibration

• Calibration Data is Nonvolatile

• Programmed Settings are Nonvolatile

• Supports Battery or Capacitor Backup

Processor Companion

• Active-low Reset Output for V

DD

and Watchdog

• Programmable Low V

DD

Reset Thresholds

• Manual Reset Filtered and De bounced

• Programmable Watchdog Timer

• Dual Battery-backed Event Counter Tracks System

Intrusions or othe r Events

• Comparator for Early Power-Fail Interrupt

• 64-bit Programmable Serial Number with Lock

Fast Two-wire Serial Interface

• Up to 1 MHz Maximum Bus Freque ncy

• Supports Legacy Timing for 100 kHz & 400 kHz

Easy to Use Configurations

• Operates from 2.7 to 5.5V

• Small Footprint 14-pin “Green” SOIC (-G)

• Low Operating Current

• -40°C to +85°C Operation

Description

The FM4005 is an integrated device that includes the

most commonly needed functions for processorbased systems. Major features include real-time

clock, low-V

DD

reset, watchdog timer, battery-backed

event counter, lockable 64-bit serial number area, and

general purpose comparator that can be used for a

power-fail (NMI) interrupt or other purpose. The

family operates from 2.7 to 5.5V.

The real-time clock (RTC) provides time and date

information in BCD format. It can be permanently

powered from external backup voltage source, either

a battery or a capacitor. The timekeeper uses a

common external 32.768 kHz crystal and provides a

calibration mode that allo ws software adjustment of

timekeeping accuracy.

The processor companion includes commonly needed

CPU support functions. Supervisory functions

include a reset output signal controlled by either a

low VDD condition or a watchdog timeout. /RST

goes active when VDD drops below a programmable

threshold and remains active for 100 ms after VDD

rises above the trip point. A programmable watchdog

timer runs from 100 ms to 3 seconds. The watchdog

timer is optional, but if enable d it will assert t he reset

signal for 100 ms if not restarted by the host before

the timeout. A flag-bit indicates the source of the

reset.

A general-purpose comparator compares an external

input pin to the onboard 1.2V reference. This is

useful for generating a power-fail interrupt (NMI) but

can be used for any purpose. The device also includes

a programmable 64-bit serial number that can be

locked making it unalterable. Additionally it offers a

dual battery-backed event counter that tracks the

number of rising or falling edges detected on

dedicated input pins.

FM4005

Rev. 2.3

Oct. 2006 Page 2 of 23

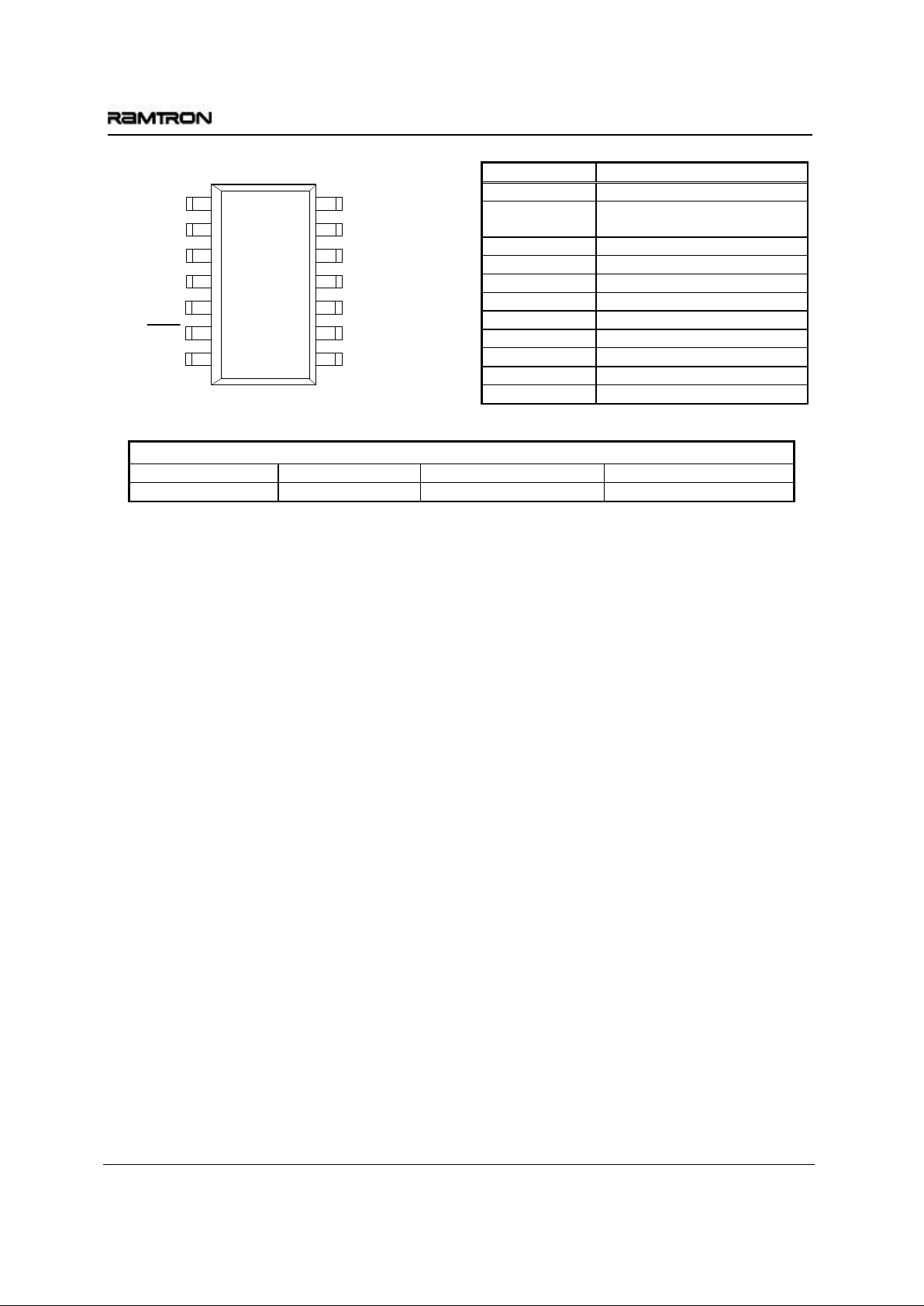

Pin Configuration

Pin Name Function

CNT1, CNT2 Battery-backed Counter Inputs

CAL/PFO Clock Calibration and Early

Power-fail Output

/RST Reset Input/Output

PFI Early Power-fail Input

X1, X2 Crystal Connections

SDA Serial Data

SCL Serial Clock

DNU Do Not Use

VBAK Battery-Backup Supply

VDD Supply Voltage

VSS Ground

Ordering Information

Base Configuration Operating Voltage Reset Threshold Ordering Part Number

FM4005 2.7-5.5V 2.6V, 2.9, 3.9, 4.4V FM4005-G

VDD

VBAK

SCL

SDA

VSS

X1

X2

CNT1

PFI

RST

DNU

DNU

CNT2

1

2

3

4

5

6

7

14

13

12

11

10

9

8

CAL/PFO

FM4005

Rev. 2.3

Oct. 2006 Page 3 of 23

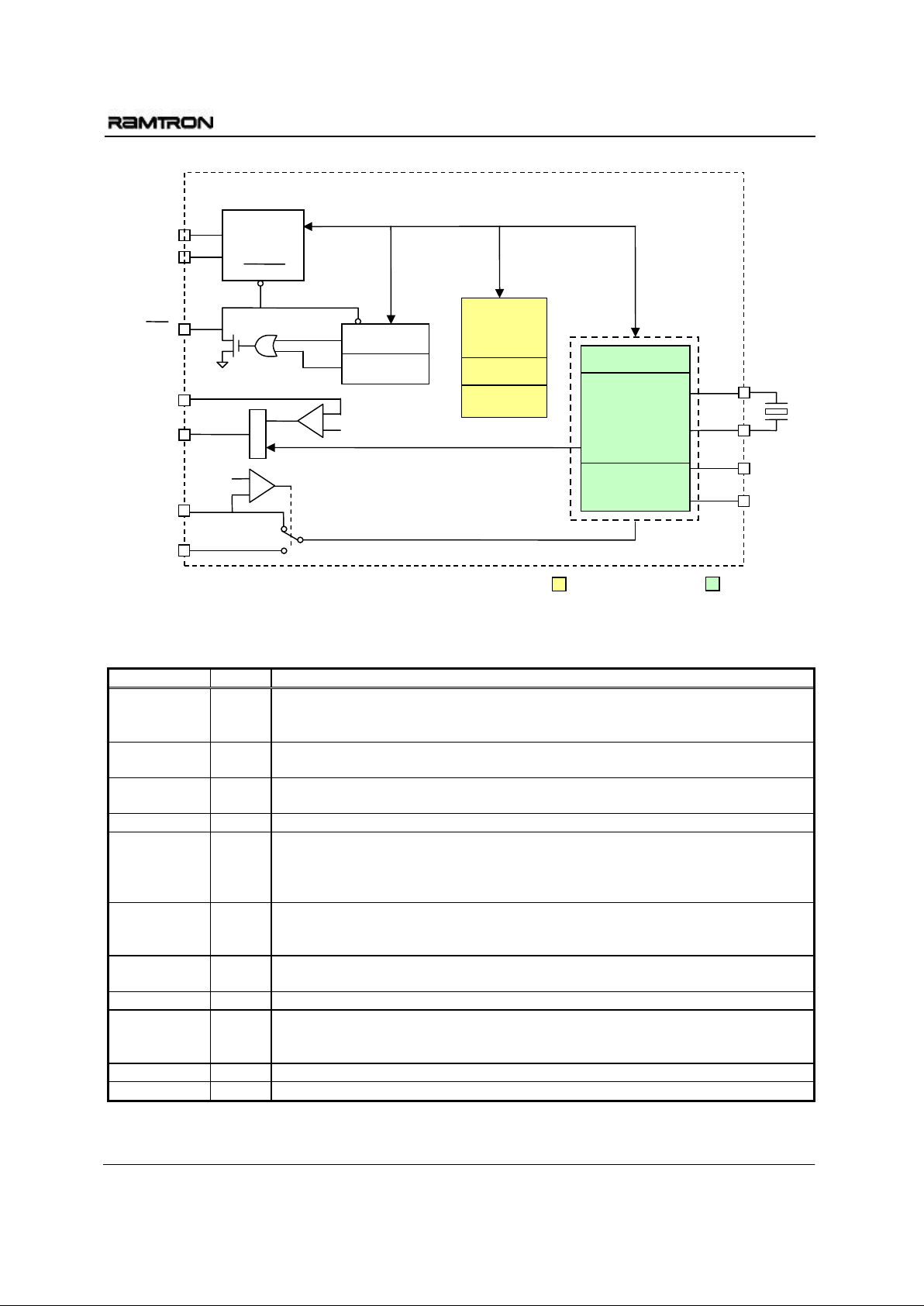

Figure 1. Block Diagram

Pin Descriptions

Pin Name Type Pin Description

CNT1, CNT2 Input Event Counter Inputs: T hese battery-backed inputs increment co unter s when an edge is

detected on the corresponding CNT pin. The polarity is programmable. These pins

should not be left floating. Tie to ground if pins are not used.

CAL/PFO Output In calibration mode, this pin supplies a 512 Hz square-wave output for clock

calibration. In normal operation, this is t he early power-fail output.

X1, X2 I/O 32.768 kHz crystal connection. When using an exter nal oscillator, apply the clock to

X1 and leave X2 floating.

/RST I/O Active low reset output with wea k p ull-up. Also input for manual reset.

SDA I/O Serial Data & Address: This is a bi-directional line for the two-wire interface. It is

open-drain and is intended to be wire-OR’d with other devices on the two-wire bus.

The input buffer incorporates a Schmitt trigger for noise immunity and the output

driver includes slope control for falling edges. A pull-up resi stor is required.

SCL Input Serial Clock: The serial clock line for the two-wire interface. Data is clocked out of the

part on the falling edge, and in on the rising edge. T he SCL input also incorporates a

Schmitt trigger input for noise immunity.

PFI Input Early Power-fa il Input: T ypically co nnected to a n unregula ted power sup ply to detec t

an early power failure. This pin should no t be left floating.

DNU - Do Not Use: This pin must be left floating.

VBAK Supply Backup supply voltage: A 3V batter y or a large value capacitor. If VDD<3.6V and no

backup supply is used, this p in should be tied to V

DD

. If VDD>3.6V and no backup

supply is used, this pin should be left floating and the VBC bit should be set.

VDD Supply Supply Voltage.

VSS Supply Ground

SCL

SDA

Nonvolatile

Battery Backed

2-Wire

Interface

RST

CAL/PFO

PFI

VDD

VBAK

RTC

2.5V

-

+

RTC Registers

Event

Counters

CNT1

CNT2

Special

Function

Registers

S/N

X1

X2

LockOut

+

-

1.2V

Watchdog

LV Detect

Switched Powe

r

512Hz

RTC Cal.

FM4005

Rev. 2.3

Oct. 2006 Page 4 of 23

Overview

The FM4005 combines a real-time clock (RTC) and a

processor companion. The companion is a highly

integrated peripheral that includes a processor

supervisor, a comparator used for early power-fail

warning, nonvolatile event counters, and a 64-bit

serial number. The FM4005 integrates these

functions that share a common interface in a single

package.

The real-time clock and supervisor functions are

accessed with a standard 2-wire device ID. The clock

and supervisor functions are controlled by 25 special

function registers. Some of these functions such as

the RTC and event counter circuits are maintained by

the power source on the VBAK pin, allowing them to

operate from battery or backup capacitor power when

V

DD

drops below an internally set threshold. Each

functional block is described below.

Processor Supervisor

Supervisors provide a host processor two basic

functions: detection of po wer supply fault conditio ns

and a watchdog timer to escape a software lockup

condition. The FM4005 has a reset pin (/RST) to

drive the processor reset input during power faults

(and power-up) and software lockups. It is an open

drain output with a weak internal pull-up to V

DD

.

This allows other reset sources to be wire-OR’d to

the /RST pin. When V

DD

is above the programmed

trip point, /RST output is pulled weakly to V

DD

. If

V

DD

drops below the reset trip point voltage level

(V

TP

) the /RST pin will be driven lo w. It will remain

low until V

DD

falls too low for circuit operation

which is the V

RST

level. When VDD rises again above

V

TP

, /RST will continue to drive low for at least 10 0

ms (t

RPU

) to ensure a robust system reset at a reliable

V

DD

level. After t

RPU

has been met, the /RST pin will

return to the weak high state. While /RST is asserted ,

serial bus activity is locked out even if a transaction

occurred as V

DD

dropped below VTP. Any register

read or write operation started while V

DD

is above

V

TP

will be completed internally.

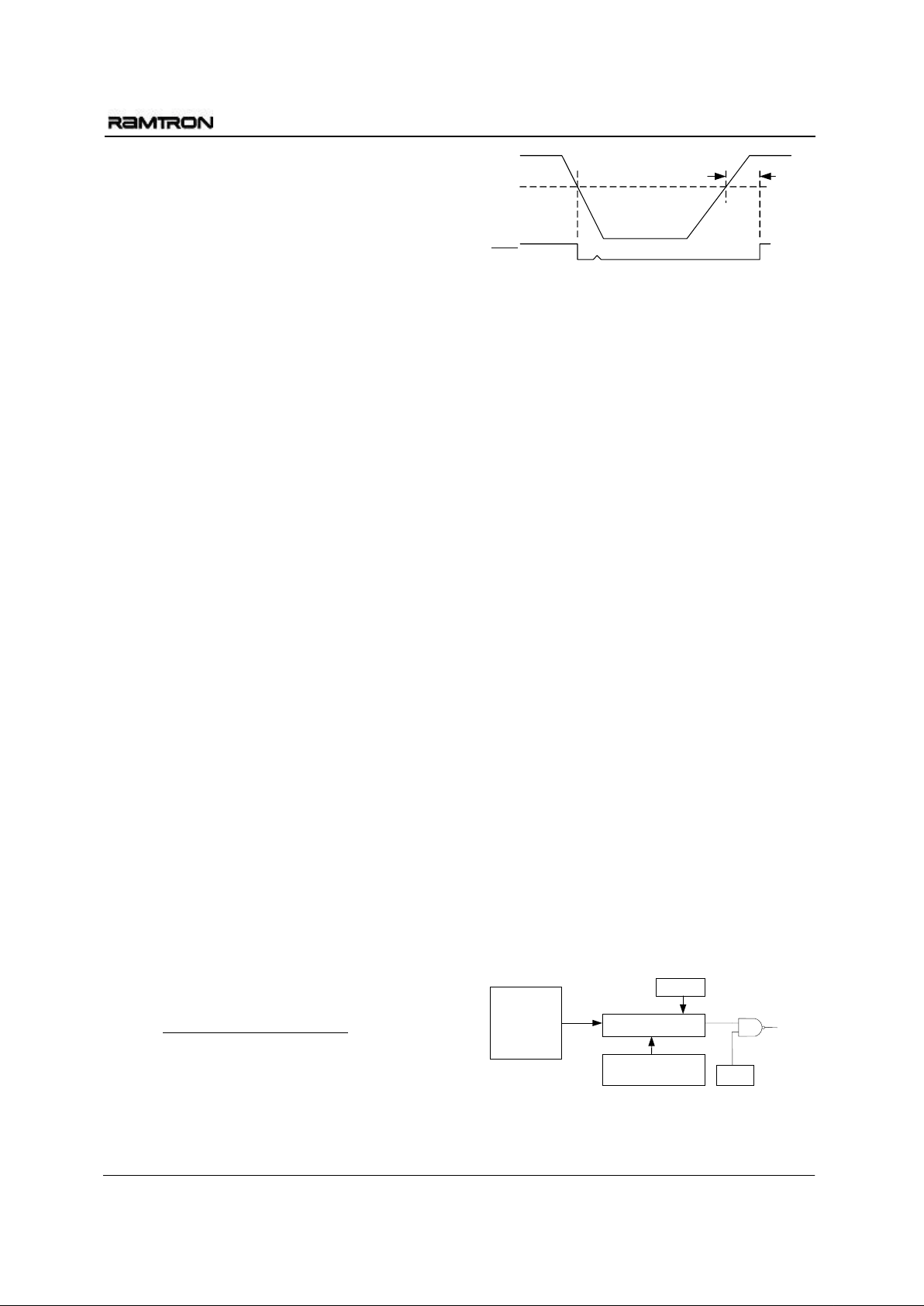

The bits VTP1 and VTP0 control the tr ip point of the

low voltage detect circuit. They are located in register

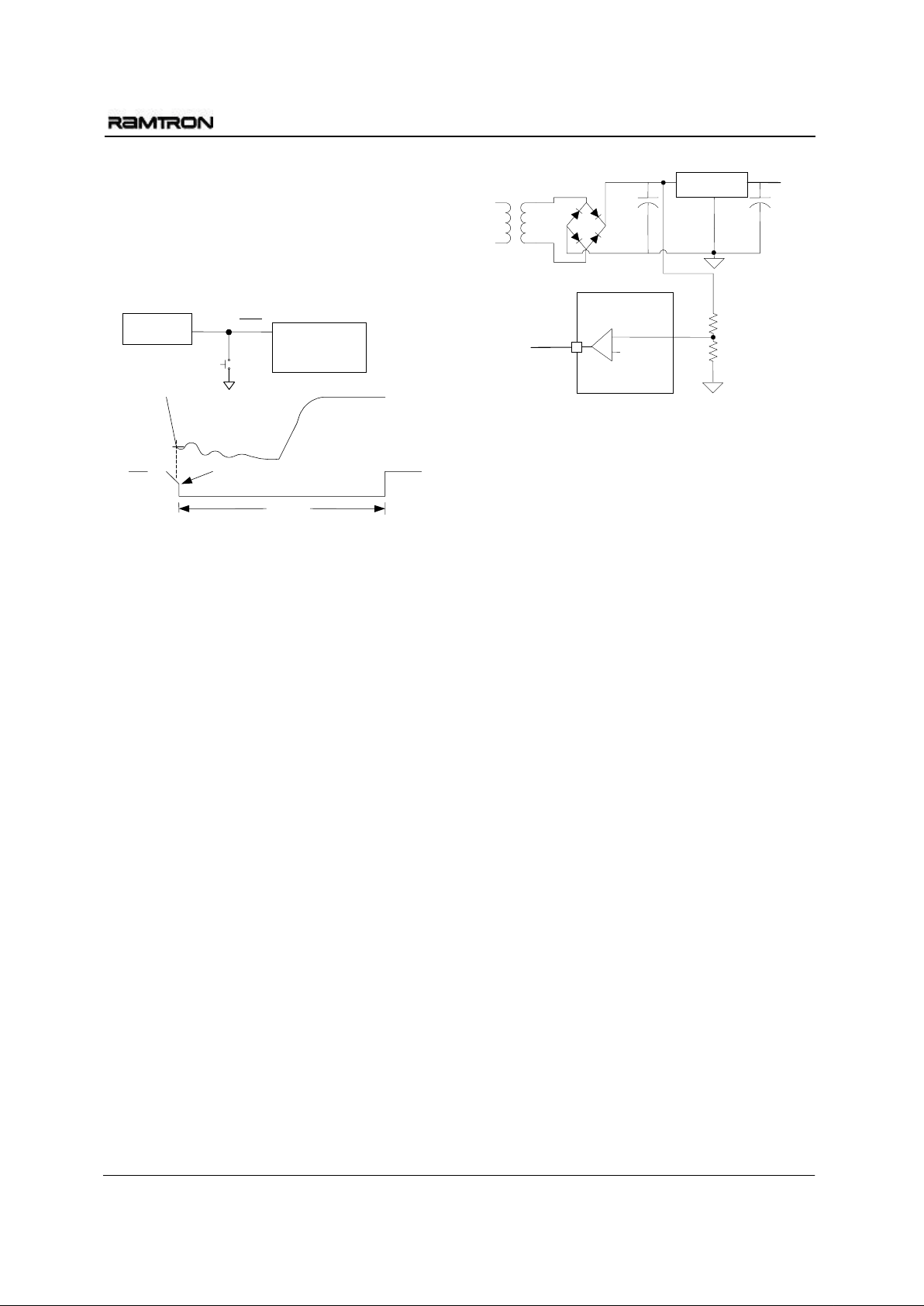

0Bh, bits 1 and 0. Figure 2 illustrates the reset

operation in response to the V

DD

voltage.

VTP VTP1 VTP0

2.6V 0 0

2.9V 0 1

3.9V 1 0

4.4V 1 1

VDD

VTP

tRPU

RST

Figure 2. Low VDD Reset

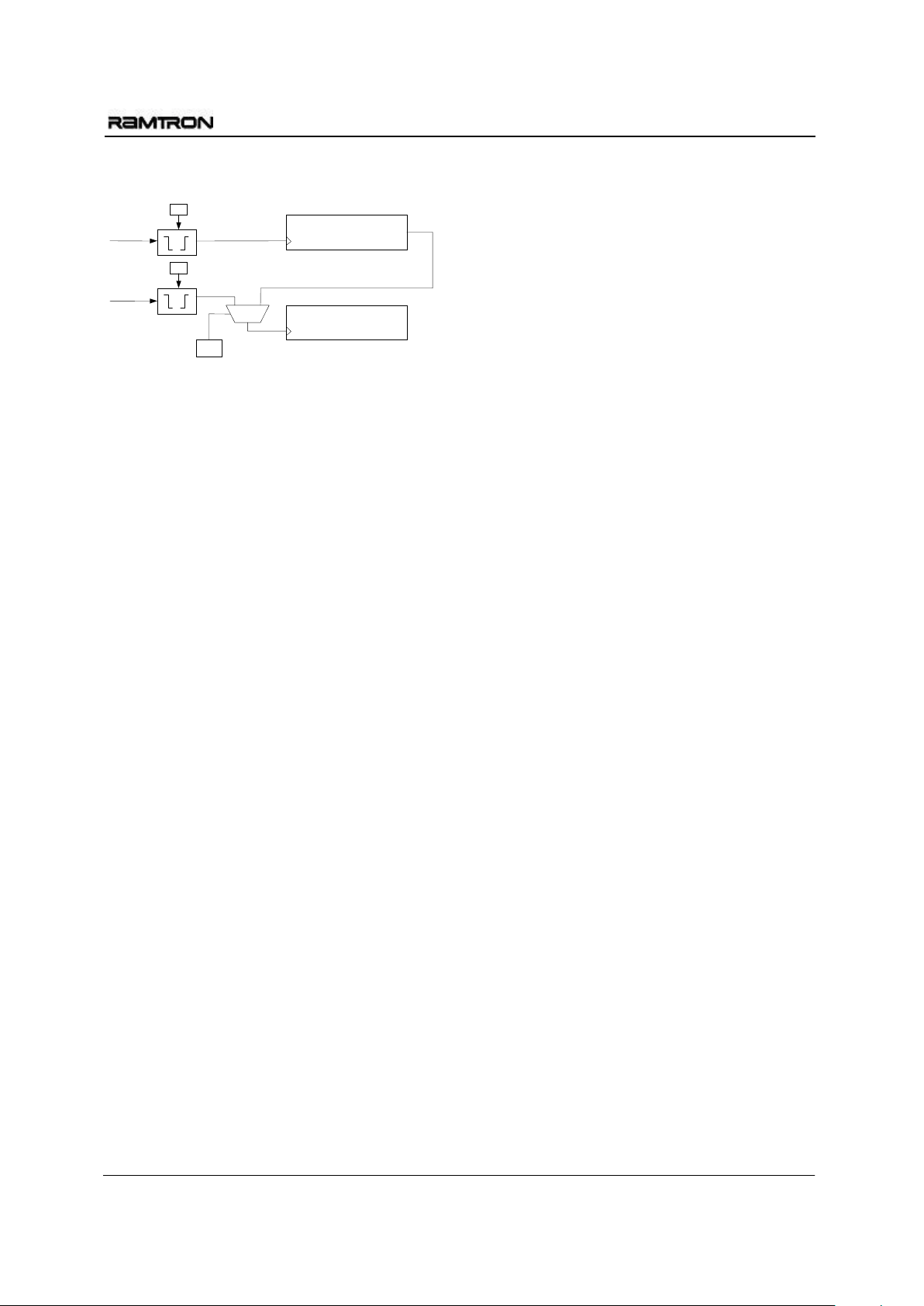

The watchdog timer can also be used to assert the

reset signal (/RST). The watchdog is a free running

programmable timer. The period can be software

programmed from 100 ms to 3 seconds in 100 ms

increments via a 5-bit nonvolatile register. All

programmed settings are minimum values and vary

with temperature according to the operating

specifications. The watchdog has two additional

controls associated with its operation, a watchdog

enable bit (WDE) and timer restart bits (WR). Both

the enable bit must be set and the watchdog must

timeout in order to drive /R ST active. If a rese t event

occurs, the timer will automatically restart on the

rising edge of the reset pulse. If not enabled, the

watchdog timer runs but has no effect on /RST. Note

that setting the maximum timeout setting (11111b)

disables the counter to save power. The second

control is a nibble that re starts the timer p reventing a

reset. The timer should be restarted after changing t he

timeout value.

The watchdog timeout value is located in register

0Ah, bits 4-0, the watchdog enable is bit 7. The

watchdog is restarted by writing the pattern 1010b to

the lower nibble of register 0 9h. Writing this pattern

will also cause the timer to load new timeout values.

Writing other patterns to this ad dress will not affect

its operation. Note the watchdog timer is freerunning. Prior to enabling it, users should restart the

timer as described above. This assures that the full

timeout period will be set im mediatel y after enabli ng.

The watchdog is disabled when VDD is below VTP.

The following table summarizes the watchd og bits. A

block diagram follows.

Watchdog timeout WDT4.0 0Ah, D4-0

Watchdog enable WDE 0Ah, D7

Watchdog restart WR3-0 09h, D3-0

Figure 3. Watchdog Timer

Timebase

Down Counter

Watchdog

timeout

100 ms

clock

WDE

/RST

WR3-0 = 1010b

FM4005

Rev. 2.3

Oct. 2006 Page 5 of 23

Manual Reset

The /RST pin is bi-directional and allows the

FM4005 to filter and de-bounce a manual reset

switch. The /RST input detects an external low

condition and responds by driving the /RST signal

low for 100 ms. Note that an internal weak pull-up on

/RST eliminates the need for additional external

components.

Figure 4. Manual Reset

Reset Flags

In case of a reset condition, a flag will be set to

indicate the source of the reset. A low V

DD

reset or

manual reset is indicated by the POR flag, register

09h bit 6. A watchdog reset is indicated by the WTR

flag, register 09h bit 7. Note that the bits are

internally set in response to reset sources, but they

must be cleared by the user. When the register is

read, it is possible that both flags are set if both have

occurred since the user last cleared them.

Early Power Fail Comparator

An early power fail warning can be provided to the

processor well before V

DD

drops out of spec. The

comparator is used to create a power fail interrupt

(NMI). This can be accomplished by connecting the

PFI pin to the unregulated power supply via a resistor

divider. An application circuit is shown below. The

voltage on the PFI input pin is compared to an

onboard 1.2V reference. When the PFI input voltage

drops below this threshold, t he comparator will dri ve

the CAL/PFO pin to a low state. The comparator has

350 mV (max) of hysteresis to reduce noise

sensitivity, only for a rising PFI signal. For a falling

PFI edge, there is no hysteresis.

Figure 5. Comparator as a Power-fail Warning

The comparator is a general purpose device and its

application is not limited to the NMI function.

The comparator is not integrated into the special

function registers except as it shares its output pin

with the CAL output. When the RTC calibration

mode is invoked by setting the CAL bit (register 00h,

bit 2), the CAL/PFO output pin will be driven with a

512 Hz square wave and the comparator will be

ignored. Since most users only invoke the calibration

mode during production, this should have no impact

on system operations using the comparator.

Note: The maximum voltag e on the comparator input PFI

is limited to 3.75V under normal operating conditions.

Event Counter

The FM4005 offers the user two battery-backed event

counters. The input pins CNT1 and CNT2 are

programmable edge detectors. Each controls a 16-bit

counter. When an edge occurs, the counters will

increment their respective registers. Counter 1 is

located in registers 0Dh and 0Eh. Counter 2 is

located in registers 0Fh and 10h. These register

values can be read anytime VDD is above VTP, and

they will be incremented as long as a valid VBAK

power source is provided. To read, set the RC bit

register 0Ch bit 3 to 1. T his takes a snapshot of all

four counter bytes allowing a stable value even if a

count occurs during the read. The registers can be

written by software allowing the counters to be

cleared or initialized by the system. Counts are

blocked during a write operation. The two counters

can be cascaded to create a single 32-bit counter by

setting the CC control bit (register 0Ch). When

cascaded, the CNT1 input will cause the counter to

increment. CNT2 is not used i n this mode.

The control bits for event counting are located in

register 0Ch. Counter 1 Polarity is bit C1P, bit 0;

FM4005

RST

MCU

Switch

Behavior

RST

FM4005

drives

100 ms

Reset

Switch

+

-

1.2V ref

Regulator

VDD

FM4005

To MCU

NMI input

CAL/PFO

FM4005

Rev. 2.3

Oct. 2006 Page 6 of 23

Counter 2 Polarity is C2P, bit 1; the Cascade Co ntrol

is CC, bit 2; and the Read Counter bit is R C bit 3.

Figure 6. Event Counter

The polarity bits must be set prior to setting the

counter value(s). If a polarity bit is changed, the

counter may inadvertently increment. If the counter

pins are not being used, tie them to ground.

Serial Number

A memory location to write a 64-bit serial nu mber is

provided. It is a writeable nonvolatile register that

can be locked by the user once the serial number is

set. The serial number registers can be written an

unlimited number of times. However once the lock bit

is set the values cannot be altered and the lock

cannot be removed. Once locked the serial number

registers can still be read by the system.

The serial number is located in registers 11h to 18h.

The lock bit is SNL, register 0Bh, b it 7. Setting the

SNL bit to a 1 disables writes to the serial number

registers, and the SNL bit cannot be cleared.

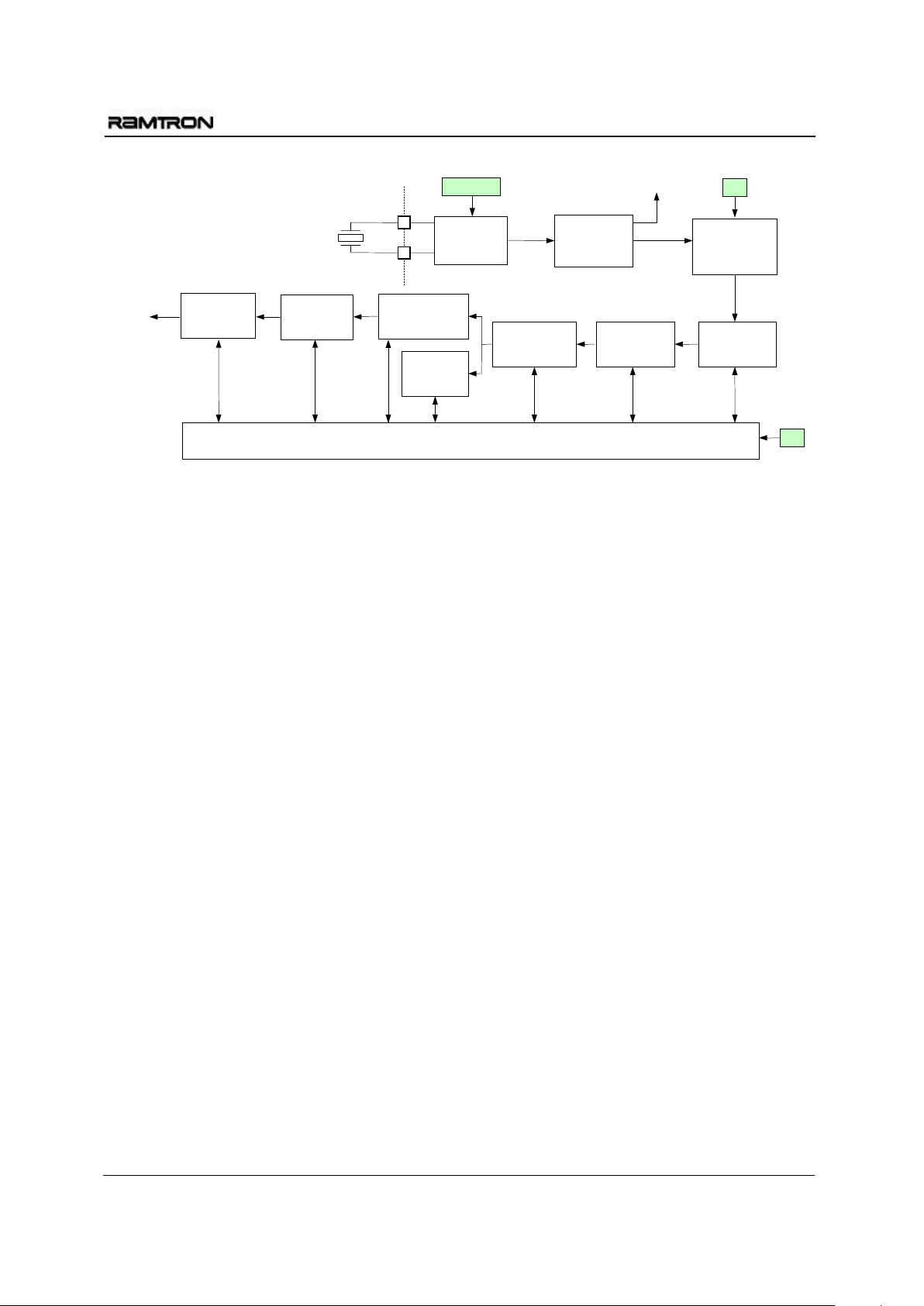

Real-time Clock Operation

The real-time clock (RTC) is a timekeeping device

that can be battery or capacitor backed for

permanently-powered operation. It offers a software

calibration feature that allows high accuracy.

The RTC consists of an oscillator, clock divider, and

a register system for user access. It divides down the

32.768 kHz time-base and provides a minimum

resolution of seconds (1 Hz). Static registers provide

the user with read/write access to the time values. It

includes registers for seconds, minutes, hours, dayof-the-week, date, months, and years. A block

diagram (Figure 7) illustrates the RTC function.

The user registers are synchronized with the

timekeeper core using R and W bits in register 00h

described below. Changing the R bit from 0 to 1

transfers timekeeping i nformation from the core into

holding registers that can be read by the user. If a

timekeeper update is pend ing while R is set, then t he

core will be updated prior to loading the user

registers. The registers are frozen and will not be

updated again until the R bit is cleared to 0 . R is used

for reading the time.

Setting the W bit to 1 locks the user registers.

Clearing it to 0 causes the values in the user registers

to be loaded into the timekeeper core. W is used for

writing new time values. Users should be certain not

to load invalid values, such as FFh, to the

timekeeping registers. Updates to the timekeeping

core occur continuously except when locked.

Backup Power

The real-time clock/calendar is intended to be

permanently powered. When the primary system

power fails, the voltage on the VDD pin will drop.

When VDD drops below 2.5V, the RTC (and event

counters) will switch to the backup power supply on

VBAK. The clock uses very little current which

maximizes battery or capacitor life.

When inserting a battery into a system board,

higher-than-normal battery drain may occur. It is

recommended that your system power-up

procedure complies with one of the following:

Scenario #1

a) Apply Vdd to board.

b) Insert battery. At this point, I

BAK

is zero.

c) When V

DD

is powered down, the I

BAK

current

will be less than 1µA.

Scenario #2

a) Insert battery without power to board (V

DD

is

off). At this point, the I

BAK

current may be

much higher than the 1µA spec limit. An

extended period of time (days) in this state

could significantly reduce battery life.

b) Apply V

DD

to board. I

BAK

goes to zero.

c) When V

DD

is powered down, the I

BAK

current

will be less than 1µA.

Trickle Charger

To facilitate capacitor backup the VBAK pin can

optionally provide a tric kle charge curre nt. When the

VBC bit, register 0Bh bit 2, is set to 1 the VBAK pin

will source approximately 15 µA until VBAK

reaches VDD or 3.75V whichever is less. In 3V

systems, this charges the capacitor to VDD without

an external diode and resistor charger. In 5V systems,

it provides the same convenience and also prevents

the user from exceeding the VBAK maximum

voltage specification.

!

!!

! Note: systems using lithium batteries should clear

the VBC bit to 0 to prevent battery charging. The

VBAK circuitry includes an internal 1 K

Ω

series

resistor as a safety element.

16-bit Counter

CNT1

CC

CNT2

C1P

C2P

16-bit Counter

FM4005

Rev. 2.3

Oct. 2006 Page 7 of 23

Figure 7. Real-Time Clock Core Block Diagram

Calibration

When the CAL bit in register 00h is set to 1, the

clock enters calibration mode. In calibration mode,

the CAL/PFO output pin is dedicated to the

calibration function and the comparator output is

temporarily unavailable. Calibration operates by

applying a digital correction to the counter based on

the frequenc y error. In this mode, the CAL/ PFO pin

is driven with a 512 Hz (nominal) square wave. Any

measured deviation from 512 Hz translates into a

timekeeping error. The user converts the measured

error in ppm and writes the appropriate correction

value to the calibration register. The correction

factors are listed in the table below. Positive ppm

errors require a negative adjustment that removes

pulses. Negative ppm errors require a positive

correction that adds pulses. P ositive pp m adjustments

have the CALS (sign) bit set to 1, where as negative

ppm adjustments have CA LS = 0. After calibration,

the clock wi ll have a maxi mum error o f ± 2.17 ppm

or ± 0.09 minutes per month at the calibrated

temperature.

The calibration setting is stored in a nonvolatile

register so is not lost should t he backup source fail. It

is accessed with bits CAL.4-0 in register 01h. This

value only can be written when the CAL bit is set to a

1. To exit the calibration mode, the user must clear

the CAL bit to a 0. When the CAL bit is 0, the

CAL/PFO pin will revert to the comparator output

function.

32.768 kHz

crystal

Oscillator

Clock

Divider

Update

Logic

512 Hz

W

R

Seconds

7 bits

Minutes

7 bits

Hours

6 bits

Date

6 bits

Months

5 bits

Years

8 bits

CF

Days

3 bits

User Interface Registers

1 Hz

OSCEN

Loading...

Loading...