RAMTRON FM3808-70-T Datasheet

Product Preview

FM3808

256Kb Bytewide FRAM w/Real-Time Clock

Features

256K bit Ferroelectric NonVolatile RAM

• Organized as 32,752 x 8 bits

• High Endurance 100 Billion (10

• 10 year Data Retention

• NoDelay™ Writes

• 70 ns Access Time/ 130 ns Cycle Time

• Built-in Low V

Protection

DD

Real-Time Clock/Calendar Function

• Clock Registers in Top 16 bytes of Address Space

• Backup Power from External Capacitor or Battery

• Tracks Seconds through Centuries in BCD Format

• Tracks Leap Years through 2099

• Runs from a 32.768 kHz Timekeeping Crystal

Description

The FM3808 combines a 256Kb FRAM array with a

real-time clock and a system supervisor function. The

timekeeping function is driven by a user supplied

32.768 kHz crystal. It maintains time and date

settings in the a bsence of system power through the

user’s choice of backup power source – either

capacitor or battery. In either case data in the memory

array does not depend on the backup source, it

remains nonvolatile in FRAM. In addition to

timekeeping, the FM3808 includes a system

supervisor to manage low V

a watchdog timer function. A programmable interrupt

output pin allows the user to select the supervisor

functions and the polarity of the signal.

Both the FRAM array and the timekeeping function

are accessed through the memory interface. The

upper 16-address locations of the memory space are

allocated to the timekeeping registers rather than to

memory. The FRAM array provides data retention

for 10 years in the absence of system power, and is

not dependent on the backup power source used for

the clock. This eliminates system concerns over data

loss in a traditional battery-backed RAM solution. In

addition, clock and supervisor control settings are

implemented in FRAM rather than battery-backed

RAM, making them more dependable. The FM3808

offers guaranteed operation over an industrial

temperature range of -40°C to +85°C.

DD

11

) Read/Writes

power conditions and

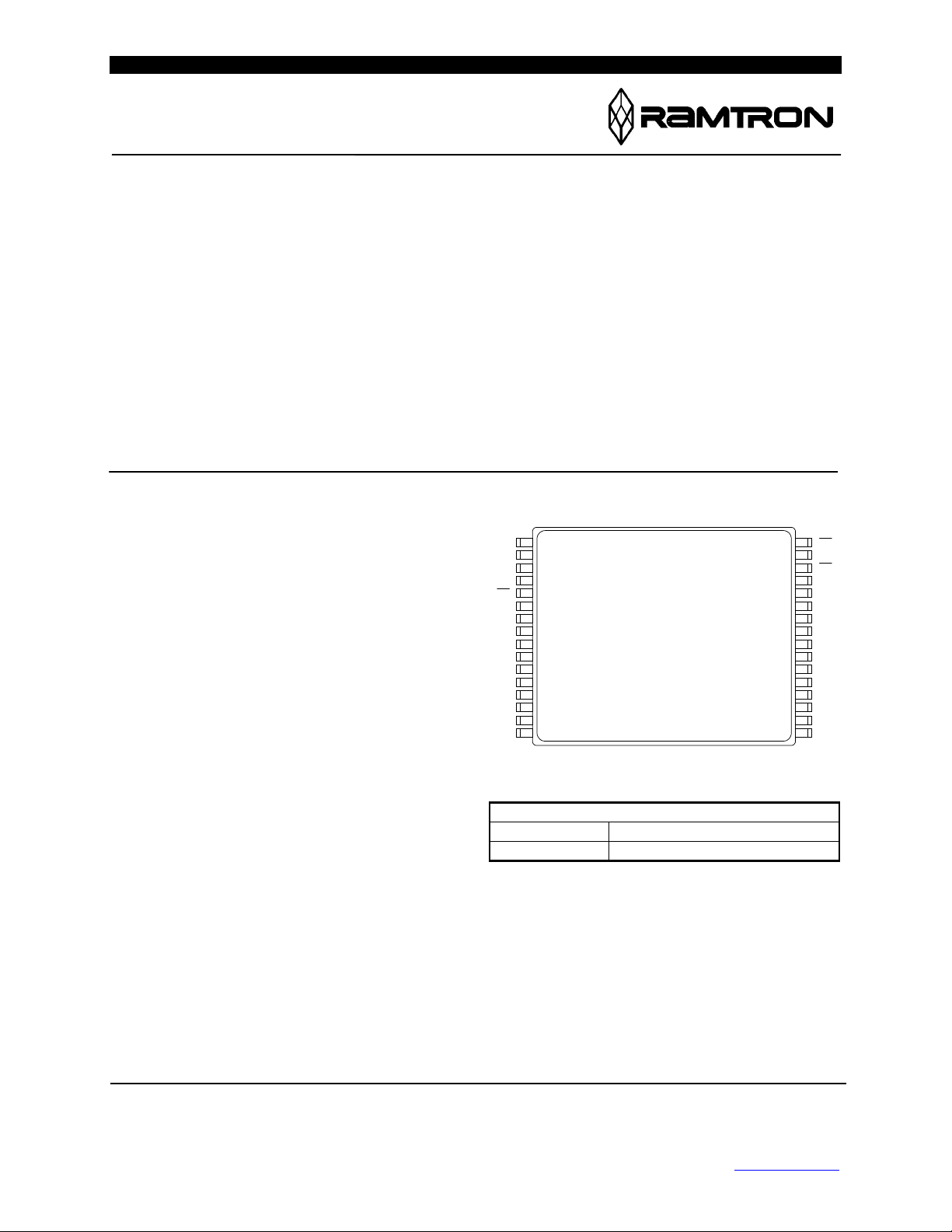

Pin Configuration

A11

A9

A8

A13

WE

VBAK

INT

VDD

X1

X2

A14

A12

A7

A6

A5

A4 A3

FM3808-70-T 70 ns access, 32-pin TSOP

FM3808DK DIP module development kit

Documentation for the DIP module development kit is

provided separately.

System Supervisor Function

• Programmable Clock/Calendar Alarm

• Programmable Watchdog Timer

• Programmable Power Supply Monitor

• Interrupt Output - Programmable active high/low

• Control Settings Inherently NonVolatile

• Generates either Processor Reset or Interrupt

Low Power Operation

• 5V Operation for Memory and Clock Interface

• Backup Voltage as low as 2.5V

• 25 mA I

• 1 µA I

Active Current

DD

Clock Backup Current

BAK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

OE

A10

CE

DQ7

DQ6

DQ5

DQ4

DQ3

VSS

DQ2

DQ1

DQ0

A0

A1

A2

Ordering Information

This is a product under development. Characteristic data and other

specifications are design goals. Ramtron reserves the right to change 1850 Ramtron Drive, Colorado Springs, CO 80921

or discontinue the product without notice. (800) 545-FRAM, (719) 481-7000, FAX (719) 481-7058

Rev 0.2

Sept 2001 Page 1 of 27

Ramtron International Corporation

www.ramtron.com

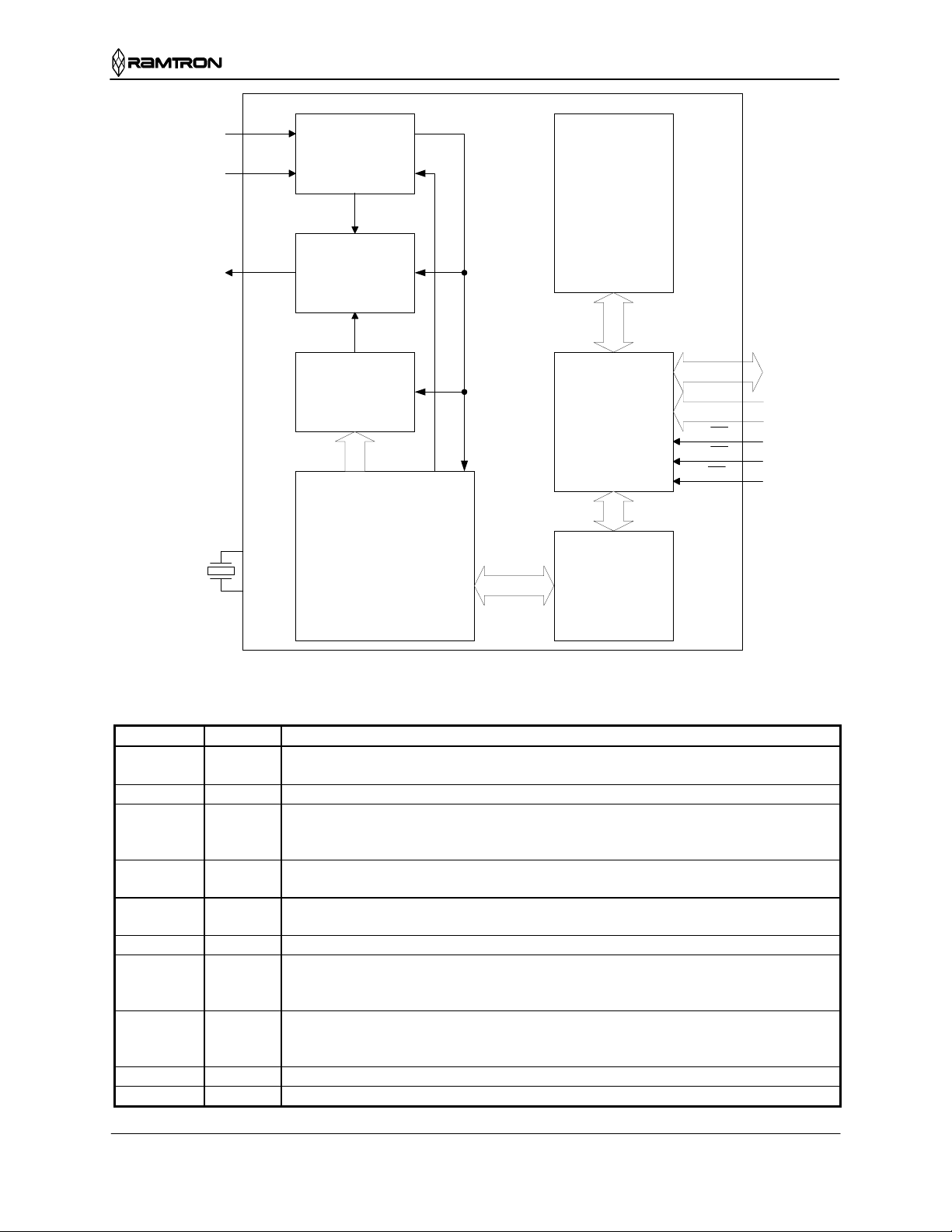

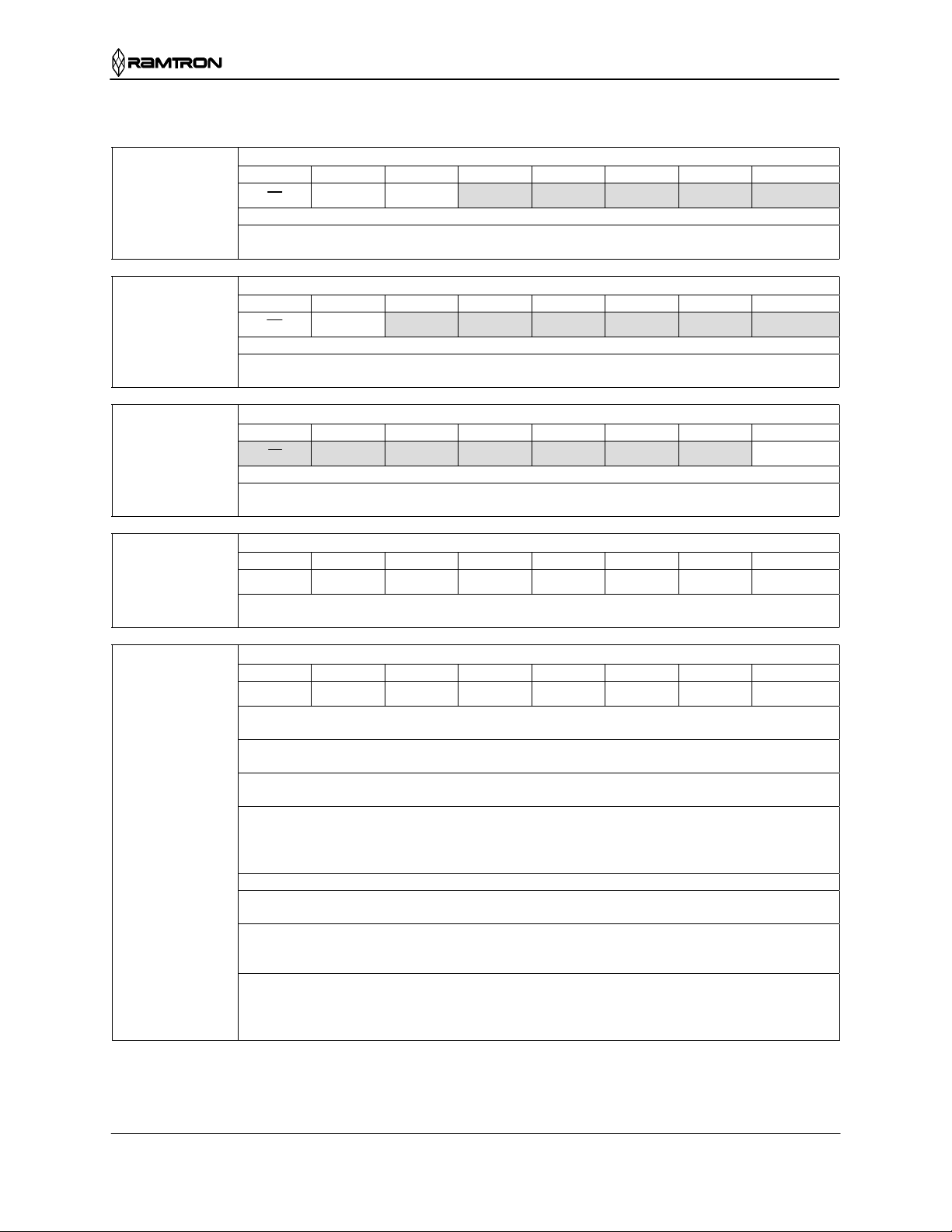

FM3808

Switched

VDD

VBAK

System Supervisor

Low VDD monitor/

Watchdog timer

power

32.768

kHz

INT

X1

X2

Watchdog

Interrupt Control

Logic

Alarm

Clock/Calendar

timebase

FRAM Array

32,752x8

Address Decoder/

Bus Interface

16 Clock/Calendar

Registers

Data

Address

CE

OE

WE

Figure 1. Block Diagram

Pin Description

Pin Name I/O Pin Description

A0-A14 Input Address: The 15 address inputs select one of 32,752 bytes in the FRAM array or one of

16 bytes in the clock/calendar. The address is latched on the falling edge of /CE.

DQ(7:0) I/O Data: Bi-directional 8-bit data bus for accessing the FRAM array and clock.

/CE Input Chip Enable: The active low /CE input selects the device. The falling edge of /CE

internally latches the address. Address changes that occur after /CE has transitioned

low are ignored until the next falling edge occurs.

/OE Input Output Enable: The active low /OE input enables the data output buffers during read

cycles. Deasserting /OE high causes the DQ pins to tri-state.

/WE Input Write Enable: T he active low /WE low enables data on the DQ pins to be written to the

address location latched by the falling edge of /CE.

X1, X2 Input Connect 32.768 kHz crystal.

INT Output Interrupt output: This output can be programmed to respond to the clock alarm, the

watchdog timer, and the power monitor. It is programmable to either active high

(push/pull) or active low (open-drain).

V

Supply Backup Supply Voltage: This supply is used to maintain power for the clock. It must

BAK

remain between 2.5V and V

battery. Current is drawn from V

-0.3V. Typically it is supplied by either a capacitor or a

DD

when VDD is below the V

BAK

voltage.

BAK

VDD Supply Supply Voltage: 5V

VSS Supply Ground.

Rev 0.2

Sept 2001 Page 2 of 27

FM3808

y

g

g

Functional Truth Table

/CE /WE /OE Function

H X X Standby/Precharge

!

X X Latch Address

L H L Read

L L X Write

Overview

The FM3808 integrates three complementary but

distinct functions under a common interface in a

single package. First, is the 32Kx8 FRAM memory

block (minus 16 bytes), second is the real-time

clock/calendar, and third is the system supervisor.

The functions are integrated to enhance their

individual performance, so that each provides better

capability than three similar stand-alone devices. All

functions use the same bytewide address/data

interface and are memory mapped. Special functions

including the clock and supervisor are controlled by

registers that reside in the top of the combined

memory map. The register map is described below,

followed by a detailed description of each functional

block.

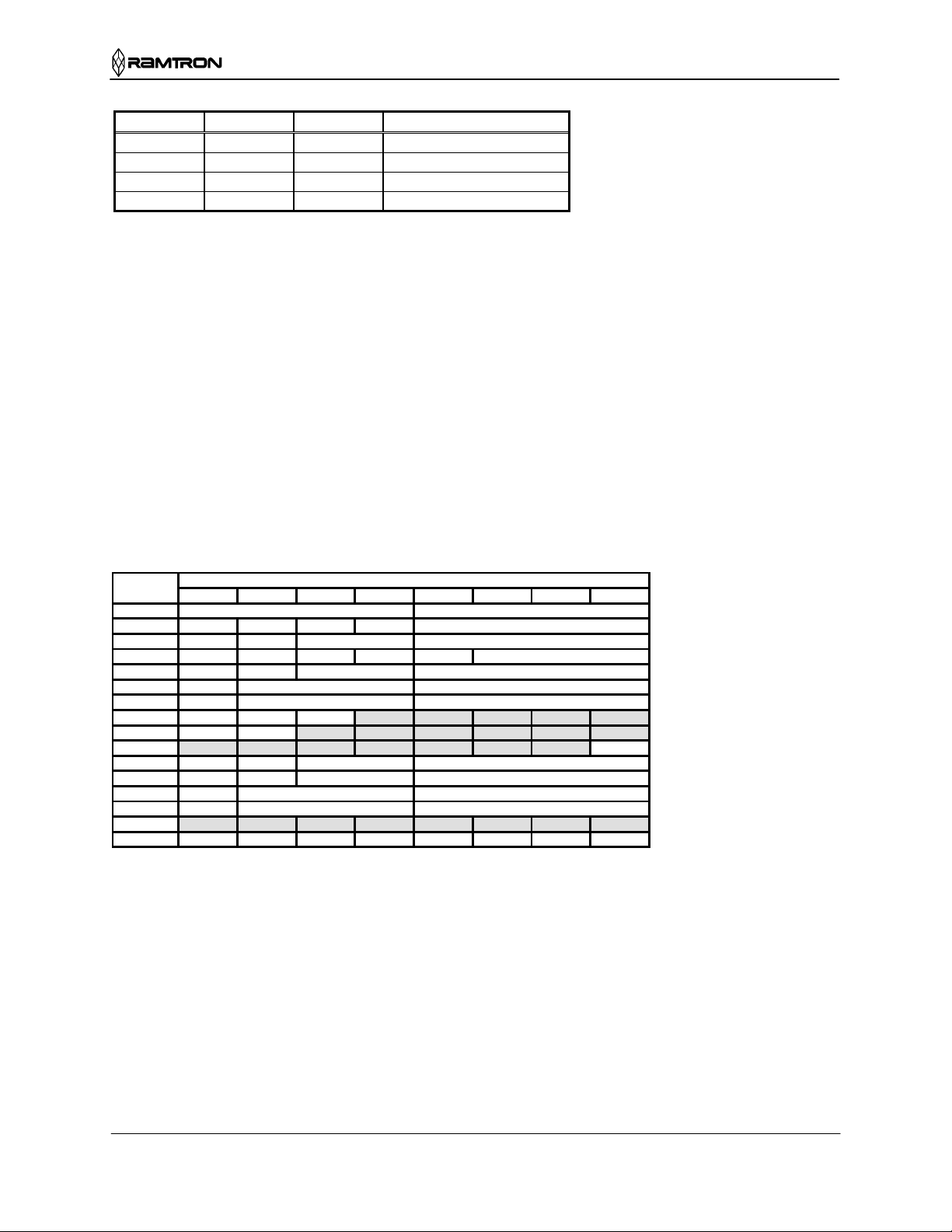

Register Map

The interface to clock and supervisor functions is via

16 address locations at the top of the address space.

The registers contain timekeeping data, control bits,

or information flags. A short description of each

register follows. Detailed descriptions of each

function follow the register summary.

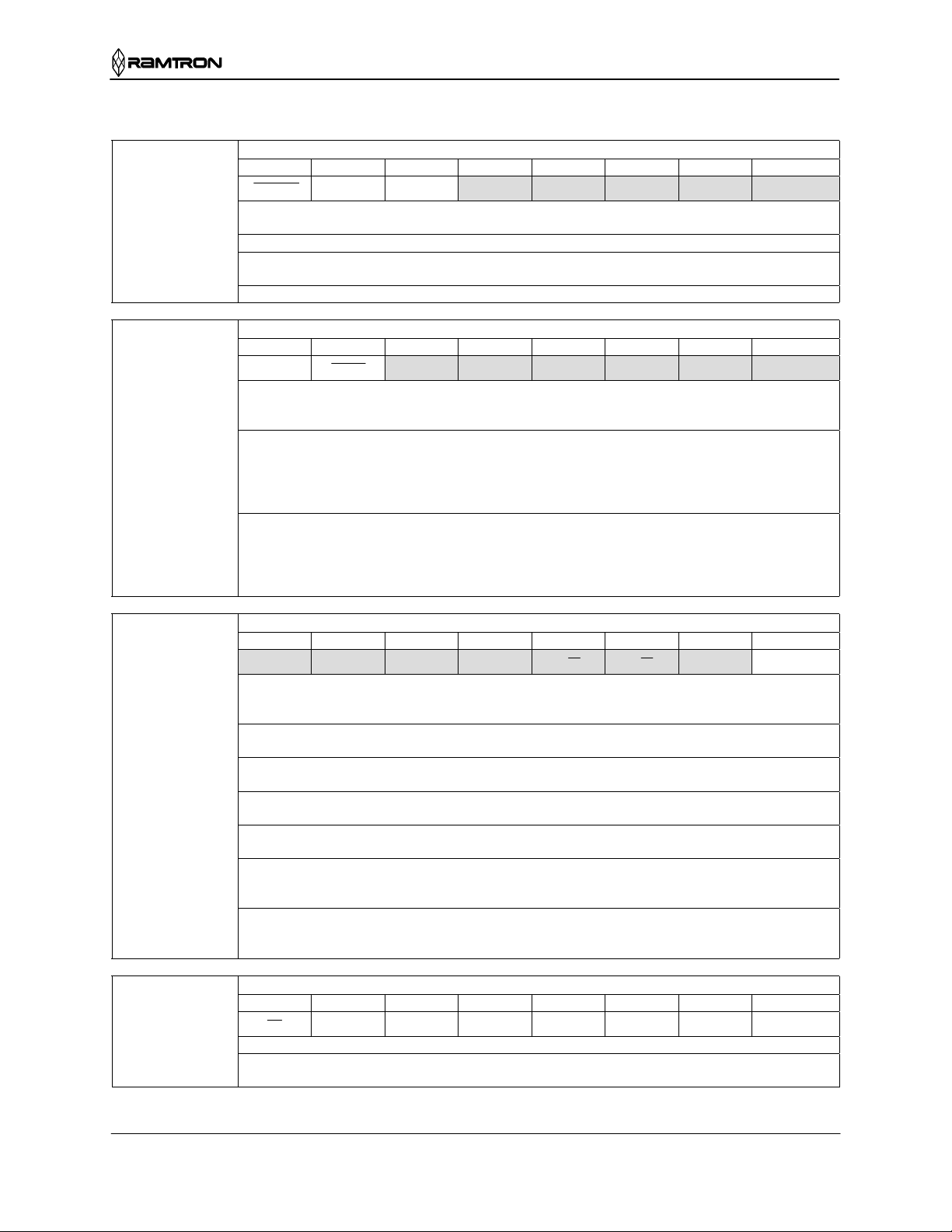

Register Map Summary Table

Address

7FFFh 10 years years

7FFEh

7FFDh

7FFCh

7FFBh

7FFAh

7FF9h

7FF8h

7FF7h

7FF6h

7FF5h

7FF4h

7FF3h

7FF2h

7FF1h

7FF0h

D7 D6 D5 D4 D3 D2 D1 D0 Function Range

00010 mo

00

00000

00

0

0

/OSCEN reserved reserved CALS CAL3 CAL2 CAL1 CAL0 Control-NV

WDS /WDW WDT5 WDT4 WDT3 WDT2 WDT1 WDT0 Watchdo

WIE AIE PFE ABE H/L P/L VINT reserved Interrupts

/Match 0

/Match 0

/Match

/Match

WDF AF PF CF TST CAL W R Fla

Alarm 10 minutes Alarm minutes

Alarm 10 seconds Alarm seconds

10 date date

10 hours hours

10 minutes minutes

10 seconds seconds

Alarm 10 date Alarm date

Alarm 10 hours hours

Data

months

day

Years 00-99

Month 1-12

Date 1-31

Da

Hours 0-23

Minutes 0-59

Seconds 0-59

Alarm Date 1-31

Alarm Hours 0-23

Alarm Minutes 0-59

Alarm Seconds 0-59

User-NV

s/Control

1-7

Note that the shaded bits are implemented in FRAM and therefore are nonvolatile even without backup power.

Rev 0.2

Sept 2001 Page 3 of 27

FM3808

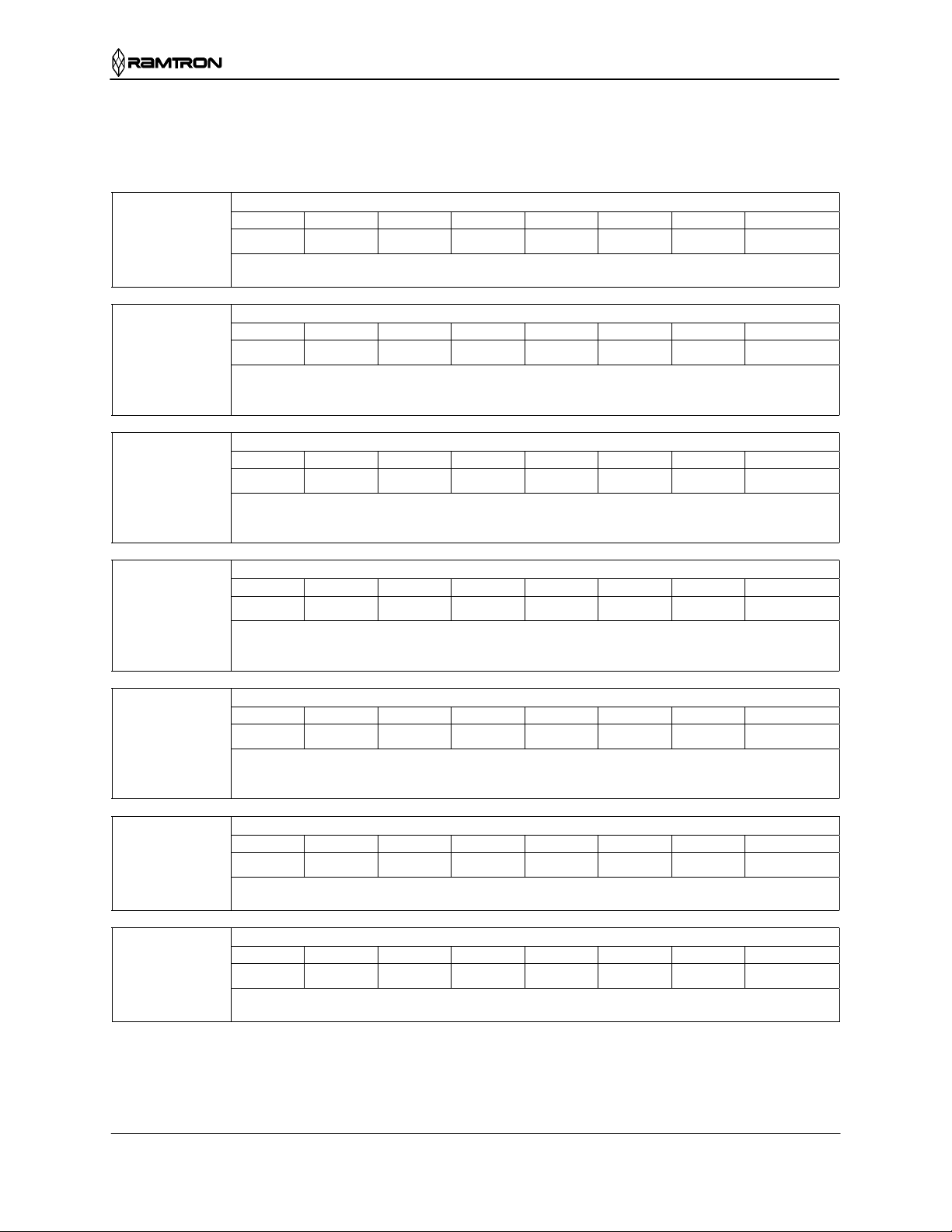

Table 1. Register Map

Address Description

7FFFh

Contains the lower two BCD digits of the year. Lower nibble contains the value for years; upper nibble

7FFEh

Contains the BCD digits for the month. Lower nibble contains the lower digit and operates from 0 to 9;

7FFDh

Contains the BCD digits for the date of the month. Lower nibble contains the lower digit and operates

7FFCh

Lower nibble contains a value that correlates to day of the week. Day of the week is a ring counter that

7FFBh

Contains the BCD value of hours in 24-hour format. Lower nibble contains the lower digit and operates

7FFAh

Contains the BCD value of minutes. Lower nibble contains the lower digit and operates from 0 to 9;

7FF9h

Contains the BCD value of seconds. Lower nibble contains the lower digit and operates from 0 to 9;

Timekeeping – Years

D7 D6 D5 D4 D3 D2 D1 D0

10 year.3 10 year.2 10 year.1 10 year.0 Year.3 Year.2 Year.1 Year.0

contains the value for 10s of years. Each nibble operates from 0 to 9. The range for the register is 0-99.

Timekeeping – Months

D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 10 Month Month.3 Month.2 Month.1 Month.0

upper nibble (one bit) contains the upper digit and operates from 0 to 1. The range for the register is 1-

12.

Timekeeping – Date of the month

D7 D6 D5 D4 D3 D2 D1 D0

0 0 10 date.1 10 date.0 Date.3 Date.2 Date.1 Date.0

from 0 to 9; upper nibble contains the upper digit and operates from 0 to 3. The range for the register is

1-31.

Timekeeping – Day of the week

D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 0 0 Day.2 Day.1 Day.0

counts from 1 to 7 then returns to 1. The user must assign meaning to the day value, as the day is not

integrated with the date.

Timekeeping – Hours

D7 D6 D5 D4 D3 D2 D1 D0

0 0 10 hours.1 10 hours.0 Hours.3 Hours2 Hours.1 Hours.0

from 0 to 9; upper nibble (two bits) contains the upper digit and operates from 0 to 2. The range for the

register is 0-23.

Timekeeping – Minutes

D7 D6 D5 D4 D3 D2 D1 D0

0 10 min.2 10 min.1 10 min.0 Min.3 Min.2 Min.1 Min.0

upper nibble contains the upper minutes digit and operates from 0 to 5. The range for the register is 0-59.

Timekeeping – Seconds

D7 D6 D5 D4 D3 D2 D1 D0

0 10 sec.2 10 sec.1 10 sec.0 Seconds.3 Seconds.2 Seconds.1 Seconds.0

upper nibble contains the upper digit and operates from 0 to 5. The range for the register is 0-59.

Rev 0.2

Sept 2001 Page 4 of 27

FM3808

Address Description

7FF8h

/OSCEN /Oscillator Enable. When set to 1, the oscillator is halted. When set to 0, the oscillator runs. Disabling

Reserved Do not use. Should remain set to 0.

CALS Calibration sign. Determines if the calibration adjustment is applied as an addition to or as a subtraction

CAL.3-0 These four bits control the calibration of the clock. These bits are implemented in FRAM.

7FF7h

WDS Watchdog Strobe. Setting this bit to 1 reloads and restarts the watchdog timer. Setting the bit to 0 has no

/WDW Watchdog Write Enable. Setting this bit to 1 masks the watchdog timeout value (WDT.5-0) so it cannot

WDT.5-0 Watchdog Timeout selection. The watchdog timer interval is selected by the 6-bit value in this register.

7FF6h

WIE Watchdog Interrupt Enable. When set to 1 and a watchdog timeout occurs, the watchdog timer drives

AIE Alarm Interrupt Enable. When set to 1, the alarm match drives the interrupt pin as well as the AF flag.

PFE Power-fail Interrupt Enable. When set to 1, the power-fail monitor drives the pin as well as the PF flag.

ABE Alarm Battery-backup Enable. When set to 1, the alarm interrupt (as controlled by AIE) will function

H/L High/Low. When set to a 1, the Interrupt pin is push/pull active high. When set to a 0, the interrupt pin

P/L Pulse/Level. When set to a 1, the interrupt pin is driven active (determined by H/L) by an interrupt

VINT Voltage Interrupt. Selects the voltage on VDD that generates a power-fail flag. When set to a 1, the flag

7FF5h

Contains t he alarm value for the date of the month and the mask bit to select or deselect the date value.

/M

Control-Nonvolatile

D7 D6 D5 D4 D3 D2 D1 D0

OSCEN Reserved Reserved CALS CAL.3 CAL.2 CAL.1 CAL.0

the oscillator can save battery power during storage. On a no battery power up, this bit is set to 1.

from the time-base. This bit is implemented in FRAM. Calibration is explained below

Watchdog Timer

D7 D6 D5 D4 D3 D2 D1 D0

WDS WDW

affect. The bit is cleared automatically once the watchdog timer is reset. The WDS bit is write only.

Reading it always will return a 0.

be written. This allows the user to strobe the watchdog without disturbing the timeout value. Setting this

bit to 0 allows bits 5-0 to be written on the next write to the Watchdog register. The new value will be

loaded on the next internal watchdog clock after the write cycle is complete. This function is explained

in more detail in the watchdog Timer section below.

It represents a multiplier of the 32 Hz count (31.25 ms). The minimum range or timeout value is 31.25

ms (a setting of 1) and the maximum timeout is 2 seconds (setting of 3Fh). Setting the watchdog timer

register to 0 disables the timer. These bits can be written only if the /WDW bit was cleared to 0 on a

previous cycle.

Interrupts

D7 D6 D5 D4 D3 D2 D1 D0

WIE AIE PFE ABE H/L P/L VINT Reserved

the interrupt pin as well as the WDF flag. When set to 0, the watchdog timeout affects only the WDF

flag.

When set to 0, the alarm match only affects the AF flag.

When set to 0, the power-fail monitor affects only the PF flag.

even in battery backup mode. When set to 0, the alarm will occur only when VDD>VLO.

is open drain active low.

source for approximately 200 ms. When set to a 0, the interrupt pin is driven to an active level (as set by

H/L) until the flag register is read.

occurs at 4.75V. When set to 0 the flag occurs at 4.6V. The interrupt pin is enabled by the PFE bit,

otherwise only an internal flag is set.

Alarm – Date of the month

D7 D6 D5 D4 D3 D2 D1 D0

M 0 10 date.1 10 date.0 Date.3 Date.2 Date.1 Date.0

Match. Setting this bit to 0 causes the date value to be used in the alarm match. Setting this bit to 1

causes the match circuit to ignore the date value.

WDT.5 WDT.4 WDT.3 WDT.2 WDT.1 WDT.0

Rev 0.2

Sept 2001 Page 5 of 27

FM3808

Address Description

7FF4h

Contains the alarm value for the hours and the mask bit to select or deselect the hours value.

/M Match. Setting this bit to 0 causes the hours value to be used in the alarm match. Setting this bit to 1

7FF3h

Contains t he alarm value for the minutes and th e mask bi t to select or deselect the minutes value

/M Match. Setting this bit to 0 causes the minutes value to be used in the alarm match. Setting this bit to 1

7FF2h

Contains the alarm value for the seconds and the mask bit to select or deselect the minutes value.

/M Match. Setting this bit to 0 causes the seconds value to be used in the alarm match. Setting this bit to1

7FF1h

This register is an uncommitted nonvolatile register. The user register is not manipulated by the real-

7FF0h

WDF Watchdog Timer Flag. This bit is set to 1 when the watchdog timer is allowed to reach 0 without being

AF Alarm Flag. This bit is set to 1 when the time and date match the values stored in the alarm registers

PF Power-fail Flag. This bit is set to 1 when power falls below the power-fail interrupt threshold VINT. It

CF Cen t ury Overflow Flag. This bit is set to a 1 when the values in the years register overflows from 99 to

TST Invokes factory test mode. Users should always set this bit to 0.

CAL Calibration Mode. When set to 1, the clock enters calibration mode. When CAL is set to 0, the clock

W Write Time. Setting the W bit to 1 freezes updates of the timekeeping registers. The user can then write

R Read Time. Setting the R bit to 1 copies a static image of the timekeeping registers and places them in a

Alarm – Hours

D7 D6 D5 D4 D3 D2 D1 D0

M 0 10 hours.1 10 hours.0 Hours.3 Hours2 Hours.1 Hours.0

causes the match circuit to ignore the hours value.

Alarm – Minutes

D7 D6 D5 D4 D3 D2 D1 D0

M 10 min.2

causes the match circuit to ignore the minutes value.

Alarm – Seconds

D7 D6 D5 D4 D3 D2 D1 D0

M 10 sec.2 10 sec.1 10 sec.0 Seconds.3 Seconds.2 Seconds.1 Seconds.0

causes the match circuit to ignore the seconds value.

User-NonVolatile

D7 D6 D5 D4 D3 D2 D1 D0

time clock other than to provide nonvolatile storage of the contents.

Flags/Control

D7 D6 D5 D4 D3 D2 D1 D0

WDF AF PF CF TST CAL W R

reset by the user. It is cleared to 0 when the Flag register is read. It is read-only for the user.

with the match bit(s) = 0. It is cleared when the Flag register is read. It is read -only for the user.

is cleared to 0 when the Fl ag register is read. It is read-only for the user.

00. This indicates a new century, such as going from 1999 to 2000 or 2099 to 2100. The user should

record the new century information as needed. This bit is cleared to 0 when the Flag register is read. It is

read-only for the user.

operates normally.

them with updated values. Setting the W bit to 0 causes the contents of the time registers to be

transferred to the timekeeping counters. This bit affects registers xF, xE, xD, xC, xB, xA, and x9.

holding register. The user can then read them without concerns over changing values causing system

errors. The R bit going from 0 to 1 causes the timekeeping capture, so the bit must be returned to 0 prior

to reading again . This bit affects registers xF, xE, xD, xC, xB, xA, and x9.

10 min.1 10 min.0 Min.3 Min.2 Min.1 Min.0

Rev 0.2

Sept 2001 Page 6 of 27

FM3808

Real-time Clock Operation

The real-time clock (RTC) consists of an oscillator, a

divider, and a register system to access the

information. It divides down the 32.768 kHz timebase to provide the user timekeeping resolution of

one second (1Hz). Static registers provide the user

with read/write access to the time values. The

synchronization of these registers with the timekeeper

core is performed using R and W bits in register

7FF0h.

Setting the R bit from 0 to 1 causes a transfer of the

timekeeping information to holding registers that can

be read by the user. If a timekeeper update is in

progress when the R is set, the update will be

completed prior to loading the registers. Another

update cannot be performed unless the R bit is first

cleared to 0 again.

Setting the W bit causes the timekeeper to freeze

updates. Clearing it to 0 causes the values in the time

registers to be written into the timekeeper core. Users

should be sure not to load invalid values, such as FFh

to any of the timekeeping registers.

Updates to the timekeeping core occur continuously

except when frozen. A diagram of the timekeeping

core is shown below.

Backup Power

The real-time clock/calendar is intended for

permanently powered operation. When primary

system power fails, the voltage on V

When it crosses the voltage on the V

will drop.

DD

supply pin,

BAK

the clock power will switch to the backup power

supply V

. The supervisor function, described

BAK

below, controls the switchover process as part of a

more complete power management circ uit.

The clock uses very little current which maximizes

battery life. Although a backup batter y may be used

with the FM3808, the key advantage to combining a

clock function with FRAM is that the configuration

data (shaded regsiter bits in Table 2) is nonvolatile

and does not require a battery backup power source.

Therefore, it is more practical to use a capacitor as a

backup energy source than a battery-backed

RAM/clock combo. With the FM3808, the user has

the choice of using a battery or a capacitor as the

backup source. Some of the parameters used in the

capacitor vs. battery decision include the expected

duration of power outages, the difficulty of resetting

the time if lost, and the cost tradeoff of using a small

battery versus a capacitor.

The following functions are powered from the backup

power source when V

DD

< V

(backup mode) :

BAK

• Clock/calendar core

• Alarm interrupt/comparator

• INT pin driver (determined by ABE & AIE

bits); active low only

• Flags connected to related functions

The following functions are not powered and are

disabled when V

< VLO :

DD

• User interface

• Watchdog timer

• Power monitor & band-gap (V

< ≈ 2.0V)

DD

• Flags connected to related functions

• All FRAM access & updates

• Calibration operation

• INT driver if active high is programmed

Rev 0.2

Sept 2001 Page 7 of 27

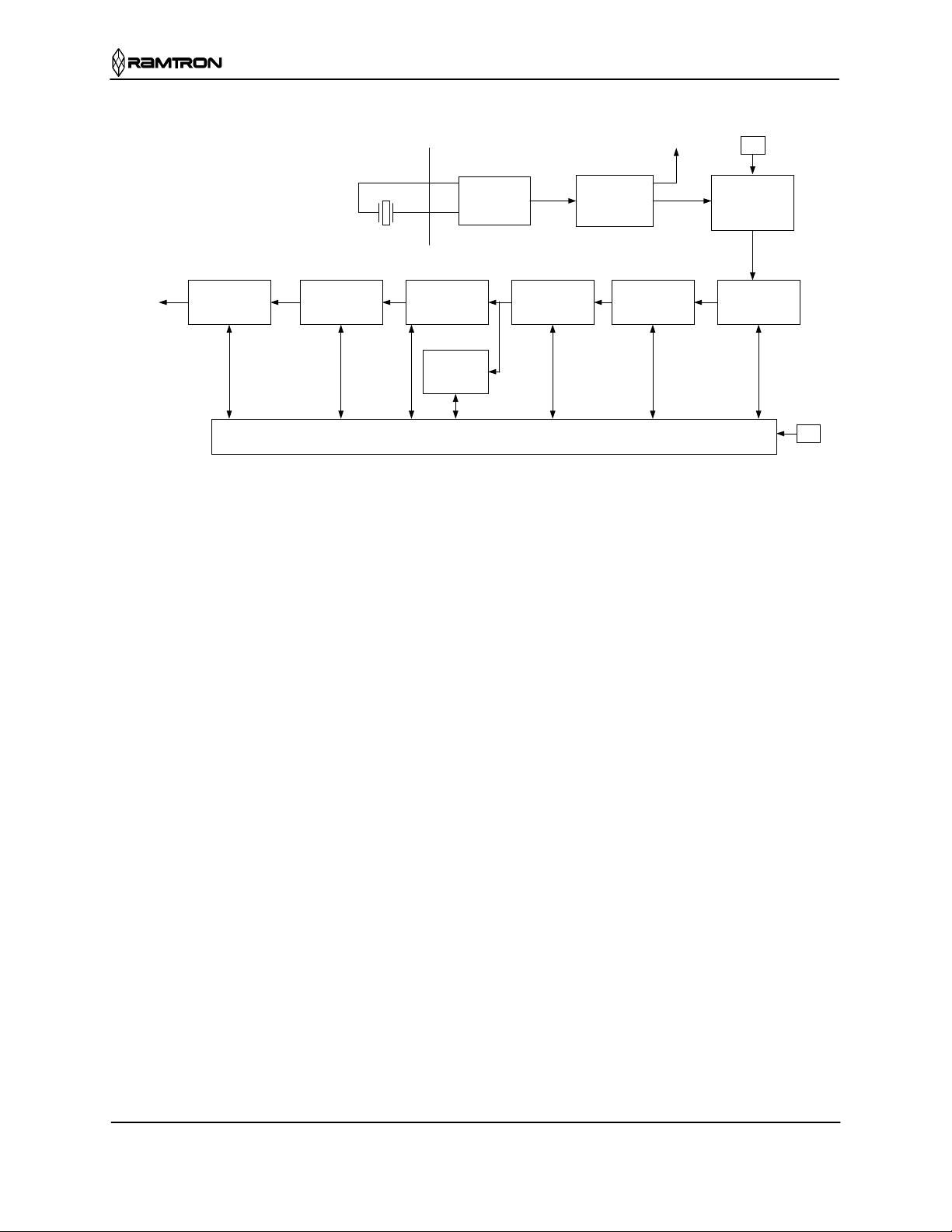

FM3808

32 Hz

512 Hz

W

32.768 kHz

crystal

CF

Years

8 bits

Months

5 bits

Date

6 bits

Days

3 bits

User Interface Registers

Figure 2. Real-time Clock Core Block Diagram

Calibration

When the CAL bit in register 7FF0.2 is set to 1, the

clock enters calibration mode. Interrupts are disabled

in CAL mode. Calibration operates by applying a

digital correction to the counter based on the

frequency error. In CAL mode, the INT pin is driven

with a 512 Hz nominal square wave. Any measured

deviation from 512 Hz is converted into an error in

ppm. This error corresponds to a correction value that

must then be written by the user into the calibration

register 7FF8h. The correction factors are listed in the

Table 2.

Positive ppm errors require a negative adjustment that

removes pulses. Negative ppm errors require a

positive correction that adds pulses. Positive ppm

adjustments have the CALS bit set to 1, where as

negative ppm adjustments have CALS = 0. After

calibration, the clock will have a maximum error of

Oscillator

Hours

6 bits

Clock

Divider

1 Hz

Minutes

7 bits

Update

Logic

Seconds

7 bits

± 4.34 ppm or ± 0.19 minutes per month at the

calibrated temperature.

The calibration setting is nonvolatile and is stored in

7FF8.4-0. This value only can be written when the

CAL bit is set to a 1. To exit calibration mode, the

user should clear the CAL bit to a 0.

When the calibration mode is entered, the user can

measure the frequency error on the INT pin. This

error expressed in ppm translates directly into

timekeeping error. An offsetting calibration

adjustment corrects this error. However, the

correction is applied by adding or removing pulses on

a periodic basis. Therefore, the correction will not

appear on the 512 Hz output. The calibration

correction must be applied using the values shown in

Table 2. The timekeeping accuracy can be verified by

comparing the FM3808 time to a reference source.

R

Rev 0.2

Sept 2001 Page 8 of 27

FM3808

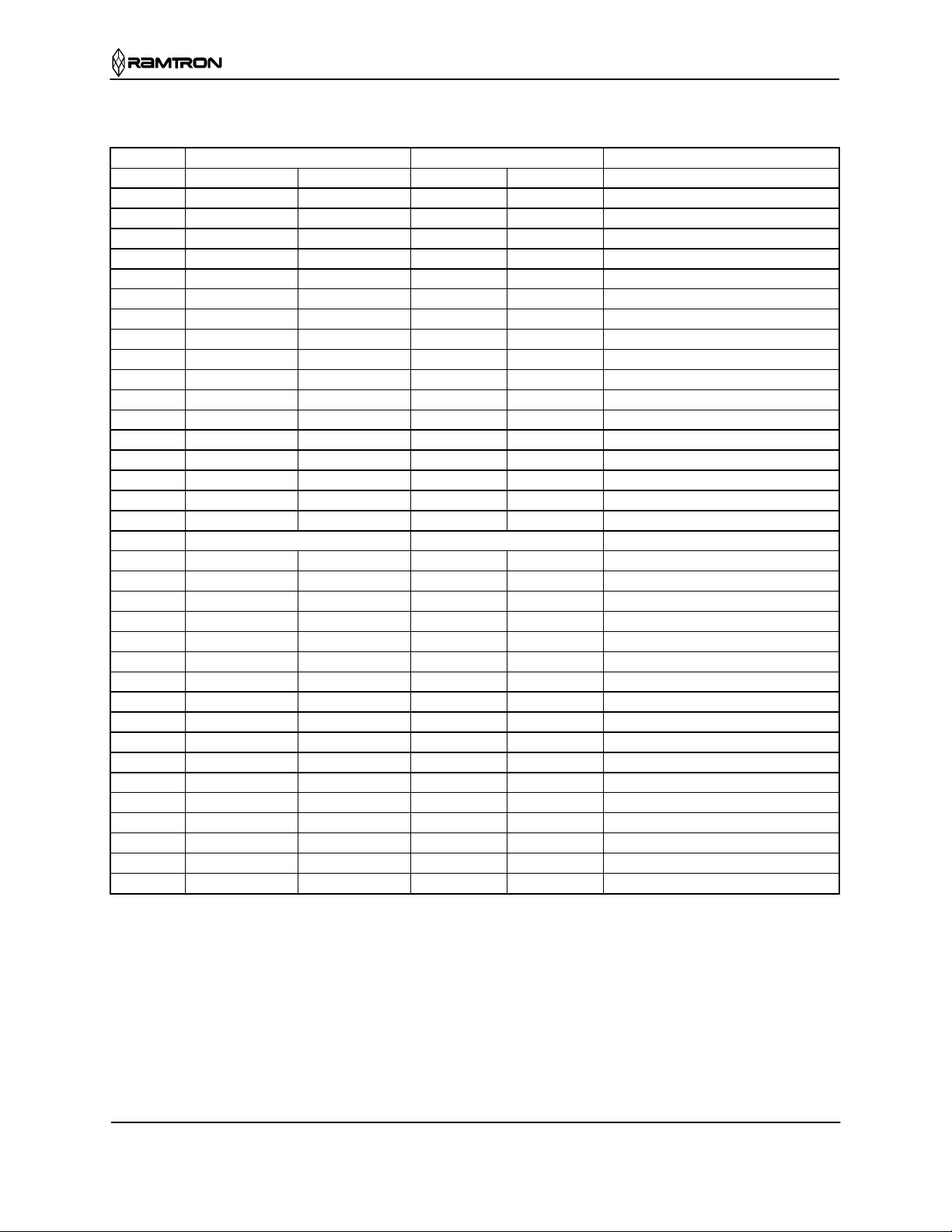

Table 2. Calibration Adjustments

Measured Frequency Range Error Range (ppm)

Min Max Min Max Program Calibration D4-D0

0 512.0000 511.9978 0 4.34 00000b

1 511.9978 511.9933 4.35 13.02 10001b

2 511.9933 511.9889 13.03 21.70 10010b

3 511.9889 511.9844 21.71 30.38 10011b

4 511.9844 511.9800 30.39 39.06 10100b

5 511.9800 511.9756 39.07 47.74 10101b

6 511.9756 511.9711 47.75 56.42 10110b

7 511.9711 511.9667 56.43 65.10 10111b

8 511.9667 511.9622 65.11 73.78 11000b

9 511.9622 511.9578 73.79 82.46 11001b

10 511.9578 511.9533 82.47 91.14 11010b

11 511.9533 511.9489 91.15 99.82 11011b

12 511.9489 511.9444 99.83 108.50 11100b

13 511.9444 511.9400 108.51 117.18 11101b

14 511.9400 511.9356 117.19 125.86 11110b

15 511.9356 511.9311 125.87 134.54 11111b

Measured Frequency Range Error Range (ppm)

Min Max Min Max Program Calibration D4-D0

0 512.0000 512.0022 0 4.34 00000b

1 512.0022 512.0067 4.35 13.02 00001b

2 512.0067 512.0111 13.03 21.70 00010b

3 512.0111 512.0156 21.71 30.38 00011b

4 512.0156 512.0200 30.39 39.06 00100b

5 512.0200 512.0244 39.07 47.74 00101b

6 512.0244 512.0289 47.75 56.42 00110b

7 512.0289 512.0333 56.43 65.10 00111b

8 512.0333 512.0378 65.11 73.78 01000b

9 512.0378 512.0422 73.79 82.46 01001b

10 512.0422 512.0467 82.47 91.14 01010b

11 512.0467 512.0511 91.15 99.82 01011b

12 512.0511 512.0556 99.83 108.50 01100b

13 512.0556 512.0600 108.51 117.18 01101b

14 512.0600 512.0644 117.19 125.86 01110b

15 512.0644 512.0689 125.87 134.54 01111b

Rev 0.2

Sept 2001 Page 9 of 27

Loading...

Loading...